## (19) **日本国特許庁(JP)**

HO1L 23/12

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2007-306039 (P2007-306039A)

(43) 公開日 平成19年11月22日(2007.11.22)

| (51) Int.C1. |           | F I  |       |      | テーマコード(参考) |

|--------------|-----------|------|-------|------|------------|

| HO1L 25/10   | (2006.01) | HO1L | 25/14 | Z    |            |

| HO1L 25/11   | (2006.01) | HO1L | 23/12 | 501S |            |

| HO1L 25/18   | (2006.01) | HO1L | 23/12 | 501W |            |

審査譜求 有 譜求項の数 11 〇L (全 51 頁)

|                       |                                                        | 一 音道        |                     |

|-----------------------|--------------------------------------------------------|-------------|---------------------|

| (21) 出願番号<br>(22) 出願日 | 特願2007-220385 (P2007-220385)<br>平成19年8月27日 (2007.8.27) | (71) 出願人    | 000003078<br>株式会社東芝 |

| (62) 分割の表示            | 特願2004-136255 (P2004-136255)                           | (- () 115 I | 東京都港区芝浦一丁目1番1号      |

|                       | の分割                                                    | (74)代理人     | 100058479           |

| 原出願日                  | 平成16年4月30日 (2004.4.30)                                 |             | 弁理士 鈴江 武彦           |

|                       |                                                        | (74)代理人     | 100091351           |

|                       |                                                        |             | 弁理士 河野 哲            |

|                       |                                                        | (74)代理人     | 100088683           |

|                       |                                                        |             | 弁理士 中村 誠            |

|                       |                                                        | (74)代理人     | 100108855           |

|                       |                                                        |             | 弁理士 蔵田 昌俊           |

|                       |                                                        | (74)代理人     | 100075672           |

|                       |                                                        |             | 弁理士 峰 隆司            |

|                       |                                                        | (74)代理人     | 100109830           |

|                       |                                                        |             | 弁理士 福原 淑弘           |

|                       |                                                        |             | 最終百に続く              |

### (54) 【発明の名称】半導体装置およびその製造方法

(2006, 01)

## (57)【要約】

【課題】構造的な汎用性が向上されており、単体での使用や複数個積層しての使用に拘らず使用でき、効率良く、かつ、低コストで容易に製造できる半導体装置を提供する。

【解決手段】チップ搭載基材41の一方の主面46a上には第1の配線5が設けられている。配線5に接続された第2の配線が基材本体42を貫通して他方の主面46b側に露出されている。半導体素子1が配線5に接続されて主面46a上に搭載されている。素子1および配線5を覆って封止部材10が主面46a上に設けられている。部材10の表面上には第3の配線47が設けられているとともに部材10の内部には配線5,47に接続された第4の配線48が設けられている。部材10の内部に形成された配線48を設けるための第4の配線用凹部49の径の大きさと、素子1、基材41、および部材10からなるパッケージ46の厚さとの比が1:1以下に設定されている。

#### 【特許請求の範囲】

## 【請求項1】

半導体素子と、

一方の主面上に第1の配線が設けられているとともに、前記第1の配線に電気的に接続された第2の配線が基材本体を貫通して他方の主面側に露出されて設けられており、かつ、前記半導体素子が前記第1の配線に電気的に接続されて前記一方の主面上に搭載されたチップ搭載基材と、

前記半導体素子および前記第1の配線を覆って前記チップ搭載基材の前記一方の主面上に設けられた封止部材と、

この封止部材の表面上に設けられた第3の配線と、

前記封止部材の内部に設けられて前記第1の配線および前記第3の配線に電気的に接続された第4の配線と、

を具備してなり、前記封止部材の内部に形成された前記第4の配線を設けるための第4の配線用凹部の径の大きさと、前記半導体素子、前記チップ搭載基材、および前記封止部材からなるパッケージの厚さとの比が1:1以下に設定されていることを特徴とする半導体装置。

## 【請求項2】

第4の配線用凹部の径の大きさは、50μm~400μmに設定されているとともに、前記第1の配線の前記第4の配線に接続される部分の径の大きさは前記第4の配線用凹部の径の大きさよりも5~100μm大きく設定されていることを特徴とする請求項1に記載の半導体装置。

### 【請求項3】

前記半導体素子が前記封止部材内で前記チップ搭載基材上に複数個積層されて前記第1の配線に電気的に接続されているとともに、請求項1~4のうちのいずれか1項に記載の半導体装置が複数個積層されているとともに、積層方向において隣接する前記各半導体装置の前記第2の配線同士、または前記第3の配線同士、あるいは前記第2の配線と前記第3の配線とが電気的に接続されていることを特徴とする半導体装置。

#### 【請求項4】

単層または複数層からなる前記各半導体装置の上下各主面のうちの少なくとも一方の主面上には、汎用部品としての外部部品、外部基板、外部装置、受動部品、実装基板、および他の半導体装置のうちの少なくとも1つが接続されることを特徴とする請求項3に記載の半導体装置。

#### 【請求項5】

前記各半導体装置の前記汎用部品が接続される側の主面上に設けられた前記第2の配線、前記第3の配線、および前記第4の配線のうち前記汎用部品が接続される配線の上、ならびに複数層からなる前記各半導体装置の上下各主面上に設けられた前記第2の配線、前記第3の配線、および前記第4の配線のうち積層方向において互いに対向し合う配線同士の間には、半導体層が設けられていることを特徴とする請求項4に記載の半導体装置。

#### 【請求頃6】

一方の主面上に第1の配線が設けられているとともに、他方の主面上に第2の配線が設けられているチップ搭載基材の前記一方の主面上に、半導体素子を前記第1の配線に電気的に接続して搭載し、

前記半導体素子が搭載された前記一方の主面に対向させて第3の配線となる導電体を配置するとともに前記導電体と前記一方の主面との間に封止部材を導入して、前記封止部材の表面を覆いつつ、かつ、前記導電体の表面を露出しつつ、前記半導体素子および前記第1の配線の封止ならびに前記導電体の前記封止部材への取り付けを一括して行い、

前記導電体をパターニングして前記第3の配線を形成するとともに、前記第1の配線、前記第2の配線、および前記第3の配線に電気的に接続するように前記第3の配線または前記導電体、前記封止部材、前記第1の配線、および前記チップ搭載基材をそれらの厚さ方向に沿って一括して貫通させて前記第4の配線を設ける、

10

20

30

40

ことを特徴とする半導体装置の製造方法。

#### 【請求項7】

一方の主面上に第1の配線が設けられているとともに、前記第1の配線に電気的に接続された第2の配線が基材本体を貫通して他方の主面側に露出されて設けられているチップ搭載基材の前記一方の主面上に、半導体素子を前記第1の配線に電気的に接続して搭載し

前記半導体素子が搭載された前記一方の主面に対向させて第3の配線となる導電体を配置するとともに前記導電体と前記一方の主面との間に封止部材を導入して、前記封止部材の表面を覆いつつ、かつ、前記導電体の表面を露出しつつ、前記半導体素子および前記第1の配線の封止ならびに前記導電体の前記封止部材への取り付けを一括して行い、

前記導電体をパターニングして前記第3の配線を形成するとともに、前記第1の配線および前記第3の配線に電気的に接続するように前記第3の配線または前記導電体および前記封止部材をそれらの厚さ方向に沿って一括して貫通させて前記第4の配線を設ける、

ことを特徴とする半導体装置の製造方法。

## 【請求項8】

前記導電体を前記半導体素子が搭載された前記チップ搭載基材とともに封止用金型の内部に配置した後、前記封止部材を前記導電体と前記一方の主面との間に圧力を掛けて射出することにより、前記導電体を前記封止部材へ取り付けつつ、外側から内側に前記封止部材が流入可能な封止部材導入口が設けられているとともに、前記封止部材導入口が設けられている箇所とは異なる箇所に内側と外側とで気体が出入り自在な通気口が設けられており、かつ、前記半導体素子に対向する側が開口されて前記チップ搭載基材に搭載された前記半導体素子を覆う箱形状に前記導電体を形成することを特徴とする請求項6または7に記載の半導体装置の製造方法。

#### 【請求項9】

半導体素子を第1の配線に電気的に接続し、

この第1の配線に接続された前記半導体素子を間に挟んで第2の配線となる導電体と第3の配線となる導電体とを互いに対向させて配置するとともに前記各導電体の間に封止部材を導入することにより、前記半導体素子と前記第1の配線との接続部を覆いつつ、かつ、この接続部とは反対側の前記第1の配線の端部および前記各導電体の表面を露出しつつ、前記半導体素子および前記接続部の封止ならびに前記導電体の前記封止部材への取り付けを一括して行い、

前記各導電体をパターニングして前記第2の配線および前記第3の配線を形成するとともに、前記第1の配線、前記第2の配線、および前記第3の配線に電気的に接続するように前記第2の配線および前記第3の配線または前記導電体、ならびに前記封止部材をそれらの厚さ方向に沿って一括して貫通させて前記第4の配線を設ける、

ことを特徴とする半導体装置の製造方法。

### 【請求項10】

前記各導電体を前記第1の配線に接続された前記半導体素子とともに封止用金型の内部に配置した後、前記封止部材を前記各導電体の間に圧力を掛けて射出することにより、前記各導電体を前記封止部材へ取り付けつつ、外側から内側に前記封止部材が流入可能な封止部材導入口が設けられているとともに、前記封止部材導入口が設けられている箇所とは異なる箇所に内側と外側とで気体が出入り自在な通気口が設けられており、かつ、前記半導体素子に対向する側が開口されて前記半導体素子を覆う箱形状に前記各導電体を形成することを特徴とする請求項9に記載の半導体装置の製造方法。

#### 【請求項11】

前記導電体として Cuを含む箔形状の金属を用いることを特徴とする請求項 8 ~ 1 0 のうちのいずれか 1 項に記載の半導体装置の製造方法。

【発明の詳細な説明】

### 【技術分野】

[0001]

20

10

30

本発明は、半導体装置のパッケージング技術に係り、特に複数個の半導体素子を電気的に接続しつつ積層可能な構造を有する半導体装置およびその製造方法に関する。

### 【背景技術】

### [0002]

半導体装置の中には、一般にマルチチップパッケージあるいはマルチチップモジュール等と称される、複数個の半導体チップ(半導体素子)を備える半導体装置がある。また、そのようなマルチチップ構造を有する半導体装置の中には、複数個の半導体チップが積層されて搭載されたチップ積層型の半導体装置がある。そして、そのようなチップ積層型の半導体装置を得るために、1個ないしは複数個の半導体チップが搭載された個々の半導体装置(パッケージ、モジュール)を複数個積層する技術が多数提案されている(例えば、特許文献1~5参照)。

#### [0003]

複数個の半導体パッケージ(半導体モジュール)を積層してチップ積層型のマルチチップパッケージ(マルチチップモジュール)を作製する場合、例えば次に述べるような作製方法がある。先ず、各パッケージを各層ごとに個別のパッケージとして作製する。次に、各パッケージを積層して1つのマルチチップパッケージとした後、このパッケージを実装基板に搭載するための下部接続配線(下部接続端子)を最下層のパッケージに設ける。また、このパッケージの上にさらに他の電気部品等を搭載する場合には、上部接続用配線(上部接続端子)を最上層のパッケージに設ける。あるいは、最下層のパッケージを予め基板実装専用の構造を有する基板実装用パッケージとして作製したり、最上層のパッケージを予め部品実装専用の構造を有する部品実装用パッケージとして作製したりする。

### [0004]

このような技術によれば、各パッケージを各層ごとに個別のパッケージとして作製するので、パッケージ全体の生産効率を向上させることが困難である。また、各パッケージごとに専用の組立設備を設ける必要が生じるおそれがあるなど、設備費の負担が大きくなるおそれがある。設備費の負担が大きくなると、各パッケージの生産コストが高くなる。ひいては、各パッケージを積層したマルチチップパッケージ全体、およびこのマルチチップパッケージを備える半導体装置の生産コストが高くなる。

【特許文献1】特開2002-134653号公報

【特許文献2】特開2002-170906号公報

【特許文献3】特開2002-184796号公報

【特許文献4】特開2002-170921号公報

【特許文献5】特開2002-305364号公報

【発明の開示】

【発明が解決しようとする課題】

## [0005]

本発明は、以上説明したような課題を解決するためになされたものであり、その目的とするところは、構造的な汎用性を向上させることにより、単体での使用あるいは他の部品を接続しての使用に拘らず、また複数個積層して使用する場合の積層数や位置に拘らず使用することができるとともに、効率良く、かつ、低コストで容易に製造できる半導体装置およびその製造方法を提供することにある。また、そのような半導体装置が複数個積層されてなるとともに、効率良く、かつ、低コストで容易に製造できる半導体装置およびその製造方法を提供することにある。

# 【課題を解決するための手段】

#### [0006]

前記課題を解決するために、本発明の一態様に係る半導体装置は、半導体素子と、一方の主面上に第1の配線が設けられているとともに、前記第1の配線に電気的に接続された第2の配線が基材本体を貫通して他方の主面側に露出されて設けられており、かつ、前記半導体素子が前記第1の配線に電気的に接続されて前記一方の主面上に搭載されたチップ搭載基材と、前記半導体素子および前記第1の配線を覆って前記チップ搭載基材の前記一

20

10

30

40

20

30

40

50

方の主面上に設けられた封止部材と、この封止部材の表面上に設けられた第3の配線と、前記封止部材の内部に設けられて前記第1の配線および前記第3の配線に電気的に接続された第4の配線と、を具備してなり、前記封止部材の内部に形成された前記第4の配線を設けるための第4の配線用凹部の径の大きさと、前記半導体素子、前記チップ搭載基材、および前記封止部材からなるパッケージの厚さとの比が1:1以下に設定されていることを特徴とするものである。

### [0007]

また、前記課題を解決するために、本発明の他の態様に係る半導体装置は、前記半導体素子が前記封止部材内で前記チップ搭載基材上に複数個積層されて前記第1の配線に電気的に接続されているとともに、本発明に係る半導体装置が複数個積層されているとともに、積層方向において隣接する前記各半導体装置の前記第2の配線同士、または前記第3の配線同士、あるいは前記第2の配線と前記第3の配線とが電気的に接続されていることを特徴とするものである。

## [0008]

また、前記課題を解決するために、本発明のまた他の態様に係る半導体装置の製造方法は、一方の主面上に第1の配線が設けられているとともに、他方の主面上に第2の配線が設けられているチップ搭載基材の前記一方の主面上に、半導体素子を前記第1の配線に電気的に接続して搭載し、前記半導体素子が搭載された前記一方の主面に対向させて第3の配線となる導電体を配置するとともに前記導電体と前記一方の主面との間に対止部材を導入して、前記封止部材の表面を覆いつつ、かつ、前記導電体の前記封止部材への取り付けを素子および前記第1の配線の封止ならびに前記導電体の前記封止部材への取り付けを一括して行い、前記導電体をパターニングして前記第3の配線を形成するとともに、前記第1の配線、前記第2の配線、および前記第3の配線に電気的に接続するように前記第1の配線または前記導電体、前記封止部材、前記第1の配線を設ける、ことを特徴とするものである。

## [0009]

また、前記課題を解決するために、本発明のまた他の態様に係る半導体装置の製造方法は、一方の主面上に第1の配線が設けられているとともに、前記第1の配線に電気的に接続された第2の配線が基材本体を貫通して他方の主面側に露出されて設けられているチップ搭載基材の前記一方の主面上に、半導体素子を前記第1の配線に電気的に接続して搭し、前記半導体素子が搭載された前記一方の主面に対向させて第3の配線となる導電体を配置するとともに前記導電体と前記一方の主面との間に封止部材を導入して、前記対止部材の表面を覆いつつ、かつ、前記導電体の表面を露出しつつ、前記半導体素子および前記第1の配線の封止ならびに前記導電体の前記封止部材への取り付けを一括して行い、前記導電体をパターニングして前記第3の配線を形成するとともに、前記第1の配線および前記第3の配線に電気的に接続するように前記第3の配線または前記導電体および前記第3の配線に電気的に接続するように前記第3の配線を設ける、ことを特徴とするものである。

#### [0010]

さらに、前記課題を解決するために、本発明のさらに他の態様に係る半導体装置の製造方法は、半導体素子を第1の配線に電気的に接続し、この第1の配線に接続された前記半導体素子を間に挟んで第2の配線となる導電体と第3の配線となる導電体とを互いに対向させて配置するとともに前記各導電体の間に封止部材を導入することにより、前記半導体素子と前記第1の配線との接続部を覆いつつ、かつ、この接続部とは反対側の前記第1の配線の端部および前記各導電体の表面を露出しつつ、前記半導体素子および前記接続部の封止ならびに前記導電体の前記封止部材への取り付けを一括して行い、前記各導電体をパターニングして前記第2の配線および前記第3の配線を形成するとともに、前記第1の配線、前記第2の配線、および前記第3の配線に電気的に接続するように前記第2の配線および前記第3の配線または前記導電体、ならびに前記封止部材をそれらの厚さ方向に沿っ

30

40

50

(6)

て一括して貫通させて前記第4の配線を設ける、ことを特徴とするものである。

### 【発明の効果】

[0011]

本発明に係る半導体装置は、構造的な汎用性が向上されているので、単体での使用あるいは他の部品を接続しての使用に拘らず、また複数個積層して使用する場合の積層数や位置に拘らず使用することができるとともに、効率良く、かつ、低コストで容易に製造され得る。また、そのような半導体装置が複数個積層されているので、効率良く、かつ、低コストで容易に製造され得る。

[0012]

また、本発明に係る半導体装置の製造方法によれば、半導体装置の構造的な汎用性を向上させることにより、単体での使用あるいは他の部品を接続しての使用に拘らず、また複数個積層して使用する場合の積層数や位置に拘らず使用することができる半導体装置を、効率良く、かつ、低コストで容易に製造することができる。また、そのような半導体装置を複数個積層してなる半導体装置を、効率良く、かつ、低コストで容易に製造することができる。

【発明を実施するための最良の形態】

[ 0 0 1 3 ]

以下、本発明に係る各実施形態を図面を参照しつつ説明する。

[ 0 0 1 4 ]

(第1の実施の形態)

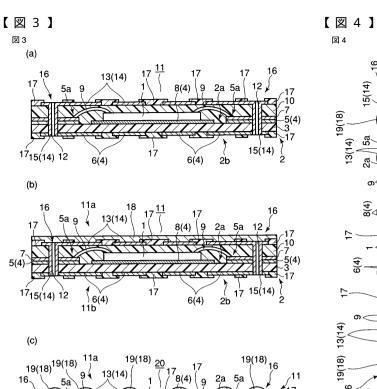

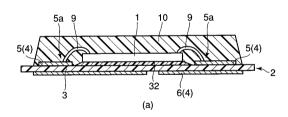

先ず、本発明に係る第1実施形態を図1~図3を参照しつつ説明する。図1~図3は、それぞれ本実施形態に係る半導体装置の製造方法を示す工程断面図である。

[0015]

本実施形態では、例えばチップ搭載基材上の半導体チップを樹脂封止した半導体パッケージ(半導体装置)において、チップ搭載基材のチップ非搭載面側(下面側)のみならず、封止樹脂の表層部(上面側)にも配線層を設ける。すなわち、半導体パッケージの上下(表裏)両側に配線層を設ける。これにより、本実施形態の半導体パッケージ自体を他の実装基材に搭載しつつ、その上部に一般に市場に流通している既存の他の半導体パッケージや受動部品等を容易に実装することができる。以下、本実施形態に係る半導体装置およびその製造方法について、図面を参照しつつ詳しく説明する。

[0016]

先ず、図1(a)に示すように、一方の主面上に半導体素子(半導体チップ)1が少なくとも1個搭載(実装)される1枚のチップ搭載基材(チップ搭載基板、チップ実装基材)2を用意する。本実施形態においては、チップ搭載基材として、その基材本体3が柔軟性(可撓性)を有する材料により形成されたフレキシブル基材2を用いる。フレキシブル基材2の基材本体3は、例えばポリイミド(polyimide)、ガラスエポキシ、あるいはBTレジン等によりテープ状に形成されている。また、基材本体3には、その表裏(上下)両主面を覆ってそれぞれ少なくとも1層の導電層(金属層)からなる導電体4が設けられている。具体的には、それら両導電体4は、ともに1層の銅箔(Cu箔、Cu層)により形成されている。このような構造からなるフレキシブル基材2は、両面銅貼テープとも称される。各Cu箔4は、それぞれ後述する第1の配線5および第2の配線6となる。

[0017]

次に、図1(b)に示すように、フレキシブル基材2の半導体チップ1が搭載される側の主面であるチップ搭載面2a上に、少なくとも1本の第1の配線5を形成する。それとともに、フレキシブル基材2のチップ搭載面2a上に、半導体チップ1を搭載するチップマウントアイランド8を形成する。本実施形態においては、複数本の第1の配線5をチップ搭載面2a上に形成する。これら各第1の配線5は、後述する第4の配線15とともに本実施形態の半導体装置20の内部配線を構成する。

[0018]

各第1の配線5のうちの少なくとも1本は、半導体チップ1に電気的に接続されるチッ

30

40

50

プ接続配線となる。すなわち、全ての第1の配線 5 がチップ接続配線として形成されるとは限らない。各第1の配線 5 のうちの幾つかは、半導体チップ1とは電気的に非接続に形成されても構わない。例えば、図示は省略するが、半導体チップ1と断線された第1の配線 5 は、いわゆるダミー配線として形成されても構わない。あるいは、半導体チップ1と断線された第1の配線 5 は、後述する第2および第3の各配線 6 ,13等を介して半導体装置20に接続される外部の装置同士や他の部品同士を、半導体チップ1を介さずに電気的に接続するための、いわゆる中継配線の一部として形成されても構わない。ただし、以下の説明においては、特に断りのない限り、各第1の配線 5 をチップ接続配線として簡略して説明することとする。また、図1(b)~(e)、図2(a)~(c)、および図3(a)~(c)においては、複数本の第1の配線 5 のうち、半導体チップ1に電気的に接続されるチップ接続配線 5 のみを図示する。

[0019]

各チップ接続配線5およびチップマウントアイランド8は、チップ搭載面2a上のCu箔4をエッチング加工することにより形成される。具体的には、先ず、チップ搭載面2a上のCu箔4のたった。 具体的には、先ず、デュして露光性レジストを所定のパターンで塗工して露光を形成する。感光性レジストのパターンは、フレキシブル基材2に搭載される半導体チップラーンは、フレキシブル基材2に搭載される半導体チップラーの配置に応じて決められる。この後、チップ搭載面2a上のCu箔4にエッチングル基材2のチップ搭載面2a上のにより、フレキシブル基材2のチップが収集するこれにより、フレキシブル基材2のチップ搭載面2a上に所定のパターンからなる複数本のチップ接続配線5を形成する。このように、チップ接続配線(第1の配線)5は、フレキシブル基材2のチップ搭載面2a上に設けられているCu箔4の一部である。すなわち、チップ接続配線(第1の配線)5は、実質的にはフレキシブル基材2のチップ搭載面2a上に予め設けられているCu箔4の一部である。

[0020]

各チップ接続配線5は、少なくとも1本の第4の配線15とともに、半導体チップ1と 後述する少なくとも1本の第2の配線6および少なくとも1本の第3の配線13との間を 所定のパターンで電気的に接続する。後述するように、第2および第3の各配線6,13 は、ともに半導体装置20の外部配線(外部端子)を構成する。また、各チップ接続配線 5の一部には、半導体チップ1の各パッド部が電気的に接続されるパッド接続部(接合部)5 aが設けられる。

[ 0 0 2 1 ]

なお、各チップ接続配線 5 を形成するためのエッチング処理を行う際には、フレキシブル基材 2 のチップ搭載面 2 a とは反対側の主面上の C u 箔 4 の表面を、図示しないマスクで全面的に覆っておく。すなわち、フレキシブル基材 2 の半導体チップ 1 を搭載しない側の主面であるチップ非搭載面 2 b 上の C u 箔 4 の表面を、マスクで全面的に覆っておく。このチップ非搭載面 2 b 上の C u 箔 4 は、後述する第 2 の配線 6 となる。

[0022]

次に、図1(c)に示すように、少なくとも各チップ接続配線5のパッド接続部5aの表面に所定の処理を施す。この表面処理としては、ワイヤボンディング法やフリップチップ接続法等、半導体チップ1のフレキシブル基材2への実装方法に応じた適正な処理が適用される。本実施形態においては、ワイヤボンディング法により半導体チップ1を各チップ接続配線5に電気的に接続して、フレキシブル基材2に搭載する。この場合、各チップ接続配線5のパッド接続部5aの表面に、ニッケル(Ni)および金(Au)を用いてめっき処理を施す。すなわち、各パッド接続部5aの表面上にNi/Auめっき部7を設ける。

[0023]

次に、図1(d)に示すように、少なくとも1個の半導体チップ1をフレキシブル基材2に搭載する。本実施形態においては、チップ搭載面2a上に設けられたCu箔4のうち

30

40

50

、半導体チップ 1 が搭載されるチップマウントアイランド 8 となる部分(領域)の上に、 1 個の半導体チップ 1 を取り付ける。半導体チップ 1 は、例えば図示しないエポキシ樹脂 等の接着剤を用いてチップマウントアイランド 8 に接着(接合)されて、フレキシブル基 材 2 に搭載される。

### [0024]

次に、図1(e)に示すように、ワイヤボンディング法により半導体チップ1を各チップ接続配線5に電気的に接続する。具体的には、複数本の金製のボンディングワイヤ(Auボンディングワイヤ)9を、半導体チップ1の各接続パッドに接続する。それとともに、各Auボンディングワイヤ9を、各チップ接続配線5のパッド接続部5a上に設けられたNi/Auめっき部7に接続する。これにより、半導体チップ1は、各Ni/Auめっき部7を介して、各チップ接続配線5に電気的に接続される。各Auボンディングワイヤ9は、例えば超音波接合により半導体チップ1の各接続パッドおよび各Ni/Auめっき部7に接合される。

## [ 0 0 2 5 ]

なお、1個の半導体チップ1をチップマウントアイランド8に搭載した後、その半導体チップ1の上にさらに少なくとも1個の半導体チップ1を積層して、チップ接続配線5にワイヤボンディング接続することもできる。これにより、半導体装置20をマルチチップパッケージ(マルチチップモジュール)として構成することもできる。そのような構造からなる半導体装置およびその製造方法については、後述する第7実施形態において詳しく説明する。

## [0026]

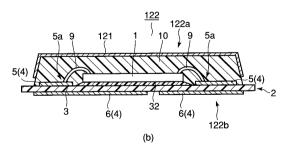

次に、図2(a)に示すように、フレキシブル基材2のチップ搭載面2a上に封止部材10を設ける。具体的には、半導体チップ1、各チップ接続配線5(各パッド接続部5aワイヤ9等を覆って、フレキシブル基材2のチップ搭載面2a上に封止部材10を設ける。これにより、少なくとも半導体チップ1および半導体チップ1と各チップ接続配線5であるパッド接続部5a等を封止する。この封止には、例えばインジをのとまた、対したは、クンモールド法やトランスファモールド法等の非気密封止法(ノン・ハーメチック法)がカンモールド法やトランスファモールド法により、対止部材10をは、トランスファモールド法により、対止部材10をは、キシブル基材2のチップ搭載面2a上に設ける。また、封止部材10としては、例えばボキシ樹脂とシリカフィラーとの混合樹脂が用いられる。これまでの工程により、半導体チップ1、フレキシブル基材2、および封止樹脂10等からなる樹脂封止パッケージ11位、本実施形態の半導体装置20の主要な構成部分となる。

## [0027]

続けて、図2(a)に示すように、第4の配線15を設けるための第4の配線用凹部(穴、孔)12を樹脂封止パッケージ11に少なくとも1個設ける。本実施形態においては、第4の配線15を樹脂封止パッケージ11に複数本設けるので、第4の配線用凹部12を樹脂封止パッケージ11に複数個設ける。各第4の配線15は、各チップ接続配線5とともに半導体装置20の内部配線を構成する。また、各第4の配線15のうちの少なくとも1本は、少なくとも1本の各チップ接続配線(第1の配線)5、少なくとも1本の第2の配線6、および少なくとも1本の第3の配線13を互いに電気的に接続するために設けられる。すなわち、少なくとも1本の第4の配線15は、少なくとも1本の各チップ接続配線5とともに、半導体装置20の外部配線(外部端子)を構成する少なくとも1本の第2の配線6および少なくとも1本の第3の配線13に半導体チップ1を電気的に接続するために設けられる。

### [0028]

本実施形態においては、各第4の配線15のうち少なくとも半導体チップ1に電気的に接続される第4の配線15を、樹脂封止パッケージ11の厚さ方向に沿って第2の配線6 および第3の配線13に一括して電気的に接続して設ける。このため、半導体チップ1に

30

40

50

電気的に接続される第4の配線15が設けられる各凹部12は、チップ接続配線5、第2の配線6、および第3の配線13を樹脂封止パッケージ11の厚さ方向に沿って一括して貫通できる位置に形成される。したがって、各凹部12のうち少なくとも半導体チップ1に電気的に接続される第4の配線15が設けられる各凹部12は、樹脂封止パッケージ11をその厚さ方向に沿って一括して貫通する貫通孔(スルーホール、ヴィアホール)として形成される。

#### [0029]

なお、図示は省略するが、半導体チップ1とは断線される第4の配線15が設けられる各凹部も、樹脂封止パッケージ11をその厚さ方向に沿って一括して貫通するスルーホール(ヴィアホール)として形成して構わないのはもちろんである。全ての第4の配線用凹部12をスルーホールとして形成することにより、半導体チップ1と各第4の配線15との接続状態に拘らず、第4の配線用凹部12を形成する工程を簡略化(単一化)することができる。ひいては、半導体装置20の製造効率を高めることができる。以下の説明において、半導体チップ1に電気的に接続される第4の配線15が、チップ接続配線5、第2の配線6、および第3の配線13に一括して電気的に接続されて設けられる箇所を、配線接続部16と称することとする。

## [0030]

配線接続部16に形成されるスルーホール12は、具体的には、封止樹脂10、各Ni/Auめっき部7、各パッド接続部5a(チップ接続配線5)、フレキシブル基材2の基材本体3、およびフレキシブル基材2のチップ非搭載面2b上のCu箔4を、それらの厚さ方向に沿って一括して貫通して形成される。この貫通作業は、例えば図示しないドリル等を用いて行われる。また、各スルーホール12の直径は、それぞれ約50μm~400μm程度の大きさに設定される。

## [ 0 0 3 1 ]

次に、図2(b)に示すように、封止樹脂10の表面上および各スルーホール12の内壁面上に、第3の配線13となる導電体(導電層)14および第4の配線15となる導電体(導電層)14および第4の配線15となる導電体14を一体に、かつ、一括して設ける。具体的には、先ず、各スルーホール12内の残渣を除去(デスミア)する。この後、無電解のっき法により、厚さが約0.01μm~1μm程度のCuからなる導電層(無電解Cu層)を、対脂10の表面上および各スルーホール12の内壁面上に全面的に設ける。続けて、層で、電解Cu層の表面上および各スルーホール12の内壁面上に全面的に設ける。これにより、電解Cu層の表面上に全面的に設ける。これにより、第3の配線15として、無電解Cu層に一体化されつつ設けられる。これにより、第3の配線13のなる1層のCu層14および第4の配線15となる1層のCu層14が、封止樹脂10の表面上および各スルーホール12の内壁面上に一体に、かつ、一括して設けられる。ルーホール12の内壁面上に設けられたCu層14は、そのまま第4の配線15と日にもれる。

## [0032]

なお、本実施形態においては、電解 C u 層の厚さは、各スルーホール 1 2 を塞がないように、各スルーホール 1 2 の直径の大きさに応じて適宜、適正な大きさに設定される。また、この一連のめっき工程においては、フレキシブル基材 2 のチップ非搭載面 2 b 上の C u 箔 4 の表面は、前述した各チップ接続配線 5 を形成する際に設けられたマスクで全面的に覆われたままであるとする。

#### [0033]

また、前述したように、本実施形態においては、無電解めっき法および電解めっき法を連続して行うことにより、第3の配線13となるCu層(導電体)14を封止樹脂10の表面上に設けた。しかし、Cu層14を設ける方法は、めっき法には限定されない。第3の配線13と封止樹脂10との密着強度を高める必要がある場合には、前述した封止樹脂10を設ける工程において、導電体14を封止樹脂10と一体に、かつ、一括して設ける

30

40

50

とよい。例えば、図示は省略するが、半導体パッケージの上面に対向するモールド上金型のキャビティ部にマット処理を施した銅箔(Cu箔)を配置した後、トランスファモールディングを行うとよい。あるいは、モールディングを行う際に、Cu箔にエポキシ樹脂やBTレジン等を塗工した樹脂付きCu箔を熱間ラミネートすることも有効である。これらの封止工程より、第3の配線13となる銅箔と封止樹脂との密着強度を高めつつ、銅箔を封止樹脂と一体に、かつ、一括して設けることができる。そのような構造からなる半導体装置およびその製造方法については、後述する第8および第9の各実施形態において詳しく説明する。

## [0034]

前述したように、配線接続部16において樹脂封止パッケージ11をその厚さ方向に沿って貫通する各スルーホール12内に形成された各第4の配線15(Cu層14)は、封止樹脂10の表面上に設けられた第3の配線13となるCu層14と一体化されている。それとともに、配線接続部16において各スルーホール12内に形成された各第4の配線15は、フレキシブル基材2のチップ搭載面2a上に形成されている各チップ接続配線(第1の配線)5を貫通しつつ、それらに電気的に接続されている。さらに、配線接続部16に形成された各第4の配線15は、フレキシブル基材2のチップ非搭載面2b上に形成された各第4の配線15は、フレキシブル基材2のチップ非搭載面2b上に形成されている、第2の配線6となるCu箔4に電気的に接続されている。すなわち、各第4の配線15は、いわゆるスループラグ(ヴィアプラグ)として樹脂封止パッケージ11の内部に設けられている。図2(b)に示すように、樹脂封止パッケージ11内の半導体チップ1は、内部配線としての各スループラグ15および各チップ接続配線5等を介して、外部配線としての第2および第3の各配線6、13に電気的に接続される。

#### [0035]

また、前述したように、配線接続部16に形成された各スループラグ15は、半導体チップ1に電気的に接続されている。ただし、全てのスループラグ15が半導体チップ1に電気的に接続されて形成される必要はない。前述した第1の配線5と同様に、各スループラグ15のうちの幾つかは、半導体チップ1とは電気的に非接続に形成されても構わない

#### [0036]

例えば、図示は省略するが、複数個の半導体装置 2 0 を積層するとともに、隣接する半導体装置 2 0 同士をそれぞれの第 2 の配線 6 および第 3 の配線 1 3 を介して電気的に接続するとする。この場合、所定の層の半導体装置 2 0 に設ける各スループラグ 1 5 のうちの幾つかを、その所定の層の半導体チップ 1 に電気的に接続される通電経路に、その所定の層に隣接する他の層の半導体チップ 1 に電気的に接続される通電経路に形成しても構わない。あるいは、各層の半導体装置 2 0 に設ける各スループラグ 1 5 を、各層の半導体チップ 1 を 1 層おきに電気的に接続する通電経路上に形成しても構わない。また、第 2 の配線 6 や第 3 の各配線 1 3 を介して、半導体装置 2 0 に複数個の外部装置や外部部品を電気的に接続したり、半導体装置 2 0 を基板に実装したりするとする。これらの場合、半導体装置 2 0 に設けられる各スループラグ 1 5 のうちの幾つかを、半導体チップ 1 とは断線させるとともに、外部装置や外部部品、あるいは基板に電気的に接続される通電経路上に形成しても構わない。

## [ 0 0 3 7 ]

このように、全てのスループラグ15が半導体チップ1に電気的に接続されて設けられる必要はない。前述した第1の配線5と同様に、半導体チップ1と断線された各スループラグ15は、ダミー配線の一部を構成するダミープラグとして形成されても構わない。あるいは、半導体チップ1と断線されたスループラグ15は、第2および第3の各配線6,13等を介して半導体装置20に接続される外部の装置同士や他の部品同士を、半導体チップ1を介さずに電気的に接続するための中継プラグとして形成されても構わない。ただし、以下の説明においては、特に断りのない限り、各スループラグ15を、半導体チップ1に電気的に接続されたスループラグとして簡略して説明することとする。また、図2(b),(c)および図3(a)~(c)においては、複数個のスループラグ15のうち、

20

30

40

50

配線接続部 1 6 に設けられて半導体チップ 1 に電気的に接続されるスループラグ 1 5 のみを図示する。

### [0038]

次に、図2(c)に示すように、フレキシブル基材2のチップ非搭載面2b上に少なくとも1本の第2の配線6を形成する。それとともに、封止樹脂10の表面上に少なくとも1本の第3の配線13を形成する。本実施形態においては、これら第2の配線6および第3の配線13をそれぞれ複数本ずつ形成する。また、各第2の配線6および各第3の配線13は、前述した第1の配線(チップ接続配線)5を形成するのと同様の方法により形成される。

## [0039]

先ず、第2の配線6を形成する場合について説明する。前述したように、樹脂封止パッケージ11内にスループラグ15を形成し終えた段階では、チップ非搭載面2b上のCu箔4の表面は、各チップ接続配線5を形成する際に設けられたマスクで全面的に覆われている。したがって、始めに、このチップ非搭載面2b上のCu箔4の表面を覆っているマスクを剥離させる。続けて、チップ非搭載面2b上のCu箔4の表面上に、図示しないいがストを予め定められた所定のパターンで塗工して露光する。これにより、チップ非搭載面2b上のCu箔4の表面上に図示しないレジストマスクを形成する。感光性レジストのパターンは、各スループラグ15の位置や、第2の配線6に電気的に接続される外部装置および外部部品等との接続位置等に応じて予め決められる。この後、チップ非搭載面2b上のCu箔4にエッチング処理や現像処理等を施して、Cu箔4を所定のパターンからで残す。これにより、フレキシブル基材2のチップ非搭載面2b上に所定のパターンからなる複数本の第2の配線6を形成する。

## [0040]

このように、第2の配線6は、フレキシブル基材2のチップ非搭載面2b上に設けられているCu箔4を、予め定められている所定のパターンにパターニングすることで形成される。すなわち、第2の配線6は、実質的にはフレキシブル基材2のチップ非搭載面2b上に予め設けられているCu箔4の一部である。

### [0041]

次に、第3の配線13を形成する場合について説明する。始めに、第2の配線6を形成する場合と同様に、封止樹脂10上のCu層14の表面上に、図示しない感光性レジストのCu層14の表面上に図示しないレジストマスクを形成する。感光性レジストのパターンは、各スループラグ15の位置や、第3の配線13に電気的に接続される外部装置およい、部部品等との接続位置等に応じて予め決められる。この後、封止樹脂10上のCu層14を所定のパターンで残す。これに10、所定のパターンからなる表層配線(表層端子)としての第3の配線13を封止樹脂10の表面上に設けられているCu層14を、予め定められている所定のパターンにパターニングすることに複数本形成する。このように、第3の配線13は、封止樹脂10の表面上に設けられているCu層14を、予め定められている所定のパターンにパターニングすることに扱けるで、第3の配線13を形成する工程は、第2の配線6を形成する工程と一括して行われても構わない。

#### [0042]

図2(c)に示すように、各第2の配線6および各第3の配線13は、半導体装置20の外部配線(外部端子)を構成する。前述したように、複数個の半導体装置20を電気的に接続して積層する際には、各半導体装置20間の電気的な接続は、各半導体装置20の各第2の配線6および各第3の配線13の少なくとも一方を介して行われる。同様に、半導体装置20を外部基板に実装したり、半導体装置20に他の半導体パッケージや外部装置、あるいは外部部品等を電気的に接続したりする際に、各第2の配線6および各第3の配線13のどちらに他の半導体装置20や実装基板、あ

20

30

40

50

るいは外部装置が接続されても構わない。すなわち、各第2の配線6および各第3の配線13のどちらを、パッケージ搭載用配線(端子)、外部装置接続用配線(端子)、部品搭載用配線(端子)、あるいは基板実装用配線(端子)等として使用しても構わない。

## [0043]

同様に、半導体装置20は、そのフレキシブル基材2側および封止樹脂10側のどちらの側を上または下に向けても構わない。すなわち、各第2の配線6および各第3の配線13のどちらを、上部配線(上部端子)あるいは下部配線(下部端子)として使用しても構わない。また、同様に、半導体装置20は、そのフレキシブル基材2側および封止樹脂10側のどちらの主面を表面または裏面として用いても構わない。すなわち、各第2の配線6および各第3の配線13のどちらを、表面側配線(表面側端子)あるいは裏面側配線(裏面側端子)として使用しても構わない。

## [0044]

また、図2(c)に示すように、各第2の配線6および各第3の配線13のうちの幾つかは、各スループラグ(第4の配線)15および各チップ接続配線(第1の配線)5を介して半導体チップ1に電気的に接続されている。しかし、前述したチップ接続配線5およびスループラグ15と同様に、全ての第2の配線6および第3の配線13が半導体チップ1に電気的に接続されて形成されても構わない。例えば、前述したチップ接続配線5およびスループラグ15と同様に、半導体チップ1と断線された形成されても構わない。例えば、前述2の配線6および第3の配線13は、ダミー配線として形成されても構わない。あるいは、半導体チップ1と断線された第2の配線6および第3の配線13は、同じく半導体チップ1と断線されたスループラグ15とともに、半導体装置20に接続される外部の装置同土を、半導体チップ1を介さずに電気的に接続するための中継配線の一部として形成されても構わない。

### [0045]

次に、図3(a)に示すように、複数本の第2の配線6が形成されたフレキシブル基材2のチップ非搭載面2b上に、予め定められた所定のパターンでソルダーレジスト17を塗工する。同様に、複数本の第3の配線13が形成された封止樹脂10の表面上に、予め定められた所定のパターンでソルダーレジスト17を塗工する。続けて、図示は省略するが、各第2の配線6および各第3の配線13のうちパッケージ搭載用端子となる配線に、必要に応じてNi/Auめっき処理や防錆処理等の所定の表面処理を施す。

## [0046]

次に、図3(b)に示すように、樹脂封止パッケージ11の封止樹脂10側の主面上に、各第3の配線13に外部部品等を電気的に接続するための接続用導電部材18を設ける。本実施形態においては、接続用導電部材としてクリーム半田18を用いる。また、本実施形態においては、樹脂封止パッケージ11の封止樹脂10側の主面をパッケージ搭載面(外部装置接続面、部品搭載面)11aとする。すなわち、本実施形態においては、樹脂封止パッケージ11のパッケージ搭載面11a上に、接続用導電部材としてのクリーム半田18を設ける。クリーム半田18は、例えば各第3の配線13およびソルダーレジスト17を覆ってスクリーン印刷されて、樹脂封止パッケージ11のパッケージ搭載面11a上に全面的に設けられる。ただし、この接続用導電部材18を設ける方法は、前述したスクリーン印刷には限られない。例えば、図示は省略するが、接続用導電部材18として、PbSnVSnAg等からなる半田ボールをソルダーレジスト17から露出している各第3の配線13の表面上に搭載しても構わない。

# [0047]

なお、樹脂封止パッケージ11の封止樹脂10側の主面をパッケージ搭載面11aとすると、樹脂封止パッケージ11のフレキシブル基材2側の主面は基板実装面11bとして用いることができる。この場合、図示は省略するが、樹脂封止パッケージ11の基板実装面11bの表面上に、必要に応じて接続用導電部材としてPbSnやSnAg等からなる複数個の半田ボールを搭載する。各半田ボールは、それらの少なくとも一部が各第2の配

30

40

50

線6に接触(接合)されて設けられていればよい。

### [0048]

次に、図3(c)に示すように、樹脂封止パッケージ11のパッケージ搭載面11a上に、半田層19を形成する。具体的には、樹脂封止パッケージ11のパッケージ搭載面11a上に設けられたクリーム半田18にリフローを実施することにより、ソルダーレジスト17から露出している各第3の配線13の表面を覆って半田層19を形成する。本実施形態においては、厚さが約50μm~0.3mmの半田層19を各第3の配線13の表面上に形成する。この際、各スループラグ15が形成された各スルーホール12の内部も半田層19により埋め込む。また、図示は省略するが、樹脂封止パッケージ11のパッケージ非搭載側である基板実装面11b上の各第2の配線6に、必要に応じて所定の表面処理を施す。例えば、防錆処理やNi/Auめっき処理等、半田が濡れ易く、かつ、高温テスト時に各第2の配線6の表面に非溶融酸化膜が形成され難くなる処理を、基板実装用端子となる各第2の配線6の表面に必要に応じて施す。

### [0049]

なお、これまでの説明では、本実施形態の内容を理解し易くするために、樹脂封止パッケージ11を単独のパッケージとして作製するものとして説明してきた。しかし、図示は省略するが、実際の製造工程では、樹脂封止パッケージ11は複数個まとめて作製される。したがって、これまでの工程により一括して作製された樹脂封止パッケージ11の集合体を、ダイシング等によりテープ状態から個々のパッケージごとに切断して個片化する。この後、同じく図示は省略するが、各樹脂封止パッケージ11が実際に製品として使用できるか否かを検査するための各種テストを、低温あるいは高温等の様々な環境下で個々の樹脂封止パッケージ11ごとに実施する。そして、これらのテストに合格した樹脂封止パッケージ11を良品とする。これにより、図3(c)に示す構成を主要な構成部分とする、本実施形態に係る所望の半導体装置20を得る。

### [0050]

すなわち、樹脂封止パッケージ11のパッケージ搭載面11a上にパッケージ搭載用端子(パッケージ搭載用配線)としてのCu配線(第3の配線)13を複数本備えるとともに、樹脂封止パッケージ11の基板実装面11b上に基板実装用端子(基板実装用配線)としてのCu配線(第2の配線)6を複数本備えており、かつ、チップ搭載基材2のチップ搭載面2a上に設けられた複数本のCuチップ接続配線(第1の配線)5にワイヤボンディング接続されてチップ搭載基材2に搭載された1個の半導体チップ1が、各Cuチップ接続配線5および樹脂封止パッケージ11をその厚さ方向に沿って貫通して設けられた複数本のCuスループラグ(第4の配線)15を介して、各Cu配線6および各Cu配線13とに接続されている樹脂封止パッケージ11からなる半導体装置20を得る。

## [0051]

この後、半導体装置20のパッケージ搭載面11a上には、必要に応じて図示しない受動部品等の所定の外部装置が搭載される。それとともに、半導体装置20の基板実装面11b上には、必要に応じて図示しない実装基板が実装される。

## [0052]

なお、本実施形態において図示は省略するが、1個の半導体装置20を基本構成単位として、複数個の半導体装置20を積層することにより、積層体としての半導体装置(マルチチップパッケージ、マルチチップモジュール)を作製することができる。この場合、積層体としてのマルチチップパッケージに対して、各半導体装置20をシングルチップパッケージ(シングルチップモジュール)と称することができる。このようなシングルチップパッケージ20を複数個積層してなるマルチチップパッケージについては、後述する第2実施形態において、図面を参照しつつ詳しく説明する。

#### [0053]

以上説明したように、この第1実施形態によれば、半導体チップ1と電気的に接続された外部配線としての第2および第3の各配線6,13が、上下(表裏)両主面上に設けられている半導体装置20を得ることができる。これら第2および第3の各配線6,13、

30

40

50

ならびに内部配線としての第1および第4の各配線5,15のそれぞれの配線パターンを適宜、適正な形状に形成することにより、半導体装置20のフレキシブル基材2側および封止樹脂10側のどちらにでも、実装基板や受動部品等の外部装置を接続することができる。また、基板や外部装置等の仕様に応じて、第2および第3の各配線6,13や第1および第4の各配線5,15の各配線パターンを適宜、適正な形状に形成することができる。これにより、半導体装置20を一般に市場に流通している様々な汎用の外部装置を接続したりするにとができる。さらに、後述する第2実施形態において詳しく説明するが、複数個の半導体装置20を積層してマルチチップパッケージを作製する場合、隣接する他の半導体装置20との接続状態等に応じて第1~第4の各配線5,6,13,15の配線パターンを適宜、適正な形状に形成する。これにより、半導体装置20の積層数に拘らず、半導体装置20を所望の位置に配置することができる。

[0054]

このように、半導体装置20は、その汎用性および実装密度が高められている。また、半導体装置20は、これを構成部品の一部として用いる電気装置において、その実装密度の向上やコンパクト化にも寄与できる。すなわち、半導体装置20は、構造的な汎用性が向上されているので、単体での使用あるいは他の部品を接続しての使用に拘らず、また複数個積層して使用する場合の積層数や位置に拘らず、様々な設定で使用することができる。それとともに、そのような構造からなる半導体装置20は、効率良く、かつ、低コストで容易に製造できる。また、本実施形態に係る半導体装置の製造方法によれば、そのような半導体装置20を効率良く、かつ、低コストで容易に製造できる。

[0055]

(第2の実施の形態)

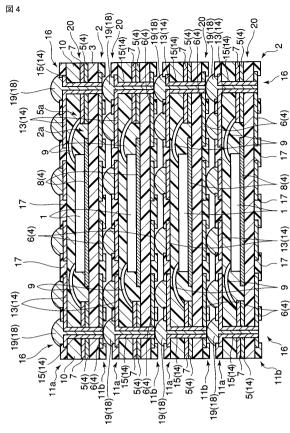

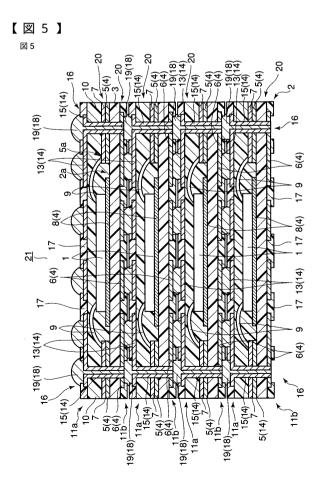

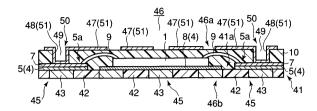

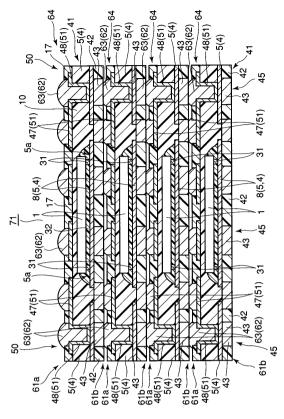

次に、本発明に係る第2実施形態を図4および図5を参照しつつ説明する。図4および図5は、それぞれ本実施形態に係る半導体装置の製造方法を示す工程断面図である。なお、第1実施形態と同一部分には同一符号を付して、その詳しい説明を省略する。

[0056]

本実施形態においては、前述した第1実施形態に係る半導体装置20を複数個積層してなる半導体装置およびその製造方法について説明する。以下、詳しく説明する。

[0057]

先ず、図4に示すように、4個の第1実施形態の半導体装置20を積層して配置する。この際、下側の半導体装置20のパッケージ搭載面11a上の各半田層19と、上側の半導体装置20の基板実装面11b上の各第2の配線(下部接続端子、下部接続配線)6とを接触させて、各半導体装置20を配置する。

[0058]

次に、図 5 に示すように、積層された 4 個の半導体装置 2 0 に対してリフローを実施する。これにより、各半導体装置 2 0 のパッケージ搭載面 1 1 a 上の各半田層 1 9 が溶融して、隣接する半導体装置 2 0 同士が電気的に接続されて接合される。

[ 0 0 5 9 ]

この後、図示は省略するが、接合された 4 個の半導体装置 2 0 からなる積層体に、これが実際に製品として使用できるか否かを検査するための各種テストを、低温あるいは高温等の様々な環境下で実施する。そして、これらのテストに合格した積層体を良品とする。これにより、図 5 に示すように、本実施形態に係る所望の半導体装置 2 1 を得る。すなわち、シングルチップパッケージ(シングルチップモジュール)としての第 1 実施形態の半導体装置 2 0 を 4 個積層してなる、チップ積層型のマルチチップパッケージ(マルチチップモジュール)としての半導体装置 2 1 を得る。

[0060]

この後、最上層のシングルチップパッケージ20のパッケージ搭載面11a上には、必要に応じて図示しない受動部品等の所定の外部装置が搭載される。それとともに、最下層のシングルチップパッケージ20の基板実装面11b上には、必要に応じて図示しない実

装基板が実装される。

## [0061]

以上説明したように、この第2実施形態によれば、前述した第1実施形態に係る半導体装置20を積層しているので、チップ積層型の半導体装置21を効率良く、かつ、低コストで容易に製造できる。

#### [0062]

従来は、複数個の半導体パッケージ(半導体モジュール)を積層してチップ積層型のマルチチップパッケージ(マルチチップモジュール)を作製する場合、各パッケージを積層して1つのマルチチップパッケージとした後、このパッケージを実装基板に搭載するための下部接続配線(下部接続端子)を最下層のパッケージに設ける。また、このパッケージに設ける。また、このパッケージに設ける。また、このパッケージに設ける。あるいは、最下層のパッケージを予め基板実装専用の構造を有する基板実装用パッケージとして作製したり、最上層のパッケージを予め部品実装専用の構造を有する部品実装用パッケージとして作製したりする。このように、従来は、チップ積層型のマルチチップパッケージを作製する場合、配置される位置に応じて各パッケージを作り分けなければならなかった。このため、製造効率が低く、製造コストも高くなり易かった。

## [0063]

これに対して、本実施形態のチップ積層型の半導体装置21は、構造的な汎用性が向上されており、複数個積層して使用する場合の積層数や位置に拘らず、様々な設定で使用することができる第1実施形態の半導体装置20を積層することにより作製されている。したがって、半導体装置21は効率良く、かつ、低コストで容易に製造できる。

#### [0064]

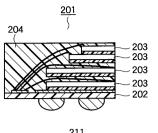

また、従来のチップ積層型のマルチチップパッケージの中には、1つのパッケージ内に複数個の半導体チップが積層されて設けられたタイプのチップ積層型のマルチチップパッケージがある。以下、図23(a),(b)および図24を参照しつつ、具体的かつ簡潔に説明する。

## [0065]

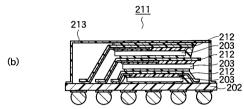

先ず、図23(a)に示すチップ積層型のマルチチップパッケージ(マルチチップモジュール)201について説明する。このマルチチップパッケージ201は、例えば次に述べる工程により製造される。先ず、図23(a)に示すように、1枚の実装基板202上に複数個の半導体チップ203を積層する。そして、ワイヤボンディングを繰り返すことにより各半導体チップ203を実装基板202に電気的に接続する。続けて、実装基板202および各半導体チップ203にモールド封止を実施して、封止樹脂204で覆う。この後、モールド封止された実装基板202および各半導体チップ203に、いわゆるBurn-Inテストを実施する。これにより、チップ積層型のマルチチップパッケージ201を作製する。

## [0066]

次に、図23(b)に示すチップ積層型のマルチチップパッケージ211について説明する。このマルチチップパッケージ211は、例えば次に述べる工程により製造される。先ず、図23(b)に示すように、複数個の半導体チップ203をそれぞれ1枚のチップ接続基板212にフリップチップ接続する。そして、各半導体チップ203を、各チップ接続基板212とともに1枚の実装基板202上に複数個積層して、実装基板202に電気的に接続(ダイアタッチ)する。続けて、実装基板202および各半導体チップ203を保護ケース213で覆って、パッケージングする。この後、前述したマルチチップパッケージ201の場合と同様に、Burn-Inテストを実施する。これにより、前述したマルチチップパッケージ201とは異なるタイプのチップ積層型のマルチチップパッケージ211を作製する。

## [0067]

50

40

20

これら各パッケージ201,211のような構成においては、各パッケージ201,211内の複数個の半導体チップ203のうち1個でもテストで不良となると、パッケージ201,211全体のテスト不良率は、各半導体チップ203それぞれの不良率を累積した不良率の影響を受ける。例えば、各パッケージ201,211のように、パッケージ内に4個の半導体チップ203が積層されているマルチチップパッケージにおいて、1層目から4層目までの各半導体チップの歩留まりが、それぞれ95%、95%、90%、85%であったとする。この場合、製品としてのパッケージ全体の最終歩留まりは、0.95×0.95×0.90×0.85×100 69(%)となり、70%を下回る。このように、パッケージ全体の歩留まりは、複数個の半導体チップのそれぞれの不良率のうち、最も高い不良率に引きずられる。それとともに、他の層の良品としての半導体チップに多大な口スが生じる。

[0068]

また、封止樹脂204や保護ケース213には、それらの上部に外部装置を搭載するための配線が設けられていないため、各パッケージ201,211の上部に外部装置を電気的に接続して搭載することは困難である。すなわち、各パッケージ201,211は、その実装密度が低い。さらに、パッケージ211については、実装基板202とは別構造のチップ接続基板212を設ける必要があるなど、その生産効率を向上し難く、かつ、パッケージ全体のコストが高価になり易い。

[0069]

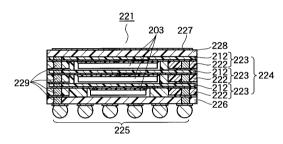

また、図24には、従来のパッケージ積層型モジュール221を示す。このモジュール221においては、先ず、複数個の半導体チップ203、各チップ203が接続されるチップ接続基板212、および隣接する各チップ203間に配置される複数枚の中間基板222からなる中間パッケージ223を、それぞれの層ごとに組み立てる。そして、各中間パッケージ223を作製した段階で一旦Burn-Inテスト等を実施し、各中間パッケージ223を良品と不良品とに選別する。続けて、良品として認められた中間パッケージ223をのみを所望の層数積層して、複数個の中間パッケージ223からなる積層体224を作製する。この後、積層体224の最下層の中間パッケージ223を、外部端子としての半田ボール(Ball Grid Array: BGA)225が複数個設けられた実装基板226に実装する。それとともに、積層体224の最上層の中間パッケージ223に、複数本の外部装置搭載用配線227が設けられた外部装置搭載用配線227は、各中間基板222を貫通して設けられた複数本のスループラグ229等を介して、互いに電気的に接続されている。

[0070]

このモジュール 2 2 1 のような構成においては、予め良品として認められた中間パッケージ 2 2 3 のみを用いるので、前述した各パッケージ 2 0 1 , 2 1 1 のような半導体チップ 2 0 3 の不良率の累積によるパッケージ全体の歩留まりロスは回避される。しかし、各パッケージ 2 0 1 , 2 1 1 と同様に、各層ごとに中間基板 2 2 2 を設けたり、チップ接続基板 2 1 2 や中間基板 2 2 2 とは別構造の実装基板 2 2 6 や外部装置搭載用基板 2 2 8 を設けたりする必要がある。そのため、モジュール 2 2 1 も、その生産効率を向上し難く、かつ、モジュール(パッケージ)全体のコストが高価になり易い。

[0071]

このように、従来の技術によれば、チップ積層型パッケージ(モジュール)全体の生産効率を向上させることが困難である。特に、モジュール221のような構成からなるチップ積層型パッケージにおいては、各中間パッケージ223ごとに専用の組立設備を設ける必要があるなど、設備費の負担が大きくなるおそれがある。設備費の負担が大きくなると、各中間パッケージの生産コストが高くなるおそれがある。ひいては、各中間パッケージ223を積層したマルチチップパッケージ221全体、およびこのマルチチップパッケージ221を備える半導体装置の生産コストが高くなるおそれがある。

[0072]

50

20

30

20

30

40

50

これに対して、本実施形態によれば、前述したように、各層毎のパッケージ20のテスト良品を図5に示すように積層することで、多層時は全層のチップ歩留まりを全層分累積することなく、多層パッケージを構築することができる。また最上層の樹脂封止パッケージ20上に受動部品も搭載でき、実装密度の向上にも寄与できる。さらには、直材として既存の半導体パッケージに銅箔を追加するだけで積層用のパッケージとすることができるとともに、組立設備の流用も可能であり、チップ積層型のマルチチップパッケージ21を低コストで提供できる。これについては、後述する第8および第9の各実施形態において詳しく説明する。

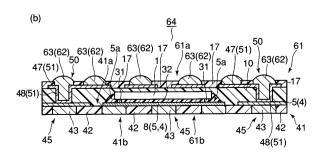

## [0073]

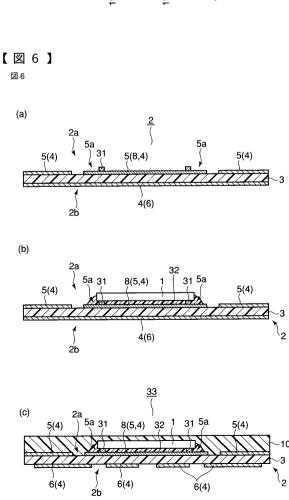

(第3の実施の形態)

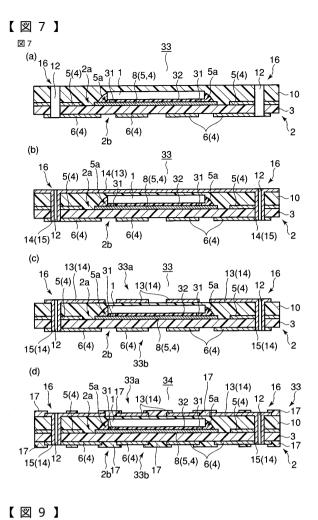

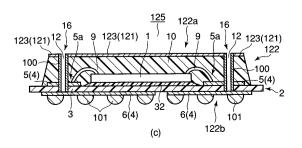

次に、本発明に係る第3実施形態を図6および図7を参照しつつ説明する。図6および図7は、それぞれ本実施形態に係る半導体装置の製造方法を示す工程断面図である。なお、第1実施形態と同一部分には同一符号を付して、その詳しい説明を省略する。

### [0074]

本実施形態においては、前述した第1実施形態におけるワイヤボンディング法に代わり、フリップチップ接続法により半導体チップ1をフレキシブル基材2に接続してなる半導体装置およびその製造方法について説明する。以下、詳しく説明する。

### [0075]

先ず、図6(a)に示すように、チップ搭載基材として、前述した第1実施形態で用いた1枚のフレキシブル基材(両面銅貼テープ)2を用意する。このフレキシブル基材2のチップ搭載面2a上には、第1実施形態と同様の工程により、少なくとも1本のチップ接続配線を含む複数本の第1の配線5が形成されている。後述するように、本実施形態においては、フリップチップ接続法により半導体チップ1をチップ接続配線5に電気的に接続してフレキシブル基材2に搭載する。したがって、チップ接続配線5のうちの少なくとも1本は、半導体チップ1が搭載されるチップマウントアイランド8を兼ねて形成される。

### [0076]

チップマウントアイランド 8 の所定の領域は、半導体チップ 1 の各接続用パッド部の配置に応じて、パッド接続部 5 a として設定される。チップマウントアイランド 8 の各パッド接続部 5 a は、図示しない他のチップ接続配線を介して、後述する第 2 の配線 6 、第 3 の配線 1 3 、およびスループラグ(第 4 の配線) 1 5 に電気的に接続されているチップ接続配線 5 に、電気的に接続されている。

## [ 0 0 7 7 ]

また、各パッド接続部5aの表面には、それらに半導体チップ1の各接続用パッド部を電気的に接続するための表面処理が施される。例えば、各パッド接続部5aの表面には、半導体チップ1の各接続用パッド部の配置に応じてNi/Auめっき処理が施される。これにより、各パッド接続部5aの表面上に、半導体チップ1の各接続用パッド部の配置に応じてNiおよびAuからなるめっきバンプ(パッド接続用バンプ)31が設けられる。ただし、フリップチップ接続法を用いる本実施形態においては、各パッド接続部5aに対する表面処理は、前述したNi/Auめっきには限定されない。例えば、Ni/Auめっきの代わりに、各パッド接続部5aの表面上に図示しない半田を設けてもよい。

# [0078]

次に、図6(b)に示すように、少なくとも1個の半導体チップ1をフレキシブル基材2のチップ搭載面2a上に搭載する。具体的には、フリップチップ接続法により、1個の半導体チップ1をチップマウントアイランド8に取り付ける。この際、半導体チップ1の各接続用パッド部は、それらに対応して各パッド接続部5aの表面上に設けられた各Ni/Auめっきバンプ31に、熱圧着や超音波接合等により接合される。それとともに、半導体チップ1は、エポキシ樹脂等の接着剤32を用いてチップマウントアイランド8に接着(接合)される。

### [0079]

次に、図6(c)に示すように、第1実施形態と同様の工程に、トランスファモールド

法により、半導体チップ1、各チップ接続配線 5、チップマウントアイランド 8 (各パッド接続部 5 a)、各 N i / A u めっきバンプ 3 1、および接着剤 3 2 等を覆って、フレキシブル基材 2 のチップ搭載面 2 a 上に封止樹脂 1 0 を設ける。それとともに、フレキシブル基材 2 のチップ非搭載面 2 b 上に、1 枚の C u 箔 4 からなる複数本の第 2 の配線 6 を形成する。これまでの工程により、半導体チップ 1、フレキシブル基材 2、各第 2 の配線 6、および封止樹脂 1 0 等からなる樹脂封止パッケージ 3 3 が作成される。この樹脂封止パッケージ 3 3 は、本実施形態の半導体装置 3 4 の主要な構成部分となる。

### [0800]

次に、図7(a)に示すように、第1実施形態と同様の工程により、樹脂封止パッケージ33の各配線接続部16に、樹脂封止パッケージ33の厚さ方向に沿って貫通して複数個のスルーホール12を設ける。

### [0081]

次に、図7(b)に示すように、第1実施形態と同様の工程により、封止樹脂10の表面上および各スルーホール12の内壁面上に、第3の配線13となる導電体14および第4の配線15となる導電体14を一体に、かつ、一括して設ける。すなわち、封止樹脂10の表面上に第3の配線13となる1層のCu層14を設けるとともに、各スルーホール12内に1層のCu層14からなるスループラグ15を設ける。

### [0082]

次に、図7(c)に示すように、第1実施形態と同様の工程により、封止樹脂10の表面上に、1層のCu層14からなる複数本の第3の配線13を形成する。前述した第1実施形態と同様に、本実施形態においても、樹脂封止パッケージ33の各第3の配線13が形成されている側(封止樹脂10側)の主面をパッケージ搭載面33aとするとともに、樹脂封止パッケージ33の各第2の配線6が形成されている側(フレキシブル基材2側)の主面を基板実装面33bとする。

### [0083]

次に、図7(d)に示すように、第1実施形態と同様の工程により、複数本の第2の配線6が形成されたフレキシブル基材2のチップ非搭載面2b上に、予め定められた所定のパターンでソルダーレジスト17を塗工する。同様に、複数本の第3の配線13が形成された封止樹脂10の表面上に、予め定められた所定のパターンでソルダーレジスト17を塗工する。

### [0084]

この後、図示は省略するが、第1実施形態と同様の工程により、パッケージ搭載用端子となる各第3の配線13に、必要に応じてNi/Auめっき処理や防錆処理等の所定の表面処理を施す。続けて、樹脂封止パッケージ33の基板実装面33a上にクリーム半田を設ける。それとともに、樹脂封止パッケージ33の基板実装面33b上に、必要に応じて複数個の半田ボールを各第2の配線6に接触(接合)させて搭載する。続けて、クリーム半田が設けられた樹脂封止パッケージ33にリフローを実施して、ソルダーレジスト17から露出している各第3の配線13の表面を覆って、厚さが約50μm~0.3mmの半田層を形成する。それとともに、各スループラグ15が形成された各スルーホール12内を半田層により埋め込む。また、基板実装用端子となる各第2の配線6に、例えば防錆処理やNi/Auめっき処理等、半田が濡れ易く、かつ、高温テスト時に各第2の配線6の表面に非溶融酸化膜が形成され難くなる表面処理を必要に応じて施す。

## [0085]

続けて、これまでの工程により一括して作製された樹脂封止パッケージ33の集合体を、ダイシング等によりテープ状態から個々のパッケージごとに切断して個片化する。この後、各樹脂封止パッケージ33ごとに各種テストを実施する。そして、これらのテストに合格した樹脂封止パッケージ33を良品とする。これにより、図7(d)に示す樹脂封止パッケージ33を主要な構成部分とする、本実施形態に係る所望の半導体装置34を得る

[0086]

10

20

30

20

30

50

すなわち、樹脂封止パッケージ33のパッケージ搭載面33a上にパッケージ搭載用端子(パッケージ搭載用配線)としてのCu配線(第3の配線)13を複数本備えるとともに、樹脂封止パッケージ33の基板実装面33b上に基板実装用端子(基板実装用配線)としてのCu配線(第2の配線)6を複数本備えており、かつ、チップ搭載基材2のチップ搭載面2a上に設けられた複数本のCuチップ接続配線(第1の配線)5にフリップチップ接続されてチップ搭載基材2に搭載された1個の半導体チップ1が、各Cuチップ接続配線5および樹脂封止パッケージ33をその厚さ方向に沿って貫通して設けられた複数本のCuスループラグ(第4の配線)15を介して、各Cu配線6および各Cu配線13とに接続されている樹脂封止パッケージ33からなる半導体装置34を得る。

#### [0087]

この後、半導体装置34のパッケージ搭載面33a上には、必要に応じて図示しない受動部品等の所定の外部装置が搭載される。それとともに、半導体装置34の基板実装面33b上には、必要に応じて図示しない実装基板が実装される。あるいは、半導体装置34を必要に応じて複数個積層して、マルチチップパッケージとして用いる。

#### [0088]

以上説明したように、この第3実施形態によれば、前述した第1実施形態と同様の効果を得ることができる。また、半導体チップ1をチップ接続配線5にフリップチップ接続するので、ワイヤボンディング法と異なりボンディングワイヤの接続不良等を排除することができるとともに、半導体チップ1のマウンティング工程を簡略化することができる。これにより、半導体装置34の品質、信頼性、性能、生産効率、および歩留まり等を向上させることができるとともに、生産コストを抑制することができる。また、フリップチップ接続法を用いることにより、チップ接続配線5、ひいては第2~第4の各配線6,13,15の微細化を図ることができる。これにより、半導体装置34のコンパクト化および高集積化を図ることができる。このように、本実施形態によれば、汎用性が高く高機能な半導体装置34を効率良く低コストで、かつ、容易に製造することができる。

#### [0089]

## (第4の実施の形態)

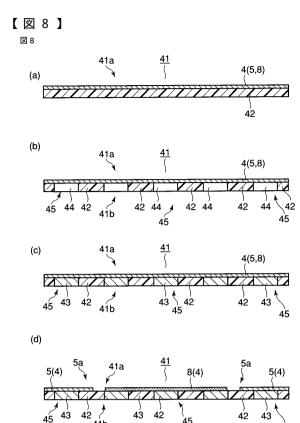

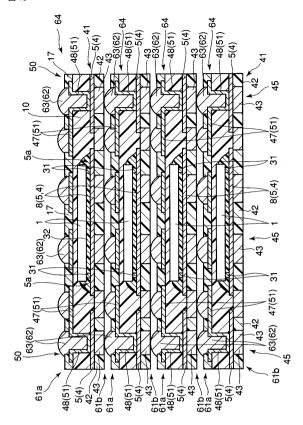

次に、本発明に係る第4実施形態を図8~図11を参照しつつ説明する。図8~図11 は、それぞれ本実施形態に係る半導体装置の製造方法を示す工程断面図である。なお、第 1実施形態と同一部分には同一符号を付して、その詳しい説明を省略する。

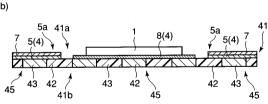

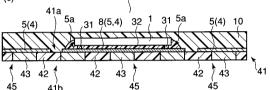

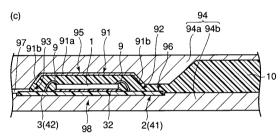

### [0090]

本実施形態においては、チップ搭載基材として、前述した第1実施形態で用いた両面銅貼テープ2の代わりに片面銅貼テープを用いる半導体装置およびその製造方法について説明する。以下、詳しく説明する。

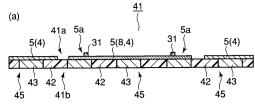

## [0091]

先ず、図8(a)に示すように、一方の主面上に半導体チップ1が少なくとも1個搭載される1枚のチップ搭載基材41を用意する。このチップ搭載基材41の基材本体42は、第1実施形態のチップ搭載基材2の基材本体3と同様に、例えばポリイミド、ガラスポキシ、あるいはBTレジン等の柔軟性を有する材料によりテープ状に形成されている。すなわち、本実施形態のチップ搭載基材41は、第1実施形態のチップ搭載基材2と異なり、本実施形態のチップ搭載基材41は、第1実施形態のチップ搭載基材2と異なり、本主のフレキシブル基材41には、その基材本体42の表裏(上下)のでは、本面で形態のチップ搭載基材41には、その基材本体42の表裏(上下)のには、本面であるチップ搭載 は、での上には、その半導体チップ1が搭載される側の主面であるチップ搭載面41aを覆って1層のCu箔4が設けられている。このような構造からなるフレキシブル基材41は、両面銅貼テープとも称される第1実施形態のフレキシブル基材2に対して、片面銅貼テープとも称される第1の配線(チップ接続配線)5およびチップウントアイランド8となる。

### [0092]

次に、図8(b)に示すように、フレキシブル基材41の基材本体42に、第2の配線

30

40

50

43を設けるための第2の配線用凹部(穴、孔)44を少なくとも1個形成する。本実施形態においては、第2の配線43をフレキシブル基材41に複数本設けるので、第2の配線43をフレキシブル基材41に複数本設けるので、第2の配線 10部 14年シブル基材41に複数本設けるので、第2の配線 10部 14年シブル基材41に複数本設けるので、第2の配沿の形式のパターンに設けられるように、その所定のパターンに沿いていていている。また、全ての第2の配線43は、基材本体42のCu第4が設けられていいの主面の表面に露出されて設けられる。すなわち、全ての第2の配線43は、フレーの表面に露出されて設けられる。すなわち、全ての第2の配線43は、10分を分に電気的に接続されて設けられる。すなわちの少なくともチップ接続配線5となるCu第4に電気的に接続される第2の配線43は、基材本体42をその厚さ方向に沿って貫通して設けられるの第2の配線43が設けられる凹部44は、基材本体42をその厚さ方向に沿って貫通10で表面に沿って貫通10に対応される。第2の配線43が設けられる凹部44は、基材本体42をその厚さ方向に沿って貫通10へルーホール、ヴィアホール)として形成される。

#### [0093]

なお、チップ接続配線 5 (半導体チップ1)とは断線される第 2 の配線 4 3 が設けられる各凹部 4 4 も、基材本体 4 2 をその厚さ方向に沿って一括して貫通するスルーホール(ヴィアホール)として形成して構わないのはもちろんである。本実施形態においては、図8 (b)に示すように、Cu箔 4 に接触して設けられる第 2 の配線 4 3 が設けられる第 2 の配線用凹部 4 4 を、全てスルーホールとして形成する。このように、全ての第 2 の配線 1 凹部 4 4 をスルーホールとして形成することにより、半導体チップ 1 と各第 2 の配線 4 3 との接続状態に拘らず、第 2 の配線用凹部 4 4 を形成する工程を簡略化(単一化)することができる。ひいては、本実施形態の半導体装置 5 2 の製造効率を高めることができる。以下の説明において、第 2 の配線 4 3 が C u 箔 4 に接触して設けられる箇所を、第 1 の配線接続部(第 1 の外部端子部) 4 5 と称することとする。

#### [0094]

第1の配線接続部45に形成される各スルーホール44は、Cu箔4が露出するまでチップ非搭載面41b側から基材本体42にその厚さ方向に沿って孔を開けることにより形成される。この掘削作業は、例えば図示しない炭酸ガスレーザー光線やUVレーザー光線等を用いて行われる。この後、例えば炭化物等の各スルーホール44内の残渣を、過マンガン酸カリウム溶液等を用いて除去(デスミア)する。

## [0095]

次に、図8(c)に示すように、各第1の配線接続部45にそれぞれ1本ずつ第2の配線43を設ける。具体的には、先ず、各第1の配線接続部45に形成された各スルーホール44の内側に所定のめっき処理を施す。続けて、めっき処理が施された各スルーホール44の内部に第2の配線となる導電体(金属)43を充填して各スルーホール44を埋め込む。この後、基材本体42のチップ非搭載面41bにCMP処理等を施すことにより、各第1の配線接続部45にそれぞれ1本ずつ第2の配線43を埋め込み形成する。なおは3の配線となる導電体43としては、例えばSn、Cu、Sn-Ag合金、あるいロロは、第2の配線となる導電体43としては、チップ1は、各第2の配線43およびにより、第1実施形態と同様に、全ての第2の配線43が半導体チップ1に電気的に接続されて形成されて形成される必要はない。半導体チップ1と断線された各第2の配線43のに非接続に形成されても構わない。半導体チップ1と断線された各第2の配線43

# [0096]

次に、図8(d)に示すように、前述した第1実施形態と同様に、Cu箔4にエッチング処理等を施して、フレキシブル基材41のチップ搭載面41a上に少なくとも1本のチップ接続配線を含む複数本の第1の配線5およびチップマウントアイランド8を形成する。なお、このエッチング処理を行う際には、フレキシブル基材41のチップ非搭載面41

30

40

50

(21)

b側に露出されている各第2の配線43の表面を図示しないマスクで全面的に覆っておく

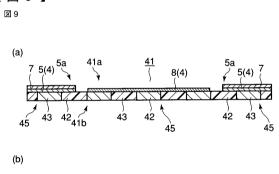

### [0097]

次に、図 9 ( a )に示すように、第 1 実施形態と同様の工程により、各チップ接続配線 5 のパッド接続部 5 a の表面上に N i / A u めっき部 7 を設ける。

#### [0098]

次に、図9(b)に示すように、第1実施形態と同様の工程により、1個の半導体チップ1をチップマウントアイランド8上に取り付ける。

#### [0099]

次に、図9(c)に示すように、第1実施形態と同様に、ワイヤボンディング法により、半導体チップ1を、各パッド接続部5a上に設けられたNi/Auめっき部7を介して各チップ接続配線5に電気的に接続する。

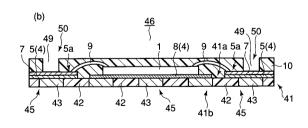

#### [0100]

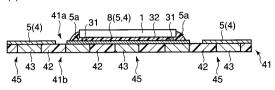

次に、図10(a)に示すように、第1実施形態と同様に、トランスファモールド法により、半導体素子1、各チップ接続配線5(各パッド接続部5a)、各Ni/Auめっき部7、チップマウントアイランド8、および各Auボンディングワイヤ9等を覆って、フレキシブル基材41のチップ搭載面41a上に封止樹脂10を設ける。これまでの工程により、半導体素子1、フレキシブル基材41、および封止樹脂10等からなる樹脂封止パッケージ(モールド封止パッケージ)46が作成される。この樹脂封止パッケージ46は、本実施形態の半導体装置52の主要な構成部分となる。封止樹脂10の表面上には、少なくとも1本の第3の配線47が設けられる。

#### [0101]

次に、図10(b)に示すように、第4の配線48を設けるための第4の配線用凹部(穴、孔)49を樹脂封止パッケージ46に少なくとも1個設ける。本実施形態においるは、第4の配線48を樹脂封止パッケージ46に複数本設けるので、第4の配線用凹部(の配線48を樹脂封止パッケージ46に複数個形成する。また、本実施形態においては、各第4の配線48ので、もとも半導体チップ1(チップ接続配線5)に電気的に接続される第4の配線48を、樹脂封止パッケージ46の厚さ方向ため、半導体チップ1に電気的に接続が記にをの配線5のため、半導体チップ1に電気的に接続が記にたり、10をその厚通して、各チップ接続配線5のパッド接続部5a上に設けられたNi/Aの配線48が設けられる各凹部49は、一次会にでは、一次の配線48が設けられる。ただした第1実施形態においては、半導体チップ1に電気的に接続される第4の配線48が設けられる各凹部49を、樹脂封止パッケージ46を貫通しない非貫通孔(非貫通ヴィアホが設けられる各凹部49を、樹脂封止パッケージ46を貫通しない非貫通孔(非貫通配線48が設けられる各凹部49は、フレキシブル基材41および各第2の配線48を貫通すること無く、封止樹脂10をその厚さ方向に沿って貫通して形成される。

### [0102]

なお、半導体チップ1に電気的に接続される第4の配線48が設けられる各凹部49は、各チップ接続配線5のパッド接続部5aおよびそれらの表面上に設けられた各Ni/Auめっき部7を貫通してもよいし、貫通しなくてもよい。半導体チップ1に電気的に接続される第4の配線48が設けられる各凹部49は、その内部に設けられる第4の配線48が、少なくとも各Ni/Auめっき部7に電気的に接触できる深さに形成されればよい。本実施形態においては、半導体チップ1に電気的に接続される第4の配線48が設けられる各凹部49を、封止樹脂10のみをその厚さ方向に沿って貫通して、各チップ接続配線5のパッド接続部5a上に設けられたNi/Auめっき部7の表面を露出する深さに形成する。

## [0103]

また、図示は省略するが、本実施形態においては、各チップ接続配線5(半導体チップ1)とは断線される第4の配線48が設けられる各凹部も非貫通ヴィアホールとして形成

20

30

40

50

する。全ての第4の配線用凹部49を非貫通ヴィアホールとして形成することにより、半導体チップ1と各第4の配線48との接続状態に拘らず、第4の配線用凹部49を形成する工程を簡略化(単一化)することができる。ひいては、半導体装置52の製造効率を高めることができる。以下の説明において、半導体チップ1に電気的に接続される第4の配線48が、各チップ接続配線5および各第3の配線47に一括して電気的に接続されて設けられる箇所を、第2の配線接続部(第2の外部端子部、表層接続端子部)50と称することとする。

### [0104]

第2の配線接続部50に形成される各非貫通ヴィアホール49は、例えばレーザー光線を用いて、Ni/Auめっき部7の表面が露出するまで封止樹脂10にその表面側から厚さ方向に沿って孔を開けることにより形成される。この際、第2の配線接続部50に形成される第4の配線用凹部49がフレキシブル基材41や各第2の配線43を貫通しない非貫通ヴィアホールとして形成されるように、エッチングされて形成された表層接続端子部50の各チップ接続配線5を、ブラインドCuマスクとして機能させる。

## [0105]

次に、図10(c)に示すように、第1実施形態と同様の工程により、第3の配線47 および第4の配線48となる1層のCu層51を、封止樹脂10の表面上および各非貫通ヴィアホール49の内側に一体に、かつ、一括して設ける。すなわち、無電解めっき法および電解めっき法を連続して行うことにより、厚さが約0.01μm~1μm程度の無電解Cu層および厚さが約1μm~30μm程度の電解Cu層が一体化されてなる1層のCu層51を、封止樹脂10の表面上および各非貫通ヴィアホール49の内側に一体に、かつ、一括して設ける。各非貫通ヴィアホール49の内側に設けられたCu層51は、そのまま第4の配線としての非貫通ヴィアプラグ48として用いられる。

### [0106]

なお、本実施形態においては、電解 C u 層の厚さは、各非貫通ヴィアホール 4 9 を塞がないように、各非貫通ヴィアホール 4 9 の直径の大きさに応じて適宜、適正な大きさに設定される。また、この一連のめっき工程においては、フレキシブル基材 4 1 のチップ非搭載面 4 1 b 側に露出されて基材本体 4 2 内に設けられた各第 2 の配線 4 3 の表面は、前述した各チップ接続配線 5 を形成する際に設けられたマスクで全面的に覆われたままであるとする。このマスクは、この一連のめっき工程が終了した後、所定の段階で各第 2 の配線 4 3 の表面から剥離されればよい。

## [0107]

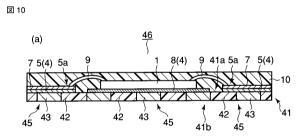

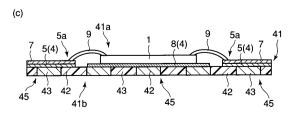

前述したように、表層接続端子部50に形成された各非貫通ヴィアプラグ48(Cu層51)は、封止樹脂10の表面上に設けられた第3の配線47となるCu層51と一体化されている。それとともに、表層接続端子部50に形成された各非貫通ヴィアプラグ48は、フレキシブル基材41のチップ搭載面41a上に形成されている各チップ接続配線に第1の配線)5に、各Ni/Auめっき部7を介して電気的に接続されている。これにより、樹脂封止パッケージ11内の半導体チップ1は、図2(b)に示すように、内部配線としての各非貫通ヴィアプラグ48および各チップ接続配線5等を介して、外部配線としての第2および第3の各配線43、47に電気的に接続される。ただし、第1実施形態と同様に、全ての非貫通ヴィアプラグ48が半導体チップ1に電気的に接続されて形成される必要はない。各非貫通ヴィアプラグ48のうちの幾つかは、半導体チップ1とは電気的に非接続に形成されても構わない。半導体チップ1と断線された各非貫通ヴィアプラグ48は、ダミープラグや中継プラグとして形成されても構わない。

#### [ 0 1 0 8 ]

次に、図11(a)に示すように、第1実施形態と同様の工程により、封止樹脂10の表面上に、1層のCu層51からなる複数本の第3の配線47を形成する。各第3の配線47のうちの幾つかは、各非貫通ヴィアプラグ(第4の配線)48および各チップ接続配線(第1の配線)5を介して半導体チップ1に電気的に接続されている。ただし、第1実施形態と同様に、全ての第3の配線47が半導体チップ1に電気的に接続されて形成され

20

30

40

50

(23)

る必要はない。各第3の配線47のうちの幾つかは、半導体チップ1とは電気的に非接続に形成されても構わない。半導体チップ1と断線された各第3の配線47は、ダミー配線や中継配線として形成されても構わない。また、前述した第1実施形態と同様に、本実施形態においても、樹脂封止パッケージ46の第3の配線47が形成されている側(封止樹脂10側)の主面をパッケージ搭載面46aとするとともに、樹脂封止パッケージ46の第2の配線43が形成されている側(フレキシブル基材41側)の主面を基板実装面46bとする。

## [0109]

次に、図11(b)に示すように、第1実施形態と同様の工程により、複数本の第3の配線47が形成された封止樹脂10の表面上に、予め定められた所定のパターンでソルダーレジスト17を塗工する。

[ 0 1 1 0 ]

この後、図示は省略するが、第1実施形態と同様の工程により、パッケージ搭載用端子となる各第3の配線47に、必要に応じてNi/Auめっき処理や防錆処理等の所定の表面処理を施す。続けて、樹脂封止パッケージ46のポッケージ搭載面46a上にクリーム半田を設ける。それとともに、樹脂封止パッケージ46の基板実装面46b上に、必要に応じて複数個の半田ボールを各第2の配線43に接触(接合)させて搭載する。続けて、クリーム半田が設けられた樹脂封止パッケージ46にリフローを実施して、ソルダーレジスト17から露出している各第3の配線47の表面を覆って、厚さが約50μm~0.3mmの半田層を形成する。それとともに、各非貫通ヴィアプラグ48が形成された各非貫通ヴィアホール49内を半田層により埋め込む。また、基板実装用端子となる各第2の配線43に、例えば防錆処理やNi/Auめっき処理等、半田が濡れ易く、かつ、高温テスト時に各第2の配線43の表面に非溶融酸化膜が形成され難くなる表面処理を必要に応じて施す。

[0111]

続けて、これまでの工程により一括して作製された樹脂封止パッケージ46の集合体を、ダイシング等によりテープ状態から個々のパッケージごとに切断して個片化する。この後、各樹脂封止パッケージ46ごとに各種テストを実施する。そして、これらのテストに合格した樹脂封止パッケージ46を良品とする。これにより、図11(b)に示す樹脂封止パッケージ46を主要な構成部分とする、本実施形態に係る所望の半導体装置52を得る。

[0112]

すなわち、樹脂封止パッケージ46のパッケージ搭載面46a上にパッケージ搭載用端子(パッケージ搭載用配線)としてのCu配線(第3の配線)47を複数本備えるとともに、樹脂封止パッケージ46の基板実装面46b側に、一端がチップ搭載基材41の基材本体42を貫通してチップ搭載基材41のチップ搭載面41a上に設けられた複数本のCuチップ接続配線(第1の配線)5に電気的に接続されているとともに、他端がチップ搭載基材41のチップ非搭載面41b側に露出された基板実装用端子としてのCu配線(第2の配線)43を複数本備えており、かつ、各Cuチップ接続配線5にワイヤボンディング接続されてチップ搭載基材41に搭載された1個の半導体チップ1が、封止樹脂10をその厚さ方向に沿って貫通して設けられた複数本の非貫通ヴィアプラグ(第4の配線)48および各Cuチップ接続配線5を介して、各Cu配線43および各Cu配線47に電気的に接続されている樹脂封止パッケージ46からなる半導体装置52を得る。

[0113]

この後、半導体装置52のパッケージ搭載面46a上には、必要に応じて図示しない受動部品等の所定の外部装置が搭載される。それとともに、半導体装置52の基板実装面46b上には、必要に応じて図示しない実装基板が実装される。あるいは、半導体装置52を必要に応じて複数個積層して、マルチチップパッケージとして用いる。

[0114]

以上説明したように、この第4実施形態によれば、前述した第1および第3の各実施形

20

30

40

50

態で用いた両面銅貼テープ2の代わりに片面銅貼テープ41を用いても、第1および第3の各実施形態と同様の効果を得ることができる。また、Cuからなる各第2の配線43は、フレキシブル基材41の基材本体42の内部に埋め込み形成されているので酸化され難い。すなわち、各第2の配線43はそれらの品質が劣化し難く形成されており、耐久性および信頼性等が向上されている。ひいては、そのような各第2の配線43を備える本実施形態の半導体装置52は、その品質、信頼性、耐久性、および歩留まり等が向上されている。このように、本実施形態によれば、汎用性、品質、信頼性、耐久性、および歩留まり等が高い半導体装置52を効率良く低コストで、かつ、容易に製造することができる。

[0115]

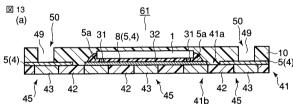

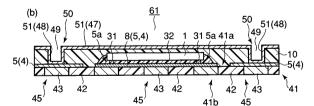

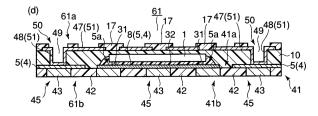

(第5の実施の形態)

次に、本発明に係る第5実施形態を図12~図14を参照しつつ説明する。図12~図14は、それぞれ本実施形態に係る半導体装置の製造方法を示す工程断面図である。なお、第1実施形態と同一部分には同一符号を付して、その詳しい説明を省略する。

[0116]

本実施形態においては、具体的には前述した第3実施形態と第4実施形態とを組み合わせてなる半導体装置およびその製造方法について説明する。以下、詳しく説明する。

[0117]

[0118]

次に、図12(b)に示すように、第3実施形態と同様の工程により、1個の半導体チップ1を各Ni/Auめっきバンプ31を介してチップマウントアイランド8にフリップチップ接続する。それとともに、半導体チップ1を接着剤32によりチップマウントアイランド8に接着する。これにより、半導体チップ1は、少なくとも1本のチップ接続配線5に電気的に接続されてフレキシブル基材41のチップ搭載面41a上に搭載される。

[0119]

次に、図12(c)に示すように、第3実施形態と同様に、トランスファモールド法により、半導体チップ1、各チップ接続配線5、チップマウントアイランド8(各パッド接続部5a)、各Ni/Auめっきバンプ31、および接着剤32等を覆って、フレキシブル基材41のチップ搭載面41a上に封止樹脂10を設ける。これまでの工程により、半導体チップ1、フレキシブル基材41、および封止樹脂10等からなる樹脂封止パッケージ61が作成される。この樹脂封止パッケージ61は、本実施形態の半導体装置64の主要な構成部分となる。

[0120]

次に、図13(a)に示すように、第4実施形態と同様の工程により、樹脂封止パッケージ61の各第2の配線接続部50に、封止樹脂10のみをその厚さ方向に沿って貫通して複数個の非貫通ヴィアホール49を設ける。

[ 0 1 2 1 ]

次に、図13(b)に示すように、第4実施形態と同様に、無電解めっき法および電解

20

30

40

50

めっき法を連続して行うことにより、厚さが約 0 . 0 1 μm ~ 1 μm程度の無電解 C u層 および厚さが約 1 μm ~ 3 0 μm程度の電解 C u層が一体化されてなる 1 層の C u 層 5 1 を、封止樹脂 1 0 の表面上および各非貫通ヴィアホール 4 9 の内側に一体に、かつ、一括して設ける。封止樹脂 1 0 の表面上に設けられた C u 層 5 1 は、後の工程において複数本の第 3 の配線 4 7 に加工形成される。また、各非貫通ヴィアホール 4 9 の内側に設けられた C u 層 5 1 は、そのまま複数本の第 4 の配線としての複数本の非貫通ヴィアプラグ 4 8 となる。

## [0122]

次に、図13(c)に示すように、第4実施形態と同様の工程により、封止樹脂10の表面上に、1層のCu層51からなる複数本の第3の配線47を形成する。各第3の配線47のうちの幾つかは、各非貫通ヴィアプラグ48および各チップ接続配線5を介して半導体チップ1に電気的に接続されている。

#### [ 0 1 2 3 ]

前述した第1、第3、および第4の各実施形態と同様に、本実施形態においても、樹脂 封止パッケージ61の第3の配線47が形成されている側(封止樹脂10側)の主面をパッケージ搭載面61aとするとともに、樹脂封止パッケージ61の第2の配線43が形成されている側(フレキシブル基材41側)の主面を基板実装面61bとする。

### [0124]

次に、図13(d)に示すように、第1、第3、および第4の各実施形態と同様の工程により、複数本の第3の配線47が形成された封止樹脂10の表面上に、予め定められた所定のパターンでソルダーレジスト17を塗工する。続けて、図示は省略するが、第1実施形態と同様の工程により、パッケージ搭載用端子となる各第3の配線13に、必要に応じてNi/Auめっき処理や防錆処理等の所定の表面処理を施す。

#### [ 0 1 2 5 ]

次に、図14(a)に示すように、樹脂封止パッケージ61のパッケージ搭載面61a上に、各第3の配線47および各非貫通ヴィアプラグ48に外部部品等を電気的に接続するための接続用導電部材62を1個ずつ設ける。本実施形態においては、具体的には、ソルダーレジスト17から露出している各第3の配線47の表面上に半田ボール62を1個ずつ設ける。それとともに、非貫通ヴィアプラグ48が1本ずつ設けられた各非貫通ヴィアホール49の開口部に半田ボール62を1個ずつ設ける。

### [0126]

次に、図14(b)に示すように、樹脂封止パッケージ61のパッケージ搭載面61a上に、半田層63を形成する。具体的には、第1実施形態と同様に、樹脂封止パッケージ61のパッケージ搭載面61a上に設けられた各半田ボール62にリフローを実施することにより、ソルダーレジスト17から露出している各第3の配線47の表面を覆って半田層63を形成する。それとともに、非貫通ヴィアプラグ48が1本ずつ設けられた各非貫通ヴィアホール49内を半田層19により埋め込む。この後、図示は省略するが、第1実施形態と同様の工程により、基板実装用端子となる各第2の配線43に、例えば防錆処理やNi/Auめっき処理等、半田が濡れ易く、かつ、高温テスト時に各第2の配線43の表面に非溶融酸化膜が形成され難くなる表面処理を必要に応じて施す。

## [0127]

続けて、これまでの工程により一括して作製された樹脂封止パッケージ61の集合体を、ダイシング等によりテープ状態から個々のパッケージごとに切断して個片化する。この後、各樹脂封止パッケージ61ごとに各種テストを実施する。そして、これらのテストに合格した樹脂封止パッケージ61を良品とする。これにより、図14(b)に示す樹脂封止パッケージ61を主要な構成部分とする、本実施形態に係る所望の半導体装置64を得る。

## [0128]

すなわち、樹脂封止パッケージ 6 1 のパッケージ搭載面 6 1 a 上にパッケージ搭載用端子(パッケージ搭載用配線)としての C u 配線(第 3 の配線) 4 7 を複数本備えるととも

に、樹脂封止パッケージ61の基板実装面61b側に、一端がチップ搭載基材41の基材本体42を貫通してチップ搭載基材41のチップ搭載面41a上に設けられた複数本のCuチップ接続配線(第1の配線)5に電気的に接続されているとともに、他端がチップ搭載基材41のチップ非搭載面41b側に露出された基板実装用端子としてのCu配線(第2の配線)43を複数本備えており、かつ、各Cuチップ接続配線5にフリップチップ接続されてチップ搭載基材41に搭載された1個の半導体チップ1が、封止樹脂10をその厚さ方向に沿って貫通して設けられた複数本の非貫通ヴィアプラグ(第4の配線)48および各Cuチップ接続配線5を介して、各Cu配線43および各Cu配線47に電気的に接続されている樹脂封止パッケージ61からなる半導体装置64を得る。

#### [0129]

この後、半導体装置64のパッケージ搭載面61a上には、必要に応じて図示しない受動部品等の所定の外部装置が搭載される。それとともに、半導体装置64の基板実装面61b上には、必要に応じて図示しない実装基板が実装される。あるいは、半導体装置64を必要に応じて複数個積層して、マルチチップパッケージとして用いる。なお、半導体装置64を複数個積層してマルチチップパッケージとして用いる技術については、後述する第6実施形態において詳しく説明する。

### [0130]

以上説明したように、この第5実施形態によれば、前述した第1、第3、および第4の各実施形態と同様の効果を得ることができる。また、本実施形態においては、Cuからなる各第2の配線43が基材本体42の内部に埋め込み形成されたフレキシブル基材(片面銅貼テープ)41に、フリップチップ接続法により半導体チップ1を搭載する。これにより、半導体装置64の品質、信頼性、耐久性、性能、生産効率、および歩留まり等を向上させつつ、半導体装置64のコンパクト化および高集積化を図ることができるとともに、その生産コストを抑制することができる。すなわち、本実施形態によれば、汎用性、品質、信頼性、耐久性、性能(機能)、および歩留まり等が高く、かつ、コンパクトな半導体装置64を効率良く低コストで、かつ、容易に製造することができる。

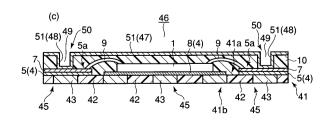

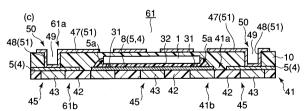

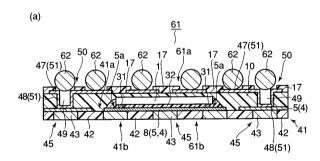

## [0131]

(第6の実施の形態)

次に、本発明に係る第6実施形態を図15および図16を参照しつつ説明する。図15および図16は、それぞれ本実施形態に係る半導体装置の製造方法を示す工程断面図である。なお、第1実施形態と同一部分には同一符号を付して、その詳しい説明を省略する。

## [0132]

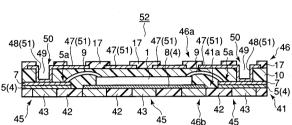

本実施形態においては、前述した第5実施形態に係る半導体装置64を複数個積層してなる半導体装置およびその製造方法について説明する。以下、詳しく説明する。

## [0133]

先ず、図15に示すように、4個の第5実施形態の半導体装置64を積層して配置する。この際、下側の半導体装置64のパッケージ搭載面61a上の各半田層63と、上側の半導体装置64の基板実装面61b上の各下部接続端子(下部接続配線、各第2の配線)43とを接触させて、各半導体装置64を配置する。

### [0134]

次に、図16に示すように、積層された4個の半導体装置64に対してリフローを実施する。これにより、隣接する半導体装置64同士が電気的に接続されるとともに、互いに接合される。

# [0135]

この後、図示は省略するが、接合された4個の半導体装置64からなる積層体に、これが実際に製品として使用できるか否かを検査するための各種テストを、低温あるいは高温等の様々な環境下で実施する。そして、これらのテストに合格した積層体を良品とする。これにより、図16に示すように、本実施形態に係る所望の半導体装置71を得る。すなわち、シングルチップパッケージ(シングルチップモジュール)としての第5実施形態の半導体装置64を4個積層してなる、チップ積層型のマルチチップパッケージ(マルチチ

10

20

30

40

ップモジュール)としての半導体装置71を得る。

## [0136]

この後、最上層のシングルチップパッケージ64のパッケージ搭載面61a上には、必要に応じて図示しない受動部品等の所定の外部装置が搭載される。それとともに、最下層のシングルチップパッケージ64の基板実装面61b上には、必要に応じて図示しない実装基板が実装される。

## [0137]

以上説明したように、この第6実施形態によれば、前述した第2実施形態と同様の効果を得ることができる。また、本実施形態のチップ積層型のマルチチップパッケージ71においては、第5実施形態の半導体装置64をシングルチップパッケージとして用いて積層する。これにより、マルチチップパッケージ71の品質、信頼性、耐久性、性能、生産効率、および歩留まり等をより向上させつつ、よりコンパクト化、かつ、より高集積化できるとともに、その生産コストをより抑制することができる。すなわち、本実施形態によれば、汎用性、品質、信頼性、耐久性、性能(機能)、および歩留まり等がより高く、かつ、よりコンパクトなチップ積層型のマルチチップパッケージ71をより効率良く、より低コストで、かつ、より容易に製造することができる。

#### [ 0 1 3 8 ]

(第7の実施の形態)

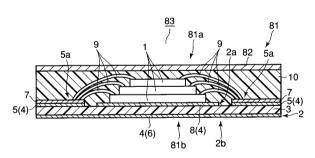

次に、本発明に係る第7実施形態を図17を参照しつつ説明する。図17は、本実施形態に係る半導体装置を示す断面図である。なお、第1実施形態と同一部分には同一符号を付して、その詳しい説明を省略する。

### [0139]

本実施形態においては、1個の半導体装置の中に複数個の半導体素子を積層してなる半 導体装置およびその製造方法について説明する。以下、詳しく説明する。

#### [ 0 1 4 0 ]

先ず、図17(a)には、前述した第1実施形態に係る樹脂封止パッケージ11(半導体装置20)と同様に、両面銅貼テープからなるフレキシブル基材2のチップ搭載面2a上に半導体チップ1をワイヤボンディング接続して搭載した樹脂封止パッケージ81を示す。フレキシブル基材2には、第1の配線(チップ接続配線)5が複数本形成されている。ただし、第1実施形態と異なり、フレキシブル基材2のチップ搭載面2a上には、3個の半導体チップ1が積層されて搭載されている。各半導体チップ1は、それぞれAuボンディングワイヤ9により各チップ接続配線5に電気的に接続されている。また、封止樹脂10の表面上には、第3の配線となるCu箔82が設けられている。

## [0141]

図示は省略するが、このような構成からなる樹脂封止パッケージ81に、第2~第4の各配線をそれぞれ複数本ずつ形成する。第2~第4の各配線のうち第2および第3の各配線は、第1実施形態と同様の工程により形成すればよい。すなわち、各第2の配線は、フレキシブル基材2のチップ非搭載面2b上に設けられているCu箔4を所定のパターンにエッチングして形成すればよい。同様に、各第3の配線は、封止樹脂10の表面上に設けられているCu箔82を所定のパターンにエッチングして形成すればよい。ただし、各第4の配線(スループラグ)は、第1実施形態と異なり、各第3の配線とは別体に、かつ、別工程で形成する。

## [0142]

具体的には、先ず、ドリル等を用いて、Cu箔82(各第3の配線)、封止樹脂10、各Ni/Auめっき部7、各チップ接続配線(第1の配線)、フレキシブル基材2、およびCu箔4(各第2の配線)を樹脂封止パッケージ81の厚さ方向に沿って一括して貫通して複数個のスルーホールを形成する。この後、例えばめっき法により、各スルーホールの内壁面を覆ってCu層を設ける。これにより、各チップ接続配線(第1の配線)、各第2の配線、および各第3の配線を樹脂封止パッケージ81の厚さ方向に沿って一括して電気的に接続するスループラグを、樹脂封止パッケージ81に複数本形成する。

10

20

30

40

### [0143]

なお、このような配線形成工程によれば、各第2の配線、各第3の配線、および各スループラグを形成する順番は適宜、適正な順番に設定することができる。例えば、各第2の配線、各第3の配線、そして各スループラグの順番に形成しても構わない。また、各第3の配線、各第2の配線、そして各スループラグの順番に形成しても構わない。また、各スループラグ、各第2の配線、そして各第3の配線の順番に形成しても構わない。あるいは、各第2の配線および各第3の配線を一括して形成した後、各スループラグを形成しても構わない。さらには、各スループラグを形成した後、各第2の配線および各第3の配線を一括して形成しても構わない。

[0144]

樹脂封止パッケージ81に第2~第4の各配線を形成した後、各第2の配線が形成されたフレキシブル基材2のチップ非搭載面2b上および各第3の配線が形成された封止樹脂10の表面上に、それぞれ予め定められた所定のパターンでソルダーレジストを塗工する。続けて、各第2の配線および各第3の配線のうちパッケージ搭載用端子となる各配線に、必要に応じてNi/Auめっき処理や防錆処理等の所定の表面処理を施す。続けて、樹脂封止パッケージ81の水ッケージ搭載面81a上にクリーム半田を設ける。それとともに、樹脂封止パッケージ81の基板実装面81b上に、必要に応じて複数個の半田ボールを各第2の配線に接触(接合)させて搭載する。

[0145]

続けて、クリーム半田が設けられた樹脂封止パッケージ81にリフローを実施して、ソルダーレジストから露出している各第3の配線の表面を覆って半田層を形成する。それとともに、各スループラグ(第4の配線)が形成された各スルーホール内を半田層により埋め込む。また、基板実装用端子となる各第2の配線に、例えば防錆処理やNi/Auめっき処理等、半田が濡れ易く、かつ、高温テスト時に各第2の配線の表面に非溶融酸化膜が形成され難くなる表面処理を必要に応じて施す。

[0146]

続けて、これまでの工程により一括して作製された樹脂封止パッケージ81の集合体を、ダイシング等によりテープ状態から個々のパッケージごとに切断して個片化する。この後、各樹脂封止パッケージ81ごとに各種テストを実施する。そして、これらのテストに合格した樹脂封止パッケージ81を良品とする。これにより、図17(a)に示す樹脂封止パッケージ81を主要な構成部分とする、本実施形態に係る所望の半導体装置83を得る。すなわち、第1実施形態の樹脂封止パッケージ11と略同様の構成からなる樹脂封止パッケージ81内に、ワイヤボンディング法により3個の半導体チップ1が積層されて搭載されている半導体装置83を得る。

[0147]

この後、半導体装置83のパッケージ搭載面81a上には、必要に応じて図示しない受動部品等の所定の外部装置が搭載される。それとともに、半導体装置83の基板実装面78b上には、必要に応じて図示しない実装基板が実装される。あるいは、半導体装置83を必要に応じて複数個積層して、マルチチップパッケージとして用いる。

[ 0 1 4 8 ]

次に、図17(b)には、前述した第4実施形態に係る樹脂封止パッケージ46(半導体装置52)と同様に、片面銅貼テープからなるフレキシブル基材41のチップ搭載面41a上に半導体チップ1をフリップチップ接続して搭載した樹脂封止パッケージ84を示す。フレキシブル基材41には、第1の配線(チップ接続配線)5および第2の配線43がそれぞれ複数本ずつ形成されている。ただし、第4実施形態と異なり、フレキシブル基材41のチップ搭載面41a上には、3個の半導体チップ1が積層されて搭載されている。各半導体チップ1は、それぞれAuボンディングワイヤ9により各チップ接続配線5に電気的に接続されている。また、封止樹脂10の表面上には、第3の配線となるCu箔82が設けられている。

10

20

30

### [0149]

図示は省略するが、このような構成からなる樹脂封止パッケージ84に、第3および第4の各配線をそれぞれ複数本ずつ形成する。各第3の配線は、第4実施形態と同様に、封止樹脂10の表面上に設けられているCu箔82を所定のパターンにエッチングして形成すればよい。ただし、各第4の配線(非貫通ヴィアプラグ)は、第4実施形態と異なり、各第3の配線とは別体に、かつ、別工程で形成する。

## [0150]

具体的には、先ず、所定のレーザー光線等を用いて、Cu箔82(各第3の配線)および封止樹脂10のみを樹脂封止パッケージ84の厚さ方向に沿って一括して貫通して複数個の非貫通ヴィアホールを形成する。この後、例えばめっき法により、各非貫通ヴィアホールの内側にCu層を設ける。これにより、各第3の配線および各第2の配線に電気的に接続されている各チップ接続配線(第1の配線)を、樹脂封止パッケージ84の厚さ方向に沿って一括して電気的に接続する非貫通ヴィアプラグを、樹脂封止パッケージ84に複数本形成する。

### [0151]

なお、このような配線形成工程によれば、各第3の配線および各非貫通ヴィアプラグを 形成する順番は適宜、適正な順番に設定することができる。例えば、各第3の配線、そして各非貫通ヴィアプラグの順番に形成しても構わない。あるいは、各非貫通ヴィアプラグ、そして各第3の配線の順番に形成しても構わない。

#### [0152]

樹脂封止パッケージ84に第3および第4の各配線を形成した後、各第2の配線43が形成されたフレキシブル基材41のチップ非搭載面41b上および各第3の配線が形成された封止樹脂10の表面上に、それぞれ予め定められた所定のパターンでソルダーレジストを塗工する。続けて、各第2の配線および各第3の配線のうちパッケージ搭載用端子となる各配線に、必要に応じてNi/Auめっき処理や防錆処理等の所定の表面処理を施す。続けて、樹脂封止パッケージ84のパッケージ搭載面84a上にクリーム半田を設ける。それとともに、樹脂封止パッケージ84の基板実装面84b上に、必要に応じて複数個の半田ボールを各第2の配線43に接触(接合)させて搭載する。

## [ 0 1 5 3 ]

続けて、クリーム半田が設けられた樹脂封止パッケージ84にリフローを実施して、ソルダーレジストから露出している各第3の配線の表面を覆って半田層を形成する。それとともに、各非貫通ヴィアプラグ(第4の配線)が形成された各非貫通ヴィアホール内を半田層により埋め込む。また、基板実装用端子となる各第2の配線43に、例えば防錆処理やNi/Auめっき処理等、半田が濡れ易く、かつ、高温テスト時に各第2の配線43の表面に非溶融酸化膜が形成され難くなる表面処理を必要に応じて施す。

## [0154]

続けて、これまでの工程により一括して作製された樹脂封止パッケージ84の集合体を、ダイシング等によりテープ状態から個々のパッケージごとに切断して個片化する。この後、各樹脂封止パッケージ84ごとに各種テストを実施する。そして、これらのテストに合格した樹脂封止パッケージ84を良品とする。これにより、図17(b)に示す樹脂封止パッケージ84を主要な構成部分とする、本実施形態に係る他の所望の半導体装置85を得る。すなわち、第4実施形態の樹脂封止パッケージ46と略同様の構成からなる樹脂封止パッケージ84内に、ワイヤボンディング法により3個の半導体チップ1が積層されて搭載されている半導体装置85を得る。

#### [ 0 1 5 5 ]

この後、半導体装置85のパッケージ搭載面84a上には、必要に応じて図示しない受動部品等の所定の外部装置が搭載される。それとともに、半導体装置85の基板実装面84b上には、必要に応じて図示しない実装基板が実装される。あるいは、半導体装置85を必要に応じて複数個積層して、マルチチップパッケージとして用いる。

## [0156]

50

10

20

30

20

30

40

50

以上説明したように、この第7実施形態によれば、前述した第1および第3~第5の各実施形態と同様の効果を得ることができる。また、本実施形態の各半導体装置83,85は、それらの中に複数個の半導体チップ1が積層されて備えられている。すなわち、本実施形態の各半導体装置83,85は、それぞれが1個でチップ積層型のマルチチップパッケージとして構成されている。したがって、各半導体装置83,85は、第1および第3~第5の各実施形態の各半導体装置20,34,52,64に比べて、さらに高集積化および高機能化(多機能化)が図られている。また、半導体チップ1の積層数が同じであれば、第1および第5の各実施形態の半導体装置20,64を複数個積層してなる第2および第6の各実施形態の半導体装置(マルチチップパッケージ)21,71に比べて、極めてコンパクトに作製することができる。

[0157]

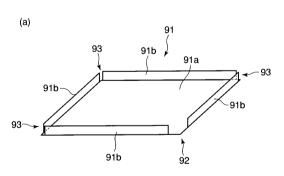

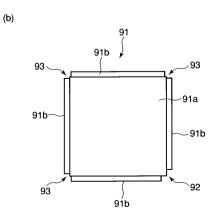

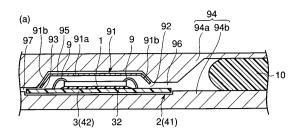

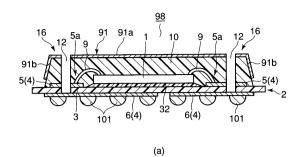

(第8の実施の形態)

次に、本発明に係る第8実施形態を図18~図20を参照しつつ説明する。図18は、本実施形態に係る半導体装置が備える第3の配線となる導電体を示す斜視図および平面図である。図19および図20は、本実施形態に係る半導体装置の製造方法を示す工程断面図である。なお、第1実施形態と同一部分には同一符号を付して、その詳しい説明を省略する。

[0158]

本実施形態においては、封止樹脂と第3の配線(上部配線、パッケージ搭載用配線)とを一括して設けてなる半導体装置およびその製造方法について説明する。以下、詳しく説明する。

[0159]

先ず、本発明を説明するのに先立って、本実施形態に対する比較例としての背景技術について図25~図27を参照しつつ説明する。

[0160]

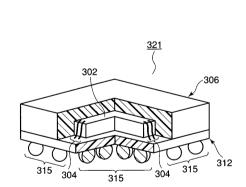

図25に示す半導体装置(半導体パッケージ)301は、例えば次に述べる方法により製造される。先ず、半導体チップ302をダイパッド303にダイアタッチする。続けて、半導体チップ302が有する図示しない複数個の接続パッド(電極)を、複数本のボンディングワイヤ304を介して複数本のリードフレーム305に電気的に接続する。続けて、半導体チップ302、ダイパッド303、各ボンディングワイヤ304、および各リードフレーム305を図示しないモールド金型のキャビティ内に収容する。この後、エポキシとシリカフィラーとの混合樹脂からなる封止樹脂(モールド樹脂)306をキャビティ内に流し込み、トランスファ成形(トランスファモールディング)を実行する。これに流し込み、トランスファ成形(トランスファモールディング)を実行する。この際、各リードフレーム305の半導体チップ302に接続されていない側の端部がモールド樹脂306により覆われない設定とする。これにより、図25に示すように、各リードフレーム305の半導体チップ302に接続されていない側の端部がモールド樹脂306から露出された半導体パッケージ(樹脂封止パッケージ)301を得る。

[0161]

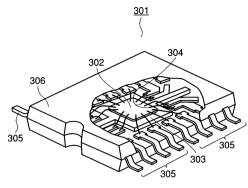

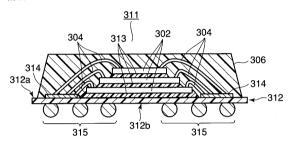

また、図26に示す半導体装置(半導体パッケージ)311は、例えば次に述べる方法により製造される。先ず、複数個の半導体チップ302を1枚のチップ搭載基板312または下側の半導体チップ302に接着材313を用いて接着される。それとともに、各半導体チップ302の各接続パッドを、複数本のボンディングワイヤ304を介してチップ搭載基板312の各接続パッドを、複数本のボンディングワイヤ304を介してチップ搭載基板312のチップ搭載面312a上に設けられている複数本のチップ接続配線314に電気的に接続する。続けて、各半導体チップ302、チップ搭載基板312、および各ボンディングワイヤ304をモールド金型のキャビティ内に収容する。この後、エポキシとシリカフィラーとの混合樹脂からなるモールド樹脂306をキャビティ内に流し込み、トランスファ 成形を実行する。この際、モールド樹脂306が、各半導体チップ302、各ボンディングワイヤ304、および各チップ接続配線314を覆って、チップ搭載基板312のチップ搭載面312a上にのみ設けられる設定とする。この後、チップ搭載基板312のチップ搭載面312a上にのみ設けられる

20

30

40

50

プ非搭載面 3 1 2 b 上に、外部端子としての半田ボール(Ball Grid Array: B G A ) 3 1 5 を複数個設ける。これにより、図 2 6 に示すように、各半導体チップ 3 0 2 、各ボンディングワイヤ 3 0 4 、および各チップ接続配線 3 1 4 がモールド樹脂 3 0 6 により覆われた、チップ積層型の半導体パッケージ(マルチチップBGAパッケージ) 3 1 1 を得る

### [0162]

また、図27に示す半導体装置(半導体パッケージ)321は、実質的に、前述した図26に示すチップ積層型の半導体パッケージ311において、チップ搭載基板312上に半導体チップ302を1個だけ搭載したパッケージである。すなわち、図27に示す半導体パッケージ321は、いわゆるシングルチップBGAパッケージである。

### [0163]

以上説明した半導体パッケージの製造方法によれば、各半田ボール315や各リードフレーム305の端部等、チップ搭載基板312やリードフレーム305に予め作り込んだ I / O端子以外はモールド樹脂306により覆われてしまう。すなわち、前述した半導体パッケージの製造方法によれば、各半導体パッケージ301,311,321の上面となるモールド樹脂306の表面に、他の装置や部品を電気的に接続するための配線や端子を作ることができない。このため、図示は省略するが、各半導体パッケージ301,311,321を実装基板上に実装すると、各半導体パッケージ301,311,321をましたエリアには他の半導体パッケージや受動部品等を実装(配置)することができない。したがって、各半導体パッケージも受動部品等を実装(配置)することができないの表面に沿った方向でしか配置することができず、半導体パッケージ301,311,321は実装密度を高めることに対する支障となってしまう。

#### [0164]

なお、図25~図27に示すような構造からなる半導体装置およびその製造方法に関する技術は、例えば特開平11-87560号公報、特開平10-284873号公報、特開2001-223295号公報、特開2001-127186号公報、特開2000-31207号公報等に開示されている。

## [0165]

本実施形態は、前述した構造からなる樹脂封止パッケージ(モールディングパッケージ)を用いる場合の実装密度の低下を改善するためになされたものであり、その目的とするところは、外部装置等を接続できる配線や端子を封止部材の表面に備えるとともに、容易に、かつ、効率良く製造できる半導体装置を提供することにある。また、そのような半導体装置を容易に、かつ、効率良く製造できる半導体装置の製造方法を提供することにある

## [0166]

本実施形態においては、前述した第1、第3~第5、および第7の各実施形態と同様に、基板上に搭載された半導体チップをトランスファモールド法により封止する。ただし、封止を行う際に、モールド金型と半導体チップ(基板)との間に、半導体チップを覆う箱形状に形成された導電体を設置する。そして、この導電体と半導体チップが搭載された基板との間に向けて封止部材を供給する。これにより、半導体チップ等の封止と封止樹脂の表面(モールド封止面)上への導電体の設置とを一括して行う。モールド封止面上に設けられた導電体は、上部配線(上部端子)やパッケージ搭載用配線(パッケージ搭載用端子)となる。以下、本実施形態に係る半導体装置およびその製造方法について、図18~図20を参照しつつ詳しく説明する。

# [0167]

先ず、図18(a),(b)を参照しつつ、封止樹脂10の表面上に設けられて第3の配線(上部配線、パッケージ搭載用配線)となる導電体91について説明する。導電体91には、その厚さが約1~20μmの電解銅からなる銅箔(Cu箔)を用いることが好ましい。本実施形態で用いるCu箔91は、図18(a)に示すように、それぞれ四角形状

30

40

50

に形成された1つの主面(蓋部、底部)91 a および4つの側面(側壁部)91 b からなる。C u 箔91 は、具体的には、後述するモールディング工程において用いるモールド金型94のキャビティ部95の形状に合う箱形状に形成される。また、C u 箔91は、封止樹脂10(半導体チップ1)に対向する側が開口されて、チップ搭載基材2(41)に搭載された半導体チップ1を覆う箱形状に形成される。

## [0168]

C u 箔 9 1 の箱形状への成形は、具体的には、図 1 8 ( b ) に示すような十字形状への切り出しと、および図 1 8 ( a ) に示すような箱形状への折り曲げとを、図示しない打ち抜き金型を用いて一括して行うことが好ましい。この際、各側壁部(折り曲げ部) 9 1 b の高さ(幅)は、それらが封止工程中および封止工程後にチップ搭載基材 2 ( 4 1 ) に搭載された半導体チップ 1 に接触するおそれがない大きさに設定される。具体的には、各側壁部 9 1 b の高さは、チップ搭載基材 2 ( 4 1 ) のチップ搭載面 2 a ( 4 1 a ) から半導体チップの表面(上面)までの高さに、約 1 0 ~ 2 0 0 μ m 加えた大きさに設定されることが好ましい。

## [0169]

また、Cu箔91には、その外側から内側に封止樹脂10を導入するための封止部材導入口92が少なくとも1箇所に設けられる。この封止部材導入口92は、モールド金型94の封止樹脂射出ゲート部96に対応する位置に設けられる。本実施形態においては、封止部材導入口92は、図18(a),(b)に示すように、Cu箔91の四隅のうちの1箇所に設けられる。また、封止部材導入口92は、これを介してCu箔91の外側から内側に封止樹脂10を円滑に流入させるために、各側壁部91b同士の間隔をモールド金型94の封止樹脂射出ゲート部96と同等以上の大きさに離間させることにより形成される

### [0170]

同様に、Cu箔91には、その内側と外側とで気体を自在に出入りさせるための通気口93が、封止部材導入口92とは異なる箇所に少なくとも1個設けられる。モールド金型94には、その内部に封止樹脂10が流れ込んだ際にその封止樹脂10と略同体積のエアを金型94内から排出するためのエアベント部(エアベントロ)97が設けられている。通気口93は、モールド金型94のエアベント部97に対応する位置に設けられる。本実施形態においては、通気口93は、図18(a),(b)に示すように、Cu箔91の四隅のうち封止部材導入口92が設けられていない3箇所に設けられる。また、通気口93は、これを介して金型94内のエアをCu箔91の内側から外側に排出できるように、各側壁部91b同士の間隔をモールド金型94のエアベント部97と同等以下の大きさに離間させることにより形成される。各通気口93は、封止部材導入口92よりも狭く形成される。

## [0171]

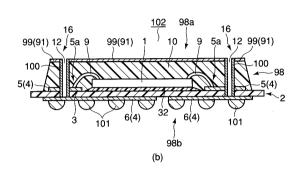

次に、図19(a)~(c)を参照しつつ、半導体チップ1等の封止および封止樹脂1 0の表面上へのCu箔91の設置を一括して行う、本実施形態のトランスファモールド法 について説明する。

## [0172]

先ず、図19(a)に示すように、モールド上金型94aおよびモールド下金型94bからなるモールド金型94のキャビティ部95内に、半導体チップ1が搭載されたチップ搭載基材2(41)を配置する。併せて、半導体チップ1やAuボンディングワイヤ9等をそれらの上方から覆うように、前述した箱形状のCu箔91を、その開口側を半導体チップ1に対向させてキャビティ部95内に配置する。すなわち、Cu箔91の蓋部91aおよび側壁部91bをキャビティ部95のモールド上金型94a側の内面に沿わせて、Cu箔91をキャビティ部95内に配置する。この際、図19(a)に示すように、Cu箔91の封止部材導入口92をモールド金型94の封止樹脂射出ゲート部96に対向させる。同様に、Cu箔91の各通気口93をモールド金型94のエアベント部97に対向させる。このように、半導体チップ1が搭載されたチップ搭載基材2(41)およびCu箔9

1 をモールド金型 9 4 のキャビティ部 9 5 内に収容した後、キャビティ部 9 5 内に向けて 封止樹脂 1 0 を射出する。

### [0173]

次に、図19(b)に示すように、モールド金型94の封止樹脂射出ゲート部96から、Cu箔91の封止部材導入口92を介して、Cu箔91と半導体チップ1が搭載されたチップ搭載基材2(41)との間に封止樹脂10を導入する。

#### [0174]

次に、図19(c)に示すように、Cu箔91の内面、チップ搭載基材2(41)上の半導体チップ1、および各Auボンディングワイヤ9等を略全て覆うまで、Cu箔91とチップ搭載基材2(41)との間に封止樹脂10を流入(充填)させる。これにより、Cu箔91の表面を露出させつつ、半導体チップ1や各Auボンディングワイヤ9等の封止と、封止樹脂10の表面(モールド封止面)上へのCu箔91の取り付けとを一括して行う。モールド封止面上に設けられたCu箔91は、第3の配線、すなわち上部配線(上部端子)やパッケージ搭載用配線(パッケージ搭載用端子)99となる。これまでの工程により、半導体チップ1、フレキシブル基材2(41)、封止樹脂10、およびCu箔91等からなる樹脂封止パッケージ(モールド封止パッケージ)98が作成される。この樹脂封止パッケージ98は、本実施形態の半導体装置102の主要な構成部分となる。

### [0175]

このような本実施形態のトランスファモールディング工程によれば、箱形状のCu箔91は、その内側に流れ込んだ封止樹脂10の圧力(射出圧)により、モールド上金型94a側に押し付けられる。この結果、Cu箔91は、さらにキャビティ部95のモールド上金型94a側の内面に沿う形状(金型形状)に成形される。前述したように、Cu箔91の各側壁部91bの高さは、それらが封止工程中および封止工程後にチップ搭載基材2(41)に搭載された半導体チップ1等に接触するおそれがない大きさに設定されている。したがって、Cu箔91は、半導体チップ1や各Auボンディングワイヤ9等に接触することなく、モールド封止面上に取り付けられる。

## [0176]

また、前述したトランスファモールディング工程によれば、図19(c)に示すように、封止樹脂10の圧力によりキャビティ部95のモールド上金型94a側の内面に沿って成形されたCu箔91が、封止樹脂(モールド樹脂)10とモールド上金型94aとの間に設けられる。そのような位置に配置されたCu箔91は離型材の役割を果たすので、モールド金型84と樹脂封止パッケージ98との離型性向上に寄与する。これにより、モールド樹脂10の組成材料全体に占める離型材の割合を低減させて、モールド樹脂10とCu箔91との密着強度を向上させることができる。けせて、モールド樹脂10と半導体チップ1やチップ搭載基材2(41)との密着強度を向上させることができる。この結果、樹脂封止パッケージ98全体の封止性(密封性)を向上させることができる。

## [0177]

なお、前述したトランスファモールディング工程を行うのに先立って、チップ搭載基材2(41)のチップ搭載面2a(41a)上には、各Auボンディングワイヤ9を介して半導体チップ1が電気的に接続されるチップ接続配線(第1の配線)5が予め複数本形成される。そして、チップ搭載基材2を用いる場合には、トランスファモールディング工程後に、チップ搭載基材2のチップ非搭載面2b上に第2の配線6が複数本形成される。電気的に接続するための外部接続配線(外部接続端子)や、半導体チップ1を実装基板に実装するための外部実装配線(外部接続端子)や、半導体チップ1を実装基材に実装するための外部実装配線(外部接続端子)で、半導体チップ指載基材2には、トランスファモールディング工程後に、前述した各第1の配線接続部(縦接続部)16においてチップ搭載基材2を貫通して第4の配線が複数本形成される。これら各第4の配線は、各チップ接続配線5と各第2の配線6とをチップ搭載基材2の厚さ方向(縦方向)に沿って電気的に接続するための縦接続配線となる。

## [0178]

40

20

30

50

これに対して、チップ搭載基材 4 1 を用いる場合には、トランスファモールディング工程を行うのに先立って、前述した各第 1 の配線接続部(第 1 の外部端子部、縦接続部) 4 5 においてチップ搭載基材 4 1 を貫通して第 2 の配線 4 3 が予め複数本形成される。そして、これら各第 2 の配線 4 3 自体が、縦接続配線の一部としての役割を果たす。

#### [0179]

ただし、図19(a)~(c)においては、図面を見易くするために、チップ搭載基材 2(41)の基材本体3,42のみを図示し、チップ接続配線(第1の配線)5および第 2の配線43等の各配線の図示を省略している。

#### [ 0 1 8 0 ]

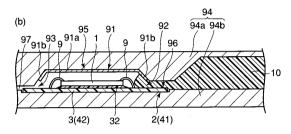

次に、図20(a),(b)を参照しつつ、前述したトランスファモールディング工程により作成された樹脂封止パッケージ98に、上部配線(パッケージ搭載用配線)としての第3の配線99や、縦接続配線としての第4の配線100等を形成する工程について簡潔に説明する。以下、チップ搭載基材として両面銅貼テープであるチップ搭載基材2を用いる場合について説明する。この場合、第3の配線99および第4の配線100は、前述した第1および第3の各実施形態と略同様の方法により形成される。なお、チップ搭載基材の代わりにリードフレームを用いる場合については、第9実施形態において説明する。

### [0181]

先ず、図20(a)に示すように、Cu箔91が封止樹脂10の表面上に一体化されて設けられた樹脂封止パッケージ98の各第1の配線接続部(縦接続部)16に、ドリルあるいはレーザーなどを用いてスルーホール12を1個ずつ形成する。本実施形態においては、各スルーホール12は、樹脂封止パッケージ98の各縦接続部16において、チ貫通 基材2のチップ非搭載面2b上に設けられているCu箔4(第2の配線6)を貫通して形成される。この際、各スルーホール12の径の大きさは、樹脂封止パッケージ98の下の比が約1:6以下となる大きさに設定されることが好ましい。また、チップ搭載 基材2の各スルーホール12の径の大きさに設定されることが好ましい。また、チップ搭載しい。すなわち、各チップ接続配線(第1の配線)5や各第2の配線6となるCu箔4のしい。すなわち、各チップ接続配線(第1の配線)5や各第2の配線6となるの大きないましい。すなわち、各チップ接続配線(第1の配線)5や各第2の配線6となるCロンカカち、第4の配線としてのスループラグ100ド電気的に接続される部分の径の大きは、スルーホール12の径の大きさに約5~100ドm程度加えた大きさに設定されることが好ましい。

# [0182]

次に、図20(b)に示すように、無電解銅めっきを行うことにより、各スルーホール12の内壁面に厚さ約0.01~3μm程度の無電解Cuめっき膜を全面的に設ける。これられているCu箔91と樹脂封止パッケージ98のポッケージ搭載面(上面、表面)988 b 上に設けられているCu箔91と樹脂封止パッケージ98の基板実装面(下面、良田とに設けられているCu箔91と樹脂対止パッケージ98の基板実装面(下面、良田とに設けられているCu箔(カーボール)の一般では、各スルーホール12内の無電解といるの無電解のっき工程を行うのに際して、樹脂封止パッケージョののに際して、樹脂対止パッケージョののに際して、樹脂対止パッケージョののに際は、それら、このの後、各スルーホール12内のの無電解といるをででは、各スルーホール12内のでは、各スルーホール12内のでは、各スルーホール12内のでは、各スルーホール12内のに際にしないででは、各スルーホール12内のに際により、各スルーホール12内のに際により、各スルーホール12内のに要により、各スルーホール12内のにはより、となる。これら各Cu膜100は、そのまま縦接続配線としてのスループラグ(第4の配線)となる。

# [0183]

この後、図示は省略するが、感光性ドライフィルムなどのレジスト膜を C u 箔 9 1 の表面上に貼り付ける。続けて、 C u 箔 9 1 側の複数個の縦接続端子(配線)、パッケージ搭載面 9 8 a 上に搭載する部品の接続端子に応じた実装端子、および複数本の第 3 の配線 9 9 等のそれぞれのパターンが描画されている露光マスクを用いて露光作業を行う。これに

より、Cu箔91の表面に、前述した各端子や各第3の配線99等のパターンを転写する。この後、Cu箔91にエッチング処理や現像処理等を施す。これにより、樹脂封止パッケージ98のパッケージ搭載面98a上に複数本の第3の配線99等が形成される。続けて、必要に応じて、各第3の配線99の表面上にソルダーレジストを塗工したり、各縦接続端子や各実装端子等の表面にNi/Auめっきを施したりする。

#### [0184]

同様に、図示は省略するが、感光性ドライフィルムなどのレジスト膜をチップ搭載基材2のチップ非搭載面2b上に設けられているCu箔4に貼り付ける。続けて、Cu箔4側の複数個の縦接続端子(配線)、基板実装面98b上に実装する基板の接続端子に応じた実装端子、および複数本の第2の配線6等のそれぞれのパターンが描画されている露光マスクを用いて露光作業を行う。これにより、Cu箔4の表面に、前述した各端子や各第2の配線6等のパターンを転写する。この後、Cu箔4にエッチング処理や現像処理等を施す。これにより、樹脂封止パッケージ98の基板実装面98b上に複数本の第2の配線6等が形成される。続けて、必要に応じて、各第2の配線6の表面上にソルダーレジストを塗工したり、各縦接続端子や各実装端子等の表面にNi/Auめっきを施したりする。

#### [ 0 1 8 5 ]

これまでの工程により、図20(b)に示すように、樹脂封止パッケージ98のパッケージ搭載面98a上に、所望の配線パターンからなる複数本の第3の配線99等を形成することができる。各第3の配線99は、パッケージ搭載面98a上にパッケージ等の部品を搭載するための部品搭載用配線(部品搭載用端子)となる。また、各第2の配線6には、例えば防錆処理やNi/Auめっき処理等、半田が濡れ易く、かつ、高温テスト時に各第2の配線6の表面に非溶融酸化膜が形成され難くなる表面処理が必要に応じて施される。それとともに、樹脂封止パッケージ98の基板実装面98b上に、複数個の半田ボール101を各第2の配線6に接触(接合)させて搭載する。

### [0186]

続けて、これまでの工程により一括して作製された樹脂封止パッケージ98の集合体を、ダイシング等によりテープ状態から個々のパッケージごとに切断して個片化する。この後、各樹脂封止パッケージ98ごとに各種テストを実施する。そして、これらのテストに合格した樹脂封止パッケージ98を良品とする。これにより、図20(b)に示す樹脂封止パッケージ98を主要な構成部分とする、本実施形態に係る所望の半導体装置102を得る。すなわち、トランスファモールディング工程により、複数本の第3の配線99と封止樹脂10とが一体に、かつ、一括して設けられた樹脂封止パッケージ98からなる半導体装置102を得る。

## [0187]

この後、半導体装置102のパッケージ搭載面98a上には、必要に応じて図示しない受動部品等の所定の外部装置が搭載される。それとともに、半導体装置102の基板実装面98b上には、必要に応じて図示しない実装基板が実装される。あるいは、半導体装置102を必要に応じて複数個積層して、マルチチップパッケージとして用いる。

## [0188]

以上説明したように、この第8実施形態によれば、前述した第1および第3~第5の各実施形態と同様の効果を得ることができる。また、本実施形態においては、トランスファモールディング工程により、第3の配線99となるCu箔91と封止樹脂10とを一体に、かつ、一括して設ける。これにより、各第3の配線99と封止樹脂10との密着強度を高められた各第3の配線99は、それらの強度、耐久性、および信頼性も高められている。それとともに、各第3の配線99と封止樹脂10との密着強度を高めることにより、封止樹脂10中の離型材の含有量を減らして、封止樹脂10と半導体チップ1やチップ搭載基材2との密着強度を高めることができる。この結果、樹脂封止パッケージ98全体の封止性(密封性)を高めて、半導体装置102全体の強度、耐久性、および信頼性を高めることができる。

## [0189]

50

40

20

30

40

50

また、Cu箔91と封止樹脂10とを一括して設けることにより、半導体装置102(樹脂封止パッケージ98)の製造工程を簡略化することができる。さらに、トランスファモールディングを行う際に、Cu箔91を半導体チップ1が搭載されたチップ搭載基材2とともにモールド金型94のキャビティ95内に配置するだけなので、一般の組立設備の流用も極めて容易である。したがって、設備費等の負担が増えるおそれは殆ど無い。このように、本実施形態によれば、汎用性、強度、信頼性、および耐久性がより高められた半導体装置102を効率良く低コストで、かつ、容易に製造することができる。

## [ 0 1 9 0 ]

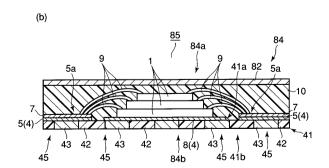

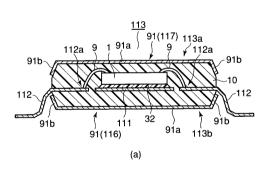

(第9の実施の形態)

次に、本発明に係る第9実施形態を図21を参照しつつ説明する。図21は、本実施形態に係る半導体装置の製造方法を示す工程断面図である。なお、第1実施形態と同一部分には同一符号を付して、その詳しい説明を省略する。

#### [0191]

本実施形態は、前述した第8実施形態に係る半導体装置およびその製造方法に関するバリエーションの一つである。具体的には、本実施形態では、チップ搭載基材の代わりにリードフレームに半導体チップを接続する。以下、詳しく説明する。

### [0192]

先ず、図21(a)に示すように、1個の半導体チップ1をチップマウントアイランド111上に接着材32を用いて接着して搭載する。続けて、半導体チップ1の各接続パッド(電極)と第1の配線としての複数本のリードフレーム112とを、それぞれAuボンディングワイヤ9を用いて電気的に接続する。各Auボンディングワイヤ9は、チップ接続配線としての各リードフレーム112のパッド接続部112aに接続される。

## [0193]

続けて、図示は省略するが、チップマウントアイランド111上に搭載された半導体チップ1、各リードフレーム112、および各Auボンディングワイヤ9等をモールド金型のキャビティ部内に配置する。併せて、半導体チップ1を、その開口側を半導体チップ1に対向させてキャビティ部内に配置する。に、本実施形態においては、半導体チップ1や各Auボンディングワイヤ9等をそれらの下方からも覆うように、他の年でで、第一日では、半導体チップ1、各Auボンディングワイヤ9等をそれらの下方からもで、他の第一日ででは、一番では、半導体チップ1、各Auボンディングワイヤ9、およびチップマウントアイランド111に対向させてキャンディングワイヤ9、およびチップマウントアイランド111をを半導体チップ1の上下(表2枚の箱形状のCu箔91を対向させてキャビティの各通気口93をモールド金型のエアベント部に対向させられて配置される。同様に、各Cu箔91は、それらの各通気口93をモールド金型のエアベント部に対向させられて配置される。

## [0194]

続けて、半導体チップ1、各リードフレーム112、および2枚のCu箔91等が収容されたキャビティ部内に向けて封止樹脂10を射出する。封止樹脂10は、モールド金型の封止樹脂射出ゲート部から、各Cu箔91の封止部材導入口92を介して、各Cu箔91の間に導入される。封止樹脂10は、各Cu箔91の内面、チップマウントアイランド111上の半導体チップ1、各Auボンディングワイヤ9、各リードフレーム112のパッド接続部112a等を略全て覆うまで、各Cu箔91の間に流入(充填)させられる。これにより、各Cu箔91の表面および各リードフレーム112のパッド接続部112a側とは反対側の端部を露出させつつ、半導体チップ1や各Auボンディングワイヤ9等の封止と、封止樹脂10の上下両主面(上下両モールド封止面)上への各Cu箔91の取り付けとを一括して行う。

### [0195]

各Cu箔91のうち、半導体チップ1に対向してモールド封止面上に設けられたCu箔

20

30

40

50

91は、第3の配線、すなわち上部配線(上部端子)やパッケージ搭載用配線(パッケージ搭載用端子)117となる。また、各Cu箔91のうち、チップマウントアイランド111に対向してモールド封止面上に設けられたCu箔91は、第2の配線、すなわち下部配線(下部端子)や基板実装用配線(基板実装用端子)116となる。なお、各Cu箔91のうち少なくとも半導体チップ1に対向してモールド封止面上に設けられたCu箔91の各側壁部91bの高さは、各側壁部91bが封止工程中および封止工程後に各リードフレーム112に接続された各Auボンディングワイヤ9等に接触するおそれがない大きさに設定されている。例えば、各側壁部91bの高さは、各リードフレーム112の表面から各Auボンディングワイヤ9の最も高い部分までの高さに、約10~200μm加えた大きさに設定されることが好ましい。これにより、Cu箔91は、各Auボンディングワイヤ9等に接触することなく、モールド封止面上に取り付けられる。

[0196]

これまでの工程により、図21(a)に示すように、半導体チップ1、各リードフレーム112、封止樹脂10、および上下2枚のCu箔91等からなる樹脂封止パッケージ(モールド封止パッケージ)113が作成される。この樹脂封止パッケージ113は、本実施形態の半導体装置119の主要な構成部分となる。このパッケージ113のように、チップ接続配線として複数本のリードフレーム112を使用する場合、トランスファモールディングを行う際に、半導体チップ1や各リードフレーム112等を間に挟んで、キャビティ部のモールド上金型側およびモールド下金型側にそれぞれ1枚ずつCu箔91を対向配置するとよい。このような設定でトランスファモールディングを行うことにより、半導体チップ1や各Auボンディングワイヤ9等の封止と併せて、封止樹脂10(パッケージ113)の上下両主面上に外部配線(外部端子)として利用する導電体(Cu箔)91を一括して取り付けることができる。

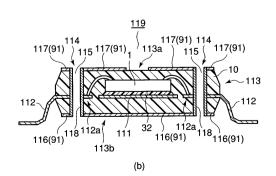

[0197]

[0198]

次に、図21(b)に示すように、無電解銅めっきを行うことにより、各スルーホール115の内壁面に厚さ約0.01~3μm程度の無電解Cuめっき膜を全面的に設ける。これにより、樹脂封止パッケージ113のパッケージ搭載面(上面、表面)113a上に設けられているCu箔91と樹脂封止パッケージ113の基板実装面(下面、裏面)113b上に設けられているCu箔91との導電性が、各スルーホール115内の無電解Cuめっき膜により確保される。なお、この無電解めっき工程を行うのに際して、樹脂封止パッケージ113の露出面上に既にエッチング済み(パターン形成済み)の配線や端子等があれば、それらを図示しないマスクにより予め覆っておく。この後、各スルーホール115内の無電解Cuめっき膜をシード層として電解銅めっきを行うことにより、各スルーホール115内のmu膜の膜厚を一般的な配線の厚さと同程度の厚さまで厚くする。これに

20

30

40

50

より、各スルーホール 1 1 5 内に一体化された無電解 C u めっき膜および電解 C u めっき膜からなる C u 膜 1 1 8 を設ける。これら各 C u 膜 1 1 8 は、そのまま縦接続配線としてのスループラグ(第 4 の配線)となる。

### [0199]

この後、図示は省略するが、感光性ドライフィルムなどのレジスト膜を上下両 C u 箔 9 1 の表面上に貼り付ける。続けて、樹脂封止パッケージ 1 1 3 の基板実装面 1 1 3 b 上に設けられている C u 箔 9 1 に対して露光作業を行う。この際、 C u 箔 9 1 側の複数個の縦接続端子(配線)、基板実装面 1 1 3 b 上に実装する基板の接続端子に応じた実装端子、および複数本の第 2 の配線 1 1 6 等のそれぞれのパターンが描画されている露光マスクを用いる。これにより、基板実装面 1 1 3 b 上の C u 箔 9 1 の表面に、前述した各端子や各第 2 の配線 1 1 6 等のパターンを転写する。この後、 C u 箔 9 1 にエッチング処理や現像処理等を施す。これにより、樹脂封止パッケージ 1 1 3 の基板実装面 1 1 3 b 上に複数本の第 2 の配線 1 1 6 等が形成される。続けて、必要に応じて、各第 2 の配線 1 1 6 の表面上にソルダーレジストを塗工したり、各縦接続端子や各実装端子等の表面にNi/Auめっきを施したりする。

#### [0200]

同様に、図示は省略するが、樹脂封止パッケージ113のパッケージ搭載面113a上に設けられているCu箔91に対して露光作業を行う。この際、Cu箔91側の複数個の縦接続端子(配線)、パッケージ搭載面113a上に搭載する部品の接続端子に応じた実装端子、および複数本の第3の配線117等のそれぞれのパターンが描画されている露光マスクを用いる。これにより、パッケージ搭載面113a上のCu箔91の表面に、前述した各端子や各第3の配線117等のパターンを転写する。この後、Cu箔91にエッチング処理や現像処理等を施す。これにより、樹脂封止パッケージ113のパッケージ搭載面113a上に複数本の第3の配線117等が形成される。続けて、必要に応じて、各第3の配線117の表面上にソルダーレジストを塗工したり、各縦接続端子や各実装端子等の表面にNi/Auめっきを施したりする。

## [ 0 2 0 1 ]

これまでの工程により、図21(b)に示すように、樹脂封止パッケージ113の基板実装面113b上に、所望の配線パターンからなる複数本の第2の配線116等を形成することができる。各第2の配線116は、基板実装面113b上に実装基板を実装するための基板実装用配線(基板実装用端子)となる。同様に、樹脂封止パッケージ113のパッケージ搭載面113a上に、所望の配線パターンからなる複数本の第3の配線117等を形成することができる。各第3の配線117は、パッケージ搭載面113a上にパッケージ等の部品を搭載するための部品搭載用配線(部品搭載用端子)となる。なお、図示は省略するが、各第2の配線116には、例えば防錆処理やNi/Auめっき処理等、半田が濡れ易く、かつ、高温テスト時に各第2の配線116の表面に非溶融酸化膜が形成され難くなる表面処理が必要に応じて施される。それとともに、各第2の配線116の露出面上には、必要に応じて複数個の半田ボールが搭載される。

# [0202]

続けて、これまでの工程により一括して作製された樹脂封止パッケージ113の集合体を、ダイシング等によりテープ状態から個々のパッケージごとに切断して個片化する。この後、各樹脂封止パッケージ113ごとに各種テストを実施する。そして、これらのテストに合格した樹脂封止パッケージ113を良品とする。これにより、図21(b)に示す樹脂封止パッケージ113を主要な構成部分とする、本実施形態に係る所望の半導体装置119を得る。すなわち、トランスファモールディング工程により、封止樹脂10を間に挟んでその上下両主面上に対向配置される複数本の第2の配線116および複数本の第3の配線117、ならびに封止樹脂10が一体に、かつ、一括して設けられた樹脂封止パッケージ113からなる半導体装置119を得る。

## [0203]

この後、半導体装置119のパッケージ搭載面113a上には、必要に応じて図示しな

い受動部品等の所定の外部装置が搭載される。それとともに、半導体装置119の基板実装面113 b 上には、必要に応じて図示しない実装基板が実装される。あるいは、半導体装置119を必要に応じて複数個積層して、マルチチップパッケージとして用いる。

### [0204]

以上説明したように、この第9実施形態によれば、前述した第1、第3~第5、および第8の各実施形態と同様の効果を得ることができる。また、第2の配線116となるCu箔91、第3の配線117となるCu箔91、および封止樹脂10を一括して設けることにより、半導体装置119(樹脂封止パッケージ113)の製造工程をさらに簡略化することができる。また、トランスファモールディングを行う際に、半導体チップ1が電気的に接続された各リードフレーム112を2枚のCu箔91の間に挟んでモールド金型のキャビティ内に配置するだけなので、一般の組立設備の流用も極めて容易である。したがって、設備費等の負担が増えるおそれは殆ど無い。このように、本実施形態によれば、汎用性、強度、信頼性、および耐久性がさらに高められた半導体装置119をより効率良くより低コストで、かつ、より容易に製造することができる。

### [0205]

(第10の実施の形態)

次に、本発明に係る第10実施形態を図22を参照しつつ説明する。図22は、本実施 形態に係る半導体装置の製造方法を示す工程断面図である。なお、第1実施形態と同一部 分には同一符号を付して、その詳しい説明を省略する。

## [0206]

本実施形態においては、前述した第8および第9の各実施形態と同様に、封止樹脂の表面上に第3の配線となる導電体を設けた後、封止樹脂の内部に第4の配線を設ける。ただし、第8および第9の各実施形態と異なり、封止樹脂と導電体とを別工程により別体に設ける。以下、簡潔に説明する。

## [0207]

先ず、図22(a)に示すように、ワイヤボンディング法により半導体チップ1が搭載されたチップ搭載基材2のチップ搭載面2a上に、半導体チップ1、各チップ接続配線5、およびAuボンディングワイヤ9等を覆って封止樹脂10を設ける。封止樹脂10は、第8および第9の各実施形態と同様に、トランスファモールディング法によりチップ搭載基材2のチップ搭載面2a上に設けられる。ただし、本実施形態のトランスファモールディング工程においては、第8および第9の各実施形態と異なり、封止樹脂10のみをチップ搭載基材2のチップ搭載面2a上に設ける。

## [0208]

次に、図22(b)に示すように、封止樹脂10の表面上に第3の配線となる導電体121を設ける。具体的には、導電体として、厚さが約5~12μm程度のCu箔121を封止樹脂10の表面上に設ける。本実施形態においては、第8および第9の各実施形態においては、第8および第9の各実施形態で用いたCu箔121は、対しも箱形状に形成される必要はない。それとともに、Cu箔121は、封止部材導入口92や通気口93を備える必要もない。ただし、本実施形態においては、第8および第9の各実施形態においては、第8および第9の各実施形態においては、第8および第9の各実施形態で用いたCu箔121は、対止部材導入口92や通気口93を備える必要もない。ただし、本実施形態においては、第8および第9の各実施形態で用いたCu箔91と同じ形状からなるCu箔121を使用することとする。このように、半導体装置の構成部分で共通化や製造工程の簡略化を図ることができる。ひいては、半導体装置の製造コストを削減することができる。

# [0209]

また、図示は省略するが、Cu箔121の封止樹脂10に接着される側の面上には、厚さが約8~50µm程度の接着材が塗工されている。この接着材には、例えばエポキシ系やイミド系の接着材が用いられる。このような接着材付きのCu箔121を、例えば熱間ラミネート法や真空プレス法により、封止樹脂10の表面(モールド封止面)上に貼り付

20

30

40

ける。これまでの工程により、半導体チップ1、フレキシブル基材 2 、封止樹脂 1 0 、および C u 箔 1 2 1 等からなる樹脂封止パッケージ(モールド封止パッケージ) 1 2 2 が作成される。この樹脂封止パッケージ 1 2 2 は、本実施形態の半導体装置 1 2 5 の主要な構成部分となる。

## [0210]

次に、図22(c)に示すように、第8実施形態と同様の工程により、樹脂封止パッケージ122の各第1の配線接続部(縦接続部)16に、複数個のスルーホール12を形成する。続けて、各スルーホール12内に、縦接続配線としてのスループラグ(第4の配線)100を1本ずつ設ける。それとともに、各スループラグが設けられた樹脂封止パッケージ122に、下部配線(基板実装用配線)としての第2の配線6や、上部配線(パッケージ搭載用配線、部品搭載用端子)としての第3の配線123等を、それぞれ複数本ずつ形成する。各第3の配線123は、Cu箔121をエッチング工程等により所定のパターンに加工することにより形成される。この後、第8実施形態と同様に、各第2の配線6および各第3の配線123等に、必要に応じて所定の表面処理を施す。それとともに、樹脂封止パッケージ122の基板実装面122b上に、複数個の半田ボール101を各第2の配線6に接触(接合)させて搭載する。

### [0211]

続けて、これまでの工程により一括して作製された樹脂封止パッケージ122の集合体を、ダイシング等によりテープ状態から個々のパッケージごとに切断して個片化する。この後、各樹脂封止パッケージ122ごとに各種テストを実施する。そして、これらのテストに合格した樹脂封止パッケージ122を良品とする。これにより、図22(c)に示す樹脂封止パッケージ122を主要な構成部分とする、本実施形態に係る所望の半導体装置125を得る。すなわち、複数本の第3の配線123となるCu箔121と封止樹脂10とが別体に、かつ、別工程で設けられた樹脂封止パッケージ122からなる半導体装置125を得る。

## [0212]

この後、半導体装置125のパッケージ搭載面122a上には、必要に応じて図示しない受動部品等の所定の外部装置が搭載される。それとともに、半導体装置125の基板実装面122b上には、必要に応じて図示しない実装基板が実装される。あるいは、半導体装置125を必要に応じて複数個積層して、マルチチップパッケージとして用いる。

### [0213]

#### [0214]

なお、本発明に係る半導体装置およびその製造方法は、前述した第1~第10の各実施 形態には制約されない。本発明の趣旨を逸脱しない範囲で、それらの構成、あるいは製造 工程などの一部を種々様々な設定に変更したり、あるいは各種設定を適宜、適当に組み合 わせて用いたりして実施することができる。

## [0215]

50

40

20

例えば、第1および第4の各実施形態においては、各チップ搭載基材2,41を、それぞれテープ状としたが、これに限定されるものではない。各チップ搭載基材2,41は、フィルム状や板状に形成されても構わない。

### [0216]

また、半導体チップ1は、1種類の機能に限定されない。半導体チップ1としては、CPU、メモリ、DSP、画像処理エンジン等、様々な機能の半導体チップを用いることができる。

# [0217]

また、第2実施形態においては、第1実施形態の半導体装置20を4個積層させて1個のマルチチップパッケージ21を作製した。同様に、第6実施形態においては、第5実施形態の半導体装置64を4個積層させて1個のマルチチップパッケージは、同一の半導体装置20、64等を複数個積層して作製されるとは限らない。例えば、第1実施形態の半導体装置20、64等を複数個積層半導体装置34、第4実施形態の半導体装置52、第5実施形態の半導体装置64、およびずりまた。の半導体装置83,85を混在させて積層することにより、1個のマルチチップパッケージを作製しても構わない。チップ積層型のマルチチップパッケージを作製する場合、各半導体装置20,34,52,64,83,85を所望の構成に応じて適宜、適正な個数ずつ、適正な位置に配置して用いればよい。また、各半導体装置20,34,52,64,83,85(各半導体チップ1)同士の電気的な接続、すなわち、第1~第4の各配線5,6,13,15,43,47,48も、所望の構成に応じて適宜、適正なパターンおよび本数に設定されればよい。

#### [ 0 2 1 8 ]

また、第4実施形態においては、フレキシブル基材41のチップ搭載面41a上に封止樹脂10を設けた後、第3の配線47と第4の配線48とを一体に、かつ、一括して設けたが、これに限定されるものではない。例えば、第8実施形態と同様の工程により、半導体装置52を作製しても構わない。すなわち、先ず、フレキシブル基材41のチップ搭載面41a上に封止樹脂10と第3の配線47となるCu箔とを一体に、かつ、一括して設ける。この後、少なくともCu箔およびこのCu箔が設けられた封止部材10をその厚さ方向に沿って一括して貫通させて、第4の配線としての非貫通ヴィアプラグ48を設ける。このように、フレキシブル基材41のチップ搭載面41a上に封止樹脂10と第3の配線47となるCu箔とを一体に、かつ、一括して設けた後、非貫通ヴィアプラグ48を第3の配線47とは別体に、かつ、別工程により設けても構わない。

#### [ 0 2 1 9 ]

あるいは、第10実施形態と同様の工程により、半導体装置52を作製しても構わない。すなわち、先ず、フレキシブル基材41のチップ搭載面41a上に封止樹脂10を設ける。この後、第3の配線47を、封止樹脂10とは別体に、かつ、別工程により封止樹脂10の表面上に設ける。続けて、少なくとも第3の配線47および第3の配線47が設けられた封止部材10をその厚さ方向に沿って一括して貫通させて、第4の配線としての非貫通ヴィアプラグ48を設ける。このように、フレキシブル基材41のチップ搭載面41a上に封止樹脂10を設けた後、第3の配線47と非貫通ヴィアプラグ48とを別体に、かつ、別工程により設けても構わない。

#### [0220]

また、第7実施形態の半導体装置83,85においては、複数個の半導体チップ1を全てワイヤボンディング法によりチップ搭載基材2,41に搭載したが、これに限定されるものではない。例えば、各半導体チップ1のうち、チップ搭載基材2,41に直接接触する最下層の半導体チップ1は、フリップチップ接続法によりチップ搭載基材2,41に搭載されても構わない。さらに、半導体装置83,85においては、CPU、メモリ、DSP、画像処理エンジン等、様々な機能の半導体チップ1を積層してチップ搭載基材2,41に混載することができるのはもちろんである。

## [0221]

50

20

30

10

20

30

40

50

また、第8実施形態においては、第4の配線100を設けるための凹部をスルーホール12として形成したが、これに限定されるものではない。例えば、チップ搭載基材として片面銅貼テープであるチップ搭載基材41を用いるとともに、第4の配線90を設けるための凹部を、第4実施形態のように、非貫通ヴィアホールとして形成しても構わない。この場合、各非貫通ヴィアホールの径の大きさを、樹脂封止パッケージ98の厚さとの比が約1:1以上となる大きさに設定することが好ましい。これは、チップ搭載基材2,41の代わりにリードフレーム112を用いる第9の実施形態の半導体装置119においても同様である。少なくとも、第2の配線116とリードフレーム112との電気的な接続が確保できればよい。

[0222]

また、第8および第9の各実施形態においては、Cu箔91の形状を図18(a),(b)に示すような四角い箱形状としたが、これに限定されるものではない。Cu箔91の形状は、モールド金型のキャビティ部の形状や、所望する樹脂封止パッケージ(半導体は、封止部材導入口92および通気口93の大きさ、形状、形成箇所、および個数などに応じて適宜、適正な形状に形成して構わない。とはおいても同様である。Cu箔91と封止樹脂10とを、トランスファモールディングではおいて一体に、かつ、一括して設ける場合、封止部材導入口92および通気口93の大きさ、形状、形成箇所、および個数などは、トランスファモールが得られるように適宜、適正な状態に設定されればよい。すなわち、封止部材導入口92および通気口93の大きさ、形状、形成箇所、および個数などは、トランスファモールが近近通気口93の大きさ、形状、形成箇所、および個数などは、トランスファモールが近近通気口93の大きさ、形状、形成箇所、および個数などは、トランスファモールがが正程においてCu箔91の表面(上面)が封止樹脂10から露出することなく、Cu箔91とチップ搭載基材2との間に封止樹脂10が適正に充填される状態に設定されればよい。

[0223]

また、第9実施形態においては、半導体チップ1をチップマウントアイランド111(リードフレーム112)の一方の主面上に1個だけ搭載したが、これに限定されるものではない。第7実施形態と同様に、チップマウントアイランド111の一方の主面上に、複数個の半導体チップ1を積層させて搭載しても構わない。あるいは、チップマウントアイランド111の上下両方の主面上に、半導体チップ1を1個ずつ対向させて搭載しても構わない。さらには、チップマウントアイランド111の上下両方の主面上に、半導体チップ1を複数個ずつ積層かつ対向させて搭載しても構わない。

[0224]

また、第9実施形態においては、第2の配線116および第3の配線117となる2枚のCu箔91と封止樹脂10とを一体に、かつ、一括して設けた後、第4の配線117となるしてのスループラグ108を設けたが、これに限定されるものではない。例えば、第1度により、半導体装置119を作製しても構わない。すなわち、先ず、半導体チップ1および半導体チップ12を作製してのリードフレーム112との接続が封に沿って封止樹脂10を設ける。この後、例えばめっき法により、封止樹脂10を設ける。この後、例えばめっき法により、封止樹脂10のおよび上でで、第2の配線116となるCu箔91のとも、一方のCu箔91に対ける。続けて、この方のCu箔91に対ける。に対して対止樹脂10の表面上に他方のCu箔91を設ける。このように、半10の反対側の表面上に他方のCu箔91を設ける。このでは対してップ1カよび半導体チップ1とひるCu箔91および第3の配線117となるCu箔91および第3の配線1118とを一体に、かつ、一括して設けても構わない。

[0225]

あるいは、第10実施形態と同様の工程により、半導体装置119を作製しても構わない。すなわち、先ず、半導体チップ1および半導体チップ1と第1の配線としてのリード

フレーム112との接続部を覆って封止樹脂10を設ける。この後、第2の配線116となるCu箔91および第3の配線117となるCu箔91の少なくとも一方を、封止樹脂10とは別体に、かつ、別工程により封止樹脂10の表面上に設ける。続けて、封止樹脂10、封止樹脂10に覆われたリードフレーム112、ならびに第2の配線116となるCu箔91および第3の配線117となるCu箔91の少なくとも一方を半導体チップ1の厚さ方向に沿って一括して貫通させてスループラグ118を設ける。続けて、一方のCu箔91に対向させて、封止樹脂10の反対側の表面上に他方のCu箔91を設ける。このように、半導体チップ1および半導体チップ1とリードフレーム112との接続部を覆って封止樹脂10を設けた後、第2の配線116となるCu箔91および第3の配線107となるCu箔91の少なくとも一方とスループラグ118とを別体に、かつ、別工程により設けても構わない。

[ 0 2 2 6 ]

さらに、第1および第3~第5の各実施形態においては、第4の配線15,48を第3の配線13,47と併行して設けた。また、第8~第10の各実施形態においては、第4の配線100,118を設けるのに先立って、第3の配線99,117,123を設けた。しかし、第4の配線15,48,100,118を設ける順番は、必ずしも前述した順番には限られない。例えば、第1、第3~第5、第8、および第10の各実施形態において、封止樹脂10内に第4の配線15,48,100を設けた後、封止樹脂10の表面上に第3の配線13,47,99,123を設けても構わない。あるいは、第9実施形態において、封止樹脂10内に第4の配線118を設けた後、封止樹脂10の表面上に第2の配線116および第3の配線117の少なくとも一方を設けても構わない。

【図面の簡単な説明】

[0227]

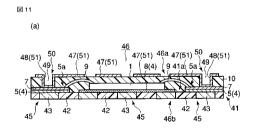

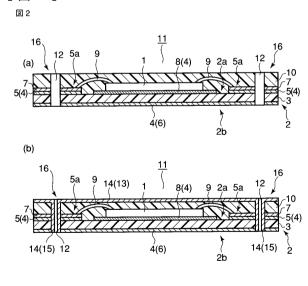

- 【図1】第1実施形態に係る半導体装置の製造方法を示す工程断面図。

- 【図2】第1実施形態に係る半導体装置の製造方法を示す工程断面図。

- 【図3】第1実施形態に係る半導体装置の製造方法を示す工程断面図。

- 【図4】第2実施形態に係る半導体装置の製造方法を示す工程断面図。

- 【図5】第2実施形態に係る半導体装置の製造方法を示す工程断面図。

- 【図6】第3実施形態に係る半導体装置の製造方法を示す工程断面図。

- 【図7】第3実施形態に係る半導体装置の製造方法を示す工程断面図。

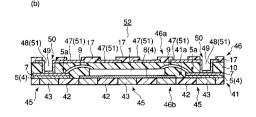

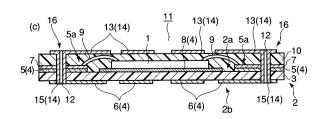

- 【図8】第4実施形態に係る半導体装置の製造方法を示す工程断面図。

- 【図9】第4実施形態に係る半導体装置の製造方法を示す工程断面図。

- 【図10】第4実施形態に係る半導体装置の製造方法を示す工程断面図。

- 【网 1 1 】 第 1 字旋形能压成了坐道体壮罕の制进于计专二士工程账面网

- 【図11】第4実施形態に係る半導体装置の製造方法を示す工程断面図。

- 【図12】第5実施形態に係る半導体装置の製造方法を示す工程断面図。 【図13】第5実施形態に係る半導体装置の製造方法を示す工程断面図。

- 【図14】第5実施形態に係る半導体装置の製造方法を示す工程断面図。

- 【図15】第6実施形態に係る半導体装置の製造方法を示す工程断面図。

- 【図16】第6実施形態に係る半導体装置の製造方法を示す工程断面図。

- 【図17】第7実施形態に係る半導体装置を示す断面図。

【図18】第8実施形態に係る半導体装置が備える第3の配線となる導電体を示す斜視図および平面図。

- 【図19】第8実施形態に係る半導体装置の製造方法を示す工程断面図。

- 【図20】第8実施形態に係る半導体装置の製造方法を示す工程断面図。

- 【図21】第9実施形態に係る半導体装置の製造方法を示す工程断面図。

- 【図22】第10実施形態に係る半導体装置の製造方法を示す工程断面図。

- 【図23】第1~第7の各実施形態に係る半導体装置に対する比較例としての背景技術に係る半導体装置を示す断面図。

- 【図24】第1~第7の各実施形態に係る半導体装置に対する比較例としての背景技術に係る他の半導体装置を示す断面図。

20

30

-

40

【図25】第8および第9の各実施形態に係る半導体装置に対する比較例としての背景技術に係る半導体装置を一部破断して示す斜視図。

【図26】第8および第9の各実施形態に係る半導体装置に対する比較例としての背景技術に係る他の半導体装置を示す断面図。

【図27】第8および第9の各実施形態に係る半導体装置に対する比較例としての背景技術に係るさらに他の半導体装置を一部破断して示す斜視図。

#### 【符号の説明】

## [0228]

1 … 半導体チップ(半導体素子)、2 … フレキシブル基材(両面銅貼テープ、チップ搭載基材)、2 a … チップ搭載面(チップ搭載基材の一方の主面)、2 b … チップ非搭載面(チップ搭載基材の一方の主面)、2 b … チップ非搭載面(チップ搭載基材の一方の主面)、3 … 基材本体、4 … C u 箔(第 1 の配線、第 2 の配線)、5 … チップ接続配線(第 1 の配線)、5 a ,1 1 2 a … パッド接続部(半導体素子と第 1 の配線との接続部)、6 ,4 3 ,1 1 6 … 基板実装用配線(基板実装用端子、第 1 の配線、第 1 の配線、上部端子、第 3 の配線)、 1 3 ,4 7 ,9 9 ,1 1 7 ,1 2 3 … パッケージ搭載用配線(パッケージ搭載用端子、部品搭載用配線、上部端子、第 3 の配線)、1 4 ,5 1 … C u めっき膜(第 3 の配線、第 4 の配線)、1 5 ,1 0 0 ,1 1 8 … スループラグ(第 4 の配線)、2 0 ,2 1 ,3 4 ,5 2 ,6 4 ,7 1 ,8 3 ,8 5 ,1 0 2 ,1 1 9 ,1 2 5 … 半導体装置、4 1 … フレキシブル基材(片面銅貼テープ、チップ搭載基材)、4 1 a … チップ搭載基材の一方の主面)、4 1 b … チップ搭載面(チップ搭載基材の一方の主面)、4 1 b … チップ搭載面(チップ搭載基材の一方の主面)、5 1 1 2 … リードフレーム(チップ接続配線、第 1 の配線)、1 1 2 … リードフレーム(チップ接続配線、第 1 の配線)

## 【図1】

# 図 1 4(5,8) (a) 4(6) (b) 5(4) 5(4) 8(4) **4**(5) (c) 2b 7 5(4) 5(4) (d) 4(5) Źb 8(4) 5(4) 4(6) źb (e) 5(4) 5(4) 4(6) ŹЬ

## 【図2】

10

15(14) 6(4) 17 17

6(4) 17

【図10】

# 【図11】

図 11

(a)

# 【図12】

図 12

(b)

(c) 61 (

# 【図13】

# 【図14】

【図 1 5】 図 15

【図 1 6】 -

図 16

【図17】

図 17

(a)

【図18】

【図19】 図19

【図20 0】 図20

【図21】 図21

【図22】

# 【図23】

(a)

図 23

# 【図24】

図 24

# 【図27】

図 27

# 【図25】

図 25

# 【図26】

# フロントページの続き

(74)代理人 100084618

弁理士 村松 貞男

(74)代理人 100092196

弁理士 橋本 良郎

(72)発明者 井本 孝志

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝マイクロエレクトロニクスセンター内

(72)発明者 田窪 知章

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝マイクロエレクトロニクスセンター内