(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2008-97804

(P2008-97804A)

(43) 公開日 平成20年4月24日(2008.4.24)

| (51) Int.Cl.             | F 1          | テーマコード (参考)       |

|--------------------------|--------------|-------------------|

| G 11 C 29/06 (2006.01)   | G 11 C 29/00 | 6 7 1 F 2 G 1 3 2 |

| G 11 C 29/12 (2006.01)   | G 11 C 29/00 | 6 7 1 Z 5 L 1 0 6 |

| G 11 C 11/4074 (2006.01) | G 11 C 11/34 | 3 5 4 F 5 M 0 2 4 |

| G 11 C 11/401 (2006.01)  | G 11 C 11/34 | 3 7 1 A           |

| GO 1 R 31/28 (2006.01)   | GO 1 R 31/28 | B                 |

審査請求 未請求 請求項の数 24 O L (全 21 頁) 最終頁に続く

|              |                              |          |                                                                                   |

|--------------|------------------------------|----------|-----------------------------------------------------------------------------------|

| (21) 出願番号    | 特願2007-214164 (P2007-214164) | (71) 出願人 | 591024111<br>株式会社ハイニックスセミコンダクター<br>H Y N I X S E M I C O N D U C T O R<br>I N C . |

| (22) 出願日     | 平成19年8月20日 (2007. 8. 20)     |          |                                                                                   |

| (31) 優先権主張番号 | 10-2006-0099652              |          |                                                                                   |

| (32) 優先日     | 平成18年10月13日 (2006. 10. 13)   |          |                                                                                   |

| (33) 優先権主張国  | 韓国 (KR)                      |          |                                                                                   |

|              |                              | (74) 代理人 | 100117514<br>弁理士 佐々木 敦朗                                                           |

|              |                              | (72) 発明者 | 崔 俊 基<br>大韓民国京畿道利川市夫鉢邑牙美里山13<br>6-1                                               |

最終頁に続く

(54) 【発明の名称】電圧制御装置および電圧制御方法

## (57) 【要約】

【課題】 半導体集積回路に関し、製造上の脆弱なセルおよび周辺ロジックにストレスを加えるテストの際に、ピーク電流の集中を防止できる電圧制御装置を提供する。

【解決手段】 オールバンクプリチャージ命令に応答してバーンイン制御信号およびバーンインプリチャージ信号を出力する信号生成手段と、前記バーンイン制御信号と前記バーンインプリチャージ信号に応答して、第1電圧又は前記第1電圧より低い第2電圧のうちいずれか1つをワード線に供給する電圧制御手段とを含む。

【選択図】 図4

**【特許請求の範囲】****【請求項 1】**

オールバンクプリチャージ命令に応答してバーンイン制御信号およびバーンインプリチャージ信号を出力する信号生成ユニットと、

前記バーンイン制御信号と前記バーンインプリチャージ信号に応答して、第1電圧又は前記第1電圧より低い第2電圧のうちいずれか1つをワード線に供給する電圧制御ユニットと

を含むことを特徴とする電圧制御装置。

**【請求項 2】**

前記電圧制御ユニットには、第1プリチャージ信号およびアクティブ信号がさらに入力されることを特徴とする請求項1に記載の電圧制御装置。 10

**【請求項 3】**

前記信号生成ユニットは、

バーンインテストモード信号および制御信号に応答して、前記バーンイン制御信号を出力する第1信号生成部と、

第2プリチャージ信号および前記アクティブ信号に応答して、前記バーンインプリチャージ信号を出力する第2信号生成部と

を含むことを特徴とする請求項2に記載の電圧制御装置。

**【請求項 4】**

前記第1信号生成部は、前記バーンインテストモード信号および前記制御信号が入力されて、前記バーンインテストモード信号および前記制御信号がいずれもハイレベルである時、イネーブルになるように設計されていることを特徴とする請求項3に記載の電圧制御装置。 20

**【請求項 5】**

前記第2信号生成部は、

前記アクティブ信号を反転する第1インバータと、

前記第2プリチャージ信号および前記第1インバータの出力信号が入力されて NANDゲートと、

前記 NANDゲートの出力信号 入力されて 前記バーンインプリチャージ信号を生成する 第2インバータと 30

を含むことを特徴とする請求項3に記載の電圧制御装置。

**【請求項 6】**

前記電圧制御ユニットは、

前記アクティブ信号、前記第1プリチャージ信号、前記バーンインプリチャージ信号および前記バーンイン制御信号に応答して、電圧制御信号を出力する制御信号生成部と、

前記電圧制御信号に応答して、前記第1電圧又は前記第2電圧のうちいずれか1つを前記ワード線に供給する電圧供給制御部と

を含むことを特徴とする請求項2に記載の電圧制御装置。

**【請求項 7】**

前記制御信号生成部は、

前記アクティブ信号が入力されて、前記アクティブ信号を遅延させたアクティブディレイ信号を生成し、前記アクティブディレイ信号に応答して、アクティブディレイパルス信号を生成する第1制御信号生成部と、

前記第1プリチャージ信号、前記バーンインプリチャージ信号、前記バーンイン制御信号、前記アクティブディレイ信号および前記アクティブディレイパルス信号に応答して、前記電圧制御信号を生成する第2制御信号生成部と

を含むことを特徴とする請求項6に記載の電圧制御装置。 40

**【請求項 8】**

前記第1制御信号生成部は、

前記アクティブ信号を第1時間ほど遅延させ、前記アクティブディレイ信号を生成する

50

20

30

40

50

信号遅延部と、

前記アクティブディレイ信号に応答して、パルス信号の前記アクティブディレイパルス信号を生成するパルス発生部と

を含むことを特徴とする請求項 7 に記載の電圧制御装置。

**【請求項 9】**

前記第 2 制御信号生成部は、

前記第 1 プリチャージ信号、前記バーンイン制御信号、前記アクティブディレイ信号および前記アクティブディレイパルス信号に応答して、第 1 ノードの電位を変化させる第 1 信号入力部と、

前記第 1 ノードの電位をラッチする第 1 ラッチ部と、

前記バーンインプリチャージ信号、前記バーンイン制御信号および前記アクティブディレイ信号に応答して、第 2 ノードの電位を変化させる第 2 信号入力部と、

前記第 2 ノードの電位をラッチする第 2 ラッチ部と、

前記アクティブディレイ信号に応答して、前記第 1 ラッチ部および前記第 2 ラッチ部の出力信号のうちいずれか 1 つを駆動させ、前記電圧制御信号として出力する信号駆動部とを含むことを特徴とする請求項 7 に記載の電圧制御装置。

**【請求項 10】**

前記電圧供給制御部は、前記電圧制御信号に応答して、前記第 1 電圧および前記第 2 電圧をショートさせるスイッチング素子を含むことを特徴とする請求項 6 に記載の電圧制御装置。

10

20

**【請求項 11】**

前記バーンインテストモード信号はバーンインテストモード時に活性化される信号であり、前記制御信号は前記オールバンクプリチャージ命令に応答して活性化される信号であることを特徴とする請求項 3 に記載の電圧制御装置。

**【請求項 12】**

前記第 1 プリチャージ信号は複数のバンクのうちの一部をプリチャージする信号であり、前記第 2 プリチャージ信号は複数の前記バンクのすべてをプリチャージする信号であることを特徴とする請求項 11 に記載の電圧制御装置。

**【請求項 13】**

オールバンクプリチャージ命令に応答して、電圧制御信号を活性化させて出力する制御信号生成ユニットと、

アクティブ動作時に、前記電圧制御信号に応答して、ワード線に第 2 電圧を印加した後前記第 1 電圧が印加されるようにし、プリチャージ動作時に、前記ワード線に予め第 2 電圧が印加されるようにする電圧供給制御ユニットと

を含むことを特徴とする電圧制御装置。

30

**【請求項 14】**

前記制御信号生成ユニットは、バーンイン制御信号、バーンインプリチャージ信号、アクティブ信号および第 1 プリチャージ信号に応答して、前記電圧制御信号を生成することを特徴とする請求項 13 に記載の電圧制御装置。

40

**【請求項 15】**

前記オールバンクプリチャージ命令に応答してバーンイン制御信号およびバーンインプリチャージ信号を出力する信号生成ユニットをさらに含むことを特徴とする請求項 13 に記載の電圧制御装置。

**【請求項 16】**

前記信号生成ユニットは、

バーンインテストモード信号および制御信号に応答して、前記バーンイン制御信号を出力する第 1 信号生成部と、

第 2 プリチャージ信号および前記アクティブ信号に応答して、前記バーンインプリチャージ信号を出力する第 2 信号生成部と

を含むことを特徴とする請求項 15 に記載の電圧制御装置。

50

**【請求項 17】**

前記第1信号生成部は、前記バーンインテストモード信号および前記制御信号がいずれもハイレベルである時、イネーブルになることを特徴とする請求項16に記載の電圧制御装置。

**【請求項 18】**

前記制御信号生成部は、

前記アクティブ信号が入力されて、前記アクティブ信号を遅延させたアクティブディレイ信号を生成し、前記アクティブディレイ信号に応答して、アクティブディレイパルス信号を生成する第1制御信号生成部と、

前記第1プリチャージ信号、前記バーンインプリチャージ信号、前記バーンイン制御信号、前記アクティブディレイ信号および前記アクティブディレイパルス信号に応答して、前記電圧制御信号を生成する第2制御信号生成部と

を含むことを特徴とする請求項13に記載の電圧制御装置。

**【請求項 19】**

前記第2制御信号生成部は、

前記第1プリチャージ信号、前記バーンイン制御信号、前記アクティブディレイ信号および前記アクティブディレイパルス信号に応答して、第1ノードの電位を変化させる第1信号入力部と、

前記第1ノードの電位をラッチする第1ラッチ部と、

前記バーンインプリチャージ信号、前記バーンイン制御信号および前記アクティブディレイ信号に応答して、第2ノードの電位を変化させる第2信号入力部と、

前記第2ノードの電位をラッチする第2ラッチ部と、

前記アクティブディレイ信号に応答して、前記第1ラッチ部および前記第2ラッチ部の出力信号のうちいずれか1つを駆動させ、前記電圧制御信号として出力する信号駆動部とを含むことを特徴とする請求項18に記載の電圧制御装置。

**【請求項 20】**

前記電圧供給制御ユニットは、前記電圧制御信号に応答して、前記第1電圧および前記第2電圧をショートさせるスイッチング素子を含むことを特徴とする請求項13に記載の電圧制御装置。

**【請求項 21】**

バーンインテストモード時にテストモード信号を活性化させるステップと、

オールバンクプリチャージ命令に応答して、バーンイン制御信号およびバーンインプリチャージ信号を活性化させ、電圧制御信号を活性化させるステップと、

アクティブ動作時、前記電圧制御信号に応答して、ワード線に第2電圧を印加してから第1電圧を印加するステップと、

プリチャージ動作時、前記ワード線が非活性化される前に前記電圧制御信号に応答して、前記ワード線に前記第2電圧を印加するステップと

を含むことを特徴とする電圧制御方法。

**【請求項 22】**

前記電圧制御信号を生成するステップは、

制御信号および前記バーンインテストモード信号に応答して、前記バーンイン制御信号を出力するステップと、

第1プリチャージ信号およびアクティブ信号に応答して、前記バーンインプリチャージ信号を出力するステップと

を含むことを特徴とする請求項21記載の電圧制御方法。

**【請求項 23】**

前記アクティブ動作時ワード線に電圧を印加するステップは、

前記アクティブ信号を遅延させ、アクティブディレイ信号を出力するステップと、

前記アクティブディレイ信号に応答して、パルス信号のアクティブディレイパルス信号を出力するステップと

10

20

30

40

50

を含むことを特徴とする請求項 2 1 に記載の電圧制御方法。

**【請求項 2 4】**

前記プリチャージ動作時ワード線に電圧を印加するステップと、

プリチャージ命令が入力される前に前記オールバンクプリチャージ命令が入力されるステップと

を含むことを特徴とする請求項 2 1 に記載の電圧制御方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0 0 0 1】**

本発明は、半導体集積回路に関し、より詳しくは、製造上の脆弱なセルおよび周辺ロジックにストレスを加えるテストを行い、不良を事前に発見できるバーンインテストモードの電圧制御装置およびこれを用いた電圧制御装置および電圧制御方法に関するものである。

10

**【背景技術】**

**【0 0 0 2】**

一般的に D R A M のような半導体集積回路は、パッケージする前に製品の不良を早期発見するため、動作電圧より高い電圧および高温でストレスを印加するバーンインテスト工程を行う（例えば、特許文献 1）。このようなバーンインテスト工程によって、脆弱なセルおよびロジック回路の脆弱な部分が判別される。

20

**【0 0 0 3】**

また、バーンインテスト工程は、高い電位で格納されたセルのストレージキャパシタの誘電膜に正常状態以上のストレスを与えて、脆弱なセルをスクリーンでき、セルトランジスタのゲート酸化物にストレスを印加して、ゲート酸化物の降伏電圧（breakdown voltage）を測定することもできる。

20

**【0 0 0 4】**

このようなバーンイン動作をするために、D R A M はアクティブ - ライト - プリチャージの動作パターンを有しなければならない。前記 D R A M の動作は、ロードアドレス（X - Address）とカラムアドレス（Y - Address）とのスキヤン方式によってローファースト（X - Fast）動作とカラムファースト（Y - Fast）動作に分けられるようになる。

30

**【0 0 0 5】**

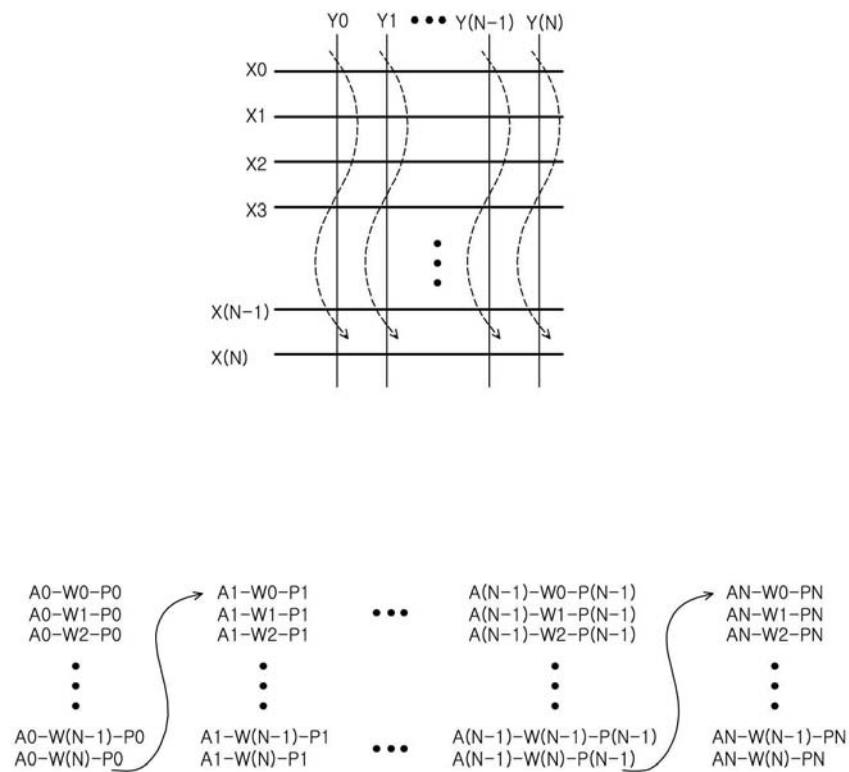

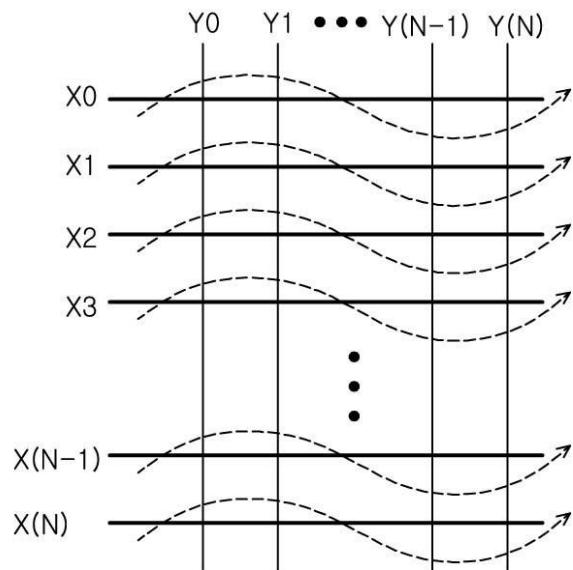

図 1 は、ローファースト（X - Fast）動作に伴うアドレス進行方向およびアドレスパターンを示す概念図であり、図 2 は、カラムファースト（Y - Fast）動作に伴うアドレス進行方向およびアドレスパターンを示す概念図である。

**【0 0 0 6】**

図 1 および図 2 に示す、A 0 ~ A (N) はアクティブ命令、W 0 ~ W (N) はライト命令、P 0 ~ P (N) はプリチャージ命令である。

40

図 1 と図 2 を比較すれば、ローファースト（X - Fast）動作の場合、アクティブプリチャージ回数がカラムファースト（Y - Fast）動作に比べて N 倍多い。これは、アクティブ又はプリチャージ時にピーク電流が多いことを意味する。

**【0 0 0 7】**

すなわち、カラムファースト（Y - Fast）動作の場合、アクティブプリチャージ方式はロードアドレスをアクティブした後にカラムの数だけライトしてプリチャージ動作をするため、ワード線 W L 動作に伴うピーク電流がローファースト（X - Fast）動作に比べて 1 / N に減少するようになる。

**【0 0 0 8】**

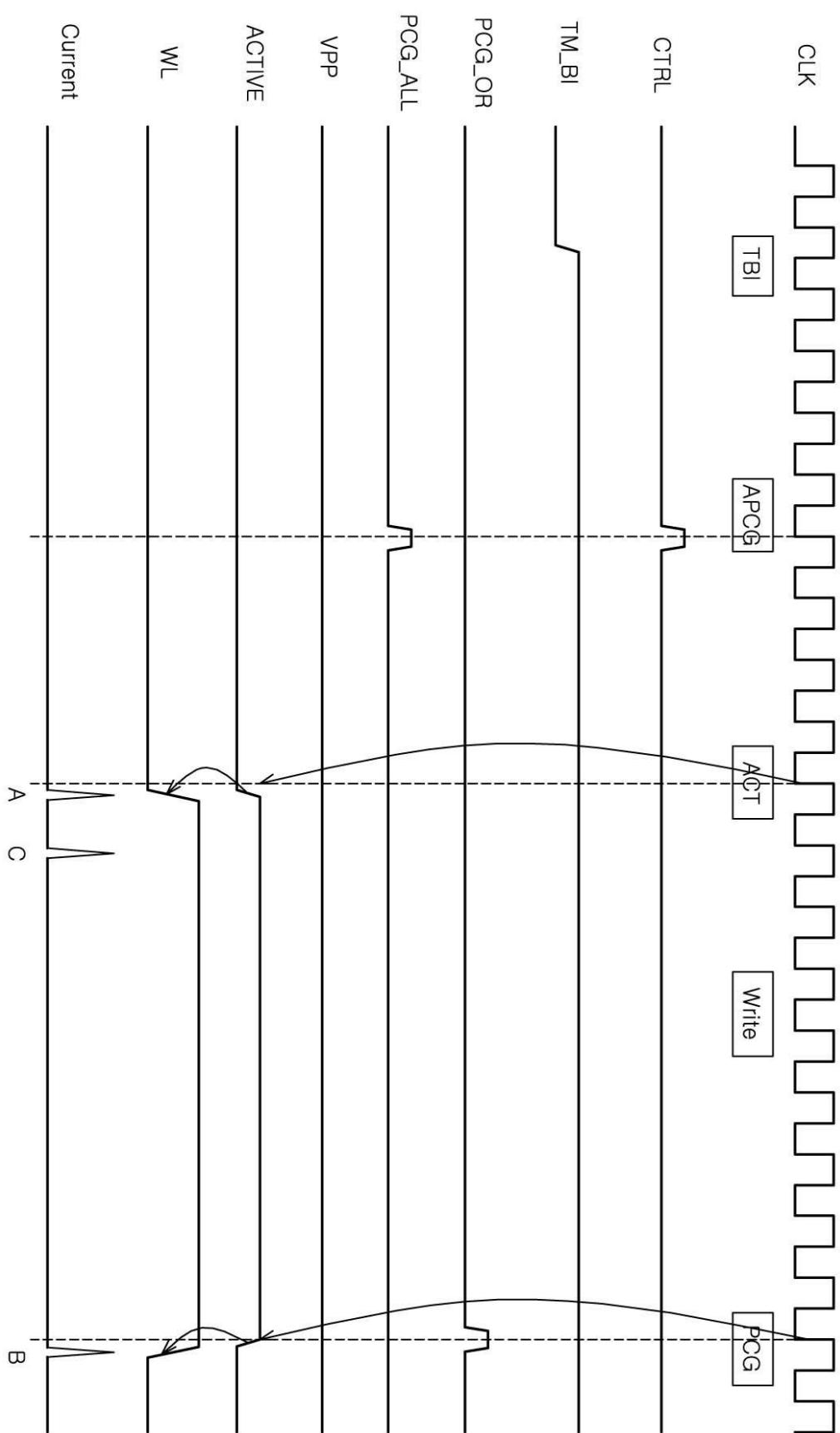

図 3 は、従来の電圧制御装置がローファースト（X - Fast）動作をする場合にアクティブプリチャージ方式を示すタイミング図である。

50

図 3 に示すように、従来の電圧制御装置は、アクティブ命令 A C T が入力されれば内部的にアクティブ信号 A C T I V E が発生するようになり、この信号に応じてワード線 W L

を高電圧 VPP レベルまで上昇させるようになる。この時、接地電圧 VSS でディスチャージされているワード線 WL を高電圧 VPP レベルまでチャージしなければならないため、瞬間的に多くの電流を消耗するようになる。

#### 【0009】

図 3 に示す、A はアクティブ動作時ワード線 WL が動作するのに伴う瞬間的なピーク電流を示し、B はプリチャージ動作時発生するピーク電流を示すものである。C はセンスアンプが動作するのに伴うピーク電流を示す。

#### 【0010】

ところで、DRAM の容量が大きくなることによって動作電流が多くなり、特に、動作電圧より高い外部電圧 VDD で 48 ~ 72 時間の間アクティブプリチャージ動作を繰り返すバーンインテストの場合、ローファースト (X-Fast) 動作時にピーク電流が多く発生するようになる。このような多量のピーク電流は半導体メモリのパッケージ工程時に、外部信号端子の導電ボールを溶かす問題を誘発する。これによって、パッケージの良品率 (yield) を低下させてバーンインソケットを損傷させる。

10

#### 【0011】

従来の異なる方法で、カラムファースト (Y-Fast) 動作でアクティブプリチャージ方式を用いてピーク電流を減らす方法がある。しかし、カラムファースト (Y-Fast) 動作でバーンインテストを進行する場合、ペリトランジスタ (peripheral transistor) が容易に劣化し、正確にスクリーンすることが難しい。

20

#### 【特許文献 1】特開 2006-139901 号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0012】

したがって、本発明の目的は、ピーク電流の集中を防止できる電圧制御装置を提供することにある。

また、本発明の他の目的は、素子の劣化なくバーンインテスト工程を行うようにする電圧制御方法を提供することにある。

#### 【課題を解決するための手段】

#### 【0013】

前記本発明の目的を達成するために、本発明の電圧制御装置は、オールバンクプリチャージ命令に応答してバーンイン制御信号およびバーンインプリチャージ信号を出力する信号生成ユニットと、前記バーンイン制御信号と前記バーンインプリチャージ信号に応答して、第 1 電圧又は前記第 1 電圧より低い第 2 電圧のうちいずれか 1 つをワード線に供給する電圧制御ユニットとを含む。

30

#### 【0014】

なお、上記発明において、電圧制御ユニットには、第 1 プリチャージ信号およびアクティブ信号がさらに入力されることが好ましい。

また、上記発明において、信号生成ユニットは、バーンインテストモード信号および制御信号に応答して、バーンイン制御信号を出力する第 1 信号生成部と、第 2 プリチャージ信号およびアクティブ信号に応答して、バーンインプリチャージ信号を出力する第 2 信号生成部とを含むことが好ましい。

40

#### 【0015】

上記発明において、第 1 信号生成部は、バーンインテストモード信号および制御信号が入力されて、バーンインテストモード信号および制御信号がいずれもハイレベルである時、イネーブルになるように設計されていることが好ましい。

#### 【0016】

上記発明において、第 2 信号生成部は、アクティブ信号を反転する第 1 インバータと、第 2 プリチャージ信号および第 1 インバータの出力信号が入力されて NAND ゲートと、NAND ゲートの出力信号入力されてバーンインプリチャージ信号を生成する第 2 インバータとを含むことが好ましい。

50

## 【0017】

上記発明において、電圧制御ユニットは、アクティブ信号、第1プリチャージ信号、バーンインプリチャージ信号およびバーンイン制御信号に応答して、電圧制御信号を出力する制御信号生成部と、電圧制御信号に応答して、第1電圧又は第2電圧のうちいずれか1つをワード線に供給する電圧供給制御部とを含むことが好ましい。

## 【0018】

上記発明において、制御信号生成部は、アクティブ信号が入力されて、アクティブ信号を遅延させたアクティブディレイ信号を生成し、アクティブディレイ信号に応答して、アクティブディレイパルス信号を生成する第1制御信号生成部と、第1プリチャージ信号、バーンインプリチャージ信号、バーンイン制御信号、アクティブディレイ信号およびアクティブディレイパルス信号に応答して、電圧制御信号を生成する第2制御信号生成部とを含むことが好ましい。10

## 【0019】

上記発明において、第1制御信号生成部は、アクティブ信号を第1時間ほど遅延させ、アクティブディレイ信号を生成する信号遅延部と、アクティブディレイ信号に応答して、パルス信号のアクティブディレイパルス信号を生成するパルス発生部とを含むことが好ましい。

## 【0020】

上記発明において、第2制御信号生成部は、第1プリチャージ信号、バーンイン制御信号、アクティブディレイ信号およびアクティブディレイパルス信号に応答して、第1ノードの電位を変化させる第1信号入力部と、第1ノードの電位をラッチする第1ラッチ部と、バーンインプリチャージ信号、バーンイン制御信号およびアクティブディレイ信号に応答して、第2ノードの電位を変化させる第2信号入力部と、第2ノードの電位をラッチする第2ラッチ部と、アクティブディレイ信号に応答して、第1ラッチ部および第2ラッチ部の出力信号のうちいずれか1つを駆動させ、電圧制御信号として出力する信号駆動部とを含むことが好ましい。20

## 【0021】

なお、上記発明において、電圧供給制御部は、電圧制御信号に応答して、第1電圧および第2電圧をショートさせるスイッチング素子を含むことが好ましい。

また、上記発明において、バーンインテストモード信号はバーンインテストモード時に活性化される信号であり、制御信号はオールバンクプリチャージ命令に応答して活性化される信号であることが好ましい。30

さらに、上記発明において、第1プリチャージ信号は複数のバンクのうちの一部をプリチャージする信号であり、第2プリチャージ信号は複数のバンクのすべてをプリチャージする信号であることが好ましい。

## 【0022】

また、本発明は、オールバンクプリチャージ命令に応答して、電圧制御信号を活性化させて出力する制御信号生成ユニットと、アクティブ動作時に、電圧制御信号に応答して、ワード線に第2電圧を印加した後第1電圧が印加されるようにし、プリチャージ動作時に、ワード線に予め第2電圧が印加されるようにする電圧供給制御ユニットとを含む。40

## 【0023】

なお、上記発明において、制御信号生成ユニットは、バーンイン制御信号、バーンインプリチャージ信号、アクティブ信号および第1プリチャージ信号に応答して、電圧制御信号を生成することが好ましい。

また、上記発明において、オールバンクプリチャージ命令に応答してバーンイン制御信号およびバーンインプリチャージ信号を出力する信号生成ユニットをさらに含むことが好ましい。

## 【0024】

上記発明において、信号生成ユニットは、バーンインテストモード信号および制御信号に応答して、バーンイン制御信号を出力する第1信号生成部と、第2プリチャージ信号お50

およびアクティブ信号に応答して、バーンインプリチャージ信号を出力する第2信号生成部とを含むことが好ましい。

上記発明において、第1信号生成部は、バーンインテストモード信号および制御信号がいずれもハイレベルである時、イネーブルになることが好ましい。

#### 【0025】

上記発明において、制御信号生成部は、アクティブ信号が入力されて、アクティブ信号を遅延させたアクティブディレイ信号を生成し、アクティブディレイ信号に応答して、アクティブディレイパルス信号を生成する第1制御信号生成部と、第1プリチャージ信号、バーンインプリチャージ信号、バーンイン制御信号、アクティブディレイ信号およびアクティブディレイパルス信号に応答して、電圧制御信号を生成する第2制御信号生成部とを含むことが好ましい。10

#### 【0026】

上記発明において、第2制御信号生成部は、第1プリチャージ信号、バーンイン制御信号、アクティブディレイ信号およびアクティブディレイパルス信号に応答して、第1ノードの電位を変化させる第1信号入力部と、第1ノードの電位をラッチする第1ラッチ部と、バーンインプリチャージ信号、バーンイン制御信号およびアクティブディレイ信号に応答して、第2ノードの電位を変化させる第2信号入力部と、第2ノードの電位をラッチする第2ラッチ部と、アクティブディレイ信号に応答して、第1ラッチ部および第2ラッチ部の出力信号のうちいずれか1つを駆動させ、電圧制御信号として出力する信号駆動部とを含むことが好ましい。20

なお、上記発明において、電圧供給制御ユニットは、電圧制御信号に応答して、第1電圧および第2電圧をショートさせるスイッチング素子を含むことが好ましい。

#### 【0027】

さらに、本発明は、バーンインテストモード時にテストモード信号を活性化させるステップと、オールバンクプリチャージ命令に応答して、バーンイン制御信号およびバーンインプリチャージ信号を活性化させ、電圧制御信号を活性化させるステップと、アクティブ動作時、電圧制御信号に応答して、ワード線に第2電圧を印加してから第1電圧を印加するステップと、プリチャージ動作時、ワード線が非活性化される前に電圧制御信号に応答して、ワード線に第2電圧を印加するステップとを含む。30

#### 【0028】

上記発明において、電圧制御信号を生成するステップは、制御信号およびバーンインテストモード信号に応答して、バーンイン制御信号を出力するステップと、第1プリチャージ信号およびアクティブ信号に応答して、バーンインプリチャージ信号を出力するステップとを含むことが好ましい。

#### 【0029】

上記発明において、アクティブ動作時ワード線に電圧を印加するステップは、アクティブ信号を遅延させ、アクティブディレイ信号を出力するステップと、アクティブディレイ信号に応答して、パルス信号のアクティブディレイパルス信号を出力するステップとを含むことが好ましい。

#### 【0030】

上記発明において、プリチャージ動作時ワード線に電圧を印加するステップと、プリチャージ命令が入力される前にオールバンクプリチャージ命令が入力されるステップとを含むことが好ましい。

#### 【発明の効果】

#### 【0031】

本発明に係る電圧制御装置は、アクティブ動作およびプリチャージ動作時に発生するピーク電流を分散させることによって過度なピーク電流によるパッケージボールメルティング(Package Ball Melting)を防止することができ、半導体メモリの生産性向上およびバーンインスクリーンの能力向上の効果を伴う。

#### 【発明を実施するための最良の形態】

10

20

30

40

50

## 【0032】

以下では、添付された図面を参照して、本発明の好ましい実施形態をより詳細に説明すれば次の通りである。

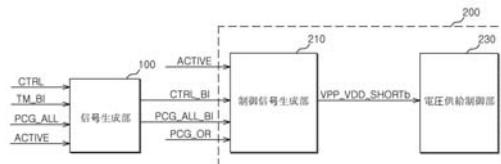

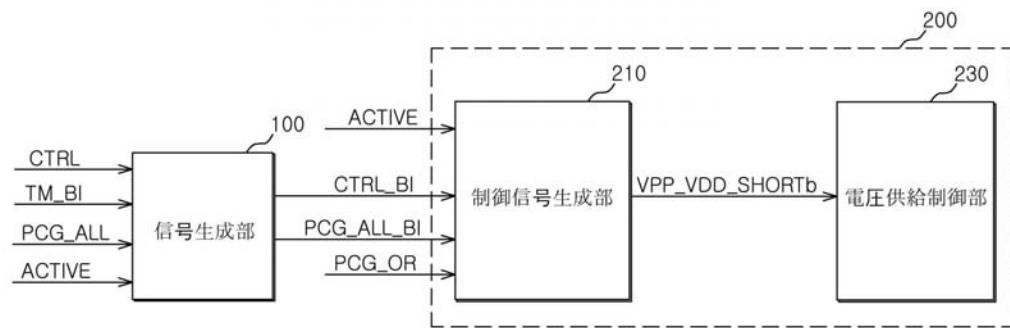

図4を参照すれば、本発明の実施形態に係る電圧制御装置は、信号生成部100および電圧制御部200を含む。

## 【0033】

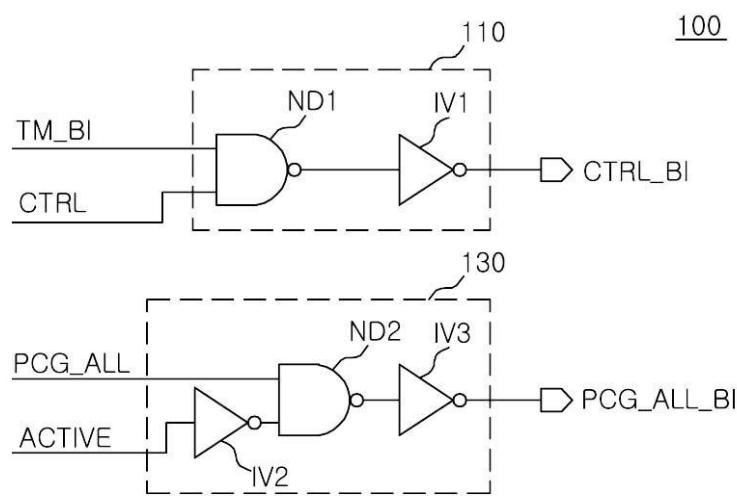

信号生成部100は、オールバンクプリチャージ命令(図示なし)に応答して、バーンイン制御信号CTR<sub>L</sub>\_B\_Iおよびバーンインプリチャージ信号PCG<sub>A</sub>LL\_B\_Iを生成する。このような信号生成部100は、第1信号生成部110、および第2信号生成部130を含む。

10

## 【0034】

第1信号生成部110は、前記バーンインテストモード信号TM\_B\_Iおよび前記制御信号CTR<sub>L</sub>に応答して、前記バーンイン制御信号CTR<sub>L</sub>\_B\_Iを生成する。前記第1信号生成部110は、前記バーンインテストモード信号TM\_B\_Iおよび前記制御信号CTR<sub>L</sub>が入力される第1 NANDゲートND<sub>1</sub>と、第1 NANDゲートND<sub>1</sub>の出力信号を反転してバーンイン制御信号CTR<sub>L</sub>\_B\_Iとして出力する第1インバータIV<sub>1</sub>とを含む。前記第1信号生成部110は、前記バーンインテストモード信号TM\_B\_Iおよび前記制御信号CTR<sub>L</sub>が入力されて、AND(A\_ND)演算を行う論理素子、すなわちANDゲートで構成されることもできる。前記バーンインテストモード信号TM\_B\_Iは、バーンインテストモード時に活性化される信号であり、前記制御信号CTR<sub>L</sub>はオールバンクプリチャージ命令が入力される場合に活性化される信号であり、特定のアドレスを利用して用いることができる。

20

## 【0035】

第2信号生成部130は、前記第2プリチャージ信号PCG<sub>A</sub>LLと前記アクティブ信号ACT<sub>I</sub>V<sub>E</sub>に応答して、前記バーンインプリチャージ信号PCG<sub>A</sub>LL\_B\_Iを出力する。前記第2信号生成部130は、前記アクティブ信号ACT<sub>I</sub>V<sub>E</sub>を反転させる第2インバータIV<sub>2</sub>と、前記第2プリチャージ信号PCG<sub>A</sub>LLおよび第2インバータIV<sub>2</sub>の出力信号が入力される第2 NANDゲートND<sub>2</sub>と、第2 NANDゲートND<sub>2</sub>の出力信号を反転して、バーンインプリチャージ信号PCG<sub>A</sub>LL\_B\_Iとして生成する第3インバータIV<sub>3</sub>とで構成することができる。

30

## 【0036】

一方、電圧制御部200は、前記バーンイン制御信号CTR<sub>L</sub>\_B\_Iおよび前記バーンインプリチャージ信号PCG<sub>A</sub>LL\_B\_Iに応答して、第1電圧V<sub>PP</sub>又は前記第1電圧V<sub>PP</sub>より低い第2電圧V<sub>DD</sub>のうちいずれか1つをワード線WLに供給する。このような前記電圧制御部200は、第1プリチャージ信号PCG<sub>O</sub>Rおよびアクティブ信号ACT<sub>I</sub>V<sub>E</sub>がさらに入力される。すなわち、前記電圧制御部200は、前記第1プリチャージ信号PCG<sub>O</sub>R、前記アクティブ信号ACT<sub>I</sub>V<sub>E</sub>、前記バーンイン制御信号CTR<sub>L</sub>\_B\_Iおよび前記バーンインプリチャージ信号PCG<sub>A</sub>LL\_B\_Iに応答して、第1電圧V<sub>PP</sub>又は第2電圧V<sub>DD</sub>を出力する。

40

このような電圧制御部200は、制御信号生成部210および電圧供給制御部230で構成することができる。

## 【0037】

制御信号生成部210は、前記アクティブ信号ACT<sub>I</sub>V<sub>E</sub>、前記第1プリチャージ信号PCG<sub>O</sub>R、前記バーンインプリチャージ信号PCG<sub>A</sub>LL\_B\_Iおよび前記バーンイン制御信号CTR<sub>L</sub>\_B\_Iに応答して、前記電圧制御信号V<sub>PP</sub>\_V<sub>DD</sub>\_SHORT<sub>b</sub>を生成する。前記第1プリチャージ信号PCG<sub>O</sub>Rは複数のバンクのうちの一部をプリチャージする信号であり、前記第2プリチャージ信号PCG<sub>A</sub>LLは複数のバンクのすべてをプリチャージする信号であり得る。前記第1プリチャージ信号PCG<sub>O</sub>Rは、例えればプリチャージ命令PCGが入力される場合に活性化される信号であり、前記第2プリチャージ信号PCG<sub>A</sub>LLは、オールバンクプリチャージ命令APCGが入力され

50

る場合に活性化される信号であり得る。

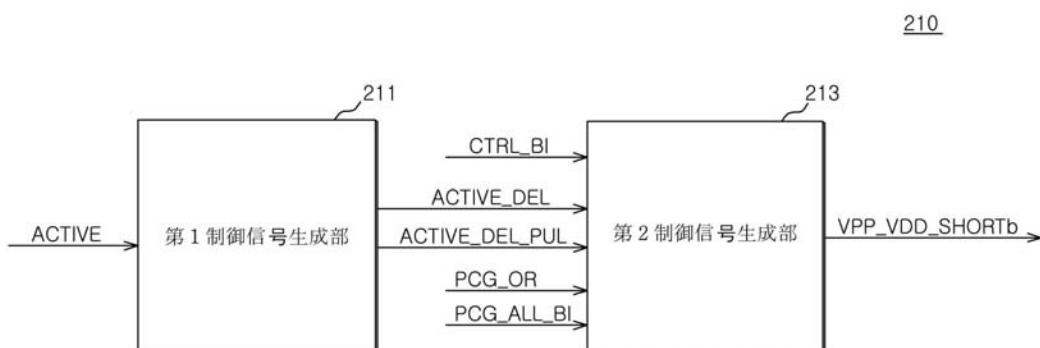

【0038】

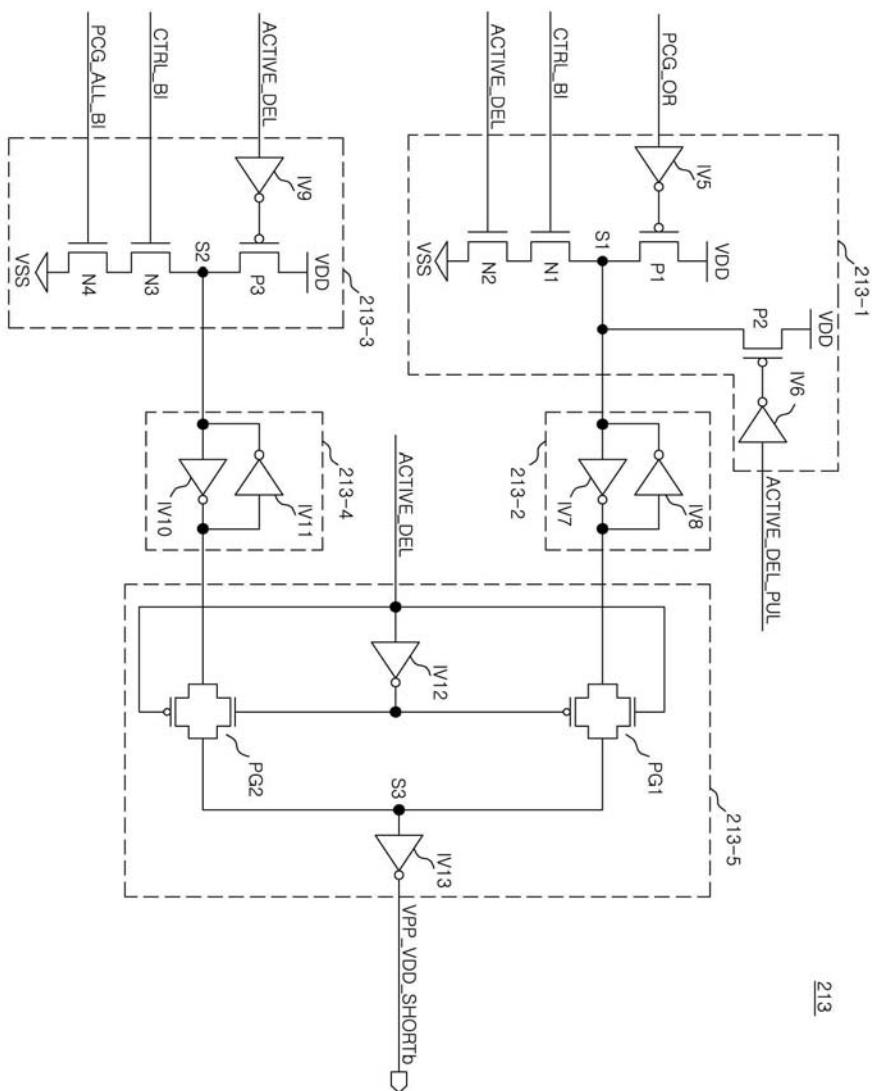

前記制御信号生成部210は、図6に示すように第1制御信号生成部211および第2制御信号生成部213で構成することができる。第1制御信号生成部211は、アクティブ信号ACTIVEが入力され、前記アクティブ信号ACTIVEを遅延させたアクティブディレイ信号ACTIVE\_DELAYを生成し、前記アクティブディレイ信号ACTIVE\_DELAYに応答するパルス信号のアクティブディレイパルス信号ACTIVE\_DELAY\_PULを生成する。

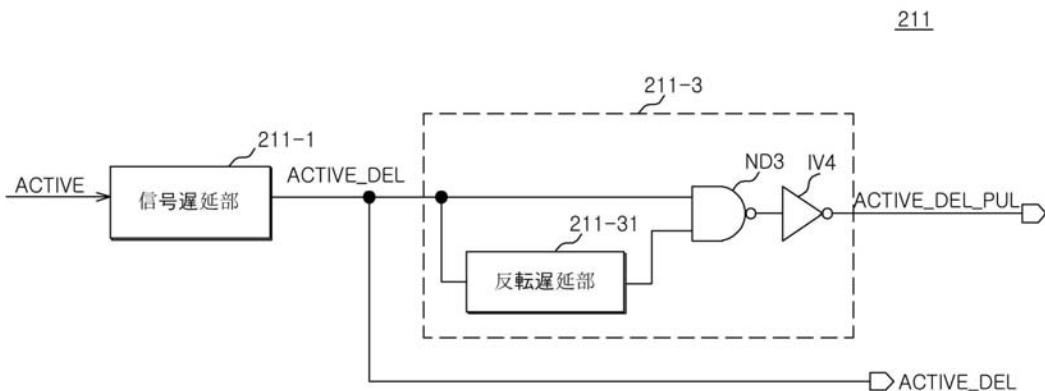

【0039】

このような第1制御信号生成部211は、図7に示すように信号遅延部211-1およびパルス発生部211-3で構成することができる。前記信号遅延部211-1は、前記アクティブ信号ACTIVEを第1時間td1ほど遅延させ、前記アクティブディレイ信号ACTIVE\_DELAYを生成する。前記パルス発生部211-3は、前記アクティブディレイ信号ACTIVE\_DELAYに応答して、アクティブディレイパルス信号ACTIVE\_DELAY\_PULを生成する。前記信号遅延部211-1は、例えば直列に接続された複数のインバータであることができる。前記パルス発生部211-3は、例えば、前記アクティブディレイ信号ACTIVE\_DELAYを第2時間td2ほど反転遅延させる反転遅延部211-31と、前記アクティブディレイ信号ACTIVE\_DELAYおよび前記反転遅延部211-31の出力信号が入力される第3 NANDゲートND3と、前記第3 NANDゲートND3の出力信号を反転させ、アクティブディレイパルス信号ACTIVE\_DELAY\_PULとして出力する第4インバータIV4とで構成することができる。本発明では、前記パルス発生部211-3を NANDゲートおよびインバータを備えて実施したが、設計者の意図により他の論理素子を用いてパルス信号を生成することができる。

【0040】

一方、第2制御信号生成部213は、前記第1プリチャージ信号PCG\_OR、前記バーンインプリチャージ信号PCG\_ALL\_BI、前記バーンイン制御信号CTRL\_BI、前記アクティブディレイ信号ACTIVE\_DELAYおよび前記アクティブディレイパルス信号ACTIVE\_DELAY\_PULに応答して、前記電圧制御信号VPP\_VDD\_SHORT\_bを生成する。

このような第2制御信号生成部213は、図8に示すように第1信号入力部213-1、第1ラッチ部213-2、第2信号入力部213-3、第2ラッチ部213-4および信号駆動部213-5で構成することができる。

【0041】

前記第1信号入力部213-1は、前記第1プリチャージ信号PCG\_OR、前記バーンイン制御信号CTRL\_BI、前記アクティブディレイ信号ACTIVE\_DELAYおよび前記アクティブディレイパルス信号ACTIVE\_DELAY\_PULに応答して、第1ノードS1の電位を変化させる。前記第1信号入力部213-1は、第5インバータIV5、第1トランジスタP1、第2トランジスタN1、第3トランジスタN2、第6インバータIV6および第4トランジスタP2で構成することができる。前記第5インバータIV5は前記第1プリチャージ信号PCG\_ORを反転させ、第1トランジスタP1は前記第5インバータIV5の出力信号に応じて第2電圧VDDをスイッチングする。第2トランジスタN1は、前記バーンイン制御信号CTRL\_BIによって前記第1ノードS1の電圧を前記第3トランジスタN2に伝達し、第3トランジスタN2はアクティブディレイ信号ACTIVE\_DELAYによって第2トランジスタN1から提供された電圧を接地端に伝達する。第6インバータIV6は、前記アクティブディレイパルス信号ACTIVE\_DELAY\_PULを反転させ、第4トランジスタP2は第6インバータIV6の出力信号により第2電圧VDDを第1ノードS1に伝達する。

【0042】

前記第1ラッチ部213-2は、前記第1ノードS1の電位をラッチさせる。前記第1ラッチ部213-2は、第7および第8インバータIV7, IV8で構成される。

第2信号入力部213-3は、前記バーンインプリチャージ信号P C G \_ A L L \_ B I 、前記バーンイン制御信号C T R L \_ B I および前記アクティブディレイ信号A C T I V E \_ D E L に応答して、第2ノードS2の電位を変化させる。前記第2信号入力部213-3は、第9インバータI V 9、第5トランジスタP 3、第6トランジスタN 3および第7トランジスタN 4で構成することができる。前記第9インバータI V 9は前記アクティブディレイ信号A C T I V E \_ D E L を反転させ、第5トランジスタP 3は第9インバータI V 9の出力信号により第2電圧V D D を第2ノードS2に伝達する。第6トランジスタN 3はバーンイン制御信号C T R L \_ B I により第2ノードS2の電圧を第7トランジスタN 4に伝達し、第7トランジスタN 4はバーンインプリチャージ信号P C G \_ A L L \_ B I により前記第6トランジスタN 3から提供される電圧を接地端V S S に伝達する。

10

## 【0043】

第2ラッチ部213-4は、前記第2ノードS2の電位をラッチする。前記第2ラッチ部213-4は、第10インバータI V 10および第11インバータI V 11で構成することができる。

## 【0044】

信号駆動部213-5は、前記アクティブディレイ信号A C T I V E \_ D E L に応答して、前記第1ラッチ部213-2および前記第2ラッチ部213-4の出力信号のうちいずれか1つを駆動させ、前記電圧制御信号V P P \_ V D D \_ S H O R T b を出力する。このような前記信号駆動部213-5は、第12インバータI V 12、第1スイッチング素子P G 1、第2スイッチング素子P G 2、および第13インバータI V 13で構成することができる。前記第12インバータI V 12は、前記アクティブディレイ信号A C T I V E \_ D E L を反転させ、第1スイッチング素子P G 1は、前記アクティブディレイ信号A C T I V E \_ D E L および前記第12インバータI V 12の出力信号により前記第1ラッチ部213-2の出力信号を第3ノードS3に伝達する。第2スイッチング素子P G 2は、前記アクティブディレイ信号A C T I V E \_ D E L および前記第12インバータI V 12の出力信号により第2ラッチ部213-4の出力信号を前記第3ノードS3に伝達する。第13インバータI V 13は前記第3ノードS3の信号を反転させ、電圧制御信号V P P \_ V D D \_ S H O R T b として出力する。本実施形態で前記第1スイッチング素子P G 1および前記第2スイッチング素子P G 2にはパスゲートが利用されることができ、前記第1トランジスタP 1、前記第4トランジスタP 2および前記第5トランジスタP 3はP M O Sトランジスタであり、前記第2トランジスタN 1、前記第3トランジスタN 2、前記第6トランジスタN 3および前記第7トランジスタN 4はN M O Sトランジスタであり得る。

20

## 【0045】

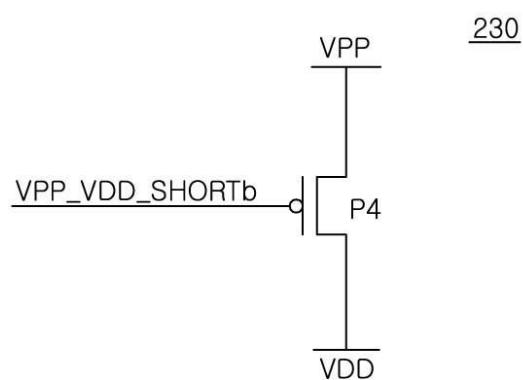

一方、電圧供給制御部230は、前記電圧制御信号V P P \_ V D D \_ S H O R T b に応答して、前記第1電圧V P P および前記第2電圧V D D より低い前記第2電圧V D D のうちいずれか1つを前記ワード線W L に供給する。前記第2電圧V D D は、外部から供給される外部供給電圧を例に挙げることができる、前記第1電圧V P P は前記第2電圧V D D をポンピングして生成される電圧を例に挙げることができる。このような電圧供給制御部230は、図9に示すように、前記電圧制御信号V P P \_ V D D \_ S H O R T b に応答して、前記第1電圧V P P および前記第2電圧V D D をショートさせる第8トランジスタP 4で構成することができる。前記第8トランジスタP 4は、前記電圧制御信号V P P \_ V D D \_ S H O R T b に応答して、前記第1電圧V P P および前記第2電圧V D D をショートさせるスイッチング素子に変えることができる。

30

## 【0046】

前記電圧供給制御部230は、設計者の意図により前記実施形態と異なる方式で前記電圧制御信号V P P \_ V D D \_ S H O R T b に応答して、前記ワード線W L に前記第1電圧V P P および前記第2電圧V D D のうちいずれか1つを供給することができる。

40

## 【0047】

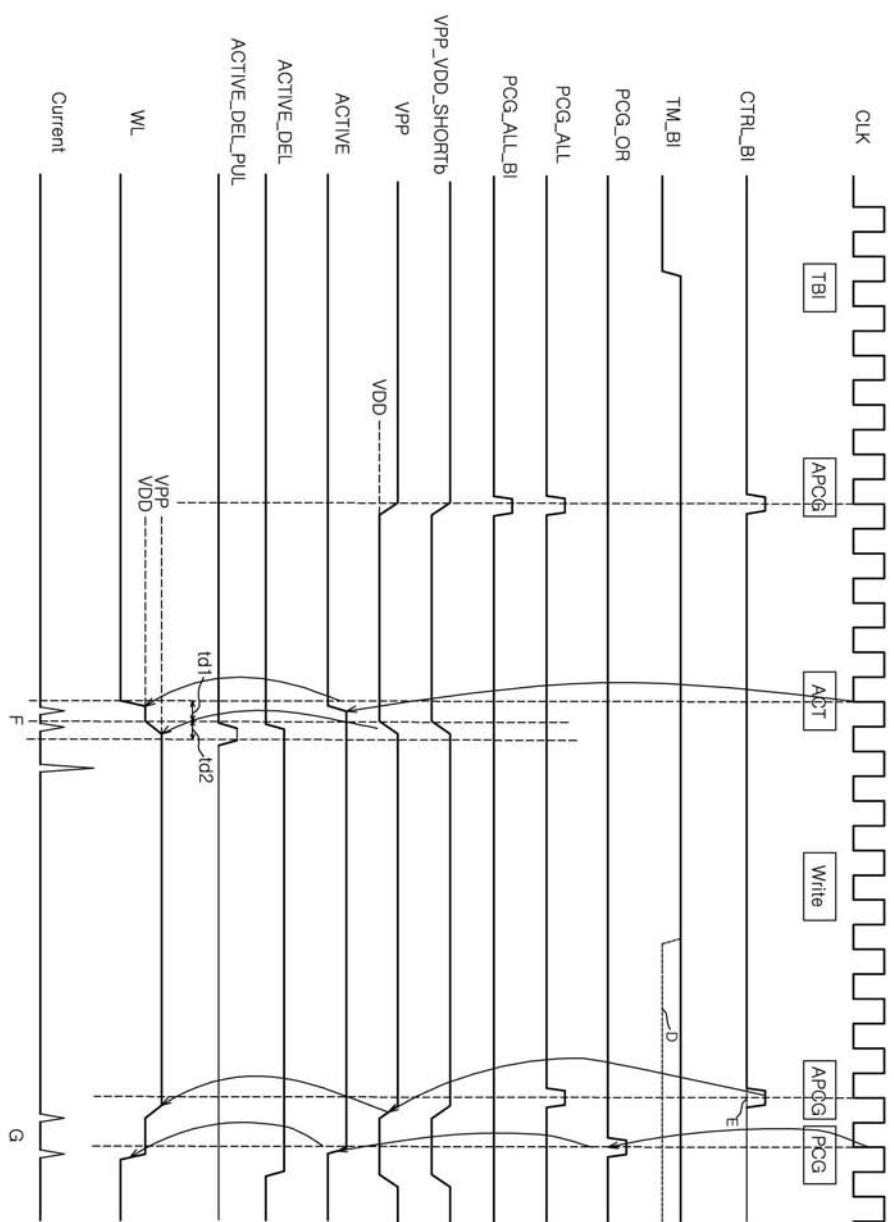

図4～図10を参照すれば、本発明の実施形態に係る電圧供給装置はバーンインテスト

50

モード進入後に所望する電圧レベルによって各パワーを安定化させた後、アクティブ信号が入力される前にオールバンクプリチャージ命令 A P C G が入力され、ダミーオールバンクプリチャージ動作を行う。前記オールバンクプリチャージ動作は、電圧制御装置においてプリチャージを再度行うことで、正常な動作に影響を及ぼさない。前記オールバンクプリチャージ動作で前記制御信号 C T R L は活性化されたパルス信号であるため、前記信号生成部 1 0 0 で活性化されたパルス信号の前記バーンイン制御信号 C T R L \_ B I を出力する。

#### 【 0 0 4 8 】

前記オールバンクプリチャージ命令 A P C G が印加される場合、前記第 2 プリチャージ信号 P C G \_ A L L はハイレベルに活性化され、前記第 1 プリチャージ信号 P C G \_ O R はローレベル状態を維持する。一方、プリチャージ命令 P C G が入力されれば前記第 1 プリチャージ信号 P C G \_ O R はハイレベルに活性化され、前記第 2 プリチャージ信号 P C G \_ A L L はローレベル状態を維持する。10

#### 【 0 0 4 9 】

前記アクティブ信号 A C T I V E がローレベルの状態で、前記オールバンクプリチャージ命令 A P C G が印加される場合、前記第 1 プリチャージ信号 P C G \_ O R はローレベルを維持して、前記アクティブディレイ信号 A C T I V E \_ D E L および前記アクティブディレイパルス信号 A C T I V E \_ D E L \_ P U L もローレベルを維持する。一方、前記第 2 プリチャージ信号 P C G \_ A L L および前記バーンイン制御信号 C T R L \_ B I は、ハイレベルに活性化されるため、前記第 2 信号生成部 1 3 0 はハイレベルの前記バーンインプリチャージ信号 P C G \_ A L L \_ B I を出力する。20

#### 【 0 0 5 0 】

図 8 を参照すれば、前記バーンイン制御信号 C T R L \_ B I および前記バーンインプリチャージ信号 P C G \_ A L L \_ B I に各々応答して、前記第 6 トランジスタ N 3 および前記第 7 トランジスタ N 4 がターンオンして前記第 2 ノード S 2 の電位はローレベルに遷移し、前記第 2 ラッチ部 2 1 3 - 4 は前記第 2 ノード S 2 の電位をローレベルに維持する。この時、前記アクティブディレイ信号 A C T I V E \_ D E L がローレベルであるため、前記第 2 パスゲート P G 2 がターンオンして前記第 3 ノード S 3 の電位はハイレベルになって、前記電圧制御信号 V P P \_ V D D \_ S H O R T b はローレベルに遷移する。前記電圧制御信号 V P P \_ V D D \_ S H O R T b に応答して、前記電圧供給制御部 2 3 0 は前記第 1 電圧 V P P と前記第 2 電圧 V D D をショートさせ前記第 1 電圧 V P P を前記第 2 電圧 V D D にダウンさせる。30

#### 【 0 0 5 1 】

以後、アクティブ命令 A C T が入力される場合、前記アクティブ信号 A C T I V E はハイレベルに活性化され、前記アクティブ信号 A C T I V E は前記信号遅延部 2 1 1 - 1 で前記第 1 時間 t d 1 ほど遅れて、前記アクティブディレイ信号 A C T I V E \_ D E L として出力される。前記パルス発生部 2 1 1 - 3 は、前記アクティブディレイ信号 A C T I V E \_ D E L が入力されて、前記第 2 時間 t d 2 ほどの活性化区間を有するパルス信号の前記アクティブディレイパルス信号 A C T I V E \_ D E L \_ P U L を出力する。

#### 【 0 0 5 2 】

前記アクティブ信号 A C T I V E に応答して前記ワード線 W L が活性化され、前記ワード線 W L の電位は前記第 1 遅延時間 t d 1 の間、前記第 2 電圧 V D D に上昇する。一方、前記アクティブディレイパルス信号 A C T I V E \_ D E L \_ P U L が発生すれば、前記ワード線 W L は、前記第 2 遅延時間 t d 2 の間、前記第 1 電圧 V P P に上昇する。40

#### 【 0 0 5 3 】

すなわち、前記電圧制御信号 V P P \_ V D D \_ S H O R T b がローレベルの区間で前記アクティブ信号 A C T I V E が活性化されれば、前記第 1 遅延時間 t d 1 の間、前記ワード線 W L は前記第 2 電圧 V D D が印加されて、前記第 2 電圧 V D D に上昇する。以後、前記アクティブディレイパルス信号 A C T I V E \_ D E L \_ P U L が活性化される区間で前記電圧制御信号 V P P \_ V D D \_ S H O R T b がハイレベルに遷移するため、前記第 2 遅50

延時間  $t_d 2$  の間、前記ワード線 WL の電位は前記第 1 電圧 VPP に上昇する。

#### 【0054】

図 8 を参照しながら詳細に説明すれば、前記アクティブディレイパルス信号 ACTIV\_E\_DEL\_PUL がハイレベルに活性化する区間で前記第 4 トランジスタ P2 がターンオンして前記第 1 ノード S1 はハイレベルに遷移し、前記第 1 ラッチ部 213-2 は前記第 1 ノード S1 をハイレベルに維持する。前記アクティブディレイ信号 ACTIVE\_DEL がハイレベル状態であるため、前記第 1 パスゲート PG1 がターンオンして前記第 3 ノード S3 はローレベルを維持する。すなわち、前記電圧制御信号 VPP\_VDD\_SHORTb はハイレベルに遷移する。

#### 【0055】

以後、前記プリチャージ命令 PCG の前に前記オールバンクプリチャージ命令 APCG によって前記制御信号 CTRL がダミーで活性化されるパルスを有するようになれば、前記第 1 信号生成部 110 でハイレベルに活性化されるパルス信号の前記バーンイン制御信号 CTRL\_BI を出力し、前記第 2 信号生成部 130 でローレベルの前記バーンインプリチャージ信号 PCG\_ALLBBI を出力する。バーンインテストモードで前記制御信号 CTRL がダミーで活性化されるパルスを有する場合、DRAM の正常動作上問題はない。例えば、D のようにバーンインテストモードではない場合、前記信号生成部 100 はローレベルの前記バーンインテストモード信号 TM\_BI とハイレベルの前記制御信号 CTRL が入力されるようになって E のようにローレベルの前記バーンイン制御信号 CTRL\_BI を出力する。

10

20

30

40

#### 【0056】

この時、前記バーンイン制御信号 CTRL\_BI および前記アクティブディレイ信号 ACTIVE\_DEL に応答して、前記第 2 トランジスタ N1 および前記第 3 トランジスタ N2 がターンオンして前記第 1 ノード S1 はローレベルに遷移し、前記第 1 ラッチ部 213-2 は前記第 1 ノード S1 の電位をローレベルに維持する。ハイレベルの前記アクティブディレイ信号 ACTIVE\_DEL に応答して、前記第 1 パスゲート PG1 がターンオンして前記第 3 ノード S3 はハイレベルに維持され、前記第 13 インバータ I13 によって前記電圧制御信号 VPP\_VDD\_SHORTb はローレベルに遷移する。前記電圧制御信号 VPP\_VDD\_SHORTb に応答して、前記電圧供給制御部 230 が前記第 1 電圧 VPP と前記第 2 電圧 VDD をショートさせることで、前記ワード線 WL の電位は前記第 2 電圧 VDD にダウンする。以後、前記プリチャージ命令 PCG が入力されれば、前記アクティブ信号 ACTIVE は非活性化され、前記アクティブ信号 ACTIVE に応答して前記ワード線 WL が前記接地電圧 VSS にダウンするようになる。前記プリチャージ命令 PCG が入力される時、前記第 1 プリチャージ信号 PCG\_OR がハイレベルに活性化されるパルス信号を有するため前記第 1 トランジスタ P1 がターンオンして前記第 1 ノード S1 の電位はハイレベルに遷移し、前記第 1 ラッチ部 213-2 は前記第 1 ノード S1 の電位をハイレベルに維持する。この時、前記アクティブディレイ信号 ACTIVE\_DEL がハイレベルに維持しているため、前記第 1 パスゲート PG1 がターンオンして前記第 3 ノード S3 の電位はローレベルに遷移する。すなわち、前記電圧制御信号 VPP\_VDD\_SHORTb がハイレベルに遷移する。

#### 【0057】

前記説明した通り、本発明に係る電圧制御装置は、アクティブ動作時前記ワード線 WL を駆動する時、前記第 2 電圧 VDD で前記ワード線 WL の電位を高めた以後前記第 2 電圧 VDD より高い前記第 1 電圧 VPP で前記ワード線 WL を駆動させることによって、ピーク電流を分散させられる。また、プリチャージ動作時、前記プリチャージ動作以前に前記ワード線 WL の電位を前記第 2 電圧 VDD に下げて、以後前記接地電圧 VSS に下げるこことによってピーク電流を分散させられる。

図 10 に示すように、F はアクティブ動作時のピーク電流が分散することを示し、G はプリチャージ動作時のピーク電流が分散することを示す。

#### 【0058】

50

このように、本発明が属する技術分野の当業者は、本発明がその技術的思想や必須特徴を変更せず、他の具体的な形態で実施され得ることを理解できる。したがって、以上で記述した実施形態はすべての面で例示的なものであり、限定的なものではないものと理解しなければならない。本発明の範囲は前記詳細な説明よりは特許請求の範囲によって示され、特許請求の範囲の意味および範囲、そしてその等価概念から導き出されるすべての変更又は変形された形態が本発明の範囲に含まれると解釈しなければならない。

【図面の簡単な説明】

【0059】

【図1】ローファースト(X-Fast)動作に伴うアドレス進行方向およびアドレスパターンを示す概念図である。

10

【図2】カラムファースト(Y-Fast)動作に伴うアドレス進行方向およびアドレスパターンを示す概念図である。

【図3】従来の電圧制御装置がローファースト(X-Fast)動作をする場合にアクティブプリチャージ方式を示すタイミング図である。

【図4】本発明の実施形態に係る電圧制御装置を示すブロック図である。

【図5】図4に示す信号生成部の内部回路図である。

【図6】図4に示す制御信号生成部の内部ブロック図である。

【図7】図6に示す第1制御信号生成部の内部回路図である。

【図8】図6に示す第2制御信号生成部の内部回路図である。

【図9】図4に示す電圧供給部の内部回路図である。

【図10】本発明の電圧制御装置がローファースト(X-Fast)動作をする場合にアクティブプリチャージ方式を示すタイミング図である。

20

【符号の説明】

【0060】

100...信号生成部

110...第1信号生成部

130...第2信号生成部

200...電圧制御部

210...制御信号生成部

211...第1制御信号生成部

211-1...信号遅延部

211-3...パルス発生部

213...第2制御信号生成部

213-1...第1信号入力部

213-2...第1ラッチ部

213-3...第2信号入力部

211-31...反転遅延部

213-4...第2ラッチ部

213-5...信号駆動部

230...電圧供給制御部

30

30

40

【図 1】

【図2】

$A_0 - W_0 - W_1 - W_2 \bullet \bullet \bullet W(N-1) - W(N) - P_0$

$A_1 - W_0 - W_1 - W_2 \bullet \bullet \bullet W(N-1) - W(N) - P_1$

$A_2 - W_0 - W_1 - W_2 \bullet \bullet \bullet W(N-1) - W(N) - P_2$

.

.

.

$A(N-1) - W_0 - W_1 - W_2 \bullet \bullet \bullet W(N-1) - W(N) - P(N-1)$

$A(N) - W_0 - W_1 - W_2 \bullet \bullet \bullet W(N-1) - W(N) - P(N)$

【図3】

【図4】

【図5】

【図6】

【図7】

【図 8】

【図 9】

【図 10】

---

フロントページの続き

(51) Int.Cl.

F I

テーマコード(参考)

G 0 1 R 31/28

V

(72)発明者 慎允宰

大韓民国京畿道利川市夫鉢邑牙美里山136-1

Fターム(参考) 2G132 AA08 AB03 AK07 AL00

5L106 AA01 DD11 DD36 EE02 FF04 FF05 GG05

5M024 AA25 AA96 BB29 BB35 BB36 FF01 FF25 MM03 MM04 PP02

PP03 PP07