(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6635670号

(P6635670)

(45) 発行日 令和2年1月29日(2020.1.29)

(24) 登録日 令和1年12月27日(2019.12.27)

|                |           |

|----------------|-----------|

| (51) Int.Cl.   | F 1       |

| HO 1 L 27/10   | (2006.01) |

| HO 1 L 21/8242 | (2006.01) |

| HO 1 L 27/108  | (2006.01) |

| HO 1 L 21/8239 | (2006.01) |

| HO 1 L 27/105  | (2006.01) |

|                |           |

| HO 1 L         | 27/10     |

| HO 1 L         | 27/108    |

| HO 1 L         | 27/105    |

| HO 1 L         | 21/28     |

| HO 1 L         | 29/50     |

|                | M         |

請求項の数 4 (全 47 頁) 最終頁に続く

|                    |                               |

|--------------------|-------------------------------|

| (21) 出願番号          | 特願2015-78296 (P2015-78296)    |

| (22) 出願日           | 平成27年4月7日(2015.4.7)           |

| (65) 公開番号          | 特開2015-207761 (P2015-207761A) |

| (43) 公開日           | 平成27年11月19日(2015.11.19)       |

| 審査請求日              | 平成30年3月26日(2018.3.26)         |

| (31) 優先権主張番号       | 特願2014-81616 (P2014-81616)    |

| (32) 優先日           | 平成26年4月11日(2014.4.11)         |

| (33) 優先権主張国・地域又は機関 | 日本国(JP)                       |

|           |                                                |

|-----------|------------------------------------------------|

| (73) 特許権者 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (72) 発明者  | 大貫 達也<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (72) 発明者  | 加藤 清<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内    |

| (72) 発明者  | 塙野入 豊<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (72) 発明者  | 熱海 知昭<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

記憶回路と、增幅回路と、集積回路と、ダミー回路と、絶縁層と、を有し、

前記記憶回路、前記增幅回路及び前記ダミー回路と、前記集積回路とは、互いに重なる

領域を有し、

前記記憶回路、前記增幅回路及び前記ダミー回路は、前記絶縁層を介して、前記集積回

路上に設けられ、

前記記憶回路は、前記絶縁層を介して前記集積回路の第1の領域上に設けられ、

前記增幅回路は、前記絶縁層を介して前記集積回路の第2の領域上に設けられ、

前記ダミー回路は、前記絶縁層を介して前記集積回路の第3の領域上に設けられ、

前記記憶回路と前記ダミー回路とは互いに重ならず、

前記增幅回路は、前記絶縁層の開口部に設けられた導電層を介して前記集積回路と接続

され、

前記增幅回路は、前記記憶回路と接続され、

前記增幅回路は、前記ダミー回路と接続されておらず、

前記記憶回路は、酸化物半導体を含む第1のチャネル形成領域を有する第1のトランジ

スタを有し、

前記增幅回路は、酸化物半導体を含む第2のチャネル形成領域を有する第2のトランジ

スタを有し、

前記ダミー回路は、酸化物半導体を含む第3のチャネル形成領域を有する第3のトラン

10

20

ジスタを有し、

前記集積回路は、単結晶半導体を含む第4のチャネル形成領域を有する第4のトランジスタを有し、する半導体装置。

【請求項2】

請求項1において、

前記第4のチャネル形成領域と、前記第1のチャネル形成領域又は前記第2のチャネル形成領域とは、互いに重なる領域を有する半導体装置。

【請求項3】

請求項1又は2において、

前記第4のトランジスタのソース又はドレインの一方は、前記第2のトランジスタのソース又はドレインの一方と電気的に接続されている半導体装置。 10

【請求項4】

請求項1乃至3のいずれか一項において、

前記酸化物半導体は、Inと、Znと、M(Mは、Al、Ti、Ga、Y、Zr、La、Ce、NdまたはHf)と、を含む半導体装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の一態様は、記憶回路および增幅回路を有する半導体装置に関する。

【0002】

なお、本発明の一態様は、上記の技術分野に限定されない。本明細書等で開示する発明の一態様の技術分野は、物、方法、または、製造方法に関するものである。または、本発明の一態様は、プロセス、マシン、マニュファクチャ、または、組成物(コンポジション・オブ・マター)に関するものである。または、本発明の一態様は、半導体装置、表示装置、発光装置、蓄電装置、記憶装置、それらの駆動方法、または、それらの製造方法に関する。

【背景技術】

【0003】

DRAM(Dynamic Random Access Memory)は、データの高速な書き込み、読み出しが可能な揮発性メモリであり、様々な記憶装置に広く用いられている。DRAMには大容量化による低コスト化が求められており、メモリセルのレイアウトの変更やメモリセルを構成する素子の微細化などにより、大容量化を図る研究開発が活発に行われている。 30

【0004】

また、一般的なDRAMにおいては、メモリセルはセンスアンプと接続されている。そして、メモリセルに保持されている電荷をビット線に放出した際の微小な電圧の差をセンスアンプによって増幅することにより、メモリセルに記憶されたデータを読み出すことができる。

【0005】

特許文献1には、複数のメモリセルアレイ領域の間にセンスアンプ領域が設けられた構成において、チップの面積の縮小のため、センスアンプ領域の面積を縮小する技術が開示されている。 40

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2004-221374号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

DRAMのメモリセルの寸法の縮小や素子の微細化には限界があり、これらの方法による

50

大容量化は技術的に困難になりつつある。また、DRAMにはメモリセルの他にセンスアンプが設けられており、これが一定の面積を占めているため、メモリセルが設けられる領域の面積が制限され、大容量化の妨げとなっている。

#### 【0008】

また、特許文献1には、センスアンプ領域の面積を縮小する技術が開示されているが、メモリセルアレイの間にセンスアンプが設けられている以上、メモリセルアレイを設置できる面積は制限され、一定以上の大容量化は困難である。

#### 【0009】

上記の技術的背景の下、本発明の一態様は、新規な半導体装置の提供を課題の一つとする。また、本発明の一態様は、面積の縮小が可能な半導体装置の提供を課題の一つとする。

10 また、本発明の一態様は、消費電力の低減が可能な半導体装置の提供を課題の一つとする。また、本発明の一態様は、高速な動作が可能な半導体装置の提供を課題の一つとする。

#### 【0010】

なお、本発明の一態様は、必ずしも上記の課題の全てを解決する必要はなく、少なくとも一の課題を解決できるものであればよい。また、上記の課題の記載は、他の課題の存在を妨げるものではない。これら以外の課題は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の課題を抽出することが可能である。

#### 【課題を解決するための手段】

#### 【0011】

本発明の一態様にかかる半導体装置は、第1の回路と、第2の回路と、絶縁層と、を有し、第1の回路は、記憶回路を有し、第2の回路は、增幅回路を有し、絶縁層は、第1の回路と第2の回路との間に設けられ、記憶回路は、第1のチャネル形成領域を有する第1のトランジスタを有し、増幅回路は、第2のチャネル形成領域を有する第2のトランジスタを有し、第1のチャネル形成領域は、単結晶半導体を含み、第2のチャネル形成領域は、酸化物半導体を含み、第1の回路と、第2の回路とは、互いに重なる領域を有する。

#### 【0012】

また、上記半導体装置において、第1のチャネル形成領域と、第2のチャネル形成領域とは、互いに重なる領域を有していてもよい。

#### 【0013】

また、上記半導体装置において、第1のトランジスタのソース又はドレインの一方は、第2のトランジスタのソース又はドレインの一方と電気的に接続されていてもよい。

#### 【0014】

また、本発明の一態様にかかる別の半導体装置は、第1の回路と、第2の回路と、第3の回路と、絶縁層と、を有し、第1の回路は、集積回路を有し、第2の回路は、記憶回路を有し、第3の回路は、増幅回路を有し、絶縁層は、第1の回路と、第2の回路及び第3の回路との間に設けられ、集積回路は、第1のチャネル形成領域を有する第1のトランジスタを有し、記憶回路は、第2のチャネル形成領域を有する第2のトランジスタを有し、増幅回路は、第3のチャネル形成領域を有する第3のトランジスタを有し、第1のチャネル形成領域は、単結晶半導体を含み、第2のチャネル形成領域は、酸化物半導体を含み、第3のチャネル形成領域は、酸化物半導体を含み、第1の回路と、第2の回路又は第3の回路とは、互いに重なる領域を有する。

#### 【0015】

また、上記半導体装置において、第1のチャネル形成領域と、第2のチャネル形成領域又は第3のチャネル形成領域とは、互いに重なる領域を有していてもよい。

#### 【0016】

また、上記半導体装置において、第1のトランジスタのソース又はドレインの一方は、第3のトランジスタのソース又はドレインの一方と電気的に接続されていてもよい。

#### 【0017】

また、上記半導体装置において、酸化物半導体は、Inと、Znと、M(Mは、Al、T

50

i、G a、Y、Z r、L a、C e、N d またはH f )と、を含んでいてもよい。

【発明の効果】

【0018】

本発明の一態様により、新規な半導体装置を提供することができる。また、本発明の一態様により、面積の縮小が可能な半導体装置を提供することができる。また、本発明の一態様により、消費電力の低減が可能な半導体装置を提供することができる。また、本発明の一態様により、高速な動作が可能な半導体装置を提供することができる。

【0019】

なお、これらの効果の記載は、他の効果の存在を妨げるものではない。なお、本発明の一態様は、必ずしも、これらの効果の全てを有する必要はない。なお、これら以外の効果は明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の効果を抽出することが可能である。

10

【図面の簡単な説明】

【0020】

【図1】半導体装置の構成の一例を説明する図。

【図2】半導体装置の構成の一例を説明する図。

【図3】半導体装置の構成の一例を説明する図。

【図4】半導体装置の構成の一例を説明する図。

【図5】半導体装置の構成の一例を説明する図。

【図6】半導体装置の構成の一例を説明する回路図。

20

【図7】タイミングチャート。

【図8】タイミングチャート。

【図9】半導体装置の構成の一例を説明する回路図。

【図10】半導体装置の構成の一例を説明する図。

【図11】トランジスタの構成の一例を説明する図。

【図12】トランジスタの構成の一例を説明する図。

【図13】トランジスタの構成の一例を説明する図。

【図14】トランジスタの構成の一例を説明する図。

【図15】トランジスタの構成の一例を説明する図。

【図16】トランジスタの構成の一例を説明する図。

30

【図17】電子機器を説明する図。

【発明を実施するための形態】

【0021】

以下、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の実施の形態における説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは、当業者であれば容易に理解される。したがって、本発明は、以下の実施の形態の記載内容に限定して解釈されるものではない。

【0022】

また、本発明の一態様は、集積回路、表示装置、R F タグを含むあらゆる装置が、その範疇に含まれる。また、表示装置には、液晶表示装置、有機発光素子に代表される発光素子を各画素に備えた発光装置、電子ペーパー、D M D (D i g i t a l M i c r o m i r r o r D e v i c e)、P D P (P l a s m a D i s p l a y P a n e l)、F E D (F i e l d E m i s s i o n D i s p l a y)など、集積回路を回路に有している表示装置が、その範疇に含まれる。

40

【0023】

なお、図面を用いて発明の構成を説明するにあたり、同じものを指す符号は異なる図面間でも共通して用いる。

【0024】

また、本明細書等においては、ある一つの実施の形態において述べる図または文章において、その一部分を取り出して、発明の一態様を構成することは可能である。したがって、

50

ある部分を述べる図または文章が記載されている場合、その一部分の図または文章を取り出した内容も、発明の一態様として開示されているものであり、発明の一態様を構成することが可能であるものとする。そして、その発明の一態様は明確であると言える。そのため、例えば、能動素子（トランジスタなど）、配線、受動素子（容量素子など）、導電層、絶縁層、半導体層、部品、装置、動作方法、製造方法などが単数もしくは複数記載された図面または文章において、その一部分を取り出して、発明の一態様を構成することが可能であるものとする。例えば、N個（Nは整数）の回路素子（トランジスタ、容量素子等）を有して構成される回路図から、M個（Mは整数で、M < N）の回路素子（トランジスタ、容量素子等）を抜き出して、発明の一態様を構成することは可能である。別の例としては、「Aは、B、C、D、E、または、Fを有する」と記載されている文章から、一部の要素を任意に抜き出して、「Aは、BとEとを有する」、「Aは、EとFとを有する」、「Aは、CとEとFとを有する」、または、「Aは、BとCとDとEとを有する」などの発明の一態様を構成することは可能である。10

#### 【0025】

また、本明細書等においては、ある一つの実施の形態において述べる図または文章において、少なくとも一つの具体例が記載される場合、その具体例の上位概念を導き出すことは、当業者であれば容易に理解される。したがって、ある一つの実施の形態において述べる図または文章において、少なくとも一つの具体例が記載される場合、その具体例の上位概念も、発明の一態様として開示されているものであり、発明の一態様を構成することが可能である。そして、その発明の一態様は、明確であると言える。20

#### 【0026】

また、本明細書等においては、少なくとも図に記載した内容（図の中の一部でもよい）は、発明の一態様として開示されているものであり、発明の一態様を構成することが可能である。したがって、ある内容について、図に記載されていれば、文章を用いて述べていなくても、その内容は、発明の一態様として開示されているものであり、発明の一態様を構成することが可能である。同様に、図の一部を取り出した図についても、発明の一態様として開示されているものであり、発明の一態様を構成することが可能である。そして、その発明の一態様は明確であると言える。

#### 【0027】

##### （実施の形態1）

本実施の形態では、本発明の一態様に係る構成の一例について説明する。30

#### 【0028】

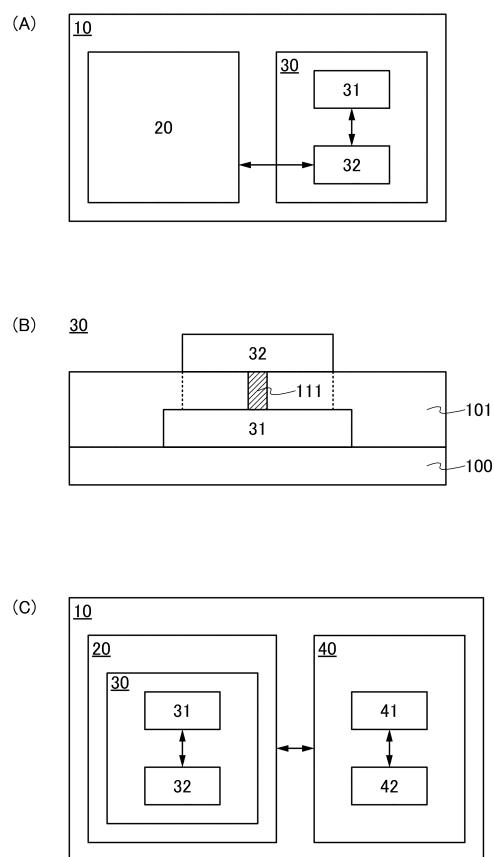

図1（A）に、本発明の一態様に係る半導体装置10の構成の一例を示す。半導体装置10は、回路20、回路30を有する。

#### 【0029】

回路20は、演算処理や他の回路の制御などを行う機能を有する。回路20は、複数のトランジスタを有する集積回路によって構成することができる。また、回路20は、順序回路や組み合わせ回路などの各種の論理回路を有する構成とすることができます。回路20は、例えば中央処理装置（CPU）として用いることができる。

#### 【0030】

回路30は、回路20や入出力装置（図示せず）などから入力されたデータを記憶する機能を有する。また、回路30は、回路30に記憶されたデータを回路20や入出力装置に出力する機能を有する。回路30は、キャッシュメモリ、主記憶装置、補助記憶装置などの各種記憶装置として用いることができる。

#### 【0031】

回路30は、回路31、回路32を有する。回路31は、データを記憶する機能を有する。なお、回路31は、データを記憶する機能を有する回路（以下、記憶回路ともいう）を複数個備えた、セルアレイを有する構成とすることができます。回路31は、例えば、DRAMやSRAMなどの揮発性メモリ、またはNAND型フラッシュメモリなどの不揮発性メモリによって構成することができる。特に、回路31をDRAMで構成すると、回路340

1を高速かつ小面積の記憶回路とすることができるため好ましい。なお、回路30は、回路31の動作を制御するための駆動回路を有していてもよい。

#### 【0032】

回路32は、入力された信号を増幅して出力する機能を有する回路（以下、増幅回路ともいう）を有する。具体的には、増幅回路は、外部から入力されたデータを増幅して回路31に書き込む機能と、回路31に記憶されたデータを増幅して出力する機能を有する。これにより、外部から入力された信号が微弱であっても、これを増幅して記憶回路に書き込むことができる。また、回路31に記憶された信号が微弱であっても、これを増幅して読み出すことができる。よって、データの書き込みおよび読み出しを正確に行うことができる。回路32は、複数のセンスアンプを備えた構成とすることができます。なお、回路30は、回路32の動作を制御するための駆動回路を有していてもよい。10

#### 【0033】

図1（B）に、回路30の断面構造の一例を示す。回路30は、基板100上の回路31と、回路31上の絶縁層101と、絶縁層101上の回路32を有する。絶縁層101は開口部を有し、開口部には導電層111が設けられている。回路32は、導電層111を介して回路31と接続されている。このように、回路30は、回路31と回路32が積層された構造を有する。なお、基板100上に回路20が設けられていてもよい。

#### 【0034】

なお、本明細書等において、XとYとが接続されている、と明示的に記載する場合は、XとYとが電気的に接続されている場合と、XとYとが機能的に接続されている場合と、XとYとが直接接続されている場合とを含むものとする。したがって、所定の接続関係、例えば、図または文章に示された接続関係に限定されず、図または文章に示された接続関係以外のものも含むものとする。ここで、X、Yは、対象物（例えば、装置、素子、回路、配線、電極、端子、導電膜、層、など）であるとする。20

#### 【0035】

XとYとが電気的に接続されている場合の一例としては、XとYとの電気的な接続を可能とする素子（例えば、スイッチ、トランジスタ、容量素子、インダクタ、抵抗素子、ダイオード、表示素子、発光素子、負荷など）が、XとYとの間に1個以上接続されることが可能である。なお、スイッチは、オンオフが制御される機能を有している。つまり、スイッチは、導通状態（オン状態）、または、非導通状態（オフ状態）になり、電流を流すか流さないかを制御する機能を有している。または、スイッチは、電流を流す経路を選択して切り替える機能を有している。30

#### 【0036】

XとYとが機能的に接続されている場合の一例としては、XとYとの機能的な接続を可能とする回路（例えば、論理回路（インバータ、NAND回路、NOR回路など）、信号変換回路（DA変換回路、AD変換回路、ガンマ補正回路など）、電位レベル変換回路（電源回路（昇圧回路、降圧回路など）、信号の電位レベルを変えるレベルシフタ回路など）、電圧源、電流源、切り替え回路、増幅回路（信号振幅または電流量などを大きく出来る回路、オペアンプ、差動増幅回路、ソースフォロワ回路、バッファ回路など）、信号生成回路、記憶回路、制御回路など）が、XとYとの間に1個以上接続されることが可能である。なお、一例として、XとYとの間に別の回路を挟んでいても、Xから出力された信号がYへ伝達される場合は、XとYとは機能的に接続されているものとする。40

#### 【0037】

なお、XとYとが電気的に接続されている、と明示的に記載する場合は、XとYとが電気的に接続されている場合（つまり、XとYとの間に別の素子又は別の回路を挟んで接続されている場合）と、XとYとが機能的に接続されている場合（つまり、XとYとの間に別の回路を挟んで機能的に接続されている場合）と、XとYとが直接接続されている場合（つまり、XとYとの間に別の素子又は別の回路を挟まずに接続されている場合）とを含むものとする。つまり、電気的に接続されている、と明示的に記載する場合は、単に、接続されている、とのみ明示的に記載されている場合と同じであるとする。50

**【 0 0 3 8 】**

なお、例えば、トランジスタのソース（又は第1の端子など）が、Z1を介して（又は介さず）、Xと電気的に接続され、トランジスタのドレイン（又は第2の端子など）が、Z2を介して（又は介さず）、Yと電気的に接続されている場合や、トランジスタのソース（又は第1の端子など）が、Z1の一部と直接的に接続され、Z1の別の一部がXと直接的に接続され、トランジスタのドレイン（又は第2の端子など）が、Z2の一部と直接的に接続され、Z2の別の一部がYと直接的に接続されている場合では、以下のように表現することが出来る。

**【 0 0 3 9 】**

例えば、「XとYとトランジスタのソース（又は第1の端子など）とドレイン（又は第2の端子など）とは、互いに電気的に接続されており、X、トランジスタのソース（又は第1の端子など）、トランジスタのドレイン（又は第2の端子など）、Yの順序で電気的に接続されている。」と表現することができる。または、「トランジスタのソース（又は第1の端子など）は、Xと電気的に接続され、トランジスタのドレイン（又は第2の端子など）はYと電気的に接続され、X、トランジスタのソース（又は第1の端子など）、トランジスタのドレイン（又は第2の端子など）、Yは、この順序で電気的に接続されている」と表現することができる。または、「Xは、トランジスタのソース（又は第1の端子など）とドレイン（又は第2の端子など）とを介して、Yと電気的に接続され、X、トランジスタのソース（又は第1の端子など）、トランジスタのドレイン（又は第2の端子など）、Yは、この接続順序で設けられている」と表現することができる。これらの例と同様な表現方法を用いて、回路構成における接続の順序について規定することにより、トランジスタのソース（又は第1の端子など）と、ドレイン（又は第2の端子など）とを、区別して、技術的範囲を決定することができる。なお、これらの表現方法は、一例であり、これらの表現方法に限定されない。ここで、X、Y、Z1、Z2は、対象物（例えば、装置、素子、回路、配線、電極、端子、導電膜、層、など）であるとする。

10

20

**【 0 0 4 0 】**

また、図面上は独立している構成要素同士が電気的に接続しているように図示されている場合であっても、1つの構成要素が、複数の構成要素の機能を併せ持っている場合もある。例えば、配線の一部が電極としても機能する場合は、一の導電膜が、配線の機能、及び電極の機能の両方の構成要素の機能を併せ持っている。したがって、本明細書における接続とは、このような、一の導電膜が、複数の構成要素の機能を併せ持っている場合も、その範疇に含める。

30

**【 0 0 4 1 】**

図1(B)において、回路31は、絶縁層101を介して回路32と重なる領域を有するように配置することができる。また、回路31は、絶縁層101を介して回路32の全面と重なるように配置することができる。上記のいずれかの構成をとることにより、回路30の面積の増加を抑えつつ、回路32を設けることができる。すなわち、回路30の面積の増加を抑えつつ、回路30に增幅回路を搭載することができる。よって、半導体装置10の面積の縮小を図ることができる。

**【 0 0 4 2 】**

40

なお、図1(C)に示すように、回路30は回路20の内部に設けられていてよい。この場合、回路30は、例えばキャッシュメモリとして用いることができる。また、図1(C)において、半導体装置10は、さらに回路40を有していてよい。回路40は、回路41、回路42を有する。回路41は回路31と同様の機能を有する回路であり、回路42は、回路32と同様の機能を有する回路である。回路41と回路42は、回路31と回路32と同様に、積層した構成とすることができます（図1(B)参照）。回路40は、例えば主記憶装置として用いることができる。

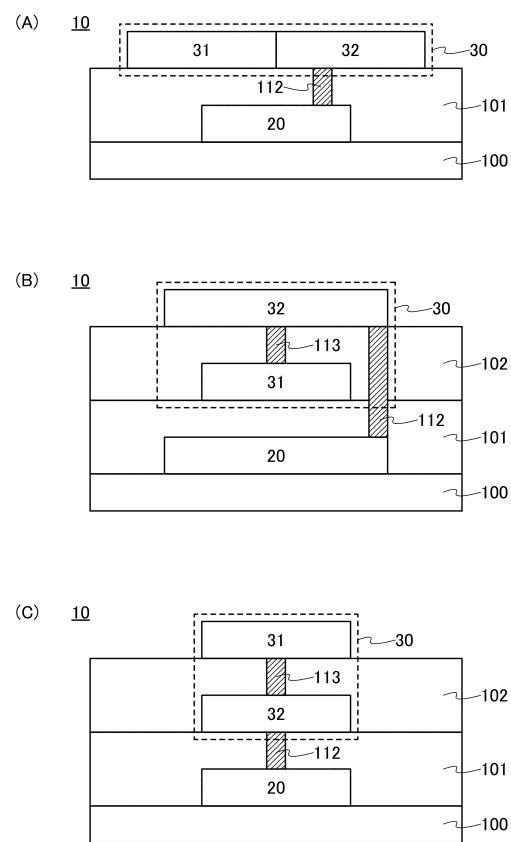

**【 0 0 4 3 】**

また、図2(A)乃至(C)に示すように、半導体装置10は、回路30を回路20上に積層した構成とすることもできる。図2(A)において、半導体装置10は、基板100

50

上の回路 20 と、回路 20 上の絶縁層 101 と、絶縁層 101 上の回路 31 および回路 32 を有する。絶縁層 101 は開口部を有し、開口部には導電層 112 が設けられている。回路 32 は、導電層 112 を介して回路 20 と接続されている。また、回路 32 は、回路 31 と接続されている。このように、半導体装置 10 は、回路 20 と、回路 31 および回路 32 とが積層された構造を有する。

#### 【0044】

回路 31 は、回路 20 と重なる領域を有するように配置することができる。また、回路 32 は、回路 20 と重なる領域を有するように配置することができる。また、回路 31 は、回路 20 の全面と重なる領域を有するように配置することができる。また、回路 32 は、回路 20 の全面と重なる領域を有するように配置することができる。上記のいずれかの構成をとることにより、半導体装置 10 の面積の増加を抑えつつ、回路 32 を設けることができる。すなわち、半導体装置 10 の面積の増加を抑えつつ、回路 30 に增幅回路を搭載することができる。よって、半導体装置 10 の面積の縮小を図ることができる。10

#### 【0045】

また、図 2 (B) に示すように、回路 31 と回路 32 を積層した構成とすることもできる。図 2 (B)において、半導体装置 10 は、基板 100 上の回路 20 と、回路 20 上の絶縁層 101 と、絶縁層 101 上の回路 31 と、回路 31 上の絶縁層 102 と、絶縁層 102 上の回路 32 を有する。絶縁層 101 および絶縁層 102 は第 1 の開口部を有し、第 1 の開口部には導電層 112 が設けられている。そして、回路 32 は、導電層 112 を介して回路 20 と接続されている。また、絶縁層 102 は第 2 の開口部を有し、第 2 の開口部には導電層 113 が設けられている。そして、回路 32 は、導電層 113 を介して回路 31 と接続されている。20

#### 【0046】

回路 31 は、回路 20 と重なる領域を有するように配置することができる。また、回路 31 は、回路 20 の全面と重なる領域を有するように配置することができる。また、回路 32 は、回路 20 と重なる領域を有するように配置することができる。また、回路 32 は、回路 20 の全面と重なる領域を有するように配置することができる。また、回路 31 は、回路 32 と重なる領域を有するように配置することができる。また、回路 31 は、回路 32 の全面と重なる領域を有するように配置することができる。上記のいずれかの構成をとることにより、半導体装置 10 の面積の増加を抑えつつ、回路 32 を設けることができる。すなわち、半導体装置 10 の面積の増加を抑えつつ、回路 30 に增幅回路を搭載することができる。よって、半導体装置 10 の面積の縮小を図ることができる。30

#### 【0047】

なお、図 2 (B)においては、回路 31 上に回路 32 が設けられた構成を示したが、図 2 (C) に示すように、回路 32 上に回路 31 が設けられた構成とすることもできる。ここで、絶縁層 101 は開口部を有し、絶縁層 101 の開口部には導電層 112 が設けられている。そして、回路 32 は、導電層 112 を介して回路 20 と接続されている。また、絶縁層 102 は開口部を有し、絶縁層 102 の開口部には導電層 113 が設けられている。そして、回路 32 は、導電層 113 を介して回路 31 と接続されている。40

#### 【0048】

回路 31 は、回路 32 と重なる領域を有するように配置することができる。また、回路 31 は、回路 32 の全面と重なる領域を有するように配置することができる。上記のいずれかの構成をとることによっても、半導体装置 10 の面積の縮小を図ることができる。

#### 【0049】

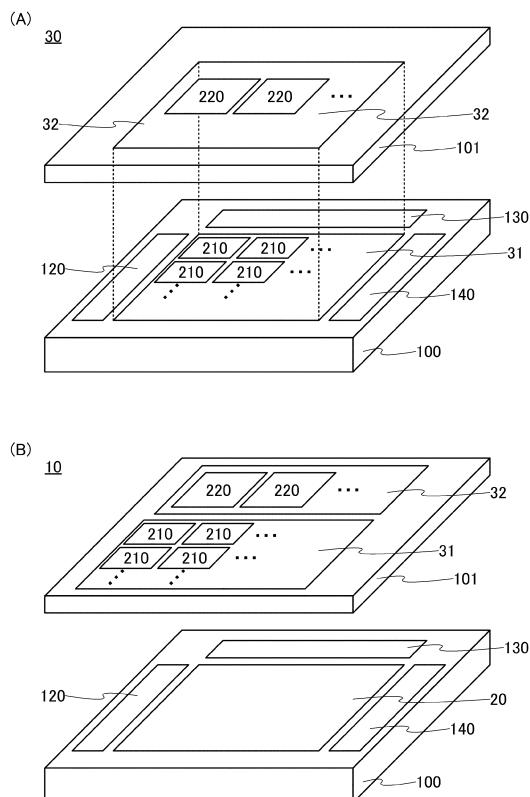

次に、半導体装置 10 のより具体的な構成の一例を、図 3 を用いて説明する。

#### 【0050】

図 3 (A) は、図 1 (A) 乃至 (C) における回路 30 の構成の一例を示す斜視図である。回路 30 は、基板 100 上の回路 31、回路 120、回路 130、回路 140 と、回路 31、回路 120、回路 130、回路 140 上の絶縁層 101 と、絶縁層 101 上の回路 32 を有する。ここでは図示しないが、回路 32 は導電層を介して回路 31 と接続されて50

いる。なお、基板 100 上に、回路 20 ( 図 1 ( A ) 、 ( C ) 参照 ) が設けられていてもよい。

#### 【 0051 】

回路 31 は、複数の回路 210 を有する。回路 210 は、データを記憶する機能を有する回路 ( 以下、記憶回路 210 と表記する ) である。記憶回路 210 は、例えば、DRAM や SRAM などの揮発性メモリ、または NAND 型フラッシュメモリなどの不揮発性メモリによって構成することができる。特に、記憶回路 210 を DRAM で構成すると、回路 31 を高速かつ小面積の記憶回路とすることができますため好ましい。

#### 【 0052 】

回路 32 は、複数の回路 220 を有する。回路 220 は、入力された信号を増幅して出力する機能を有する回路 ( 以下、增幅回路 220 と表記する ) である。ここでは図示しないが、複数の增幅回路 220 はそれぞれ、複数の記憶回路 210 のいずれかと接続されている。增幅回路 220 は、外部 ( 回路 20 や入出力装置など ) から入力されたデータを増幅して、記憶回路 210 に書き込む機能を有する。また、增幅回路 220 は、記憶回路 210 に記憶されたデータを増幅して外部に出力する機能を有する。

10

#### 【 0053 】

回路 120 は、複数の記憶回路 210 のうち特定の記憶回路 210 を選択するための信号を供給する機能を有する駆動回路である。回路 130 は、記憶回路 210 へのデータの書き込み、記憶回路 210 からのデータの読み出しを制御する機能を有する駆動回路である。なお、回路 130 は、記憶回路 210 と接続された配線に所定の電位を供給 ( プリチャージ ) する機能を有していてもよい。回路 140 は、増幅回路 220 を制御するための信号を供給する機能を有する駆動回路である。

20

#### 【 0054 】

ここで、基板 100 は、単結晶半導体を有する基板とすることができます。このような基板としては、単結晶シリコン基板、単結晶ゲルマニウム基板などを用いることができる。また、記憶回路 210 、回路 120 、回路 130 、回路 140 は、基板 100 の一部にチャネル形成領域が形成されるトランジスタにより構成することができる。よって、記憶回路 210 、回路 120 、回路 130 、回路 140 は、チャネル形成領域に単結晶半導体を有するトランジスタによって構成することができる。このようなトランジスタを用いて記憶回路 210 、回路 120 、回路 130 、回路 140 を構成することにより、これらの回路の動作速度を向上させることができる。

30

#### 【 0055 】

一方、増幅回路 220 は、半導体膜にチャネル形成領域が形成されるトランジスタにより構成することができる。例えば、増幅回路 220 は、チャネル形成領域に非単結晶半導体を有するトランジスタによって構成することができる。非単結晶半導体としては、非晶質シリコン、微結晶シリコン、多結晶シリコンなどの非単結晶シリコンや、非晶質ゲルマニウム、微結晶ゲルマニウム、多結晶ゲルマニウムなどの非単結晶ゲルマニウムなどを用いることができる。また、増幅回路 220 は、チャネル形成領域に酸化物半導体を有するトランジスタ ( 以下、OSトランジスタともいう ) によって構成することもできる。

40

#### 【 0056 】

上記のような、半導体膜にチャネル形成領域が形成されるトランジスタは、絶縁層 101 上に形成することができるため、増幅回路 220 を絶縁層 101 上に形成することができます。これにより、図 3 ( A ) に示すように、複数の記憶回路 210 上に絶縁層 101 を設け、絶縁層 101 上に複数の増幅回路 220 を設けた構成とすることができる。すなわち、記憶回路 210 と増幅回路 220 を積層した構成とすることができる。これにより、回路 30 の面積を縮小することができる。

#### 【 0057 】

ここで、増幅回路 220 は、特に OSトランジスタによって構成することが好ましい。酸化物半導体は、シリコン等よりもバンドギャップが広く、真性キャリア密度が低い。そのため、OSトランジスタはオフ電流が極めて小さい。従って、増幅回路 220 に OSトランジ

50

ンジスタを用いることにより、オフ電流が小さく、消費電力が小さい増幅回路 220 を構成することができる。

#### 【0058】

また、OSトランジスタは微細化により高速な動作が可能となる。そのため、増幅回路 220 に OSトランジスタを用いることにより、増幅回路 220 の動作速度を向上させることができる。例えば、増幅回路 220 の動作速度を 10 ns 以下、より好ましくは 5 ns 以下、より好ましくは 1 ns 以下とすることができます。OSトランジスタのチャネル長は、100 nm 以下、好ましくは 60 nm 以下、より好ましくは 40 nm 以下、さらに好ましくは 30 nm 以下とすることができます。

#### 【0059】

ここで、複数の増幅回路 220 のいずれかは、複数の記憶回路 210 のいずれかと重なる領域を有するように配置することができる。また、複数の増幅回路 220 のいずれかは、複数の記憶回路 210 のいずれかの全面と重なる領域を有するように配置することができる。また、複数の増幅回路 220 の全ては、複数の記憶回路 210 のいずれかと重なる領域を有するように配置することができる。また、複数の増幅回路 220 の全ては、複数の記憶回路 210 のいずれかの全面と重なる領域を有するように配置することができる。上記のいずれかの構成をとることにより、回路 30 の面積の増加を抑えつつ、回路 32 を設けることができる。すなわち、回路 30 の面積の増加を抑えつつ、回路 30 に増幅回路を搭載することができる。よって、半導体装置 10 の面積の縮小を図ることができる。なお、増幅回路 220 は、回路 120、回路 130 または回路 140 と重なる領域を有するように配置することもできる。

10

#### 【0060】

なお、ここでは回路 120、回路 130、回路 140 が基板 100 上に設けられた構成を示したが、回路 120、回路 130、回路 140 が絶縁層 101 上に設けられた構成とすることもできる。この場合、回路 120、回路 130、回路 140 が有するトランジスタは、半導体膜にチャネル形成領域が形成されるトランジスタとすることが好ましい。また、当該トランジスタには、高速な動作が可能である OSトランジスタを用いることが好ましい。

20

#### 【0061】

図 3 (B) は、図 2 (A) における半導体装置 10 の構成の一例を示す斜視図である。半導体装置 10 は、基板 100 上の回路 20、回路 120、回路 130、回路 140 と、回路 20、回路 120、回路 130、回路 140 上の絶縁層 101 と、絶縁層 101 上の回路 31、回路 32 を有する。ここで、回路 32 は、回路 20 および回路 31 と接続されている。また、複数の増幅回路 220 はそれぞれ、複数の記憶回路 210 のいずれかと接続されている。

30

#### 【0062】

このように、回路 20 を基板 100 上に設け、回路 31 および回路 32 を絶縁層 101 上に設け、回路 20 と、回路 31 および回路 32 とを積層した構成とすることができる。これにより、半導体装置 10 の面積を縮小することができる。なお、この場合、回路 31 に設けられた複数の記憶回路 210 が有するトランジスタと、回路 32 に設けられた複数の増幅回路 220 が有するトランジスタは、半導体膜にチャネル形成領域が形成されるトランジスタとすることが好ましい。また、当該トランジスタには、オフ電流が小さく高速な動作が可能である OSトランジスタを用いることが好ましい。

40

#### 【0063】

回路 20 は、複数のトランジスタを有する集積回路によって構成することができる。また、当該トランジスタは、基板 100 の一部にチャネル形成領域が形成されるトランジスタにより構成することができる。すなわち、回路 20 は、チャネル形成領域に単結晶半導体を有するトランジスタを有する集積回路によって構成することができる。これにより、回路 20 の動作速度を向上させることができます。

#### 【0064】

50

複数の記憶回路 210 のいずれかは、回路 20 と重なる領域を有するように配置することができる。また、複数の記憶回路 210 の全ては、回路 20 と重なる領域を有するように配置することができる。また、複数の增幅回路 220 のいずれかは、回路 20 と重なる領域を有するように配置することができる。また、複数の增幅回路 220 の全ては、回路 20 と重なる領域を有するように配置することができる。上記のいずれかの構成をとることにより、半導体装置 10 の面積の増加を抑えつつ、回路 31 および回路 32 を設けることができる。すなわち、半導体装置 10 の面積の増加を抑えつつ、半導体装置 10 に記憶回路および增幅回路を搭載することができる。よって、半導体装置 10 の面積の縮小を図ることができる。なお、記憶回路 210 のいずれかは、回路 120、回路 130、または回路 140 と重なる領域を有するように配置することもできる。また、増幅回路 220 のいずれかは、回路 120、回路 130、または回路 140 と重なる領域を有するように配置することもできる。10

#### 【0065】

なお、ここでは回路 120、回路 130、回路 140 が基板 100 上に設けられた構成を示したが、回路 120、回路 130、回路 140 が絶縁層 101 上に設けられた構成とすることもできる。この場合、回路 120、回路 130、回路 140 が有するトランジスタは、半導体膜にチャネル形成領域が形成されるトランジスタとすることが好ましい。また、当該トランジスタには、高速な動作が可能である OS トランジスタを用いることが好ましい。

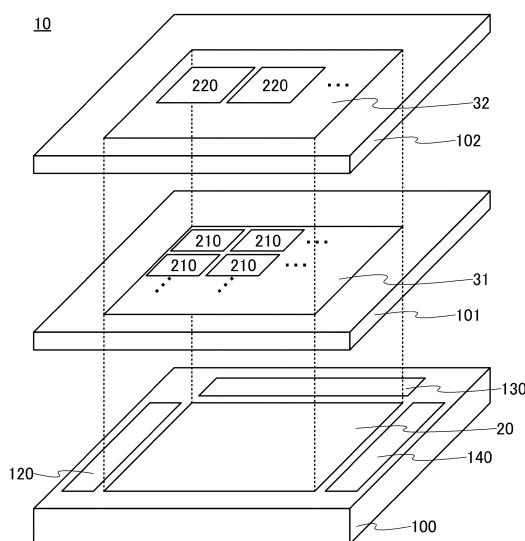

#### 【0066】

また、図 3 (B)においては、回路 31 と回路 32 が同一の層に設けられている構成を示したが、図 4 に示すように、回路 31 と回路 32 が積層された構成とすることもできる。図 4 に示す半導体装置 10 は、基板 100 上の回路 20、回路 120、回路 130、回路 140 と、回路 20、回路 120、回路 130、回路 140 上の絶縁層 101 と、絶縁層 101 上の回路 31 と、回路 31 上の絶縁層 102 と、絶縁層 102 上の回路 32 を有する。なお、回路 32 は、回路 20 および回路 31 と接続されている。20

#### 【0067】

ここで、複数の增幅回路 220 のいずれかは、複数の記憶回路 210 のいずれかと重なる領域を有するように配置することができる。また、複数の增幅回路 220 のいずれかは、複数の記憶回路 210 のいずれかの全面と重なる領域を有するように配置することができる。また、複数の增幅回路 220 の全ては、複数の記憶回路 210 のいずれかと重なる領域を有するように配置することができる。また、複数の增幅回路 220 の全ては、複数の記憶回路 210 のいずれかの全面と重なる領域を有するように配置することができる。上記のいずれかの構成をとることにより、半導体装置 10 の面積の増加を抑えつつ、回路 31 および回路 32 を設けることができる。すなわち、半導体装置 10 の面積の増加を抑えつつ、半導体装置 10 に記憶回路および增幅回路を搭載することができる。よって、半導体装置 10 の面積の縮小を図ることができる。なお、記憶回路 210 のいずれかは、回路 120、回路 130、または回路 140 と重なる領域を有するように配置することもできる。また、増幅回路 220 のいずれかは、回路 120、回路 130、または回路 140 と重なる領域を有するように配置することもできる。30

#### 【0068】

また、ここでは回路 120、回路 130、回路 140 が基板 100 上に設けられた構成を示したが、回路 120、回路 130、回路 140 が絶縁層 101 上、または絶縁層 102 上に設けられた構成とすることもできる。この場合、回路 120、回路 130、回路 140 が有するトランジスタは、半導体膜にチャネル形成領域が形成されるトランジスタとすることが好ましい。また、当該トランジスタには、高速な動作が可能である OS トランジスタを用いることが好ましい。

#### 【0069】

なお、図 4 においては、回路 31 上に回路 32 を設けた構成としたが、回路 32 上に回路 31 を設けた構成とすることもできる。この場合、半導体装置 10 は、絶縁層 102 上の40

10

20

30

40

50

回路 3 2 と、回路 3 2 上の絶縁層 1 0 1 と、絶縁層 1 0 1 上の回路 3 1 を有する構成となる。

#### 【 0 0 7 0 】

以上の通り、本発明の一態様においては、記憶回路を有する回路 3 1 と、増幅回路を有する回路 3 2 が積層された構成、または、回路 2 0 と、回路 3 1 または回路 3 2 とが積層された構成を有する半導体装置を実現することができる。これにより、半導体装置 1 0 の面積の増加を抑えつつ、半導体装置 1 0 に記憶回路および増幅回路を搭載することができる。よって、半導体装置 1 0 の面積の縮小を図ることができる。

#### 【 0 0 7 1 】

また、OSトランジスタを用いて回路を構成することにより、オフ電流が低減され、且つ高速な動作が可能な記憶回路や増幅回路を構成することができる。よって、半導体装置 1 0 の消費電力の低減および動作速度の向上が可能となる。

#### 【 0 0 7 2 】

なお、本実施の形態は他の実施の形態の記載と適宜組み合わせができる。よって、本実施の形態の中で述べる内容（一部の内容でもよい）は、その実施の形態で述べる別的内容（一部の内容でもよい）、及び／又は、一つ若しくは複数の別の実施の形態で述べる内容（一部の内容でもよい）に対して、適用、組み合わせ、又は置き換えなどを行うことが出来る。なお、実施の形態の中で述べる内容とは、各々の実施の形態において、様々な図を用いて述べる内容、又は明細書に記載される文章を用いて述べる内容のことである。また、ある一つの実施の形態において述べる図（一部でもよい）は、その図の別の部分、その実施の形態において述べる別の図（一部でもよい）、及び／又は、一つ若しくは複数の別の実施の形態において述べる図（一部でもよい）に対して、組み合わせることにより、さらに多くの図を構成させることができる。これは、以下の実施の形態においても同様である。

#### 【 0 0 7 3 】

##### （実施の形態 2 ）

本実施の形態では、本発明の一態様に係る構成の、より具体的な構成の一例について説明する。

#### 【 0 0 7 4 】

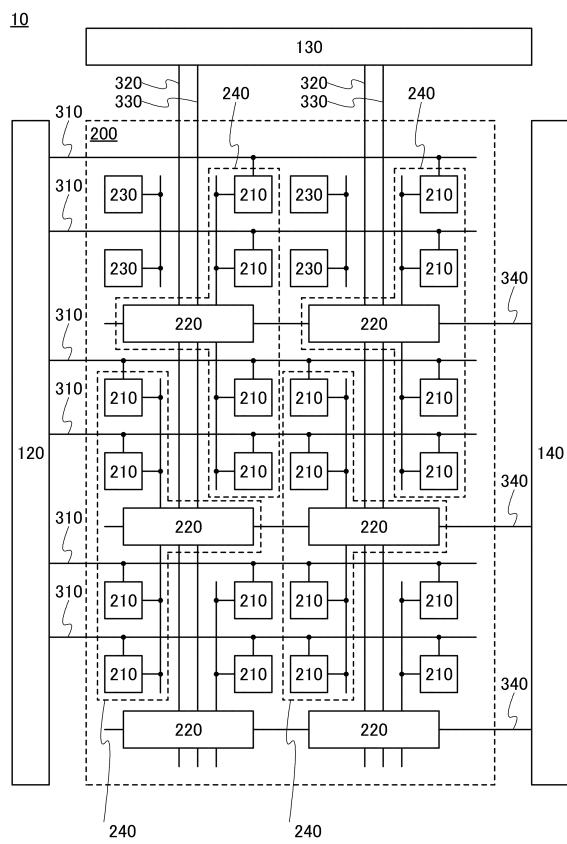

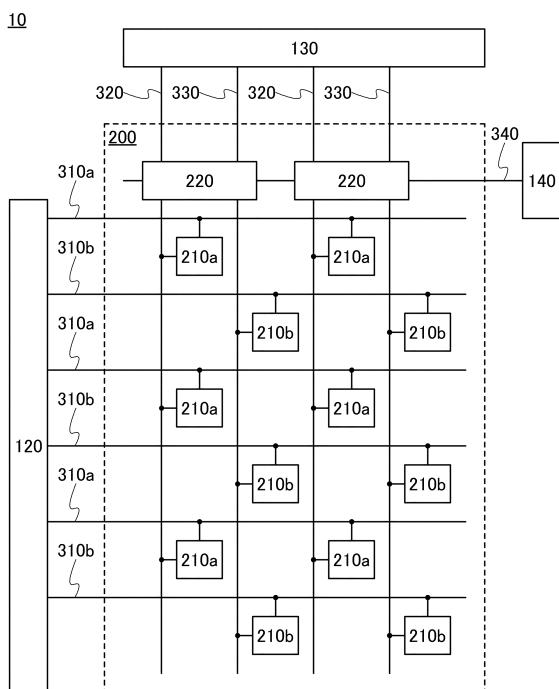

図 5 に、半導体装置 1 0 の構成の一例を示す。半導体装置 1 0 は、回路 1 2 0 、回路 1 3 0 、回路 1 4 0 、回路 2 0 0 を有する。また、回路 2 0 0 は、複数の記憶回路 2 1 0 、複数の増幅回路 2 2 0 を有する。なお、回路 2 0 0 は、図 1 乃至 4 における回路 3 1 および回路 3 2 を包含した回路に相当する。

#### 【 0 0 7 5 】

回路 1 2 0 は、複数の配線 3 1 0 を介して複数の記憶回路 2 1 0 と接続されている。回路 1 2 0 は、複数の記憶回路 2 1 0 のうち特定の行の記憶回路 2 1 0 を選択するための信号を配線 3 1 0 に供給する機能を有する駆動回路である。

#### 【 0 0 7 6 】

回路 1 3 0 は、複数の配線 3 2 0 または複数の配線 3 3 0 を介して、複数の増幅回路 2 2 0 と接続されている。回路 1 3 0 は、記憶回路 2 1 0 に書き込むデータに対応する電位を配線 3 2 0 または配線 3 3 0 に供給する機能と、配線 3 2 0 または配線 3 3 0 の電位から、記憶回路 2 1 0 に記憶されたデータを読み出す機能を有する駆動回路である。また、回路 1 3 0 は、配線 3 2 0 または配線 3 3 0 に所定の電位を供給（プリチャージ）する機能を有していてもよい。

#### 【 0 0 7 7 】

回路 1 4 0 は、複数の配線 3 4 0 を介して、複数の増幅回路 2 2 0 と接続されている。回路 1 4 0 は、配線 3 4 0 を介して増幅回路 2 2 0 に制御信号を供給する機能を有する駆動回路である。なお、配線 3 4 0 はそれぞれ、複数本の配線によって構成することもできる。この場合、当該複数本の配線にはそれぞれ異なる信号を供給することができる。これにより、回路 1 4 0 は、同一の増幅回路 2 2 0 に複数種類の信号を同時に供給することができる。

10

20

30

40

50

きる。

**【 0 0 7 8 】**

回路 200において、同一の行に属する記憶回路 210は、同一の配線 310と接続されている。また、同一の列に属する所定の記憶回路 210は、同一の増幅回路 220と接続されている。なお、ここでは、同一の列に属する4つの記憶回路 210が、同一の増幅回路 220と接続されている例を示すが、これに限定されない。すなわち、1以上の任意の個数の記憶回路 210が同一の増幅回路 220と接続された構成とすることができる。

**【 0 0 7 9 】**

増幅回路 220は、それぞれ複数の記憶回路 210と接続されている。増幅回路 220は、回路 130から配線 320または配線 330に供給された電位を増幅して、記憶回路 210に書き込む機能を有する。また、増幅回路 220は、記憶回路 210に記憶されたデータを増幅して、回路 130に出力する機能を有する。10

**【 0 0 8 0 】**

このように、回路 200は、1つの増幅回路 220と、当該増幅回路 220と接続された複数個（図 5においては4個）の記憶回路 210を有する回路 240が、複数設けられた構成を有する。

**【 0 0 8 1 】**

なお、図 5においては、説明の便宜上、回路 200を複数の記憶回路 210と複数の増幅回路 220が重ならないように図示しているが、実際は、図 3、4に示すように複数の記憶回路 210と複数の増幅回路 220が積層された構成となっている。20

**【 0 0 8 2 】**

また、回路 200は、回路 230を有していてもよい。回路 230は、記憶回路 210と同一工程で作製することができ、回路 210と同様の構成を有する回路とすることができる。回路 230は、増幅回路 220と接続されておらず、データの書き込みや読み出しが行われないダミー回路である。記憶回路 210が形成されない領域に回路 230を設けることにより、回路 210および回路 230上に形成される絶縁層 101（図 3、4 参照）の平坦性を向上させることができる。なお、回路 200が複数の回路 230を有する場合、回路 230同士が配線によって接続されていてもよい。

**【 0 0 8 3 】**

なお、増幅回路 220は、回路 230と重なる領域を有するように配置してもよい。これによって、回路 200の面積を縮小することができる。30

**【 0 0 8 4 】**

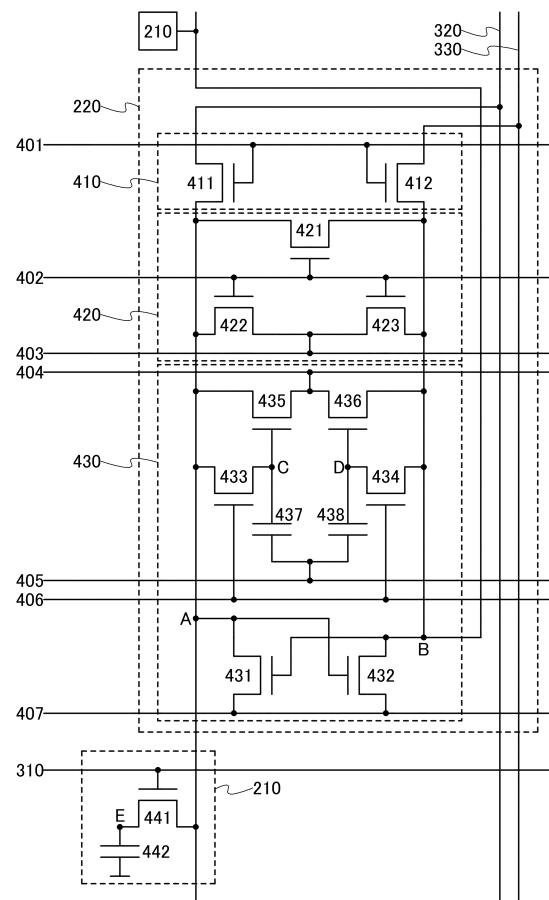

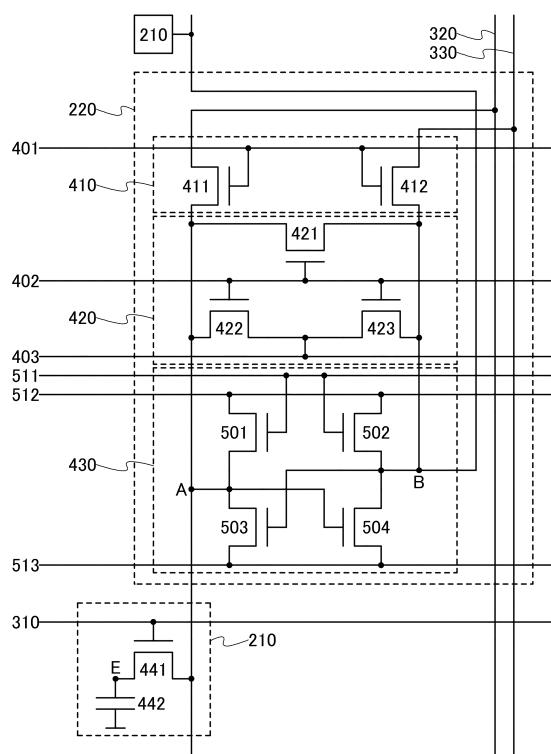

次に、増幅回路 220と、当該増幅回路 220と接続された記憶回路 210の具体的な構成の一例を図 6に示す。

**【 0 0 8 5 】**

増幅回路 220は、回路 410、回路 420、回路 430を有する。回路 410は、増幅回路 220の選択、非選択を制御する選択回路としての機能を有する。回路 420は、ノード A およびノード B の電位をプリチャージするプリチャージ回路としての機能を有する。回路 430は、ノード A およびノード B の電位を増幅する増幅回路としての機能を有する。40

**【 0 0 8 6 】**

回路 410は、トランジスタ 411、412を有する。トランジスタ 411のゲートは配線 401と接続され、ソースまたはドレインの一方は配線 320と接続され、ソースまたはドレインの他方はノード A と接続されている。トランジスタ 412のゲートは配線 401と接続され、ソースまたはドレインの一方は配線 330と接続され、ソースまたはドレインの他方はノード B と接続されている。

**【 0 0 8 7 】**

配線 401の電位を制御してトランジスタ 411、412を導通状態とすることにより、増幅回路 220を選択することができる。

**【 0 0 8 8 】**

10

20

30

40

50

回路 420 は、トランジスタ 421 乃至 423 を有する。トランジスタ 421 のゲートは配線 402 と接続され、ソースまたはドレインの一方はノード A と接続され、ソースまたはドレインの他方はノード B と接続されている。トランジスタ 422 のゲートは配線 402 と接続され、ソースまたはドレインの一方はノード A と接続され、ソースまたはドレインの他方は配線 403 と接続されている。トランジスタ 423 のゲートは配線 402 と接続され、ソースまたはドレインの一方はノード B と接続され、ソースまたはドレインの他方は配線 403 と接続されている。

#### 【 0089 】

配線 402 の電位を制御してトランジスタ 421 乃至 423 を導通状態とすることにより、ノード A およびノード B の電位を配線 403 の電位にプリチャージすることができる。

10

#### 【 0090 】

回路 430 は、トランジスタ 431 乃至 436、容量素子 437、438 を有する。トランジスタ 431 のゲートはノード B と接続され、ソースまたはドレインの一方はノード A と接続され、ソースまたはドレインの他方は配線 407 と接続されている。トランジスタ 432 のゲートはノード A と接続され、ソースまたはドレインの一方はノード B と接続され、ソースまたはドレインの他方は配線 407 と接続されている。トランジスタ 433 のゲートは配線 406 と接続され、ソースまたはドレインの一方はノード A と接続され、ソースまたはドレインの他方はノード C と接続されている。トランジスタ 434 のゲートは配線 406 と接続され、ソースまたはドレインの一方はノード B と接続され、ソースまたはドレインの他方はノード D と接続されている。トランジスタ 435 のゲートはノード C と接続され、ソースまたはドレインの一方はノード A と接続され、ソースまたはドレインの他方は配線 404 と接続されている。トランジスタ 436 のゲートはノード D と接続され、ソースまたはドレインの一方はノード B と接続され、ソースまたはドレインの他方は配線 404 と接続されている。容量素子 437 の一方の電極はノード C と接続され、他方の電極は配線 405 と接続されている。容量素子 438 の一方の電極はノード D と接続され、他方の電極は配線 405 と接続されている。

20

#### 【 0091 】

回路 430 は、ノード A の電位を增幅して、記憶回路 210 または配線 320 に供給する機能を有する。また、回路 430 は、ノード B の電位を增幅して、記憶回路 210 または配線 330 に供給する機能を有する。

30

#### 【 0092 】

記憶回路 210 は、トランジスタ 441、容量素子 442 を有する。トランジスタ 441 のゲートは配線 310 と接続され、ソースまたはドレインの一方はノード A と接続され、ソースまたはドレインの他方はノード E と接続されている。容量素子 442 の一方の電極はノード E と接続され、他方の電極は所定の電位を供給する機能を有する配線と接続されている。なお、所定の電位を供給する機能を有する配線は高電位電源線であっても低電位電源線（接地線など）であってもよく、また、所定の電位は一定の電位であっても変動する電位であってもよい。また、所定の電位の大きさは 0 ボルトに限定されない。以上のように、記憶回路 210 は DRAM セルを構成している。なお、記憶回路 210 は、SRAM セルなどにより構成することもできる。

40

#### 【 0093 】

記憶回路 210 において、配線 310 の電位を制御してトランジスタ 441 を導通状態とすることにより、ノード A の電位をノード E に供給することができる（データの書き込み）。その後、配線 310 の電位を制御してトランジスタ 441 を非導通状態とすることにより、ノード E の電位を保持することができる（データの保持）。また、ノード A を浮遊状態にした上で、配線 310 の電位を制御してトランジスタ 441 を導通状態とすることにより、ノード E の電位をノード A に供給することができる（データの読み出し）。

#### 【 0094 】

なお、配線 401 乃至 407 は、複数の配線によって構成された配線 340（図 5 参照）に対応し、回路 140 と接続されている。そして配線 401 乃至 407 にはそれぞれ、回

50

路 1 4 0 から制御信号が供給される。

**【 0 0 9 5 】**

なお、上記において、トランジスタのソースとは、活性層として機能する半導体膜の一部であるソース領域、或いは上記半導体膜に接続されたソース電極を意味する。同様に、トランジスタのドレインとは、上記半導体膜の一部であるドレイン領域、或いは上記半導体膜に接続されたドレイン電極を意味する。また、ゲートはゲート電極を意味する。

**【 0 0 9 6 】**

また、トランジスタが有するソースとドレインは、トランジスタの導電型及び各端子に与えられる電位の高低によって、その呼び方が入れ替わる。一般的に、nチャネル型トランジスタでは、低い電位が与えられる端子がソースと呼ばれ、高い電位が与えられる端子がドレインと呼ばれる。また、pチャネル型トランジスタでは、低い電位が与えられる端子がドレインと呼ばれ、高い電位が与えられる端子がソースと呼ばれる。本明細書では、便宜上、ソースとドレインとが固定されているものと仮定して、トランジスタの接続関係を説明する場合があるが、実際には上記電位の関係に従ってソースとドレインの呼び方が入れ替わる。

10

**【 0 0 9 7 】**

トランジスタ 4 1 1、4 1 2、4 2 1 乃至 4 2 3、4 3 1 乃至 4 3 6 は、半導体膜にチャネル形成領域が形成されるトランジスタにより構成することが好ましい。これにより、增幅回路 2 2 0 を、記憶回路 2 1 0 や回路 2 0 上に積層することができる（図 3、4 参照）。これにより、半導体装置 1 0 の面積を縮小することができる。なお、半導体膜の材料としては、実施の形態 1 に記載の材料を適宜用いることができる。

20

**【 0 0 9 8 】**

また、トランジスタ 4 1 1、4 1 2、4 2 1 乃至 4 2 3、4 3 1 乃至 4 3 6 は、OSトランジスタとすることが好ましい。OSトランジスタはオフ電流が極めて小さいため、トランジスタ 4 1 1、4 1 2、4 2 1 乃至 4 2 3、4 3 1 乃至 4 3 6 を OSトランジスタとすることにより、これらのトランジスタが非導通状態であるとき、ノード A およびノード B への電荷のリークを極めて少なくすることができる。よって、ノード A およびノード B の意図しない電位の変動を極めて小さくすることができる。

**【 0 0 9 9 】**

また、OSトランジスタは微細化により高速な動作が可能となる。そのため、トランジスタ 4 1 1、4 1 2、4 2 1 乃至 4 2 3、4 3 1 乃至 4 3 6 を OSトランジスタによって構成することにより、增幅回路 2 2 0 の動作速度を向上させることができる。この場合、增幅回路 2 2 0 の動作速度を 1 0 n s 以下、好ましくは 5 n s 以下、より好ましくは 1 n s 以下とすることができる。OSトランジスタのチャネル長は、1 0 0 n m 以下、好ましくは 6 0 n m 以下、より好ましくは 4 0 n m 以下、さらに好ましくは 3 0 n m 以下とすることができる。

30

**【 0 1 0 0 】**

トランジスタ 4 4 1 は、チャネル形成領域に単結晶半導体を有するトランジスタによって構成することができる。具体的には、単結晶半導体を有する基板にチャネル形成領域が形成されるトランジスタにより構成することができる。このようなトランジスタを用いて記憶回路 2 1 0 を構成することにより、記憶回路 2 1 0 の動作速度を向上させることができます。なお、単結晶半導体の材料としては、実施の形態 1 に記載の材料を適宜用いることができる。

40

**【 0 1 0 1 】**

また、トランジスタ 4 4 1 は、半導体膜にチャネル形成領域が形成されるトランジスタにより構成することができる。これにより、記憶回路 2 1 0 を、回路 2 0 や増幅回路 2 2 0 上に積層することができる。これにより、半導体装置 1 0 の面積を縮小することができる。なお、半導体膜の材料としては、実施の形態 1 に記載の材料を適宜用いることができる。

**【 0 1 0 2 】**

50

また、トランジスタ441は、OSトランジスタとすることができます。この場合、トランジスタ441のオフ電流を極めて小さくすることができるため、データの保持期間においてノードEの電位を長時間にわたって維持することができる。そのため、所定の周期で再度書き込みを行う動作（リフレッシュ動作）が不要となるか、または、リフレッシュ動作の頻度を極めて低くすることができる。

#### 【0103】

また、OSトランジスタは微細化により高速な動作が可能となる。そのため、トランジスタ441をOSトランジスタによって構成することにより、記憶回路210の動作速度を向上させることができる。この場合、記憶回路210の書き込み速度を10ns以下、好みしくは5ns以下、より好みしくは1ns以下とすることができる。OSトランジスタのチャネル長は、100nm以下、好みしくは60nm以下、より好みしくは40nm以下、さらに好みしくは30nm以下とすることができる。10

#### 【0104】

なお、図6においてはここではトランジスタ411、412、421乃至423、431乃至436、441がnチャネル型である場合を示すが、これに限られず、トランジスタ411、412、421乃至423、431乃至436、441はそれぞれnチャネル型であってもpチャネル型であってもよい。

#### 【0105】

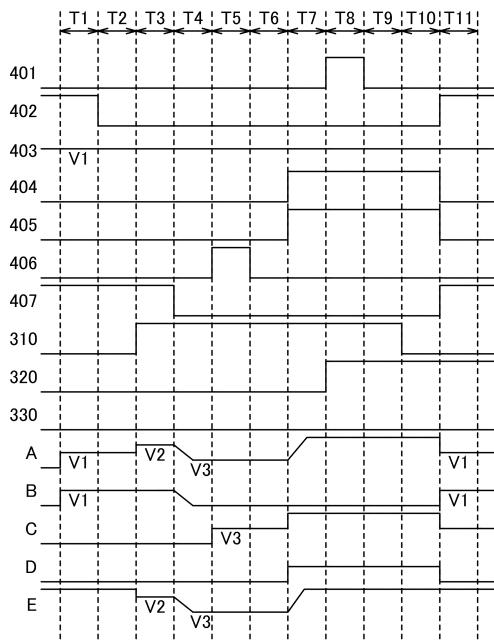

次に、図6に示す增幅回路220および記憶回路210の動作の一例を説明する。

#### 【0106】

<記憶回路からの読み出し>

まず、記憶回路210からデータを読み出す際の動作について、図7のタイミングチャートを用いて説明する。なお、ここでは一例として、記憶回路210にハイレベルのデータが記憶されている場合（ノードEの電位がハイレベルである場合）について説明する。

#### 【0107】

まず、期間T1において、配線403の電位をハイレベルとローレベルの中間の電位（V1）とした状態で、配線402の電位をハイレベルとし、トランジスタ421、422、423を導通状態とする。これにより、ノードAおよびノードBの電位がV1にプリチャージされる。なお、配線407はハイレベルとなっている。

#### 【0108】

次に、期間T2において、配線402の電位をローレベルとし、トランジスタ421、422、423を非導通状態とする。これにより、V1にプリチャージされたノードAおよびノードBは浮遊状態となる。30

#### 【0109】

次に、期間T3において、配線310の電位をハイレベルとし、トランジスタ441を導通状態とする。これにより、ノードEとノードAが導通状態となり、ノードAの電位は上昇してV2となり、ノードEの電位は下降してV2となる。一方、ノードBの電位はV1に維持されている。そのため、ノードAの電位がノードBの電位よりも高い状態となる。

#### 【0110】

また、ノードAはトランジスタ431を介して配線407と接続されており、ノードBはトランジスタ432を介して配線407と接続されているため、ノードAおよびノードBの電位は配線407の電位（ローレベル）に近づく。ここで、ノードBの電位はノードAの電位よりも低いため、ノードBの電位はノードAの電位よりも早くローレベルに達する。そして、ノードBの電位がローレベルとなると、トランジスタ431のゲートの電位もローレベルとなり、トランジスタ431は非導通状態となる。その結果、ノードAの電位の下降が止まり、ノードAの電位はノードBの電位（ローレベル）よりも高いV3となる（期間T4）。また、期間T4において、配線407の電位をローレベルとする。40

#### 【0111】

次に、期間T5において、配線406の電位をハイレベルとし、トランジスタ433、434を導通状態とする。これにより、ノードAの電位がトランジスタ433を介してノー

10

20

30

40

50

ドCに供給され、ノードBの電位がトランジスタ434を介してノードDに供給される。その結果、ノードCの電位はV3となり、ノードDの電位はローレベルとなる。

#### 【0112】

次に、期間T6において、配線406の電位をローレベルとし、トランジスタ433、434を非導通状態とする。これにより、ノードCおよびノードDは浮遊状態となる。

#### 【0113】

次に、期間T7において、配線404の電位をハイレベルとする。また、配線405の電位をハイレベルとすることにより、ノードCおよびノードDの電位を上昇させる。これにより、トランジスタ435は導通状態となり、ノードAの電位は配線404の電位に近づく。この結果、ノードAの電位はハイレベルとなる。

10

#### 【0114】

なお、ノードDの電位の上昇に伴い、トランジスタ436も導通状態に近い状態となることがある。この場合、配線404の電位（ハイレベル）がトランジスタ436を介してノードBに供給され得る。しかしながら、この時、ノードAの電位はハイレベルであるため、トランジスタ432のゲートもハイレベルとなり、トランジスタ432は導通状態となる。その結果、ノードBの電位は配線407の電位（ローレベル）に近づき、ノードBの電位はローレベルに維持される。

#### 【0115】

次に、期間T8において、配線401の電位をハイレベルとし、トランジスタ411、412を導通状態とする。これにより、ノードAの電位（ハイレベル）が配線320に供給され、ノードBの電位（ローレベル）が配線330に供給される。ここで、配線320の電位は、記憶回路210に格納されていたデータ（ハイレベル）に対応する。従って、配線320の電位を読み取ることにより、記憶回路210に格納されたデータの読み出しが可能となる。

20

#### 【0116】

次に、期間T9において、配線401の電位をローレベルとする。これにより、ノードAおよびノードBは浮遊状態となる。

#### 【0117】

次に、期間T10において、配線310の電位をローレベルとすることにより、トランジスタ441を非導通状態とする。これにより、ノードEにノードAの電位（ハイレベル）が保持される。このような動作により、読み出し前に記憶回路210に格納されていたデータ（ハイレベル）のリフレッシュを行うことができる。

30

#### 【0118】

次に、期間T11において、配線404、405の電位をローレベルとする。また、配線402をハイレベルとし、ノードAおよびノードBの電位をV1にプリチャージする。また、配線407の電位をハイレベルとする。

#### 【0119】

以上の動作により、記憶回路210から出力された電位を増幅して読み出すことができる。

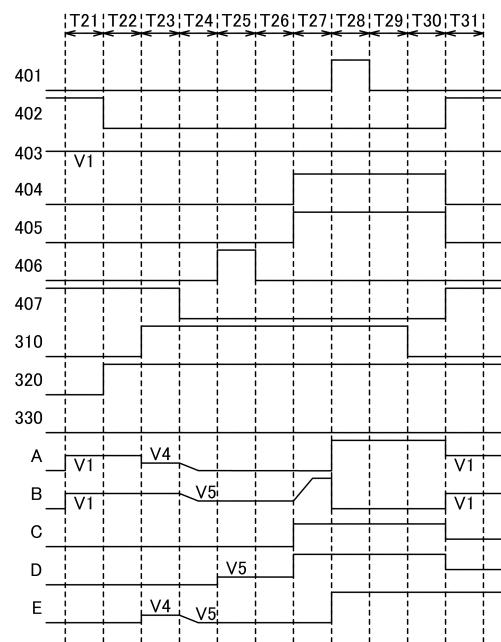

#### 【0120】

40

#### <記憶回路への書き込み>

次に、記憶回路210にデータを書き込む際の動作について、図8のタイミングチャートを用いて説明する。なお、ここでは一例として、記憶回路210に記憶されているローレベルのデータをハイレベルのデータに書き換える場合の動作について説明する。

#### 【0121】

まず、期間T21において、配線403の電位をV1とした状態で、配線402の電位をハイレベルとし、トランジスタ421、422、423を導通状態とする。これにより、ノードAおよびノードBの電位がV1にプリチャージされる。なお、配線407はハイレベルとなっている。

#### 【0122】

50

次に、期間T22において、配線402の電位をローレベルとし、トランジスタ421、422、423を非導通状態とする。これにより、V1にプリチャージされたノードAおよびノードBは浮遊状態となる。また、配線320の電位をハイレベルとする。配線320の電位は、記憶回路210に書き込むデータに対応する。

#### 【0123】

次に、期間T23において、配線310の電位をハイレベルとし、トランジスタ441を導通状態とする。これにより、ノードEとノードAが導通状態となり、ノードAの電位は下降してV4となり、ノードEの電位は上昇してV4となる。一方、ノードBの電位はV1に維持されている。そのため、ノードAの電位がノードBの電位よりも低い状態となる。

10

#### 【0124】

また、ノードAはトランジスタ431を介して配線407と接続されており、ノードBはトランジスタ432を介して配線407と接続されているため、ノードAおよびノードBの電位は配線407の電位（ローレベル）に近づく。ここで、ノードAの電位はノードBの電位よりも低いため、ノードAの電位はノードBの電位よりも早くローレベルに達する。そして、ノードAの電位がローレベルとなると、トランジスタ432のゲートの電位もローレベルとなり、トランジスタ432は非導通状態となる。その結果、ノードBの電位の下降が止まり、ノードBの電位はノードAの電位（ローレベル）よりも高いV5となる（期間T24）。また、期間T24において、配線407の電位をローレベルとする。

#### 【0125】

20

次に、期間T25において、配線406の電位をハイレベルとし、トランジスタ433、434を導通状態とする。これにより、ノードAの電位がトランジスタ433を介してノードCに供給され、ノードBの電位がトランジスタ434を介してノードDに供給される。その結果、ノードCの電位はローレベルとなり、ノードDの電位はV5となる。

#### 【0126】

次に、期間T26において、配線406の電位をローレベルとし、トランジスタ433、434を非導通状態とする。これにより、ノードCおよびノードDは浮遊状態となる。

#### 【0127】

次に、期間T27において、配線404の電位をハイレベルとする。また、配線405の電位をハイレベルとすることにより、ノードCおよびノードDの電位を上昇させる。これにより、トランジスタ436は導通状態となり、ノードBの電位は配線404の電位に近づく。この結果、ノードBの電位はハイレベルとなる。

30

#### 【0128】

なお、ノードCの電位の上昇に伴い、トランジスタ435も導通状態に近い状態となることがある。この場合、配線404の電位（ハイレベル）がトランジスタ435を介してノードAに供給され得る。しかしながら、この時、ノードBの電位はハイレベルであるため、トランジスタ431のゲートもハイレベルとなり、トランジスタ431は導通状態となる。その結果、ノードAの電位は配線407の電位（ローレベル）に近づき、ノードAの電位はローレベルに維持される。

#### 【0129】

40

次に、期間T28において、配線401の電位をハイレベルとし、トランジスタ411、412を導通状態とする。これにより、配線320の電位（ハイレベル）がノードAおよびノードEに供給され、配線330の電位（ローレベル）がノードBに供給される。なお、配線320の電位（ハイレベル）は、記憶回路210に書き込むデータに対応する。

#### 【0130】

次に、期間T29において、配線401の電位をローレベルとする。これにより、ノードAおよびノードBは浮遊状態となる。

#### 【0131】

次に、期間T30において、配線310の電位をローレベルとすることにより、トランジスタ441を非導通状態とする。これにより、ノードEにノードAの電位（ハイレベル）

50

が保持される。このような動作により、記憶回路 210 にデータ（ハイレベル）を書き込みることができる。

**【0132】**

次に、期間 T31において、配線 404、405 の電位をローレベルとする。また、配線 402 をハイレベルとし、ノード A およびノード B の電位を V1 にプリチャージする。また、配線 407 の電位をハイレベルとする。

**【0133】**

以上の動作により、記憶回路 210 に記憶されたデータの書き換えを行うことができる。

**【0134】**

なお、增幅回路 220 の構成は、図 6 に限られない。例えば、增幅回路 220 を図 9 に示す構成とすることもできる。図 9 における増幅回路 220 の構成は、回路 430 の構成が異なる点を除いて、図 6 における増幅回路 220 と同様である。10

**【0135】**

図 9 における回路 430 は、トランジスタ 501 乃至 504 を有する。トランジスタ 501 のゲートは配線 511 と接続され、ソースまたはドレインの一方は配線 512 と接続され、ソースまたはドレインの他方はノード A と接続されている。トランジスタ 502 のゲートは配線 511 と接続され、ソースまたはドレインの一方は配線 512 と接続され、ソースまたはドレインの他方はノード B と接続されている。トランジスタ 503 のゲートはノード B と接続され、ソースまたはドレインの一方はノード A と接続され、ソースまたはドレインの他方は配線 513 と接続されている。トランジスタ 504 のゲートはノード A と接続され、ソースまたはドレインの一方はノード B と接続され、ソースまたはドレインの他方は配線 513 と接続されている。20

**【0136】**

図 9 における回路 430 は、図 6 における回路 430 と同様、ノード A に供給された電位を増幅して、記憶回路 210 または配線 320 に供給する機能と、ノード B に供給された電位を増幅して、記憶回路 210 または配線 330 に供給する機能を有する。

**【0137】**

なお、トランジスタ 501 乃至 504 には、トランジスタ 431 乃至 436（図 6 参照）と同様の材料を用いることができるが、特に、トランジスタ 501 乃至 504 は OS トランジスタとすることが好ましい。30

**【0138】**

また、半導体装置 10 は、図 10 に示す構成とすることもできる。図 10 における半導体装置 10 は、回路 200 の構成が異なる点を除いて、図 5 における半導体装置 10 と同様の構成を有する。

**【0139】**

図 10 における回路 200 は、複数の記憶回路 210a、複数の記憶回路 210b、複数の増幅回路 220 を有する。ここで、記憶回路 210a は、奇数行奇数列に設けられた記憶回路であり、記憶回路 210b は、偶数行偶数列に設けられた記憶回路である。また、記憶回路 210a は、奇数行の配線 310a と接続され、記憶回路 210b は、偶数行の配線 310b と接続されている。40

**【0140】**

増幅回路 220 は、それぞれ複数の記憶回路 210 と接続されている。具体的には、増幅回路 220 は、2 列の記憶回路 210 と接続されている。ここでは、増幅回路 220 が、奇数列の複数の記憶回路 210a および偶数列の複数の記憶回路 210b と接続されている例を示す。

**【0141】**

上記の構成を有する回路 200 においても、図 5 における回路 200 と同様、配線 320 または配線 330 に供給された電位を増幅して、記憶回路 210a または記憶回路 210b に書き込むことができる。また、記憶回路 210a または記憶回路 210b に記憶されたデータを増幅して読み出すことができる。50

**【 0 1 4 2 】**

なお、ここでは、説明の便宜上、回路 200 を、複数の增幅回路 220 が複数の記憶回路 210a および複数の記憶回路 210b と重ならないように図示しているが、実際は、図 3(A)、4 に示すように、複数の增幅回路 220 と、複数の記憶回路 210a および複数の記憶回路 210b とが積層された構成となっている。すなわち、複数の增幅回路 220 は、絶縁層を介して複数の記憶回路 210a および複数の記憶回路 210b 上に設けられている。

**【 0 1 4 3 】**

以上の通り、本発明の一態様においては、記憶回路を有する回路 31 と、增幅回路を有する回路 32 が積層された構成、または、回路 20 と、回路 31 または回路 32 とが積層された構成を有する半導体装置を実現することができる。これにより、半導体装置 10 の面積の増加を抑えつつ、半導体装置 10 に記憶回路および增幅回路を搭載することができる。よって、半導体装置 10 の面積の縮小を図ることができる。10

**【 0 1 4 4 】**

また、OSトランジスタを用いて回路を構成することにより、オフ電流が低減され、且つ高速な動作が可能な記憶回路や增幅回路を構成することができる。よって、半導体装置 10 の消費電力の低減および動作速度の向上が可能となる。

**【 0 1 4 5 】**

なお、本実施の形態は他の実施の形態の記載と適宜組み合わせることができる。

**【 0 1 4 6 】****( 実施の形態 3 )**

本実施の形態では、記憶回路や增幅回路などに用いることができるトランジスタの構成について説明する。

**【 0 1 4 7 】**

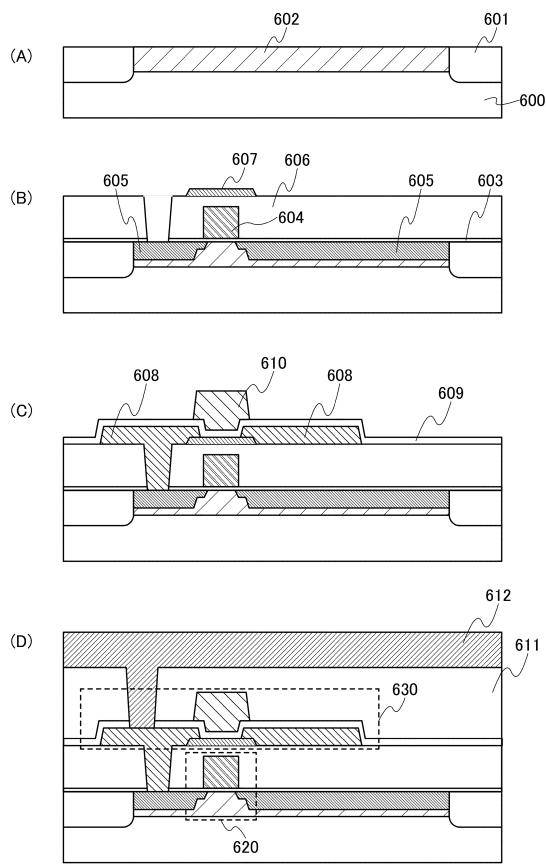

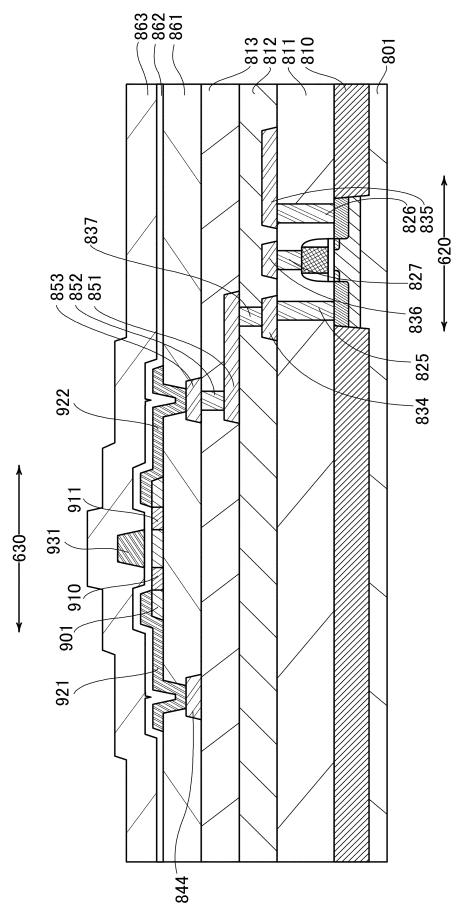

図 11 に、トランジスタ 620 とトランジスタ 630 とを積層した構造を有する半導体装置の作製方法の一例を示す。ここでは、トランジスタ 620 がチャネル形成領域に単結晶半導体を有するトランジスタであり、トランジスタ 630 が OSトランジスタである場合について説明する。

**【 0 1 4 8 】**

まず、半導体基板 600 に、素子分離用の絶縁物 601 と N型のウェル 602 を形成する30

( 図 11 ( A ) )。

**【 0 1 4 9 】**

次に、ゲート絶縁膜 603 とゲート電極 604 を形成し、また、ウェル 602 に P型の不純物領域 605 を設ける。不純物領域 605 上には、不純物領域 605 よりも導電性の高い材料(シリサイドなど)を有する層を積層してもよい。また、不純物領域 605 はエクステンション領域を有してもよい。

**【 0 1 5 0 】**

次に、絶縁層 606 を形成する。絶縁層 606 は单層でも多層でもよい。また、絶縁層 606 は、絶縁層 606 の上に設けられる層へ酸素を供給する機能と、絶縁層 606 の下に設けられた層から絶縁層 606 の上に設けられる層への水素や水の浸入を遮断する機能と、を有する層であることが好ましい。40

**【 0 1 5 1 】**

次に、絶縁層 606 上に酸化物半導体層 607 を形成する(図 11 ( B ) )。その後、ゲート絶縁膜 603 および絶縁層 606 に、不純物領域 605 の一方に達するコンタクトホールを形成する。

**【 0 1 5 2 】**

次に、導電性材料を堆積して、コンタクトホールに導電性材料を埋め込む。このとき、酸化物半導体層 607 は、導電性材料で覆われる。導電性材料は、单層でも多層でもよい。そして、導電性材料を選択的にエッチングして、配線 608 を形成する。なお、コンタクトホールに不純物領域 605 の一方と接する導電層を形成し、当該導電層と配線 608 の50

一方が接する構造としてもよい。

**【0153】**

次に、配線608を覆うゲート絶縁膜609を形成する。さらに、ゲート絶縁膜609上に導電性材料を堆積する。導電性材料は、単層でも多層でもよい。また、導電性材料は、導電性材料の上に設けられる層から導電性材料の下に設けられた層への水素や水の浸入を遮断する機能を有することが好ましい。そして、導電性材料を選択的にエッチングして、ゲート電極610を形成する(図11(C))。

**【0154】**

次に、絶縁層611を堆積する。そして、ゲート絶縁膜609および絶縁層611に、配線608の一方に達するコンタクトホールを形成し、当該コンタクトホールを導電性材料で埋め、配線612を形成する(図11(D))。なお、当該コンタクトホールに配線608の一方と接する導電層を形成し、当該導電層と配線612が接する構造としてもよい。また、配線612は、単層でも多層でもよい。

10

**【0155】**

このようにして、チャネル形成領域に単結晶半導体を有するトランジスタ620と、OSトランジスタであるトランジスタ630が積層された構成を有する半導体装置を作製することができる。

**【0156】**

なお、図11(D)において、不純物領域605の一方と配線608の一方が接続されている。すなわち、トランジスタ620のソースまたはドレインの一方とトランジスタ630のソースまたはドレインの一方が接続されている。このような構成は、図6、9に示すトランジスタに適用することができる。例えば、トランジスタ620は図6、9におけるトランジスタ441などに対応し、トランジスタ630は図6におけるトランジスタ411、412、421乃至423、431乃至436、図9におけるトランジスタ411、412、421乃至423、501乃至504などに対応する。また、トランジスタ620は、図1乃至4における回路20(例えば、回路20が有する集積回路など)に用いることができる。

20

**【0157】**

なお、トランジスタ620とトランジスタ630の接続関係は図11に示すものに限られない。例えば、図12(A)に示すように、不純物領域605の一方とゲート電極610が配線612を介して接続された構成とすることもできる。これにより、トランジスタ620のソースまたはドレインの一方とトランジスタ630のゲートが接続された構成を得ることができる。例えば、図12(A)におけるトランジスタ620は図6、9におけるトランジスタ441などに対応し、トランジスタ630は図6におけるトランジスタ432、図9におけるトランジスタ504などに対応する。

30

**【0158】**

また、図12(B)に示すように、ゲート電極604と配線608の一方が接続された構成とすることもできる。これにより、トランジスタ620のゲートとトランジスタ630のソースまたはドレインの一方が接続された構成を得ることができる。

**【0159】**

40

また、図12(C)に示すように、ゲート電極604とゲート電極610が配線612を介して接続された構成とすることもできる。これにより、トランジスタ620のゲートとトランジスタ630のゲートが接続された構成を得ることができる。

**【0160】**

なお、図11(D)、図12(A)乃至(C)に示すように、トランジスタ620とトランジスタ630とは、絶縁層606を介して、互いに重なる領域を有していてもよい。例えば、図11(D)、図12(A)に示すように、トランジスタ620のチャネル形成領域とトランジスタ630のチャネル形成領域とは、絶縁層606を介して、互いに重なる領域を有していてもよい。また、図11(D)、図12(A)に示すように、トランジスタ620のゲート電極604とトランジスタ630のゲート電極610とは、絶縁層60

50

6を介して、互いに重なる領域を有していてもよい。これにより、トランジスタ620およびトランジスタ630を有する回路の面積を縮小することができる。

#### 【0161】

なお、図11(D)及び図12(A)乃至(C)に示すトランジスタの積層構造は、図1乃至6、9、10に示す各種の回路に適宜用いることができる。

#### 【0162】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することができる。

#### 【0163】

(実施の形態4)

本実施の形態では、記憶回路または論理回路に用いることができるトランジスタの構成について説明する。

10

#### 【0164】

<半導体装置の断面構造の例>

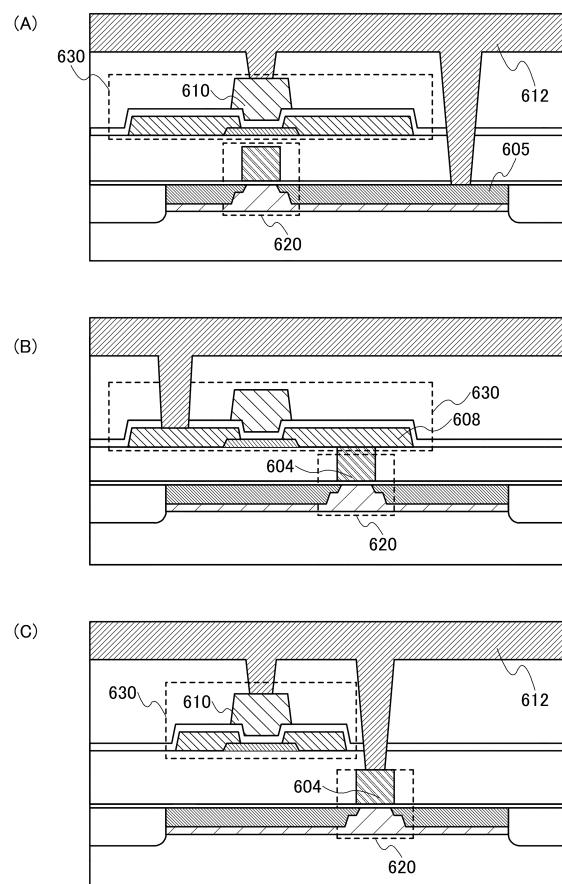

図13に、トランジスタ620、630の構成の一例を示す。なお、図13では、OSトランジスタであるトランジスタ630が、単結晶のシリコン基板にチャネル形成領域を有するトランジスタ(以下、Siトランジスタともいう)であるトランジスタ620上に形成されている場合を例示している。なお、このようにSiトランジスタとOSトランジスタが積層された構成は、図1乃至6、9、10に示す各回路が有するトランジスタに適宜用いることができる。なお、本実施の形態では、図11(D)と同様に、トランジスタ620のソースまたはドレインの一方とトランジスタ630のソースまたはドレインの一方が接続された構成を示すが、これに限られない。トランジスタ620のソースまたはドレインの一方とトランジスタ630のゲートが接続されていてもよいし(図12(A)参照)、トランジスタ620のゲートとトランジスタ630のソースまたはドレインの一方が接続されていてもよいし(図12(B)参照)、トランジスタ620のゲートとトランジスタ630のゲートが接続されていてもよい(図12(C)参照)。

20

#### 【0165】

トランジスタ620は、非晶質、微結晶、多結晶または単結晶である、シリコン又はゲルマニウムなどの半導体膜または半導体基板に、チャネル形成領域を有していても良い。或いは、トランジスタ620は、酸化物半導体膜または酸化物半導体基板に、チャネル形成領域を有していても良い。全てのトランジスタが酸化物半導体膜または酸化物半導体基板に、チャネル形成領域を有している場合、トランジスタ630はトランジスタ620上に積層されなくとも良く、トランジスタ630とトランジスタ620とは、同一の層に形成されていても良い。

30

#### 【0166】

シリコンの薄膜を用いてトランジスタ620を形成する場合、当該薄膜には、プラズマCVD(Chemical Vapor Deposition)法などの気相成長法若しくはスパッタリング法で作製された非晶質シリコン、非晶質シリコンにレーザーを照射する等の処理により結晶化させた多結晶シリコン、単結晶シリコンウェハに水素イオン等を注入して表層部を剥離した単結晶シリコンなどを用いることができる。

40

#### 【0167】

トランジスタ620が形成される半導体基板801は、例えば、シリコン基板、ゲルマニウム基板、シリコンゲルマニウム基板等を用いることができる。図13では、単結晶シリコン基板を半導体基板801として用いる場合を例示している。

#### 【0168】

また、トランジスタ620は、素子分離法により電気的に分離されている。素子分離法として、選択酸化法(LOCOS法: Local Oxidation of Silicon法)、トレンチ分離法(STI法: Shallow Trench Isolation)等を用いることができる。図13では、トレンチ分離法を用いてトランジスタ620を電気的に分離する場合を例示している。具体的に、図13では、半導体基板801にエッティング等によりトレンチを形成した後、酸化珪素などを含む絶縁物を当該トレンチに

50

埋め込むことで形成される素子分離領域 810 により、トランジスタ 620 を素子分離させる場合を例示している。

**【0169】**

トランジスタ 620 上には、絶縁膜 811 が設けられている。絶縁膜 811 には開口部が形成されている。そして、上記開口部には、トランジスタ 620 のソースまたはドレインにそれぞれ電気的に接続されている導電膜 825 及び導電膜 826 と、トランジスタ 620 のゲートに電気的に接続されている導電膜 827 とが、形成されている。

**【0170】**

そして、導電膜 825 は、絶縁膜 811 上に形成された導電膜 834 に電気的に接続されており、導電膜 826 は、絶縁膜 811 上に形成された導電膜 835 に電気的に接続されており、導電膜 827 は、絶縁膜 811 上に形成された導電膜 836 に電気的に接続されている。10

**【0171】**

導電膜 834 乃至導電膜 836 上には、絶縁膜 812 が形成されている。絶縁膜 812 には開口部が形成されており、上記開口部に、導電膜 834 に電気的に接続された導電膜 837 が形成されている。そして、導電膜 837 は、絶縁膜 812 上に形成された導電膜 851 に、電気的に接続されている。

**【0172】**

また、導電膜 851 上には、絶縁膜 813 が形成されている。絶縁膜 813 には開口部が形成されており、上記開口部に、導電膜 851 に電気的に接続された導電膜 852 が形成されている。そして、導電膜 852 は、絶縁膜 813 上に形成された導電膜 853 に、電気的に接続されている。また、絶縁膜 813 上には、導電膜 844 が形成されている。20

**【0173】**

導電膜 853 及び導電膜 844 上には絶縁膜 861 が形成されている。そして、図 13 では、絶縁膜 861 上にトランジスタ 630 が形成されている。

**【0174】**

トランジスタ 630 は、絶縁膜 861 上に、酸化物半導体を含む半導体膜 901 と、半導体膜 901 上の、ソースまたはドレインとして機能する導電膜 921 及び導電膜 922 と、半導体膜 901、導電膜 921 及び導電膜 922 上のゲート絶縁膜 862 と、ゲート絶縁膜 862 上に位置し、導電膜 921 と導電膜 922 の間において半導体膜 901 と重なっているゲート電極 931 と、を有する。なお、導電膜 922 は、絶縁膜 861 に設けられた開口部において、導電膜 853 に電気的に接続されている。30

**【0175】**

そして、トランジスタ 630 では、半導体膜 901 において、導電膜 921 に重なる領域と、ゲート電極 931 に重なる領域との間に、領域 910 が存在する。また、トランジスタ 630 では、半導体膜 901 において、導電膜 922 に重なる領域と、ゲート電極 931 に重なる領域との間に、領域 911 が存在する。領域 910 及び領域 911 に、導電膜 921、導電膜 922、及びゲート電極 931 をマスクとしてアルゴン、p 型の導電型を半導体膜 901 に付与する不純物、或いは、n 型の導電型を半導体膜 901 に付与する不純物を添加することで、半導体膜 901 のうちゲート電極 931 に重なる領域よりも、領域 910 及び領域 911 の抵抗率を下げることができる。40

**【0176】**

そして、トランジスタ 630 上に、絶縁膜 863 が設けられている。

**【0177】**

なお、図 13 において、トランジスタ 630 は、ゲート電極 931 を半導体膜 901 の片側において少なくとも有していれば良いが、半導体膜 901 を間に挟んで存在する一対のゲート電極を有していても良い。

**【0178】**

トランジスタ 630 が、半導体膜 901 を間に挟んで存在する一対のゲート電極を有している場合、一方のゲート電極には導通状態または非導通状態を制御するための信号が与え50

られ、他方のゲート電極は、電位が他から与えられている状態であっても良い。この場合、一対のゲート電極に、同じ高さの電位が与えられていても良いし、他方のゲート電極にのみ接地電位などの固定の電位が与えられていても良い。他方のゲート電極に与える電位の高さを制御することで、トランジスタの閾値電圧を制御することができる。

#### 【0179】

また、図13では、トランジスタ630が、一のゲート電極931に対応した一のチャネル形成領域を有する、シングルゲート構造である場合を例示している。しかし、トランジスタ630は、電気的に接続された複数のゲート電極を有することで、一の活性層にチャネル形成領域を複数有する、マルチゲート構造であっても良い。

#### 【0180】

<トランジスタについて>

次いで、OSトランジスタの構成例について説明する。

#### 【0181】

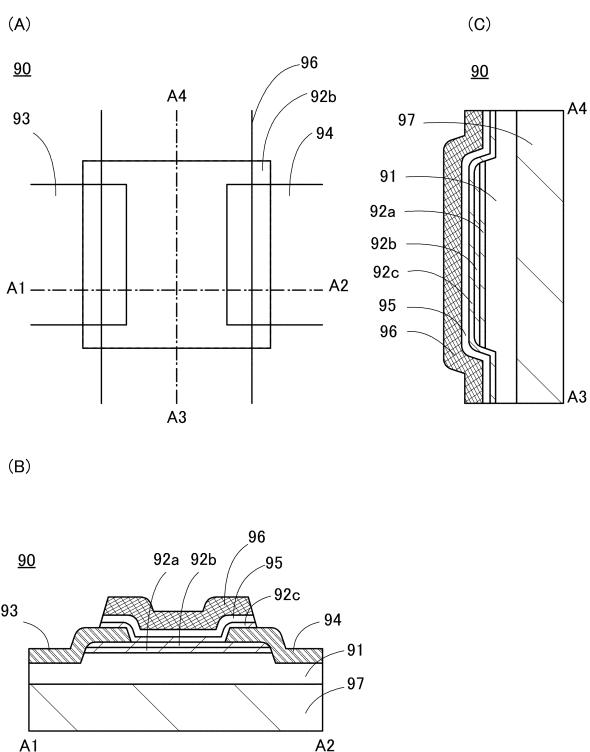

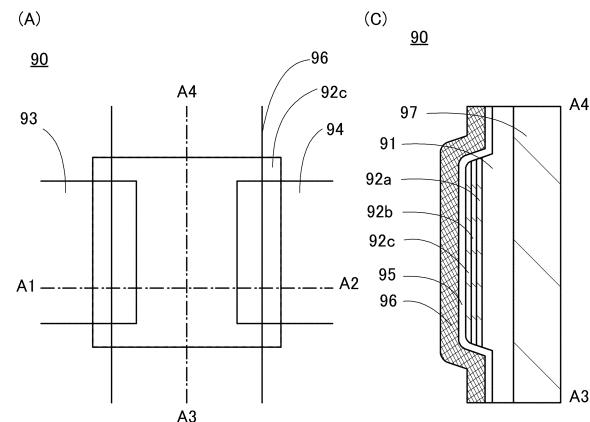

図14に、OSトランジスタであるトランジスタ90の構成を、一例として示す。図14(A)には、トランジスタ90の上面図を示す。なお、図14(A)では、トランジスタ90のレイアウトを明確にするために、各種の絶縁膜を省略している。また、図14(A)に示した上面図の、一点鎖線A1-A2における断面図を図14(B)に示し、一点鎖線A3-A4における断面図を図14(C)に示す。

#### 【0182】

図14に示すように、トランジスタ90は、基板97に形成された絶縁膜91上において順に積層された酸化物半導体膜92a及び酸化物半導体膜92bと、酸化物半導体膜92bに電気的に接続され、ソース電極またはドレイン電極としての機能を有する導電膜93及び導電膜94と、酸化物半導体膜92b、導電膜93及び導電膜94上の酸化物半導体膜92cと、ゲート絶縁膜としての機能を有し、なおかつ酸化物半導体膜92c上に位置する絶縁膜95と、ゲート電極としての機能を有し、なおかつ絶縁膜95上において酸化物半導体膜92a乃至酸化物半導体膜92cと重なる導電膜96とを有する。なお、基板97は、ガラス基板や半導体基板などであってもよいし、ガラス基板や半導体基板上に半導体素子が形成された素子基板であってもよい。

#### 【0183】

また、トランジスタ90の、具体的な構成の別の一例を、図15に示す。図15(A)には、トランジスタ90の上面図を示す。なお、図15(A)では、トランジスタ90のレイアウトを明確にするために、各種の絶縁膜を省略している。また、図15(A)に示した上面図の、破線A1-A2における断面図を図15(B)に示し、破線A3-A4における断面図を図15(C)に示す。

#### 【0184】

図15に示すように、トランジスタ90は、絶縁膜91上において順に積層された酸化物半導体膜92a乃至酸化物半導体膜92cと、酸化物半導体膜92cに電気的に接続され、ソース電極またはドレイン電極としての機能を有する導電膜93及び導電膜94と、ゲート絶縁膜としての機能を有し、なおかつ酸化物半導体膜92c、導電膜93及び導電膜94上に位置する絶縁膜95と、ゲート電極としての機能を有し、なおかつ絶縁膜95上において酸化物半導体膜92a乃至酸化物半導体膜92cと重なる導電膜96とを有する。

#### 【0185】

なお、図13及び図14では、積層された酸化物半導体膜92a乃至酸化物半導体膜92cを用いるトランジスタ90の構成を例示している。トランジスタ90が有する酸化物半導体膜は、積層された複数の酸化物半導体膜で構成されているとは限らず、単膜の酸化物半導体膜で構成されていても良い。

#### 【0186】

酸化物半導体膜92a乃至酸化物半導体膜92cが順に積層されている半導体膜をトランジスタ90が有する場合、酸化物半導体膜92a及び酸化物半導体膜92cは、酸化物半

10

20

30

40

50

導体膜 9 2 b を構成する金属元素の少なくとも 1 つを、その構成要素に含み、伝導帯下端のエネルギーが酸化物半導体膜 9 2 b よりも 0 . 0 5 e V 以上、 0 . 0 7 e V 以上、 0 . 1 e V 以上または 0 . 1 5 e V 以上、かつ 2 e V 以下、 1 e V 以下、 0 . 5 e V 以下または 0 . 4 e V 以下、真空準位に近い酸化物膜である。さらに、酸化物半導体膜 9 2 b は、少なくともインジウムを含むと、キャリア移動度が高くなるため好ましい。

#### 【 0 1 8 7 】

上記構成の半導体膜をトランジスタ 9 0 が有する場合、ゲート電極に電圧を印加することで、半導体膜に電界が加わると、半導体膜のうち、伝導帯下端のエネルギーが小さい酸化物半導体膜 9 2 b にチャネル領域が形成される。即ち、酸化物半導体膜 9 2 b と絶縁膜 9 5との間に酸化物半導体膜 9 2 c が設けられていることによって、絶縁膜 9 5 と離隔している酸化物半導体膜 9 2 b に、チャネル領域を形成することができる。10

#### 【 0 1 8 8 】

また、酸化物半導体膜 9 2 c は、酸化物半導体膜 9 2 b を構成する金属元素の少なくとも 1 つをその構成要素に含むため、酸化物半導体膜 9 2 b と酸化物半導体膜 9 2 c の界面では、界面散乱が起こりにくい。従って、当該界面においてキャリアの動きが阻害されにくいため、トランジスタ 9 0 の電界効果移動度が高くなる。

#### 【 0 1 8 9 】

また、酸化物半導体膜 9 2 b と酸化物半導体膜 9 2 a の界面に界面準位が形成されると、界面近傍の領域にもチャネル領域が形成されるために、トランジスタ 9 0 の閾値電圧が変動してしまう。しかし、酸化物半導体膜 9 2 a は、酸化物半導体膜 9 2 b を構成する金属元素の少なくとも 1 つをその構成要素に含むため、酸化物半導体膜 9 2 b と酸化物半導体膜 9 2 a の界面には、界面準位が形成されにくい。よって、上記構成により、トランジスタ 9 0 の閾値電圧等の電気的特性のばらつきを、低減することができる。20

#### 【 0 1 9 0 】

また、酸化物半導体膜間に不純物が存在することによって、各膜の界面にキャリアの流れを阻害する界面準位が形成されることがないよう、複数の酸化物半導体膜を積層させることが望ましい。積層された酸化物半導体膜の膜間に不純物が存在していると、酸化物半導体膜間における伝導帯下端のエネルギーの連続性が失われ、界面近傍において、キャリアがトラップされるか、あるいは再結合により消滅してしまうからである。膜間における不純物を低減させることで、主成分である一の金属を少なくとも共に有する複数の酸化物半導体膜を、単に積層させるよりも、連続接合（ここでは特に伝導帯下端のエネルギーが各膜の間で連続的に変化する U 字型の井戸構造を有している状態）が形成されやすくなる。30

#### 【 0 1 9 1 】

連続接合を形成するためには、ロードロック室を備えたマルチチャンバー方式の成膜装置（スパッタリング装置）を用いて各膜を大気に触れさせることなく連続して積層することが必要となる。スパッタリング装置における各チャンバーは、酸化物半導体にとって不純物となる水等を可能な限り除去すべくクライオポンプのような吸着式の真空排気ポンプを用いて高真空排気（ $5 \times 10^{-7}$  Pa 乃至  $1 \times 10^{-4}$  Pa）することが好ましい。または、ターボ分子ポンプとコールドトラップを組み合わせて排気系からチャンバー内に気体が逆流しないようにしておくことが好ましい。40

#### 【 0 1 9 2 】

高純度の真性な酸化物半導体を得るためにには、各チャンバー内を高真空排気するのみならず、スパッタリングに用いるガスの高純度化も重要である。上記ガスとして用いる酸素ガスやアルゴンガスの露点を、 - 40 以下、好ましくは - 80 以下、より好ましくは - 100 以下とし、使用するガスの高純度化を図ることで、酸化物半導体膜に水分等が取り込まれることを可能な限り防ぐことができる。具体的に、酸化物半導体膜 9 2 b が In - M - Zn 酸化物（M は、 Al 、 Ti 、 Ga 、 Y 、 Zr 、 La 、 Ce 、 Nd または Hf ）の場合、酸化物半導体膜 9 2 b を成膜するために用いるターゲットにおいて、金属元素の原子数比を In : M : Zn = x 1 : y 1 : z 1 とすると、 x 1 / y 1 は、 1 / 3 以上 6 以下、さらには 1 以上 6 以下であって、 z 1 / y 1 は、 1 / 3 以上 6 以下、さらには 1 以上50

6以下であることが好ましい。なお、 $z_1 / y_1$ を1以上6以下とすることで、酸化物半導体膜92bとしてCAAC-OS(C Axis Aligned Crystalline Oxide Semiconductor)膜が形成されやすくなる。ターゲットの金属元素の原子数比の代表例としては、In:M:Zn=1:1:1、In:M:Zn=3:1:2等がある。なお、CAAC-OSについての詳細は後述する。

#### 【0193】

具体的に、酸化物半導体膜92a、酸化物半導体膜92cがIn-M-Zn酸化物(MはAl、Ti、Ga、Y、Zr、La、Ce、NdまたはHf)の場合、酸化物半導体膜92a、酸化物半導体膜92cを成膜するために用いるターゲットにおいて、金属元素の原子数比をIn:M:Zn=x2:y2:z2とすると、 $x_2 / y_2 < x_1 / y_1$ であって、 $z_2 / y_2$ は、1/3以上6以下、さらには1以上6以下であることが好ましい。なお、 $z_2 / y_2$ を1以上6以下とすることで、酸化物半導体膜92a、酸化物半導体膜92cとしてCAAC-OS膜が形成されやすくなる。ターゲットの金属元素の原子数比の代表例としては、In:M:Zn=1:3:2、In:M:Zn=1:3:4、In:M:Zn=1:3:6、In:M:Zn=1:3:8等がある。

#### 【0194】

なお、酸化物半導体膜92a及び酸化物半導体膜92cの厚さは、3nm以上100nm以下、好ましくは3nm以上50nm以下とする。また、酸化物半導体膜92bの厚さは、3nm以上200nm以下、好ましくは3nm以上100nm以下であり、さらに好ましくは3nm以上50nm以下である。

#### 【0195】

3層構造の半導体膜において、酸化物半導体膜92a乃至酸化物半導体膜92cは、非晶質または結晶質の両方の形態を取りうる。ただし、チャネル領域が形成される酸化物半導体膜92bが結晶質であることにより、トランジスタ90に安定した電気的特性を付与することができるため、酸化物半導体膜92bは結晶質であることが好ましい。

#### 【0196】

なお、チャネル形成領域とは、トランジスタ90の半導体膜のうち、ゲート電極と重なり、かつソース電極とドレイン電極に挟まれる領域を意味する。また、チャネル領域とは、チャネル形成領域において、電流が主として流れる領域をいう。

#### 【0197】

例えば、酸化物半導体膜92a及び酸化物半導体膜92cとして、スパッタリング法により形成したIn-Ga-Zn酸化物膜を用いる場合、酸化物半導体膜92a及び酸化物半導体膜92cの成膜には、In-Ga-Zn酸化物(In:Ga:Zn=1:3:2[原子数比])であるターゲットを用いることができる。成膜条件は、例えば、成膜ガスとしてアルゴンガスを30sccm、酸素ガスを15sccm用い、圧力0.4Paとし、基板温度を200とし、DC電力0.5kWとすればよい。

#### 【0198】

また、酸化物半導体膜92bをCAAC-OS(C Axis Aligned Crystalline Oxide Semiconductor)膜とする場合、酸化物半導体膜92bの成膜には、In-Ga-Zn酸化物(In:Ga:Zn=1:1:1[原子数比])を含む多結晶ターゲットを用いることが好ましい。成膜条件は、例えば、成膜ガスとしてアルゴンガスを30sccm、酸素ガスを15sccm用い、圧力を0.4Paとし、基板の温度300とし、DC電力0.5kWとすることができます。また、酸化物半導体膜92bをCAAC-OS膜とする場合、酸化物半導体膜92bの成膜には、In-Ga-Zn酸化物(In:Ga:Zn=2:1:3[原子数比])をターゲットに用いてもよい。このようなターゲットを用いて成膜されたCAAC-OS膜は、一定の範囲におけるCAAC-OSの回折パターンが観測される領域の割合(CAAC化率ともいう)を高くすることができるので、当該CAAC-OS膜にチャネル形成領域を有するトランジスタの周波数特性(f特)を高めることができます。

#### 【0199】

10

20

30

40

50

なお、酸化物半導体膜 92a 乃至 92c は、スパッタリング法により形成することができる。

#### 【0200】

なお、電子供与体（ドナー）となる水分または水素などの不純物が低減され、なおかつ酸素欠損が低減されることにより高純度化された酸化物半導体（purified Oxide Semiconductor）は、キャリア発生源が少ないため、i型（真性半導体）又はi型に限りなく近くすることができる。そのため、高純度化された酸化物半導体膜にチャネル形成領域を有するトランジスタは、オフ電流が著しく小さく、信頼性が高い。そして、当該酸化物半導体膜にチャネル形成領域が形成されるトランジスタは、閾値電圧がプラスとなる電気的特性（ノーマリーオフ特性ともいう。）になりやすい。

10

#### 【0201】

具体的に、高純度化された酸化物半導体膜にチャネル形成領域を有するトランジスタのオフ電流が小さいことは、いろいろな実験により証明できる。例えば、チャネル幅が $1 \times 10^6 \mu\text{m}$ でチャネル長が $10 \mu\text{m}$ の素子であっても、ソース電極とドレイン電極間の電圧（ドレイン電圧）が $1\text{V}$ から $10\text{V}$ の範囲において、オフ電流が、半導体パラメータアナライザの測定限界以下、すなわち $1 \times 10^{-13}\text{A}$ 以下という特性を得ることができる。この場合、トランジスタのチャネル幅で規格化したオフ電流は、 $100\text{zA}/\mu\text{m}$ 以下であることが分かる。また、容量素子とトランジスタとを接続して、容量素子に流入または容量素子から流出する電荷を当該トランジスタで制御する回路を用いて、オフ電流の測定を行った。当該測定では、高純度化された酸化物半導体膜を上記トランジスタのチャネル形成領域に用い、容量素子の単位時間あたりの電荷量の推移から当該トランジスタのオフ電流を測定した。その結果、トランジスタのソース電極とドレイン電極間の電圧が $3\text{V}$ の場合に、数十 $\text{yA}/\mu\text{m}$ という、さらに小さいオフ電流が得られることが分かった。従って、高純度化された酸化物半導体膜をチャネル形成領域に用いたトランジスタは、オフ電流が、結晶性を有するシリコンを用いたトランジスタに比べて著しく小さい。

20

#### 【0202】

なお、半導体膜として酸化物半導体膜を用いる場合、酸化物半導体としては、少なくともインジウム（In）あるいは亜鉛（Zn）を含むことが好ましい。また、該酸化物半導体を用いたトランジスタの電気的特性のばらつきを減らすためのスタビライザーとして、それらに加えてガリウム（Ga）を有することが好ましい。また、スタビライザーとしてスズ（Sn）を有することが好ましい。また、スタビライザーとしてハフニウム（Hf）を有することが好ましい。また、スタビライザーとしてアルミニウム（Al）を有することが好ましい。また、スタビライザーとしてジルコニウム（Zr）を含むことが好ましい。

30

#### 【0203】

酸化物半導体の中でも In - Ga - Zn 酸化物、In - Sn - Zn 酸化物などは、炭化シリコン、窒化ガリウム、または酸化ガリウムとは異なり、スパッタリング法や湿式法により電気的特性の優れたトランジスタを作製することが可能であり、量産性に優れるといった利点がある。また、炭化シリコン、窒化ガリウム、または酸化ガリウムとは異なり、上記 In - Ga - Zn 酸化物は、ガラス基板上に、電気的特性の優れたトランジスタを作製することが可能である。また、基板の大型化にも対応が可能である。

40

#### 【0204】

また、他のスタビライザーとして、ランタノイドである、ランタン（La）、セリウム（Ce）、プラセオジム（Pr）、ネオジム（Nd）、サマリウム（Sm）、ユウロピウム（Eu）、ガドリニウム（Gd）、テルビウム（Tb）、ジスプロシウム（Dy）、ホルミウム（Ho）、エルビウム（Er）、ツリウム（Tm）、イッテルビウム（Yb）、ルテチウム（Lu）のいずれか一種または複数種を含んでいてもよい。

#### 【0205】

例えば、酸化物半導体として、酸化インジウム、酸化ガリウム、酸化スズ、酸化亜鉛、In - Zn 酸化物、Sn - Zn 酸化物、Al - Zn 酸化物、Zn - Mg 酸化物、Sn - Mg 酸化物、In - Mg 酸化物、In - Ga 酸化物、In - Ga - Zn 酸化物（IGZOとも

50

表記する)、In-Al-Zn酸化物、In-Sn-Zn酸化物、Sn-Ga-Zn酸化物、Al-Ga-Zn酸化物、Sn-Al-Zn酸化物、In-Hf-Zn酸化物、In-La-Zn酸化物、In-Pr-Zn酸化物、In-Nd-Zn酸化物、In-Ce-Zn酸化物、In-Sm-Zn酸化物、In-Eu-Zn酸化物、In-Gd-Zn酸化物、In-Tb-Zn酸化物、In-Dy-Zn酸化物、In-Ho-Zn酸化物、In-Er-Zn酸化物、In-Tm-Zn酸化物、In-Yb-Zn酸化物、In-Lu-Zn酸化物、In-Sn-Ga-Zn酸化物、In-Hf-Ga-Zn酸化物、In-Al-Ga-Zn酸化物、In-Sn-Al-Zn酸化物、In-Sn-Hf-Zn酸化物、In-Hf-Al-Zn酸化物を用いることができる。

## 【0206】

10

なお、例えば、In-Ga-Zn酸化物とは、InとGaとZnを含む酸化物という意味であり、InとGaとZnの比率は問わない。また、InとGaとZn以外の金属元素を含んでいてもよい。In-Ga-Zn酸化物は、無電界時の抵抗が十分に高くオフ電流を十分に小さくすることが可能であり、また、移動度も高い。

## 【0207】

例えば、In-Sn-Zn酸化物では比較的容易に高い移動度が得られる。しかしながら、In-Ga-Zn酸化物でも、バルク内欠陥密度を低減することにより移動度を上げることができる。

## 【0208】

20

また、トランジスタ90において、ソース電極及びドレイン電極に用いられる導電性材料によっては、ソース電極及びドレイン電極中の金属が、酸化物半導体膜から酸素を引き抜くことがある。この場合、酸化物半導体膜のうち、ソース電極及びドレイン電極に接する領域が、酸素欠損の形成によりn型化される。n型化された領域は、ソース領域またはドレイン領域として機能するため、酸化物半導体膜とソース電極及びドレイン電極との間ににおけるコンタクト抵抗を下げることができる。よって、n型化された領域が形成されることで、トランジスタ90の移動度及びオン電流を高めることができ、それにより、トランジスタ90を用いた半導体装置の高速動作を実現することができる。

## 【0209】

なお、ソース電極及びドレイン電極中の金属による酸素の引き抜きは、ソース電極及びドレイン電極をスパッタリング法などにより形成する際に起こりうるし、ソース電極及びドレイン電極を形成した後に行われる加熱処理によても起こりうる。また、n型化される領域は、酸素と結合し易い導電性材料をソース電極及びドレイン電極に用いることで、より形成されやすくなる。上記導電性材料としては、例えば、Al、Cr、Cu、Ta、Ti、Mo、Wなどが挙げられる。

30

## 【0210】

複数の積層された酸化物半導体膜を有する半導体膜をトランジスタ90に用いる場合、n型化される領域は、チャネル領域となる酸化物半導体膜92bにまで達していることが、トランジスタ90の移動度及びオン電流を高め、半導体装置の高速動作を実現する上で好ましい。

## 【0211】

40

絶縁膜91は、加熱により上記酸素の一部を酸化物半導体膜92a乃至酸化物半導体膜92cに供給する機能を有する絶縁膜であることが望ましい。また、絶縁膜91は、欠陥が少ないことが好ましく、代表的には、ESR測定により得られる、シリコンのダンギングボンドに由来する $g = 2.001$ を持つスピノの密度が $1 \times 10^{18} \text{ spins/cm}^3$ 以下であることが好ましい。

## 【0212】

絶縁膜91は、加熱により上記酸素の一部を酸化物半導体膜92a乃至酸化物半導体膜92cに供給する機能を有するため、酸化物であることが望ましく、例えば、酸化アルミニウム、酸化マグネシウム、酸化珪素、酸化窒化珪素、窒化酸化珪素、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニア、酸化ランタン、酸化ネオジム、酸

50

化ハフニウムおよび酸化タンタルなどを用いることができる。絶縁膜91は、プラズマCVD法またはスパッタリング法等により、形成することができる。

#### 【0213】

なお、本明細書中において、酸化窒化物は、その組成として、窒素よりも酸素の含有量が多い材料を指し、窒化酸化物は、その組成として、酸素よりも窒素の含有量が多い材料を指す。

#### 【0214】

なお、図14及び図15に示すトランジスタ90は、チャネル領域が形成される酸化物半導体膜92bの端部のうち、導電膜93及び導電膜94とは重ならない端部、言い換えると、導電膜93及び導電膜94が位置する領域とは異なる領域に位置する端部と、導電膜96とが、重なる構成を有する。酸化物半導体膜92bの端部は、当該端部を形成するためのエッチングでプラズマに曝されるときに、エッチングガスから生じた塩素ラジカル、フッ素ラジカル等が、酸化物半導体を構成する金属元素と結合しやすい。よって、酸化物半導体膜の端部では、当該金属元素と結合していた酸素が脱離しやすい状態にあるため、酸素欠損が形成され、n型化しやすい。しかし、図14及び図15に示すトランジスタ90では、導電膜93及び導電膜94とは重ならない酸化物半導体膜92bの端部と、導電膜96とが重なるため、導電膜96の電位を制御することにより、当該端部にかかる電界を制御することができる。よって、酸化物半導体膜92bの端部を介して導電膜93と導電膜94の間に流れる電流を、導電膜96に与える電位によって制御することができる。このようなトランジスタ90の構造を、Surrounded Channel (S-C channel) 構造とよぶ。

#### 【0215】

具体的に、S-Channel構造の場合、トランジスタ90がオフとなるような電位を導電膜96に与えたときは、当該端部を介して導電膜93と導電膜94の間に流れるオフ電流を小さく抑えることができる。そのため、トランジスタ90では、大きなオン電流を得るためにチャネル長を短くし、その結果、酸化物半導体膜92bの端部における導電膜93と導電膜94の間の長さが短くなってしまっても、トランジスタ90のオフ電流を小さく抑えることができる。よって、トランジスタ90は、チャネル長を短くすることで、オンのときには大きいオン電流を得ることができ、オフのときにはオフ電流を小さく抑えることができる。

#### 【0216】

また、具体的に、S-Channel構造の場合、トランジスタ90がオンとなるような電位を導電膜96に与えたときは、当該端部を介して導電膜93と導電膜94の間に流れる電流を大きくすることができます。当該電流は、トランジスタ90の電界効果移動度とオン電流の増大に寄与する。そして、酸化物半導体膜92bの端部と、導電膜96とが重なることで、酸化物半導体膜92bにおいてキャリアの流れる領域が、絶縁膜95に近い酸化物半導体膜92bの界面近傍のみでなく、酸化物半導体膜92bの広い範囲においてキャリアが流れるため、トランジスタ90におけるキャリアの移動量が増加する。この結果、トランジスタ90のオン電流が大きくなると共に、電界効果移動度が高くなり、代表的には電界効果移動度が $10 \text{ cm}^2 / \text{V} \cdot \text{s}$ 以上、さらには $20 \text{ cm}^2 / \text{V} \cdot \text{s}$ 以上となる。なお、ここでの電界効果移動度は、酸化物半導体膜の物性値としての移動度の近似値ではなく、トランジスタの飽和領域における電流駆動力の指標であり、見かけ上の電界効果移動度である。

#### 【0217】

##### <酸化物半導体膜の構造>

以下では、酸化物半導体膜の構造について説明する。なお、以下の説明において、「平行」とは、二つの直線が $-10^\circ$ 以上 $10^\circ$ 以下の角度で配置されている状態をいう。従って、 $-5^\circ$ 以上 $5^\circ$ 以下の場合も含まれる。また、「垂直」とは、二つの直線が $80^\circ$ 以上 $100^\circ$ 以下の角度で配置されている状態をいう。従って、 $85^\circ$ 以上 $95^\circ$ 以下の場合も含まれる。また、本明細書において、結晶が三方晶または菱面体晶である場合、六方

10

20

30

40

50

晶系として表す。

**【0218】**

酸化物半導体膜は、非単結晶酸化物半導体膜と単結晶酸化物半導体膜とに大別される。非単結晶酸化物半導体膜とは、CAC-O<sub>S</sub>膜、多結晶酸化物半導体膜、微結晶酸化物半導体膜、非晶質酸化物半導体膜などをいう。

**【0219】**

<CAC-O<sub>S</sub>膜>

まずは、CAC-O<sub>S</sub>膜について説明する。

**【0220】**

CAC-O<sub>S</sub>膜は、c軸配向した複数の結晶部を有する酸化物半導体膜の一つである。

10

**【0221】**

透過型電子顕微鏡(TEM: Transmission Electron Microscope)によって、CAC-O<sub>S</sub>膜の明視野像および回折パターンの複合解析像(高分解能TEM像ともいう。)を観察することで複数の結晶部を確認することができる。一方、高分解能TEM像によっても明確な結晶部同士の境界、即ち結晶粒界(グレインバウンダリーともいう。)を確認することができない。そのため、CAC-O<sub>S</sub>膜は、結晶粒界に起因する電子移動度の低下が起こりにくいといえる。

**【0222】**

試料面と概略平行な方向から、CAC-O<sub>S</sub>膜の断面の高分解能TEM像を観察すると、結晶部において、金属原子が層状に配列していることを確認できる。金属原子の各層は、CAC-O<sub>S</sub>膜の膜を形成する面(被形成面ともいう。)または上面の凹凸を反映した形状であり、CAC-O<sub>S</sub>膜の被形成面または上面と平行に配列する。

20

**【0223】**

一方、試料面と概略垂直な方向から、CAC-O<sub>S</sub>膜の平面の高分解能TEM像を観察すると、結晶部において、金属原子が三角形状または六角形状に配列していることを確認できる。しかしながら、異なる結晶部間で、金属原子の配列に規則性は見られない。

**【0224】**

CAC-O<sub>S</sub>膜に対し、X線回折(XRD:X-Ray Diffraction)装置を用いて構造解析を行うと、例えばInGaZnO<sub>4</sub>の結晶を有するCAC-O<sub>S</sub>膜のout-of-plane法による解析では、回折角(2θ)が31°近傍にピークが現れる場合がある。このピークは、InGaZnO<sub>4</sub>の結晶の(009)面に帰属されることから、CAC-O<sub>S</sub>膜の結晶がc軸配向性を有し、c軸が被形成面または上面に概略垂直な方向を向いていることが確認できる。

30

**【0225】**

なお、InGaZnO<sub>4</sub>の結晶を有するCAC-O<sub>S</sub>膜のout-of-plane法による解析では、2θが31°近傍のピークの他に、2θが36°近傍にもピークが現れる場合がある。2θが36°近傍のピークは、CAC-O<sub>S</sub>膜中の一部に、c軸配向性を有さない結晶が含まれることを示している。CAC-O<sub>S</sub>膜は、2θが31°近傍にピークを示し、2θが36°近傍にピークを示さないことが好ましい。

**【0226】**

40

CAC-O<sub>S</sub>膜は、不純物濃度の低い酸化物半導体膜である。不純物は、水素、炭素、シリコン、遷移金属元素などの酸化物半導体膜の主成分以外の元素である。特に、シリコンなどの、酸化物半導体膜を構成する金属元素よりも酸素との結合力の強い元素は、酸化物半導体膜から酸素を奪うことで酸化物半導体膜の原子配列を乱し、結晶性を低下させる要因となる。また、鉄やニッケルなどの重金属、アルゴン、二酸化炭素などは、原子半径(または分子半径)が大きいため、酸化物半導体膜内部に含まれると、酸化物半導体膜の原子配列を乱し、結晶性を低下させる要因となる。なお、酸化物半導体膜に含まれる不純物は、キャリアトラップやキャリア発生源となる場合がある。

**【0227】**

また、CAC-O<sub>S</sub>膜は、欠陥準位密度の低い酸化物半導体膜である。例えば、酸化物

50

半導体膜中の酸素欠損は、キャリアトラップとなることや、水素を捕獲することによってキャリア発生源となることがある。

#### 【0228】

不純物濃度が低く、欠陥準位密度が低い（酸素欠損の少ない）ことを、高純度真性または実質的に高純度真性と呼ぶ。高純度真性または実質的に高純度真性である酸化物半導体膜は、キャリア発生源が少ないとため、キャリア密度を低くすることができる。したがって、当該酸化物半導体膜を用いたトランジスタは、しきい値電圧がマイナスとなる電気特性（ノーマリーオンともいう。）になることが少ない。また、高純度真性または実質的に高純度真性である酸化物半導体膜は、キャリアトラップが少ない。そのため、当該酸化物半導体膜を用いたトランジスタは、電気特性の変動が小さく、信頼性の高いトランジスタとなる。なお、酸化物半導体膜のキャリアトラップに捕獲された電荷は、放出するまでに要する時間が長く、あたかも固定電荷のように振る舞うことがある。そのため、不純物濃度が高く、欠陥準位密度が高い酸化物半導体膜を用いたトランジスタは、電気特性が不安定となる場合がある。10

#### 【0229】

また、CAC-O<sub>x</sub>膜を用いたトランジスタは、可視光や紫外光の照射による電気特性的変動が小さい。

#### 【0230】

<微結晶酸化物半導体膜>

次に、微結晶酸化物半導体膜について説明する。20

#### 【0231】

微結晶酸化物半導体膜は、高分解能TEM像において、結晶部を確認することのできる領域と、明確な結晶部を確認することのできない領域と、を有する。微結晶酸化物半導体膜に含まれる結晶部は、1 nm以上100 nm以下、または1 nm以上10 nm以下の大きさであることが多い。特に、1 nm以上10 nm以下、または1 nm以上3 nm以下の微結晶であるナノ結晶（nc：nanocrystal）を有する酸化物半導体膜を、nc-O<sub>x</sub>（nanocrystalline Oxide Semiconductor）膜と呼ぶ。また、nc-O<sub>x</sub>膜は、例えば、高分解能TEM像では、結晶粒界を明確に確認できない場合がある。30

#### 【0232】

nc-O<sub>x</sub>膜は、微小な領域（例えば、1 nm以上10 nm以下の領域、特に1 nm以上3 nm以下の領域）において原子配列に周期性を有する。また、nc-O<sub>x</sub>膜は、異なる結晶部間で結晶方位に規則性が見られない。そのため、膜全体で配向性が見られない。したがって、nc-O<sub>x</sub>膜は、分析方法によっては、非晶質酸化物半導体膜と区別が付かない場合がある。例えば、nc-O<sub>x</sub>膜に対し、結晶部よりも大きい径のX線を用いるXRD装置を用いて構造解析を行うと、out-of-plane法による解析では、結晶面を示すピークが検出されない。また、nc-O<sub>x</sub>膜に対し、結晶部よりも大きいプローブ径（例えば50 nm以上）の電子線を用いる電子回折（制限視野電子回折ともいう。）を行うと、ハローパターンのような回折パターンが観測される。一方、nc-O<sub>x</sub>膜に対し、結晶部の大きさと近いか結晶部より小さいプローブ径の電子線を用いるナノビーム電子回折を行うと、スポットが観測される。また、nc-O<sub>x</sub>膜に対しナノビーム電子回折を行うと、円を描くように（リング状に）輝度の高い領域が観測される場合がある。また、nc-O<sub>x</sub>膜に対しナノビーム電子回折を行うと、リング状の領域内に複数のスポットが観測される場合がある。40

#### 【0233】

nc-O<sub>x</sub>膜は、非晶質酸化物半導体膜よりも規則性の高い酸化物半導体膜である。そのため、nc-O<sub>x</sub>膜は、非晶質酸化物半導体膜よりも欠陥準位密度が低くなる。ただし、nc-O<sub>x</sub>膜は、異なる結晶部間で結晶方位に規則性が見られない。そのため、nc-O<sub>x</sub>膜は、CAC-O<sub>x</sub>膜と比べて欠陥準位密度が高くなる。

#### 【0234】

10

20

30

40

50

## &lt; 非晶質酸化物半導体膜 &gt;

次に、非晶質酸化物半導体膜について説明する。

## 【 0 2 3 5 】

非晶質酸化物半導体膜は、膜中における原子配列が不規則であり、結晶部を有さない酸化物半導体膜である。石英のような無定形状態を有する酸化物半導体膜が一例である。

## 【 0 2 3 6 】

非晶質酸化物半導体膜は、高分解能 TEM 像において結晶部を確認することができない。

## 【 0 2 3 7 】

非晶質酸化物半導体膜に対し、XRD 装置を用いた構造解析を行うと、out-of-plane 法による解析では、結晶面を示すピークが検出されない。<sup>10</sup> また、非晶質酸化物半導体膜に対し、電子回折を行うと、ハローパターンが観測される。また、非晶質酸化物半導体膜に対し、ナノビーム電子回折を行うと、スポットが観測されず、ハローパターンが観測される。

## 【 0 2 3 8 】

なお、酸化物半導体膜は、n c - O S 膜と非晶質酸化物半導体膜との間の物性を示す構造を有する場合がある。そのような構造を有する酸化物半導体膜を、特に非晶質ライク酸化物半導体 (amorphous-like O S : amorphous-like Oxide Semiconductor) 膜と呼ぶ。

## 【 0 2 3 9 】

amorphous-like O S 膜は、高分解能 TEM 像において鬆（ボイドともいう。）が観察される場合がある。また、高分解能 TEM 像において、明確に結晶部を確認することのできる領域と、結晶部を確認することのできない領域と、を有する。amorphous-like O S 膜は、TEM による観察程度の微量な電子照射によって、結晶化が起こり、結晶部の成長が見られる場合がある。一方、良質な n c - O S 膜であれば、TEM による観察程度の微量な電子照射による結晶化はほとんど見られない。<sup>20</sup>

## 【 0 2 4 0 】

なお、amorphous-like O S 膜および n c - O S 膜の結晶部の大きさの計測は、高分解能 TEM 像を用いて行うことができる。例えば、In Ga Zn O<sub>4</sub> の結晶は層状構造を有し、In - O 層の間に、Ga - Zn - O 層を 2 層有する。In Ga Zn O<sub>4</sub> の結晶の単位格子は、In - O 層を 3 層有し、また Ga - Zn - O 層を 6 層有する、計 9 層が c 軸方向に層状に重なった構造を有する。よって、これらの近接する層同士の間隔は、(009) 面の格子面間隔 (d 値ともいう。) と同程度であり、結晶構造解析からその値は 0.29 nm と求められている。そのため、高分解能 TEM 像における格子縞に着目し、格子縞の間隔が 0.28 nm 以上 0.30 nm 以下である箇所においては、それぞれの格子縞が In Ga Zn O<sub>4</sub> の結晶の a - b 面に対応する。<sup>30</sup>

## 【 0 2 4 1 】

なお、酸化物半導体膜は、例えば、非晶質酸化物半導体膜、amorphous-like O S 膜、微結晶酸化物半導体膜、CAAC - O S 膜のうち、二種以上を有する積層膜であってもよい。

## 【 0 2 4 2 】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することができる。<sup>40</sup>

## 【 0 2 4 3 】

## (実施の形態 5 )

本実施の形態では、図 13 とは異なる構造を有する半導体装置の構造の一例について説明する。

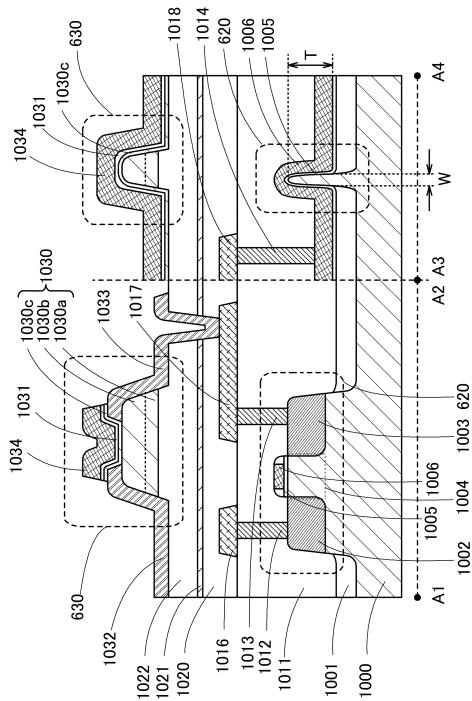

## 【 0 2 4 4 】

図 16 に、半導体装置の断面構造を、一例として示す。なお、破線 A 1 - A 2 で示す領域では、トランジスタ 620 及びトランジスタ 630 のチャネル長方向における構造を示しており、破線 A 3 - A 4 で示す領域では、トランジスタ 620 及びトランジスタ 630 のチャネル幅方向における構造を示している。ただし、本発明の一態様では、トランジスタ <sup>50</sup>

620のチャネル長方向とトランジスタ630のチャネル長方向とが、必ずしも一致していないともよい。

#### 【0245】

なお、チャネル長方向とは、ソース領域及びドレイン領域として機能する一対の領域間ににおいて、キャリアが最短距離で移動する方向を意味し、チャネル幅方向は、基板と水平な面内において、チャネル長方向に対して垂直の方向を意味する。

#### 【0246】

なお、図16では、OSトランジスタであるトランジスタ630が、Siトランジスタであるトランジスタ620上に形成されている場合を例示している。このようにSiトランジスタとOSトランジスタが積層された構成は、図1乃至6、9、10に示す各回路が有するトランジスタに適宜用いることができる。なお、本実施の形態では、図11(D)と同様に、トランジスタ620のソースまたはドレインの一方とトランジスタ630のソースまたはドレインの一方が接続された構成を示すが、これに限られない。トランジスタ620のソースまたはドレインの一方とトランジスタ630のゲートが接続されていてもよいし(図12(A)参照)、トランジスタ620のゲートとトランジスタ630のソースまたはドレインの一方が接続されていてもよいし(図12(B)参照)、トランジスタ620のゲートとトランジスタ630のゲートが接続されていてもよい(図12(C)参照)。

10

#### 【0247】

トランジスタ620は、非晶質、微結晶、多結晶または単結晶である、シリコン又はゲルマニウムなどの半導体膜または半導体基板に、チャネル形成領域を有していても良い。或いは、トランジスタ620は、酸化物半導体膜または酸化物半導体基板に、チャネル形成領域を有していても良い。全てのトランジスタが酸化物半導体膜または酸化物半導体基板に、チャネル形成領域を有している場合、トランジスタ630はトランジスタ620上に積層されていなくとも良く、トランジスタ630とトランジスタ620とは、同一の層に形成されていても良い。

20

#### 【0248】

シリコンの薄膜を用いてトランジスタ620を形成する場合、当該薄膜には、プラズマCVD法などの気相成長法若しくはスパッタリング法で作製された非晶質シリコン、非晶質シリコンをレーザーの照射などの処理により結晶化させた多結晶シリコン、単結晶シリコンウェハに水素イオン等を注入して表層部を剥離した単結晶シリコンなどを用いることができる。

30

#### 【0249】

トランジスタ620が形成される基板1000は、例えば、シリコン基板、ゲルマニウム基板、シリコンゲルマニウム基板等を用いることができる。図16では、単結晶シリコン基板を基板1000として用いる場合を例示している。

#### 【0250】

また、トランジスタ620は、素子分離法により電気的に分離されている。素子分離法として、トレンチ分離法等を用いることができる。図16では、トレンチ分離法を用いてトランジスタ620を電気的に分離する場合を例示している。具体的に、図16では、エッチング等により基板1000に形成されたトレンチに、酸化珪素などが含まれる絶縁物を埋め込んだ後、当該絶縁物をエッチング等により部分的に除去することで形成される素子分離領域1001により、トランジスタ620を素子分離させる場合を例示している。

40

#### 【0251】

また、トレンチ以外の領域に存在する基板1000の凸部には、トランジスタ620の不純物領域1002及び不純物領域1003と、不純物領域1002及び不純物領域1003に挟まれたチャネル形成領域1004とが設けられている。さらに、トランジスタ620は、チャネル形成領域1004を覆う絶縁膜1005と、絶縁膜1005を間に挟んでチャネル形成領域1004と重なるゲート電極1006とを有する。

#### 【0252】

50

トランジスタ 620 では、チャネル形成領域 1004 における凸部の側部及び上部と、ゲート電極 1006 とが絶縁膜 1005 を間に挟んで重なることで、チャネル形成領域 1004 の側部と上部を含めた広い範囲においてキャリアが流れる。そのため、トランジスタ 620 の基板上における専有面積を小さく抑えつつ、トランジスタ 620 におけるキャリアの移動量を増加させることができる。その結果、トランジスタ 620 は、オン電流が大きくなると共に、電界効果移動度が高められる。特に、チャネル形成領域 1004 における凸部のチャネル幅方向の長さ（チャネル幅）を W、チャネル形成領域 1004 における凸部の膜厚を T とすると、チャネル幅 W に対する膜厚 T の比に相当するアスペクト比が高い場合、キャリアが流れる範囲はより広くなるため、トランジスタ 620 のオン電流をより大きくすることができ、電界効果移動度もより高められる。

10

#### 【0253】

なお、バルクの半導体基板を用いたトランジスタ 620 の場合、アスペクト比は 0.5 以上であることが望ましく、1 以上であることがより望ましい。

#### 【0254】

トランジスタ 620 上には、絶縁膜 1011 が設けられている。絶縁膜 1011 には開口部が形成されている。そして、上記開口部には、不純物領域 1002、不純物領域 1003 にそれぞれ電気的に接続されている導電膜 1012、導電膜 1013 と、ゲート電極 1006 に電気的に接続されている導電膜 1014 とが、形成されている。

#### 【0255】

そして、導電膜 1012 は、絶縁膜 1011 上に形成された導電膜 1016 に電気的に接続されており、導電膜 1013 は、絶縁膜 1011 上に形成された導電膜 1017 に電気的に接続されており、導電膜 1014 は、絶縁膜 1011 上に形成された導電膜 1018 に電気的に接続されている。

20

#### 【0256】

導電膜 1016 乃至導電膜 1018 上には、絶縁膜 1020 が設けられている。そして、絶縁膜 1020 上には、酸素、水素、水の拡散を防ぐブロッキング効果を有する絶縁膜 1021 が設けられている。絶縁膜 1021 は、密度が高くて緻密である程、また未結合手が少なく化学的に安定である程、より高いブロッキング効果を示す。酸素、水素、水の拡散を防ぐブロッキング効果を示す絶縁膜 1021 として、例えば、酸化アルミニウム、酸化窒化アルミニウム、酸化ガリウム、酸化窒化ガリウム、酸化イットリウム、酸化窒化イットリウム、酸化ハフニウム、酸化窒化ハフニウム等を用いることができる。水素、水の拡散を防ぐブロッキング効果を示す絶縁膜 1021 として、例えば、窒化シリコン、窒化酸化シリコン等を用いることができる。

30

#### 【0257】

絶縁膜 1021 上には絶縁膜 1022 が設けられており、絶縁膜 1022 上には、トランジスタ 630 が設けられている。

#### 【0258】

トランジスタ 630 は、絶縁膜 1022 上に、酸化物半導体を含む半導体膜 1030 と、半導体膜 1030 に電気的に接続された、ソース電極またはドレイン電極として機能する導電膜 1032 及び導電膜 1033 と、半導体膜 1030 を覆っているゲート絶縁膜 1031 と、ゲート絶縁膜 1031 を間に挟んで半導体膜 1030 と重なるゲート電極 1034 と、を有する。なお、絶縁膜 1020 乃至絶縁膜 1022 には開口部が設けられており、導電膜 1033 は、上記開口部において導電膜 1017 に接続されている。

40

#### 【0259】

なお、図 16において、トランジスタ 630 は、ゲート電極 1034 を半導体膜 1030 の片側において少なくとも有していれば良いが、絶縁膜 1022 を間に挟んで半導体膜 1030 と重なるゲート電極を、さらに有していても良い。

#### 【0260】

トランジスタ 630 が、一対のゲート電極を有している場合、一方のゲート電極には導通状態または非導通状態を制御するための信号が与えられ、他方のゲート電極は、電位が他

50

から与えられている状態であっても良い。この場合、一対のゲート電極に、同じ高さの電位が与えられても良いし、他方のゲート電極にのみ接地電位などの固定の電位が与えられても良い。他方のゲート電極に与える電位の高さを制御することで、トランジスタの閾値電圧を制御することができる。

#### 【0261】

また、図16では、トランジスタ630が、一のゲート電極1034に対応した一のチャネル形成領域を有する、シングルゲート構造である場合を例示している。しかし、トランジスタ630は、電気的に接続された複数のゲート電極を有することで、一の活性層にチャネル形成領域を複数有する、マルチゲート構造であっても良い。

#### 【0262】

また、図16に示すように、トランジスタ630は、半導体膜1030が、絶縁膜1022上において順に積層された酸化物半導体膜1030a乃至酸化物半導体膜1030cを有する場合を例示している。ただし、本発明の一態様では、トランジスタ630が有する半導体膜1030が、単膜の金属酸化物膜で構成されていても良い。

10

#### 【0263】

なお、本実施の形態は、他の実施の形態と適宜組み合わせて実施することができる。

#### 【0264】

##### (実施の形態6)

他の実施の形態で開示された、導電膜、半導体膜、絶縁膜など様々な膜はスパッタ法やプラズマCVD法により形成することができるが、他の方法、例えば、熱CVD法により形成してもよい。熱CVD法の例としてMOCVD(Metal Organic Chemical Vapor Deposition)法やALD(Atomic Layer Deposition)法を使っても良い。

20

#### 【0265】

熱CVD法は、プラズマを使わない成膜方法のため、プラズマダメージにより欠陥が生成されることが無いという利点を有する。

#### 【0266】

熱CVD法は、原料ガスと酸化剤を同時にチャンバー内に送り、チャンバー内を大気圧または減圧下とし、基板近傍または基板上で反応させて基板上に堆積させることで成膜を行ってもよい。

30

#### 【0267】

また、ALD法は、チャンバー内を大気圧または減圧下とし、反応のための原料ガスが順次にチャンバーに導入され、そのガス導入の順序を繰り返すことで成膜を行ってもよい。例えば、それぞれのスイッチングバルブ(高速バルブとも呼ぶ)を切り替えて2種類以上の原料ガスを順番にチャンバーに供給し、複数種の原料ガスが混ざらないよう第1の原料ガスと同時またはその後に不活性ガス(アルゴン、或いは窒素など)などを導入し、第2の原料ガスを導入する。なお、同時に不活性ガスを導入する場合には、不活性ガスはキャリアガスとなり、また、第2の原料ガスの導入時にも同時に不活性ガスを導入してもよい。また、不活性ガスを導入する代わりに真空排気によって第1の原料ガスを排出した後、第2の原料ガスを導入してもよい。第1の原料ガスが基板の表面に吸着して第1の層を成膜し、後から導入される第2の原料ガスと反応して、第2の層が第1の層上に積層されて薄膜が形成される。このガス導入順序を制御しつつ所望の厚さになるまで複数回繰り返すことで、段差被覆性に優れた薄膜を形成することができる。薄膜の厚さは、ガス導入順序を繰り返す回数によって調節することができるため、精密な膜厚調節が可能であり、微細なFETを作製する場合に適している。

40

#### 【0268】

MOCVD法やALD法などの熱CVD法は、これまでに記載した実施形態に開示された導電膜、半導体膜、絶縁膜など様々な膜を形成することができ、例えば、In-Ga-Zn-O膜を成膜する場合には、トリメチルインジウム、トリメチルガリウム、及びジメチル亜鉛を用いる。なお、トリメチルインジウムの化学式は、In(CH<sub>3</sub>)<sub>3</sub>である。ま

50

た、トリメチルガリウムの化学式は、 $\text{Ga}(\text{CH}_3)_3$ である。また、ジメチル亜鉛の化学式は、 $\text{Zn}(\text{CH}_3)_2$ である。また、これらの組み合わせに限定されず、トリメチルガリウムに代えてトリエチルガリウム（化学式 $\text{Ga}(\text{C}_2\text{H}_5)_3$ ）を用いることもでき、ジメチル亜鉛に代えてジエチル亜鉛（化学式 $\text{Zn}(\text{C}_2\text{H}_5)_2$ ）を用いることもできる。

#### 【0269】

例えば、ALDを利用する成膜装置により酸化ハフニウム膜を形成する場合には、溶媒とハフニウム前駆体化合物を含む液体（ハフニウムアルコキシドや、テトラキスジメチルアミドハフニウム（TDMAH）などのハウニウムアミド）を気化させた原料ガスと、酸化剤としてオゾン（ $\text{O}_3$ ）の2種類のガスを用いる。なお、テトラキスジメチルアミドハフニウムの化学式は $\text{Hf}[\text{N}(\text{CH}_3)_2]_4$ である。また、他の材料液としては、テトラキス（エチルメチルアミド）ハフニウムなどがある。

#### 【0270】

例えば、ALDを利用する成膜装置により酸化アルミニウム膜を形成する場合には、溶媒とアルミニウム前駆体化合物を含む液体（トリメチルアルミニウム（TMA）など）を気化させた原料ガスと、酸化剤として $\text{H}_2\text{O}$ の2種類のガスを用いる。なお、トリメチルアルミニウムの化学式は $\text{Al}(\text{CH}_3)_3$ である。また、他の材料液としては、トリス（ジメチルアミド）アルミニウム、トリイソブチルアルミニウム、アルミニウムトリス（2,2,6,6-テトラメチル-3,5-ヘプタンジオナート）などがある。

#### 【0271】

例えば、ALDを利用する成膜装置により酸化シリコン膜を形成する場合には、ヘキサクロロジシランを被成膜面に吸着させ、吸着物に含まれる塩素を除去し、酸化性ガス（ $\text{O}_2$ 、一酸化二窒素）のラジカルを供給して吸着物と反応させる。

#### 【0272】

例えば、ALDを利用する成膜装置によりタングステン膜を成膜する場合には、 $\text{WF}_6$ ガスと $\text{B}_2\text{H}_6$ ガスを順次繰り返し導入して初期タングステン膜を形成し、その後、 $\text{WF}_6$ ガスと $\text{H}_2$ ガスを同時に導入してタングステン膜を形成する。なお、 $\text{B}_2\text{H}_6$ ガスに代えて $\text{SiH}_4$ ガスを用いてもよい。

#### 【0273】

例えば、ALDを利用する成膜装置により酸化物半導体膜、例えば $\text{In-Ga-Zn-O}$ 膜を成膜する場合には、 $\text{In}(\text{CH}_3)_3$ ガスと $\text{O}_3$ ガスを順次繰り返し導入して $\text{In-O}$ 層を形成し、その後、 $\text{Ga}(\text{CH}_3)_3$ ガスと $\text{O}_3$ ガスを同時に導入して $\text{GaO}$ 層を形成し、更にその後 $\text{Zn}(\text{CH}_3)_2$ ガスと $\text{O}_3$ ガスを同時に導入して $\text{ZnO}$ 層を形成する。なお、これらの層の順番はこの例に限らない。また、これらのガスを混ぜて $\text{In-Ga-O}$ 層や $\text{In-Zn-O}$ 層、 $\text{Ga-Zn-O}$ 層などの混合化合物層を形成しても良い。なお、 $\text{O}_3$ ガスに変えて $\text{Ar}$ 等の不活性ガスでバーピングして得られた $\text{H}_2\text{O}$ ガスを用いても良いが、Hを含まない $\text{O}_3$ ガスを用いる方が好ましい。また、 $\text{In}(\text{CH}_3)_3$ ガスにかえて、 $\text{In}(\text{C}_2\text{H}_5)_3$ ガスを用いても良い。また、 $\text{Ga}(\text{CH}_3)_3$ ガスにかえて、 $\text{Ga}(\text{C}_2\text{H}_5)_3$ ガスを用いても良い。また、 $\text{Zn}(\text{CH}_3)_2$ ガスを用いても良い。

#### 【0274】

なお、本実施の形態は、他の実施の形態と適宜組み合わせて実施することができる。

#### 【0275】

##### (実施の形態7)

本発明の一態様に係る半導体装置は、表示機器、パーソナルコンピュータ、記録媒体を備えた画像再生装置（代表的にはDVD：Digital Versatile Disc等の記録媒体を再生し、その画像を表示しうるディスプレイを有する装置）に用いることができる。その他に、本発明の一態様に係る半導体装置を用いることができる電子機器として、携帯電話、携帯型を含むゲーム機、携帯情報端末、電子書籍端末、ビデオカメラ、デジタルスチルカメラ等のカメラ、ゴーグル型ディスプレイ（ヘッドマウントディスプレ

10

20

30

40

50

イ)、ナビゲーションシステム、音響再生装置（カーオーディオ、デジタルオーディオプレイヤー等）、複写機、ファクシミリ、プリンタ、プリンタ複合機、現金自動預け入れ払い機（ATM）、自動販売機、医療機器などが挙げられる。これら電子機器の具体例を図17に示す。

#### 【0276】

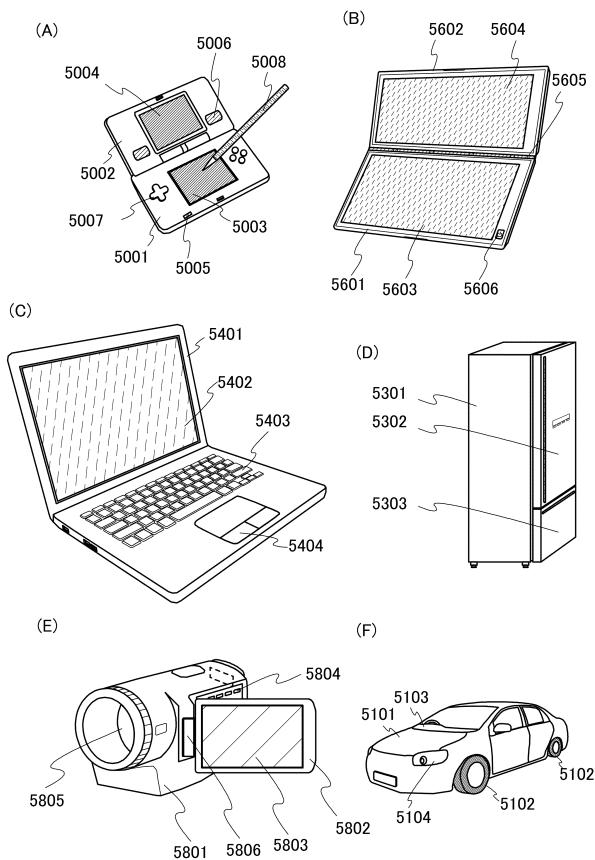

図17（A）は携帯型ゲーム機であり、筐体5001、筐体5002、表示部5003、表示部5004、マイクロホン5005、スピーカー5006、操作キー5007、スタイルス5008等を有する。本発明の一態様にかかる半導体装置は、携帯型ゲーム機の各種集積回路に用いることができる。なお、図17（A）に示した携帯型ゲーム機は、2つの表示部5003と表示部5004とを有しているが、携帯型ゲーム機が有する表示部の数は、これに限定されない。10

#### 【0277】

図17（B）は携帯情報端末であり、第1筐体5601、第2筐体5602、第1表示部5603、第2表示部5604、接続部5605、操作キー5606等を有する。本発明の一態様にかかる半導体装置は、携帯情報端末の各種集積回路に用いることができる。第1表示部5603は第1筐体5601に設けられており、第2表示部5604は第2筐体5602に設けられている。そして、第1筐体5601と第2筐体5602とは、接続部5605により接続されており、第1筐体5601と第2筐体5602の間の角度は、接続部5605により変更が可能である。第1表示部5603における映像を、接続部5605における第1筐体5601と第2筐体5602との間の角度に従って、切り替える構成としても良い。また、第1表示部5603及び第2表示部5604の少なくとも一方に、位置入力装置としての機能が付加された表示装置を用いるようにしても良い。なお、位置入力装置としての機能は、表示装置にタッチパネルを設けることで付加することができる。或いは、位置入力装置としての機能は、フォトセンサとも呼ばれる光電変換素子を表示装置の画素部に設けることでも、付加することができる。20

#### 【0278】

図17（C）はノート型パーソナルコンピュータであり、筐体5401、表示部5402、キーボード5403、ポインティングデバイス5404等を有する。本発明の一態様にかかる半導体装置は、ノート型パーソナルコンピュータの各種集積回路に用いることができる。30

#### 【0279】

図17（D）は電気冷凍冷蔵庫であり、筐体5301、冷蔵室用扉5302、冷凍室用扉5303等を有する。本発明の一態様にかかる半導体装置は、電気冷凍冷蔵庫の各種集積回路に用いることができる。

#### 【0280】

図17（E）はビデオカメラであり、第1筐体5801、第2筐体5802、表示部5803、操作キー5804、レンズ5805、接続部5806等を有する。本発明の一態様にかかる半導体装置は、ビデオカメラの各種集積回路に用いることができる。操作キー5804及びレンズ5805は第1筐体5801に設けられており、表示部5803は第2筐体5802に設けられている。そして、第1筐体5801と第2筐体5802とは、接続部5806により接続されており、第1筐体5801と第2筐体5802の間の角度は、接続部5806により変更が可能である。表示部5803における映像を、接続部5806における第1筐体5801と第2筐体5802との間の角度に従って切り替える構成としても良い。40

#### 【0281】

図17（F）は普通自動車であり、車体5101、車輪5102、ダッシュボード5103、ライト5104等を有する。本発明の一態様にかかる半導体装置は、普通自動車の各種集積回路に用いることができる。

#### 【0282】

なお、本実施の形態は、他の実施の形態と適宜組み合わせて実施することができる。50

## 【符号の説明】

## 【0283】

|         |         |    |

|---------|---------|----|

| 1 0     | 半導体装置   |    |

| 2 0     | 回路      |    |

| 3 0     | 回路      |    |

| 3 1     | 回路      |    |

| 3 2     | 回路      |    |

| 4 0     | 回路      |    |

| 4 1     | 回路      |    |

| 4 2     | 回路      | 10 |

| 9 0     | トランジスタ  |    |

| 9 1     | 絶縁膜     |    |

| 9 2 a   | 酸化物半導体膜 |    |

| 9 2 b   | 酸化物半導体膜 |    |

| 9 2 c   | 酸化物半導体膜 |    |

| 9 3     | 導電膜     |    |

| 9 4     | 導電膜     |    |

| 9 5     | 絶縁膜     |    |

| 9 6     | 導電膜     |    |

| 9 7     | 基板      | 20 |

| 1 0 0   | 基板      |    |

| 1 0 1   | 絶縁層     |    |

| 1 0 2   | 絶縁層     |    |

| 1 1 1   | 導電層     |    |

| 1 1 2   | 導電層     |    |

| 1 1 3   | 導電層     |    |

| 1 2 0   | 回路      |    |

| 1 3 0   | 回路      |    |

| 1 4 0   | 回路      |    |

| 2 0 0   | 回路      | 30 |

| 2 1 0   | 回路      |    |

| 2 1 0 a | 記憶回路    |    |

| 2 1 0 b | 記憶回路    |    |

| 2 2 0   | 回路      |    |

| 2 3 0   | 回路      |    |

| 2 4 0   | 回路      |    |

| 3 1 0   | 配線      |    |

| 3 1 0 a | 配線      |    |

| 3 1 0 b | 配線      |    |

| 3 2 0   | 配線      | 40 |

| 3 3 0   | 配線      |    |

| 3 4 0   | 配線      |    |

| 4 0 1   | 配線      |    |

| 4 0 2   | 配線      |    |

| 4 0 3   | 配線      |    |

| 4 0 4   | 配線      |    |

| 4 0 5   | 配線      |    |

| 4 0 6   | 配線      |    |

| 4 0 7   | 配線      |    |

| 4 1 0   | 回路      | 50 |

|       |         |    |

|-------|---------|----|

| 4 1 1 | トランジスタ  |    |

| 4 1 2 | トランジスタ  |    |

| 4 2 0 | 回路      |    |

| 4 2 1 | トランジスタ  |    |

| 4 2 2 | トランジスタ  |    |

| 4 2 3 | トランジスタ  |    |

| 4 3 0 | 回路      |    |

| 4 3 1 | トランジスタ  |    |

| 4 3 2 | トランジスタ  |    |

| 4 3 3 | トランジスタ  | 10 |

| 4 3 4 | トランジスタ  |    |

| 4 3 5 | トランジスタ  |    |

| 4 3 6 | トランジスタ  |    |

| 4 3 7 | 容量素子    |    |

| 4 3 8 | 容量素子    |    |

| 4 4 1 | トランジスタ  |    |

| 4 4 2 | 容量素子    |    |

| 5 0 1 | トランジスタ  |    |

| 5 0 2 | トランジスタ  |    |

| 5 0 3 | トランジスタ  | 20 |

| 5 0 4 | トランジスタ  |    |

| 5 1 1 | 配線      |    |

| 5 1 2 | 配線      |    |

| 5 1 3 | 配線      |    |

| 6 0 0 | 半導体基板   |    |

| 6 0 1 | 絶縁物     |    |

| 6 0 2 | ウェル     |    |

| 6 0 3 | ゲート絶縁膜  |    |

| 6 0 4 | ゲート電極   |    |

| 6 0 5 | 不純物領域   | 30 |

| 6 0 6 | 絶縁層     |    |

| 6 0 7 | 酸化物半導体層 |    |

| 6 0 8 | 配線      |    |

| 6 0 9 | ゲート絶縁膜  |    |

| 6 1 0 | ゲート電極   |    |

| 6 1 1 | 絶縁層     |    |

| 6 1 2 | 配線      |    |

| 6 2 0 | トランジスタ  |    |

| 6 3 0 | トランジスタ  |    |

| 8 0 1 | 半導体基板   | 40 |

| 8 1 0 | 素子分離領域  |    |

| 8 1 1 | 絶縁膜     |    |

| 8 1 2 | 絶縁膜     |    |

| 8 1 3 | 絶縁膜     |    |

| 8 2 5 | 導電膜     |    |

| 8 2 6 | 導電膜     |    |

| 8 2 7 | 導電膜     |    |

| 8 3 4 | 導電膜     |    |

| 8 3 5 | 導電膜     |    |

| 8 3 6 | 導電膜     | 50 |

|           |          |    |

|-----------|----------|----|

| 8 3 7     | 導電膜      |    |

| 8 4 4     | 導電膜      |    |

| 8 5 1     | 導電膜      |    |

| 8 5 2     | 導電膜      |    |

| 8 5 3     | 導電膜      |    |

| 8 6 1     | 絶縁膜      |    |

| 8 6 2     | ゲート絶縁膜   |    |

| 8 6 3     | 絶縁膜      |    |

| 9 0 1     | 半導体膜     |    |

| 9 1 0     | 領域       | 10 |

| 9 1 1     | 領域       |    |

| 9 2 1     | 導電膜      |    |

| 9 2 2     | 導電膜      |    |

| 9 3 1     | ゲート電極    |    |

| 1 0 0 0   | 基板       |    |

| 1 0 0 1   | 素子分離領域   |    |

| 1 0 0 2   | 不純物領域    |    |

| 1 0 0 3   | 不純物領域    |    |

| 1 0 0 4   | チャネル形成領域 |    |

| 1 0 0 5   | 絶縁膜      | 20 |

| 1 0 0 6   | ゲート電極    |    |

| 1 0 1 1   | 絶縁膜      |    |

| 1 0 1 2   | 導電膜      |    |

| 1 0 1 3   | 導電膜      |    |

| 1 0 1 4   | 導電膜      |    |

| 1 0 1 6   | 導電膜      |    |

| 1 0 1 7   | 導電膜      |    |

| 1 0 1 8   | 導電膜      |    |

| 1 0 2 0   | 絶縁膜      |    |

| 1 0 2 1   | 絶縁膜      | 30 |

| 1 0 2 2   | 絶縁膜      |    |

| 1 0 3 0   | 半導体膜     |    |

| 1 0 3 0 a | 酸化物半導体膜  |    |

| 1 0 3 0 c | 酸化物半導体膜  |    |

| 1 0 3 1   | ゲート絶縁膜   |    |

| 1 0 3 2   | 導電膜      |    |

| 1 0 3 3   | 導電膜      |    |

| 1 0 3 4   | ゲート電極    |    |

| 5 0 0 1   | 筐体       |    |

| 5 0 0 2   | 筐体       | 40 |

| 5 0 0 3   | 表示部      |    |

| 5 0 0 4   | 表示部      |    |

| 5 0 0 5   | マイクロホン   |    |

| 5 0 0 6   | スピーカー    |    |

| 5 0 0 7   | 操作キー     |    |

| 5 0 0 8   | スタイラス    |    |

| 5 1 0 1   | 車体       |    |

| 5 1 0 2   | 車輪       |    |

| 5 1 0 3   | ダッシュボード  |    |

| 5 1 0 4   | ライト      | 50 |

|         |             |

|---------|-------------|

| 5 3 0 1 | 筐体          |

| 5 3 0 2 | 冷蔵室用扉       |

| 5 3 0 3 | 冷凍室用扉       |

| 5 4 0 1 | 筐体          |

| 5 4 0 2 | 表示部         |

| 5 4 0 3 | キー ボード      |

| 5 4 0 4 | ポインティングデバイス |

| 5 6 0 1 | 筐体          |

| 5 6 0 2 | 筐体          |

| 5 6 0 3 | 表示部         |

| 5 6 0 4 | 表示部         |

| 5 6 0 5 | 接続部         |

| 5 6 0 6 | 操作キー        |

| 5 8 0 1 | 筐体          |

| 5 8 0 2 | 筐体          |

| 5 8 0 3 | 表示部         |

| 5 8 0 4 | 操作キー        |

| 5 8 0 5 | レンズ         |

| 5 8 0 6 | 接続部         |

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

## フロントページの続き

| (51)Int.Cl. |         | F I       |        |               |

|-------------|---------|-----------|--------|---------------|

| H 01 L      | 21/28   | (2006.01) | H 01 L | 29/58 G       |

| H 01 L      | 29/417  | (2006.01) | H 01 L | 29/78 6 1 3 B |

| H 01 L      | 29/423  | (2006.01) | H 01 L | 29/78 6 1 8 B |

| H 01 L      | 29/49   | (2006.01) | G 11 C | 11/4063       |

| H 01 L      | 29/786  | (2006.01) | G 11 C | 11/4091 1 2 0 |

| G 11 C      | 11/4063 | (2006.01) |        |               |

| G 11 C      | 11/4091 | (2006.01) |        |               |

(72)発明者 松島 隆徳

神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内

(72)発明者 井上 広樹

神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内

(72)発明者 長塚 修平

神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内

(72)発明者 八窪 裕人

神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内

審査官 小山 満

|          |                                |

|----------|--------------------------------|

| (56)参考文献 | 特開2012-257203 (JP, A)          |

|          | 特開2011-129889 (JP, A)          |

|          | 特開2013-093594 (JP, A)          |

|          | 特開2009-071313 (JP, A)          |

|          | 特開2011-151383 (JP, A)          |

|          | 米国特許出願公開第2012/0262983 (US, A1) |

|          | 米国特許出願公開第2011/0114946 (US, A1) |

|          | 国際公開第2011/062029 (WO, A1)      |

|          | 米国特許出願公開第2011/0108836 (US, A1) |

|          | 国際公開第2011/055626 (WO, A1)      |

|          | 欧州特許出願公開第03051588 (EP, A1)     |

|          | 米国特許出願公開第2009/0086525 (US, A1) |

|          | 欧州特許出願公開第02037461 (EP, A2)     |

|          | 米国特許出願公開第2011/0156027 (US, A1) |

|          | 国際公開第2011/077967 (WO, A1)      |

(58)調査した分野(Int.Cl., DB名)

H 01 L 27 / 10

G 11 C 11 / 4063

G 11 C 11 / 4091

H 01 L 21 / 28

H 01 L 21 / 8239

H 01 L 21 / 8242

H 01 L 27 / 105

H 01 L 27 / 108

H 01 L 29 / 417

H 01 L 29 / 423

H 01 L 29 / 49

(47)

JP 6635670 B2 2020.1.29

H 0 1 L 2 9 / 7 8 6