(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5154033号

(P5154033)

(45) 発行日 平成25年2月27日(2013.2.27)

(24) 登録日 平成24年12月14日(2012.12.14)

(51) Int.Cl.

F 1

|      |        |           |      |           |

|------|--------|-----------|------|-----------|

| G09G | 3/36   | (2006.01) | G09G | 3/36      |

| G02F | 1/1368 | (2006.01) | G02F | 1/1368    |

| G02F | 1/1345 | (2006.01) | G02F | 1/1345    |

| G09F | 9/30   | (2006.01) | G09F | 9/30 338  |

| G09G | 3/20   | (2006.01) | G09G | 3/20 670A |

請求項の数 10 (全 18 頁) 最終頁に続く

(21) 出願番号 特願2006-156997 (P2006-156997)

(22) 出願日 平成18年6月6日 (2006.6.6)

(65) 公開番号 特開2006-343746 (P2006-343746A)

(43) 公開日 平成18年12月21日 (2006.12.21)

審査請求日 平成21年5月19日 (2009.5.19)

(31) 優先権主張番号 10-2005-0048299

(32) 優先日 平成17年6月7日 (2005.6.7)

(33) 優先権主張国 韓国 (KR)

(31) 優先権主張番号 10-2005-0074963

(32) 優先日 平成17年8月16日 (2005.8.16)

(33) 優先権主張国 韓国 (KR)

(73) 特許権者 390019839

三星電子株式会社

Samsung Electronics

Co., Ltd.

大韓民国京畿道水原市靈通区三星路 129

129, Samsung-ro, Yeongtong-gu, Suwon-si, Gyeonggi-do, Republic

of Korea

(74) 代理人 100121382

弁理士 山下 託嗣

(74) 代理人 100094145

弁理士 小野 由己男

(74) 代理人 100106367

弁理士 稲積 朋子

最終頁に続く

(54) 【発明の名称】表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

スイッチング素子を各々含む複数の画素、

前記スイッチング素子に連結されているゲート線、

前記ゲート線の各々の一端に一つずつ連結されていて、前記ゲート線に対して順番にゲート信号を出力する複数のステージを含む主ゲート駆動部、及び、

順番にゲート信号を出力する複数のステージ、を含む副ゲート駆動部を有し、

各ゲート線は、同一のゲート信号を伝達し、かつ互いに分離されている第1部分及び第2部分と、前記第1部分と前記第2部分との間に位置し、かつ前記第1部分及び前記第2部分を必要によって互いに導通させることができるスイッチング部とを含み、

前記主ゲート駆動部の全てのステージが正常に動作しているときには、前記副ゲート駆動部は動作せず、

前記第1部分は前記主ゲート駆動部のいずれか1つのステージに連結され、

前記第2部分は前記第1部分に連結される前記ステージと同一なゲート信号を出力する副ゲート駆動部のいずれか1つのステージに連結されており、

前記ゲート線の前記第1部分及び前記第2部分のそれぞれは、前記ゲート線と、直後のゲート線を駆動するステージに入力されるキャリー信号を伝達するキャリー信号線とを必要に応じて短絡させるための短絡部を有する表示装置。

## 【請求項 2】

前記主ゲート駆動部のステージのいずれかがゲート信号を生成できない不良ステージを

10

20

有する場合、前記不良ステージと対応する前記副ゲート駆動部のステージを代替ステージとするため、前記不良ステージに連結されている前記ゲート線の前記第1部分と前記第2部分とを前記スイッチング部を通じて連結して導通させる請求項1に記載の表示装置。

**【請求項3】**

前記スイッチング部の別の一つが、前記不良ステージの直前のステージに連結されている前記ゲート線の前記第1部分と前記代替ステージの直前のステージに連結されている前記ゲート線の前記第2部分との間を前記スイッチング部を通じて導通させる請求項2に記載の表示装置。

**【請求項4】**

前記不良ステージから前記ゲート線の一端へゲート信号を伝達するための配線が途中で切斷され、10

前記不良ステージからその前後のステージへキャリー信号を伝達するためのキャリー信号線が途中で切斷され、

前記不良ステージから切斷された前記ゲート線の一端が、前記不良ステージからその前後のステージへキャリー信号を伝達するためのキャリー信号線、への短絡により前記不良ステージの前後のステージに連結され、

前記代替ステージへその直前のステージからキャリー信号を伝達するための信号線が途中で切斷され、

前記代替ステージの直前のステージから前記スイッチング部の別の一つへゲート信号を伝達するための配線が途中で切斷され、20

前記代替ステージの直前のステージから切斷された前記スイッチング部の別の一つが、前記代替ステージへその直前のステージからキャリー信号を伝達するためのキャリー信号線、への短絡により前記代替ステージに連結されている請求項3に記載の表示装置。

**【請求項5】**

前記代替ステージからその前後のステージへキャリー信号を伝達するためのキャリー信号線が切斷されている請求項4に記載の表示装置。

**【請求項6】**

前記主ゲート駆動部のステージと前記副ゲート駆動部のステージとのそれぞれが、セット端子、リセット端子、ゲートオフ電圧端子、第1出力端子、第2出力端子、第1クロック端子及び第2クロック端子を含む請求項1～5のいずれかに記載の表示装置。30

**【請求項7】**

前記画素、前記ゲート線、前記主ゲート駆動部及び前記副ゲート駆動部が同じ表示パネルに集積化されている請求項1から6のいずれか1つに記載の表示装置。

**【請求項8】**

前記表示パネルが駆動回路チップを更に含む請求項7に記載の表示装置。

**【請求項9】**

前記画素に連結されているデータ線、

データ電圧を前記データ線に対して印加するデータ駆動部、並びに、

前記主ゲート駆動部、前記副ゲート駆動部、及び前記データ駆動部に対して制御信号を印加する信号制御部を更に有する請求項1から7のいずれか1つに記載の表示装置。40

**【請求項10】**

前記表示パネルが、前記画素に連結されているデータ線を含み、

前記駆動回路チップが、

データ電圧を前記データ線に対して印加するデータ駆動部、並びに、

前記主ゲート駆動部、前記副ゲート駆動部、及び前記データ駆動部に対して制御信号を印加する信号制御部を含む請求項8に記載の表示装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は表示装置に関し、特にその駆動回路に関する。

50

**【背景技術】****【0002】**

陰極線管 (cathode ray tube、CRT) を用いた表示装置とは異なり、平板表示装置（プラズマ表示装置（PDP）、液晶表示装置（LCD）、有機発光（有機EL）表示装置等）は小型化や軽量化が著しく容易であるので、携帯電話などの携帯型電子機器への搭載が容易である。近年、特に折り畳み式携帯電話用の小型表示装置としてデュアル表示装置の開発が活発である。デュアル表示装置は表と裏との両面に表示パネルを含み、それらを共通の駆動回路で制御する。それにより、特に携帯電話の更なる小型化や薄型化を図っている。

**【0003】**

10

液晶表示装置及び有機発光表示装置では特に、各画素がスイッチング素子を含む。ゲート駆動部がゲート線を通して各画素のスイッチング素子を導通させると、データ駆動部によりデータ線に対して印加されたデータ電圧が、その導通したスイッチング素子を通して各画素に伝達される。それにより、各画素がそのデータ電圧に応じた輝度で発光する。

**【0004】**

ゲート駆動部は実質的にシフトレジスタであり、一列に並んだ複数のステージを含む。各ステージが一つのゲート線に連結され、更に前後のステージに連結されている。各ステージがゲート線に対してゲート信号を出力するとき、同時に、次のステージにキャリー信号を出力する。次のステージはそのキャリー信号に応じ、ゲート信号と、更に次のステージへのキャリー信号とを出力する。こうして、複数のステージが一つずつ順番に、ゲート線に対して信号（ゲート信号）を出力する。

20

**【発明の開示】****【発明が解決しようとする課題】****【0005】**

従来の表示装置では、表示領域の外側を囲む周辺領域に複数の修理線が予め設置されている。例えばゲート線が断線などの不良部位を含む場合、その不良部位の左右を修理線で短絡してバイパスを形成する。それにより、ゲート信号がその不良部位を越えてゲート線の全体に伝達される。

しかし、特に中小型表示装置の場合、ゲート線が極めて細く、かつ間隔が狭いので、ゲート線の修理では、虫眼鏡を使用しながら、不良部位の探索やレーザー照射による結線を行わねばならない。従って、修理時間の短縮が困難である。更に、周辺領域に設置可能な修理線の数には限界があるので、不良部位が多い場合には修理が不可能である。

30

**【0006】**

従来の表示装置では、ゲート駆動部のいずれかのステージに欠陥があり、ゲート信号を出力できない場合、それ以降のステージもゲート信号を出力できないので、結局、ゲート駆動部全体が機能を失う。この不具合を修理で除去することは、従来の表示装置では困難である。

本発明の目的は、ゲート線に断線等の不良部位が含まれる場合、又はゲート駆動部のいずれかのステージが機能しない場合、簡単な修理だけで正常な機能を迅速に回復できる表示装置の提供にある。

40

**【課題を解決するための手段】****【0007】**

本発明の一つの観点による表示装置は、

スイッチング素子を各々含む複数の画素、

スイッチング素子に連結されているゲート線、

ゲート線の各々の一端に一つずつ連結されていて、ゲート線に対して順番にゲート信号を出力する複数のステージ、を含む第1ゲート駆動部、及び、

ゲート線の各々の他端に一つずつ連結されていて、ゲート線に対して順番にゲート信号を出力する複数のステージ、を含む第2ゲート駆動部、

を有する。第1ゲート駆動部及び第2ゲート駆動部では好ましくは、同じゲート線に連結

50

されているステージが同じ時間にゲート信号を出力する。

**【0008】**

本発明の他の観点による表示装置は、

スイッチング素子を各々含む複数の画素、

そのスイッチング素子に連結されているゲート線、

ゲート線の各々の一端に一つずつ連結されていて、ゲート線に対して順番にゲート信号

を出力する複数のステージ、を含む主ゲート駆動部、

順番にゲート信号を出力する複数のステージ、を含む副ゲート駆動部、及び、

副ゲート駆動部のステージを一つずつ、ゲート線の各々の他端に連結するスイッチング

部、を有する。

10

**【0009】**

本発明によるこの表示装置では好ましくは、主ゲート駆動部のステージのいずれかがゲ

ート信号を生成できない不良ステージである場合、スイッチング部の一つが、その不良ス

テージに連結されているゲート線の他端と副ゲート駆動部のステージの一つ（以下、代替

ステージという）との間を導通させる。更に好ましくは、スイッチング部の別の一つが、

不良ステージの直前のステージに連結されているゲート線の他端と代替ステージとの間を

導通させる。その上で、

不良ステージからゲート線の一端へゲート信号を伝達するための配線が途中で切断され、

不良ステージからその前後のステージへキャリー信号を伝達するためのキャリー信号線が

途中で切断され、

20

不良ステージから切断されたゲート線の一端が、不良ステージからその前後のステージへ

キャリー信号を伝達するためのキャリー信号線、への短絡により不良ステージの前後のス

テージに連結され、

代替ステージへその直前のステージからキャリー信号を伝達するための信号線が途中で切

断され、

代替ステージの直前のステージからスイッチング部の別の一つへゲート信号を伝達するた

めの配線が途中で切断され、

代替ステージの直前のステージから切断されたスイッチング部の別の一つが、代替ステ

ージへその直前のステージからキャリー信号を伝達するためのキャリー信号線、への短絡に

より代替ステージに連結されている。

30

**【発明の効果】**

**【0010】**

本発明の一つの観点による表示装置では、各ゲート線の両端に一つずつゲート駆動部が

連結され、同じゲート線に対してゲート信号を同時に output する。それにより、ゲート線が

途中で断線していても、ゲート線の全体にゲート信号が伝達される。従って、従来の表示

装置とは異なり、断線部位の両側にレーザー照射でバイパスを結線する必要がない。

本発明の他の観点による表示装置では、各ゲート線の一端に主ゲート駆動部のステージ

が一つずつ連結され、各ゲート線の他端に、スイッチング部を介して副ゲート駆動部のス

テージが一つずつ連結されている。それにより、主ゲート駆動部のいずれかのステージに

欠陥がある場合、その不良ステージに連結されたスイッチング部を導通させることにより

、その不良ステージを副ゲート駆動部のステージで容易に代替できる。

40

こうして、本発明による表示装置では、ゲート線やゲート駆動部の修理について、作業

時間及び費用が削減されるので、生産性が更に向上する。

**【発明を実施するための最良の形態】**

**【0011】**

以下、本発明の好ましい実施例による表示装置について、添付した図面を参照しながら

詳細に説明する。

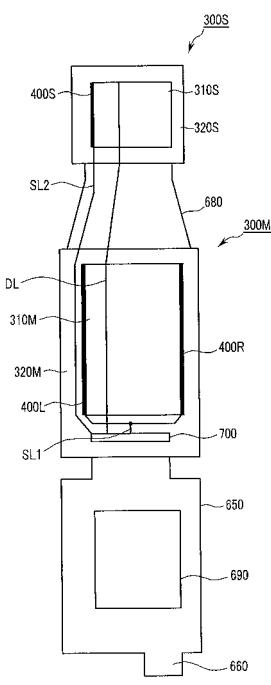

本発明の一つの実施例による液晶表示装置は好ましくはデュアル表示装置であり、更に

好ましくは折り畳み式携帯電話に搭載される。図1にその展開図を示す。この液晶表示装

置は、FPC (flexible printed circuit film) 650、補助FPC 680、主表示パネル

50

300M、副表示パネル300S、及び統合チップ700を有する。

#### 【0012】

FPC650は、主表示パネル300Mの一辺の近くに接着されている（図1参照）。液晶表示装置が携帯電話に組み込まれるとき、FPC650はその接着部付近で折り曲げられ、主表示パネル300Mの画面の上に重ねられる。FPC650は特に開口部690を含む。FPC650が折り曲げられた時、その開口部690の内側から主表示パネル300Mの一部が露出する。主表示パネル300Mに接着された辺とは反対側にあるFPC650の一辺には入力部660が形成されていて、そこに外部から信号が入力される。FPC650には更に複数の信号線が形成されている（図示せず）。それらの信号線が入力部660を統合チップ700や主表示パネル300Mに連結されている。それらの信号線は好ましくは、統合チップ700に連結される箇所や主表示パネル300Mに接着される箇所に、幅の広いパッドを含む（図示せず）。

10

#### 【0013】

補助FPC680は、FPC650が接着された辺とは反対側にある主表示パネル300Mの一辺と、副表示パネル300Sの一辺との間に接着されている（図1参照）。液晶表示装置が携帯電話に組み込まれるとき、補助FPC680は折り曲げられ、主表示パネル300Mの裏側（すなわち、FPC650とは反対側）に重ねられる。補助FPC680には特に複数の信号線SL2、DLが形成され、統合チップ700と副表示パネル300Sとの間を連結している。

#### 【0014】

主表示パネル300Mは、表示領域（すなわち画面）310M及び周辺領域320Mを含む（図1参照）。周辺領域320Mには、光を遮断する遮光層（ブラックマトリックス）が形成されても良い（図示せず）。その場合、FPC650及び補助FPC680がその遮光層に接着される。副表示パネル300Sは主表示パネル300Mと同様な構造であり、表示領域（すなわち画面）310S及び周辺領域320Sを含む。但し、副表示パネル300Sのサイズは主表示パネル300Mのサイズより小さい。周辺領域320Sには、光を遮断する遮光層（ブラックマトリックス）が形成されても良い（図示せず）。その場合、補助FPC680はその遮光層に接着される。液晶表示装置が携帯電話に組み込まれるとき、補助FPC680が折り曲げられることにより、副表示パネル300Sの裏側（すなわち、その画面とは反対側）が主表示パネル300Mの裏側（すなわち、その画面とは反対側）に重ねられる。それにより、主表示パネル300Mの画面が折り畳み式携帯電話の内面から見え、副表示パネル300Sがその携帯電話の外から見える。

20

#### 【0015】

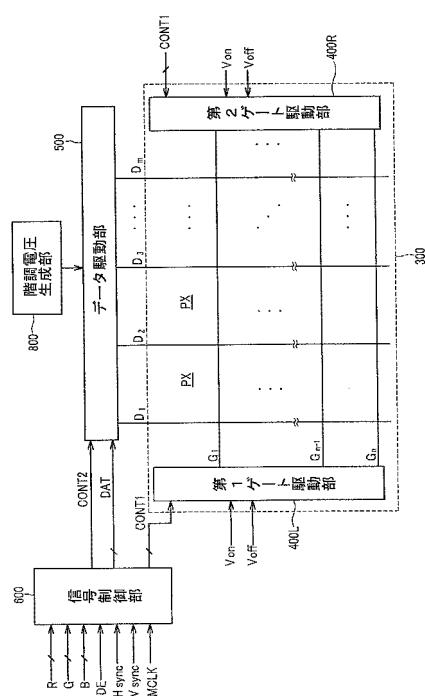

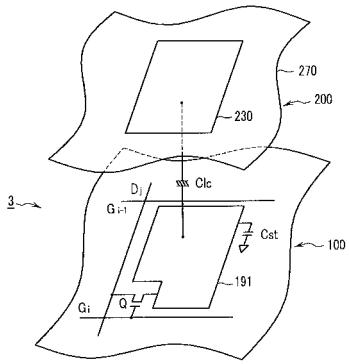

図2に示されているように、各表示パネル300（300M又は300S）は、n本（ $n > 1$ ）のゲート線G<sub>1</sub> - G<sub>n</sub>、m本（ $m > 1$ ）のデータ線D<sub>1</sub> - D<sub>m</sub>、及び画素PXのマトリックスを含む。主表示パネル300Mは更に、第1ゲート駆動部400Lと第2ゲート駆動部400Rとを含む。一方、副表示パネル300Sはゲート駆動部400Sを一つだけ含む（図1参照）。尚、副表示パネル300Sが主表示パネル300Mと同様に、一対のゲート駆動部を含んでも良い。好ましくは、副表示パネル300Sでは主表示パネル300Mより、ゲート線とデータ線との各本数が少ない。各表示パネル300M、300Sは、図3に示されているように、互いに対向している下部表示パネル100と上部表示パネル200、及びそれら二枚の表示パネルの間に挟まれた液晶層3を含む。画素PXのマトリックス、ゲート線G<sub>1</sub> - G<sub>n</sub>の大部分、及びデータ線D<sub>1</sub> - D<sub>m</sub>の大部分は各表示領域310M、310Sに位置する。各ゲート駆動部400L、400R、400Sは各周辺領域320M、320Sに位置する。各周辺領域320M、320Sでは好ましくは、各ゲート駆動部400L、400R、400Sが位置する部分の幅が広い。

30

#### 【0016】

好ましくは、図1に示されているように、主表示パネル300Mのデータ線D<sub>1</sub> - D<sub>m</sub>の一部DLが補助FPC680を通じて副表示パネル300Sのデータ線の一つに連結されている。つまり、二つの表示パネル300M、300S間では、データ線D<sub>1</sub> - D<sub>m</sub>のいくつかDLが共有されている。好ましくは上部表示パネル200が下部表示パネル100より小さいので、下部表示パネル100の周辺領域の一部が露出している（図3参照）。この露出領域までデータ線D<sub>1</sub> - D<sub>m</sub>が延びてデータ駆動部500に連結されている。一方、ゲート線G<sub>1</sub> - G<sub>n</sub>は各周辺領域320M、320Sま

40

50

で延びて各ゲート駆動部400R、400L、400Sに連結されている。好ましくは、ゲート線 $G_1 - G_n$ とデータ線 $D_1 - D_m$ とがそれぞれ、FPC650や補助FPC680に連結される箇所で幅の広いパッドを構成している（図示せず）。更に好ましくは、各表示パネル300M、300S、及び各FPC650、680が異方性導電膜（図示せず）に接着され、それを通して上記のパッドに連結されている。

#### 【0017】

図3に示されているように、各画素PXは、スイッチング素子Q、液晶キャパシタClc、及びストレージキャパシタCstを含む。ストレージキャパシタCstは、必要に応じて省略されても良い。スイッチング素子Qは好ましくは、下部表示パネル100に形成されている薄膜トランジスタであり、その制御端子がゲート線の一つ $G_i$  ( $i = 1, 2, \dots, n$ ) に連結され、入力端子がデータ線 $D_j$  の一つ ( $j = 1, 2, \dots, m$ ) に連結され、出力端子が液晶キャパシタClc及びストレージキャパシタCstに連結されている。スイッチング素子Qはゲート線 $G_i$  を伝わるゲート信号に応じてオンオフし、データ線 $D_j$  と液晶キャパシタClc（又はストレージキャパシタCst）との間を導通させ、又は遮断する。

10

#### 【0018】

液晶キャパシタClcは、下部表示パネル100に形成された画素電極191と、上部表示パネル200に形成された共通電極270とを二つの端子として含む。更に、それら二つの電極191、270の間に挟まれた液晶層3の部分が誘電体として機能する。画素電極191はスイッチング素子Qを通してデータ線 $D_j$  に連結され、データ電圧を受ける。共通電極270は上部表示パネル200の全面を覆い、外部から一定の電圧（共通電圧）を受ける。尚、図3とは異なり、共通電極270が下部表示パネル100に形成されても良い。その場合、二つの電極191、270のうち、少なくとも一つが線状又は棒状に形成される。

20

#### 【0019】

ストレージキャパシタCstは、下部表示パネル100に形成された別の信号線（図示せず）と画素電極191とが絶縁体を間に挟んで重なっている部分から構成されている。この別の信号線には外部から一定の電圧（好ましくは共通電圧）が印加される。ストレージキャパシタCstは液晶キャパシタClcを補助し、その両端電圧を所定時間（好ましくは1フレームの間）安定化させる。尚、ストレージキャパシタCstが、絶縁体を間に挟んで重なっている画素電極191と前段のゲート線 $G_{i-1}$  とから構成されていても良い。

30

#### 【0020】

好ましくは、各画素PXの色が基本色の一つに固定されている（空間分割方式）。その他に、各画素PXの色が時間の経過に伴って様々な基本色に変化しても良い（時間分割方式）。そのような基本色の空間的变化又は時間的变化により所望の色相が表現される。ここで、基本色は好ましくは三原色（赤色、緑色、青色）である。図3は空間分割方式の一例であり、液晶層3を隔てて画素電極191に対向している上部表示パネル200の領域に色フィルタ230が形成されている。色フィルタ230の色は画素ごとに異なる。図3とは異なり、色フィルタ230が下部表示パネル100、特に画素電極191の上又は下に形成されていても良い。

30

#### 【0021】

好ましくは、下部表示パネル100と上部表示パネル200との各外面に一つずつ偏光子が接着されている（図示せず）。二枚の偏光子の透過軸は方向が異なり、好ましくは直交している。液晶層3は液晶分子の配列を含み、その液晶分子の配列の異方性に起因する誘電率異方性を示す。それにより、液晶層3を透過する光は偏光方向が回転する。特に液晶層3を透過する光の偏光方向の回転角が上記二枚の偏光子の透過軸間の角度と一致するとき、各表示パネル300M、300Sの透過率が高い。

40

#### 【0022】

主表示パネル300Mでは一対のゲート駆動部400L、400Rが画面の左右に配置され、副表示パネル300Sではゲート駆動部400Sが画面の右側に配置されている（図1参照）。各ゲート駆動部400R、400L、400Sは図1に示されているように、信号線SL1、SL2を通じて統合チップ700に連結されている。各ゲート駆動部400R、400L、400Sは更に図2に示されているようにゲート線 $G_1 - G_n$ に連結され、統合チップ700からのゲート制御信号CONT1に従って各ゲ

50

一ト線に対してゲート信号を出力する。ゲート信号は、各画素PXのスイッチング素子Qを導通させるゲートオン電圧Von、及びそのスイッチング素子Qを遮断させるゲートオフ電圧Voffとの組み合わせから成る。特に主表示パネル300Mでは一対のゲート駆動部400R、400Lが、統合チップ700からの同じ制御信号CONT1に従い、同一のゲート線に対して出力されるゲート信号を同期させる（その詳細については後述する）。各ゲート駆動部400R、400L、400Sは好ましくは、各画素のスイッチング素子Qや信号線SL1、SL2と同じ工程で各表示パネル300M、300Sに集積化される。

#### 【 0 0 2 3 】

統合チップ700は好ましくは主表示パネル300Mに実装された集積回路チップであり、外部（好ましくは、グラフィックコントローラ）から入力部660に入力された画像信号（入力画像信号）を処理し、主表示パネル300M及び副表示パネル300Sに伝達する（図1参照）。統合チップ700は好ましくは、図2に示されているように、信号制御部600、階調電圧生成部800、及びデータ駆動部500を含む。10

#### 【 0 0 2 4 】

信号制御部600は入力部660を通して外部のグラフィックコントローラ（図示せず）から入力画像信号R、G、Bと入力制御信号とを受信する（図2参照）。入力画像信号R、G、Bは各画素PXの輝度情報を含む。入力制御信号は好ましくは、垂直同期信号Vsync、水平同期信号Hsync、メインクロックMCLK、データイネーブル信号DEを含む。信号制御部600は表示パネル300（300M又は300S）の動作条件に合わせて入力画像信号R、G、Bを適切に処理し（例えばガンマ補正を施し）、出力画像信号DATに変換する。好ましくは、出力画像信号DATが画素マトリックスの各行の輝度情報をごとに伝送される。更に好ましくは、主表示パネル300Mに対する1フレームの出力画像信号DATと、副表示パネル300Sに対する1フレームの出力画像信号DATとが交互に出力される。信号制御部600は更に、水平同期信号Hsyncと垂直同期信号Vsyncとに基づいてゲート制御信号CONT1とデータ制御信号CONT2とを生成する。ゲート制御信号CONT1は好ましくは、フレームごとにゲートオン電圧Vonの出力開始を指示する走査開始信号（垂直同期開始信号ともいう）、各フレーム内でゲートオン電圧Vonとゲートオフ電圧Voffとの各タイミングを指示する二つのクロック信号、及び、ゲートオン電圧Vonの持続時間を限定する出力イネーブル信号、を含む。データ制御信号CONT2は好ましくは、画素PXのマトリックスの行ごとに出力画像信号DATの伝送開始を知らせる水平同期開始信号、データ線D<sub>1</sub> - D<sub>m</sub>に対するデータ電圧の印加を指示するロード信号、共通電圧に対するデータ電圧の極性（以下、データ電圧の極性と略す）の反転を指示する反転信号、及びデータクロック信号を含む。20 ゲート制御信号CONT1はゲート駆動部400L、400R、または400Sに送られ、データ制御信号CONT2と出力画像信号DATとはデータ駆動部500に送られる。

#### 【 0 0 2 5 】

階調電圧生成部800は、好ましくは二組の階調電圧の集合を生成する。ここで、各階調電圧のレベルは、画素PXの輝度の階調別（すなわち透過率別）に設定されている。一組の集合は共通電圧に対して正の階調電圧から成り、他の一組は共通電圧に対して負の階調電圧から成る。尚、階調電圧生成部800は二組の階調電圧の集合に代え、基準階調電圧の集合を生成しても良い。各基準階調電圧は一定の電圧であり、好ましくは上記の正（又は負）の階調電圧のいずれよりも高い（又は低い）。その場合、基準階調電圧を分圧することで各階調電圧が得られる。30

#### 【 0 0 2 6 】

データ駆動部500は、主表示パネル300Mのデータ線D<sub>1</sub> - D<sub>m</sub>に連結され、更に補助FPC680に延びているデータ線DLを通し、副表示板部表示パネル300Sのデータ線にも連結されている（図1、2参照）。データ駆動部500は出力画像信号DATに従い、階調電圧生成部800により出力される二組の階調電圧の集合からいずれかの階調電圧を選択する。選択された階調電圧はデータ電圧として、目標の画素PXに連結されたデータ線D<sub>1</sub> - D<sub>m</sub>に対し、データ制御信号CONT2の示すタイミングで印加される。尚、階調電圧生成部800が所定数の基準階調電圧を提供する場合、データ駆動部500は出力画像信号DATに基づいていずれかの基準階4050

調電圧を複数の異なる階調電圧に分圧し、目標の階調に対応する階調電圧をデータ電圧として選択する。データ駆動部500はデータ電圧を、画素マトリックスの行ごとに印加する。更に、好ましくは、主表示パネル300Mの全ての画素に対してデータ電圧が印加された後に、副表示パネル300Sのデータ線に連結されたデータ線DLに対するデータ電圧の印加が開始される。

#### 【0027】

本発明の実施例による上記の液晶表示装置は以下のように表示動作を行う。

まず、信号制御部600が外部のグラフィックコントローラ（図示せず）から入力画像信号R、G、B、及び入力制御信号を受信する（図2参照）。信号制御部600は、入力画像信号R、G、Bを出力画像信号DATに変換し、入力制御信号に基づいてゲート制御信号CONT1及びデータ制御信号CONT2を生成する。10

#### 【0028】

次に、データ駆動部500が、信号制御部600からのデータ制御信号CONT2に従い、画素PXのマトリックスの行ごとに出力画像信号DATを受信する。データ駆動部500はそのとき、出力画像信号DATの示す各画素の輝度情報に基づき、対応する階調電圧をデータ電圧として選択する。データ駆動部500は更にそのデータ電圧を、目標の画素に連結されたデータ線D<sub>1</sub> - D<sub>m</sub>に対して印加する。

#### 【0029】

一方、主表示パネル300Mでは、一対のゲート駆動部400L、400Rがゲート制御信号CONT1に従い、ゲートオン電圧Vonをゲート線G<sub>1</sub> - G<sub>n</sub>に対して順番に一定時間ずつ印加する（図2参照）。特に、一対のゲート駆動部400L、400Rがゲートオン電圧Vonを同じゲート線G<sub>1</sub> - G<sub>n</sub>に対して同時に印加する。更に、主表示パネル300Mの全てのゲート線G<sub>1</sub> - G<sub>n</sub>に対してゲートオン電圧Vonが一回ずつ印加された後に、副表示パネル300Sのゲート駆動部400Sがゲートオン電圧Vonをゲート線に対して順番に一定時間ずつ印加する。尚、ゲートオン電圧Vonの持続時間が経過した後は各ゲート線G<sub>1</sub> - G<sub>n</sub>に対してゲートオフ電圧Voffが印加される。20

#### 【0030】

各ゲート線G<sub>i</sub>に連結された画素PX（図3参照）ではスイッチング素子Qが導通し、データ線D<sub>j</sub>に対して印加されたデータ電圧がスイッチング素子Qを通じて画素電極191に対して印加される。そのデータ電圧と共通電圧との差（画素電圧）により液晶キャパシタClcとストレージキャパシタCstとが充電される。ここで、ストレージキャパシタCstが液晶キャパシタClcの両端電圧（画素電圧）を一フレームの間（特にスイッチング素子Qが遮断された後）、安定に維持する。そのとき、液晶キャパシタClcに含まれている液晶層3の部分では、液晶分子の配向が画素電圧の大きさに応じて変化する。従って、液晶層3の透過により線偏光の受ける回転の角度が変化する。更に、この偏光方向の変化により、上部表示パネル200の外面に接着された偏光子を透過可能な光の量が変化する。その結果、各画素の透過率が変化するので、各画素の輝度が出力画像信号DATの示す階調に調節される。30

#### 【0031】

データ駆動部500によるデータ電圧の印加とゲート駆動部400L、400R、400Sによるゲートオン電圧Vonの印加とは1水平周期（水平同期信号Hsync及びデータイネーブル信号DEの一周期と等しい）ごとに繰り返される。全てのゲート線G<sub>1</sub> - G<sub>n</sub>に対してゲートオン電圧Vonが印加されるとき、全ての画素PXにデータ電圧が印加されるので、1フレームの画像が表示パネル300の画面に表示される。好ましくは、データ駆動部500に伝達される反転信号の制御により、フレームごとにデータ電圧の極性が反転する（フレーム反転）。更に、同じフレーム内でも、画素マトリックスの行ごとにデータ電圧の極性が反転し（例：行反転、ドット反転）、又は隣接する二つのデータ線間でデータ電圧の極性が反転しても良い（例：列反転、ドット反転）。

#### 【0032】

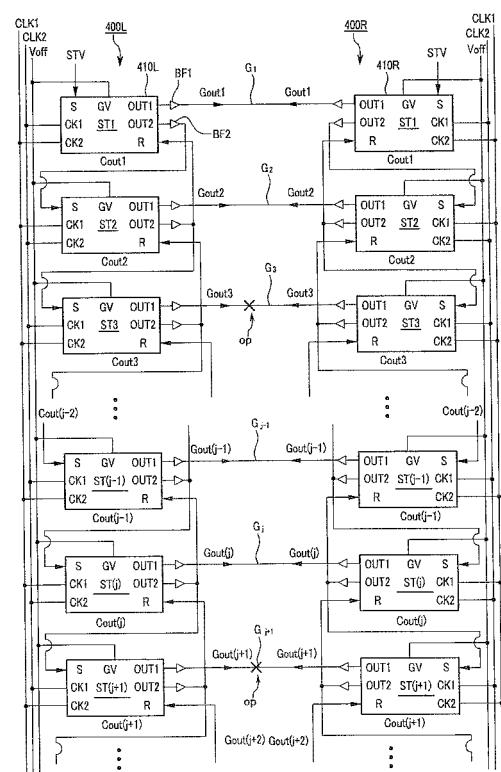

本発明の実施例による上記の表示装置では特に、主表示パネル300Mの一対のゲート駆動部400L、400Rが次のように構成されている（図4、5参照）。

10

20

30

40

50

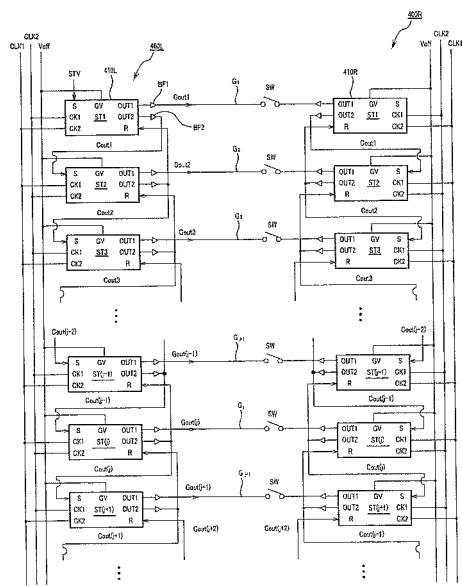

図4に示されているように、各ゲート駆動部400L、400Rはシフトレジスタであり、画面の左右に一列ずつ配置された複数のステージ410L、410Rを含む。各ステージ410L、410Rは、セット端子S、ゲートオフ電圧端子GV、一対のクロック端子CK1、CK2、リセット端子R、一対の出力端子OUT1、OUT2、及び一対のバッファBF1、BF2を有する。

#### 【0033】

左右の先頭のステージ(第1ステージ)ST1のセット端子Sには、ゲート制御信号CONT1に含まれている走査開始信号STVが入力される。第jステージST(j)(j-2)のセット端子Sには、直前のステージST(j-1)の第2出力端子OUT2から第2バッファBF2を通してキャリー信号Cout(j-1)が入力される。第jステージST(j)(j-1)のリセット端子Rには、次のステージST(j+1)の第2出力端子OUT2から第2バッファBF2を通してキャリー信号Cout(j+1)が入力される。ゲートオフ電圧端子GVにはゲートオフ電圧Voffが入力される。第jステージST(j)の第1出力端子OUT1は第1バッファBF1を通じて第jゲート線Gjにゲート信号Gout(j)を出力する。第jステージST(j)の第2出力端子OUT2は第2バッファBF2を通じてキャリー信号Cout(j)を、直前のステージST(j-1)と次のステージST(j+1)とに出力する。

10

#### 【0034】

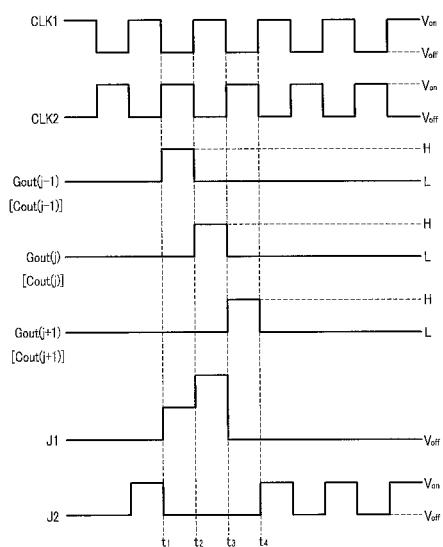

一対のクロック端子CK1、CK2には、ゲート制御信号CONT1に含まれている二つのクロック信号CLK1、CLK2が入力される。特に図4に示されているように、第jステージST(j)の第1クロック端子CK1に第1クロック信号CLK1が入力され、第2クロック端子CK2に第2クロック信号CLK2が入力される場合、好ましくは、第(j+1)ステージST(j+1)の第1クロック端子CK1には第2クロック信号CLK2が入力され、第2クロック端子CK2には第1クロック信号CLK1が入力される。ここで、各クロック信号CLK1、CLK2がハイレベルである場合、その電圧レベルがゲートオン電圧Vonに等しく、ローレベルである場合、その電圧レベルがゲートオフ電圧Voffに等しい。更に、図6に示されているように、二つのクロック信号CLK1、CLK2はデューティ比が50%であり、位相差が180°である。

20

#### 【0035】

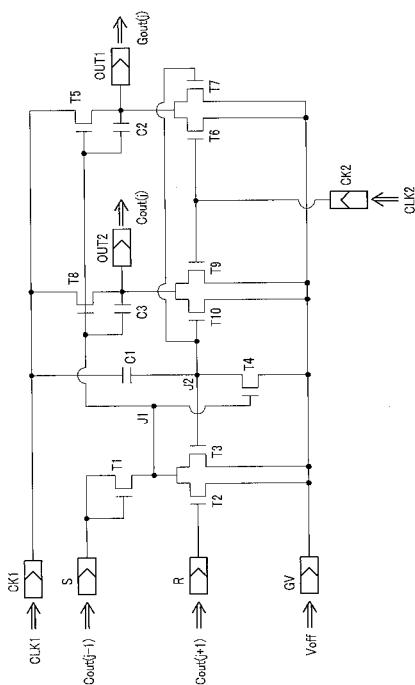

図5に示されているように、第jステージ(j-1)は好ましくは、10個のスイッチング素子T1-T10及び3個のキャパシタC1-C3を含む。各スイッチング素子T1-T10は好ましくはN MOSトランジスタであり、更に好ましくは非晶質シリコンを含む。尚、各スイッチング素子T1-T10がPMOSトランジスタであっても良い。また、各キャパシタC1-C3が、MOSトランジスタのゲート-ドレイン間(又はゲート-ソース間)の寄生容量であっても良い。

30

#### 【0036】

以下に述べる通り、第5~10のトランジスタT5-T10、第2キャパシタC2、及び第3キャパシタC3が出力回路を構成し、第1~4のトランジスタT1-T4と第1キャパシタC1とがその出力回路に対する駆動回路を構成している。ここで、駆動回路はセット端子Sとリセット端子Rとの各状態に応じて二つの接続点J1、J2の電位を変化させる。一方、出力回路はそれらの接続点J1、J2と第2クロック端子CK2との各電位に応じ、第1クロック端子CK1に入力されるクロック信号CLK1(又はCLK2)を二つの出力端子OUT1、OUT2の両方から出力し、又はその出力を停止する。

40

#### 【0037】

駆動回路では第1~4のトランジスタT1-T4と第1キャパシタC1とが次のように接続されている(図5参照)。第1トランジスタT1の入力端子と制御端子とはセット端子Sに共通接続(ダイオード接続)され、前のステージからキャリー信号Cout(j-1)を受信する。第1トランジスタT1の出力端子は第1接続点J1に連結されている。第2トランジスタT2と第3トランジスタT3とは第1接続点J1とゲートオフ電圧端子GVとの間に並列に連結されている。特に、各入力端子が第1接続点J1に連結されている。一方、各出力端子がゲートオフ電圧端子GVに連結され、各電位がゲートオフ電圧Voffに維持されている。第2トランジスタT2の制御端子はリセット端子Rに連結され、次のステージからキャリー信号Cout(j+1)を受信する。第3トランジスタT4の制御端子は第2接続点J2に連結されている。第1キャパシタC1は第1クロック端子CK1と第2接続点J2との間に連結されている。第4トランジスタT5は第2クロック端子CK2と第2接続点J2との間に連結されている。

50

ジスタT4の入力端子は第2接続点J2に連結され、第1キャパシタC1を通してクロック信号CLK1又はCLK2を受信する。第4トランジスタT4の出力端子はゲートオフ電圧端子GVに連結され、その電位がゲートオフ電圧Voffに維持されている。第4トランジスタT4の制御端子は第1接続点J1に連結されている。

#### 【0038】

出力回路では第5～7のトランジスタT5～T7と第2キャパシタC2とが次のように接続されている(図5参照)。第5トランジスタT5の入力端子が第1クロック端子CK1に連結され、クロック信号CLK1又はCLK2を受信する。第5トランジスタT5の出力端子が第1出力端子OUT1に連結され、制御端子が第1接続点J1に連結されている。第2キャパシタC2は第5トランジスタT5の制御端子(すなわち第1接続点J1)と出力端子(すなわち第1出力端子OUT1)との間に連結されている。第6トランジスタT6と第7トランジスタT7とは第1出力端子OUT1とゲートオフ電圧端子GVとの間に並列に連結されている。特に、各入力端子が第1出力端子OUT1に連結されている。一方、各出力端子がゲートオフ電圧端子GVに連結され、各電位がゲートオフ電圧Voffに維持されている。第6トランジスタT6の制御端子は第2クロック端子CK2に連結され、第1クロック端子CK1で受信されるクロック信号とは異なるクロック信号CLK2又はCLK1を受信する。第7トランジスタT7の制御端子は第2接続点J2に連結されている。

10

#### 【0039】

出力回路では第8～10のトランジスタT8～T10と第3キャパシタC3とが、第5～7のトランジスタT5～T7と第2キャパシタC2と同様に接続されている(図5参照)。すなわち、第8トランジスタT8の入力端子が第1クロック端子CK1に連結され、クロック信号CLK1又はCLK2を受信する。第8トランジスタT8の出力端子が第2出力端子OUT2に連結され、制御端子が第1接続点J1に連結されている。第3キャパシタC3は第8トランジスタT8の制御端子(すなわち第1接続点J1)と出力端子(すなわち第2出力端子OUT2)との間に連結されている。第9トランジスタT9と第10トランジスタT10とは第2出力端子OUT2とゲートオフ電圧端子GVとの間に並列に連結されている。特に、各入力端子が第2出力端子OUT2に連結されている。一方、各出力端子がゲートオフ電圧端子GVに連結され、各電位がゲートオフ電圧Voffに維持されている。第9トランジスタT9の制御端子は第2クロック端子CK2に連結され、第1クロック端子CK1で受信されるクロック信号とは異なるクロック信号CLK2又はCLK1を受信する。第10トランジスタT10の制御端子は第2接続点J2に連結されている。

20

#### 【0040】

各ゲート駆動回路400L、400Rでは各ステージが以下のように動作する。尚、以下の説明では便宜上、次の場合を想定する：図6に示されているように、各クロック信号CLK1、CLK2のハイレベルの電圧がゲートオン電圧Vonに等しく、ローレベルの電圧がゲートオフ電圧Voffに等しい。更に、整数j(j-2)を一つの値に固定し、第jステージST(j)(j-1)では図5に示されているように、第1クロック端子CK1が第1クロック信号CLK1を受信し、第2クロック端子CK2が第2クロック信号CLK2を受信する。

30

#### 【0041】

図6に示されている時刻t1では、第2クロック信号CLK2がハイレベルVonに遷移する。そのとき、直前のステージのキャリー信号Cout(j-1)がハイレベルHに遷移するので、第1トランジスタT1が導通する。ここで、次のステージのキャリー信号Cout(j+1)はローレベルLに維持されているので、第2トランジスタT2と第3トランジスタT3とが遮断状態を維持する。従って、第1接続点J1の電位が上昇するので、第4トランジスタT4が導通し、第2接続点J2をゲートオフ電圧端子GVに連結する。それにより、第2接続点J2の電位がゲートオフ電圧Voffに維持されるので、第7トランジスタT7と第10トランジスタT10とが遮断状態を維持する。第1接続点J1の電位上昇は更に、第5トランジスタT5と第8トランジスタT8とを共に導通させてるので、第1クロック端子CK1が各出力端子OUT1、OUT2に連結される。一方、第2クロック端子CK2の電位がゲートオン電圧Vonに等しいので、第6トランジスタT6と第9トランジスタT9とが導通し、各出力端子OUT1、OUT2をゲートオフ電圧端

40

50

子GVに連結する。その結果、各出力端子OUT1、OUT2の電位がゲートオフ電圧Voffに安定に維持されるので、ゲート信号Gout(j)及びキャリー信号Cout(j)が共にローレベルLに維持される。尚、その期間では、第1キャパシタC1は両端電圧が零に等しいので充電されないが、第2キャパシタC2と第3キャパシタC3とは第1接続点J1の高電圧（すなわち、キャリー信号Cout(j-1)のハイレベルH）とゲートオフ電圧Voffとの間の差で充電される。

#### 【0042】

図6に示されているように、時刻t1に続く時刻t2では、第2クロック信号CLK2がローレベルVoffに遷移する。そのとき、直前のステージのキャリー信号Cout(j-1)がローレベルLに遷移するので、第1トランジスタT1が遮断される。ここで、次のステージのキャリー信号Cout(j+1)はローレベルLに維持されているので、第2トランジスタT2と第3トランジスタT3とが遮断状態を維持する。従って、第1接続点J1が浮遊状態になり、第2キャパシタC2と第3キャパシタC3との各両端電圧がそのまま維持される。従って、第4トランジスタT4が導通状態を維持し、第2接続点J2の電位がゲートオフ電圧Voffに維持されるので、第7トランジスタT7と第10トランジスタT10とが遮断状態を維持する。第2キャパシタC2と第3キャパシタC3との各両端電圧の維持は更に、第5トランジスタT5と第8トランジスタT8とをいずれも導通状態に維持する。一方、第2クロック端子CK2の電位がゲートオフ電圧Voffに等しいので、第6トランジスタT6と第9トランジスタT9とが遮断され、各出力端子OUT1、OUT2をゲートオフ電圧端子GVから切断する。その結果、ハイレベルVonに遷移した第1クロック信号CLK1が第1クロック端子CK1を通して二つの出力端子OUT1、OUT2の各電位、すなわち、ゲート信号Gout(j)及びキャリー信号Cout(j)の各レベルをハイレベルHに遷移させる。尚、各出力端子OUT1、OUT2の電位上昇に伴い、第1接続点J1の電位が第1クロック信号CLK1のハイレベルVonより第2キャパシタC2（又は、第3キャパシタC3）の両端電圧だけ高い電位まで更に上昇する。また、第1キャパシタC1が第1クロック信号CLK1のハイレベルVonとゲートオフ電圧Voffとの間の差で充電される。10

#### 【0043】

図6に示されているように、時刻t2に続く時刻t3では、第1クロック信号CLK1がローレベルVoffに遷移するので、第1キャパシタC1の両端電圧が零まで下降する。一方、第2クロック信号CLK2がハイレベルVonに遷移する。そのとき、次のステージのキャリー信号Cout(j+1)がハイレベルHに遷移するので、第2トランジスタT2が導通して第1接続点J1をゲートオフ電圧端子GVに連結する。ここで、直前のステージのキャリー信号Cout(j-1)はローレベルLに維持されているので、第1トランジスタT1が遮断状態を維持する。従って、第1接続点J1の電位がゲートオフ電圧Voffまで下降するので、第5トランジスタT5と第8トランジスタT8とがいずれも遮断される。更に、第4トランジスタT4が遮断されるので、第2接続点J2が浮遊状態になり、第2キャパシタC2の両端電圧が零に維持される。従って、第2接続点J2の電位が第1クロック信号CLK1のローレベルVoffに等しいので、第7トランジスタT7と第10トランジスタT10とが遮断状態を維持する。しかし、第2クロック信号CLK2のハイレベルVonへの遷移が第6トランジスタT6と第9トランジスタT9とを導通させるので、各出力端子OUT1、OUT2がゲートオフ電圧端子GVに連結される。その結果、二つの出力端子OUT1、OUT2の各電位、すなわち、ゲート信号Gout(j)及びキャリー信号Cout(j)の各レベルがローレベルLに遷移する。30

#### 【0044】

図6に示されているように、時刻t3に続く時刻t4では、第1クロック信号CLK1がハイレベルVonに遷移する。そのとき、第1キャパシタC1の両端電圧が零であるので、第2接続点J2の電位が上昇する。それにより、第3トランジスタT4が導通して第1接続点J1をゲートオフ電圧端子GVに連結する。ここで、直前のステージのキャリー信号Cout(j-1)はローレベルLに維持されているので、第1トランジスタT1が遮断状態を維持する。従って、第1接続点J1の電位がゲートオフ電圧Voffに維持され、第5トランジスタT5と第8トランジスタT8とが遮断状態を維持する。第2接続点J2の電位上昇は更に、第7トランジスタT7と第10トランジスタT10とを導通させてるので、各出力端子OUT1、OUT2がゲートオフ電圧端子GVに連結される。その結果、各出力端子OUT1、OUT2の電位、すなわち、ゲート信号Gout40

50

(j)及びキャリー信号Cout(j)の各レベルがローレベルLに維持される。

**【0045】**

図6に示されているように、時刻t4以後は、直前のステージのキャリー信号Cout(j-1)がハイレベルHに遷移するまで、第1トランジスタT1が遮断状態を維持するので、第1接続点J1の電位がゲートオフ電圧Voffに維持される。一方、第4トランジスタT4が遮断状態を維持するので、第2接続点J2が第1キャバシタC1を通して第1クロック端子CK1に連結され続ける。従って、第2接続点J2の電位変化が第1クロック信号CLK1に同期するので、第7トランジスタT7と第10トランジスタT10との各オンオフが第1クロック信号CLK1に同期する。一方、第6トランジスタT6と第9トランジスタT9との各オンオフは第2クロック信号CLK2に同期する。その結果、第6トランジスタT6と第7トランジスタT7とが交互に導通して第1出力端子OUT1の電位をゲートオフ電圧Voffに維持し、第9トランジスタT9と第10トランジスタT10とが交互に導通して第2出力端子OUT2の電位をゲートオフ電圧Voffに維持する。こうして、クロック信号CLK1、CLK2の変動に関わらず、各出力端子OUT1、OUT2の電位、すなわち、ゲート信号Gout(j)及びキャリー信号Cout(j)の各レベルがローレベルLに維持される。10

以上の通り、図4に示されているステージST(j)は、前後のステージのキャリー信号Cout(j-1)、Cout(j+1)を利用して、ゲート信号Gout(j)を一つずつ順番にクロック信号CLK1、CLK2に同期して各ゲート線G<sub>j</sub>に対して印加する。

**【0046】**

本発明の上記の実施例では特に、図4に示されている通り、各ゲート線G<sub>j</sub>の左端に第1ゲート駆動部400Lのステージ410Lが一つずつ連結され、右端に第2ゲート駆動部400Rのステージ410Rが一つずつ連結されている。各ゲート駆動部400L、400Rの先頭ステージST1が同じ走査開始信号STVで動作を開始するので、同じゲート線G<sub>j</sub>に連結されたステージ410L、410Rはそのゲート線G<sub>j</sub>に対してゲート信号Gout(j)を同時に印加する。この構成が以下のように、断線等によるゲート線の不良に対する修理を不要にする。例えば、図4に示されているように、第3ゲート線G<sub>3</sub>が断線した場合、その断線部位opの左側の部分に対しては第3ゲート線G<sub>3</sub>の左端に連結されたステージ410Lから、その断線部位opの右側の部分に対しては第3ゲート線G<sub>3</sub>の右端に連結されたステージ410Rから、それぞれゲート信号Gout<sub>3</sub>が同時に印加される。第(j+1)ゲート線G<sub>j+1</sub>が断線した場合も同様に、その断線部位opの左側の部分に対しては第(j+1)ゲート線G<sub>j+1</sub>の左端に連結されたステージ410Lから、その断線部位opの右側の部分に対しては第(j+1)ゲート線G<sub>j+1</sub>の右端に連結されたステージ410Rから、それぞれゲート信号Gout(j+1)が同時に印加される。従って、断線部位opの存在に関わらず、各ゲート線G<sub>j+1</sub>の全体にゲート信号が良好に伝達される。それ故、不良なゲート線G<sub>1</sub> - G<sub>n</sub>に対する従来の修理工程（例えば断線部位opの両側に修理線をレーザー照射で結線してその断線部位opをバイパスする工程）が不要である。こうして、修理時間及び費用が削減されるので、生産性が更に向上する。その上、表示パネルの基板を、プラスチック等、レーザー照射による修理が容易でない材質から形成しても、ゲート線不良に対しては歩留まりを高く維持できる。2030

**【0047】**

本発明の他の実施例による表示装置では、図4に示されているゲート駆動部400L、400Rに代え、図7に示されている主ゲート駆動部400Lと副ゲート駆動部400Rとが実装されている。特に、副ゲート駆動部400Rは、図4に示されている第2ゲート駆動部400Rとは異なり、先頭ステージST1に走査開始信号STVが入力されない。更に、副ゲート駆動部400Rに接続された各ゲート線G<sub>1</sub> - G<sub>n</sub>の端部付近にはスイッチング部SWが一つずつ配置されている。スイッチング部SWは好ましくはトランジスタであり、更に好ましくは信号制御部600からの制御信号に従ってオンオフする。スイッチング部SWは好ましくは、正常時には遮断状態に維持され、必要に応じて導通する。尚、スイッチング部SWに代え、各ゲート線G<sub>1</sub> - G<sub>n</sub>が、レーザー照射によって連結可能な断線部位を含んでいても良い。それらの相違点を除き、図7に示されている構成要素は図4に示されている構成要素と同様であるので、それら同様な構成要素の詳細は、図4に示されている構成要素についての上記の説明を援用する。4050

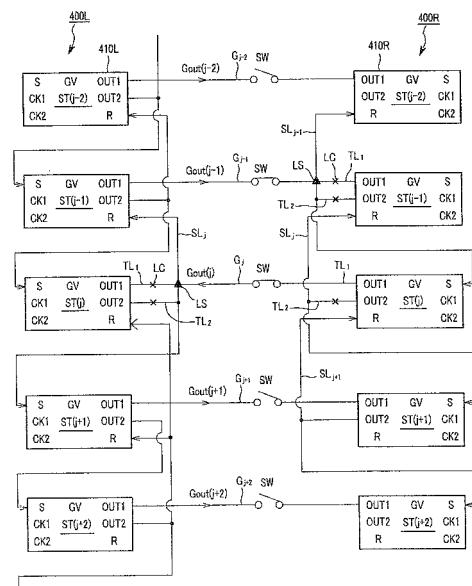

**【0048】**

例えば、主ゲート駆動部400Lの第jステージST(j) (j-2)に欠陥があり、ゲート信号を出力できない場合、上記のスイッチング部SWを利用してその不良な第jステージに起因する不具合を次のように除去できる(図8参照)。ここで、図8に示されているように、各ステージST(j-2) - ST(j+2)の第1出力端子OUT1が入力端子線TL<sub>1</sub>によりスイッチング部SWに連結され、第2出力端子OUT2が制御端子線TL<sub>2</sub>とキャリー信号線SL<sub>j-1</sub>、SL<sub>j</sub>、又はSL<sub>j+1</sub>とにより直前のステージのリセット端子Rと次のステージのセット端子Sとに連結されている。

**【0049】**

まず、第(j-1)ゲート線G<sub>j-1</sub>に配置されているスイッチング部SWと、第jゲート線G<sub>j</sub>に配置されているスイッチング部SWとを導通させる。それにより、第jゲート線G<sub>j</sub>に対しては、主ゲート駆動部400Lの不良な第jステージST(j)に代え、副ゲート駆動部400Rの第jステージST(j)からゲート信号Gout(j)を印加する。

10

**【0050】**

次に、副ゲート駆動部400Rの第(j-1)ステージST(j-1)の第1出力端子OUT1から延びている入力端子線TL<sub>1</sub>を切断し、第2出力端子OUT2から延びている制御端子線TL<sub>2</sub>を切断する(図8に×印で示されている切断点LC参照)。一方、キャリー信号線SL<sub>j-1</sub>と第(j-1)ゲート線G<sub>j-1</sub>との間の交差点にレーザーを照射して両線間を短絡する(図8に三角印で示されている短絡点LS参照)。それにより、主ゲート駆動部400Lの第(j-1)ステージST(j-1)から出力されたゲート信号Gout(j-1)をキャリー信号Cout(j-1)として、副ゲート駆動部400Rの第jステージST(j)のセット端子Sに入力し、その第jステージST(j)を動作させる。

20

**【0051】**

続いて、主ゲート駆動部400Lの不良な第jステージST(j)の第1出力端子OUT1から延びている入力端子線TL<sub>1</sub>を切断し、第2出力端子OUT2から延びている制御端子線TL<sub>2</sub>を切断する(図8に×印で示されている切断点LC参照)。一方、キャリー信号線SL<sub>j</sub>と第jゲート線G<sub>j</sub>との間の交差点にレーザーを照射して両線間を短絡する(図8に三角印で示されている短絡点LS参照)。それにより、副ゲート駆動部400Lの第jステージST(j)から出力されたゲート信号Gout(j)をキャリー信号Cout(j)として、主ゲート駆動部400Rの第(j-1)ステージST(j-1)のリセット端子R及び第(j+1)ステージST(j+1)のセット端子Sに入力する。更に、副ゲート駆動部400Lの第jステージST(j)の第2出力端子OUT2から延びている制御端子線TL<sub>2</sub>を切断し、その第2出力端子OUT2から出力されるキャリー信号Cout(j)を前後のステージから遮断する。それにより、副ゲート駆動部400Lでは第(j+1)ステージST(j+1)以後のステージの起動を阻止する。

30

**【0052】**

こうして、図7に示されている表示装置では、主ゲート駆動部400Lのいずれかのステージが不良な場合、簡単な作業で、その不良ステージを副ゲート駆動部400Rの対応するステージで代替可能である。従って、修理時間及び費用が削減されるので、生産性が更に向上升る。

尚、主ゲート駆動部400Lの先頭ステージST1(図7参照)が不良でゲート信号を出力できない場合、走査開始信号STVを副ゲート駆動部400Rの先頭ステージST1のセット端子Sに入力すれば、後は上記と同様な修理により、主ゲート駆動部400Lの先頭ステージを副ゲート駆動部400Rの先頭ステージで代替できる。

40

**【0053】**

以上、本発明の好ましい実施例について詳細に説明した。しかし、本発明の技術的範囲は上記の実施例には限定されない。実際、当業者であれば、特許請求の範囲から特定される本発明の基本概念を利用して多様な変形や改良が可能であろう。従って、それらの変形や改良も当然に、本発明の技術的範囲に属すると解されるべきである。

**【図面の簡単な説明】****【0054】****【図1】本発明の一実施例による液晶表示装置の展開図**

50

- 【図2】図1に示されている主表示パネルのブロック図

【図3】図1に示されている表示パネルに含まれている一つの画素の構造を示す模式図

【図4】本発明の一実施例によるゲート駆動部のブロック図

【図5】図4に示されているゲート駆動部の第jステージの回路図

【図6】図4に示されているゲート駆動部の動作を示す信号波形図

【図7】本発明の他の実施例によるゲート駆動部のブロック図

【図8】図7に示されているゲート駆動部の修理箇所を示すブロック図

## 【符号の説明】

## 【0055】

|       |                 |    |

|-------|-----------------|----|

| 3     | 液晶層             | 10 |

| 100   | 下部表示パネル         |    |

| 191   | 画素電極            |    |

| 200   | 上部表示パネル         |    |

| 230   | 色フィルタ           |    |

| 270   | 共通電極            |    |

| 300   | 表示パネル           |    |

| 300M  | 主表示パネル          |    |

| 310M  | 主表示パネルの表示領域     |    |

| 320M  | 主表示パネルの周辺領域     |    |

| 300S  | 副表示パネル          | 20 |

| 310S  | 副表示パネルの表示領域     |    |

| 320M  | 副表示パネルの周辺領域     |    |

| 400L  | 主表示パネルの第1ゲート駆動部 |    |

| 410L  | 第1ゲート駆動部のステージ   |    |

| 400R  | 主表示パネルの第2ゲート駆動部 |    |

| 410R  | 第2ゲート駆動部のステージ   |    |

| 400S  | 副表示パネルのゲート駆動部   |    |

| 500   | データ駆動部          |    |

| 600   | 信号制御部           |    |

| 650   | FPC             | 30 |

| 660   | 入力部             |    |

| 680   | 補助FPC           |    |

| 690   | FPCの開口部         |    |

| 700   | 統合チップ           |    |

| 800   | 階調電圧生成部         |    |

| R、G、B | 入力画像信号          |    |

| DE    | データイネーブル信号      |    |

| MCLK  | メインクロック信号       |    |

| Hsync | 水平同期信号          |    |

| Vsync | 垂直同期信号          | 40 |

| CONT1 | ゲート制御信号         |    |

| CONT2 | データ制御信号         |    |

| DAT   | 出力画像信号          |    |

| PX    | 画素              |    |

| C1c   | 液晶キャパシタ         |    |

| Cst   | ストレージキャパシタ      |    |

| Q     | スイッチング素子        |    |

| STV   | 走査開始信号          |    |

| CLK1  | 第1クロック信号        |    |

| CLK2  | 第2クロック信号        | 50 |

$V_{off}$  ゲートオフ電圧

$Gout_1, Gout_2, Gout_3, Gout(j-1), Gout(j), Gout(j+1)$  ゲート信号

$Cout_1, Cout_2, Cout_3, Cout(j-1), Cout(j), Cout(j+1)$  キャリー信号

$G_1, G_2, G_3, G_{j-1}, G_j, G_{j+1}$  ゲート線

$ST_1, ST_2, ST_3, ST(j-1), ST(j), ST(j+1)$  ゲート駆動部のステージ

BF1 第1バッファ

BF2 第2バッファ

S セット端子

R リセット端子

GV ゲートオフ電圧端子

10

OUT1 第1出力端子

OUT2 第2出力端子

op ゲート線の断線部位

SW スイッチング部

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

---

フロントページの続き

(51)Int.Cl.

F I

G 0 9 G 3/20 6 2 2 E

G 0 9 G 3/20 6 2 1 M

G 0 9 G 3/20 6 8 0 G

(72)発明者 全 亨 -

大韓民国仁川市南区龍 ヒョン 4洞41-42番地14/4ショフン住宅B棟102号

(72)発明者 張 在 ヒョック

大韓民国ソウル市永登浦区堂山洞1街眞露アパート102棟902号

(72)発明者 朴 大 眞

大韓民国仁川市延壽区延壽3洞プンリム1次アパート105棟402号

(72)発明者 李 鍾 煥

大韓民国京畿道安養市東安区達安洞セッピヨルアパート602棟1705号

(72)発明者 林 都 基

大韓民国忠清南道天安市雙龍洞2045番地ヒョンデホームタウンアイパーク114棟303号

審査官 西島 篤宏

(56)参考文献 特開平07-056142(JP,A)

特開平03-197125(JP,A)

特開平06-281944(JP,A)

特開2002-258819(JP,A)

特開2002-099257(JP,A)

特開平07-199876(JP,A)

特開2004-004287(JP,A)

米国特許第06362643(US,B1)

(58)調査した分野(Int.Cl., DB名)

G 0 9 G 3 / 0 0 - 3 / 3 8

G 0 2 F 1 / 1 3 3