(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5522690号

(P5522690)

(45) 発行日 平成26年6月18日(2014.6.18)

(24) 登録日 平成26年4月18日(2014.4.18)

(51) Int.Cl.

G06F 12/00 (2006.01)

F 1

G06F 12/00 560C

G06F 12/00 564A

請求項の数 4 (全 15 頁)

(21) 出願番号 特願2010-547658 (P2010-547658)

(86) (22) 出願日 平成21年1月16日 (2009.1.16)

(65) 公表番号 特表2011-513812 (P2011-513812A)

(43) 公表日 平成23年4月28日 (2011.4.28)

(86) 國際出願番号 PCT/US2009/031202

(87) 國際公開番号 WO2009/105295

(87) 國際公開日 平成21年8月27日 (2009.8.27)

審査請求日 平成24年1月16日 (2012.1.16)

(31) 優先権主張番号 12/034,888

(32) 優先日 平成20年2月21日 (2008.2.21)

(33) 優先権主張国 米国(US)

(73) 特許権者 504199127

フリースケール セミコンダクター イン

コーポレイテッド

アメリカ合衆国 テキサス州 78735

オースティン ウィリアム キャノン

ドライブ ウエスト 6501

(74) 代理人 100142907

弁理士 本田 淳

(72) 発明者 チャン、シャヤン

アメリカ合衆国 78750 テキサス州

オースティン スコティッシュ パスチ

ャーズ コープ 9111

最終頁に続く

(54) 【発明の名称】メモリ回路中の調整可能なパイプライン

## (57) 【特許請求の範囲】

## 【請求項 1】

メモリ回路を動作させる方法であって、

メモリ回路の個々の回路部に関連するタイミングマージンを感知し、該感知されたタイミングマージンに基づいてフィードバック信号を生成すること、

前記メモリ回路により生成された前記フィードバック信号に少なくとも部分的に基づいて、メモリ回路の動作モードを選択すること、および

前記メモリ回路の選択された動作モードに基づく数のパイプライン段を使用して、メモリ回路を動作させること、

からなる方法。

## 【請求項 2】

前記動作モードは、メモリ回路の制御クロック信号の周波数およびメモリ回路の電源電圧レベルのうちの少なくとも1つの値に対応する動作モード情報の表の少なくとも1つのエントリに部分的に基づいて選択される請求項1に記載の方法。

## 【請求項 3】

集積回路であって、

メモリ回路と、

メモリ回路によって生成されたフィードバック信号に少なくとも部分的に基づいて、メモリ回路の動作モードを選択するように構成された制御回路であって、前記フィードバック信号は、メモリ回路の個々の回路部に関連したタイミングマージンを示す、制御回路と

を備え、

メモリ回路は、前記メモリ回路の選択された動作モードに基づく数のパイプライン段を使用して動作するように構成される、集積回路。

【請求項 4】

制御回路に接続され、メモリ回路の制御クロック信号の周波数およびメモリ回路の電源電圧のレベルから成るグループの少なくとも 1 つの値に対応する動作モード情報を格納するように構成された第 2 のメモリ回路をさらに備え、

制御回路は、制御クロック信号の特定の周波数および電源電圧の特定のレベルに対応する第 2 のメモリ回路の内容に部分的に基づいて動作モードを選択するように構成される、

請求項 3 に記載の集積回路。

10

【発明の詳細な説明】

【技術分野】

【0001】

本開示は、一般には記憶システムに関し、より詳細にはパイプライン型記憶システムに関する。

【背景技術】

【0002】

一般に、メモリ回路は特定の動作点で特定の性能目標を満たすように設計される。性能目標は、ピーク性能動作点におけるメモリ回路の待ち時間および電力消費（例えばピーク制御クロック信号周波数および特定の電源電圧）により定義され得る。性能目標を達成するため、メモリ回路は、論理回路の間に挿入された状態要素（例えばラッチ回路、フリップフロップ、または他の適切な状態要素）によりパイプラインでアクセスされ得る。典型的には、パイプライン型メモリ回路の個々のパイプライン段（pipeline stage）は、性能目標に関連する動作点で、制御クロック信号の全期間を利用するように設計される。しかしながら、パイプライン型メモリ回路の各パイプライン段を通じた伝搬遅延（つまり各パイプライン段の入力から各パイプライン段の出力までの遅延）は、実際の動作条件では一定でない。伝搬遅延は、温度、電源電圧または他の運転条件の変化により変わり得る。

20

【0003】

本発明は、例示として示され、添付図面により制限されない。図中、同様な参照数値は同様の要素を示す。図中の要素は単純さと明確さを目的に示されており、必ずしも正しい縮尺で描かれていない。異なる図中の同じ参照記号の使用は、類似または同一の項目を示す。

30

【図面の簡単な説明】

【0004】

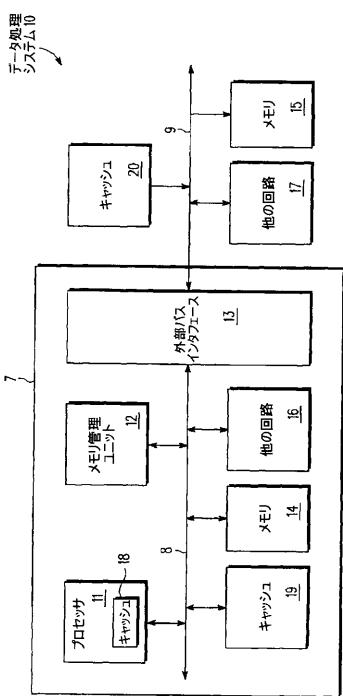

【図 1】本発明の少なくとも 1 つの実施形態と一致する例証的なデータ処理システムのブロック図。

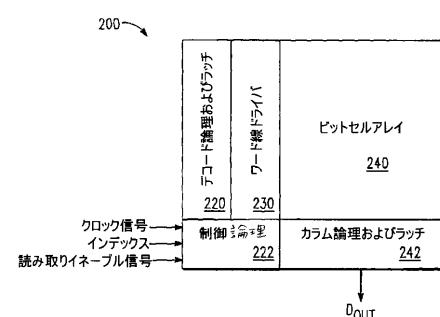

【図 2】例証的なパイプライン型メモリ回路のブロック図。

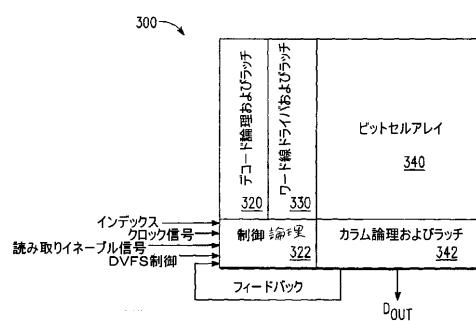

【図 3】本発明の少なくとも 1 つの実施形態と一致する例証的なパイプライン型メモリ回路のブロック図。

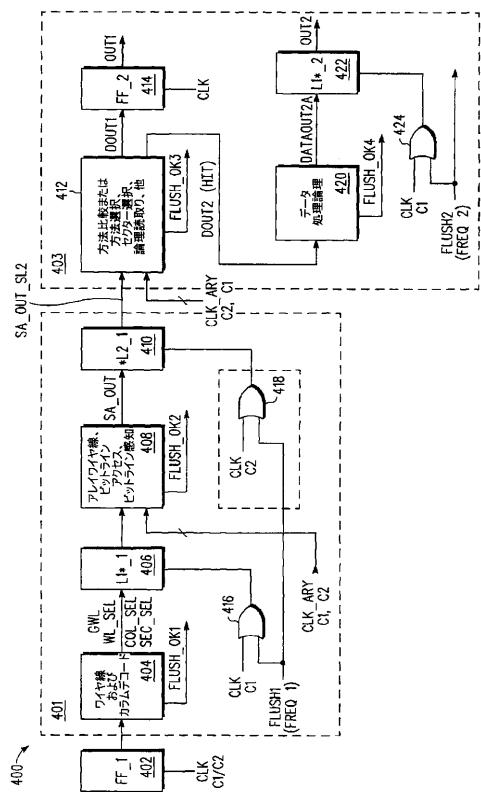

【図 4】本発明の少なくとも 1 つの実施形態と一致する例証的なパイプライン型メモリ回路部分のブロック図。

40

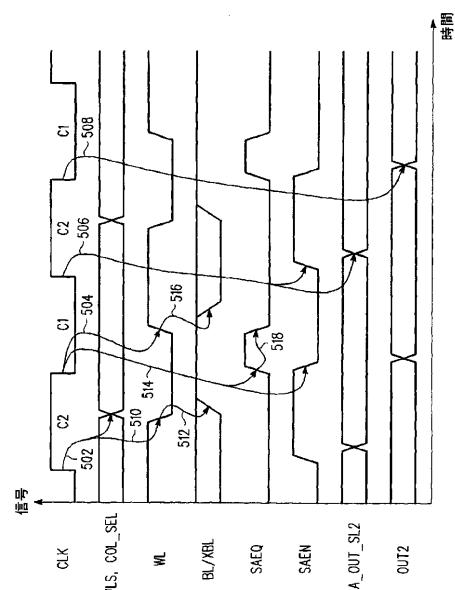

【図 5】本発明の少なくとも 1 つの実施形態と一致するよう構成された図 4 のパイプライン型メモリ回路部分の波形を示すタイミング図。

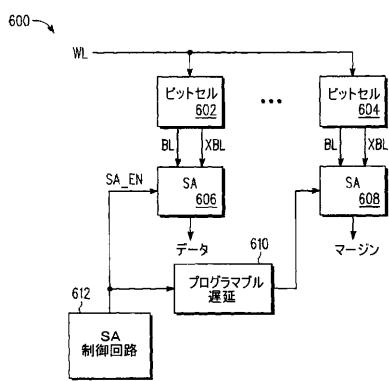

【図 6】メモリ回路フィードバック信号の生成のための例証的な技術を示すブロック図。

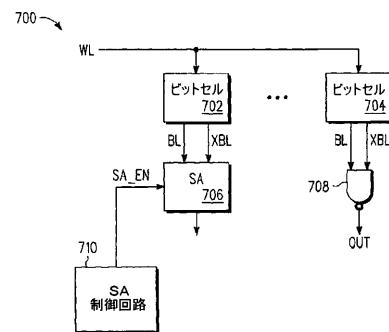

【図 7】メモリ回路フィードバック信号の生成のための例証的な技術を示すブロック図。

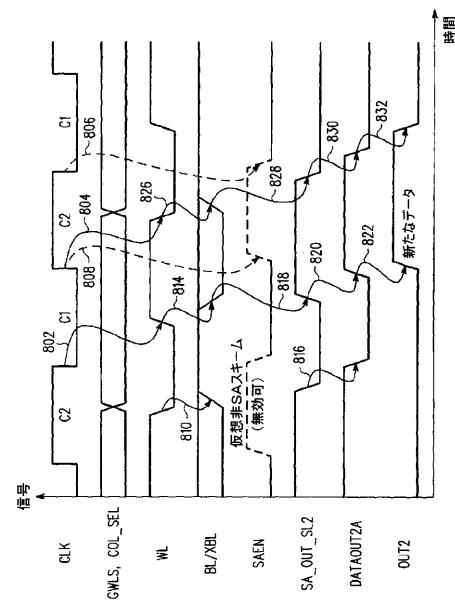

【図 8】本発明の少なくとも 1 つの実施形態と一致するよう構成された図 4 のパイプライン型メモリ回路部分の波形を示すタイミング図。

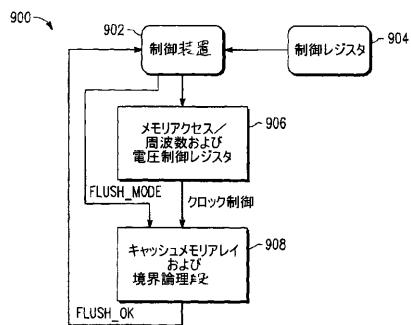

【図 9】本発明の少なくとも 1 つの実施形態と一致する例証的な制御システムのブロック図。

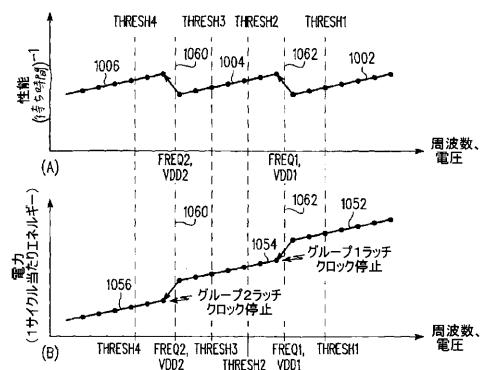

【図 10】本発明の少なくとも 1 つの実施形態と一致するメモリ構造の例証的な動作点を

50

示す。

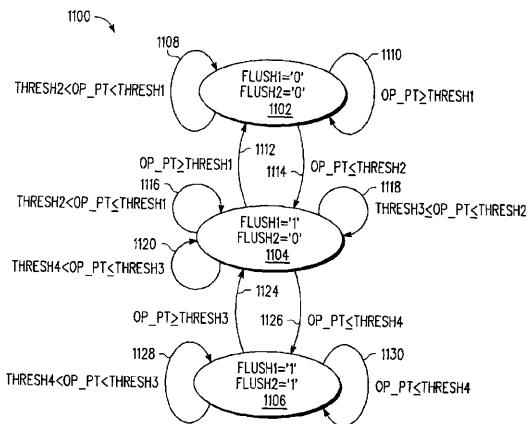

【図11】本発明の少なくとも1つの実施形態と一致する例証的な制御フローを示す状態図。

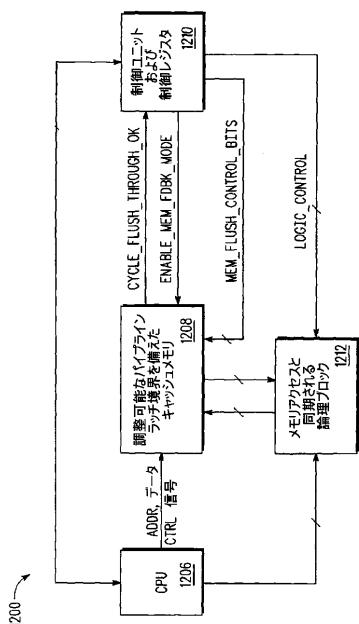

【図12】本発明の少なくとも1つの実施形態と一致する例証的な制御システムのプロック図。

#### 【発明を実施するための形態】

##### 【0005】

通常のパイプライン型メモリ回路では、パイプライン型メモリ回路の個々のパイプライン段は、パイプライン段に割り当てられた制御クロック信号の全体部分を利用することが可能であり、それは制御クロック信号の全期間であってもよい。メモリが目標動作点で動作している間、パイプラインはメモリ回路の性能を改善し得るが、他の動作点ではパイプラインはメモリ回路のメモリ性能を制限し得る。制御クロック信号周波数が減少されるにつれて通常のパイプライン型メモリ回路の待ち時間は単調に減少する一方で、タイミングマージンは個々のパイプライン段で増加する。本明細書で述べる場合、パイプライン段のタイミングマージンは、目標振動数で動作している時にパイプライン段に割り当てられるクロック信号の部分と、パイプライン段が入力の処理を完了して出力を生成するのに必要な時間との間の差である。パイプライン型メモリ回路が、性能目標に関連する動作点に対して構成された場合、メモリ回路は他の動作点（例えば電源電圧および／または制御クロック信号周波数がより低い）でよりも多くの電力を消費する。一般に、パイプライン型メモリ回路では、状態要素（例えばラッチ、フリップ・フロップ、または他の適切な状態要素）の数がメモリ回路のサイズの増加とともに指数関数的に増加し、それらの状態要素の電力消費は全メモリ電力消費のうちのかなりの部分を占める。

10

20

30

##### 【0006】

従って、パイプライン型メモリ回路の性能と電力消費との関係は、電源電圧レベルおよび／または制御クロック信号周波数のスケーリングに比例して改善しない可能性がある。さらに、1つの応用（例えばバックエンドキャッシュアレイ）のための特定の目標動作条件（例えば特定の周波数および電源電圧レベル）を満たすメモリ回路設計は、信頼性要件（例えばエラー訂正コード動作または他のプラットフォーム機能特徴）を満たすために追加のパイプライン時間を要求する他の応用（例えば、より低い周波数で動作するマルチコアフロントエンド／プラットフォームキャッシュアレイ）のための使用を満たさない可能性がある。さらに、個々のパイプライン段に関連するタイミングマージンは、（例えば温度差、電源電圧レベル変化、動作周波数調整、または他の動作状況への変更により）動的に変化し、パイプライン型メモリ回路の性能および電力消費に有害な影響を及ぼし得る。従って、メモリ回路を動作させる新しい技術が望まれる。

##### 【0007】

メモリ回路の性能および／またはメモリ回路の少なくともいくつかの動作点に対する電力消費を改善するメモリ回路を動作させる技術は、メモリの動作点に少なくとも部分的に基づいて、動作パイプライン段の数を調整することを含む。本発明の少なくとも1つの実施形態では、メモリ回路を動作させる方法は、メモリ回路によって生成されたフィードバック信号に少なくとも部分的に基づいて、メモリ回路の動作モードを選択することを含む。方法は、メモリ回路の選択された動作モードに基づく数のパイプライン段を使用して、メモリ回路を動作させることを含む。本発明の少なくとも1つの実施形態では、技術は個々のパイプライン段に関連するタイミングマージンを感知し、感知されたタイミングマージンに基づいてフィードバック信号を生成することを含む。

40

##### 【0008】

図1を参照すると、例証的なデータ処理システムは、インタフェース（例えば外部バスインターフェース13およびバス9）を介して外部回路（例えば他の回路17、キャッシュメモリ回路20およびメモリ回路15）に接続可能な集積回路（例えば集積回路7）を備え得る。集積回路は、キャッシュメモリ回路（例えばキャッシュメモリ回路18）を備えてもよいプロセッサ回路（例えばプロセッサ回路11）を備え得る。プロセッサ回路11

50

は、マイクロプロセッサ、マイクロコントローラ、デジタル信号プロセッサ、または他の適切な情報処理回路であってよい。さらに、データ処理システム10の少なくとも1つの実施形態では、集積回路7は、(例えばバス8を介して)プロセッサ回路に接続された他の回路(例えばキャッシュメモリ回路19、メモリ回路14、メモリ管理ユニット12および他の回路16)を備える。集積回路7内に示されたコンポーネントの種類、数または配置は単なる例であり、当業者には、本発明と一致するシステムおよび/または集積回路の実施形態が、より一般的に、他のコンポーネントの種類、数、および配置を備えてよいことが理解されるだろう。

#### 【0009】

一般に、メモリ14、15、18、19および20は、任意の種類の情報(例えばアドレス、データ、タグまたは他の適切な情報)を格納してもよく、かかる情報においてまたはかかる情報に関連して、パイプライン型アレイアクセスが記憶階層中の何らかのレベルで行なわれる。同様に、キャッシュ19および/または同様の設計の他のコンポーネントがメモリ管理ユニットの一部として現われてもよい。図1はメモリ14およびキャッシュ19を別々に示しているが、本発明と一致する他の実施態様は一方を含むが他方を含まなくてもよく、または2レベル以上の記憶階層を1つの要素またはブロックへ組み合わせてもよい。

10

#### 【0010】

コンポーネントは例証的な集積回路7として具現化されているが、別の実施形態では、1または複数のコンポーネントが別々の複数の集積回路で実装されてもよい。図の集積回路7の内部コンポーネントは相互に連結し、任意の適切な技術を使用して共同作業する。簡単にするため、主な機能的ブロックの相互接続がバス8で示されているが、任意の様々な相互接続技術およびトポロジーが本発明から逸脱せずに使用されてもよいことが当業者には理解される。

20

#### 【0011】

本明細書で説明する技術は、データ処理システム10の1つまたは複数のメモリ回路または他の適切なメモリ回路で具現化可能である。技術をキャッシュメモリ回路の例について説明するが、任意の様々なメモリ回路を使用してもよいことが当業者には理解される。図2を参照すると、例証的なキャッシュメモリ回路200は、デコード論理およびラッチ回路220、ワード線ドライバ230、ビットセルアレイ240、カラム論理およびラッチ242、および制御論理回路222を備えている。キャッシュメモリ回路200は、適切な境界で複数の段にメモリアクセスを分割する例証的なパイプライン型メモリ回路である。個々のパイプライン段は制御論理回路222によって制御され、制御論理回路222は、制御クロック信号、読み取りイネーブル信号および指標値(インデックス)に応じて制御信号を生成する。例えば、キャッシュメモリ回路200は2つのパイプライン段へ分割されてもよい。第1のパイプライン段は、デコード論理段(例えばデコード論理およびラッチ回路220)、ワード線ドライバ(例えばワード線ドライバ230)およびメモリアレイ(例えばビットセルアレイ240)を備えてもよい。デコード論理段は、少なくとも部分的にアドレス(例えばインデックス)をデコードし、結果を格納する。デコード論理およびラッチ回路の220の出力は、ワード線ドライバ230およびビットセルアレイ240に提供され、ビットアレイセル240は例えばカラム論理およびラッチ回路242を含む第2のパイプライン段にメモリ内容を提供する。特定のカラム出力が選択され、1つのクロックサイクルと2つのクロックサイクルの待ち時間当たり1つの新しいデータ値のスループットで、Doutに対して新しいデータが提供されてもよい。

30

#### 【0012】

少なくとも1つの動作点について、キャッシュメモリ回路部分200は、目標性能(つまり制御クロック信号の目標振動数、例えば2GHz)で動作する制御クロック信号の全サイクルを利用して、メモリアクセスの対応する部分を実行するパイプライン段へ分割される。しかしながら、キャッシュメモリ回路部分200は、異なる動作点(例えば目標性能動作点より低い電源電圧および/または低い制御クロック信号周波数を備えた動作点)

40

50

に対して構成されてもよい。従って、キャッシュメモリ回路部分 200 の電源電圧レベルおよび / または制御クロック信号の周波数が下がり、それによりキャッシュメモリ回路部分 200 の待ち時間が増加する。一貫した電源電圧レベルを備えた制御クロック信号の周波数の減少または制御クロック信号の周波数および電源電圧レベルの両方の減少の結果、個々のパイプライン段のタイミングマージンが増加する。

#### 【0013】

より低い動作点で動作する完全パイプライン型モードの場合、キャッシュメモリ回路部分 200 における個々のパイプライン段によって制御クロック信号の全期間は利用されないため、図 3 のキャッシュメモリ回路部分 300 は調整可能なパイプラインを備えている。ある条件下では、パイプラインはキャッシュメモリ回路部分 300 のより少数の段（つまり 1つまたは複数のフラッシュスルーモード）で動作するように構成され、それにより同じ動作点における完全パイプライン型動作と比較して、キャッシュメモリ回路部分 300 の待ち時間が短縮される。したがって、キャッシュメモリ回路部分 300 は、目標動作点におけるよりも低い電源電圧レベルおよび / または低い制御クロック信号周波数を有する動作点で余分のタイミングマージンを利用するように動的に構成され得る。例えば、キャッシュメモリ回路部分 300 がピーク性能（例えば  $f_{PEAK}$ 、 $V_{PEAK}$ ）に対して構成される場合、フラッシュスルーモードはすべて無効になる。しかしながら、キャッシュメモリ回路部分 300 が低電力モード（例えば  $f_{PEAK}/2$ 、 $V_{DD2}$ ）で動作するように構成される場合、完全パイプライン型モードにおけるよりも少なくとも 1つの少ない数のパイプライン段を使用した第 1 のフラッシュスルーモードが有効になり得る。キャッシュメモリ回路部分 300 がさらに低い電力 / 性能モード（例えば  $f_{PEAK}/4$ 、 $V_{DD3}$ ）でも動作するように構成される場合、さらに少ない数のパイプライン段を使用した対応フラッシュスルーモードが有効になり得る。キャッシュメモリ回路部分 300 の少なくとも 1つの実施形態では、制御論理 322 は、測定された電源電圧レベルのインジケータ（例えば DVFS CONTROL）および / または集積回路 7 の少なくとも一部の測定された動作周波数に基づいて低電力モードで動作するようキャッシュメモリ回路部分 300 を構成し、かかる測定値は任意の適切な技術によって生成されてよい。キャッシュメモリ回路部分 300 少なくとも 1つの実施形態では、DVFS CONTROL 信号は制御ユニット（例えば以下に説明する図 9 の制御システム 900）により生成される。制御ユニットは、キャッシュメモリ回路 300 の少なくとも一部によって受け取られた電源電圧レベルおよび / またはキャッシュメモリ回路部分 300 における動作のタイミングを制御するために使用される制御クロック信号の周波数を調整する。

#### 【0014】

コンポーネントを、図 1 のデータ処理システム 10 の少なくとも 1つの実施形態における、例証的なキャッシュメモリ回路部分 300 として具現化されるものとして説明しているが、1 または複数のコンポーネントが対応するメモリ回路部分の外部で実装され、他の回路と共有される。例えば、制御論理回路 322 の機能の少なくとも一部が集積回路 7 の他の部分により、またはデータ処理システム 10 の他の部分により実装可能であることが当業者には理解される。

#### 【0015】

図 3 に参照すると、例証的なキャッシュメモリ回路部分 300 は、図 4 のメモリ回路部分 400 に示すような例証的な動作の分割を有する調整可能なパイプラインを備えている。キャッシュメモリ回路 300 のデコード論理およびラッチ 320、ワード線ドライバ 330、およびビットセルアレイ 340 の動作が第 1 のパイプライン段（例えば図 4 のパイプライン段 401）に組み合わされ、図 3 のカラム論理およびラッチ 342 および追加論理回路の動作が第 2 のパイプライン段（例えば図 4 のパイプライン段 403）に組み合わせられる。

#### 【0016】

図 4 および 5 を参照すると、パイプライン段 401 は、インデックスまたはメモリアドレスの複号機能を行ない、出力（例えばワード線選択、カラム選択およびセクタ選択）を

10

20

30

40

50

生成する、フロントエンド回路 404 を備えている。完全パイプライン型動作中、フロントエンド回路 404 の出力は制御クロック信号の高い位相（例えば C L K の C 2 位相）の間变化（例えば遷移 502）し、ラッチ 406 によりラッチされ、これが制御クロック信号の低い位相（例えば C L K の C 1 位相）の間、データをバックエンド回路 408 へと通過させる。メモリ回路部分 400 の少なくとも 1 つの実施形態では、フロントエンド回路 404 は行デコーダ、列デコーダ、マルチプレクサ回路および / または他の適切な回路を備えている。

#### 【 0017 】

パイプライン段 401 は、ワード線をアサートしメモリアレイ回路のビットラインを感じおよびアクセスすることによりメモリアレイにアクセスする、バックエンド回路 408 を備えている。メモリ回路部分 400 の少なくとも 1 つの実施形態では、バックエンド回路 408 は、センス増幅器、メモリセル、マルチプレクサ回路および / または他の適切な回路を備えている。メモリ回路部分 400 の少なくとも 1 つの実施形態では、バックエンド回路 408 が動的論理回路（例えば制御クロック信号の第 1 相中に特定の電圧準位に予め充電され、制御クロック信号の別の位相中に条件付きで放出される出力ノードを含む論理構造）を備えることに注意する。10

#### 【 0018 】

例えば、メモリ回路部分 400 の少なくとも 1 つの実施形態では、バックエンド回路 408 がメモリセルからのデータにアクセスし、それをデータ出力信号に提供する（例えば、ワード線を選択し、ビットライン上で対応する信号を発達させる）。バックエンド回路 408 中のアレイに接続されたビットラインは、制御クロック信号の高位相中に予め充電される（例えば遷移 512）。ワード線は、制御の低位相中に信号遷移を選択し（例えば W L の遷移 504）、制御クロック信号の低位相中にビットライン上で信号が開発される（例えば遷移 516）。センス増幅器中のノードは、制御クロック信号の低位相の第 1 部分の間の例えば S A E Q が高い間に、零入力値に設定され（例えば遷移 514）、ちょうどワード線セレクト信号が高く活性化される（例えば S A E Q の遷移 518）前にリセットされる。ビットライン上のデータは、S A E N が高いとき（例えば遷移 506）に感知され、バックエンド回路 408 の出力（例えば S A \_ O U T \_ S L 2 ）がラッチ 410 により次の回路に渡される。その後、メモリアレイのセンス増幅器出力のラッチバージョン（例えば S A \_ O U T \_ S L 2 ）が、パイプライン段 403 へ提供される。完全パイプライン型動作中、制御クロック信号の第 1 段中のフロントエンドの回路 404 の動作と、制御クロック信号の第 2 段中のバックエンド 408 の動作により、制御クロック信号の完全な 1 サイクルで、パイプライン段 401 のワード線およびカラムデコードおよびメモリアレイが実行される。2030

#### 【 0019 】

本発明の少なくとも 1 つの実施形態では、パイプライン段 403 は、S A \_ O U T \_ S L 2 信号から適切な信号を選択する選択回路 412 を備えている（例えば方法選択、セクタ選択、データ再整列または他の適切な動作）。完全パイプライン型動作中に、選択回路 412 の出力はフリップフロップ 414 で格納され、制御クロック信号の立下がりエッジ（例えば遷移 508）後に、新しいデータがメモリ回路部分 400 により提供される。本発明の少なくとも 1 つの実施形態では、パイプライン段 403 は、データ処理論理回路 420 も備えており、データ処理論理回路 420 は S A \_ O U T \_ S L 2 信号に含まれる適切な信号の論理処理（例えばエラー訂正コード動作）および / または他の適切な処理を行なう。完全型パイプライン型動作中、データ処理論理回路 420 の出力は制御クロック信号の特定の位相中にラッチされる。従って、完全パイプライン型動作中、パイプライン段 403 のデータ選択および処理動作は、制御クロック信号の少なくとも 1 つの半サイクルに実行する。40

#### 【 0020 】

メモリ回路部 400 の 1 または複数の個々の回路部は、フィードバック信号、例えば f l u s h \_ o k 1 、 f l u s h \_ o k 2 、 f l u s h \_ o k 3 、 f l u s h \_ o k 4 を生50

成し、これらは回路部が余分のタイミングマージンを有しているかどうか示し、かつ／または、対応する回路部のタイミングマージンの量を示す。図6を参照すると、バックエンド回路408に備えられ得る例証的な回路部は、*f l u s h\_o k*信号であってもよい信号を生成する。回路600は、メモリアレイに含まれるビットセル602を示す。ビットセル602の内容を反映するために、ビットラインBLおよびXBLは予め充電され、読み込みアクセスの間に放電される。センス増幅器606は、SA\_EN信号によるBLおよびXBLの評価に基づいてデータ信号を生成する。プログラマブル遅延回路610は、センス増幅器606に類似の別のセンス増幅器（例えばセンス増幅器608）へのSA\_EN信号を遅延させることにより、読み動作のマージンを決定するために使用される。センス増幅器608の出力を適切に評価する場合、適切な技術を使用してプログラマブル遅延の大きさに基づいて定量可能なタイミングマージンが存在する。

#### 【0021】

図7を参照すると、バックエンド回路408に備えられ得るフィードバック信号生成回路の別の実施形態は、NANDゲート感知回路708を備えている。ビットセル702とセンス増幅器706は、回路710により制御される。NANDゲート感知回路708は、 $V_{DD}(k * V_{DD})$ の分数である所定のトリガー点を有する。タイミングマージンが存在すれば、NANDゲート感知回路は適切にビットセル704の出力を評価するだろう。タイミングマージンは、任意の適切な技術を使用して、NANDゲート感知回路708のトリガー点に基づいて定量化され得る。

#### 【0022】

戻って図4に参照すると、メモリ回路部分400はフロントエンド回路404、バックエンド回路408、選択回路412およびデータ処理論理回路420の各々に対する1つのフィードバック信号を備えているが、メモリ回路部分400の少なくとも1つの実施形態では、フィードバック信号は個々の回路部のうちのただ一つまたは複数により生成されてもよい。例えば、本質的にバランスのとれたパイプラインの任意の1つのパイプライン段が、タイミングマージンが存在するか否か示すかまたはパイプライン段のタイミングマージンの量を示す、フィードバック信号を生成してもよい。代わりに、最悪の場合のパイプライン段だけが、フィードバック信号を生成してもよい。メモリ回路部分400の少なくとも1つの実施形態では、フィードバック信号は、メモリ回路部分400に接続された制御回路（例えば図3の制御論理回路322）により、動作モードを選択するために使用されてもよい。選択された動作モードは、完全パイプライン型動作モードであってもよいし、またはフラッシュスルーモード（つまり減少数のパイプライン段を使用してパイプラインが実行する動作モード）であってもよい。特定のメモリ回路は、別のパイプライン段（つまりフラッシュ段）へ合体されるパイプライン段の数だけ異なる複数のフラッシュスルーモードを有してもよい。例えば、完全パイプライン型動作で4段階のパイプラインを有するメモリ回路は、3つのパイプライン段、2つのパイプライン段または1つの段（つまりメモリ回路自体の中にはパイプラインがないが、メモリ回路の境界に複数の状態要素を含む）を有するメモリ回路の個々の構成に相当するフラッシュスルーモードでも別々に動作してもよい。

#### 【0023】

フラッシュスルーモードでは、パイプラインの1つまたは複数の状態要素はトランスペアメントに構成される。例えば、状態要素は、状態要素を備えたバスから、または状態要素をバイパスする別のバスから選択するために、マルチプレクサを使用して完全にバイパスされてもよい。代わりに、フラッシュスルーモードでは、状態要素は入力信号を直接通って制御クロック信号と非同期に出力ノードへと入力信号を送るように構成されてもよい。メモリ回路部分400の少なくとも1つの実施形態では、状態要素をバイパスするのではなく、制御クロック信号はフラッシュモードを示す制御信号で論理上ORにされる。例えば、ラッチ406およびラッチ410を制御するためには*f l u s h\_l*が使用される。*f l u s h\_l*が低い場合、ラッチ406および410は、クロック制御信号に関して同期してそれぞれの入力信号を対応する出力ノードへ渡すように構成される。*f l u s*

10

20

30

40

50

$h_1$  が高い場合、ラッチ 406 および 410 は、クロック制御信号に関して非同期にそれぞれの入力信号を対応する出力ノードへ渡すように構成される。結果として、パイプライン段 401 および 403 は、完全パイプライン型構成と比較して待ち時間が短縮された、かかるパイプライン段に対応する動作を実行する一つのパイプライン段へと組み合わされる。

#### 【0024】

図 4 および 8 を参照すると、メモリ回路 400 が、第 1 のクロック周波数閾値（例えば  $f_{PEAK}/2$ ）に相当する第 1 のフラッシュスルーモード（例えば  $f_{1ush1} = '1'$  かつ  $f_{1ush2} = '0'$ ）に構成されている場合、フロントエンド回路 404 の出力は制御クロック信号の高い位相中に変化し、かつラッチ 406 を通ってバックエンド回路 408 に渡される。バックエンド回路 408 中のアレイに接続されたビットラインは、制御クロック信号の高位相（例えば遷移 810）中に予め充電される。制御クロック信号の低位相中、ワード線選択信号が遷移（例えば遷移 802）し、制御クロック信号の低位相中にかかる信号がビットライン上で発達する。バックエンド回路 408 の少なくとも 1 つの実施形態では、センス増幅器はフラッシュスルーモードで有効となる。従って、SAEN が高い（例えば破線の SAEN 波形で遷移 808）場合にビットライン上のデータが感知され、バックエンド回路 408 の出力がラッチ 410（例えば SA\_OUT\_SL2）を通ってパイプライン段 403 へ渡される。

#### 【0025】

バックエンド回路 408 の 1 つの少なくとも実施形態では、SAEN 信号は、フラッシュスルーモードで無効となり、これにより選択ビット線が無効にされたセンス増幅器を通過し、ラッチ 410（例えば遷移 818）を通じてパイプライン段 403 へ SA\_OUT および SA\_OUT\_SL2 が生成される。アレイ出力の特定の部分は選択回路 412 により選択され、データ処理論理回路 420 に提供される。その後、データ処理論理回路 420 の結果が、制御クロック信号の低位相中（例えば遷移 822）に OUT2 に渡される。制御クロック信号の低位相中に新しいデータがメモリ回路部分 400 により提供され、制御クロック信号の立ち上がりエッジ（例えば遷移 822 および 832 により定義）の後で有効となる。データは、完全型パイプライン型構成と比較して、待ち時間が改善された（例えばセンス増幅器が有効の場合、クロックサイクルの 2 分の 1 以下だけ改善され、センス増幅器が無効になる場合、クロックサイクルの 2 分の 1 よりも大きくだけ改善される）出力で提供されることに注意する。

#### 【0026】

図 4 を参照すると、メモリ回路部分 400 の少なくとも 1 つの実施形態では、クロック周波数の減少に伴いパイプラインの待ち時間が増加するため、パイプライン段の数は、第 2 のクロック周波数閾値（例えば  $f_{PEAK}/4$ ）に相当する 1 つまたは複数の追加の制御信号（例えば  $f_{1ush2}$ ）を使用して、一つのパイプライン段へ組み合わせることによりさらに減少され得る。例えば、制御クロック信号周波数が第 2 のクロック周波数閾値未満に低下した場合、 $f_{1ush2}$  はアサートされ、それによりラッチ 422 がトランスペアレントに構成される。従って、DOUT2A は、本質的に遅延無く、クロック制御信号と非同期に、OUT2 に移行する。結果として、フロントエンド回路 404、バックエンド回路 408、選択回路 412、およびデータ処理論理回路 420 は、制御クロック信号の多くて 1 つのサイクルの待ち時間を有する一つのパイプライン段を形成する。図 4 のメモリ回路の分割が例証的であることに留意する。パイプライン型メモリ回路の別の実施形態が他の適切な回路境界で分割されてもよいことが、当業者には理解される。

#### 【0027】

図 9 を参照すると、例証的な集積回路プロセッサ（例えば図 1 のプロセッサ 11）は、制御システム 900 の少なくとも一部分を備えている。制御システム 900 の少なくとも 1 つの実施形態では、制御装置 902 は、完全パイプライン型動作またはフラッシュスルーモードのためのキャッシュメモリ回路 908 を構成するために入力（例えば集積回路 7 に接続されたヒューズまたは図 1 の集積回路 7 の入力ピン上の信号の状態）を検知する。少

10

20

30

40

50

なくとも 1 つの実施形態では、制御装置 902 は、制御レジスタ 904 の内容に従い電源電圧レベルおよび / またはプロセッサ 11 のクロック信号周波数を動的に測定する。制御レジスタ 904 はハードウェアまたはソフトウェアの少なくとも一方により設定されてよい。例えば、集積回路プロセッサ上で実行するソフトウェアは、図 1 のプロセッサ 11 上で実行する命令に基づく制御レジスタ 904 を構成してもよい。それらの命令は、命令の種類（例えば L2 nap、deep nap、snoops、またはスレッドがすべて使用されていない場合）により、または命令中の追加の事前複号により、低電力モードの集積回路プロセッサを構成する。少なくとも 1 つの実施形態では、集積回路プロセッサは、パイプライン動作モードの表と、メモリ回路の制御クロック信号の 1 つまたは複数の周波数と電源電圧の 1 つまたは複数のレベルとに対応する値と、に基づいてパイプラインの動作モードを選択する。集積回路プロセッサは、対応する動作モードを決定すべくメモリ回路の 1 つまたは複数の目標待ち時間と、目標電力消費とを用いて表（例えば制御レジスタ 904 または他の適切な記憶回路に格納された表）にアクセスし、制御レジスタ 906 を構成する。

#### 【 0028 】

少なくとも 1 実施形態では、集積回路プロセッサが、低周波数および / または低電力モードを開始するためにパッドまたはピンから受け取った 1 または複数の入力に基づいて制御レジスタ 904 を書き込む。図 9 を戻って参照すると、制御装置 902 は、制御レジスタ 904 の内容に基づいて各メモリ回路に対するローカルメモリ制御信号（例えば制御クロック信号周波数および電源電圧レベル）を構成する。それらの値はメモリアクセス周波数および電圧制御レジスタ 906 に格納されてよく、これらはキャッシュメモリ回路 908 を制御するために使用される。

#### 【 0029 】

制御装置 902 は、キャッシュメモリ回路 908 が完全パイプライン型モードで動作するか、またはフラッシュスルーモードで動作するかを動的に選択するための、1 または複数のフラッシュモード制御信号も生成する。図 9 および 10 を参照すると、少なくとも 1 実施形態では、制御装置 902 は、特定のメモリ回路の動作点を、1 または複数の所定の閾値（例えば ( $f_{FREQ1}, V_{DD1}$ ) ( $f_{FREQ2}, V_{DD2}$ ) , THRESH1, THRESH2, THRESH3、および THRESH4）と比較することにより、特定のフラッシュスルーモードを有効または無効にする。かかる所定の閾値はメモリ回路（メモリ制御レジスタ 906 または他の適切なメモリ回路）に格納される。閾値レベルは、シミュレーション、目標動作点、温度、他の環境要因、または他の適切なパラメータの 1 つまたは複数に基づいて決定され、かつ利用され得る。さらに、閾値レベルは、例えばパイプライン段の動作を保証し、かつ動作モード間の余分の切り替えを低減すべく、制御ループヘヒステリシスを導入するように決定されてもよい。少なくとも 1 つの実施形態では、メモリ制御レジスタ 906 は、制御クロック信号の目標周波数と、電源電圧の目標レベルとを備えている。

#### 【 0030 】

図 10 を参照すると、動作点の関数としての、完全パイプライン型動作、第 1 のフラッシュスルーモードおよび第 2 のフラッシュスルーモード中の例証的な性能（例えば待ち時間）および電力消費が例証される。曲線部分 1002 および 1052 は、完全パイプライン型動作で構成された（例えば n 個のパイプライン段を有する）メモリ回路部分の性能と電力消費にそれぞれ相当する。曲線部分 1004 および 1054 は、第 1 のフラッシュスルーモードで構成された（例えば n - 1 個のパイプライン段を有する）メモリ回路部分の性能と電力消費にそれぞれ相当する。曲線部分 1006 および 1056 は、第 2 のフラッシュスルーモードで構成された（例えば n - 2 個のパイプライン段を有する）メモリ回路部分の性能と電力消費にそれぞれ相当する。モード間の遷移点は、シミュレーション、特定の動作点における目標電力消費と性能、温度、他の環境要因または他の適切なパラメータの 1 つまたは複数に基づいて決定可能である。

#### 【 0031 】

10

20

30

40

50

図4を戻って参照すると、完全パイプライン型モードに構成された時、フリップフロップ402からフリップフロップ414の出力までのメモリアクセスは、制御クロック信号の2つのサイクルの待ち時間を有する（例えば、制御クロック信号周波数は $f_{PEAK}$ に等しい）。制御クロック周波数が $f_{PEAK}$ から周波数 $f$ （ $f_{FREQ2} < f < f_{FREQ1}$ （例えば、 $f_{PEAK}/4 < f < f_{PEAK}/2$ ））を有する動作点まで減少される場合、2つのパイプライン段の論理の合計伝播遅延が、制御クロックサイクルよりも小さくなる。合計遅延時間が制御クロックサイクルの所定の割合よりも小さい場合（例えば制御クロックサイクルの85%）、クロックをスケールダウンしたときに失われた性能の一部を、 $f_{FREQ1}, V_{DD1}$ における曲線部分1002から曲線部分1004の性能の不連続性により示されるように、フラッシュスルーモードに入ることにより回復することが可能である。同様に、制御クロックが $f_{FREQ2}$ より低い動作点にさらに減少される場合、 $V_{DD2}$ （例えば $f_{PEAK}/4$ ）ラッチ422はフラッシュスルーモードに設定され、第2のフラッシュスルーモードに入つてもよい。クロックが $f_{FREQ2}$ よりも低く減少された場合に失われた性能の一部を、 $V_{DD2}$ で曲線部分1004から曲線部分1006までの性能の不連続性によって示されるように、少なくともクロックが $f_{FREQ2}$ 以下に計られる時失われた性能の一部は、 $f_{FREQ2}, V_{DD2}$ における曲線部分1004から曲線部分1006の性能の不連続性により示されるように、第2のフラッシュスルーモードに入ることにより回復することが可能である。

#### 【0032】

図9および11を参照すると、制御システム900の少なくとも1つの実施形態では、メモリ回路の動作方法の選択の際に、制御装置902はヒステレシスを導入する。つまり、電源電圧および/または制御クロック信号周波数の関数としてのモード選択は、電源電圧および/または制御クロック信号周波数の減少値と比較して、電源電圧および/または制御クロック信号周波数の増大値については異なる。電源電圧および/または制御クロック信号周波数の関数としてのモード選択は、電源電圧および/または制御クロック信号周波数に対する変更の大きさおよび方向に基づく。したがって、モード選択は、電源電圧および/または制御クロック信号周波数のみならず、電源電圧および/または制御クロック信号周波数の前回の値にも基づいて決まる。

#### 【0033】

例えば、少なくとも1実施形態では、制御装置902は、次の動作点を1または複数の閾値（例えば図10の閾値）と比較し、それに基づき1または複数の対応するインジケータを生成する。その後、制御装置902は、1または複数のインジケータに基づいて、パイプライン型動作モードを少なくとも部分的に選択する。キャッシュメモリ回路908が完全にパイプライン型動作のために構成される場合（例えば、状態1102）、次の動作点が第1の閾値（例えばTHRESH1）より大きいと、キャッシュメモリ回路908は次の動作点（1110）で完全にパイプライン化されたモードで動作し続ける。同様に、キャッシュメモリ回路908が完全パイプライン型動作のために構成され、次の動作点が、第1の閾値と第2の閾値（例えば第2の閾値は第1の閾値の85%に設定することが可能である）の間にある場合、キャッシュメモリ回路908は次の動作点（1108）で完全パイプライン端動作モードで動作し続ける。しかしながら、キャッシュメモリ回路908が完全パイプライン型動作のために構成され、次の動作点が第2の閾値よりも低い場合、制御装置902は次の動作点（1114）でキャッシュメモリ回路908を第1のフラッシュスルーモード（例えば、状態1104）に構成する。制御装置の少なくとも1つの実施形態では、第2のフラッシュスルーモードをサポートするのに十分なタイミングマージンをメモリが有していることをフィードバック信号（例えば図4の $f_{flush\_ok1}$ および/または $f_{flush\_ok2}$ ）が示さない限り、状態1102から状態1104への遷移はなされない。

#### 【0034】

キャッシュメモリ回路908が第1のフラッシュスルーモードで動作している場合（例えば状態1104）、次の動作点が第1の閾値よりも大きいと、キャッシュメモリ回路908は次の動作点（1112）で完全パイプライン型モードで動作する。キャッシュメモリ回路908が第2のフラッシュスルーモードで動作している場合（例えば状態1104）、次の動作点が第2の閾値よりも大きいと、キャッシュメモリ回路908は次の動作点（1112）で完全パイプライン型モードで動作する。

リ回路 908 が第 1 のフラッシュスルーモードで動作している場合に、次の動作点が第 4 の閾値よりも大きいが第 1 の閾値よりも小さいと、キャッシュメモリ回路 908 は次の動作点 (1116, 1118, 1120) で第 1 のフラッシュスルーモードで動作する。しかしながら、キャッシュメモリ回路 908 が第 1 のフラッシュスルーモードのために構成され、次の動作点が第 4 の閾値よりも小さい場合、キャッシュメモリ回路 908 は次の動作点 (1126) で第 2 のフラッシュスルーモード (例えば状態 1106) で動作する。制御装置の少なくとも 1 つの実施形態では、第 2 のフラッシュスルーモードをサポートするのに十分なタイミングマージンをメモリ回路が有していることをメモリフィードバック信号 (図 4 の例えば  $f_{l u s h\_o k 3}$  および / または  $f_{l u s h\_o k 4}$ ) が示さない限り、状態 1104 から状態 1106 への遷移はなされない。

10

### 【0035】

キャッシュメモリ回路 908 が第 2 のフラッシュスルーモード (例えば状態 1106) で動作している場合に、次の動作点が第 3 の閾値より大きいと、キャッシュメモリ回路 908 は次の動作点 (1124) で第 1 のフラッシュスルーモードで動作する。キャッシュメモリ回路 908 が第 2 のフラッシュモードで動作している場合に、次の動作点が第 3 の閾値未満であると、キャッシュメモリ回路 908 は次の動作点 (1128, 1130) で第 2 のフラッシュスルーモードで動作する。メモリ回路 400 のパイプライン段が対応する動作モードで適切に動作するだろうということを保証するために第 1, 第 2, 第 3, 第 4 の閾値を選択しければならないことに注意する。

### 【0036】

戻って図 10 に参照すると、完全パイプライン型動作の性能を有する動作点と比較していくつかの動作点の性能が改善されるのに加えて、キャッシュメモリ回路 908 の少なくとも 1 つの実施形態では、フラッシュスルーモードが電力消費の低減という利点を与える。省電力は、状態要素 (例えば状態要素を計測しないフロースルーモードまたはバイパスモードで構成) の切り換えの減少により達成されてもよい。一般に、状態要素の電力消費は、パイプラインラッチが多数 (例えば、通常 1 メガバイト、レベル 2 キャッシュでは 10,000 個のパイプラインラッチ) あるためメモリ回路において重要である。メモリ回路を動作させるフラッシュスルーモードは、低減された周波数制御クロック信号で動作する完全パイプライン型回路の電力消費から電力消費をさらに低減させてもよく、これは図 10 の曲線部分 1052 から曲線部分 1054 への、曲線部分 1054 から曲線部分 1056 への電力消費の不連続性により示されている通りである。

20

### 【0037】

図 12 を参照すると、本発明の少なくとも 1 つの実施形態では、調整可能なパイプラインメモリ回路部分 (例えばキャッシュメモリ回路 1208) に接続された論理回路 (例えば論理ブロック 1212) は、制御装置 1210 からメモリ回路の動作モードのインジケータを受け取る。制御装置 1210 は論理回路に制御信号を提供する。論理回路は、メモリ回路の可変の待ち時間に従って入力を受け取るべくメモリ回路を論理回路と同期させるために使用可能な論理制御信号を受け取る。論理回路も、かかる制御信号に基づいて適切な数のパイプライン段で構成されてもよい。

### 【0038】

回路と物理構造は一般的なものが想定されるが、現在の半導体設計および組立てでは、物理構造と回路が、後続の設計、試験または組立て段階に使用するのに適したコンピュータ可読の記述形式で具現化され得ることがよく理解されている。複数の構造および例証的な構成中の複数の個別部品として提示された機能が、組み合わされた構造またはコンポーネントとして実装されてもよい。本発明は、いずれも本明細書で説明し添付の特許請求の範囲に定義されるように、回路、回路のシステム、関連方法、およびかかる回路、システムならびに方法をコードするコンピュータ可読媒体を含むことが想定される。本明細書に使用する場合、コンピュータ可読媒体は少なくともディスク、テープまたは他の磁気媒体、光学媒体、半導体媒体 (例えばフラッシュメモリカード、ROM)、または電子媒体を含む。

30

40

50

## 【 0 0 3 9 】

本明細書に記載した本発明の説明は例示であって、以下の請求項に記載した本発明の範囲を限定することは意図しない。例えば、本発明は完全パイプライン型モードでメモリ回路部分 400 がパイプライン段 401 および 403 を備えた実施形態で説明されているが、当業者にはかかる教示を他の適切な境界により複数のパイプライン段へ分割されたメモリ回路部分に利用可能であることが理解されよう。本明細書に開示された実施形態のバリエーションおよび修正は、以下の請求項に記載した発明の範囲および趣旨から逸脱せずに、本明細書に記載した説明に基づいてなされ得る。

【 図 1 】

【 図 2 】

【 図 3 】

【図4】

【図5】

【図6】

【図8】

【図7】

【図 9】

【図 10】

【図 11】

【図 12】

---

フロントページの続き

(72)発明者 モイヤー、ウィリアム シー .

アメリカ合衆国 78620 テキサス州 ドリッピング スプリングス メドウ リッジ ドラ

イブ 1111

(72)発明者 グエン、ワイ ビー .

アメリカ合衆国 78754 テキサス州 オースティン ペイトン フォールズ ドライブ 1

635

審査官 野田 佳邦

(56)参考文献 特開平11-073770(JP,A)

特開2002-329395(JP,A)

(58)調査した分野(Int.Cl., DB名)

G06F 12/00 - G06F 12/06

G11C 11/401 - G11C 11/4099

G11C 11/41 - G11C 11/4197