(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-294418

(P2005-294418A)

(43) 公開日 平成17年10月20日(2005.10.20)

(51) Int.Cl.<sup>7</sup>

**H01L 21/336**

**G02F 1/1368**

**H01L 21/822**

**H01L 21/8234**

**H01L 27/04**

F 1

H01L 29/78    616A

G02F 1/1368

H01L 27/08    331E

H01L 27/04    C

H01L 27/08    102B

テーマコード(参考)

2 H092

5 F038

5 F048

5 F110

審査請求 未請求 請求項の数 11 O L (全 19 頁) 最終頁に続く

(21) 出願番号

特願2004-105182 (P2004-105182)

(22) 出願日

平成16年3月31日 (2004.3.31)

(71) 出願人

000006013

三菱電機株式会社

東京都千代田区丸の内二丁目2番3号

(74) 代理人

100064746

弁理士 深見 久郎

(74) 代理人

100085132

弁理士 森田 俊雄

(74) 代理人

100083703

弁理士 仲村 義平

(74) 代理人

100096781

弁理士 堀井 豊

(74) 代理人

100098316

弁理士 野田 久登

(74) 代理人

100109162

弁理士 酒井 将行

最終頁に続く

(54) 【発明の名称】半導体装置およびその製造方法

## (57) 【要約】

【課題】 製造工程を削減することができ、画素電極の電圧の低下を十分に抑止することができるGOLD構造の半導体装置およびその製造方法を提供する。

【解決手段】 本発明の半導体装置100は、n型TFT30とキャパシタ60とを備えた半導体装置であって、n型TFT30はソース領域30aおよびドレイン領域30bを有している。ソース領域30aおよびドレイン領域30bの各々は、n型TFT30のゲート電極12の真下に形成された第1不純物領域5b, 5cと、第1不純物領域5b, 5cの不純物濃度よりも高い不純物濃度を有する第2不純物領域5f, 5gとを有している。第1不純物領域5b, 5cの不純物濃度とキャパシタ60の一方電極8aの不純物濃度と同じである。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

トランジスタとキャパシタとを備えた半導体装置であって、

前記トランジスタはソース領域およびドレイン領域を有し、

前記ソース領域および前記ドレイン領域の各々は、前記トランジスタのゲート電極の真下に形成された前記第1不純物領域と、前記第1不純物領域の不純物濃度よりも高い不純物濃度を有する第2不純物領域とを有し、

前記第1不純物領域の不純物濃度と前記キャパシタの一方電極の不純物濃度とが同じであることを特徴とする、半導体装置。

**【請求項 2】**

前記トランジスタは第3不純物領域をさらに有し、

前記第3の不純物領域は前記第1不純物領域と前記第2不純物領域との間に形成されており、

前記第3不純物領域の不純物濃度は、前記第1不純物領域の不純物濃度よりも高く、前記第2の不純物領域の不純物濃度よりも低いことを特徴とする、請求項1に記載の半導体装置。

**【請求項 3】**

前記第1不純物領域の不純物濃度と同じ不純物濃度である前記一方電極の電位よりも前記キャパシタの他方電極の電位の方が常に高いことを特徴とする、請求項1または2に記載の半導体装置。

**【請求項 4】**

前記キャパシタの前記一方電極または他方電極と画素電極とは電気的に接続されていることを特徴とする、請求項1～3のいずれかに記載の半導体装置。

**【請求項 5】**

前記トランジスタはnチャネル型トランジスタであることを特徴とする、請求項1～4のいずれかに記載の半導体装置。

**【請求項 6】**

前記第1不純物領域の不純物濃度は $10^{17}$ 原子/ $\text{cm}^3$ 以上 $10^{19}$ 原子/ $\text{cm}^3$ 以下であることを特徴とする、請求項1～5のいずれかに記載の半導体装置。

**【請求項 7】**

第1トランジスタとキャパシタとを備えた半導体装置の製造方法であって、

第1トランジスタ形成領域とキャパシタ形成領域とを有する半導体膜を基板上に形成する工程と、

第1不純物濃度を有する1対の第1不純物領域を前記半導体膜の前記第1トランジスタ形成領域に形成する工程と、

前記1対の第1不純物領域の間に挟まれるチャネル形成領域と、前記1対の第1不純物領域の各々の一部とを第1絶縁膜を介して覆うように、前記第1トランジスタの第1ゲート電極を前記半導体膜上に形成する工程と、

前記第1不純物領域よりも不純物濃度の高い第2不純物濃度を有する1対の第2不純物領域を前記第1ゲート電極の真下を除く第1不純物領域内に形成する工程とを備え、

前記1対の第1不純物領域を形成する工程と同一の工程により、前記第1不純物濃度を有する前記キャパシタの一方電極が前記半導体膜に形成されることを特徴とする、半導体装置の製造方法。

**【請求項 8】**

前記第1不純物領域よりも不純物濃度が高く、前記第2不純物領域よりも不純物濃度が低い第3不純物濃度を有する1対の第3不純物領域を前記第1不純物領域と前記第2不純物領域との間に形成する工程をさらに備えることを特徴とする、請求項7に記載の半導体装置の製造方法。

**【請求項 9】**

前記第1ゲート電極を形成する工程は、

10

20

30

40

50

前記半導体膜の前記第1トランジスタ形成領域上に前記第1絶縁膜を介して第1導電膜を形成する工程と、

前記チャネル形成領域と、前記1対の第1不純物領域の各々の一部とを覆うように、第1レジストを前記第1導電膜上に形成する工程と、

前記第1レジストをマスクとして、前記第1レジストよりも線幅が細くなるように前記第1導電膜をエッチングする工程とを含み、

前記第1レジストをマスクとして不純物を注入することにより前記第2不純物濃度を有する前記1対の第2不純物領域が前記第1不純物領域内に形成され、

前記第1のゲート電極をマスクとして不純物を注入することにより前記1対の第3不純物領域が形成されることを特徴とする、請求項8に記載の半導体装置の製造方法。 10

#### 【請求項10】

第2トランジスタを形成する工程をさらに備え、

前記第2トランジスタを形成する工程は、

前記第1導電膜を形成する工程と同一の工程により、前記第2トランジスタ形成領域をさらに有する前記半導体膜の前記第2トランジスタ形成領域上に第2絶縁膜を介して第2導電膜を形成する工程と、

第1レジストを形成する工程と同一の工程により、第2レジストを前記第2導電膜上に形成する工程と、

前記第1導電膜をエッチングする工程と同一の工程により、前記第2レジストをマスクとして、前記第2レジストよりも線幅が細くなるように前記第2導電膜をエッチングする工程と、 20

前記1対の第2不純物領域を形成する工程と同一の工程により、前記第2レジストをマスクとして不純物を注入することにより第4不純物濃度を有する1対の第4不純物領域を前記半導体層の前記第2トランジスタ形成領域に形成する工程と、

前記1対の第3不純物領域を形成する工程と同一の工程により、前記第2導電層をマスクとして不純物を注入することにより第5の不純物濃度を有する1対の第5不純物領域を形成する工程とを含むことを特徴とする、請求項9に記載の半導体装置の製造方法。

#### 【請求項11】

前記第1ゲート電極を形成する工程と同一の工程により、前記キャパシタの他方電極が形成されることを特徴とする、請求項7～10のいずれかに記載の半導体装置の製造方法 30。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、半導体装置およびその製造方法に関し、より特定的には、トランジスタとキャパシタとを備えた半導体装置およびその製造方法に関する。

##### 【背景技術】

##### 【0002】

近年、絶縁表面を有する基板上に形成された、厚さ数～数百nm程度の半導体薄膜を用いて薄膜トランジスタ(TFT:Thin Film Transistor)を構成し、このTFTで形成した大面積集積回路を有する半導体装置の開発が進んでいる。アクティブマトリクス型液晶表示装置、EL表示装置、および密着型イメージセンサはその代表例として知られている。特に、ポリシリコン膜などの結晶質シリコン膜を活性層にしたTFTは電界効果移動度が高いことから、いろいろな機能回路を形成することも可能である。 40

##### 【0003】

たとえば、アクティブマトリクス型液晶表示装置は、機能ブロックごとに画像表示を行なう画素回路と、CMOS(Complementary Metal Oxide Semiconductor)回路を基本としたシフトレジスタ回路、レベルシフタ回路、バッファ回路、サンプリング回路などの画 50

素回路を制御するための駆動回路とが一枚の基板上に形成される。

#### 【0004】

アクティブマトリクス型液晶表示装置の画素回路が設けられた基板には、数十から数百個の画素の各々に画素TFTの各々が配置され、その画素TFTの各々に画素が設けられている。液晶を挟んで対向するもう一方の基板には対向電極が設けられており、液晶を誘電体とした一種のコンデンサを形成している。そして、画素の各々に印加する電圧をTFTのスイッチング機能により制御して、このコンデンサへの電荷の供給が制御される。これにより、液晶を駆動し、透過光量を制御して画像が表示される。

#### 【0005】

画素TFTはnチャネル型TFTからなり、スイッチング素子として液晶に電圧を印加して駆動させるものである。液晶は交流で駆動させるので、フレーム反転駆動と呼ばれる方式が多く採用されている。この方式では画面を書き換えるまでの1フレームの間、液晶に印加された電圧を保持する必要がある。画素TFTのオフ電流(TFTがオフ動作時に流れるドレイン電流)が大きいと、液晶に印加された電圧が時間とともに減少し、表示品質を劣化させることになる。このため、画素TFTのオフ電流値を低減することが求められている。

#### 【0006】

オフ電流値を低減することのできるTFTの構造として、LDD(Lightly Doped Drain)構造が知られている。LDD構造のTFTは、ソース領域およびドレイン領域の各々からチャネル形成領域側へ伸びた低濃度の不純物領域(LDD領域)の各々を有している。LDD構造のTFTによれば、ドレイン領域とチャネル形成領域との界面付近の電界を緩和することができるので、オフ電流値を低減することができる。また、LDD構造のTFTでは、ソース/ドレイン間の電界をLDD領域で緩和することでソース/ドレイン間の耐圧をある程度向上できるが、ソース/ドレイン間の耐圧はそれでもなお不十分であった。

#### 【0007】

そこで、ソース/ドレイン間の耐圧を一層向上することのできるTFTの構造として、GOLD(Gate Overlapped Lightly Doped Drain)構造が知られている。GOLD構造のTFTは、ソース領域およびドレイン領域から伸びた低濃度の不純物領域(GOLD領域)をゲート電極の真下のチャネル形成領域に有している。GOLD構造のTFTによれば、不純物の注入によりGOLD領域の閾値電圧が低下するので、ドレイン領域側の空乏層の形成が抑制される。したがって、ソース/ドレイン間の耐圧を向上することができる。

#### 【0008】

また、GOLD構造のTFTによれば、TFTのオン動作時にソース/ドレイン間に流れる電流(オン電流)の低下を防ぐことができる。すなわち、通常のTFTでは、ゲートに比べてドレインに高電圧を印加すると、ドレイン側の接合部に大きな電界ができる。そして、この電界により加速された電子がインパクトイオン化現象を起こし、電子・正孔対を発生する。電子・正孔対のうち、電子は、ゲート酸化膜と半導体膜との間のエネルギー障壁を超えて、ゲート酸化膜中に注入される。そして、酸化膜に入った電子は負の固定電荷となり、TFTの閾値電圧を正側へシフトさせる。その結果、TFTのオン電流の低下を招く。これに対し、GOLD構造のTFTによれば、ゲートに比べてドレインに高電圧を印加しても、ドレイン側の接合部に大きな電界が形成されない。このため、インパクトイオン化現象が起こりにくくなるので、TFTのオン電流の低下を抑止することができる。

#### 【0009】

しかしながら、GOLD構造のTFTでは、ゲート電極下のチャネル形成領域にまで低濃度の不純物領域が形成されているので、チャネルが形成されやすくなり、GOLD領域の閾値電圧がチャネル部分に比べて低くなる。このため、オフ電流が流れやすくなり、オフ電流値が増加するという問題があった。このような問題は、GOLD構造とLDD構造

10

20

30

40

50

とを有するTFTにも共通する問題であった。ここで、GOLD構造とLDD構造とを有するTFTとは、ソース領域およびドレイン領域よりも低濃度の不純物領域であるLDD領域を、ソース領域およびドレイン領域とチャネル形成領域との間に有しており、かつLDD領域よりもさらに低濃度のGOLD領域を、LDD領域とチャネル形成領域との間に有しているTFTである。

#### 【0010】

オフ電流値が増加するというGOLD構造のTFTの問題を解決する方法として、画素の各々に印加する電圧を保持するためのキャパシタをさらに形成する方法がある。画素の各々に印加する電圧の低下量はオフ電流の量に比例し、キャパシタの容量に反比例する。したがって、この方法によれば、TFTのオン電流の低下を抑止しつつ、TFTのオフ電流による画素電極の電圧の低下をキャパシタに蓄積した電荷によって抑制することができる。

#### 【0011】

なお、ソース領域およびドレイン領域が高濃度の不純物領域と低濃度の不純物領域とを有するTFTとの製造方法が、たとえば特開2001-345448号公報（特許文献1）に開示されている。また、MOS（Metal Oxide Semiconductor）キャパシタとGOLD構造のTFTとの製造方法が、たとえば特開2002-76351号公報（特許文献2）に開示されている。

【特許文献1】特開2001-345448号公報

【特許文献2】特開2002-76351号公報

10

20

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0012】

キャパシタと、GOLD構造のTFTとを1つの基板上に形成しようとすると、その製造工程が複雑なものになり、工程数が増加してしまうという問題があった。

#### 【0013】

ここで、特許文献2に開示された技術では、GOLD構造のTFTとMOSキャパシタとがほぼ同一の工程によって製造されている。MOSキャパシタとは、MOSトランジスタとほぼ同様の構成を有するキャパシタである。MOSキャパシタにおいては、MOSトランジスタのゲート電極となる部分がキャパシタの上部電極となり、MOSトランジスタのソース領域となる部分と、ドレイン領域となる部分と、チャネル形成領域となる部分とがキャパシタの下部電極となる。MOSキャパシタにおいては、キャパシタの上部電極に印加される電圧によってキャパシタの容量が大きく変化する。このため、安定してキャパシタに電荷を蓄積することができず、TFTのオフ電流による画素電極の電圧の低下を十分に抑止することができないという問題があった。

#### 【0014】

したがって、本発明の目的は、製造工程を削減することができ、画素電極の電圧の低下を十分に抑止することができるGOLD構造の半導体装置およびその製造方法を提供することである。

#### 【課題を解決するための手段】

#### 【0015】

本発明の半導体装置は、トランジスタとキャパシタとを備えた半導体装置であって、トランジスタはソース領域およびドレイン領域を有している。ソース領域およびドレイン領域の各々は、トランジスタのゲート電極の真下に形成された第1不純物領域と、第1不純物領域の不純物濃度よりも高い不純物濃度を有する第2不純物領域とを有している。第1不純物領域の不純物濃度とキャパシタの一方電極の不純物濃度とが同じである。

#### 【発明の効果】

#### 【0016】

本発明の半導体装置およびその製造方法によれば、1対の第1不純物領域を形成する工程と同一の工程により、第1不純物濃度を有するキャパシタの一方電極を形成することが

30

40

50

できる。したがって、半導体装置の製造工程を削減することができる。また、キャパシタの一方電極が1つの不純物領域で形成されるので、キャパシタの容量がキャパシタに印加される電圧によって変化しにくい。したがって、安定してキャパシタに電荷を蓄積することができ、画素電極の電圧の低下を十分に抑止することができる。

#### 【発明を実施するための最良の形態】

##### 【0017】

以下、本発明の実施の形態について、図に基づいて説明する。

##### 【0018】

###### (実施の形態1)

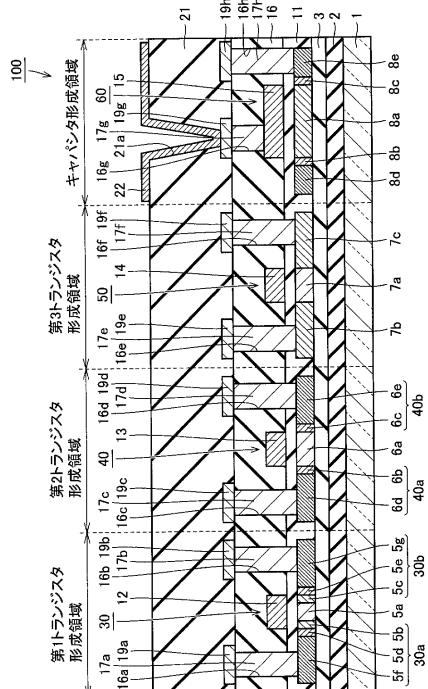

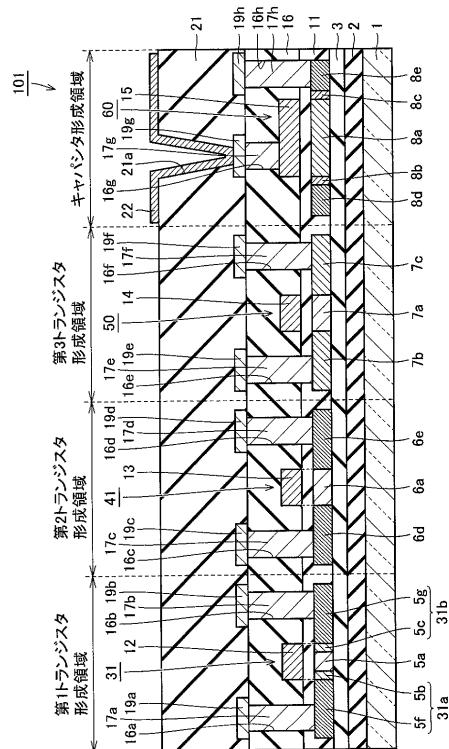

図1は、本発明の実施の形態1における半導体装置の構成を示す断面図である。

10

##### 【0019】

図1に示すように、本実施の形態の半導体装置100は、第1トランジスタ形成領域に形成されたGOLD構造とLDD構造とを有するn型TFT30と、第2トランジスタ形成領域に形成されたLDD構造のn型TFT40と、第3トランジスタ形成領域に形成されたp型TFT50と、キャパシタ形成領域に形成されたキャパシタ60とを備えている。

##### 【0020】

基板1の上にSiN(窒化シリコン)膜2および下地膜3が積層して形成されている。n型TFT30は、ソース領域30aと、ドレイン領域30bと、チャネル形成領域5aとを第1トランジスタ形成領域の下地膜3の上に有している。ソース領域30aは、GOLD領域である第1不純物領域5bと、LDD領域である第3不純物領域5dと、第2不純物領域5fとを有している。ドレイン領域30bは、GOLD領域である第1不純物領域5cと、LDD領域である第3不純物領域5eと、第2不純物領域5gとを有している。第3の不純物領域5d, 5eの各々は、第2の不純物領域5f, 5gの各々からチャネル形成領域5aの方へ伸びるように形成されている。第1不純物領域5b, 5cの各々は、第3の不純物領域5d, 5eの各々からチャネル形成領域5aの方へ伸びるように形成されている。チャネル形成領域5aのチャネル長(図1中横方向の長さ)は、たとえば1μmである。第3の不純物領域5d, 5eの各々の不純物濃度は第1不純物領域5b, 5cの各々の不純物濃度よりも高く、第2の不純物領域5g, 5fの各々の不純物濃度は第3不純物領域5d, 5eの各々の不純物濃度よりも高い。第1不純物領域5b, 5cの各々はゲート電極12の真下に形成されている。すなわち、チャネル形成領域5aと、第1不純物領域5b, 5cの各々とをゲート絶縁膜となるSiO<sub>2</sub>膜11を介して覆うように、n型TFT30のゲート電極12が形成されている。なお、第1不純物領域5b, 5cの不純物濃度は10<sup>17</sup>原子/cm<sup>3</sup>以上10<sup>19</sup>原子/cm<sup>3</sup>以下であることが好ましい。

20

30

30

40

##### 【0021】

キャパシタ60は、下部電極8aと上部電極15とをキャパシタ形成領域の下地膜3上有している。下部電極8aと上部電極15とは、誘電体となるSiO<sub>2</sub>膜11を挟んで互いに対向している。本実施の形態の半導体装置においては、キャパシタ60の下部電極8aの不純物濃度と、n型TFT30の第1不純物領域5b, 5cの不純物濃度とが同じである。なお、下部電極8aの両側には中濃度不純物領域8b, 8cの各々が形成されており、中濃度領域8b, 8cの各々の両側には高濃度不純物領域8d, 8eの各々が形成されている。

##### 【0022】

n型TFT40は、ソース領域40aと、ドレイン領域40bと、チャネル形成領域6aとを第2トランジスタ形成領域の下地膜3の上に有している。ソース領域40aは、LDD領域である第5不純物領域6bと、第4不純物領域6dとを有している。ドレイン領域30bは、LDD領域である第5不純物領域6cと、第4不純物領域6eとを有している。第5の不純物領域6b, 6cの各々は、第4の不純物領域6d, 6eの各々からチャネル形成領域5aの方へ伸びるように形成されている。第4の不純物領域6d, 6eの各々の不純物濃度は第5不純物領域6b, 6cの各々の不純物濃度よりも高い。チャネル形

50

成領域 6 a をゲート絶縁膜となる  $\text{SiO}_2$  膜 11 を介して覆うように、n 型 TFT40 のゲート電極 13 が形成されている。

#### 【0023】

p 型 TFT50 は、ソース領域 7 b と、ドレイン領域 7 c と、チャネル形成領域 7 a を第3トランジスタ形成領域の下地膜 3 の上に有している。チャネル形成領域 7 a をゲート絶縁膜となる  $\text{SiO}_2$  膜 11 を介して覆うように、p 型 TFT50 のゲート電極 14 が形成されている。

#### 【0024】

ゲート電極 12 ~ 14 と上部電極 15 とを覆うように、 $\text{SiO}_2$  膜 11 上に層間絶縁膜 16 が形成されている。 $\text{SiO}_2$  膜 11 および層間絶縁膜 16 には孔 16 a ~ 16 h の各々が形成されており、孔 16 a ~ 16 h の各々にはコンタクト 17 a ~ 17 h の各々が形成されている。コンタクト 17 a と n 型 TFT30 の第1不純物領域 5 f とは電気的に接続されており、コンタクト 17 b と n 型 TFT30 の第1不純物領域 5 g とは電気的に接続されている。コンタクト 17 c と n 型 TFT40 の第4不純物領域 6 d とは電気的に接続されており、コンタクト 17 d と n 型 TFT40 の第4不純物領域 6 e とは電気的に接続されている。コンタクト 17 e と p 型 TFT50 のソース領域 7 b とは電気的に接続されており、コンタクト 17 f と p 型 TFT50 のドレイン領域 7 c とは電気的に接続されている。コンタクト 17 g とキャパシタ 60 の上部電極 15 とは電気的に接続されており、コンタクト 17 h とキャパシタ形成領域の高濃度不純物領域 8 e とは電気的に接続されている。

10

20

30

#### 【0025】

コンタクト 17 a, 17 b の各々と電気的に接続するように、n 型 TFT30 のソース電極 19 a およびドレイン電極 19 b の各々が層間絶縁膜 16 上に形成されている。コンタクト 17 c, 17 d の各々と電気的に接続するように、n 型 TFT40 のソース電極 19 c およびドレイン電極 19 d の各々が層間絶縁膜 16 上に形成されている。コンタクト 17 e, 17 f の各々と電気的に接続するように、p 型 TFT50 のソース電極 19 e およびドレイン電極 19 f の各々が層間絶縁膜 16 上に形成されている。コンタクト 17 g, 17 h の各々と電気的に接続するように、配線 19 g, 19 h の各々が層間絶縁膜 16 上に形成されている。

#### 【0026】

ソース電極 19 a, 19 c, 19 e、ドレイン電極 19 b, 19 d, 19 f および配線 19 g, 19 h の各々を覆うように、層間絶縁膜 16 上に層間絶縁膜 21 が形成されている。層間絶縁膜 21 には溝 21 a が形成されており、溝 21 a の内壁に沿うように画素電極 22 が形成されている。画素電極 22 と配線 19 g とは電気的に接続されている。配線 19 h には、配線 19 g よりも配線 19 h が低い電位となるような電圧が常に印加される。また、画素電極 22 は画素用トランジスタのドレイン領域と（図示なし）電気的に接続されている。

#### 【0027】

本実施の形態の半導体装置 100 では、GOLD構造とLDD構造とを有する n 型 TFT30 と、LDD構造の n 型 TFT40 と、p 型 TFT50 とが、各々の特性に応じて適切に配置される。具体的には、画素用トランジスタのように高電圧で駆動され、低いオフ電流が要求される部分には GOLD 構造と LDD 構造とを有する n 型 TFT30 が配置される。また、CMOS 駆動回路のように多数のトランジスタを集積する部分には占有面積の小さい LDD 構造の n 型 TFT40 および p 型 TFT50 が配置される。

40

#### 【0028】

なお、n 型 TFT30 のゲート絶縁膜と、n 型 TFT40 のゲート絶縁膜と、p 型 TFT50 のゲート絶縁膜と、キャパシタ 60 の誘電体膜とは、連続した  $\text{SiO}_2$  膜 11 で形成されている場合について示したが、本発明はこのような場合の他、ゲート絶縁膜とキャパシタの誘電体膜とが互いに分離していてもよい。また、n 型 TFT30 のソース領域 30 a およびドレイン領域 30 b およびチャネル形成領域 5 a（以下、半導体膜）と、n 型

50

TFT40の半導体膜と、p型TFT50の半導体膜と、キャパシタ60の下部電極8aとが互いに分離している場合について示したが、本発明はこのような場合の他、これらの半導体膜とキャパシタの下部電極とが互いに連続していてもよい。

#### 【0029】

続いて、本実施の形態の半導体装置の製造方法について説明する。

#### 【0030】

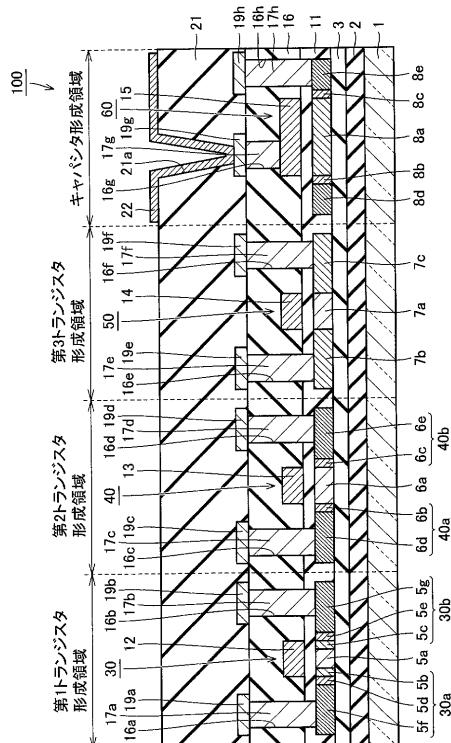

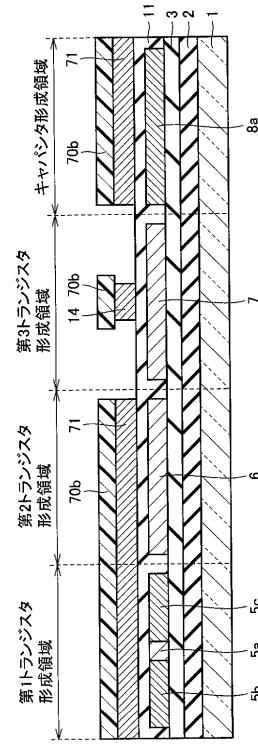

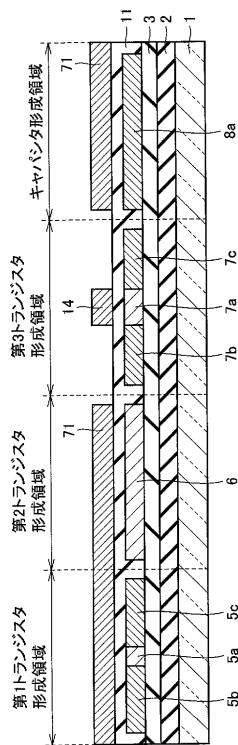

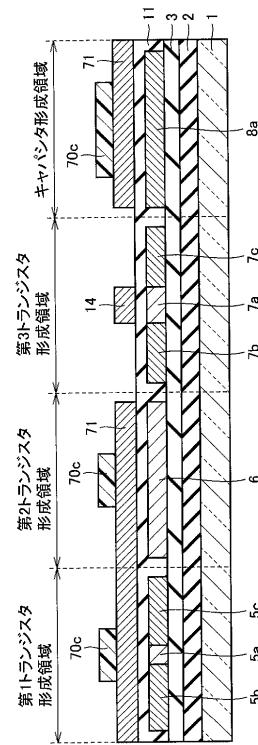

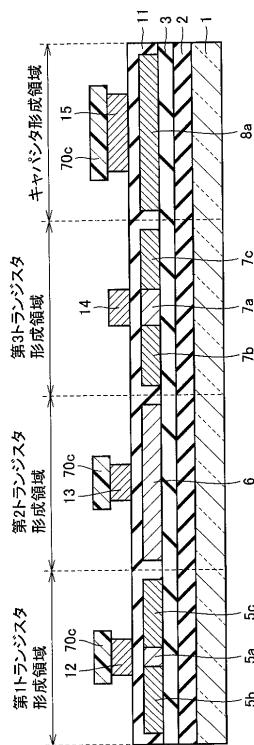

図2～図10は、本発明の実施の形態1における半導体装置の製造方法を工程順に説明する図である。

#### 【0031】

図2に示すように、たとえば1737ガラス(コーニング社製)よりなる基板1を準備する。そして、たとえば100nmの膜厚のSiN膜2と、たとえば100nmの膜厚のSiO<sub>2</sub>よりなる下地膜3とをプラズマCVD(Chemical Vapor Deposition)により基板1上に積層して形成する。ここで、SiN膜2は、基板1からの不純物が半導体膜へ拡散するのを防ぐために形成されるものである。SiNの代わりにSiON, SiC, AlN, Al<sub>2</sub>O<sub>3</sub>などを用いてもよい。また、SiN膜2と下地膜3とを省略してもよく、基板1上に他の下地膜をさらに積層してもよい。次に、アモルファスシリコン膜をプラズマCVDにより下地膜3上に形成し、アモルファスシリコン膜を真空中で熱処理する。この熱処理によってアモルファスシリコン中の不要な水素が除去される。次に、アモルファスシリコン膜にたとえばXeClレーザを照射することにより、アモルファスシリコン膜を多結晶シリコン膜に変える。多結晶シリコン膜中のシリコンの結晶粒径は約0.5μmとなる。なお、XeClレーザを照射する代わりに、たとえばYAG(Yttrium Aluminum Garnet)レーザやCW(Continuous Wave)レーザを照射してもよく、たとえばNi(ニッケル)などの触媒を用いて熱アニールを行なってもよい。次に、多結晶シリコン膜上にレジストをパターニングし、このレジストをマスクとして多結晶シリコン膜をドライエッティングする。これにより、半導体膜としての多結晶シリコン膜5～8がアイランド状に形成される。その後、アッシングと薬液処理によりレジストを除去する。

#### 【0032】

続いて、図3に示すように、多結晶シリコン膜5～8を覆うようにたとえば100nmの膜厚のSiO<sub>2</sub>膜をプラズマCVDにより形成する。プラズマCVDの原料としてはたとえばTEOS(Tetra Ethyl Ortho Silicate)とO<sub>2</sub>とを用いる。次に、第1トランジスタ形成領域のSiO<sub>2</sub>膜11の一部と、第2および第3トランジスタ形成領域のSiO<sub>2</sub>膜11とを覆うようにレジスト70aを形成する。次に、レジスト70aをマスクとして、多結晶シリコン膜5と多結晶シリコン膜8とにたとえば1.3×10<sup>-17</sup>Jの加速エネルギーで5×10<sup>12</sup>原子/cm<sup>2</sup>の注入量のP(リン)を注入する。これにより、多結晶シリコン膜5に第1不純物領域5b, 5cが形成され、それと同時に、多結晶シリコン膜8にキャパシタ60の下部電極8aが形成される。なお、多結晶シリコン膜5における第1不純物領域5bと第1不純物領域5cとの間の領域は、チャネル形成領域5aとなる。その後、アッシングと薬液処理によりレジスト70aを除去する。

#### 【0033】

続いて、図4に示すように、たとえば200nmの膜厚のCr(クロム)よりなる導電膜71をスパッタ法により形成する。これにより、第1不純物領域5b, 5cおよびチャネル形成領域6aの第1トランジスタ形成領域上にSiO<sub>2</sub>膜11を介して導電膜71が形成される。次に、第1および第2トランジスタ形成領域の導電膜71と、第3トランジスタ形成領域の導電膜71の一部と、キャパシタ形成領域の導電膜71とを覆うようにレジスト70bを形成する。次に、レジスト70bをマスクとして導電膜71をウエットエッティングする。これにより、p型TFT50のゲート電極14が形成される。その後、アッシングと薬液処理によりレジスト70bを除去する。

#### 【0034】

続いて、図5に示すように、導電膜71をマスクとして、第3トランジスタ形成領域の多結晶シリコン膜7にたとえばB(ボロン)を注入する。これにより、多結晶シリコン膜

10

20

30

40

50

7 にソース領域 7 b およびドレイン領域 7 c が形成される。多結晶シリコン膜 7 のソース領域 7 b とドレイン領域 7 c との間の領域は、チャネル形成領域 7 a となる。

#### 【0035】

続いて、図 6 に示すように、チャネル形成領域 5 a と、第 1 不純物領域 5 b , 5 c の各々の一部とを覆うように、レジスト 70 c を導電膜 71 上に形成する。また、第 2 トランジスタ形成領域の一部と、キャパシタ形成領域の一部とを覆うように、レジスト 70 c を導電膜 71 上にも形成する。

#### 【0036】

続いて、図 7 に示すように、レジスト 70 c をマスクとして、レジスト 70 c よりも線幅が細くなるように導電膜 71 をウェットエッチングする。ここで、「線幅」とは、チャネル長（図 7 中横方向）方向の長さである。これにより、チャネル形成領域 5 a と、第 1 不純物領域 5 b , 5 c の各々の一部とを SiO<sub>2</sub> 膜 11 を介して覆うように、第 1 トランジスタのゲート電極 12 が形成される。ゲート電極 12 の形成と同時に、n 型 TFT 40 のゲート電極 13 が形成され、キャパシタ 60 の上部電極 15 が形成される。

#### 【0037】

続いて、図 8 に示すように、レジスト 70 d を第 3 トランジスタ形成領域に形成する。そして、レジスト 70 c , 70 d をマスクとして、たとえば  $1.3 \times 10^{-17}$  J の加速エネルギーで  $1 \times 10^{14}$  原子 / cm<sup>2</sup> の注入量の P を注入する。これにより、n 型 TFT 30 の第 2 不純物領域 5 f , 5 g が第 1 不純物領域 5 b , 5 c 内に形成され、それと同時に、第 4 不純物領域 6 d , 6 e が多結晶シリコン膜 6 に形成される。さらに、下部電極 8 a の両端に高濃度不純物領域 8 d , 8 e が形成される。

#### 【0038】

続いて、図 9 に示すように、アッシングと薬液処理によりレジスト 70 c , 70 d を除去する。そして、ゲート電極 12 ~ 14 および上部電極 15 をマスクとして、たとえば  $1.3 \times 10^{-17}$  J の加速エネルギーで  $1 \times 10^{13}$  原子 / cm<sup>2</sup> の注入量の P を注入する。このとき、ゲート電極 12 , 13 および上部電極 15 はレジスト 70 c よりも線幅が細くなっているので、ゲート電極 12 , 13 および上部電極 15 をマスクとして不純物を注入することにより、レジスト 70 c をマスクとしたときには不純物が注入されなかった領域にも不純物を注入することができる。これにより、第 3 不純物領域 5 d , 5 e が第 1 不純物領域 5 b , 5 c 内に形成され、それと同時に、第 5 不純物領域 6 b , 6 c が多結晶シリコン膜 6 に形成される。なお、多結晶シリコン膜 6 の第 5 不純物領域 6 b と第 5 不純物領域 6 c との間の領域は、チャネル形成領域 6 a となる。さらに、下部電極 8 a の両端に中濃度不純物領域 8 b , 8 c が形成される。

#### 【0039】

続いて、図 10 に示すように、ゲート電極 12 ~ 14 および上部電極 15 を覆うように SiO<sub>2</sub> 膜 11 上に層間絶縁膜 16 を形成する。次に、ソース領域 30 a , 40 a , 7 b の各々と、ドレイン領域 30 b , 40 b , 7 c の各々と、上部電極 15 の一部と、高濃度不純物領域 8 e とを露出するように、層間絶縁膜 16 に孔 16 a ~ 16 h の各々を形成する。次に、孔 16 a ~ 16 h の各々の内部にたとえば Cr よりなるコンタクト 17 a ~ 17 h の各々を形成する。ここで、高濃度不純物領域 8 e とコンタクト 17 h とを電気的に接続することにより、コンタクト 17 h のコンタクト抵抗を低減することができる。次に、ソース電極 19 a , 19 c , 19 e 、ドレイン電極 19 b , 19 d , 19 f および配線 19 g , 19 h の各々をコンタクト 17 a ~ 17 h の各々と電気的に接続するように層間絶縁膜 16 上に形成する。ソース電極 19 a , 19 c , 19 e 、ドレイン電極 19 b , 19 d , 19 f および配線 19 g , 19 h は、たとえば Al (アルミニウム) により形成される。

#### 【0040】

次に、図 1 に示すように、ソース電極 19 a , 19 c , 19 e 、ドレイン電極 19 b , 19 d , 19 f および配線 19 g , 19 h の各々を覆うように、層間絶縁膜 16 上に層間絶縁膜 21 を形成する。次に、配線 19 g の一部を露出するように、層間絶縁膜 21 に溝

10

20

30

40

50

21aを形成する。次に、溝21aの内壁面に沿って画素電極22を形成する。以上の工程により本実施の形態の半導体装置100が完成する。

#### 【0041】

本実施の形態の半導体装置100およびその製造方法によれば、GOLD領域である第1不純物領域5b, 5cを形成する工程と同一の工程により、第1不純物領域5b, 5cと同じ不純物濃度を有するキャパシタ60の下部電極8aを形成することができる。したがって、半導体装置の製造工程を削減することができる。また、キャパシタ60の下部電極8aが1つの不純物領域8aで形成されるので、キャパシタの容量がキャパシタに印加される電圧によって変化しにくい。したがって、安定してキャパシタに電荷を蓄積することができ、画素電極22の電圧の低下を十分に抑止することができる。

10

#### 【0042】

本実施の形態の半導体装置100においては、ソース領域30aおよびドレイン領域30bは第3不純物領域5d, 5eを有している。第3の不純物領域5d, 5eは第1不純物領域5b, 5cと第2不純物領域5f, 5gとの間に形成されており、第3不純物領域5d, 5eの不純物濃度は、第1不純物領域5b, 5cの不純物濃度よりも高く、第2の不純物領域5f, 5gの不純物濃度よりも低い。

#### 【0043】

本実施の形態の半導体装置100の製造方法においては、第1不純物領域5b, 5cよりも不純物濃度が高く、第2不純物領域5f, 5gよりも不純物濃度が低い第3不純物領域5d, 5eを第1不純物領域5b, 5cと第2不純物領域5f, 5gとの間に形成する。

20

#### 【0044】

これにより、ソース領域30aおよびドレイン領域30bの各々がGOLD領域とLD領域とを有するので、ドレイン領域30bとチャネル形成領域5aとの界面付近の電界を一層緩和することができる。その結果、n型TFT30のオフ電流値を一層低減することができる。

#### 【0045】

本実施の形態の半導体装置100においては、キャパシタ60の下部電極8aの電位よりもキャパシタ60の上部電極15の電位の方が常に高い。

30

#### 【0046】

キャパシタの一方電極が不純物領域で形成される場合には、キャパシタの容量がキャパシタに印加される電圧により変化する。言い換えれば、キャパシタがC(容量)-V(電圧)特性を有する。キャパシタは、電圧が一定値以下の場合に電圧により容量が変化し、電圧が一定値以上になると容量が一定になるようなC-V特性を有している。容量が一定となる電圧をフラットバンド電圧という。特許文献2に開示された技術におけるキャパシタはMOSキャパシタであったので、フラットバンド電圧が正の大きな値となる。すなわち、下部電極の電位に対して上部電極の電位を高くしたとしても依然としてキャパシタの容量は電圧により変化する。一方、本実施の形態のキャパシタ60の下部電極は1つの不純物領域により形成されているので、フラットバンド電圧がマイナスの値となる。このため、下部電極8aの電位よりも上部電極15の電位を高く保つことにより、キャパシタ60の容量は電圧に関わらず一定となる。

40

#### 【0047】

本実施の形態の半導体装置100においては、キャパシタ60の上部電極15と画素電極20とが電気的に接続されている。

#### 【0048】

これにより、画素電極20に印加する電圧の低下をキャパシタ60に蓄積した電荷によって抑制することができる。

#### 【0049】

本実施の形態の半導体装置100において、第1不純物領域5b, 5cの不純物濃度は $10^{17}$ 原子/ $\text{cm}^3$ 以上 $10^{19}$ 原子/ $\text{cm}^3$ 以下である。

50

## 【0050】

これにより、n型TFT30の耐圧を向上することができる。また、第1不純物領域5b, 5cの不純物濃度は $10^{17}$ 原子/ $\text{cm}^3$ 以上とすることにより、キャパシタ60のフラットバンド電圧が正の値になる。すなわち、下部電極8aの電位よりも上部電極15の電位の方を高くすることによりキャパシタ60の容量を一定に保つことができる。

## 【0051】

本実施の形態の半導体装置100の製造方法において、ゲート電極12は、多結晶シリコン膜5上にSiO<sub>2</sub>膜11を介して導電膜71を形成し、チャネル形成領域5aと、第1不純物領域5b, 5cの各々の一部とを覆うように、レジスト70cを導電膜71上に形成し、レジスト70cをマスクとして、レジスト70cよりも線幅が細くなるように導電膜71をエッチングすることにより形成される。また、レジスト70cをマスクとして不純物を注入することにより第2不純物領域5f, 5gが第1不純物領域5b, 5c内に形成され、ゲート電極12をマスクとして不純物を注入することにより第3不純物領域5d, 5eが形成される。10

## 【0052】

これにより、簡易な方法によりゲート電極12と第2の不純物領域5f, 5gと、第3の不純物領域5d, 5eとが形成される。

## 【0053】

本実施の形態の半導体装置100の製造方法は、p型TFT40が以下の方法により形成される。導電膜71を形成すると同時に、半導体膜6上にSiO<sub>2</sub>膜11を介して導電膜71を形成する。レジスト70cを形成すると同時に、レジスト70cを第2トランジスタ形成領域の導電膜71上に形成する。導電膜71をエッチングすると同時に、レジスト70cをマスクとして、レジスト70cよりも線幅が細くなるように第2トランジスタ形成領域の導電膜71をエッチングする。第2不純物領域5f, 5gを形成すると同時に、レジスト70cをマスクとして不純物を注入することにより第4不純物領域6d, 6eを半導体層6に形成する。第3不純物領域5d, 5eを形成すると同時に、ゲート電極13をマスクとして不純物を注入することにより第5不純物領域6b, 6cを形成する。20

## 【0054】

これにより、GOLD構造とLDD構造とを有するn型TFT30を形成すると同時に、LDD構造のn型TFT40を形成することができる。30

## 【0055】

本実施の形態の半導体装置100においては、ゲート電極12を形成すると同時に、キャパシタ60の上部電極15を形成する。

## 【0056】

これにより、ゲート電極12と上部電極15とを別々の工程で形成する場合に比べて製造方法を簡略化できる。

## 【0057】

なお、本実施の形態においては、GOLD構造のTFTがn型TFT30である場合について示したが、本発明はこのような場合に限定されるものではなく、GOLD構造のTFTがpチャネル型トランジスタであってもよい。また、nチャネル型トランジスタであることが好ましい。40

## 【0058】

## (実施の形態2)

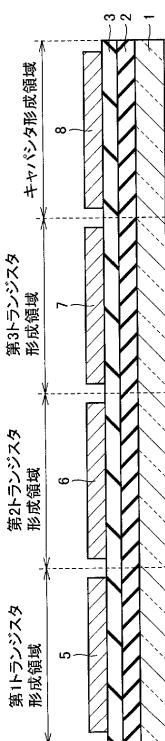

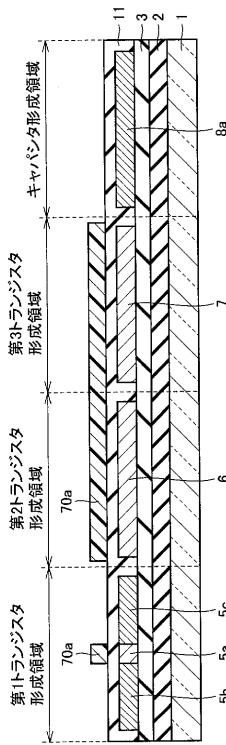

図11は、本発明の実施の形態2における半導体装置の構成を示す断面図である。

## 【0059】

図11に示すように、本実施の形態の半導体装置101においては、第1トランジスタ形成領域にGOLD構造のn型TFT31が形成され、第2トランジスタ形成領域にn型TFT41が形成されている。n型TFT31は、ソース領域31aと、ドレイン領域31bと、チャネル形成領域5aとを第1トランジスタ形成領域の下地膜3の上に有している。ソース領域31aは、GOLD領域である第1不純物領域5bと、第2不純物領域5

$f$ とを有している。ドレイン領域31bは、GOLD領域である第1不純物領域5cと、第2不純物領域5gとを有している。第1不純物領域5b, 5cの各々は、第2の不純物領域5f, 5gの各々からチャネル形成領域5aの方へ伸びるようにゲート電極12の真下に形成されている。第2の不純物領域5f, 5gの各々の不純物濃度は第1不純物領域5b, 5cの各々の不純物濃度よりも高い。チャネル形成領域5aをゲート絶縁膜となるSiO<sub>2</sub>膜11を介して覆うように、n型TFT31のゲート電極12が形成されている。

#### 【0060】

n型TFT41は、ソース領域としての第4不純物領域6dと、ドレイン領域としての第4不純物領域6eと、チャネル形成領域6aとを第2トランジスタ形成領域の下地膜3の上に有している。チャネル形成領域6aをゲート絶縁膜となるSiO<sub>2</sub>膜11を介して覆うように、n型TFT41のゲート電極13が形成されている。10

#### 【0061】

なお、これ以外の半導体装置101の構成は、図1に示す実施の形態1の半導体装置100の構成とほぼ同様であるので、同一の部材には同一の符号を付し、その説明を省略する。

#### 【0062】

続いて、本実施の形態の半導体装置の製造方法について説明する。

#### 【0063】

本実施の形態の半導体装置101の製造方法は、まず図2～図7に示す実施の形態1の製造工程とほぼ同様の製造工程を経る。次に、図8に示すようなレジスト70dをマスクとしたPの注入を行なわずにレジスト70dが除去される。その後、図9および図10に示す実施の形態1の製造工程とほぼ同様の製造工程を経て、本実施の形態の半導体装置101が完成する。20

#### 【0064】

本実施の形態のように、GOLD構造のn型TFT31とn型TFT41とキャパシタ60とを備えた半導体装置101についても、本発明を適用することによって実施の形態1と同様の効果を得ることができる。

#### 【実施例1】

#### 【0065】

以下本発明の実施例について説明する。

#### 【0066】

##### (実施例1)

本実施例においては、まず、図1に示す実施の形態1の半導体装置100を製造した。半導体装置100におけるn型TFT30のチャネル幅を10μmとし、チャネル長は5μmとした。また、第1不純物領域5b, 5cのチャネル長方向の長さを1μmとし、第3不純物領域5d, 5eのチャネル長方向の長さを0.5μmとした。また、ゲート電極12のチャネル長方向の長さを7μmとした。

#### 【0067】

なお、本実施例では第1不純物領域5b, 5cのチャネル長方向の長さを1μmとしたが、これは設計値である、実際の第1不純物領域5b, 5cのチャネル長方向の長さは、ゲート電極12をマスクするレジスト70cのアライメント精度の影響を受ける。現状のステッパーでは、第1不純物領域5b, 5cのチャネル長方向の長さを1μmで設計すると、実際にはチャネル長方向の長さが1μm ± 0.3μmの第1不純物領域5b, 5cの長さとなる。すなわち、第1不純物領域5b, 5cのチャネル長方向の長さを0.7μm確保するためには、本実施例のように第1不純物領域5b, 5cのチャネル長方向の長さを1μmで設計する必要がある。以上のように、第1不純物領域5b, 5cのチャネル長方向の長さを設計する際には、ゲート電極12をマスクするレジスト70cのアライメント精度の影響を考慮する必要がある。40

#### 【0068】

10

20

30

40

50

次に、第1不純物領域5b, 5cおよび下部電極8aの不純物濃度と、第3不純物領域5d, 5eの不純物濃度をSIMS(Secondary Ion Mass Spectrometer)によって測定した。その結果、第1不純物領域5b, 5cおよび下部電極8aの不純物濃度は $5 \times 10^{17}$ 原子/ $\text{cm}^3$ であり、第3不純物領域5d, 5eの不純物濃度は $1.5 \times 10^{18}$ 原子/ $\text{cm}^3$ であった。

#### 【0069】

続いて、GOLD構造とLDD構造とを有するn型TFT30の耐圧およびオン電流を測定した。耐圧の測定については、ゲート電極12およびソース電極19aを接地して0Vとした状態でソース/ドレイン間に電圧を印加し、ソース/ドレイン間に流れるドレン電流を測定した。そして、ドレン電流が $0.1\mu\text{A}$ となるときのソース/ドレイン間の電圧(ソース電極19aに対するドレン電極19bの電位)をn型TFT30の耐圧とした。また、比較のために、従来のLDD構造のTFTの耐圧およびオン電流も測定した。なお、従来のLDD構造のTFTのチャネル幅を $10\mu\text{m}$ とし、チャネル長は $5\mu\text{m}$ とした。また、LDD領域のチャネル長方向の長さを $0.5\mu\text{m}$ とした。本発明のn型TFT30の耐圧およびオン電流と、LDD構造のTFTの耐圧およびオン電流との測定結果を表1に示す。

#### 【0070】

【表1】

|         | 本発明のGOLD構造とLDD構造とを有するTFT | 従来のLDD構造のTFT         |

|---------|--------------------------|----------------------|

| 耐圧(V)   | 22.8                     | 12.9                 |

| オン電流(A) | $2.1 \times 10^{-4}$     | $2.2 \times 10^{-4}$ |

#### 【0071】

表1に示すように、LDD構造のTFTの耐圧が $12.9\text{V}$ であるのに対し、本発明のn型TFT30の耐圧は $22.8\text{V}$ となっている。このことから、本発明のn型TFT30の耐圧はLDD構造のTFTの耐圧よりも高いことが分かる。また、LDD構造のTFTのオン電流が $2.1 \times 10^{-4}\text{A}$ であるのに対し、本発明のn型TFT30のオン電流は $2.2 \times 10^{-4}\text{A}$ となっている。このことから、本発明のn型TFT30のオン電流はLDD構造のTFTのオン電流とほぼ同様の値となっていることが分かる。

#### 【0072】

##### (実施例2)

本実施例においては、第1不純物領域5b, 5cおよび下部電極8aの不純物濃度をそれぞれ $5 \times 10^{17}$ 原子/ $\text{cm}^3$ ,  $1 \times 10^{18}$ 原子/ $\text{cm}^3$ ,  $2 \times 10^{18}$ 原子/ $\text{cm}^3$ と変化させて図1に示す実施の形態1の半導体装置100を製造した。そして、それぞれの半導体装置100についてキャパシタ60のフラットバンド電圧を測定した。この結果を表2に示す。なお、表2のフラットバンド電圧は、下部電極8aの電位に対する上部電極15の電位で示されている。

#### 【0073】

【表2】

|              | 第1不純物領域(GOLD領域)の不純物濃度(原子/ $\text{cm}^3$ ) |                    |                    |

|--------------|-------------------------------------------|--------------------|--------------------|

|              | $5 \times 10^{17}$                        | $1 \times 10^{18}$ | $2 \times 10^{18}$ |

| フラットバンド電圧(V) | -2                                        | -5                 | -10                |

#### 【0074】

表2に示すように、不純物濃度が $5 \times 10^{17}$ 原子/ $\text{cm}^3$ である場合にはフラットバン

10

20

30

40

50

ド電圧は - 2 V となっており、不純物濃度が  $1 \times 10^{17}$  原子 /  $\text{cm}^3$  である場合にはフラットバンド電圧は - 5 V となっており、不純物濃度が  $2 \times 10^{18}$  原子 /  $\text{cm}^3$  である場合にはフラットバンド電圧は - 10 V となっている。ここで、フラットバンド電圧が - 10 V である場合には、下部電極 8 a の電位を上部電極 15 の電位よりも - 10 V 以上高くすることでキャパシタ 60 の容量が一定になる。表 2 の結果によれば、第 1 不純物領域 5 b , 5 c および下部電極 8 a の不純物濃度がいずれの場合にもフラットバンド電圧はマイナスとなっている。上述のように、フラットバンド電圧がマイナスであれば、下部電極 8 a の電位よりも上部電極 15 の電位を高く保つことによりキャパシタ 60 の容量は電圧に関わらず一定となる。したがって、本発明の半導体装置によれば、安定してキャパシタに電荷を蓄積することができ、画素電極の電圧の低下を十分に抑止できることがわかる。

10

## 【0075】

## (実施例 3)

本実施例においては、第 1 不純物領域 5 b , 5 c および下部電極 8 a の不純物濃度をそれぞれ  $5 \times 10^{16}$  原子 /  $\text{cm}^3$  、  $1 \times 10^{17}$  原子 /  $\text{cm}^3$  、  $5 \times 10^{17}$  原子 /  $\text{cm}^3$  と変化させて図 1 に示す実施の形態 1 の半導体装置 100 を製造した。そして、それぞれの半導体装置 100 の n 型 TFT 30 について、実施例 1 と同様の方法により耐圧を測定した。この結果を表 3 に示す。

20

## 【0076】

## 【表 3】

|        | 第 1 不純物領域 (GOLD 領域) の不純物濃度 (原子 / $\text{cm}^3$ ) |                    |                    |

|--------|--------------------------------------------------|--------------------|--------------------|

|        | $5 \times 10^{16}$                               | $1 \times 10^{17}$ | $5 \times 10^{17}$ |

| 耐圧 (V) | 14.2                                             | 23.5               | 22.8               |

## 【0077】

表 3 に示すように、不純物濃度が  $5 \times 10^{16}$  原子 /  $\text{cm}^3$  である場合には n 型 TFT 30 の耐圧は 14.2 V となっており、不純物濃度が  $1 \times 10^{17}$  原子 /  $\text{cm}^3$  である場合には n 型 TFT 30 の耐圧は 23.5 V となっており、不純物濃度が  $5 \times 10^{17}$  原子 /  $\text{cm}^3$  である場合には n 型 TFT 30 の耐圧は 22.8 V となっている。実施例 3 と実施例 2 との結果から、不純物濃度を  $1 \times 10^{17}$  原子 /  $\text{cm}^3$  以上とすることにより、キャパシタ 60 のフラットバンド電圧がマイナスの値となり、かつ n 型 TFT 30 の耐圧が一層向上することが分かる。

30

## 【0078】

以上に開示された実施の形態および実施例はすべての点で例示であって制限的なものではないと考慮されるべきである。本発明の範囲は、以上の実施の形態および実施例ではなく、特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての修正や変形を含むものと意図される。

## 【図面の簡単な説明】

## 【0079】

40

【図 1】本発明の実施の形態 1 における半導体装置の構成を示す断面図である。

【図 2】本発明の実施の形態 1 における半導体装置の製造方法の第 1 工程を示す断面図である。

【図 3】本発明の実施の形態 1 における半導体装置の製造方法の第 2 工程を示す断面図である。

【図 4】本発明の実施の形態 1 における半導体装置の製造方法の第 3 工程を示す断面図である。

【図 5】本発明の実施の形態 1 における半導体装置の製造方法の第 4 工程を示す断面図である。

【図 6】本発明の実施の形態 1 における半導体装置の製造方法の第 5 工程を示す断面図である。

50

ある。

【図7】本発明の実施の形態1における半導体装置の製造方法の第6工程を示す断面図である。

【図8】本発明の実施の形態1における半導体装置の製造方法の第7工程を示す断面図である。

【図9】本発明の実施の形態1における半導体装置の製造方法の第8工程を示す断面図である。

【図10】本発明の実施の形態1における半導体装置の製造方法の第9工程を示す断面図である。

【図11】本発明の実施の形態2における半導体装置の構成を示す断面図である。 10

#### 【符号の説明】

#### 【0080】

1 基板、2 SiN膜、3 下地膜、5 ~ 8 多結晶シリコン膜、5a, 6a, 7a

チャネル形成領域、5b ~ 5g, 6b ~ 6e, 8b ~ 8e 不純物領域、7b, 30a

, 31a, 40a ソース領域、7c, 30b, 31b, 40b ドレイン領域、8a

下部電極、11 SiO<sub>2</sub>膜、12 ~ 14 ゲート電極、15 上部電極、16, 21

層間絶縁膜、16a ~ 16h 孔、17a ~ 17h コンタクト、19a, 19c, 19

e ソース電極、19b, 19d, 19f ドレイン電極、19g, 19h 配線、21

a 溝、22 画素電極、30, 31, 40, 41 n型TFT、50 p型TFT、6

0 キャパシタ、70a ~ 70d レジスト、71 導電膜、100, 101 半導体装

置。 20

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【 図 1 1 】

## フロントページの続き

|                          |              |            |

|--------------------------|--------------|------------|

| (51)Int.Cl. <sup>7</sup> | F I          | テーマコード(参考) |

| H 01 L 27/06             | H 01 L 29/78 | 6 1 2 Z    |

| H 01 L 27/08             | H 01 L 27/06 | 1 0 2 A    |

| H 01 L 27/088            |              |            |

| H 01 L 29/786            |              |            |

(72)発明者 中川 直紀

東京都千代田区丸の内二丁目2番3号 三菱電機株式会社内

(72)発明者 豊田 吉彦

東京都千代田区丸の内二丁目2番3号 三菱電機株式会社内

(72)発明者 坂本 孝雄

東京都千代田区丸の内二丁目2番3号 三菱電機株式会社内

(72)発明者 須賀原 和之

東京都千代田区丸の内二丁目2番3号 三菱電機株式会社内

F ターム(参考) 2H092 JA25 JB58 JB63 MA07 MA14 MA15 MA17 MA27 MA29 MA30

MA37 NA22 NA27

5F038 AC02 AC03 AC05 AC15 AC19 DF01 EZ13 EZ14 EZ15 EZ17

EZ20

5F048 AC04 AC10 BA16 BB03 BC05 BC06 BC16 BC18 BC20 BG07

DA01

5F110 AA06 AA13 AA16 BB02 BB04 CC02 DD02 DD12 DD13 DD14

DD15 DD17 EE04 EE44 FF02 FF30 GG02 GG13 GG16 GG28

GG29 GG45 HJ01 HJ04 HJ13 HL03 HL04 HL11 HM13 HM15

NN03 NN72 NN73 NN78 PP01 PP03 PP34 PP35 QQ05 QQ08

QQ11