(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2008-70408

(P2008-70408A)

(43) 公開日 平成20年3月27日(2008.3.27)

(51) Int.Cl.

G 1 O H 1/053 (2006.01)

G 1 O H 1/18 (2006.01)

F 1

G 1 O H 1/053

G 1 O H 1/18D

1 O 1

テーマコード(参考)

5 D 3 7 8

審査請求 未請求 請求項の数 6 O L (全 17 頁)

(21) 出願番号

(22) 出願日特願2006-246322 (P2006-246322)

平成18年9月12日 (2006.9.12)(71) 出願人 000001443

カシオ計算機株式会社

東京都渋谷区本町1丁目6番2号

(74) 代理人 100099715

弁理士 吉田 聰

(72) 発明者 金子 洋二

東京都羽村市栄町3丁目2番1号 カシオ

計算機株式会社羽村技術センター内

F ターム(参考) 5D378 DD02 DE06 DE42 DE52 DE58

EE11 HB18 HB38 SF01

(54) 【発明の名称】タッチレスポンス検出装置および電子楽器

## (57) 【要約】

**【課題】** 小さい処理負荷で、適切なタッチレスポンスデータを得る

**【解決手段】** タッチ検出回路5は、鍵の第1のスイッチのオンに伴って計数を開始し、現在のカウント値に、カウントレート値を加算するベロシティカウントユニット29と、現在のカウント値を記憶するRAM24と、鍵の第2のスイッチのオンに伴って、その鍵の現在のカウント値に基づくタッチレスポンスデータを出力するインターフェースユニット22と、現在のカウント値に加算すべきカウントレート値を算出するベロシティカウントレート発生器28とを備える。RAM24は、カウント値の上位ビットに関連付けられたカウントレート値を記憶し、ベロシティカウントレート発生器28は、現在のカウント値に基づくカウントレート値を、現在のカウント値の下位ビットにより補間したカウントレート値の補間値を求める補間手段を有し、補間値が、現在のカウント値に加算される。

【選択図】 図2

**【特許請求の範囲】****【請求項 1】**

鍵盤を構成する各鍵に離間して配置された2つのスイッチのオン時間差を計測することにより、押鍵速度を示すタッチレスポンスデータを算出するタッチレスポンス検出装置であって、

前記鍵の2つのスイッチのうち第1のスイッチのオンに伴って、当該鍵に関するカウント値の計数を開始し、所定のタイミングで、現在のカウント値に、カウントレート値を加算するベロシティカウント手段と、

前記現在のカウント値を記憶する記憶手段と、

前記第2のスイッチのオンに伴って、前記鍵の現在のカウント値に基づくタッチレスポンスデータを出力するインターフェース手段と、

前記現在のカウント値に加算すべきカウントレート値を算出するカウントレート値算出手段と、を備え、

前記記憶手段が、前記カウント値の所定の上位ビットのビット値に関連付けられたカウントレート値を記憶し、

前記カウントレート値算出手段が、前記記憶手段から出力された、前記現在のカウント値に基づくカウントレート値を、前記現在のカウント値の上記上位ビットを除く所定の下位ビットのビット値により補間したカウントレート値の補間値を求める補間手段を有し、前記カウントレート値の補間値が、前記現在のカウント値に加算されることを特徴とするタッチレスpons検出装置。

10

20

30

30

40

50

**【請求項 2】**

前記補間手段が、前記上位ビットのビット値に関連付けられたカウントレート値と当該ビット値の次の値の関連付けられたカウントレート値との差分値と、前記カウント値の前記所定の下位ビットのビット値との乗算値、および、前記カウントレート値の加算値を、前記カウントレート値の補間値として算出することを特徴とする請求項1に記載のタッチレスpons検出装置。

**【請求項 3】**

前記上位ビットを除く所定の下位ビットが、前記現在のカウント値の最下位ビットを含む所定数の下位ビットを除いた、現在のカウント値の中位ビットであることを特徴とする請求項1または2に記載のタッチレスpons検出装置。

**【請求項 4】**

前記カウントレート値算出手段が、前記補間値を指数変換する指数変換テーブルを有することを特徴とする請求項1ないし3の何れか一項に記載のタッチレスpons検出装置。

**【請求項 5】**

前記インターフェース手段が、前記現在のカウント値のビットを反転することで、タッチレスponsデータを得ることを特徴とする請求項1ないし4の何れか一項に記載のタッチレスpons検出装置。

**【請求項 6】**

複数の鍵を備え、各鍵において、離間して配置された2つのスイッチを有する鍵盤と、前記鍵盤を構成する各鍵の2つのスイッチのオン時間差を計測することにより、押鍵速度を示すタッチレスponsデータを算出するタッチレスpons検出手段であって、

前記鍵の2つのスイッチのうち第1のスイッチのオンに伴って、当該鍵に関するカウント値の計数を開始し、所定のタイミングで、現在のカウント値に、カウントレート値を加算するベロシティカウント手段、

前記現在のカウント値を記憶する記憶手段、

前記第2のスイッチのオンに伴って、前記鍵の現在のカウント値に基づくタッチレスponsデータを出力するインターフェース手段、並びに、

前記現在のカウント値に加算すべきカウントレート値を算出するカウントレート値算出手段、を有し、

前記記憶手段が、前記鍵ごとに前記カウントレート値を補正するための補正データを記

憶し、かつ、前記カウントレート値算出手段が、前記カウントレート値を、前記補正データに基づいて補正することにより、補正されたカウントレート値を算出し、前記補正されたカウントレート値を、前記ベロシティカウント手段に出力することを特徴とするタッチレスポンス検出手段と、

タッチレスポンスデータおよび押鍵された鍵の音高を受信して、かつ、指定された音色で、受信した音高で、かつ、当該タッチレスポンスデータに基づくベロシティの楽音の生成を、楽音発生手段に指示する制御手段と、

前記制御手段から指示された音色、音高、および、ベロシティの楽音データを生成する楽音発生手段と、

を備えたことを特徴とする電子楽器。

10

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、鍵など演奏操作子の操作の速さを検出するためのタッチレスポンス検出装置、および、当該タッチレスポンス検出装置を備えた電子楽器に関する。

【背景技術】

【0002】

従来、電子鍵盤楽器の鍵など演奏操作子の操作の速さ、つまり、演奏操作子の押下速度を、段差のある2つのゴム接点のスイッチがオンするときの時間差を計測することにより検出することが一般的である。

20

【0003】

鍵を押下する速度に相当するタッチレスポンスデータを検出するタッチ検出装置は、鍵の第1のスイッチのオンからカウントを開始し、第2のスイッチのオンでカウントを終了し、そのカウント値に基づいてタッチレスポンスデータを検出している。なお、人間の聴感特性から、タッチレスポンスデータと上記時間差との間がほぼ指數関数になるように、タッチレスポンスデータが求められるのが望ましいとされている。

【0004】

特許文献1のタッチレスポンス検出装置においては、鍵が最初のスイッチにオンしたときから、ダウンカウントするカウンタが設けられている。このダウンカウンタをカウントダウンさせるタイミングを、段階的に変化させている。たとえば、初期的には、ダウンカウンタには、クロック発生器におけるもっとも高速なクロックによりダウンカウントするが、その後、段階的に、(1/2)、(1/3)、(1/8)、(1/10)、(1/75)のクロックによりダウンカウントし、その結果、指數関数を直線で近似したようなカウンタ出力を得られるようにしている。

30

【特許文献1】特開昭63-41900号公報(第1図、第4図)

【発明の開示】

【発明が解決しようとする課題】

【0005】

しかしながら、特許文献1に示すタッチレスポンスデータは、折れ線により指數関数を近似したものであり、実際に指數関数の値との間で誤差が生じる。したがって、従来、電子鍵盤楽器を制御するマイクロコンピュータが、誤差を修正するテーブルを参照して、タッチレスポンスデータを補正している。

40

【0006】

このように折れ線にしたがったタッチレスポンスデータを、マイクロコンピュータにて補正する手法では、発音開始時のマイクロコンピュータの処理の負荷が大きくなってしまう。特に、和音など複数の楽音を発生させる際にも、それぞれの発音を遅らせることはできないため、マイクロコンピュータの処理負荷はできるだけ小さくするのが望ましい。

【0007】

本発明は、小さい処理負荷で、適切なタッチレスポンスデータを得ることができるタッチレスポンス検出装置、および、当該タッチレスポンス検出装置を備えた電子楽器を提供

50

することを目的とする。

【課題を解決するための手段】

【0008】

本発明の目的は、鍵盤を構成する各鍵に離間して配置された2つのスイッチのオン時間差を計測することにより、押鍵速度を示すタッチレスポンスデータを算出するタッチレスポンス検出装置であって、前記鍵の2つのスイッチのうち第1のスイッチのオンに伴って、当該鍵に関するカウント値の計数を開始し、所定のタイミングで、現在のカウント値に、カウントレート値を加算するベロシティカウント手段と、前記現在のカウント値を記憶する記憶手段と、前記第2のスイッチのオンに伴って、前記鍵の現在のカウント値に基づくタッチレスポンスデータを出力するインタフェース手段と、前記現在のカウント値に加算すべきカウントレート値を算出するカウントレート値算出手段と、を備え、前記記憶手段が、前記カウント値の所定の上位ビットのビット値に関連付けられたカウントレート値を記憶し、前記カウントレート値算出手段が、前記記憶手段から出力された、前記現在のカウント値に基づくカウントレート値を、前記現在のカウント値の上記上位ビットを除く所定の下位ビットのビット値により補間したカウントレート値の補間値を求める補間手段を有し、前記カウントレート値の補間値が、前記現在のカウント値に加算されることを特徴とするタッチレスポンス検出装置により達成される。

10

【0009】

本発明によれば、タッチレスポンス検出装置において、現在のカウント値の上位ビットのビット値に関連付けられた、粗いカウントレート値を、現在のカウント値の上位ビットを除く所定の下位ビットのビット値により補間して、現在のカウント値に基づく精度の良いカウントレート値を算出する。記憶手段に記憶するカウントレート値の量をそれほど大きくすることなく、また、処理負荷をそれほど大きくすることなく、精度の良い（きめ細かい）カウントレート値を得ることができる。したがって、得られるベロシティカーブは折れ線状ではなく曲線状となる。

20

【0010】

好ましい実施態様においては、前記補間手段が、前記上位ビットのビット値に関連付けられたカウントレート値と当該ビット値の次の値の関連付けられたカウントレート値との差分値と、前記カウント値の前記所定の下位ビットのビット値との乗算値、および、前記カウントレート値の加算値を、前記カウントレート値の補間値として算出する。

30

【0011】

また、好ましい実施態様においては、前記上位ビットを除く所定の下位ビットが、前記現在のカウント値の最下位ビットを含む所定数の下位ビットを除いた、現在のカウント値の中位ビットである。つまり、所定数の上位ビットにより、粗いカウントレート値が決定され、それに引き続く所定数の中位ビットにより補間が行われる。この実施態様によれば、演算量を大きくすることなく、きめの細かいカウントレート値を得ることができる。

【0012】

別の好ましい実施態様においては、前記カウントレート値算出手段が、前記補間値を指数変換する指数変換テーブルを有する。

40

【0013】

また、別の好ましい実施態様においては、前記インタフェース手段が、前記現在のカウント値のビットを反転することで、タッチレスポンスデータを得る。

【0014】

また、本発明の目的は、複数の鍵を備え、各鍵において、離間して配置された2つのスイッチを有する鍵盤と、

前記鍵盤を構成する各鍵の2つのスイッチのオン時間差を計測することにより、押鍵速度を示すタッチレスポンスデータを算出するタッチレスポンス検出手段であって、

前記鍵の2つのスイッチのうち第1のスイッチのオンに伴って、当該鍵に関するカウント値の計数を開始し、所定のタイミングで、現在のカウント値に、カウントレート値を加算するベロシティカウント手段、前記現在のカウント値を記憶する記憶手段、

50

前記第2のスイッチのオンに伴って、前記鍵の現在のカウント値に基づくタッチレスポンスデータを出力するインターフェース手段、並びに、前記現在のカウント値に加算すべきカウントレート値を算出するカウントレート値算出手段、を有し、前記記憶手段が、前記鍵ごとに前記カウントレート値を補正するための補正データを記憶し、かつ、前記カウントレート値算出手段が、前記カウントレート値を、前記補正データに基づいて補正することにより、補正されたカウントレート値を算出し、前記補正されたカウントレート値を、前記ベロシティカウント手段に出力することを特徴とするタッチレスポンス検出手段と、

タッチレスポンスデータおよび押鍵された鍵の音高を受信して、かつ、指定された音色で、受信した音高で、かつ、当該タッチレスポンスデータに基づくベロシティの楽音の生成を、楽音発生手段に指示する制御手段と、

前記制御手段から指示された音色、音高、および、ベロシティの楽音データを生成する楽音発生手段と、

を備えたことを特徴とする電子楽器により達成される。

#### 【発明の効果】

#### 【0015】

本発明によれば、小さい処理負荷で、適切なタッチレスポンスデータを得ることができタッチレスポンス検出装置、および、当該タッチレスポンス検出装置を備えた電子楽器を提供することが可能となる。

#### 【発明を実施するための最良の形態】

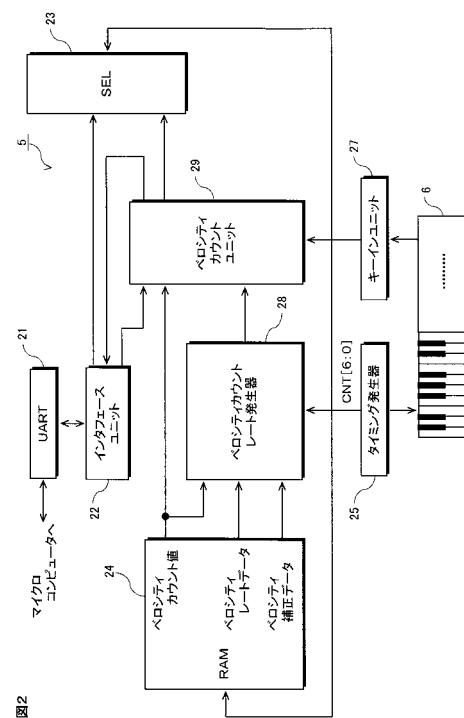

#### 【0016】

以下、添付図面を参照して、本発明の実施の形態について説明する。図1は、本発明の実施の形態にかかる電子楽器の概略を示すブロックダイヤグラムである。図1に示すように、電子楽器は、マイクロコンピュータ1、ROM(Read Only Memory)2、RAM(Random Access Memory)3、スイッチ類4、タッチ検出回路5、鍵盤6、楽音発生回路7、波形ROM8、D/A変換器(DAC)9、増幅回路10およびスピーカ11、12を備えている。マイクロコンピュータ1、ROM2、RAM3および楽音発生回路は、バス13と接続されており、タッチ検出回路5はマイクロコンピュータ1とシリアルインターフェースで接続されている。

#### 【0017】

マイクロコンピュータ1は、電子楽器全体を制御し、プログラムやデータを格納したROM2から、プログラムやデータを読み出して、プログラムを実行する。プログラムの実行にて生成されるデータなどはワークエリアであるRAM3に記憶される。スイッチ類4は、電子楽器のコンソールパネル上に配置されている。マイクロコンピュータ1は、演奏者によるスイッチ類4の操作を検出する。タッチ検出回路5は、後に詳述するように所定のタイミングで鍵盤6に対して走査信号を送出し、各鍵盤6の鍵に配置された2つのスイッチのオンに応答して、演奏操作データ(音高およびタッチレスポンスデータ)を生成して、マイクロコンピュータ1に出力する。本実施の形態において、鍵盤6は88個の鍵を有し、各鍵には、その長手方向に2つのスイッチが配置され、鍵の押下によってまず第1のスイッチがオンされ、さらに、鍵が押下されることにより第2のスイッチがオンされるようになっている。

#### 【0018】

マイクロコンピュータ1は、スイッチ類4の操作により指定された音色、および、タッチ検出回路5から出力されたタッチレスポンスデータを含む演奏操作データに基づき、楽音発生回路7を制御して、所定の楽音を発生させる。楽音発生回路7は、波形ROM8から指定された音色の波形データを読み出して、演奏操作データにしたがった音高および音量(ベロシティ)の楽音を生成してDAC9に出力する。DAC9は、楽音発生回路7から出力されたディジタルデータをアナログ信号に変換する。アナログ信号は増幅回路10を介してスピーカ11、12から放音される。

#### 【0019】

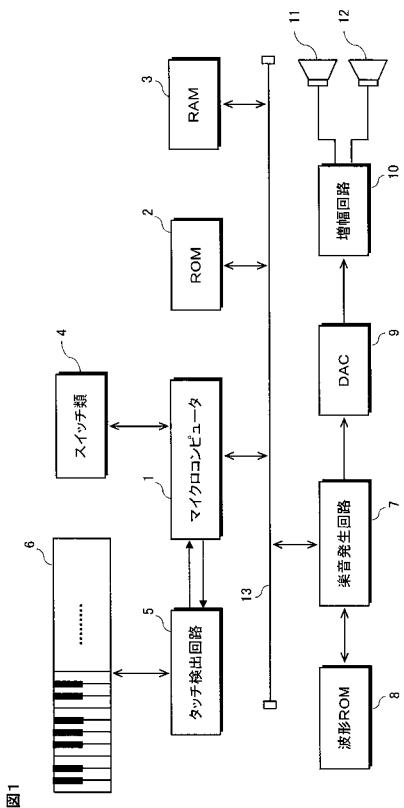

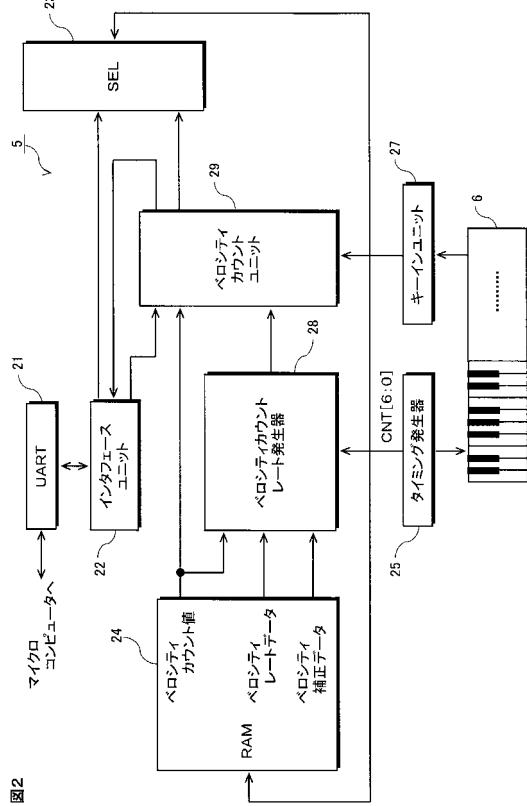

図2は、本実施の形態にかかるタッチ検出回路の構成をより詳細に示すブロックダイヤ

グラムである。図2においては、タッチ検出回路5を構成する部材のほか、図1の鍵盤6も表示している。図2に示すように、タッチ検出回路5は、U A R T (Universal Asynchronous Receiver Transmitter) 21、インターフェースユニット22、セレクタ(S E L)23、R A M 24、タイミング発生器25、キーインユニット27、ベロシティカウントレート発生器28、および、ベロシティカウントユニット29を有する。

#### 【0020】

U A R T 21は非同期のシリアルインターフェースであり、マイクロコンピュータ1との間のデータ送受信を制御する。マイクロコンピュータ1からシリアル形式で送られるデータは、パラレル形式に変換され、さらにインターフェースユニット22およびセレクタ23を介して、R A M 24の所定の領域に書き込まれる。また、タッチ検出回路5における演算により得られたタッチレスポンスデータは、インターフェースユニット22およびU A R Tを介してマイクロコンピュータ1に転送される。10

#### 【0021】

インターフェースユニット22は、U A R T 21経由で書き込まれたタッチ検出用制御データを、もう一方の入力にベロシティカウントユニット29からの出力が接続されているセレクタ23を介して、R A M 24の所定の領域に格納する。タッチ検出用制御データには、ベロシティレートデータおよびベロシティ補正データが含まれる。

#### 【0022】

セレクタ23は、上述したようにインターフェースユニット22がU A R T 経由でタッチ検出用制御データを出力する場合には、このタッチ検出用制御データを選択して、R A M 24に出力する。それ以外の場合には、ベロシティカウントユニット29からの出力(ベロシティカウント値)を選択して、これをR A M 24に出力する。20

#### 【0023】

タイミング発生器25は、鍵盤6に対して、鍵盤6のスイッチのオン／オフを検出するためのタイミング信号を出力するとともに、R A M 24のアドレスとなるC N T [ 6 : 0 ]を出力する。前述したように、本実施の形態においては、88鍵のそれぞれに2つずつスイッチが設けられ、鍵盤6には176個のスイッチが配置される。スイッチは $8 \times 22$ のマトリクスを構成している。キーインユニット27は、マトリクスを走査して、タイミング発生器25のタイミング信号にしたがって、鍵盤6の各鍵のスイッチのオン／オフを検出する。キーインユニット27は、取り込んだスイッチの状態を示す信号を時分割化して、ベロシティカウントユニット29に出力する。30

#### 【0024】

ベロシティカウントレート発生器28は、後に詳述するように、ベロシティカウント値、ベロシティレートデータおよびベロシティ補正データに基づいて、ベロシティカウントレートを算出して、ベロシティカウントユニット29に出力する。ベロシティカウントユニット29は、ベロシティカウント値と、ベロシティカウントレート発生器28から出力されたベロシティカウントレートとを加算して、新たなベロシティカウント値を算出する。新たなベロシティカウント値は、セレクタ23を介して、R A M 24の所定の領域に格納される。

#### 【0025】

本実施の形態においては、R A M 24は30ビットのデータを格納できる。アドレス0～87には、各アドレスに対応してS T [ 3 : 0 ]、V C [ 19 : 0 ]およびC O R [ 5 : 0 ]が格納される。30ビットのデータS T [ 3 : 0 ]、V C [ 19 : 0 ]およびC O R [ 5 : 0 ]は、鍵盤ごとの情報を表す。ステータスS T [ 3 : 0 ]は、その鍵のカウントのステータスを示す。たとえば、この4ビットの値により、カウント準備中、カウント中などのステータスが特定される。ベロシティカウント値V C [ 19 : 0 ]は、鍵盤6のある鍵において、第1のスイッチがオンされた後、第2のスイッチがオンされるまでの間にカウントされる値を示す。ベロシティカウント値V C [ 19 : 0 ]は、ステータスS Tが「カウント中」を示す間、所定のタイミングで、後述するように算出されるベロシティカウントレートが加算されていく。ベロシティ補正データC O R [ 5 : 0 ]は、鍵盤6の40

鍵ごとにベロシティカウント値を補正するため（より詳細には、ベロシティカウント値に加算するベロシティカウントレートを補正するため）の値である。上記データは、後述する信号 CNT [ 6 : 0 ] をアドレスとして指定される。

#### 【0026】

また、RAMのアドレス 88～105には、各アドレスに対応して VR [ 7 : 0 ] が格納されている。これらは、後述する信号 VC [ 19 : 16 ] をアドレスとして指定される。

#### 【0027】

図2に示すタッチ検出回路5において、キーインユニット27が、ある鍵の第1スイッチのオンを検出すると、その鍵に対応するアドレスのデータ中、ステータス ST [ 3 : 0 ] が、カウント中を示す値に変更され、ベロシティカウント値 VC [ 19 : 0 ] のカウントが開始される。

10

#### 【0028】

ベロシティカウントユニット29は、所定のタイミングで、ベロシティカウント値 VC [ 19 : 0 ] に、ベロシティカウントレート発生器28で算出されたベロシティカウントレートを加算する。ベロシティカウント値 VC は、セレクタ23を介して、RAM24中、鍵のアドレスに格納される。ベロシティカウント値 VC に対するベロシティカウントレートの加算は、キーインユニット27により同じ鍵の第2のスイッチのオンが検出されるまで繰り返される。

#### 【0029】

キーインユニット27が、上記鍵の第2のスイッチのオンを検出すると、その時点での当該鍵のベロシティカウント値 VC が、インタフェースユニット22に与えられ、かつ、インタフェースユニット22において、ベロシティカウント値の各ビット値が反転される。この反転された値が、鍵の押下速度を示すタッチレスポンスデータとなる。タッチレスポンスデータは、鍵の情報（たとえば、音高情報）とともに、UART21を介して、マイクロコンピュータ1に対して出力される。マイクロコンピュータ1は、音高情報およびタッチレスポンスデータに基づいて、ある音高をある強度（或いは速度）でキーオンしたときの演奏操作データを生成して、これを楽音発生回路7に出力する。

20

#### 【0030】

また、キーインユニット27が、鍵のスイッチのオフを検出すると、ベロシティカウントユニット29からインタフェース22に対して、鍵の情報（音高情報）とキーオフを示す情報が与えられる。与えられた情報は、UART21を介して、マイクロコンピュータ1に対して出力される。マイクロコンピュータ1は、キーオフを示す情報の受信に応答して、キーオフを示す演奏操作データを生成して、これを楽音発生回路7に出力する。

30

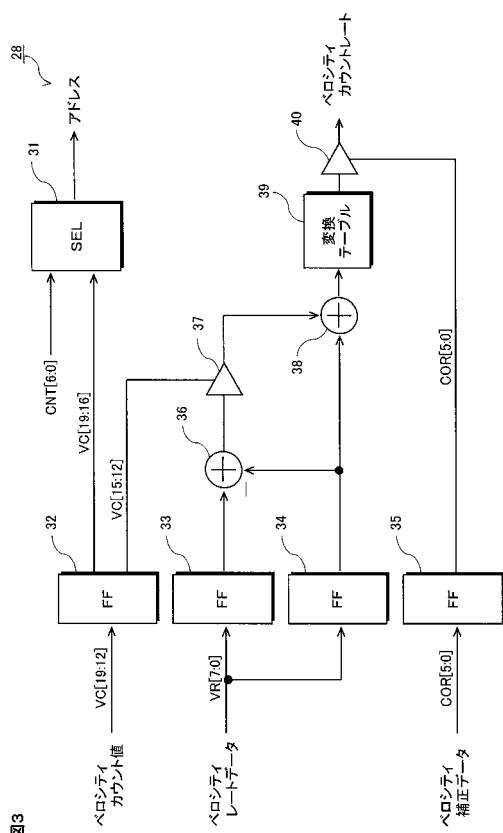

#### 【0031】

図3は、本実施の形態にかかるベロシティカウントレート発生器の構成を詳細に示すブロックダイヤグラムである。図3に示すように、ベロシティカウントレート発生器28は、セレクタ（SEL）31と、FF32～35と、減算器36と、乗算器37、40と、加算器38と、変換テーブル39とを有する。

#### 【0032】

FF33は、ベロシティカウント値 VC のうちの上位ビット VC [ 19 : 12 ] を保持する。セレクタ31の一方の入力には、タイミング発生器25からの CNT [ 6 : 0 ] が与えられ、他方の入力には、VCのうちのさらに上位の所定ビット VC [ 19 : 16 ] が与えられ、タイミングにより何れか一方を出力するようになっている。セレクタ31の出力は、RAM24のアドレスとなる。

40

#### 【0033】

FF34には、RAM24においてアドレス VC [ 19 : 16 ] で指定して読み出されたベロシティレートデータ VR が格納される（以下、このデータを、VR（VC [ 19 : 16 ] ）と記す。）。FF33には、アドレス（VC [ 19 : 16 ] + 1）で指定して読み出されたベロシティデータが格納される（以下、このデータを、VR（VC [ 19 : 1

$2] + 1$ )と記す。)。また、FF35には、ベロシティ補正データCOR[5:0]が格納される。

#### 【0034】

前述したように、FF32からの出力のうち、上位のビットVC[19:12]のうち上位側VC[19:16]はセレクタ31に出力され、その一方、下位側VC[15:12]は乗算器37に出力される。

#### 【0035】

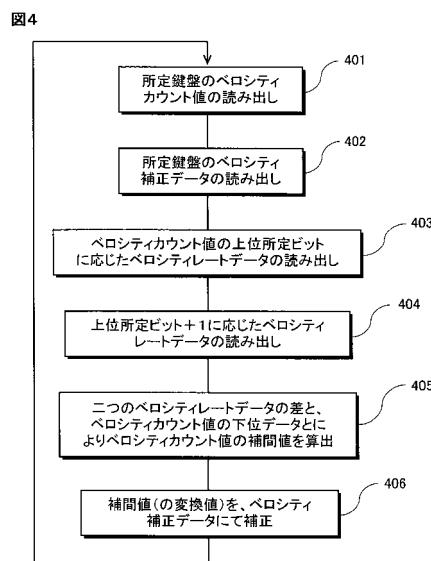

以下、図3に示すベロシティカウントレート発生器28における動作について説明する。図4は、本実施の形態にかかるベロシティカウントレート発生器の動作を示すフローチャートである。ベロシティカウントレート発生器28は、タイミング発生器25の出力CNT[6:0]の値で特定される鍵について、RAM24からアドレスCNT[6:0]のデータを読み出す。RAM24から読み出されたデータのうち、ベロシティカウント値の上位ビットVC[19:12]は、FF32に格納される(ステップ401)。また、RAM24から読み出されたデータのうち、ベロシティ補正データCOR[5:0]は、FF35に格納される(ステップ402)。

10

#### 【0036】

次いで、FF32に格納されたベロシティカウント値の上位データVC[19:12]のうちさらに上位のデータVC[19:12]をアドレスとして、RAM24からベロシティレートデータVR(VC[19:16])が読み出され、FF34に格納される(ステップ403)。また、(VC[19:12]+1)をアドレスとして、RAM24からベロシティレートデータVR(VC[19:12]+1)が読み出され、FF33に格納される(ステップ404)。

20

#### 【0037】

FF33の出力VR(VC[19:12]+1)およびFF34の出力VR(VC[19:16])は減算器36に印加され、差分値Diff[7:0]=VR(VC[19:12]+1)-VR(VC[19:16])が算出される。さらに、差分値Diffは、VC[19:12]の下位側のデータVC[15:12]と乗算器37により乗算され、さらに、加算器38によりVR(VC[19:16])と加算される。これにより、補間値Int=VR(VC[19:16])+VC[15:12]×Diffが得られる(ステップ405)。

30

#### 【0038】

本実施の形態において、減算器36、乗算器37、加算器38は、VR(VC[19:12]+1)とVR(VC[19:16])との差であるDiffを、VC[15:12]で直線補完するための演算系を構成する。DiffとVC[15:12]との積を、VR(VC[19:16])に加えることにより、アドレスVC[19:16]による比較的粗い値であるVR[7:0]を、アドレス下位の値VC[15:12]で補間した補間値Intを得ることができる。

#### 【0039】

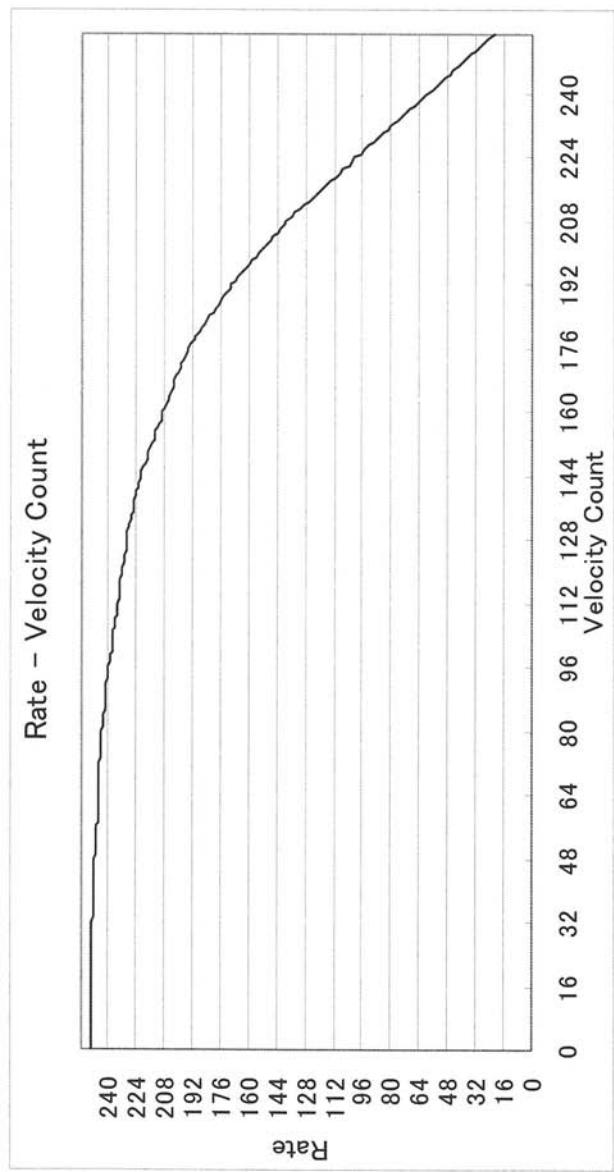

図5(a)は、本実施の形態にかかるベロシティレートデータを説明する図である。図5(a)において、左側はベロシティカウント値の上位データVC[19:12]に相当する。このように、ベロシティカウント値の所定の上位ビット(最上位4ビット)ごとに、これをアドレスとしてRAM24からベロシティレートデータVR[7:0]が読み出される。上述した補間ににより図6に示すような補間値を得ることができる。図6のグラフにおいて、縦軸がベロシティレート値の補間値に相当し、横軸がベロシティカウント値の上位データVC[19:12]に相当する。

40

#### 【0040】

さらに、補間値Intは、変換テーブル39に出力され、変換テーブル39から変換値が出力される。図5(b)は、本実施の形態にかかる変換テーブルの構成例を示す図である。図5(b)に示すように、変換テーブル39は、補間値Int、VR[7:0]と示されている。)を入力として、変換データに示すような値を出力する。図5(b)から理

50

解できるように、変換テーブル39は、直線補間された補間値を、指数変換する。

【0041】

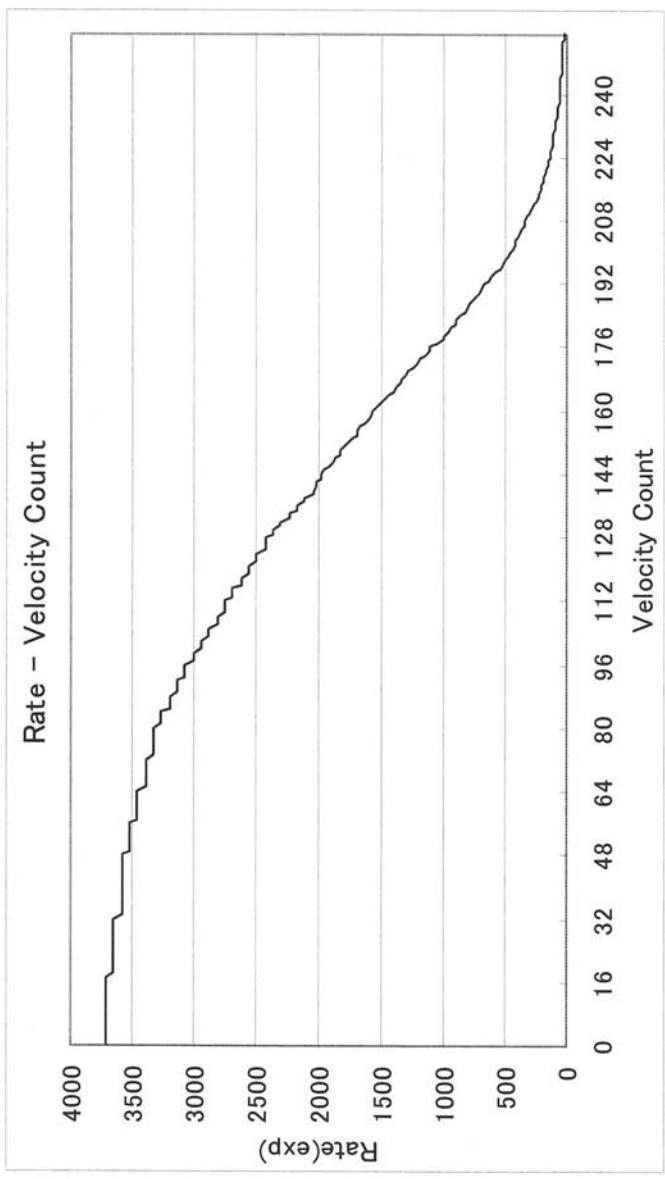

図7は、変換テーブル39を経た補間値を説明するためのグラフである。図7において、縦軸が、指数変換されたベロシティレート値の補間値に相当し、横軸がベロシティカウント値に相当する。

【0042】

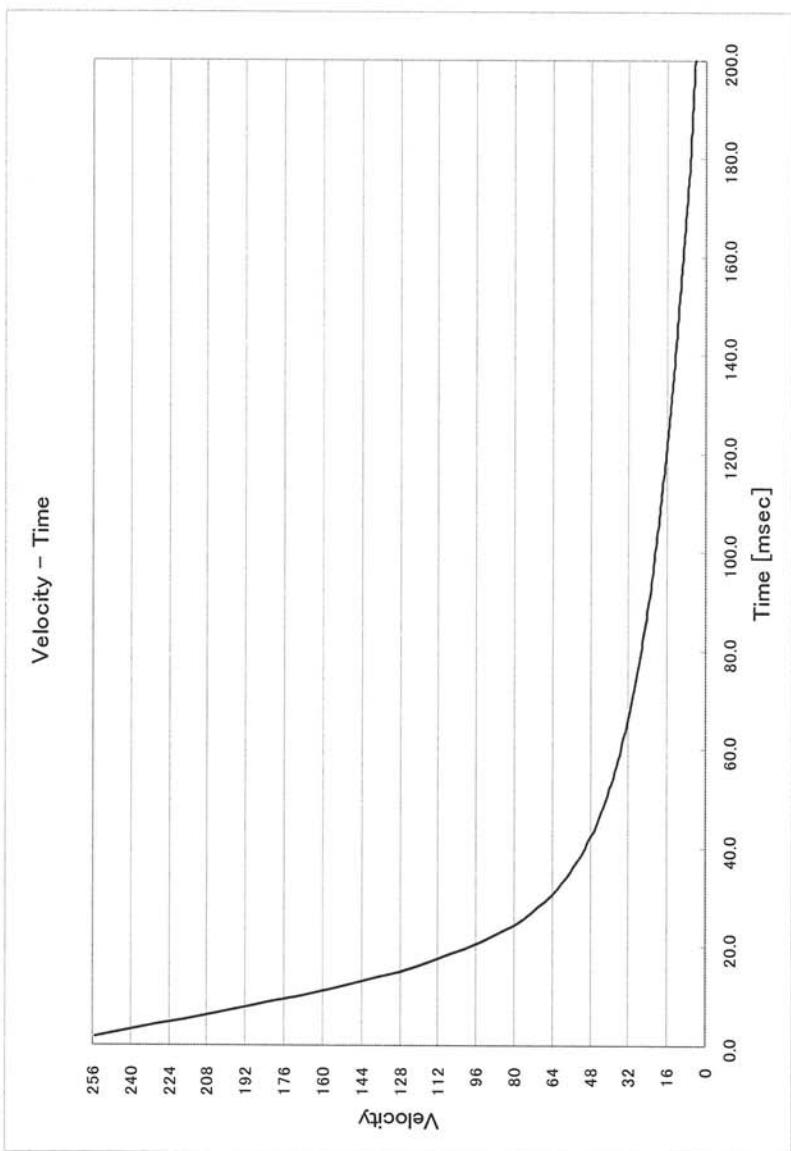

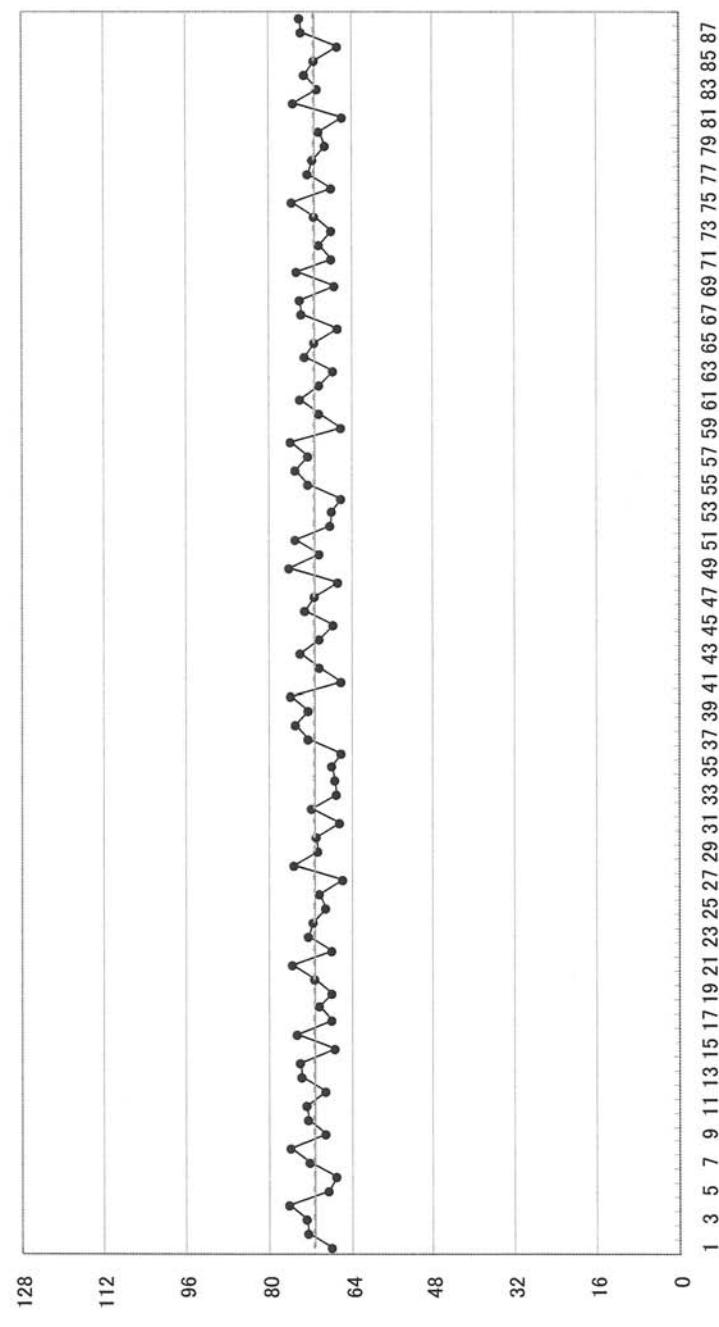

このように指数変換された補間値は、後述するベロシティ補正データによる補正を経て、ベロシティカウントレートとして、ベロシティカウントユニット29において、ベロシティカウント値と加算される。このように、指数変換された補間値をカウントすることにより、図8のグラフに示すようなベロシティカウントカーブを得ることができる。このベロシティカーブにおいて、縦軸はベロシティデータ（つまりベロシティカウント値の反転値）、横軸は時間である。

10

【0043】

このように、本実施の形態においては、折れ線のベロシティレートを補間し、かつ、これを指数変換してレンジを拡張したものをカウント（積分）する。したがって、得られるベロシティカーブ（図8）は曲線状となる。

【0044】

本実施の形態によれば、ベロシティカウント値の上位ビットVC[19:16]に関連付けられたベロシティレートデータVR[7:0]を、ベロシティカウント値の上記上位ビットに引き続く所定の中位ビットVC[15:12]で補間して補間されたベロシティレートデータを算出する。またh、補間されたベロシティレートデータを指数変換し、指数変換した補間値を、ベロシティカウント値に加算する。したがって、上述したように、ベロシティカーブを曲線状にすることが可能となる。

20

【0045】

次に、本実施の形態にかかる補正について説明する。変換テーブル39の出力である指数変換された補間値は、乗算器40の一方の入力に与えられる。乗算器40の他方の入力には、FF35からのベロシティ補正データCOR[5:0]が与えられる。ここで、補正範囲を制限することによって補正データのビット長を削減しているため、補正データCOR[5:0]は上位に11（2進数）を付加され、11000000~11111111（2進数）の範囲の8ビットデータとして乗算器40に与えられる。したがって、乗算器40において、変換値とベロシティ補正データとが乗算されて出力される。この出力が、ベロシティカウントレートとして、ベロシティカウントユニット29において、ベロシティカウント値VC[19:0]と加算される。

30

【0046】

なお、変換後の補正值11100000（2進数）を補正ゼロとすると、

$$11000000 \text{ (2進数)} = 192 \text{ (10進数)}$$

$$11100000 \text{ (2進数)} = 224 \text{ (10進数)} : \text{補正ゼロ}$$

$$11111111 \text{ (2進数)} = 255 \text{ (10進数)}$$

であるから、補正範囲としては

$$(192 - 224) / 224 = -14.286\%$$

40

から

$$(255 - 224) / 224 = 13.839\%$$

となる。

【0047】

本実施の形態においては、鍵毎に、スイッチの接点間のばらつきを補正するための補正データを、ベロシティ補正データとしてRAM24に格納している。鍵に配置された2つのスイッチの物理的な配置位置のずれや、スイッチ自体の特性から、同じ強さで鍵をオンした場合であっても、第1スイッチのオンから第2スイッチのオンにいたるまでの時間が鍵によって異なる場合がある。本実施の形態においては、これをスイッチ接点間の誤差という。そこで、本実施の形態においては、別途、鍵盤のスイッチ接点間の誤差を測定し、

50

その誤差に基づく鍵ごとのベロシティ補正データCORを、マイクロコンピュータ1から、UART21、インターフェースユニット22およびセレクタ23を介して、RAM24に格納している。

#### 【0048】

図9は、本実施の形態にかかるベロシティ補正データを説明するためのグラフである。図9において、横軸は鍵を示す。また、縦軸は、測定された鍵ごとのスイッチ接点間の誤差を示す。この例では、測定装置(図示せず)において、ベロシティデータを0~127とした場合に、ベロシティデータが「72」に相当するように押鍵し、実際に、第1スイッチのオンから第2スイッチのオンに至るまでの時間差に基づいて、本実施の形態にかかるタッチ検出回路5から、ベロシティ補正データによる補正なしで出力されたベロシティデータを取得している。実際に測定され、出力されたベロシティデータは、図9に示すように、鍵により若干のばらつきがある。そこで、本実施の形態においては、鍵ごとに誤差をキャンセルするための値を算出して、この値を、その鍵についてのベロシティ補正データとして、RAM24に格納している。このベロシティ補正データのRAM24への格納は、マイクロコンピュータ1から、UART21、インターフェースユニット22、セレクタ23を介して、RAM24に鍵ごとのベロシティ補正データを与え、RAM24に書き込むことにより実現される。

10

#### 【0049】

図9の例では、ベロシティ補正データは、誤差をキャンセルするための比の値である( $100 + A$ ) / 100とすれば良い。ここで、Aは、符号付きの誤差の割合(パーセント)、つまり、(実測値 - 理論値) / 理論値である。たとえば、上記例で、ある鍵について、実際に測定されたベロシティデータが「66」であれば、ベロシティ補正データは、 $(100 + (66 - 72)) / 72 / 100$ となる。

20

#### 【0050】

ベロシティカウント値は、基本的には、2接点間距離をカウントレートで除したものである。つまり、以下のように書くことができる。

#### 【0051】

ベロシティカウント値 = 2接点間距離 / カウントレート

そこで、誤差がA%であれば、

ベロシティカウント値 = (2接点間距離 × (100 + A)) / 100 /

30

(カウントレート × ベロシティ補正值)

ベロシティ補正值 = (100 + A) / 100

上記ベロシティ補正データを、カウントレートに乗じて補正值を得ることによって、接点間のばらつきをキャンセルすることが可能となる。

#### 【0052】

本実施の形態によれば、鍵ごとに、スイッチ接点間のばらつき(誤差)をキャンセルするベロシティ補正データをRAM24に格納し、ベロシティ補正データを、カウントレート(本実施の形態では、指數変換されたベロシティレートデータ)と乗算することで、ベロシティカウント値に加算すべき、最終的な補正されたベロシティカウントレートを得ている。これにより、鍵ごとのスイッチ接点間のばらつきをキャンセルすることができ、鍵ごとの誤差のないタッチレスポンスデータを得ることが可能となる。

40

#### 【0053】

本発明は、以上の実施の形態に限定されることなく、特許請求の範囲に記載された発明の範囲内で、種々の変更が可能であり、それらも本発明の範囲内に包含されるものであることは言うまでもない。

#### 【図面の簡単な説明】

#### 【0054】

【図1】図1は、本発明の実施の形態にかかる電子楽器の概略を示すブロックダイヤグラムである。

【図2】図2は、本実施の形態にかかるタッチ検出回路の構成をより詳細に示すブロック

50

ダイヤグラムである。

【図3】図3は、本実施の形態にかかるベロシティカウントレート発生器の構成を詳細に示すブロックダイヤグラムである。

【図4】図4は、本実施の形態にかかるベロシティカウントレート発生器の動作を示すフローチャートである。

【図5】図5(a)は、本実施の形態にかかるベロシティレートデータを説明する図、図5(b)は、本実施の形態にかかる変換テーブルの構成例を示す図である。

【図6】図6は、本実施の形態にかかる補間値の例を示すグラフである。

【図7】図7は、本実施の形態にかかる変換テーブルを経た補間値を説明するためのグラフである。

【図8】図8は、本実施の形態にかかるベロシティカーブを説明するためのグラフである。

【図9】図9は、本実施の形態にかかるベロシティ補正データを説明するためのグラフである。

【符号の説明】

【0055】

- |       |                 |

|-------|-----------------|

| 1     | マイクロコンピュータ      |

| 2     | R O M           |

| 3     | R A M           |

| 4     | スイッチ類           |

| 5     | タッチ検出回路         |

| 6     | 鍵盤              |

| 7     | 楽音発生回路          |

| 8     | 波形 R O M        |

| 9     | D A C           |

| 10    | 増幅回路            |

| 11、12 | スピーカ            |

| 21    | U A R T         |

| 22    | インターフェースユニット    |

| 23    | セレクタ            |

| 24    | R A M           |

| 25    | タイミング発生器        |

| 27    | キーインユニット        |

| 28    | ベロシティカウントレート発生器 |

| 29    | ベロシティカウントユニット   |

10

20

30

【図1】

図1

【図2】

図2

【図3】

図3

【図4】

図4

【 义 5 】

【図6】

図6

【図7】

【図8】

図8

【図9】

図9