(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6759784号

(P6759784)

(45) 発行日 令和2年9月23日(2020.9.23)

(24) 登録日 令和2年9月7日(2020.9.7)

(51) Int.Cl.

F 1

H01L 25/07 (2006.01)

H01L 25/04

C

H01L 25/18 (2006.01)

H01L 23/36

C

H01L 23/36 (2006.01)

請求項の数 3 (全 8 頁)

(21) 出願番号

特願2016-137730 (P2016-137730)

(22) 出願日

平成28年7月12日(2016.7.12)

(65) 公開番号

特開2018-10929 (P2018-10929A)

(43) 公開日

平成30年1月18日(2018.1.18)

審査請求日

平成30年11月19日(2018.11.19)

前置審査

(73) 特許権者 000006013

三菱電機株式会社

東京都千代田区丸の内二丁目7番3号

(74) 代理人 100082175

弁理士 高田 守

(74) 代理人 100106150

弁理士 高橋 英樹

(74) 代理人 100148057

弁理士 久野 淑己

(72) 発明者 村上 晴彦

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

(72) 発明者 米山 玲

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

最終頁に続く

(54) 【発明の名称】半導体モジュール

## (57) 【特許請求の範囲】

## 【請求項 1】

絶縁層と、前記絶縁層の上面に形成された第1金属パターンと、前記絶縁層の下面に形成された第2金属パターンとを有する絶縁基板と、

前記第1金属パターンに第1金属接合材で固定され、SiCによって形成された半導体チップと、

前記第2金属パターンに第2金属接合材で固定された放熱板と、を備え、

前記半導体チップの厚みは0.25mm以上0.35mm以下であり、

前記絶縁層の厚みは前記半導体チップの厚みに対し2.66倍以上5倍以下であり、

前記第2金属接合材は、前記半導体チップの直下にある直下部分と、前記直下部分につながり前記半導体チップの直下にない非直下部分とを有し、

前記第1金属接合材に導入されたクラックは、前記非直下部分に導入されたクラックより小規模であることを特徴とする半導体モジュール。

## 【請求項 2】

前記絶縁層の材料は、AlN、Al<sub>2</sub>O<sub>3</sub>又はSiNであることを特徴とする請求項1に記載の半導体モジュール。

## 【請求項 3】

前記絶縁基板と、前記半導体チップを収容し、前記放熱板に固定されたケースと、

前記半導体チップを駆動させる駆動回路と、前記半導体チップの保護回路とを集積した制御ICと、を備え、

10

20

前記制御 I C は前記ケースの中に収容されたことを特徴とする請求項 1 又は 2 に記載の半導体モジュール。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、例えば大電流のスイッチングなどに用いられる半導体モジュール、及びその半導体モジュールを用いた電力変換装置に関する。

【背景技術】

【0002】

特許文献 1 には、セラミック板と、セラミック板の上面と下面に形成された電極とを有する絶縁基板が開示されている。そして、一方の電極には金属接合材でベース板が固定され、他方の電極には金属接合材で半導体素子が固定されている。 10

【先行技術文献】

【特許文献】

【0003】

【特許文献 1】特開 2014-130875 号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

電力制御用の半導体モジュールは、IGBT、MOSFET 及び FWDi 等の半導体チップを搭載している。このような半導体モジュールはパワーモジュールと呼ばれている。パワーモジュールは、放熱板にはんだ接合された絶縁基板と、絶縁基板の金属パターンにはんだ接合された半導体チップを備える。 20

【0005】

パワーモジュールの応用製品であるインバータ機器には低損失化と小型化が求められているため、半導体モジュールにも低損失化と小型化が求められている。低損失化は、搭載する半導体チップを薄くしたり、半導体チップ構造を最適化したりすることにより実現される。小型化はパッケージ構造の最適化により実現される。しかしながら、半導体モジュールを小型化すると、半導体モジュール内で半導体チップが密集し、放熱面積も小さくなるので、放熱性の悪化が懸念される。この放熱性の悪化を回避するために絶縁基板の絶縁層を薄くすることが考えられる。 30

【0006】

このように、半導体モジュールの低損失化のために半導体チップを薄くし、放熱性改善のために絶縁基板の絶縁層を薄くする、というのが最近の傾向である。

【0007】

半導体チップと絶縁基板を接合する第 1 はんだと、絶縁基板と放熱板を接合する第 2 はんだは、半導体モジュール使用時に半導体チップの接合温度とケース温度に大きな温度変化が生じる動作パターンにおいて、半導体チップ、絶縁基板、及び放熱板の線膨張係数差によって熱疲労を起こす。熱疲労により第 1 はんだと第 2 はんだにクラックが生じると、半導体チップの放熱性が悪化し信頼性の寿命が低下する問題があった。 40

【0008】

特に SiC のような Si と比較して固い物性値を持つ材料で半導体チップを形成すると、温度変化時に第 1 はんだに大きな応力歪が生じる。絶縁層を薄くすると第 1 はんだにさらに大きな応力歪がかかり、半導体モジュールの寿命を短くする問題があった。

【0009】

半導体チップの厚みを薄くすることによって第 1 はんだにかかる応力歪を低減することが考えられる。しかし、SiC は Si に比べて固い材質であるため、ウエハを薄くするために用いる研磨治具の摩耗が激しく量産効率が悪化する。

【0010】

本発明は、上述のような課題を解決するためになされたもので、半導体チップの放熱性 50

を高く保つことができる半導体モジュールと電力変換装置を提供することを目的とする。

【課題を解決するための手段】

【0011】

本願の発明に係る半導体モジュールは、絶縁層と、該絶縁層の上面に形成された第1金属パターンと、該絶縁層の下面に形成された第2金属パターンとを有する絶縁基板と、該第1金属パターンに第1金属接合材で固定され、SiCによって形成された半導体チップと、該第2金属パターンに第2金属接合材で固定された放熱板と、を備え、該半導体チップの厚みは0.25mm以上0.35mm以下であり、該絶縁層の厚みは該半導体チップの厚みに対し2.66倍以上5倍以下であり、該第2金属接合材は、該半導体チップの直下にある直下部分と、該直下部分につながり該半導体チップの直下にない非直下部分とを有し、該第1金属接合材に導入されたクラックは、該非直下部分に導入されたクラックより小規模であることを特徴とする。

10

【発明の効果】

【0012】

本発明によれば、半導体チップの直下に形成される第1金属接合材のクラックを抑制し、SiC半導体チップを用いたときに大きく形成される基板である絶縁基板の下の第2金属接合材のクラックを許容することで、半導体チップの放熱性を高く保つことができる。

【図面の簡単な説明】

【0013】

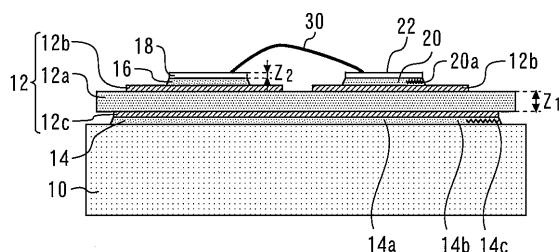

【図1】実施の形態1に係る半導体モジュールの断面図である。

20

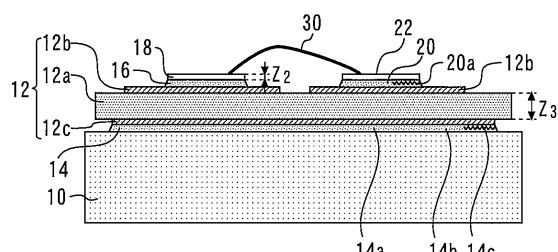

【図2】半導体モジュールの断面図と平面図である。

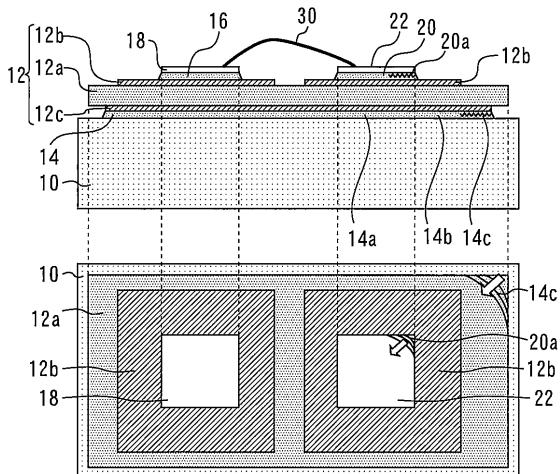

【図3】実施の形態2に係る半導体モジュールの断面図である。

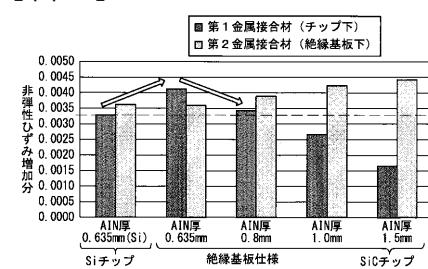

【図4】絶縁層の厚みと、第1金属接合材及び第2金属接合材に及ぶひずみとの関係を示す図である。

【図5】実施の形態3に係る半導体モジュールの断面図である。

【図6】実施の形態4に係る電力変換装置を示す図である。

【発明を実施するための形態】

【0014】

本発明の実施の形態に係る半導体モジュールと電力変換装置について図面を参照して説明する。同じ又は対応する構成要素には同じ符号を付し、説明の繰り返しを省略する場合がある。

30

【0015】

実施の形態1.

図1は、実施の形態1に係る半導体モジュールの断面図である。この半導体モジュールは絶縁基板12を備えている。絶縁基板12は、絶縁層12aと、絶縁層12aの上面に形成された第1金属パターン12bと、絶縁層12aの下面に形成された第2金属パターン12cとを有している。絶縁層12aの材料は例えばAlN、Al<sub>2</sub>O<sub>3</sub>又はSiNである。

【0016】

第1金属パターン12bには第1金属接合材16、20で半導体チップ18、22が固定されている。半導体チップ18、22はSiCによって形成されている。半導体チップ18は例えばIGBT(Insulated Gate Bipolar Transistor)であり、半導体チップ22は例えば還流ダイオードである。SiCによって形成された半導体チップ又はウエハの厚みは0.25mm～0.35mmとすることが一般的である。例えば、特開2014-82361号公報の明細書段落0005にはn型SiCウエハの厚さが350μmであることが開示されている。本発明の実施の形態1に係る半導体モジュールの半導体チップ18、22の厚みZ2は0.25mm以上0.35mm以下とした。

40

【0017】

第2金属パターン12cには第2金属接合材14によって放熱板10が固定されている。放熱板10は例えば金属などの放熱性の高い材料で形成する。第1金属接合材16、2

50

0と第2金属接合材14は例えばはんだである。第2金属接合材14は、半導体チップ18、22の直下にある直下部分14aと、直下部分14aにつながり半導体チップ18、22の直下にない非直下部分14bとを有している。第2金属接合材14が形成される面積は、第1金属接合材16、20が形成される面積より大きい。

【0018】

ところで、絶縁層12aと半導体チップ18、22の物性値及び線膨張係数の関係から、絶縁層12aの厚みを厚くすると、半導体チップ18、22下の第1金属接合材16、20の歪みが低減され、絶縁基板12下の第2金属接合材14の歪みが増加する。このような関係は、絶縁層12aを窒化アルミで形成し、半導体チップ18、22をSiCで形成した場合だけでなく、一般的に成立する関係である。

10

【0019】

熱サイクルによって半導体モジュールの各部が膨張と収縮を繰り返すと、第1金属接合材16、20の端部にクラックが形成され、第2金属接合材14の端部にクラックが形成される。図1には第1金属接合材20に形成されたクラック20aと、第2金属接合材14に形成されたクラック14cが示されている。

【0020】

図2には、半導体モジュールの断面図と平面図が示されている。図2において、第2金属接合材14に形成されたクラック14cと、第1金属接合材20に形成されたクラック20aを説明の便宜のために表示する。第1金属接合材20のクラック20aは半導体チップ22の放熱性の悪化に直結する。他方、第2金属接合材14のクラック14cについては、非直下部分14bに形成されたものであるから、半導体チップ22の放熱性への影響は小さい。

20

【0021】

そして、クラック20a、14cの規模は、上述のとおり絶縁層12aの厚さで調整できる。本発明の実施の形態1では、絶縁層12aの厚みZ1は半導体チップ18、22の厚みZ2に対し2.66倍以上5倍以下とした。すなわち、絶縁層12aを厚くして、半導体チップ18、22下の第1金属接合材16、20のクラックを低減し、絶縁基板12下の第2金属接合材14のクラックが増加するようにした。

【0022】

つまり、半導体チップ18、20の放熱性を大きく悪化させる第1金属接合材16、20のクラックを抑制しつつ、半導体チップ18、20の放熱性への寄与が小さい第2金属接合材14の非直下部分14bにクラックを生成させる。これにより、半導体チップの放熱性を高く保つことができる。半導体チップ18、20の材料をSiCのような固い材料とした場合には第1金属接合材16、20に特にクラックが生じやすいが、上記のようにクラックの発生しやすさを調整することで、第1金属接合材16、20の熱疲労に起因するクラックを抑制又は小規模にとどめることができる。

30

【0023】

このように、本発明の実施の形態1に係る半導体モジュールでは、第1金属接合材16、20に導入されたクラックは、第2金属接合材14に導入されたクラックより小規模となる。第2金属接合材14には相対的に大規模なクラックが導入されるが、平面視で半導体チップ18、20を絶縁基板12の中央に配置することで、直下部分14aへのクラックを防止しつつ非直下部分14bにクラックを形成できるから、半導体チップ18、22の放熱性を大きく損ねることはない。

40

【0024】

半導体チップ18、20をSiCで形成した場合には大電流を扱うことができるので絶縁基板12を大きくする。その場合、第2金属接合材14の非直下部分14bの面積が大きくなるので、クラックが非直下部分14bから直下部分14aに進展する可能性を低くすることができる。

【0025】

本発明の実施の形態1に係る半導体モジュールはその特徴を失わない範囲で様々な変形

50

が可能である。例えば、絶縁基板 12 に固定する半導体チップの数は任意である。以下の実施の形態に係る半導体モジュールと電力変換装置についても同様である。なお、以下の実施の形態に係る半導体モジュールと電力変換装置については、実施の形態 1 との類似点が多いので、実施の形態 1 との相違点を中心に説明する。

【 0 0 2 6 】

実施の形態 2 .

図 3 は、実施の形態 2 に係る半導体モジュールの断面図である。半導体チップの厚さ  $Z_2$  は 0.25 mm 以上 0.35 mm 以下である。絶縁層 12a の厚み  $Z_3$  は 0.8 mm 以上である。図 4 は、AIN で形成した絶縁層 12a の厚みと、第 1 金属接合材 16、20 及び第 2 金属接合材 14 に及ぶひずみとの関係を示す図である。図 4 の A には、参考までに、半導体チップが Si で形成され、絶縁層 AIN を 0.653 mm としたときの、第 1 金属接合材 16、20 と第 2 金属接合材 14 の非弾性ひずみ増加分が示されている。

【 0 0 2 7 】

この場合、絶縁基板 12 の下にある第 2 金属接合材 14 に、第 1 金属接合材 16、20 よりも大きいひずみが及ぶ。しかしながら、図 4 の B に示すように、半導体チップの材料を SiC に変更すると、AIN で形成された絶縁層 12a の厚さは 0.653 mm のままでしても、半導体チップの下の第 1 金属接合材 16、20 に大きなひずみが及ぶようになる。これは SiC が Si より硬い材料であることが原因である。このように、半導体チップを SiC で形成する場合には、第 1 金属接合材 16、20 に大きなひずみが及びやすい。

【 0 0 2 8 】

しかし、図 4 の C、D、E に示すとおり、絶縁層 12a の厚さを 0.8 mm、1.0 mm、1.5 mm と増加させていくと、第 1 金属接合材 16、20 に及ぶひずみが減少し、第 2 金属接合材 14 に及ぼされるひずみが増加する。本発明の実施の形態 2 では、絶縁層 12a の厚み  $Z_3$  は 0.8 mm 以上としたので、第 1 金属接合材 16、20 におけるひずみは、常に第 2 金属接合材 14 に及ぶひずみより小さい。具体的には、第 1 金属接合材 16、20 のひずみは、図 4 の A に示す絶縁層が Si の場合と同等以下にすることができる。よって、半導体チップの放熱性を高く保つことができる。

【 0 0 2 9 】

実施の形態 3 .

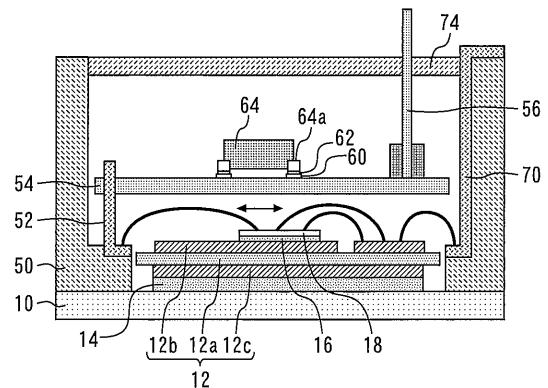

図 5 は、実施の形態 3 に係る半導体モジュールの断面図である。絶縁基板 12 と半導体チップ 18 はケース 50 に収容されている。ケース 50 は、放熱板 10 に固定されている。ケース 50 には端子 52 が固定されている。この端子 52 にはプリント基板 54 が固定されている。プリント基板 54 はケース 50 の中の絶縁基板 12 の直上にある。プリント基板 54 には導電性の材料でランド 60 が形成されている。このランド 60 には、制御 IC 64 の端子 64a がはんだ 62 で固定されている。制御 IC 64 は、半導体チップ 18 を駆動させる駆動回路と、半導体チップ 18 の保護回路とを集積した IC である。制御 IC 64 はケース 50 の中に収容されている。

【 0 0 3 0 】

プリント基板 54 にはケース 50 の外に伸びる端子 56 が接続されている。端子 56 は信号端子として機能する。ケース 50 には、ケース 50 の外部に伸びる主端子 70 が固定されている。ケース 50 にはふた 74 が取り付けられている。このように、ケース 50 の中に半導体チップ 18 の駆動回路と保護回路を集積した制御 IC 64 を内蔵した半導体モジュールをインテリジェントパワーモジュール (IPM) と呼ぶ。IPM の場合、半導体モジュールより小型化が求められる。パッケージの小型化に伴ってチップを高集積すると、IPM 内部の熱密度が高くなり、IPM 動作時のチップ接合温度の温度変化が大きくなる。そのような状況において実施の形態 1、2 で説明した構成を採用すれば、半導体チップの放熱性を高く保つことができる。

【 0 0 3 1 】

実施の形態 4 .

10

20

30

40

50

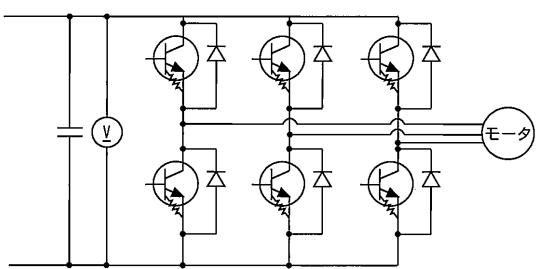

図6は、実施の形態4に係る電力変換装置を示す図である。電力変換装置は、実施の形態1～3のいずれか1つで説明した半導体モジュールを少なくとも1つ有する。すなわち、電力変換装置の少なくとも一箇所は、実施の形態1～3で説明した厚さの絶縁層12aと、半導体チップが形成される。図6には、半導体チップとして、6つのスイッチング素子と6つの還流ダイオードが設けられ、全体として3相交流インバータ回路を構成する電力変換装置が示されている。インバータ回路に限らず、コンバータ装置、サーボアンプ又は電源ユニットなどを形成してもよい。

### 【0032】

電力変換装置に、実施の形態1～3のいずれかの半導体モジュールを使用することで、半導体モジュール自体を小型化でき、高密度化でき、高寿命化できる。そのため、電力変換装置の筐体及びバスバーの設計制約が減り、電力変換装置の筐体サイズを小型化できる。また、従来は、インバータの筐体サイズに搭載できる半導体モジュールのレイアウト制約によって、インバータの制御電力素子数が制限されたが、本発明の半導体モジュールを用いることで電力変換装置内のレイアウト自由度が向上するので、制御電力素子数を増加することができ、インバータ自体の機能向上を実現することができる。

10

### 【0033】

なお、ここまで説明した各実施の形態で説明した技術的特徴は適宜に組み合わせて用いてもよい。

### 【符号の説明】

### 【0034】

20

10 放熱板、 12 絶縁基板、 12a 絶縁層、 12b 第1金属パターン、

12c 第2金属パターン、 14 第2金属接合材、 16, 20 第1金属接合材

、 18, 22 半導体チップ

【図1】

【図3】

【図2】

【図4】

【図5】

【図6】

---

フロントページの続き

(72)発明者 大月 高実

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

(72)発明者 山下 秋彦

兵庫県川西市久代三丁目13番21号 株式会社Wave Technology内

審査官 平林 雅行

(56)参考文献 国際公開第2014/030659 (WO, A1)

特開2015-095540 (JP, A)

特開2001-284513 (JP, A)

特開2013-202648 (JP, A)

国際公開第2015/178296 (WO, A1)

特開2001-358263 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 23/12-23/15

H01L 23/29

H01L 23/34-23/36

H01L 23/373-23/427

H01L 23/44

H01L 23/467-23/473

H01L 25/00-25/07

H01L 25/10-25/11

H01L 25/16-25/18