(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5961409号

(P5961409)

(45) 発行日 平成28年8月2日(2016.8.2)

(24) 登録日 平成28年7月1日(2016.7.1)

(51) Int.Cl.

F 1

|              |           |      |       |      |

|--------------|-----------|------|-------|------|

| HO1L 21/8242 | (2006.01) | HO1L | 27/10 | 321  |

| HO1L 27/108  | (2006.01) | HO1L | 29/78 | 613B |

| HO1L 29/786  | (2006.01) | HO1L | 29/78 | 618B |

| HO1L 21/8247 | (2006.01) | HO1L | 29/78 | 618C |

| HO1L 27/115  | (2006.01) | HO1L | 27/10 | 434  |

請求項の数 5 (全 16 頁) 最終頁に続く

(21) 出願番号

特願2012-48891(P2012-48891)

(22) 出願日

平成24年3月6日(2012.3.6)

(65) 公開番号

特開2012-199536(P2012-199536A)

(43) 公開日

平成24年10月18日(2012.10.18)

審査請求日 平成27年2月4日(2015.2.4)

(31) 優先権主張番号 特願2011-52270(P2011-52270)

(32) 優先日 平成23年3月10日(2011.3.10)

(33) 優先権主張国 日本国(JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 野田 耕生

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 加藤 俊哉

(56) 参考文献 特開2002-094029 (JP, A

)特開2009-016368 (JP, A

)

特開平05-297413 (JP, A)

最終頁に続く

(54) 【発明の名称】半導体記憶装置

## (57) 【特許請求の範囲】

## 【請求項1】

半導体と、

前記半導体上方の第1の絶縁膜と、

前記第1の絶縁膜上方の第1の導電膜と、

前記第1の絶縁膜上方の第2の導電膜と、

前記第1の絶縁膜上方に設けられ、前記第1の導電膜と前記第2の導電膜との間に、前記第1の絶縁膜に達する溝部を有する第2の絶縁膜と、

前記第1の導電膜および前記第2の導電膜と接する領域を有し、前記溝部の側面および底面と接する領域を有する酸化物半導体膜と、

前記酸化物半導体膜上方の第3の絶縁膜と、

前記第3の絶縁膜上方の第3の導電膜と、

を有し、

前記第1の導電膜は、前記第1の絶縁膜を介して前記半導体と重なる領域を有し、

前記第3の導電膜は、前記第3の絶縁膜を介して前記酸化物半導体膜と重なる領域を有し、

前記酸化物半導体膜は、前記第1の絶縁膜と接する領域を有することを特徴とする半導体記憶装置。

## 【請求項2】

半導体と、

10

20

前記半導体上方の第1の絶縁膜と、

前記第1の絶縁膜上方の第1の導電膜と、

前記第1の絶縁膜上方の第2の導電膜と、

前記第1の絶縁膜上方に設けられ、前記第1の導電膜と前記第2の導電膜との間に、前記第1の絶縁膜に達する溝部を有する第2の絶縁膜と、

前記第1の導電膜および前記第2の導電膜と接する領域を有し、前記溝部の側面および底面と接する領域を有する酸化物半導体膜と、

前記酸化物半導体膜上方の第3の絶縁膜と、

前記第3の絶縁膜上方の第3の導電膜と、

前記第3の絶縁膜上方の第4の導電膜と、

を有し、

前記第1の導電膜は、前記第1の絶縁膜を介して前記半導体と重なる領域を有し、

前記第3の導電膜は、前記第3の絶縁膜を介して前記酸化物半導体膜と重なる領域を有し、

前記第4の導電膜は、前記第3の絶縁膜および前記酸化物半導体膜を介して前記第1の導電膜と重なる領域を有し、

前記酸化物半導体膜は、前記第1の絶縁膜と接する領域を有することを特徴とする半導体記憶装置。

【請求項3】

請求項2において、

前記第4の導電膜は、前記第3の導電膜と同一材料を有することを特徴とする半導体記憶装置。

【請求項4】

請求項1乃至3のいずれか一項において、

前記第2の導電膜は、前記第1の導電膜と同一材料を有することを特徴とする半導体記憶装置。

【請求項5】

請求項1乃至4のいずれか一項において、

前記第2の絶縁膜は、前記第1の導電膜および前記第2の導電膜の上面を露出するよう設けられることを特徴とする半導体記憶装置。 30

【発明の詳細な説明】

【技術分野】

【0001】

トランジスタなどの半導体素子を含む回路を有する半導体記憶装置に関する。

【背景技術】

【0002】

データの書き込み、データの読み出し、およびデータの消去が可能な記憶回路を有する半導体記憶装置の開発が進められている。

【0003】

半導体記憶装置としては、例えば記憶素子であるトランジスタ（メモリトランジスタともいう。）または強誘電体材料を用いた素子を有する半導体記憶装置などが挙げられる（特許文献1および特許文献2参照。）。 40

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開昭57-105889号公報

【特許文献2】特開平06-196647号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

10

20

30

40

50

しかしながら、従来の半導体記憶装置は、メモリトランジスタにデータを書き込んだ後に、電荷のリークによりデータが消失してしまうといった問題があった。そのため、データを定期的に書き込むリフレッシュ動作が必要になり、半導体記憶装置の消費電力の増加に繋がっている。

【0006】

また、半導体記憶装置の集積度を高めるには、半導体記憶装置を構成する素子（トランジスタ、キャパシタなど）のサイズを小さくしていくことになる。スケーリング則に従いトランジスタのサイズを縮小すると、例えばチャネル長が100nm以下では短チャネル効果の影響が無視できなくなり、パンチスルーエフェクトによるリーク電流が流れやすくなるため、トランジスタがスイッチング素子として機能しなくなる問題があった。

10

【0007】

本発明の一態様では、半導体記憶装置において、集積度を高めつつ、データの保持時間を持続することを課題とする。

【課題を解決するための手段】

【0008】

本発明の一態様は、第1のトランジスタと、第2のトランジスタと、キャパシタと、を有し、第2のトランジスタのソースまたはドレインの一方が、第1のトランジスタのゲートと、キャパシタを構成する容量電極の一方と、を兼ねる半導体記憶装置である。

【0009】

前述の半導体記憶装置は、基板と、基板上に設けられた半導体膜と、半導体膜を覆う第1のゲート絶縁膜と、第1のゲート絶縁膜を介して半導体膜上に設けられた第1のゲート電極と、第1のゲート絶縁膜上にあり、半導体膜と重畳しない、第1のゲート電極と同一層かつ同一材料である第1の導電膜と、第1のゲート絶縁膜上にあり、かつ第1のゲート電極および第1の導電膜の上面を露出し、ならびに第1のゲート絶縁膜を露出する溝部を有する絶縁膜と、該絶縁膜上にあり、第1のゲート絶縁膜、第1のゲート電極および第1の導電膜と接する酸化物半導体膜と、酸化物半導体膜を覆う第2のゲート絶縁膜と、第2のゲート絶縁膜を介して酸化物半導体膜および溝部上に設けられた第2のゲート電極と、第2のゲート絶縁膜および酸化物半導体膜を介して第1のゲート電極上に設けられた、第2のゲート電極と同一層かつ同一材料である第2の導電膜と、を有する。

20

【0010】

ここで、第1のゲート電極は第1のトランジスタのゲート電極、第2のトランジスタのソース電極またはドレイン電極の一方およびキャパシタを構成する容量電極の一方を兼ねる。また、半導体膜および第1のゲート絶縁膜は、それぞれ第1のトランジスタのチャネル領域およびゲート絶縁膜として機能する。

30

【0011】

また、第1の導電膜は、第2のトランジスタのソース電極またはドレイン電極の他方として機能する。

【0012】

また、酸化物半導体膜、第2のゲート絶縁膜および第2のゲート電極は、それぞれ第2のトランジスタのチャネル領域、ゲート絶縁膜およびゲート電極として機能する。

40

【0013】

なお、酸化物半導体膜をトランジスタのチャネル領域に用いることで、トランジスタのオフ電流を低減できる。

【0014】

また、第2のゲート絶縁膜および第2の導電膜は、それぞれキャパシタを構成する誘電体膜および容量電極の他方として機能する。

【0015】

なお、第1のゲート絶縁膜を露出するために絶縁膜に設けられた溝部は、第2のトランジスタの実効的なチャネル長 $L'$ を長くするために設けられる。例えば、上面から見たソース電極およびドレイン電極間距離（第1の導電膜と第1のゲート電極との直線的距離）で

50

ある見かけ上のチャネル長 $L$ に対して、断面から見たソース電極およびドレイン電極間距離（第1の導電膜と第1のゲート電極との酸化物半導体膜に沿っての距離）である実効上のチャネル長 $L'$ の長さが2倍以上となるように絶縁膜の厚さを選択すればよい。そのためには、一例として絶縁膜の厚さを上面から見たソース電極およびドレイン電極間距離の二分の一以上とすればよい。ただし、絶縁膜の厚さは前述の範囲に限定されるものではない。

#### 【0016】

本明細書において、「第1の膜と第2の膜が同一層かつ同一材料である」という場合、第1の膜を延長した先が第2の膜であってもよいし、第1の膜と第2の膜が分離されていてもよい。

10

#### 【0017】

本発明の一態様を適用することによって、データの保持期間が長く、集積度の高い半導体記憶装置を提供することができる。

#### 【0018】

また、集積度の高い半導体記憶装置を作製することができるため、記憶容量あたりの半導体記憶装置の価格を安くすることが可能となる。

#### 【発明の効果】

#### 【0019】

絶縁膜に設けられた溝に接してチャネル領域を設けることで、半導体記憶装置の集積度を高めつつ、データの保持時間を長くすることができます。

20

#### 【図面の簡単な説明】

#### 【0020】

【図1】本発明の一態様である半導体記憶装置の例を示す上面図、断面図、回路図および電気特性。

【図2】本発明の一態様である半導体記憶装置の例を示す上面図、断面図および回路図。

【図3】本発明の一態様である半導体記憶装置の作製方法の例を示す断面図。

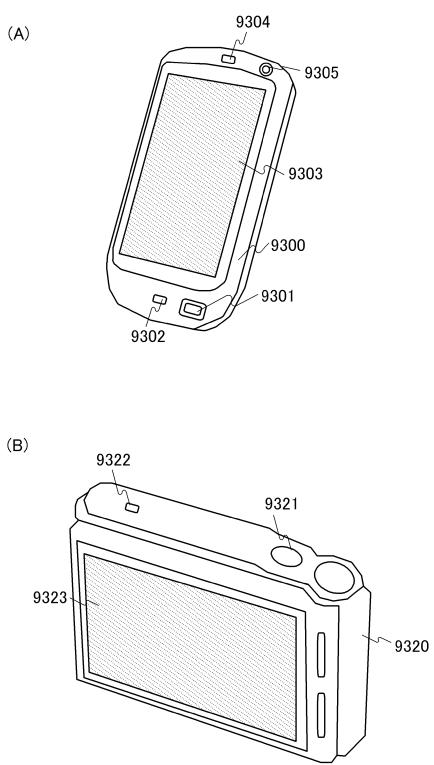

【図4】本発明の一態様である半導体記憶装置を有する電子機器の例を示す斜視図。

#### 【発明を実施するための形態】

#### 【0021】

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、その形態および詳細を様々に変更し得ることは、当業者であれば容易に理解される。また、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、図面を用いて発明の構成を説明するにあたり、同じものを指す符号は異なる図面間でも共通して用いる。なお、同様のものを指す際にはハッチパターンを同じくし、特に符号を付さない場合がある。

30

#### 【0022】

以下、本発明の説明を行うが、本明細書で用いる用語について簡単に説明する。まず、トランジスタのソースとドレインについては、本明細書においては、一方をドレインと呼ぶとき他方をソースとする。すなわち、電位の高低によって、それらを区別しない。従って、本明細書において、ソースとされている部分をドレインと読み替えることもできる。

40

#### 【0023】

また、電圧は、ある電位と、基準の電位（例えばグラウンド電位）との電位差のことを示す場合が多い。よって、電圧、電位、電位差を、各々、電位、電圧、電圧差と言い換えることが可能である。

#### 【0024】

本明細書においては、「接続する」と表現される場合であっても、現実の回路においては、物理的な接続部分がなく、配線が延在している場合だけのこともある。

#### 【0025】

なお、第1、第2として付される序数詞は便宜上用いるものであり、工程順または積層順を示すものではない。また、本明細書において発明を特定するための事項として固有の名

50

称を示すものではない。

**【0026】**

(実施の形態1)

本実施の形態では、本発明の一態様を適用した半導体記憶装置である不揮発性メモリを構成するトランジスタおよびキャパシタの構造、回路構成、ならびにその作製方法について図1乃至図3を用いて説明する。

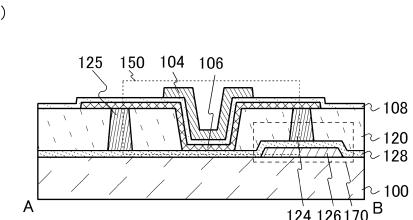

**【0027】**

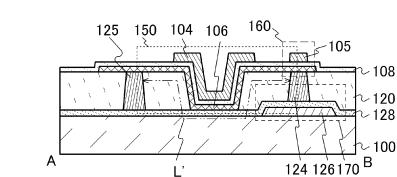

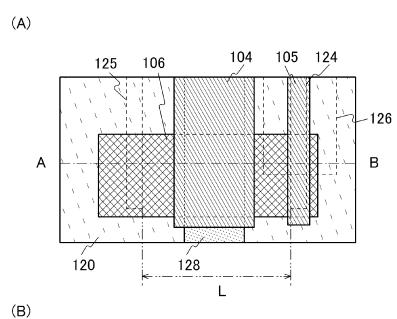

図1(A)は、半導体記憶装置である不揮発性メモリの上面図である。図1(A)における一点鎖線A-Bに対応する断面A-Bを図1(B)に示す。ただし、簡単のため、図1(A)では絶縁膜108を省略して示す。

10

**【0028】**

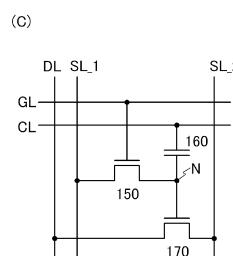

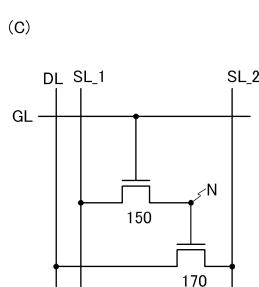

図1(C)は、不揮発性メモリの回路構成を示す。不揮発性メモリは、オフ電流が極めて小さいトランジスタ150と、トランジスタ150のゲートと接続するゲート配線GLと、トランジスタ150のソースと接続するソース配線SL\_1と、トランジスタ170と、トランジスタ170のソースと接続するソース配線SL\_2と、トランジスタ170のドレインと接続するドレイン配線DLと、キャパシタ160と、キャパシタ160の一端と接続する容量配線CLと、キャパシタ160の他端、トランジスタ150のドレインおよびトランジスタ170のゲートと接続するノードNと、を有する。

**【0029】**

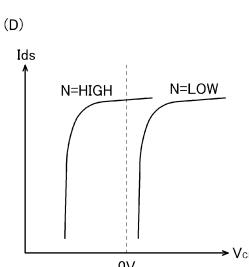

なお、本実施の形態に示す不揮発性メモリは、ノードNの電圧に応じて、トランジスタ170のしきい値電圧が変動することを利用したものである。例えば、図1(D)は容量配線CLの電圧 $V_{cL}$ と、トランジスタ170を流れるドレイン電流 $I_{ds}$ との関係を説明する図である。

20

**【0030】**

ここで、トランジスタ150を介して、ノードNの電圧を調整することができる。例えば、ソース配線SL\_1の電圧をVDDとする。このとき、ゲート配線GLの電圧をトランジスタ150のしきい値電圧VthにVDDを加えた電圧以上とすることで、ノードNの電圧をN=HIGHにすることができる。また、ゲート配線GLの電圧をトランジスタ150のしきい値電圧Vth以下とすることで、ノードNの電圧をN=LOWにすることができる。

30

**【0031】**

そのため、N=LOWで示した $V_{cL}$ - $I_{ds}$ カーブと、N=HIGHで示した $V_{cL}$ - $I_{ds}$ カーブのいずれかを得ることができる。即ち、N=LOWでは、 $V_{cL}=0V$ にて $I_{ds}$ が小さいため、データ0となる。また、N=HIGHでは、 $V_{cL}=0V$ にて $I_{ds}$ が大きいため、データ1となる。このようにして、データを記憶することができる。

**【0032】**

ここで、トランジスタ150にオフ電流が極めて小さいトランジスタを適用することで、ノードNに蓄積された電荷がトランジスタ150を通して意図せずにリークすることを抑制できる。そのため、長期間に渡ってデータを保持することができる。

**【0033】**

40

次に、本発明の一形態である不揮発性メモリを構成するトランジスタおよびキャパシタの構造について、図1(B)に示す断面A-Bを用いて説明する。

**【0034】**

半導体記憶装置は、基板100と、基板100上の半導体膜126と、半導体膜126を覆う絶縁膜128と、絶縁膜128を介して半導体膜126上に設けられた導電膜124と、絶縁膜128上にあり半導体膜126と重疊しない、導電膜124と同一層かつ同一材料である導電膜125と、絶縁膜128上にあり、導電膜124および導電膜125の上面を露出し、絶縁膜128を露出する溝部を有する絶縁膜120と、絶縁膜120上にあり、絶縁膜120の溝部の側面および底面(絶縁膜128)、導電膜124ならびに導電膜125と接する酸化物半導体膜106と、酸化物半導体膜106を覆う絶縁膜108

50

と、絶縁膜 108 を介して酸化物半導体膜 106 および絶縁膜 120 の溝部上に設けられた導電膜 104 と、絶縁膜 108 および酸化物半導体膜 106 を介して導電膜 124 と重畠する、導電膜 104 と同一層かつ同一材料である導電膜 105 と、を有する。

#### 【0035】

なお、絶縁膜 120 に設けられた溝部は絶縁膜 128 ではなく基板 100 を露出しても構わない。また、溝部は、導電膜 124 と導電膜 125 との間に設けられる。

#### 【0036】

ここで、トランジスタ 150において、導電膜 124 はソース電極またはドレイン電極の一方として機能する。また、導電膜 125 はソース電極またはドレイン電極の他方として機能する。また、酸化物半導体膜 106 はチャネル領域を有する。また、絶縁膜 108 は 10 、ゲート絶縁膜として機能する。また、導電膜 104 はゲート電極として機能する。

#### 【0037】

このとき、チャネル領域を有する酸化物半導体膜 106 が、絶縁膜 120 の溝部に接して設けられるため、上面から見たソース電極およびドレイン電極（導電膜 124 および導電膜 125 ）間距離である見かけ上のチャネル長 L（図 1 (A) 参照。）に対して、断面から見たチャネル領域（酸化物半導体膜 106 ）におけるチャネル領域の長さである実効上のチャネル長 L'（図 1 (B) 参照。）を長くすることができる。例えば、絶縁膜 120 に設けられる溝部の深さを、上面から見た導電膜 124 および導電膜 125 間距離の二分の一以上にすれば、見かけ上のチャネル長 L に対する実効上のチャネル長 L' の長さを 2 倍以上にすることができる。好ましくは、見かけ上のチャネル長 L に対する実効上のチャネル長 L' の長さを 3 倍以上、さらに好ましくは 4 倍以上とするように絶縁膜 120 の厚さおよび溝部の深さを選択する。例えば、見かけ上のチャネル長 L が 15 nm 以上 100 nm 以下の範囲の場合、絶縁膜 120 に設けられる溝部の深さは 7.5 nm 以上 200 nm 以下とすればよい。絶縁膜 120 に設けられる溝部の深さは前述の範囲に限定されない。ただし、酸化物半導体膜 106 の厚さを溝部の深さよりも薄くしなければ、見かけ上のチャネル長 L に対して、実効上のチャネル長 L' を長くすることができないことは述べるまでもない。そのため、溝部の深さは酸化物半導体膜 106 の厚さ以上とする。 20

#### 【0038】

絶縁膜 120 に設けられた溝部は絶縁膜 128 または基板 100 を露出するとしているが、これに限定されない。例えば、絶縁膜 120 中に溝部の底面を有していてもよい。また、絶縁膜 128 または基板 100 上にエッチストップ膜を別途設け、該エッチストップ膜を露出してもよい。 30

#### 【0039】

キャパシタ 160 の構成は以下の通りである。導電膜 124 は第 1 の容量電極として機能する。絶縁膜 108 は、誘電体膜として機能する。導電膜 105 は第 2 の容量電極として機能する。

#### 【0040】

トランジスタ 170 の構成は以下の通りである。導電膜 124 はゲート電極として機能する。また、半導体膜 126 はチャネル領域を有する。また、絶縁膜 128 は、ゲート絶縁膜として機能する。図示しないが、半導体膜 126 において、少なくとも導電膜 124 と重畠しない領域に、半導体膜 126 に設けられるチャネル領域よりも低抵抗であるソース領域およびドレイン領域を設ける。また、ソース領域およびドレイン領域と接し、導電膜 124 および導電膜 125 とは異なる層であるソース配線 S\_L\_2 およびドレイン配線 D\_L を有する。また、ソース領域およびドレイン領域に加えて、チャネル領域よりも抵抗が低く、ソース領域およびドレイン領域よりも抵抗の高い LDD (Lightly Doped Drain) 領域を設けてもよい。LDD 領域を設けることにより、チャネル長が小さくなると生じるホットキャリア劣化などのトランジスタの劣化を低減することができ、さらに短チャネル効果を低減することができる。 40

#### 【0041】

基板 100 に大きな制限はないが、少なくとも、後の熱処理に耐えうる程度の耐熱性を有 50

している必要がある。例えば、ガラス基板、セラミック基板、石英基板、サファイア基板などを、基板100として用いてもよい。また、シリコンや炭化シリコンなどの単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウムなどの化合物半導体基板、S O I (Silicon On Insulator) 基板などを適用することも可能であり、これらの基板上に半導体素子が設けられたものを、基板100として用いてもよい。また、該半導体素子をトランジスタ170に代えても構わない。

#### 【0042】

基板100として、可とう性基板を用いてもよい。その場合は、可とう性基板上に直接的にトランジスタを作製する。なお、可とう性基板上にトランジスタを設ける方法としては、非可とう性の基板上にトランジスタを作製した後、トランジスタを剥離し、可とう性基板である基板100に転置する方法もある。その場合には、非可とう性基板とトランジスタとの間に剥離層を設けるとよい。10

#### 【0043】

半導体膜126は、非晶質シリコン、微結晶シリコン、多結晶シリコンもしくは単結晶シリコンなどのシリコン系材料、ゲルマニウム系材料、シリコンゲルマニウム系材料、ガリウムヒ素系材料または炭素系材料などを用いればよい。

#### 【0044】

導電膜124、導電膜125、導電膜104および導電膜105は、Al、Ti、Cr、Co、Ni、Cu、Y、Zr、Mo、Ag、TaおよびW、それらの窒化物、酸化物ならびに合金から一以上選択し、単層でまたは積層で用いればよい。また、導電膜104として酸化物を用いる場合は、 $5 \times 10^{19} \text{ cm}^{-3}$ 以上20 atomic%以下、または $1 \times 10^{20} \text{ cm}^{-3}$ 以上7 atomic%以下の窒素を含んでもよい。例えば、 $1 \times 10^{20} \text{ cm}^{-3}$ 以上7 atomic%以下の窒素を含み、かつIn、GaおよびZnを含む酸化物膜を用いるとよい。酸化物膜を導電膜104に用いる場合、酸化物膜は金属膜と比べて抵抗が高いため、ゲート電極全体の抵抗を低減するために、シート抵抗が10 / s q以下 の低抵抗膜を積層して設けると好ましい。なお、単位が $\text{cm}^{-3}$ で示す濃度はSIMS (Secondary Ion Mass Spectrometry) 分析によって定量化でき、単位がatomic%の濃度はXPS (X-ray Photoelectron Spectroscopy) 分析によって定量化できる。20

#### 【0045】

酸化物半導体膜106は、6 nm以上100 nm以下、好ましくは15 nm以上40 nm以下とする。トランジスタ150のチャネル長を小さくすると、スケーリング則に従い、酸化物半導体膜106の厚さを薄くしていくことが好ましい。しかしながら、本発明の一態様を適用することによって、見かけ上のチャネル長Lが短いま実効上のチャネル長L'を長くすることができるため、前述の範囲の厚さとすることが可能となる。30

#### 【0046】

酸化物半導体膜106は、スパッタリング法、プラズマCVD法、PLD (Pulse Laser Deposition) 法、MBE (Molecular Beam Epitaxy) 法または蒸着法などを用い、例えば、In、Ga、ZnおよびSnから選ばれた二種以上を含む材料を用いればよい。40

#### 【0047】

酸化物半導体膜106として、例えば、四元系金属酸化物であるIn-Sn-Ga-Zn-O系の材料や、三元系金属酸化物であるIn-Ga-Zn-O系の材料、In-Sn-Zn-O系の材料、In-Al-Zn-O系の材料、Sn-Ga-Zn-O系の材料、Al-Ga-Zn-O系の材料、Sn-Al-Zn-O系の材料や、二元系金属酸化物であるIn-Zn-O系の材料、Sn-Zn-O系の材料、Al-Zn-O系の材料、Zn-Mg-O系の材料、Sn-Mg-O系の材料、In-Mg-O系の材料、In-Ga-O系の材料や、In-O系の材料、Sn-O系の材料、Zn-O系の材料などを用いればよい。ここで、例えば、In-Ga-Zn-O系の材料とは、インジウム(In)、ガリウム(Ga)、亜鉛(Zn)を有する酸化物、という意味であり、その組成比は特に問わな50

い。また、InとGaとZn以外の元素を含んでいてもよい。このとき、酸化物半導体膜106の化学量論比に対し、Oを過剰にすると好ましい。Oを過剰にすることで酸化物半導体膜106の酸素欠損に起因するキャリアの生成を抑制することができる。

#### 【0048】

なお、一例として、酸化物半導体膜106としてIn-Zn-O系の材料を用いる場合、原子数比で、In/Zn = 0.5以上5.0以下、好ましくはIn/Zn = 1以上2.0以下、さらに好ましくはIn/Zn = 1.5以上1.5以下とする。Znの原子数比を前述の範囲とすることで、トランジスタの電界効果移動度を向上させることができる。ここで、化合物の原子数比がIn : Zn : O = X : Y : Zのとき、Z > 1.5X + Yとすると好ましい。

10

#### 【0049】

酸化物半導体膜106として、化学式 $InMO_3 (ZnO)_m (m > 0)$ で表記される材料を用いてもよい。ここで、Mは、Ga、Al、MnおよびCoから選ばれた一または複数の金属元素を示す。例えば、Mとして、Ga、GaおよびAl、GaおよびMnまたはGaおよびCoなどを用いてもよい。

#### 【0050】

酸化物半導体膜106は、バンドギャップが2.5eV以上、好ましくは3.0eV以上の材料を選択する。バンドギャップが大きいことにより、熱などによる価電子帯から伝導帯へのキャリアの励起が少なく、該キャリアの励起に起因する電流が生じにくい。加えて、酸化物半導体膜106中に準位を形成する不純物などが少ないと好ましい。

20

#### 【0051】

ここで、酸化物半導体膜106は、水素、アルカリ金属およびアルカリ土類金属などが低減され、極めて不純物濃度の低い酸化物半導体膜である。そのため、酸化物半導体膜106をチャネル領域に用いたトランジスタはオフ電流を小さくできる。

#### 【0052】

酸化物半導体膜106中の水素濃度は、 $5 \times 10^{18} \text{ cm}^{-3}$ 未満、好ましくは $1 \times 10^{18} \text{ cm}^{-3}$ 以下、より好ましくは $5 \times 10^{17} \text{ cm}^{-3}$ 以下、さらに好ましくは $1 \times 10^{16} \text{ cm}^{-3}$ 以下とする。

#### 【0053】

アルカリ金属は酸化物半導体を構成する元素ではないため、不純物である。アルカリ土類金属も、酸化物半導体を構成する元素ではない場合において、不純物となる。特に、アルカリ金属のうちナトリウム(Na)は、酸化物半導体膜に接する絶縁膜において、当該絶縁膜中に拡散して $Na^+$ となる。また、Naは、酸化物半導体膜内において、酸化物半導体を構成する金属と酸素の結合を分断する、または、その結合中に割り込む。その結果、例えば、しきい値電圧がマイナス方向にシフトすることによるノーマリオン化、電界効果移動度の低下などの、トランジスタ特性の劣化が起こり、加えて、特性のばらつきも生じる。この不純物によりもたらされるトランジスタ特性の劣化と、特性のばらつきは、酸化物半導体膜中の水素濃度が十分に低い場合において顕著に現れる。従って、酸化物半導体膜中の水素濃度が $1 \times 10^{18} \text{ cm}^{-3}$ 以下、または $1 \times 10^{17} \text{ cm}^{-3}$ 以下である場合には、上記不純物の濃度を低減することが望ましい。具体的に、Na濃度の測定値は、 $5 \times 10^{16} \text{ cm}^{-3}$ 以下、好ましくは $1 \times 10^{16} \text{ cm}^{-3}$ 以下、さらに好ましくは $1 \times 10^{15} \text{ cm}^{-3}$ 以下とする。同様に、リチウム(Li)濃度の測定値は、 $5 \times 10^{15} \text{ cm}^{-3}$ 以下、好ましくは $1 \times 10^{15} \text{ cm}^{-3}$ 以下とする。同様に、カリウム(K)濃度の測定値は、 $5 \times 10^{15} \text{ cm}^{-3}$ 以下、好ましくは $1 \times 10^{15} \text{ cm}^{-3}$ 以下とする。

30

#### 【0054】

以上に示した酸化物半導体膜106をトランジスタのチャネル領域に用いることでトランジスタのオフ電流を小さくできる。具体的には、酸化物半導体膜106を用いることにより、例えば、チャネル長が3μm、チャネル幅が1μmのときのトランジスタのオフ電流を $1 \times 10^{-18} \text{ A}$ 以下、または $1 \times 10^{-21} \text{ A}$ 以下、または $1 \times 10^{-24} \text{ A}$ 以下と

40

50

することができる。

**【0055】**

酸化物半導体膜106は、単結晶、多結晶（ポリクリスタルともいう。）または非晶質などの状態をとる。

**【0056】**

好ましくは、酸化物半導体膜106は、CAAC-OS(C Axis Aligned Crystalline Oxide Semiconductor)膜とする。

**【0057】**

CAAC-OS膜は、完全な単結晶ではなく、完全な非晶質でもない。CAAC-OS膜は、非晶質相に結晶部および非晶質部を有する結晶-非晶質混相構造の酸化物半導体膜である。なお、当該結晶部は、一辺が100nm未満の立方体内に収まる大きさであることが多い。また、透過型電子顕微鏡（TEM：Transmission Electron Microscope）による観察像では、CAAC-OS膜に含まれる非晶質部と結晶部との境界は明確ではない。また、TEMによってCAAC-OS膜には粒界（グレインバウンダリーともいう。）は確認できない。そのため、CAAC-OS膜は、粒界に起因する電子移動度の低下が抑制される。

10

**【0058】**

CAAC-OS膜に含まれる結晶部は、c軸がCAAC-OS膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃い、かつab面に垂直な方向から見て三角形状または六角形状の原子配列を有し、c軸に垂直な方向から見て金属原子が層状または金属原子と酸素原子とが層状に配列している。なお、異なる結晶部間で、それぞれa軸およびb軸の向きが異なっていてもよい。本明細書において、単に垂直と記載する場合、85°以上95°以下の範囲も含まれることとする。また、単に平行と記載する場合、-5°以上5°以下の範囲も含まれることとする。

20

**【0059】**

なお、CAAC-OS膜において、結晶部の分布が一様でなくてもよい。例えば、CAAC-OS膜の形成過程において、酸化物半導体膜の表面側から結晶成長させる場合、被形成面の近傍に対し表面の近傍では結晶部の占める割合が高くなることがある。また、CAAC-OS膜へ不純物を添加することにより、当該不純物添加領域において結晶部が非晶質化することもある。

30

**【0060】**

CAAC-OS膜に含まれる結晶部のc軸は、CAAC-OS膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃うため、CAAC-OS膜の形状（被形成面の断面形状または表面の断面形状）によっては互いに異なる方向を向くことがある。なお、結晶部のc軸の方向は、CAAC-OS膜が形成されたときの被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向となる。結晶部は、成膜することにより、または成膜後に加熱処理などの結晶化処理を行うことにより形成される。

**【0061】**

CAAC-OS膜を用いたトランジスタは、可視光や紫外光の照射による電気特性の変動を低減することが可能である。よって、当該トランジスタは、信頼性が高い。

40

**【0062】**

絶縁膜108は、等価酸化膜厚換算（酸化シリコン膜厚換算）で0.5nm以上50nm以下、好ましくは5nm以上30nm以下とする。トランジスタ150のチャネル長を小さくすると、スケーリング則に従い、絶縁膜108の厚さを薄くしていくことが好ましい。しかしながら、本発明の一態様を適用することによって、見かけ上のチャネル長L'が短いままで実効上のチャネル長L'を長くすることができるため、前述の範囲の厚さとすることが可能となる。

**【0063】**

絶縁膜128、絶縁膜120および絶縁膜108は、例えば酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化アルミニウム、酸化ハフニウム、酸化イッ

50

トリウムまたは酸化ジルコニウムなどを用いればよく、積層または単層で設ける。例えば、熱酸化法、プラズマ CVD 法、スパッタリング法などで形成すればよい。

#### 【0064】

絶縁膜 128 は、絶縁膜 120 を加工する際にエッチストップ膜としての機能を有すると好ましい。そのため、絶縁膜 128 と絶縁膜 120 とは、加工の際に選択比がとれる材料を選択することが好ましい。例えば、絶縁膜 128 として酸化シリコン膜を用い、絶縁膜 120 として窒化シリコン膜を用いるなど、異なる材料とすればよい。

#### 【0065】

絶縁膜 128、絶縁膜 120 および絶縁膜 108 は、加熱処理により酸素を放出する膜を用いると好ましい。加熱処理により酸素を放出する膜を用いることで、酸化物半導体膜 106 および酸化物半導体膜 106 の界面近傍に生じる欠陥を修復することができ、トランジスタの電気特性の劣化を抑制できる。

10

#### 【0066】

「加熱処理により酸素を放出する」とは、TDS (Thermal Desorption Spectroscopy : 昇温脱離ガス分光法) 分析にて、酸素原子に換算しての酸素の放出量が  $1.0 \times 10^{18}$  atoms/cm<sup>3</sup> 以上、または  $3.0 \times 10^{20}$  atoms/cm<sup>3</sup> 以上であることをいう。

#### 【0067】

ここで、TDS 分析にて、酸素原子に換算しての酸素の放出量の測定方法について、以下に説明する。

20

#### 【0068】

TDS 分析したときの気体の放出量は、所定の温度範囲におけるイオン強度の積分値に比例する。このため、測定したイオン強度の積分値と、標準試料の基準値との比により、気体の放出量を計算することができる。標準試料の基準値とは、所定の原子を含む試料において、所定の原子に相当するイオン強度の積分値に対する所定の原子の密度の割合である。

#### 【0069】

例えば、標準試料である所定の密度の水素を含むシリコンウェハの TDS 分析結果、および絶縁膜の TDS 分析結果から、絶縁膜の酸素分子の放出量 ( $N_{O_2}$ ) は、数式 1 で求めることができる。ここで、TDS 分析で得られる質量数 32 で検出されるガスの全てが酸素分子由来と仮定する。質量数 32 のものとしてほかに CH<sub>3</sub>OH があるが、存在する可能性が低いものとしてここでは考慮しない。また、酸素原子の同位体である質量数 17 の酸素原子および質量数 18 の酸素原子を含む酸素分子についても、自然界における存在比率が極微量であるため考慮しない。

30

#### 【0070】

$$N_{O_2} = N_{H_2} / S_{H_2} \times S_{O_2} \times \quad \text{(数式 1)}$$

#### 【0071】

$N_{H_2}$  は、標準試料から脱離した水素分子を密度で換算した値である。 $S_{H_2}$  は、標準試料を TDS 分析したときのイオン強度の積分値である。ここで、標準試料の基準値を、 $N_{H_2} / S_{H_2}$  とする。 $S_{O_2}$  は、絶縁膜を TDS 分析したときのイオン強度の積分値である。 は、TDS 分析におけるイオン強度に影響する係数である。数式 1 の詳細に関しては、特開平 6 - 275697 公報を参照する。なお、上記絶縁膜の酸素の放出量は、電子科学株式会社製の昇温脱離分析装置 EMD-WA1000S/W を用い、標準試料として  $1 \times 10^{16}$  atoms/cm<sup>3</sup> の水素原子を含むシリコンウェハを用いて測定した。

40

#### 【0072】

また、TDS 分析において、酸素の一部は酸素原子として検出される。酸素分子と酸素原子の比率は、酸素分子のイオン化率から算出することができる。なお、上述の は酸素分子のイオン化率を含むため、酸素分子の放出量を評価することで、酸素原子の放出量について見積もることができる。

#### 【0073】

50

なお、 $N_{O_2}$  は酸素分子の放出量である。酸素原子に換算したときの放出量は、酸素分子の放出量の 2 倍となる。

#### 【0074】

上記構成において、加熱処理により酸素を放出する膜は、酸素が過剰な酸化シリコン ( $SiO_x$  ( $X > 2$ )) であってもよい。酸素が過剰な酸化シリコン ( $SiO_x$  ( $X > 2$ )) とは、シリコン原子数の 2 倍より多い酸素原子を単位体積当たりに含むものである。単位体積当たりのシリコン原子数および酸素原子数は、ラザフォード後方散乱法により測定した値である。

#### 【0075】

絶縁膜 128、絶縁膜 120 および絶縁膜 108 から酸化物半導体膜 106 に酸素が供給されることで、酸化物半導体膜 106 と絶縁膜 128 との界面準位密度、酸化物半導体膜 106 と絶縁膜 120 との界面準位密度、または酸化物半導体膜 106 と絶縁膜 108 との界面準位密度を低減できる。この結果、トランジスタの動作などに起因して、酸化物半導体膜 106 と絶縁膜 128 との界面、酸化物半導体膜 106 と絶縁膜 120 との界面、または酸化物半導体膜 106 と絶縁膜 108 との界面にキャリアが捕獲されることを抑制することができ、良好な電気特性のトランジスタを得ることができる。10

#### 【0076】

さらに、酸化物半導体膜 106 の酸素欠損に起因して電荷が生じる場合がある。一般に酸化物半導体膜の酸素欠損は、一部がドナーとなりキャリアである電子を放出する。この結果、トランジスタのしきい値電圧がマイナス方向にシフトしてしまう。絶縁膜 128、絶縁膜 120 および絶縁膜 108 から酸化物半導体膜 106 に酸素が十分に供給されることにより、しきい値電圧がマイナス方向へシフトする要因である、酸化物半導体膜の酸素欠損を低減することができる。20

#### 【0077】

以上のようにして得られたトランジスタ 150 は、酸化物半導体膜 106 を用いることにより、オフ電流を低減できるため、キャパシタ 160 に蓄積された電荷を長期間に渡って保持することが可能な不揮発性メモリを提供することができる。また、トランジスタ 150 は、動作頻度が低くなるため電気特性の劣化が少なく、信頼性の高い不揮発性メモリを提供することができる。30

#### 【0078】

また、絶縁膜 120 に溝部を設け、該溝部と接する酸化物半導体膜 106 を形成することによって、上面図で見る導電膜 124 および導電膜 125 間距離である見かけ上のチャネル長  $L$  に対し、実効上のチャネル長  $L'$  を 2 倍以上、好ましくは 3 倍以上、さらに好ましくは 4 倍以上の長さとすることができます。そのため、トランジスタ 150 のサイズを縮小しても短チャネル効果の影響を低減することが可能となり、不揮発性メモリの集積度を高めることができるとなる。

#### 【0079】

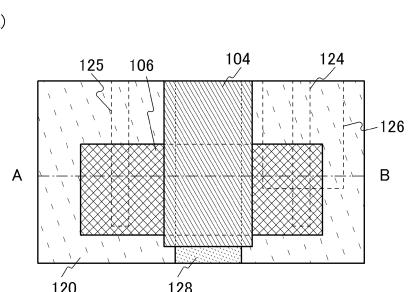

次に、図 1 に示した不揮発性メモリにおいて、キャパシタを含まない構成について図 2 を用いて説明する。

#### 【0080】

図 2 (C) は、不揮発性メモリの回路図である。不揮発性メモリは、トランジスタ 150 と、トランジスタ 150 のゲートと接続するゲート配線  $GL$  と、トランジスタ 150 のソースと接続するソース配線  $SL\_1$  と、トランジスタ 170 と、トランジスタ 170 のソースと接続するソース配線  $SL\_2$  と、トランジスタ 170 のドレインと接続するドレン配線  $DL$  と、トランジスタ 150 のドレインとトランジスタ 170 のゲートと接続するノード  $N$  と、を有する。40

#### 【0081】

トランジスタ 150 にオフ電流の小さなトランジスタを用いる場合、キャパシタを設けなくてもトランジスタ 150 のドレインとトランジスタ 170 のゲートの間のノード  $N$  に電荷を保持できる。キャパシタを設けない構成であるため、容量配線などが省略されること50

で小面積化が可能となる。そのため、キャパシタを設けた場合と比べさらに集積度を高めることができる。

#### 【0082】

また、本実施の形態では、配線を4本または5本用いる不揮発性メモリを示したが、これに限定されるものではない。例えば、ソース配線S L \_ 1 とドレイン配線D L を共通にする構成としても構わない。

#### 【0083】

なお、本実施の形態で示した不揮発性メモリを複数組み合わせて集積化し、メモリセルアレイを作製してもよい。その場合、適宜アドレス線などを追加する。本実施の形態で示した不揮発性メモリを適用することにより、メモリセルアレイの集積度を高めることができる。10

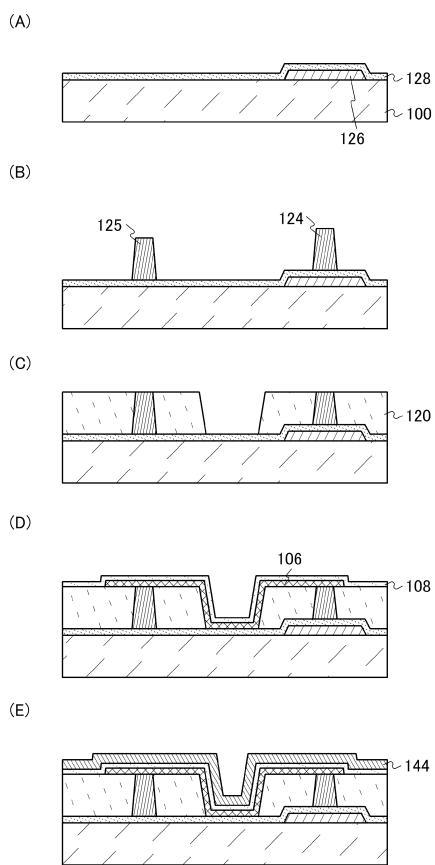

#### 【0084】

次に、本実施の形態に示すトランジスタ150、キャパシタ160およびトランジスタ170を作製する方法の一例について、図3を用いて説明する。

#### 【0085】

まず、基板100上に半導体膜126を形成する。次に、絶縁膜128を成膜する（図3（A）参照。）。

#### 【0086】

次に、導電膜124および導電膜125を形成する。（図3（B）参照。）。なお、この後、導電膜124をマスクに用いて、半導体膜126に対し、キャリアを生成する不純物（シリコン系の材料の場合、リン、ヒ素、ボロンなど）をイオン注入またはイオンドーピングにより添加してもよい。半導体膜126に不純物を添加することにより、ソース領域およびドレイン領域、またはLDD領域を設けることができる。20

#### 【0087】

次に、絶縁膜120を形成する（図3（C）参照。）。絶縁膜120は、絶縁膜を成膜した後、化学的機械研磨（CMP：Chemical Mechanical Polishing）またはエッチバックを行い、その後フォトリソグラフィ工程によって絶縁膜128を露出する溝部を設けることによって形成することができる。または、フォトリソグラフィ工程によって絶縁膜128を露出する溝部を形成し、その後CMPまたはエッチバックによって導電膜124および導電膜125を露出して形成することができる。なお、CMPまたはエッチバックによって導電膜124および導電膜125の一部が除去されてもよい。30

#### 【0088】

エッチバックとは、凹凸のある膜表面に平坦化膜を形成し、平坦化膜ごと凹凸のある膜に対して異方性の高いエッティング（例えば、ドライエッティング）を行うことで、膜の凹凸を低減する工程をいう。または、単に、全面に形成された膜に対し、被形成面の一部が露出するまで行うエッティング工程をいう。

#### 【0089】

次に、酸化物半導体膜を成膜し、フォトリソグラフィ工程によって酸化物半導体膜106を形成する。酸化物半導体膜106の形成前に、逆スパッタリング処理などのプラズマ処理を行い、絶縁膜120の溝部が有する断面形状上の角を、曲面形状に加工すると好ましい。こうすることで、絶縁膜120の溝部における酸化物半導体膜106の被覆性が向上し、トランジスタ150の電気特性上の不良を低減することができる。次に、絶縁膜108を成膜する（図3（D）参照。）。なお、酸化物半導体膜106となる酸化物半導体膜を成膜した後、および絶縁膜108を成膜した後のいずれか一方、または両方の後に熱処理を行っても構わない。熱処理は150以上650以下、好ましくは250以上450以下で行う。熱処理を行うことで、絶縁膜128、絶縁膜120または絶縁膜108より酸素が放出され、酸化物半導体膜106中および酸化物半導体膜106の界面近傍の欠陥を低減することができる。なお、この熱処理は、絶縁膜108を成膜した直後に行うことには限定されず、導電膜144を成膜した直後に行ってもよいし、絶縁膜108の成4050

膜以降のどの工程の後に行っても構わない。

**【0090】**

次に、導電膜144を成膜する(図3(E)参照。)。次に、導電膜144を加工し、酸化物半導体膜106と重畠する導電膜104、および導電膜124と重畠する導電膜105を形成する(図1(B)参照。)。ここで、導電膜104をマスクにして、酸化物半導体膜106に対し、間接的または直接的にキャリアを生成する不純物(水素、ヘリウム、ネオン、アルゴン、クリプトン、キセノン、窒素、リンなど)をイオン注入法またはイオンドーピング法により添加してもよい。酸化物半導体膜106に不純物を添加することにより、ソース領域およびドレイン領域またはLDD領域を設けることができる。

**【0091】**

以上の工程によって、図1に示すトランジスタ150、キャパシタ160およびトランジスタ170を作製することができる。

**【0092】**

なお、図2に示すトランジスタ150およびトランジスタ170を形成するためには、図1(B)に示すトランジスタ作製の工程中、導電膜105を形成しなければよい。

**【0093】**

このように、トランジスタ150、キャパシタ160およびトランジスタ170を同時に作製することが可能であるため、不揮発性メモリを作製するためのフォトリソグラフィ工程数を削減することができる。

**【0094】**

以上により、三次元の形状を適用することで、集積度を高めても短チャネル効果の影響が低減され、かつフォトリソグラフィ工程数の増加を抑えた半導体記憶装置である不揮発性メモリを提供することができる。

**【0095】**

本実施の形態は、他の実施の形態と適宜組み合わせて用いることができる。

**【0096】**

(実施の形態2)

本実施の形態では、実施の形態1を適用した電子機器の例について説明する。

**【0097】**

図4(A)は携帯型情報端末である。筐体9300と、ボタン9301と、マイクロフォン9302と、表示部9303と、スピーカ9304と、カメラ9305と、を具備し、携帯型電話機としての機能を有する。本発明の一態様は、携帯型情報端末の内部にあるメモリモジュールに適用することができる。

**【0098】**

図4(B)は、デジタルスチルカメラである。筐体9320と、ボタン9321と、マイクロフォン9322と、表示部9323と、を具備する。本発明の一態様は、デジタルスチルカメラの内部にあるメモリモジュールに適用することができる。

**【0099】**

本発明の一態様を用いることで、電子機器の消費電力を低減でき、また電子機器の価格を安くすることができる。

**【0100】**

本実施の形態は、他の実施の形態と適宜組み合わせて用いることができる。

**【符号の説明】**

**【0101】**

100 基板

104 導電膜

105 導電膜

106 酸化物半導体膜

108 絶縁膜

120 絶縁膜

10

20

30

40

50

|         |         |    |

|---------|---------|----|

| 1 2 4   | 導電膜     |    |

| 1 2 5   | 導電膜     |    |

| 1 2 6   | 半導體膜    |    |

| 1 2 8   | 絶縁膜     |    |

| 1 4 4   | 導電膜     |    |

| 1 5 0   | トランジスタ  |    |

| 1 6 0   | キャパシタ   |    |

| 1 7 0   | トランジスタ  |    |

| 9 3 0 0 | 筐体      |    |

| 9 3 0 1 | ボタン     | 10 |

| 9 3 0 2 | マイクロフォン |    |

| 9 3 0 3 | 表示部     |    |

| 9 3 0 4 | スピーカ    |    |

| 9 3 0 5 | カメラ     |    |

| 9 3 2 0 | 筐体      |    |

| 9 3 2 1 | ボタン     |    |

| 9 3 2 2 | マイクロフォン |    |

| 9 3 2 3 | 表示部     |    |

【図1】

【図2】

【図3】

【図4】

---

フロントページの続き

(51)Int.Cl.

F I

|        |        |           |        |       |       |

|--------|--------|-----------|--------|-------|-------|

| H 01 L | 21/336 | (2006.01) | H 01 L | 29/78 | 3 7 1 |

| H 01 L | 29/788 | (2006.01) | H 01 L | 27/10 | 4 4 1 |

| H 01 L | 29/792 | (2006.01) |        |       |       |

| H 01 L | 27/105 | (2006.01) |        |       |       |

(58)調査した分野(Int.Cl., DB名)

|        |               |

|--------|---------------|

| H 01 L | 2 1 / 8 2 4 2 |

| H 01 L | 2 1 / 3 3 6   |

| H 01 L | 2 1 / 8 2 4 7 |

| H 01 L | 2 7 / 1 0 5   |

| H 01 L | 2 7 / 1 0 8   |

| H 01 L | 2 7 / 1 1 5   |

| H 01 L | 2 9 / 7 8 6   |

| H 01 L | 2 9 / 7 8 8   |

| H 01 L | 2 9 / 7 9 2   |