(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6410827号

(P6410827)

(45) 発行日 平成30年10月24日(2018.10.24)

(24) 登録日 平成30年10月5日(2018.10.5)

(51) Int.Cl.

F 1

G O 1 B 7/00 (2006.01)

G O 1 R 27/02 (2006.01)G O 1 B 7/00 1 O 1 E

G O 1 R 27/02 A

請求項の数 20 (全 12 頁)

(21) 出願番号 特願2016-544105 (P2016-544105)

(86) (22) 出願日 平成26年12月31日 (2014.12.31)

(65) 公表番号 特表2017-502302 (P2017-502302A)

(43) 公表日 平成29年1月19日 (2017.1.19)

(86) 國際出願番号 PCT/US2014/073071

(87) 國際公開番号 WO2015/103429

(87) 國際公開日 平成27年7月9日 (2015.7.9)

審査請求日 平成29年12月28日 (2017.12.28)

(31) 優先権主張番号 61/922,716

(32) 優先日 平成25年12月31日 (2013.12.31)

(33) 優先権主張國 米国(US)

(31) 優先権主張番号 14/585,455

(32) 優先日 平成26年12月30日 (2014.12.30)

(33) 優先権主張國 米国(US)

(73) 特許権者 390020248

日本テキサス・インスツルメンツ株式会社

東京都新宿区西新宿六丁目24番1号

(73) 特許権者 507107291

テキサス インスツルメンツ インコーポ

レイテッド

アメリカ合衆国 テキサス州 75265

-5474 ダラス メイル ステイショ

ン 3999 ピーオーボックス 655

474

(74) 上記1名の代理人 100098497

弁理士 片寄 恒三

最終頁に続く

(54) 【発明の名称】負インピーダンス制御ループを備えた共振インピーダンス感知

## (57) 【特許請求の範囲】

## 【請求項 1】

共振器発振振幅と周波数とにより特徴付けられ、共振において、感知された状態に応答して変化する共振インピーダンス(損失係数)により特徴付けられる共振器を備える共振誘導性感知に適したインダクタンス・デジタル変換(IDC)回路であって、前記IDC回路が、

負インピーダンス回路要素であって、

共振器発振電圧を受信し、前記共振器発振周波数に同期化される周波数を有するD級スイッチング出力D\_ckを提供するD級コンパレータと、

制御された負のインピーダンスに対応するディスクリートループ制御信号に基づいてディスクリート電流レベルを有するディスクリート駆動電流を出力するディスクリート電流源と、

前記ディスクリート電流源を前記共振器にインターフェースするHブリッジ回路要素であって、前記ディスクリート駆動電流の時間平均が共振器発振振幅に対応するように、前記ディスクリート駆動電流を前記共振器発振電圧と同期化するようにD\_ckにより制御される、前記Hブリッジ回路要素と、

を含む、前記負インピーダンス回路要素と、

前記共振器をループフィルタとして組み込むループ制御回路要素であって、

D\_ckによりクロックされる振幅サンプリング回路要素であって、前記共振器発振振幅を振幅サンプルに変換する、前記振幅サンプリング回路要素と、

10

20

D \_ クロックによりクロックされる出力コンパレータであって、前記制御された負のインピーダンスが共振インピーダンスを実質的に相殺し、それにより、定常状態発振に対応する実質的に一定の共振器発振振幅を保つように、前記振幅サンプルと振幅基準との比較に基づいて前記ディスクリートループ制御信号を出力する、前記出力コンパレータと、

を含む、前記ループ制御回路要素と、

を含む、I D C回路。

**【請求項 2】**

請求項 1 に記載の I D C回路であって、

前記出力コンパレータが、2 レベル g m \_ 低 / 高ループ制御信号を出力するシングルビットコンパレータであり、

前記ディスクリート電流源が、前記 g m \_ 低 / 高ループ制御信号に基づいて g m \_ 低及び g m \_ 高駆動電流レベルを出力する、回路。

10

**【請求項 3】**

請求項 1 に記載の I D C回路であって、

前記ディスクリート電流源が電流 D A C である、回路。

**【請求項 4】**

請求項 1 に記載の I D C回路であって、

前記振幅サンプリング回路要素が、

前記共振器発振振幅に対応する検出された振幅信号を生成する振幅検出回路要素と、

前記検出された振幅信号をサンプリングし、前記振幅サンプルを提供するサンプル / ホールド回路要素と、

を含む、回路。

20

**【請求項 5】**

請求項 4 に記載の I D C回路であって、

前記ループ制御回路要素が、前記振幅検出回路要素への入力のために前記共振器発振振幅をバッファするように構成されるバッファ回路を更に含む、回路。

**【請求項 6】**

請求項 1 に記載の I D C回路であって、

前記ディスクリートループ制御信号に対応するセンサ応答データを前記制御された負のインピーダンスを表すものとして出力するセンサ出力回路要素を更に含む、回路。

30

**【請求項 7】**

請求項 6 に記載の I D C回路であって、

D \_ c l k を共振器発振周波数に対応する周波数信号に変換する周波数推定回路要素を更に含み、

前記センサ出力回路要素が、前記ディスクリートループ制御信号と前記周波数信号とに対応するセンサ応答データを出力する、回路。

**【請求項 8】**

共振器発振振幅と周波数とにより特徴付けられ、共振において、感知された状態に応答して変化する共振インピーダンス（損失係数）により特徴付けられる共振器を備える共振誘導性感知に適したインダクタンス・デジタル変換（I D C）回路であって、前記 I D C回路が、

40

制御された負のインピーダンスに対応するディスクリートループ制御信号に基づくディスクリート電流レベルを備えるディスクリート駆動電流で前記共振器を駆動する負インピーダンス回路要素と、

前記共振器をループフィルタとして組み込むループ制御回路要素であって、前記制御された負のインピーダンスが共振インピーダンスを実質的に相殺し、それにより、定常状態発振に対応する実質的に一定の共振器発振振幅を維持するように、共振器発振振幅に基づいて前記ディスクリートループ制御信号を生成する、前記ループ制御回路要素と、

を含み、

前記負インピーダンス回路要素が、

50

共振器発振電圧を受信し、前記共振器発振周波数に同期化される周波数を有するD級スイッチング出力D\_c1kを提供するD級コンパレータと、

前記ディスクリートループ制御信号を前記ディスクリート駆動電流に変換するディスクリート電流源と、

前記ディスクリート電流源を前記共振器にインターフェースするHブリッジ回路要素であって、前記ディスクリート駆動電流の時間平均が前記共振器発振振幅に対応するよう前に記ディスクリート駆動電流を前記共振器発振電圧と同期化するようにD\_c1kにより制御される、前記Hブリッジ回路要素と、

を含み、

前記ループ制御回路要素が、

10

D\_クロックによりクロックされ、前記共振器発振振幅を振幅サンプルに変換する振幅サンプリング回路要素と、

D\_クロックによりクロックされ、前記振幅サンプルと振幅基準との比較に基づいて前記ディスクリートループ制御信号を出力する出力コンパレータと、

を含む、回路。

【請求項9】

請求項8に記載のIDC回路であって、

前記出力コンパレータが、2レベルg\_m\_低/高ループ制御信号を出力するシングルピットコンパレータであり、

前記ディスクリート電流源が、前記g\_m\_低/高ループ制御信号に基づいてg\_m\_低及びg\_m\_高駆動電流レベルを出力する、回路。

20

【請求項10】

請求項8に記載のIDC回路であって、

前記ディスクリート電流源が電流DACである、回路。

【請求項11】

請求項8に記載のIDC回路であって、

前記振幅サンプリング回路要素が、

前記共振器発振振幅から検出された振幅信号を生成する振幅検出回路要素と、

前記検出された振幅信号をサンプリングし、前記共振器発振振幅サンプルを提供するサンプル/ホールド回路要素と、

30

を含む、回路。

【請求項12】

請求項11に記載のIDC回路であって、

前記ループ制御回路要素が、前記振幅検出回路要素への入力のために前記共振器発振振幅をバッファするバッファ回路を更に含む、回路。

【請求項13】

請求項8に記載のIDC回路であって、

前記ディスクリートループ制御信号に対応するセンサ応答データを前記制御された負のインピーダンスを表すものとして出力するセンサ出力回路要素を更に含む、回路。

【請求項14】

請求項13に記載のIDC回路であって、

D\_c1kを共振器発振周波数に対応する周波数信号に変換する周波数推定回路要素を更に含み、

前記センサ出力回路要素が、前記ディスクリートループ制御信号と前記周波数信号とに対応するセンサ応答データを出力する、回路。

【請求項15】

共振誘導性感知に適した誘導性感知システムであって、

共振器発振振幅と周波数とにより特徴付けられ、共振において、感知された状態に応答して変化する共振インピーダンス(損失係数)により特徴付けられる共振器と、

前記共振器に結合されるインダクタンス・デジタル変換ユニットと、

40

50

を含み、

前記インダクタンス・デジタル変換ユニットが、

負のインピーダンス回路要素であって、

共振器発振電圧を受信し、前記共振器発振周波数に同期化される周波数を有するD級スイッチング出力D\_c1kを提供するD級コンパレータと、

制御された負のインピーダンスに対応するディスクリートループ制御信号に基づいてディスクリート電流レベルを備えるディスクリート駆動電流を出力するディスクリート電流源と、

前記ディスクリート電流源を前記共振器にインターフェースするHブリッジ回路要素であって、前記ディスクリート駆動電流の時間平均が共振器発振振幅に対応するように、前記ディスクリート駆動電流を前記共振器発振電圧と同期化するようにD\_c1kにより制御される、前記Hブリッジ回路要素と、

を含む、前記負のインピーダンス回路要素と、

前記共振器をループフィルタとして組み込むループ制御回路要素であって、

Dクロックによりクロックされ、前記共振器発振振幅を振幅サンプルに変換する振幅サンプリング回路要素と、

Dクロックによりクロックされる出力コンパレータであって、前記制御された負のインピーダンスが共振インピーダンスを実質的に相殺し、それにより、定常状態発振に対応する実質的に一定の共振器発振振幅を維持するように、前記振幅サンプルと振幅基準との比較に基づいて前記ディスクリートループ制御信号を出力する、前記出力コンパレータと

、

を含む、前記ループ制御回路要素と、

を含む、システム。

#### 【請求項16】

請求項15に記載のシステムであって、

前記出力コンパレータが、2レベルg\_m\_低／高ループ制御信号を出力する単一ビットコンパレータであり、

前記ディスクリート電流源が、前記g\_m\_低／高ループ制御信号に基づいてg\_m\_低及びg\_m\_高駆動電流レベルを出力する電流D A Cを含む、システム。

#### 【請求項17】

請求項15に記載のシステムであって、

前記振幅サンプリング回路要素が、

前記共振器発振振幅から検出された振幅信号を生成する振幅検出回路要素と、

前記検出された振幅信号をサンプリングし、前記共振器発振振幅サンプルを提供するサンプル／ホールド回路要素と、

を含む、システム。

#### 【請求項18】

請求項17に記載のシステムであって、

前記ループ制御回路要素が、前記振幅検出回路要素への入力のために前記共振器発振振幅をバッファするバッファ回路を更に含む、システム。

#### 【請求項19】

請求項15に記載のシステムであって、

前記制御された負のインピーダンスを表すものとして前記ディスクリートループ制御信号に対応するセンサ応答データを出力するセンサ出力回路要素を更に含む、システム。

#### 【請求項20】

請求項19に記載のシステムであって、

D\_c1kを共振器発振周波数に対応する周波数信号に変換する周波数推定回路要素を更に含み、

前記センサ出力回路要素が、前記ディスクリートループ制御信号と前記周波数信号とに対応するセンサ応答データを出力する、システム。

10

20

30

40

50

## 【発明の詳細な説明】

## 【背景技術】

## 【0001】

本願は、概して誘導性センサに関し、特に、位置、近接度、又は物理的状態又は状況を感知する際に用いられるなどの、共振誘導センサ及び感知に関連する。

## 【0002】

共振センサは、共振状態（共振周波数及び振幅）におけるオペレーションのために構成される共振器を含む。センサ電子機器は、共振（定常状態発振）を保つために共振器発振電圧と同期化されたA C励起電流で共振器を駆動し、共振器インピーダンス（直列 / 並列抵抗  $R_s / R_p$  など）によって表される共振器損失係数を克服する。例えば、誘導性感知の場合、共振器は、磁気感知フィールドに投じられる共振で動作される誘導性感知コイルを含む。

10

## 【0003】

共振感知は、例えば、導電性ターゲットに応答する共振器インピーダンスの変化に起因する共振器振幅及び周波数の変化により明示化される、共振状態の変化に基づく。例えば、誘導性感知の場合、共振は、導電性ターゲットに関連付けられる渦電流効果により生じるなど、誘導性感知コイルからの投じられた磁気フラックスエネルギー出力における蓄積又は損失により影響を受ける。このセンサ応答は、共振器インピーダンス（損失係数  $R_s / R_p$ ）における変化として明示化される。

20

## 【発明の概要】

## 【0004】

説明される例は、位置、近接度、又は物理的状態又は状況を感知するためなど、共振センサを用いる感知の問題に向けられている。説明される例は、ループフィルタとして共振器を組み込み、D級コンパレータで実装されるD級負インピーダンス段と、D級コンパレータにより同期化される出力コンパレータで実装される制御ループ段とを含む、負インピーダンス制御ループを備えた共振インピーダンス感知のための装置及び方法を含む。

## 【0005】

例示の態様に従って、共振インピーダンス感知システムが、共振器とインダクタンス・デジタル変換（I D C）ユニットとを含む。共振器は、共振器発振振幅及び周波数により、及び感知された状態に応答して変化する共振インピーダンス（損失係数）による共振で、特徴付けられる。I D C回路は、負インピーダンス回路要素及びループ制御回路要素を含む。

30

## 【0006】

負のインピーダンス回路要素は、D級コンパレータと、Hブリッジ回路要素を介して共振器にインターフェースされるディスクリート電流源とを含む。D級コンパレータは、共振器発振電圧を受信するように、及び共振器発振周波数に同期化される周波数を備えたD級スイッチング出力  $D_{c1k}$  を提供するように構成される。ディスクリート電流源は、制御された負のインピーダンスに対応するディスクリートループ制御信号に基づくディスクリート電流レベルのディスクリート駆動電流を出力するように構成される。Hブリッジ回路要素は、ディスクリート駆動電流の時間平均が共振器発振振幅に対応するように、ディスクリート駆動電流を共振器発振電圧と同期化するように  $D_{c1k}$  により制御される。

40

## 【0007】

ループ制御回路要素は、共振器をループフィルタとして組み込み、振幅サンプリング回路要素及び出力コンパレータを含み、振幅サンプリング回路要素及び出力コンパレータはいずれも  $D_{c1k}$  によりクロックされる。振幅サンプリング回路要素は、共振器発振振幅を振幅サンプルに変換するように構成される。出力コンパレータは、制御された負のインピーダンスが共振インピーダンスを実質的に相殺し、それにより定常状態発振に対応する共振器発振振幅を実質的に一定に保つように、振幅サンプル及び振幅基準の比較に基づいてディスクリートループ制御信号を出力するように構成される。

50

## 【図面の簡単な説明】

## 【0008】

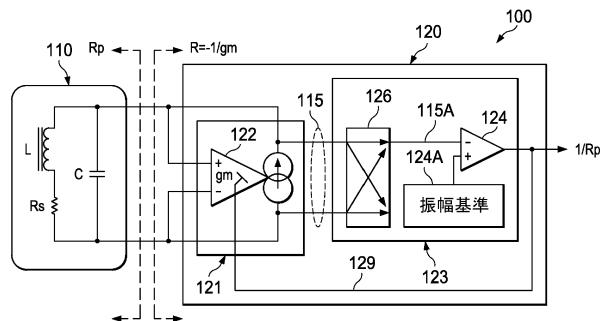

【図1】負のインピーダンスで励起電流を駆動するD級負インピーダンス段を含むインダクタンス・デジタル（IDC）コンバータにより駆動され、共振器発振振幅に応答する同期化された制御ループを備え、ループフィルタとして共振器を含む、LC共振器を含む共振誘導センサシステムの例示の実施例を図示する。

## 【0009】

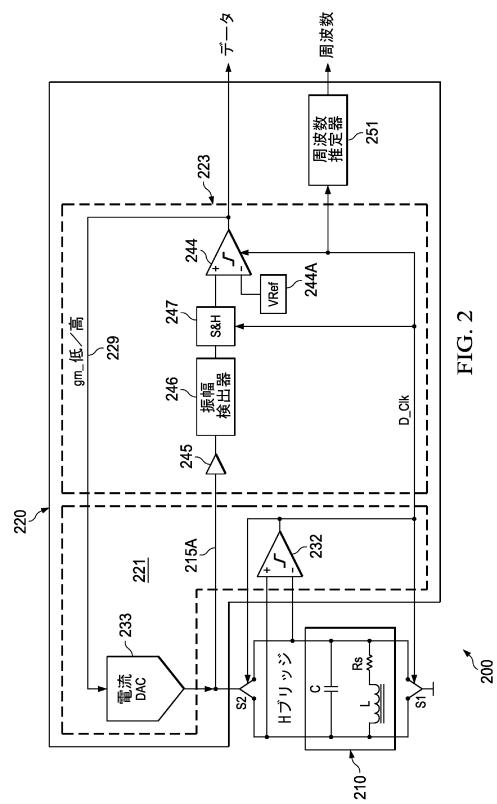

【図2】電流DACを備えるD級負インピーダンス段を含むインダクタンス・デジタルコンバータ（IDC）により駆動されるLC共振器（損失係数Rsを有する）を含む共振誘導センサシステムの例示の実施例を図示し、電流DACが、共振器発振電圧に基づいてD級コンパレータにより制御される接地基準のHブリッジを介して共振器にインターフェースされ、共振誘導センサシステムが、D級コンパレータにより同期化される出力コンパレータを備え、検出された共振器発振振幅に基づいてディスクリートループ制御信号を提供するループ制御段を含み、共振器インピーダンス（損失係数Rs）を平衡化させるため及び一定の共振器発振振幅を維持するために負の抵抗を制御する。

10

## 【発明を実施するための形態】

## 【0010】

例示の実施例及び応用例は、負インピーダンス制御ループを備えた共振インピーダンス感知の種々の特徴及び利点を達成し、負インピーダンス制御ループは、ループフィルタとして共振器を組み込み、D級コンパレータで実装されるD級負インピーダンス段と、D級コンパレータによりクロックされる出力コンパレータで実装される制御ループ段とを含む。「D級コンパレータ」という用語は、D級機能性を実装する際に用いられるコンパレータを意味し、MOSFETスイッチを駆動するD級モードで動作するコンパレータを意味しない。

20

## 【0011】

概略を述べると、共振インピーダンス感知システムの例示の実施例が、D級負インピーダンス段とループ制御段とを含むインダクタンス・デジタル変換ユニットを含む。D級コンパレータは、共振器発振電圧を受信し、共振器発振周波数と同期化されるD級スイッチング出力を生成する。ディスクリート電流源（電流DACなど）が、D級スイッチング出力により切り替えられるHブリッジを介して共振器を駆動し、そのため、ディスクリート駆動電流の時間平均が共振器発振振幅に対応する。共振器発振振幅に基づいて、出力コンパレータは、ディスクリートループ制御信号をディスクリート電流源に提供し、共振インピーダンスを平衡させる負インピーダンスで共振器を駆動し、それにより、定常状態発振に対応する一定の共振器発振振幅を維持する。

30

## 【0012】

例示の実施例において、共振誘導性感知システムが、IDCユニットとセンサ/共振器とを含み、センサ/共振器は、共振器発振振幅及び周波数により、及び感知された状況に応答して共振インピーダンス（損失係数）を変更することによる共振で、特徴付けられる。IDCユニットは、負インピーダンス回路要素及びループ制御回路要素を含む。負のインピーダンス回路要素は、制御された負のインピーダンスに対応するディスクリートループ制御信号に基づいてディスクリート電流レベルを有するディスクリート駆動電流で共振器を駆動するように構成される。ループ制御回路要素は、共振器をループフィルタとして組み込み、共振器発振振幅に基づいてディスクリートループ制御信号を生成するように構成され、そのため、制御された負のインピーダンスが共振インピーダンスを実質的に相殺し、それにより、定常状態発振に対応する共振器発振振幅が実質的に一定に保たれる。

40

## 【0013】

例示の実施例において、負のインピーダンス回路要素は、D級コンパレータと、Hブリッジ回路要素を介して共振器にインターフェースされるディスクリート電流源とを含む。D級コンパレータは、共振器発振電圧を受信するように、及び共振器発振周波数に同期化される周波数を有するD級スイッチング出力D\_ckを提供するように構成される。デ

50

ディスクリート電流源は、ディスクリートループ制御信号をディスクリート駆動電流に変換するように構成される。Hブリッジ回路要素は、ディスクリート駆動電流を共振器発振電圧と同期化するようにD\_c1kにより制御され、そのため、ディスクリート駆動電流の時間平均は共振器発振振幅に対応する。ループ制御回路要素は、振幅サンプリング回路要素及び出力コンパレータを含み、振幅サンプリング回路要素及び出力コンパレータはいずれもD\_c1kによりクロックされる。振幅サンプリング回路要素は、共振器発振振幅を振幅サンプルに変換するように構成される。出力コンパレータは、振幅サンプル及び振幅基準の比較に基づいてディスクリートループ制御信号を出力するように構成される。

#### 【0014】

例示の実施例において、出力コンパレータは、2レベルg m\_低 / 高ループ制御信号を出力するシングルビットコンパレータであり得、ディスクリート電流源は、g m\_低 / 高制御信号に基づいてg m\_低及びg m\_高駆動電流レベルを出力する電流D A Cである。振幅サンプリング回路要素は、検出された振幅信号を共振器発振振幅から生成する振幅検出回路要素と、検出された振幅信号をサンプリングし共振器発振振幅サンプルを提供するサンプル / ホールド回路要素とで実装され得る。ループ制御回路要素は更に、振幅検出回路要素への入力のため共振器発振振幅をバッファするように構成されるバッファ回路を含み得る。

10

#### 【0015】

例示の実施例において、IDCは、制御された負のインピーダンスを表すものとしてディスクリートループ制御信号に対応するセンサ応答データを出力するように構成されるセンサ出力回路要素を含み得る。また、IDCは更に、D\_c1kを共振器発振周波数に対応する周波数信号に変換するように構成される周波数推定回路要素を含み得、センサ出力回路要素は、ディスクリートループ制御信号及び周波数信号に対応するセンサ応答データを出力するように構成され得る。

20

#### 【0016】

図1は、共振誘導センサ100の例示の実施例を図示する。センサ100は、Rsによって表される損失係数を有するLC共振器110と、インダクタンス・デジタル(IDC)コンバータ120とを含む。損失係数Rsは、等価並列抵抗 / インピーダンスRpと同等である。

#### 【0017】

30

例示の応用例において、導電性ターゲットの近接度 / 位置感知のためにセンサ100を用いることができる。近接する導電性ターゲット(センサ100の感知範囲内)が、共振インピーダンス(損失係数Rs / Rp)における変化を引き起こし得、これはIDC120により検出される。

#### 【0018】

IDC120は、共振器の発振周波数と同期化されたAC励起電流で共振器110を駆動する。IDC120は、負インピーダンス段121及びループ制御段123を含み、ローパスループフィルタとして共振器110を含む負インピーダンス制御ループを確立する。IDC負インピーダンス制御ループは、共振器発振振幅を一定(定常状態発振)に保つために共振器110を負インピーダンスで駆動する。

40

#### 【0019】

負インピーダンス段121は、共振器発振電圧と同期化された、ループ制御された負のインピーダンスを有する共振器励起電流で駆動する。ループ制御段123は、共振器発振振幅(115)を監視し、共振器発振振幅を一定に保つために負インピーダンスを制御するフィードバックループ制御信号129を負インピーダンス段121に提供する。一定の共振器発振振幅が定常状態発振に対応し、負のインピーダンス / 抵抗が、共振器インピーダンス / 抵抗(Rs / Rp損失係数)を平衡化する。

#### 【0020】

負インピーダンス段121は、制御されたトランスアドミッタンス(g m)を有するトランスアドミッタンス増幅器122として実装され得る。トランスアドミッタンス増幅器

50

122は、共振器発振電圧（トランスアドミッタンス増幅器への入力）で同期化された励起／駆動電流で共振器110を駆動し、負インピーダンスが、ループ制御段123からのフィードバック  $g_m$  アドミッタンスループ制御信号129により制御される。

【0021】

ループ制御段123は、増幅器124及び整流器126によって表され得る。増幅器124は、整流された共振器発振振幅115A及び振幅基準124Aに基づいて  $g_m$  アドミッタンスループ制御信号129を提供する。つまり、ループ制御123は、共振器発振振幅115 / 115Aに応答して、増幅器122の  $g_m$  (アドミッタンス) を変調／調整するために  $g_m$  振幅制御信号129を生成し、共振器振幅を一定に保つために負インピーダンスを制御する。

10

【0022】

IDC120は、負インピーダンス ( $1 / R_p$ 、ここで、 $R_p = L / (C \times R_s)$ ) を制御する  $g_m$  振幅ループ制御信号129に対応するセンサ応答データを出力する。センサ応答データは、近接導電性ターゲットなどに起因する、共振インピーダンス ( $R_s / R_p$ ) の変化に対応する負インピーダンスの変化を定量化する。

【0023】

図2は、共振誘導センサ200の例示の実施例を図示する。センサ200は、 $R_s$  によって表される損失係数を有するLC共振器210、及びインダクタンス・デジタル(IDC)コンバータ220を含む。損失係数  $R_s$  は、等価並列抵抗／インピーダンス  $R_p$  と同等である。

20

【0024】

例示の応用例において、導電性ターゲットの近接度／位置感知のためにセンサ200を用いることができる。近接する導電性ターゲット（センサ100の感知範囲内）が、共振インピーダンス（損失係数  $R_s / R_p$ ）における変化を起こし得、これはIDC220により検出される。

【0025】

IDC220は、共振器210を、共振器発振電圧と同期化される（即ち、共振状態で動作する共振器の発振周波数に同期化される）AC励起電流で駆動する。IDC220は、近接導電性ターゲットなどに起因する、共振インピーダンス ( $R_s / R_p$ ) の変化により生じる共振器210の共振状態の変化を検出する、共振器210をローパスループフィルタとして含む負インピーダンス制御ループを確立する。

30

【0026】

IDC220は、D級負インピーダンス段221及びループ制御段223を含む。D級負インピーダンス段221は、D級コンバレータ232で実装される。ループ制御段223は、D級コンバレータ232からのD級スイッチング出力 ( $D_{c1k}$ ) と同期化される（によりクロックされる）出力コンバレータ244で実装される。

【0027】

D級負インピーダンス段221は、D級コンバレータ232と接地基準のHブリッジS1 / S2を介して共振器210にインターフェースされる電流DAC233を含む、D級トランスアドミッタンス増幅器として実装される。共振器発振電圧はD級コンバレータ232に入力され、D級コンバレータ232は、HブリッジS1 / S2を整流するD級スイッチングパルストレインを出力し、電流DAC233（Hブリッジを介する入力）からの駆動／励起電流を共振器発振電圧（D級コンバレータへの入力）と同期化する。

40

【0028】

D級コンバレータ232及びHブリッジは、駆動電流を共振器発振電圧（共振器発振周波数）と同期化するために、D級スイッチングを提供する。D級コンバレータ232は、正のフィードバックを提供するためにHブリッジを整流し、共振器210の正側を電流DAC233に、及び共振器の負側を接地に接続する。

【0029】

D級コンバレータ232のスイッチング出力はまた、ループ制御段223（共振器発振

50

周波数と同期化される)を同期化するために用いられるD\_c1kとして出力される。

【0030】

電流D A C 2 3 3は、共振器2 1 0( Hブリッジを介して)をディスクリート駆動/励起電流レベル(g m\_低及びg m\_高)で駆動する。電流D A C 2 3 3は、ループ制御段2 2 3からのディスクリート2レベルg m\_低/高フィードバック制御信号2 2 9により制御され、共振器2 1 0を、ループ制御段2 2 3(出力コンパレータ2 4 4)からのディスクリートg m\_低/高ループ制御信号2 2 9により制御される負インピーダンスで効果的に駆動する。電流D A C 2 3 3からのディスクリート電流駆動は、共振器2 1 0により時間平均化され、これはI D C制御ループにおいてローパスループフィルタとして機能する。つまり、電流D A C 2 3 3から共振器2 1 0(D級コンパレータ2 3 2)により共振器発振周波数と同期化される)へのディスクリート電流レベルの時間平均は、ループ制御段2 2 3に入力される共振器発振振幅2 1 5 Aに対応する。10

【0031】

D級負インピーダンス段2 2 1は、接地基準のHブリッジインターフェースを備えた、D級O T A(オペレーションナルトランスマミッタス増幅器)により実装され得る。D級負インピーダンス段2 2 1をトランスマミッタス増幅器として実装することで、負インピーダンスが、トランジスタに関連して低温度係数を有するレジスタによって定義され得、それにより温度ドリフトが緩和される。また、D級機能性は、共振器2 1 0の電力消費を最小化する。20

【0032】

ループ制御段2 2 3は、D級負インピーダンス段2 2 1から、共振器発振振幅2 1 5 A及びD級コンパレータ2 3 2のD\_c1k出力を受信する。共振器振幅2 1 5 Aは、共振器2 1 0に負荷をかけることを避けるために1×バッファ2 4 5を介してループ制御段2 2 3に入力される。20

【0033】

HブリッジS 1 / S 2は、ループ制御段2 2 3(即ち、図1の1 2 6)にあるように整流を提供すること)に入力される共振器電圧2 1 5 Aを効果的に整流する。ループ制御段2 2 3をD級負インピーダンス段(いずれも、共振器発振周波数に同期化される)と同期化するためにD\_c1kが用いられる。30

【0034】

ループ制御段2 2 3は、D\_c1kによりクロックされる出力コンパレータ2 4 4を含み、電流D A C 2 3 3を制御するディスクリートフィードバック制御信号2 2 9を生成する。出力コンパレータ2 4 4は、シングル又はマルチビットの出力コンパレータであり得、シングル又はマルチビット電流D A Cを駆動する。例示の実施例では、出力コンパレータ2 4 4は、ディスクリートの2レベルg m\_低/高ループ(振幅)制御2 2 9信号を出力するシングルビットコンパレータであり、これは、2レベル電流D A C 2 3 3を制御し、ディスクリートg m\_低及びg m\_高電流レベルを共振器2 1 0に(Hブリッジを介して)供給する。30

【0035】

出力コンパレータ2 4 4は、共振器発振振幅2 1 5 Aに基づいてディスクリート2レベルg m\_低/高制御信号2 2 9を生成する。振幅検出器2 4 6が、共振器振幅2 1 5 Aを検出し、これは、サンプル/ホールド2 4 7によりサンプリングされ、D\_c1kによりクロックされる。D\_クロック周波数での共振器振幅サンプルが出力コンパレータ2 4 4に入力される。振幅検出器2 4 6及びサンプル/ホールド2 4 7(及び1×バッファ2 4 5)は、積分及びダンプフィルタとして実装され得る。40

【0036】

D\_c1kに同期化される出力コンパレータ2 4 4は、共振器振幅サンプル2 1 5 Aを振幅電圧基準V R e fと比較し、ディスクリートの2レベルg m\_低/高ループ(振幅)制御信号2 2 9を生成し、これは、D級負インピーダンス段2 2 1において電流D A C 2 3 3にフィードバックされる。つまり、出力コンパレータ2 4 4の出力レベルは、電流D50

A C 2 3 3 によって共振器 2 1 0 のための駆動電流に変換される g m \_ 低 / 高アドミッタ

ンスレベルに対応する。

【 0 0 3 7 】

g m \_ 低 / 高ループ ( 振幅 ) 制御信号 2 2 9 は、共振器インピーダンス ( 損失係数 R s / R p ) を相殺するため及び共振器発振振幅を一定に保つために必要とされる負インピーダンスに対応する。つまり、ループ制御信号 2 2 9 は、それが、共振器発振振幅 ( 2 1 5 A ) を実質的に一定に保つために必要とされる負インピーダンス ( 1 / R p ) を表すという点で、( 例え、ターゲット近接度 / 位置に対する ) 共振センサ 2 1 0 の感知応答に対応する。このように、ループ制御信号 2 2 9 は、I D C 2 2 0 からセンサ応答データ出力を提供する。

10

【 0 0 3 8 】

I D C 2 2 0 は、共振器発振周波数に対応して、D \_ c 1 k を受信する周波数推定器 2 5 1 を含む。周波数推定器 2 5 1 は、D \_ c 1 k を I D C 2 2 0 からの周波数出力に変換する。

【 0 0 3 9 】

I D C 2 2 0 は、データ及び周波数を出力し、これらは、そのセンサ共振器についての定量化された情報を提供する。例え、導電性ターゲット ( 湧電流感知 ) と共に用いられる共振誘導センサ 2 0 0 に対して、ターゲット近接度 / 位置を判定するためにこういったデータ及び / 又は周波数出力を用いることができる。

【 0 0 4 0 】

20

D 級及び出力コンパレータ 2 3 2 及び 2 4 4 を備えた、D 級負インピーダンス段 2 2 1 及びループ制御段 2 2 3 によって提供される I D C 制御ループは、積分又はその他のフィルタリングを必要としない。代わりに、それは、出力コンパレータのディスクリート出力を平均化するために共振器 2 1 0 を一次ローパスフィルタとして組み込む。D 級 / 出力コンパレータ 2 3 2 / 2 4 4 のみがアクティブ構成要素であり、センサ共振器において消失される電力への電力消費が低減される。

【 0 0 4 1 】

共振器 2 1 0 は、加算ノードにおいて I D C 制御ループに含まれ、ここで、共振器の正の共振インピーダンスが I D C 制御ループ ( D 級負インピーダンス段 2 2 1 ) の負インピーダンスと比較される。この構成の利点には： ( a ) 共振インピーダンスを、それに相關されたパラメータを測定するのではなく、直接的に測定すること、 ( b ) 例え、センサの一定共振器発振の振幅が、センサにより生成される磁束の一定振幅を示唆するので、磁気コアからの非線形を抑制すること、 ( c ) 制御ループの過渡応答がセンサの過渡応答を追跡するので、センサのための I D C 過渡応答を最適化すること、及び ( d ) センサによる I D C からの量子化ノイズを減衰すること、が含まれる。

30

【 0 0 4 2 】

本発明の特許請求の範囲内で、説明した例示の実施例に変形が成され得、多くの他の実施例が可能である。

【 図 1 】

FIG. 1

【 図 2 】

FIG. 2

---

フロントページの続き

(72)発明者 ジョージ ピー リーツマ

アメリカ合衆国 94061 カリフォルニア州 レッドウッド シティ, ブエナヴィスタ

アヴェニュー 511

審査官 真岩 久恵

(56)参考文献 米国特許出願公開第2003/0071638 (US, A1)

特開昭51-82651 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G01B 7/00 - 7/34

G01R 27/00 - 27/32