(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5351176号

(P5351176)

(45) 発行日 平成25年11月27日(2013.11.27)

(24) 登録日 平成25年8月30日(2013.8.30)

(51) Int.Cl.

G 11 C 16/02 (2006.01)

F 1

G 11 C 17/00 601 E

G 11 C 17/00 611 G

G 11 C 17/00 613

G 11 C 17/00 641

請求項の数 19 (全 22 頁)

(21) 出願番号 特願2010-543040 (P2010-543040)

(86) (22) 出願日 平成20年8月4日 (2008.8.4)

(65) 公表番号 特表2011-510428 (P2011-510428A)

(43) 公表日 平成23年3月31日 (2011.3.31)

(86) 國際出願番号 PCT/KR2008/004530

(87) 國際公開番号 WO2009/093786

(87) 國際公開日 平成21年7月30日 (2009.7.30)

審査請求日 平成23年8月3日 (2011.8.3)

(31) 優先権主張番号 10-2008-0006501

(32) 優先日 平成20年1月22日 (2008.1.22)

(33) 優先権主張国 韓国 (KR)

(73) 特許権者 503447036

サムスン エレクトロニクス カンパニー

リミテッド

大韓民国・443-742・キョンギード

・スウォンーシ・ヨントンク・サムスン

一口・129

(74) 代理人 100064908

弁理士 志賀 正武

(74) 代理人 100089037

弁理士 渡邊 隆

(74) 代理人 100110364

弁理士 実広 信哉

最終頁に続く

(54) 【発明の名称】メモリプログラミング装置および方法

## (57) 【特許請求の範囲】

## 【請求項 1】

データページを格納するデータ格納部と、

前記データページから1つ以上の基準閾値電圧の状態を有するセルの数を計数してインデックス情報を生成する第1計数部と、

前記生成されたインデックス情報を格納するインデックス格納部と、

前記データ格納部に前記データページを格納し、前記インデックス格納部に前記生成されたインデックス情報を格納するプログラミング部と、

前記データ格納部のデータの複数の基準閾値電圧の状態の中で1つ以上の基準電圧状態を選択する基準選択部と、

を含み、

前記第1計数部は、前記生成されたインデックス情報を前記プログラミング部に伝達し

、同時にプログラムされる物理的なマルチビットセルの集合をページといい、1つのページは1つのワード線に接続されたマルチビットセルの集合であり、1つのページが前記データ格納部および前記インデックス格納部に分けられていることを特徴とするメモリプログラミング装置。

## 【請求項 2】

前記データ格納部に格納された前記データページを読み出す検出部と、

前記読み出したデータページから前記1つ以上の基準閾値電圧の状態それぞれの個数を

計数して検証情報を生成する第2計数部と、

前記生成された検証情報および前記インデックス格納部に格納された前記インデックス情報に基づいて、前記読み出したデータページのエラーの有無を判定するエラー判定部と、

をさらに含むことを特徴とする請求項1に記載のメモリプログラミング装置。

#### 【請求項3】

前記データ格納部に格納されたデータページを読み出す検出部と、

前記読み出したデータページから前記1つ以上の基準閾値電圧の状態それぞれの個数を計数して検証情報を生成する第2計数部と、

前記生成された検証情報および前記インデックス格納部に格納された前記インデックス情報に基づいて、前記データ格納部に形成された散布状態の変化をモニタリングする閾値電圧モニタリング部と、

をさらに含むことを特徴とする請求項1に記載のメモリプログラミング装置。

#### 【請求項4】

前記プログラミング部は、前記データ格納部に前記データページを格納する間に前記インデックス格納部に前記生成されたインデックス情報を格納することを特徴とする請求項1に記載のメモリプログラミング装置。

#### 【請求項5】

前記データ格納部および前記インデックス格納部は、マルチビットデータが格納される少なくとも1つのマルチビットセルを含むことを特徴とする請求項1に記載のメモリプログラミング装置。

#### 【請求項6】

前記プログラミング部は、前記データ格納部に複数の前記データページを第1密度で格納し、前記インデックス格納部に前記生成されたインデックス情報を第2密度で格納し、前記第1密度は前記第2密度よりも大きいことを特徴とする請求項5に記載のメモリプログラミング装置。

#### 【請求項7】

前記プログラミング部は、複数のページプログラミング動作を行って複数の前記データページを前記データ格納部に格納し、前記複数のページプログラミング動作の中に最後のページプログラミング動作が行われる間に前記生成されたインデックス情報を前記インデックス格納部に格納することを特徴とする請求項5に記載のメモリプログラミング装置。

#### 【請求項8】

前記プログラミング部は、複数のページプログラミング動作を行って複数の前記データページを前記データ格納部に格納し、前記複数のページプログラミング動作のそれぞれが行われる間に前記生成されたインデックス情報を前記インデックス格納部に順次に格納することを特徴とする請求項5に記載のメモリプログラミング装置。

#### 【請求項9】

前記プログラミング部は、前記データ格納部には第1検証電圧集合を用いて前記データページを格納し、前記インデックス格納部には第2検証電圧集合を用いて前記インデックス情報を格納することを特徴とする請求項5に記載のメモリプログラミング装置。

#### 【請求項10】

前記プログラミング部は、前記データ格納部および前記インデックス格納部を消去するように構成され、

前記プログラミング部は、前記データ格納部および前記インデックス格納部が消去される前に、前記データ格納部および前記インデックス格納部の中でプログラムされないセルをプリプログラミングすることを特徴とする請求項1に記載のメモリプログラミング装置。

#### 【請求項11】

前記プログラミング部は、複数の閾値電圧の状態の中で前記1つ以上の基準閾値電圧の状態を選択するように構成されることを特徴とする請求項1に記載のメモリプログラミング装置。

10

20

30

40

50

グ装置。

【請求項 1 2】

前記インデックス情報は、前記 1 つ以上の基準閾値電圧の状態それぞれに対応して生成され、前記生成されたインデックス情報それぞれは対応する基準閾値電圧の状態以上の閾値電圧を有する閾値電圧の状態の数をすべて合算することによって生成されることを特徴とする請求項 1 に記載のメモリプログラミング装置。

【請求項 1 3】

前記インデックス格納部は、前記データ格納部が接続されたワード線に接続され、

前記プログラミング部は、前記ワード線に複数の第 1 電圧レベルを印加して前記データ格納部に前記データページをマルチビットプログラミングし、前記ワード線に第 2 電圧レベルを印加して前記インデックス格納部に前記生成されたインデックス情報を前記データページよりも少ないビット数でマルチビットプログラミングし、

前記第 2 電圧レベルは、前記第 1 電圧レベルの中で前記マルチビットプログラミングの最初ページプログラミング動作に対応するように選択されることを特徴とする請求項 3 に記載のメモリプログラミング装置。

【請求項 1 4】

データページから 1 つ以上の基準閾値電圧の状態それぞれの個数を計数してインデックス情報を生成するステップと、

前記データページを格納するステップと、

前記生成されたインデックス情報を格納するステップと、

を含み、

データページのデータの複数の基準閾値電圧の状態の中で 1 つ以上の基準電圧状態を選択するステップと、

を含み、

同時にプログラムされる物理的なマルチビットセルの集合をページといい、1 つのページは 1 つのワード線に接続されたマルチビットセルの集合であり、1 つのページがデータ格納部およびインデックス格納部に分けられていることを特徴とするメモリプログラミング方法。

【請求項 1 5】

前記格納されたデータページを読み出すステップと、

前記読み出したデータページから前記 1 つ以上の基準閾値電圧の状態それぞれの個数を計数して検証情報を生成するステップと、

前記生成された検証情報および前記格納された前記インデックス情報に基づいて、前記読み出したデータページのエラーの有無を判定するステップと、

をさらに含むことを特徴とする請求項 1 4 に記載のメモリプログラミング方法。

【請求項 1 6】

前記格納されたデータページを読み出すステップと、

前記読み出したデータページから前記 1 つ以上の基準閾値電圧の状態それぞれの個数を計数して検証情報を生成するステップと、

前記生成された検証情報および前記格納された前記インデックス情報に基づいて、前記読み出したデータページを格納するセルの閾値電圧の散布変化をモニタリングするステップと、

をさらに含むことを特徴とする請求項 1 4 に記載のメモリプログラミング方法。

【請求項 1 7】

前記生成されたインデックス情報を格納するステップは、前記データページを格納する間に行われる特徴とする請求項 1 4 に記載のメモリプログラミング方法。

【請求項 1 8】

前記生成されたインデックス情報を格納するステップおよび前記データページを格納するステップは、マルチビットデータを格納することを含むことを特徴とする請求項 1 4 に記載のメモリプログラミング方法。

10

20

30

40

50

**【請求項 19】**

請求項 14 の方法を実行するためのプログラムが符号化されて記録されていることを特徴とするコンピュータで読み出し可能な記録媒体。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、メモリ装置にデータをプログラミングする装置および方法に関する。また、マルチレベルセル (Multi-Level Cell, MLC) メモリ装置にデータをマルチレベル (または、マルチビット) プログラミングする装置および方法に関する。

**【背景技術】**

10

**【0002】**

シングルレベルセル (SLC: Single-Level Cell) メモリは、1つのメモリセルに1ビットのデータを格納することができる。SLCメモリは、シングルビットセル (SBC: Single-Bit Cell) メモリとも呼ばれる。SLCメモリは、メモリセルにプログラムされた閾値電圧によって区分される2つの散布 (distribution) に含まれる電圧として1ビットのデータを格納して読み出す。プログラムされた閾値電圧は、SLCメモリの間の微細な電気的な特性の差に応じて一定の範囲の散布を有するようになる。例えば、メモリセルから読み出された電圧が0.5Vよりも大きいか、あるいは1.5Vよりも小さい場合、前記メモリセルに格納されたデータは論理「1」と解釈してもよい。メモリセルから読み出された電圧が2.5Vよりも大きくて3.5Vよりも小さい場合は、前記メモリセルに格納されたデータは論理「0」と解釈してもよい。メモリセルに格納されたデータは、読み出し動作時にセル電流および/または電圧の差によって区分される。

20

**【0003】**

一方、メモリの高集積化の要求に応答して1つのメモリセルに2ビット以上のデータを格納することのできるマルチレベルセル (MLC: Multi-Level Cell) メモリが提案された。MLCメモリは、マルチビットセル (MBC: Multi-Bit Cell) メモリとも呼ばれる。しかし、1つのメモリセルに格納するビットの数が増加するほど信頼性は落ち、読み出しの失敗率は増加するようになる。1つのメモリセルにm個のビットを格納しようとすれば、 $2^m$  個の散布を形成しなければならない (ここで、「m」は実数である)。しかし、メモリの電圧ウィンドウは制限されているため、mが増加することによって隣接したビット間の閾値電圧の差は減少し、これによって読み出しの失敗率が増加する。かかる理由により、従来技術ではMLCメモリを用いた格納密度の向上が容易ではなかった。

30

**【発明の概要】****【発明が解決しようとする課題】****【0004】**

実施形態は、マルチレベルセルメモリに新しいマルチレベル (マルチビット) プログラミング技法を適用することによって、メモリセルに格納されたデータを読み出すときのエラーを最小化することのできるプログラミング装置および方法を提供する。

40

**【0005】**

また、実施形態は、メモリセルに形成された閾値電圧の状態の変化をモニタすることのできるプログラミング装置および方法を提供する。このとき、実施形態は、データ領域に形成された閾値電圧の状態の変化を直接的にモニタリングすることによって、信頼性がより高いモニタリング結果を提供することができる。

**【0006】**

また、実施形態はメモリセルに形成された閾値電圧の状態の変化をモニタリングすることによって、必要なメモリ面積を減少させるプログラミング装置および方法を提供する。

**【0007】**

また、実施形態は、メモリセルに格納されたデータを読み出すときエラーを最小化また

50

は減少することによって、必要なメモリ面積を減少させるプログラミング装置および方法を提供する。

【課題を解決するための手段】

【0008】

一実施形態に係るメモリプログラミング装置は、データ格納部、第1計数部、インデックス格納部および／またはプログラミング部を含む。前記データ格納部は、データページを格納する。第1計数部は、前記データページから1つ以上の基準閾値電圧の状態それぞれの個数を計数してインデックス情報を生成する。インデックス格納部は、前記生成されたインデックス情報を格納する。プログラミング部は、前記データ格納部に前記データページを格納し、前記インデックス格納部に前記生成されたインデックス情報を格納する。前記1計数部は、前記生成されたインデックス情報を前記プログラミング部に伝達する。

10

【0009】

また、本発明の他の実施形態に係るメモリプログラミング方法は、データページに基づいて1つ以上の基準閾値電圧の状態それぞれに含まれたセルの数を計数してインデックス情報を生成するステップ、前記データページを格納するステップおよび／または前記生成されたインデックス情報を格納するステップを含むことを特徴とする。

【図面の簡単な説明】

【0010】

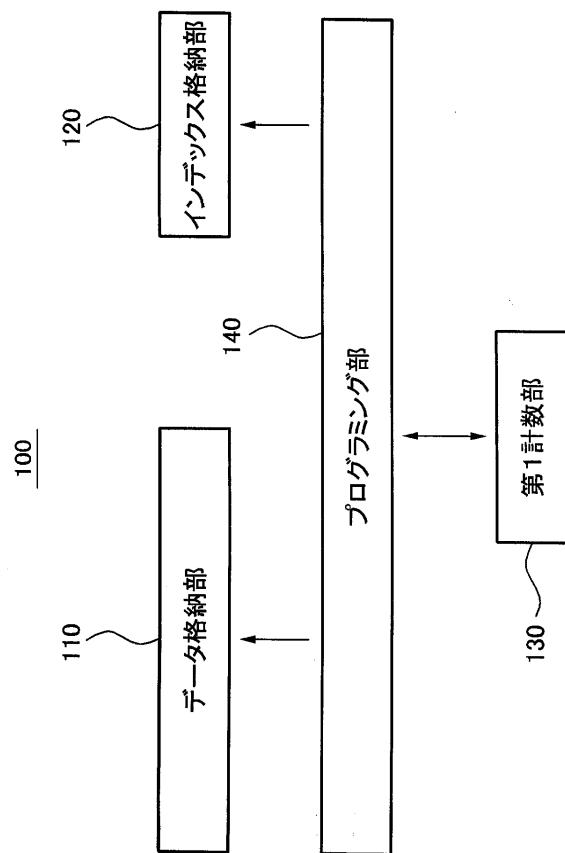

【図1】本発明の一実施形態に係るメモリプログラミング装置を示す図である。

20

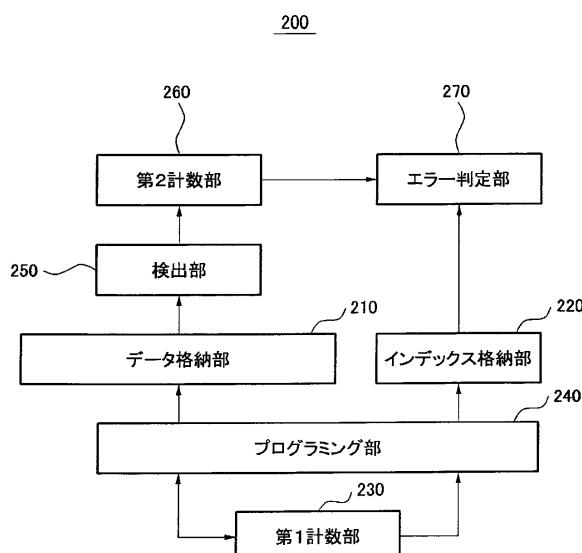

【図2】本発明の他の実施形態に係るメモリプログラミング装置を示す図である。

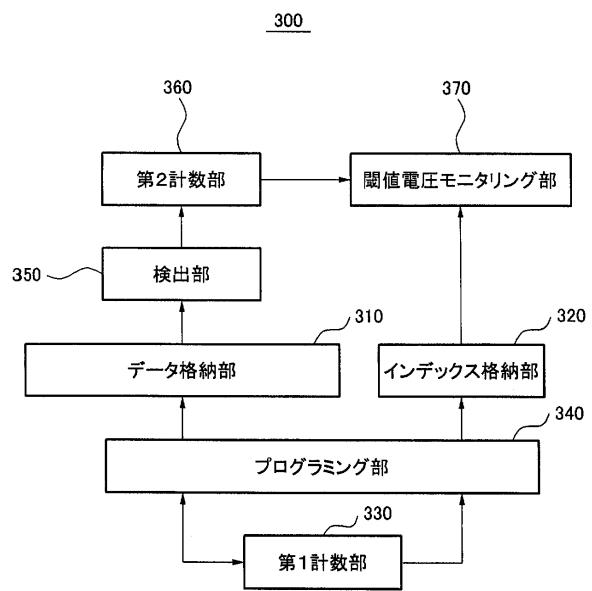

【図3】本発明の更なる実施形態に係るメモリプログラミング装置を示す図である。

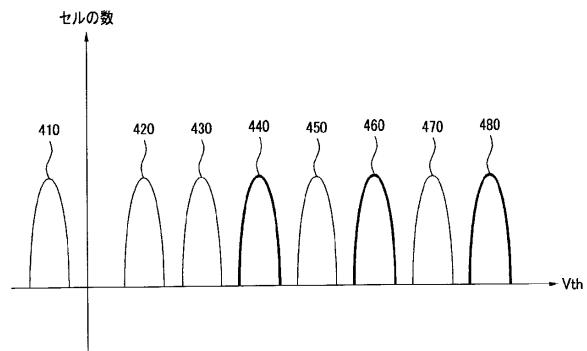

【図4】図1のメモリプログラミング装置によって形成されたデータ格納部の閾値電圧の散布状態の一例を示す図である。

【図5】図3のメモリプログラミング装置によって散布状態の変化をモニタする過程の一例を示す図である。

【図6】図1のメモリプログラミング装置によってデータ格納部の閾値電圧の散布状態が形成される過程の一例を示す図である。

【図7】図1のメモリプログラミング装置によってインデックス格納部にインデックス情報がプログラミングされる過程の一例を示す図である。

【図8】図1のメモリプログラミング装置によってインデックス格納部にインデックス情報がプログラミングされる過程の他の例を示す図である。

30

【図9】図1のメモリプログラミング装置によってインデックス格納部にインデックス情報がプログラミングされる過程の更なる例を示す図である。

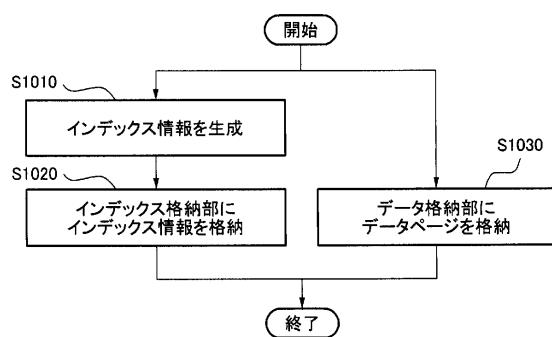

【図10】本発明の一実施形態に係るメモリプログラミング方法を示す動作フローチャートである。

【発明を実施するための形態】

【0011】

以下、本発明に係る好適な実施形態を添付した図面を参照して詳細に説明する。しかし、本発明が実施形態によって制限されたり限定されることはない。各図面に提示された同一の参照符号は同一の部材を示す。

40

【0012】

実施形態のメモリプログラミング方法が適用されるメモリセルは、データフィールドおよびインデックスフィールドに区分される。

【0013】

データフィールドには有効なデータが格納される。インデックスフィールドにはデータフィールドのメモリセルがプログラムされる時、データフィールドのメモリセルの閾値電圧の状態を示すことができる情報が格納される。

【0014】

一般的に不揮発性メモリにおけるプログラミングは、メモリセルの閾値電圧を変化させることによって行われる。メモリセルの閾値電圧はメモリセルに格納されたデータを示す

50

。メモリセルの閾値電圧は、一定の範囲の誤差を有して各状態に対する散布範囲を有する。

【0015】

不揮発性メモリにデータが格納された後、浮遊ゲートにおける電荷損失などのメカニズムによってプログラムされたメモリセルの閾値電圧が変化してもよい。

【0016】

本発明の実施形態は、メモリセルの閾値電圧の変化をモニタするためのメモリプログラミング装置および方法を提供し、メモリセルに格納されたデータのエラーを検証することにおいて、面積のオーバーヘッドを減少または最小化できるメモリプログラミング装置および方法を提供する。

10

【0017】

図1は、本発明の一実施形態に係るメモリプログラミング装置100を示す図である。

【0018】

図1に示すように、メモリプログラミング装置100は、データ格納部110、インデックス格納部120、第1計数部130、およびプログラミング部140を含む。

【0019】

データ格納部110は前記のデータフィールドに対応する構成要素であり、データ格納部110にはデータページが格納される。

【0020】

データ格納部110はデータページにデータをプログラムし、データページは実施形態によれば、1つのワード線に接続されたメモリセルへ同時にプログラムされる格納されたデータの集合を意味する場合もある。

20

【0021】

第1計数部130は、データページから1つ以上の基準閾値電圧の状態のそれぞれの個数を計数してインデックス情報を生成する。

【0022】

インデックス格納部120には生成されたインデックス情報を格納される。

【0023】

プログラミング部140は、データ格納部110にデータページを格納し、インデックス格納部120にインデックス情報を格納する。

30

【0024】

データ格納部110およびインデックス格納部120は、複数のマルチビットセルを含んでもよい。1つのマルチビットセルは、マルチビットデータを格納してもよい。

【0025】

1つのマルチビットセルにデータを格納（プログラム）する過程は、1つのマルチビットセルの閾値電圧を変化させてもよい。1つのマルチビットセルが最大Nビットのデータを格納することができれば（ここで、「N」は実数である）、1つのマルチビットセルに形成されることのできる閾値電圧レベルの数は $2^N$ 個である。

【0026】

データを格納（または、プログラム）する過程は、データを読み出す過程に比べて長い時間を要するため、メモリプログラミング装置100は、物理的に隣接した複数のマルチビットセルを同時にプログラムすることによって、マルチビットセルの全体に対するプログラム時間を短縮することができる。このとき、同時にプログラムされる物理的なマルチビットセルの集合をページといい、1つのページは1つのワード線に接続されたマルチビットセルの集合であってもよい。

40

【0027】

便宜上、1つのページがデータ格納部110およびインデックス格納部120にかけられている場合を仮定し、1つのページの中のデータ格納部110に含まれる領域をメインページ、1つのページの中のインデックス格納部120に含まれる領域をサブページと命名することにする。

50

**【 0 0 2 8 】**

一方、メインページおよびサブページは便宜上に命名されたものであり、この名称により本発明の実施形態によって請求しようとする内容が制限的に解釈されることはない。

**【 0 0 2 9 】**

メインページが最大Nビットを格納することのできるマルチビットセルからなれば、メインページは最大N個のデータページを格納してもよい。

**【 0 0 3 0 】**

プログラミング部140は、1つのメインページにN個のデータページを格納するためにはN個のページプログラミング動作を行ってもよい。各ページプログラミング動作は1つのメインページに1つのデータページを格納する過程であってもよい。

10

**【 0 0 3 1 】**

1つのマルチビットセルは、N回のページプログラミングの動作後に $2^N$ 個の閾値電圧レベルのうちのいずれか1つを有してもよい。数多くのマルチビットセルを含む1つのメインページは、N回のページプログラミングの動作後に $2^N$ 個の閾値電圧レベルを有してもよい。実際には、各マルチビットセルの特性が微細に異なるため、同じデータを格納するマルチビットセルの閾値電圧レベルには差があり得る。このようなマルチビットセルの閾値電圧レベルの差によって、1つのメインページ内のマルチビットセルの閾値電圧は、 $2^N$ 個の散布状態を形成してもよい。

**【 0 0 3 2 】**

実施形態によれば、プログラミング部140は、データページ別にプログラミング動作を行わずに1回のプログラミング動作のシーケンスに応じてマルチビットデータをマルチビットセルに格納してもよい。このとき、プログラミング部140は、プログラミング動作シーケンスを行う間に生成されるインデックス情報をインデックス格納部120に格納してもよい。

20

**【 0 0 3 3 】**

本発明の他の実施形態によれば、プログラミング部140は、データ格納部110にデータページを格納する間にインデックス格納部120にインデックス情報を格納してもよい。

**【 0 0 3 4 】**

本発明の更なる実施形態によれば、プログラミング部140は、データ格納部110のメインページにはN個のデータページを第1密度で格納し、インデックス格納部120のサブページにはインデックス情報を第2密度で格納してもよい。このとき第1密度は、Nビットであり、第2密度はNビットよりも小さい値であってもよい。

30

**【 0 0 3 5 】**

このとき、プログラミング部140は、N回のページプログラミング動作を行ってN個のデータページをデータ格納部110に格納してもよい。プログラミング部140は、N回のページプログラミング動作のうち、最後のページプログラミング動作であるN番目のページプログラミングの動作が行われる間、インデックス情報をインデックス格納部120に格納してもよい。プログラミング部140は、このような方法を用いてインデックス情報を格納過程がデータ格納部110に及ぼす影響を減少または最小化することができる。

40

**【 0 0 3 6 】**

実施形態によれば、プログラミング部140は、1回のプログラミング動作のシーケンスを行ってデータとインデックス情報をそれぞれデータ格納部110およびインデックス格納部120に格納してもよい。このとき、インデックス格納部120は、インデックス情報を格納する過程はデータがデータ格納部110に格納される間に起きててもよい。プログラミング部140は、同じ時間区間にデータおよびインデックス情報を格納することによって、インデックス情報の格納過程がデータ格納部110に及ぼす影響を減少または最小化することができる。このとき、インデックス情報の格納過程は、N回のページプログラミングの動作が行われる場合の最後のページプログラミングの動作と類似するよう行わ

50

れてもよい。

【0037】

本発明の更なる実施形態によれば、プログラミング部140は、N回のページプログラミング動作のそれぞれを行う間にインデックス情報をインデックス格納部120に順次格納してもよい。プログラミング部140は、このような方法を用いてインデックス情報の格納過程においてインデックス格納部120のセルの閾値電圧が急激に変化することを防ぎ、データ格納部110のセルの閾値電圧の変化を減少または最小化することができる。

【0038】

本発明の更なる実施形態によれば、プログラミング部140は、データ格納部110およびインデックス格納部120に同じプログラミングメカニズムを用いてデータページおよびインデックス情報を格納してもよい。しかし、更なる実施形態によれば、プログラミング部140は、データ格納部110には第1プログラミングメカニズムを用いてデータページを格納し、インデックス格納部120には第2プログラミングメカニズムを用いてインデックス情報を格納してもよい。

【0039】

プログラミング部140は、データ格納部110には第1検証電圧集合を用いてデータページを格納し、インデックス格納部120には第2検証電圧集合を用いてインデックス情報を格納してもよい。

【0040】

本発明の更なる実施形態によれば、プログラミング部140は、消去条件による電圧を印加することによって、データ格納部110およびインデックス格納部120に格納されたすべてのデータを消去してもよい。

【0041】

このとき、プログラミング部140は、データ格納部110およびインデックス格納部120に格納されたデータを消去する前にデータ格納部110およびインデックス格納部120のメモリセルの中でプログラムされないセルを検出してもよい。

【0042】

プログラミング部140は、検出されたプログラムされないセルをプリプログラミングした後、データ格納部110およびインデックス格納部120を消去してもよい。プリプログラミング過程は、検出されたプログラムされないセルを特定の閾値電圧までプログラミングする過程であってもよい。

【0043】

メモリプログラミング装置100は、このようなプリプログラミング過程によってデータ格納部110およびインデックス格納部120内のすべてのメモリセルのプログラム／消去サイクルの数を平滑化してもよい。

【0044】

メモリセルのP/Eサイクルの数は、メモリセルのプログラミング特性および電荷維持特性に影響を及ぼしてもよい。メモリプログラミング装置100は、メモリセルのP/Eサイクルの数を平滑化することによって、メモリセルのプログラミング特性および電荷維持特性を平滑化してもよい。

【0045】

本発明の更なる実施形態に係るメモリプログラミング装置100は、 $2^N$ 個の閾値電圧の状態の中で1つ以上の基準電圧状態を選択する基準選択部(図示せず)をさらに含んでもよい。基準選択部は、データページによってメモリセルそれぞれに形成される閾値電圧の散布状態を参照して基準電圧状態を選択してもよい。または、プログラミング部140は、データページによってメモリセルそれぞれに形成される閾値電圧の散布状態を参照して基準閾値電圧の状態を選択してもよい。

【0046】

例えば、基準選択部は散布状態を高い閾値電圧領域、中間閾値電圧領域、低い閾値電圧領域に分けて各領域から1つずつ基準閾値電圧の状態を選択してもよい。高い閾値電圧領

10

20

30

40

50

域における閾値電圧の変化が重要な環境では、基準選択部は高い閾値電圧領域で複数の基準閾値電圧の状態を選択してもよい。

【0047】

第1計数部130は、データページから基準閾値電圧の状態それが検出される回数に基づいてインデックス情報を生成してもよい。例えば、第1計数部130が3つの基準閾値電圧の状態を用いてインデックス情報を生成すれば、第1計数部130は、データページから第1基準閾値電圧の状態が検出される回数を第1インデックス情報に、第2基準閾値電圧の状態が検出される回数を第2インデックス情報に、第3基準閾値電圧の状態が検出される回数を第3インデックス情報に生成してもよい。

【0048】

本発明の更なる実施形態に係る第1計数部130は、第1基準閾値電圧の状態および第1基準閾値電圧の状態よりも高い閾値電圧を有する閾値電圧の状態の数をすべて合算することによって、第1インデックス情報を生成してもよい。第1計数部130は、第2インデックス情報および第3インデックス情報も同様な方法により生成してもよい。

【0049】

図2は、本発明の更なる実施形態に係るメモリプログラミング装置200を示す図である。

【0050】

図2に示すように、メモリプログラミング装置200は、データ格納部210、インデックス格納部220、第1計数部230、およびプログラミング部240を含み、図1のメモリプログラミング装置100と類似する。メモリプログラミング装置200は、検出部250、第2計数部260、およびエラー判定部270をさらに含む。

【0051】

データ格納部210にはデータページが格納される。

【0052】

第1計数部230は、データページから1つ以上の基準閾値電圧の状態それの個数を計数してインデックス情報を生成する。

【0053】

インデックス格納部220には生成されたインデックス情報を格納される。

【0054】

プログラミング部240は、データ格納部210にデータページを格納し、インデックス格納部220にインデックス情報を格納する。

【0055】

検出部250は、データ格納部210に格納されたデータページを読み出す。

【0056】

第2計数部260は、読み出したデータページから1つ以上の基準閾値電圧の状態それの個数を計数して検証情報を生成する。

【0057】

エラー判定部270は、生成された検証情報およびインデックス格納部220に格納されたインデックス情報に基づいて読み出したデータページのエラーの有無を判定する。

【0058】

図3は、本発明の更なる実施形態に係るメモリプログラミング装置300を示す図である。

【0059】

図3に示すように、メモリプログラミング装置300は、データ格納部310、インデックス格納部320、第1計数部330、およびプログラミング部340を含み、図1のメモリプログラミング装置100と類似する。メモリプログラミング装置300は、検出部350、第2計数部360、および閾値電圧モニタリング部370をさらに含む。

【0060】

データ格納部310にはデータページが格納される。

10

20

30

40

50

## 【0061】

第1計数部330は、データページから1つ以上の基準閾値電圧の状態それぞれの個数を計数してインデックス情報を生成する。

## 【0062】

インデックス格納部320には生成されたインデックス情報を格納される。

## 【0063】

プログラミング部340は、データ格納部310にデータページを格納し、インデックス格納部320にインデックス情報を格納する。

## 【0064】

検出部350は、データ格納部310に格納されたデータページを読み出す。

10

## 【0065】

第2計数部360は、読み出したデータページから1つ以上の基準閾値電圧の状態それぞれの個数を計数して検証情報を生成する。

## 【0066】

閾値電圧モニタリング部370は、生成された検証情報およびインデックス格納部320に格納されたインデックス情報に基づいてデータ格納部310に形成された閾値電圧の散布状態の変化をモニタする。

## 【0067】

図4は、本発明のメモリプログラミング装置100によって形成されたデータ格納部110の閾値電圧の散布状態の一例を示す図である。

20

## 【0068】

図4に示すように、横軸はデータ格納部110のメモリセルの閾値電圧に対応する。図4の縦軸は閾値電圧を有するメモリセルの数に対応する。

## 【0069】

散布状態410は、プログラムされないか、あるいは消去されたメモリセルの閾値電圧の散布を示す。

## 【0070】

散布状態420、430、440、450、460、470、480は、図1のプログラミング部140によってプログラムされたメモリセルの閾値電圧の散布を示す。

30

## 【0071】

図4に示す散布状態410、420、430、440、450、460、470、480は、1つのセルに最大3ビットのデータが格納される可能性があることを示す。

## 【0072】

メモリプログラミング装置100は、データ格納部110のメモリセルそれぞれを散布状態410、420、430、440、450、460、470、480のうちのいずれか1つにマッピングさせることによって、3ビットのデータページを格納する。

## 【0073】

散布状態410はデータ「111」に対応し、散布状態420は「110」に対応する。散布状態430はデータ「100」に対応し、散布状態440は「101」に対応する。散布状態450は「001」に対応し、散布状態460は「000」に対応する。散布状態470は「010」に対応し、散布状態480は「011」に対応する。

40

## 【0074】

第1計数部130は、散布状態440、460、480に対応する閾値電圧の状態を基準閾値電圧の状態として用いる。基準閾値電圧の状態は、予め決定されていてもよく、第1計数部130がプログラミング過程で選択してもよい。

## 【0075】

第1計数部130は、3ビットのデータページ内でデータ「101」が現れる頻度数に応じて第1インデックス情報を生成してもよい。第1インデックス情報は、散布状態440に対応するインデックス情報である。

## 【0076】

50

第1計数部130は、3ビットのデータページ内でデータ「000」が現れる頻度数に応じて第2インデックス情報を生成してもよい。第2インデックス情報は、散布状態460に対応するインデックス情報である。

【0077】

第1計数部130は、3ビットのデータページ内でデータ「011」が現れる頻度数に応じて第3インデックス情報を生成してもよい。第3インデックス情報は、散布状態480に対応するインデックス情報である。

【0078】

本発明の更なる実施形態に係る第1計数部130は、第1インデックス情報を散布状態440、450、460、470、480に対応するインデックス情報に生成し、データ「101」、「001」、「000」、「010」、「011」が現れる頻度数に基づいて生成してもよい。第1計数部130は、第2インデックス情報を散布状態460、470、480に対応するインデックス情報に生成し、データ「000」、「010」、「011」が現れる頻度数に基づいて生成してもよい。

【0079】

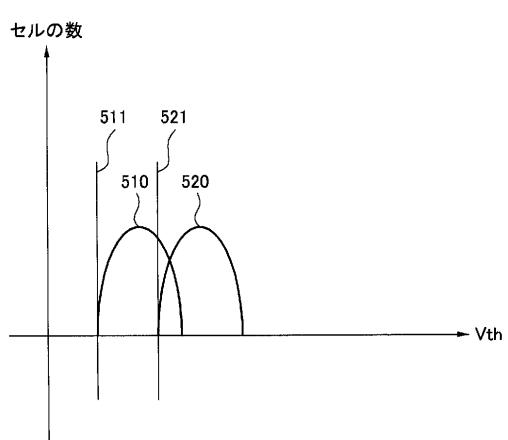

図5は、本発明のメモリプログラミング装置300によって散布状態の変化をモニタする過程の一例を示す図である。

【0080】

図5に示すように、横軸はデータ格納部310のメモリセルの閾値電圧に対応する。図5の縦軸は閾値電圧を有するメモリセルの数に対応する。

【0081】

散布状態520は、プログラムされた直後のメモリセルの閾値電圧の散布状態を示す。

【0082】

散布状態510はプログラムされ、一定の時間が経過した後のメモリセルの閾値電圧の散布状態を示す。

【0083】

散布状態520は、テスト読み出し電圧レベル521によって下位散布状態と区分してもよい。

【0084】

散布状態510は、テスト読み出し電圧レベル511によって下位散布状態と区分してもよい。

【0085】

一般に、不揮発性メモリセルがプログラムされた後、時間が経過すれば浮遊ゲートの電荷が消失する電荷消失によってメモリセルの閾値電圧が変化する傾向が現れる。

【0086】

プログラムされた直後のメモリセルの散布状態は散布状態520にしたがう。時間が経過することによってプログラムされたメモリセルの閾値電圧が減少するため、散布状態520にしたがう一部のメモリセルの閾値電圧は散布状態510にしたがう。このとき、検出部350がテスト読み出し電圧レベル521を用いてデータ格納部310のメモリセルに格納されたデータを読み出せば、散布状態510にしたがうメモリセルの数の一部のみを検出することができる。

【0087】

第2計数部360が生成した検証情報は、散布状態510のメモリセルの数よりも小さい値を含み、インデックス格納部320に格納されたインデックス情報は、散布状態520のメモリセルの数（散布状態510のメモリセルの数と同一）と同一の値を含むため、検証情報がインデックス情報よりも小さい値を示す。

【0088】

閾値電圧モニタリング部370は、検証情報がインデックス情報よりも小さい値を示せば、テスト読み出し電圧レベルを次第に低くし、メモリセルの閾値電圧の変化動向をモニタする。

10

20

30

40

50

## 【0089】

本発明の更なる実施形態に係る閾値電圧モニタリング部370は、検証情報がインデックス情報よりも小さい値を示せば、(インデックス情報 - 検証情報)の値に比例してテスト読み出し電圧レベルを低くし、セルの閾値電圧の変化動向をモニタしてもよい。検証情報がインデックス情報よりも小さい場合、(次のテスト読み出し電圧)レベル = 以下の式 : (現在のテスト読み出し電圧) - (比例常数) X (インデックス情報 - 検証情報)の関係が成り立つ。このような関係によってメモリプログラミング装置300は、最適化されたテスト読み出し電圧レベルを迅速に探すことができる。最適化されたテスト読み出し電圧レベルは、(検証情報 = インデックス情報)条件が成り立つようにするテスト読み出し電圧である。

10

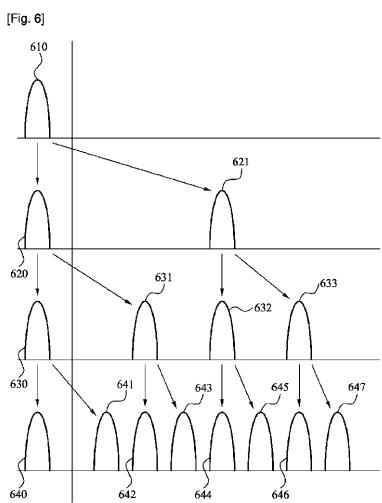

## 【0090】

図6は、本発明のメモリプログラミング装置100によってデータ格納部110の閾値電圧の散布状態が形成される過程の一例を示す図である。

## 【0091】

図6に示すように、横軸はデータ格納部110のメモリセルの閾値電圧に対応する。図6の縦軸は閾値電圧を有するメモリセルの数に対応する。

## 【0092】

図1のプログラミング部140がデータページを格納する前に、データ格納部110のすべてのセルは散布状態610を形成する。

20

## 【0093】

図6において、3ビットのマルチビットデータを1つのメモリセルに格納するページプログラミング過程を示す。

## 【0094】

第1ページプログラミング動作の間プログラミング部140は、データページのMSB (Most Significant Bit)によりメモリセルの閾値電圧を上昇させるか否かを決定する。プログラミング部140は、データ「111」、「110」、「100」、「101」が格納されるメモリセルの閾値電圧をそのまま維持してメモリセルが散布状態620を形成するようとする。プログラミング部140は、データ「001」、「000」、「010」、「011」が格納されるメモリセルの閾値電圧を上昇させてメモリセルが散布状態621を形成するようとする。このような過程を第1ページプログラミング動作という。

30

## 【0095】

第2ページプログラミング動作の間にプログラミング部140は、データページのMSBおよび第2ビットによってメモリセルの閾値電圧を上昇させるか否かを決定する。プログラミング部140は、散布状態620に対応するメモリセルの中でデータ「111」、「110」が格納されるメモリセルの閾値電圧を比較的小さい値だけ高めるか、そのまま維持する。データ「111」、「110」が格納されるメモリセルが散布状態630を形成するようとする。プログラミング部140は、散布状態620に対応するメモリセルの中でデータ「100」、「101」が格納されるメモリセルの閾値電圧を上昇させる。データ「100」、「101」が格納されるメモリセルが散布状態631を形成するようとする。

40

## 【0096】

プログラミング部140は、散布状態621に対応するメモリセルの中でデータ「001」、「000」が格納されるメモリセルの閾値電圧をそのまま維持する。データ「001」、「000」が格納される前記メモリセルが散布状態632を形成するようとする。プログラミング部140は、散布状態621に対応するメモリセルの中でデータ「010」、「011」が格納されるメモリセルの閾値電圧を上昇させる。データ「010」、「011」が格納される前記メモリセルが散布状態633を形成するようとする。このような過程を第2ページプログラミング動作という。

## 【0097】

50

第3ページプログラミングの動作の間にプログラミング部140は、データページのMSB、第2ビットおよびLSB(Least Significant Bit)によってメモリセルの閾値電圧を上昇させるか否かを決定する。

【0098】

プログラミング部140は、散布状態630に対応するメモリセルの中でデータ「111」が格納されるメモリセルの閾値電圧をそのまま維持する。データ「111」が格納される前記メモリセルが散布状態640を形成するようにする。

【0099】

プログラミング部140は、散布状態630に対応するメモリセルの中でデータ「110」が格納されるメモリセルの閾値電圧を上昇させる。データ「110」が格納される前記メモリセルが散布状態641を形成するようにする。

10

【0100】

プログラミング部140は、散布状態631に対応するメモリセルの中でデータ「100」が格納されるメモリセルの閾値電圧を比較的小さい値だけ高めるか、そのまま維持する。データ「100」が格納される前記メモリセルが散布状態642を形成するようにする。

【0101】

プログラミング部140は、散布状態631に対応するメモリセルの中でデータ「101」が格納されるメモリセルの閾値電圧を上昇させる。データ「101」が格納される前記メモリセルが散布状態643を形成するようにする。

20

【0102】

プログラミング部140は、散布状態632に対応するメモリセルの中でデータ「001」が格納されるメモリセルの閾値電圧を比較的小さい値だけ高めるか、そのまま維持する。データ「001」が格納される前記メモリセルが散布状態644を形成するようにする。

【0103】

プログラミング部140は、散布状態632に対応するメモリセルの中でデータ「000」が格納されるメモリセルの閾値電圧を上昇させる。データ「000」が格納される前記メモリセルが散布状態645を形成するようにする。

【0104】

30

プログラミング部140は、散布状態633に対応するメモリセルの中でデータ「010」が格納されるメモリセルの閾値電圧を比較的小さい値だけ高めるか、そのまま維持する。データ「010」が格納される前記メモリセルが散布状態646を形成するようにする。

【0105】

プログラミング部140は、散布状態633に対応するメモリセルの中でデータ「110」が格納されるメモリセルの閾値電圧を上昇させる。データ「110」が格納される前記メモリセルが散布状態647を形成するようにする。このような過程を第3ページプログラミング動作という。

【0106】

40

図7は、本発明のメモリプログラミング装置100によってインデックス格納部120にインデックス情報がプログラミングされる過程の一例を示す図である。

【0107】

図7に示すように、横軸はインデックス格納部120のメモリセルの閾値電圧に対応する。図7の縦軸は閾値電圧を有するメモリセルの数に対応する。

【0108】

プログラミング部140は、インデックス格納部120にインデックス情報を2ビットのデータ密度で格納する。

【0109】

プログラミング部140は、3ビットのデータ密度でインデックス情報を格納すること

50

のできるメモリセルに2ビットのデータにインデックス情報を格納することによって、格納されたインデックス情報の信頼性を高めることができる。

【0110】

プログラミング部140は、データ格納部110に対する第1ページプログラミング動作および第2ページプログラミング動作の間、インデックス格納部120にインデックス情報を格納しない。このとき、第1ページプログラミングを前後にメモリセルの閾値電圧は散布状態710から散布状態720にマッピングされ、実質的には変化しない。同様に、第2ページプログラミングを前後にメモリセルの閾値電圧は散布状態720から散布状態730にマッピングされる。

【0111】

プログラミング部140は、第3ページプログラミング動作の間にインデックス格納部120にインデックス情報を格納する。メモリセルに格納されるインデックス情報が「11」であれば、第3ページプログラミング動作の間のメモリセルの閾値電圧は散布状態740にマッピングされる。このとき、実質的には閾値電圧は変化しない。

【0112】

メモリセルに格納されるインデックス情報が「10」であれば、第3ページプログラミング動作の間のメモリセルの閾値電圧は散布状態742に移動する。インデックス情報が「00」であれば、メモリセルの閾値電圧は散布状態744に移動し、インデックス情報が「01」であれば、メモリセルの閾値電圧は散布状態746に移動する。

【0113】

プログラミング部140は、インデックス情報を格納する過程において別途のプログラミングの過程なしにデータページを格納するプログラミング過程と同じ技法を用いてよい。

【0114】

ページプログラミング動作によって同時にプログラムされるデータ格納部110のメモリページが、例えば、4Ki10Bytesである場合、1つの散布状態当たり必要なインデックス情報の格納空間は15ビットである。インデックス格納部120のメモリセル1つが2ビットのデータ密度でインデックス情報を格納すれば、1つの散布状態当たり8個のメモリセルがインデックス情報を格納するために必要となる。

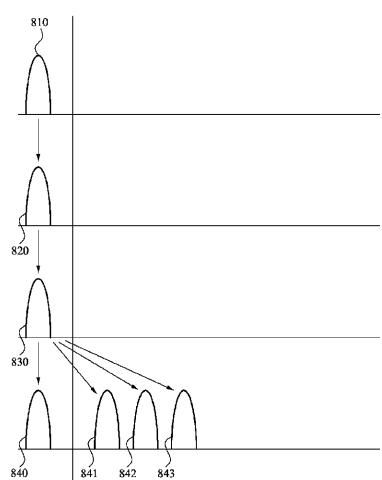

【0115】

図8は、本発明のメモリプログラミング装置100によってインデックス格納部120にインデックス情報がプログラミングされる過程の他の例を示す図である。

【0116】

図8に示すように、横軸はインデックス格納部120のメモリセルの閾値電圧に対応する。図8の縦軸は閾値電圧を有するメモリセルの数に対応する。

【0117】

プログラミング部140は、インデックス格納部120にインデックス情報を2ビットのデータ密度で格納する。

【0118】

プログラミング部140は、3ビットのデータ密度でインデックス情報を格納することのできるメモリセルに2ビットのデータにインデックス情報を格納することによって、格納されたインデックス情報の信頼性を高めることができる。

【0119】

プログラミング部140は、データ格納部110に対する第1ページプログラミング動作および第2ページプログラミング動作の間にはインデックス格納部120にインデックス情報を格納しない。このとき、第1ページプログラミングを前後にメモリセルの閾値電圧は散布状態810から散布状態820にマッピングされ、第2ページプログラミングを前後にメモリセルの閾値電圧は散布状態820から散布状態830にマッピングされる。

【0120】

プログラミング部140は、第3ページプログラミング動作の間にインデックス格納部

10

20

30

40

50

120にインデックス情報を格納する。メモリセルに格納されるインデックス情報が「11」であれば、第3ページプログラミング動作の間にメモリセルの閾値電圧は散布状態840にマッピングされる。このとき、実質的には閾値電圧は変化しない。

【0121】

メモリセルに格納されるインデックス情報が「10」であれば、第3ページプログラミング動作の間にメモリセルの閾値電圧は散布状態841に移動する。インデックス情報が「00」であれば、メモリセルの閾値電圧は散布状態842に移動し、インデックス情報が「01」であれば、メモリセルの閾値電圧は散布状態843に移動する。

【0122】

プログラミング部140は、第3ページプログラミング動作の間にインデックス格納部120のメモリセルの閾値電圧の変化を減らしてもよい。これによって、インデックス格納部120およびデータ格納部110のメモリセルの浮遊ポリシリコンカップリング(floating poly-silicon coupling、FP coupling)のメカニズムによる閾値電圧の所望しない変化を減らすことができる。FPカップリングは、周辺メモリセルの閾値電圧の急激な変化によって、中心メモリセルの閾値電圧が変化する現象をいう。

【0123】

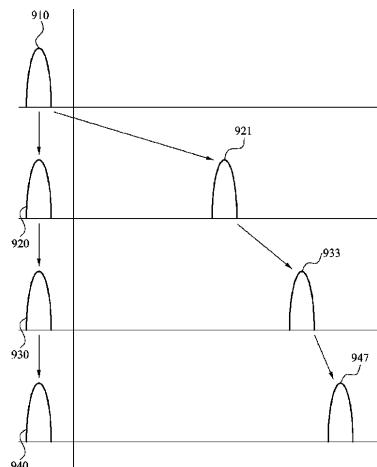

図9は、本発明のメモリプログラミング装置100によってインデックス格納部120にインデックス情報がプログラミングされる過程の更なる例を示す図である。

【0124】

図9に示すように、横軸はインデックス格納部120のメモリセルの閾値電圧に対応する。図9の縦軸は、閾値電圧を有するメモリセルの数に対応する。

【0125】

プログラミング部140は、インデックス格納部120にインデックス情報を2ビットのデータ密度で格納する。

【0126】

プログラミング部140は、3ビットのデータ密度でインデックス情報を格納することができるメモリセルに2ビットのデータにインデックス情報を格納することによって、格納されたインデックス情報の信頼性を高めることができる。

【0127】

プログラミング部140は、3回のページプログラミング動作の間にインデックス情報を順次インデックス格納部120に格納する。

【0128】

インデックス格納部120のメモリセルに格納されるインデックス情報が「11」であれば、プログラミングが行われた後のメモリセルの閾値電圧は散布状態940に対応する。インデックス情報が「10」であれば、プログラミングが行われた後のメモリセルの閾値電圧は散布状態921に対応する。インデックス情報が「00」であれば、プログラミングが行われた後のメモリセルの閾値電圧は散布状態933に対応する。インデックス情報が「01」であれば、プログラミングが行われた後のメモリセルの閾値電圧は散布状態947に対応する。

【0129】

第1ページプログラミング動作の間にプログラミング部140は、インデックス情報「11」を格納するメモリセルの閾値電圧はそのまま維持して散布状態920を形成する。第1ページプログラミング動作の間にプログラミング部140は、インデックス情報「10」、「00」、「01」を格納するメモリセルの閾値電圧を上昇させて散布状態921を形成する。

【0130】

第2ページプログラミング動作の間にプログラミング部140は、インデックス情報「00」、「01」を格納するメモリセルの閾値電圧を上昇させて散布状態933を形成する。このとき、インデックス情報「11」を格納するメモリセルは散布状態930を形成

10

20

30

40

50

し、インデックス情報「10」を格納するメモリセルは散布状態921を形成する。

【0131】

第3ページプログラミング動作の間にプログラミング部140は、インデックス情報「01」を格納するメモリセルの閾値電圧を上昇させて散布状態947を形成する。このとき、インデックス情報「11」を格納するメモリセルは散布状態940を形成し、インデックス情報「10」を格納するメモリセルは散布状態921を形成し、インデックス情報「00」を格納するメモリセルは散布状態933を形成する。

【0132】

プログラミング部140は、インデックス格納部120に対するプログラミングを順次に行うことによって、FPカップリングによる閾値電圧の所望しない変化を分散してもよい。

10

【0133】

図10は、本発明の一実施形態に係るメモリプログラミング方法を示す動作フローチャートである。

【0134】

図10に示すように、メモリプログラミング方法は、データ格納部110に格納されるデータページから1つ以上の基準閾値電圧の状態それぞれの個数を計数してインデックス情報を生成する(S1010)。

【0135】

メモリプログラミング方法は、データ格納部110にデータページを格納する(S1030)。

20

【0136】

メモリプログラミング方法は、インデックス格納部120にインデックス情報を格納する(S1020)。

【0137】

ステップS1020は、ステップS1030が行われる間に行われてもよい。

【0138】

データ格納部110およびインデックス格納部120は、マルチビットセルを含んでもよい。1つのマルチビットセルは、2ビット以上のマルチビットデータを格納してもよい。

30

【0139】

メモリプログラミング方法は、格納されたデータページを読み出してもよい。メモリプログラミング方法は、読み出したデータページから1つ以上の基準閾値電圧の状態それぞれの個数を計数して検証情報を生成することができる。

【0140】

メモリプログラミング方法は、生成された検証情報およびインデックス格納部120に格納されたインデックス情報を基づいて読み出したデータページのエラーの有無を判定することができる。

【0141】

メモリプログラミング方法は、生成された検証情報およびインデックス格納部120に格納されたインデックス情報を基づいてデータ格納部110に形成された散布状態の変化をモニタすることができる。

40

【0142】

本発明に係るメモリプログラミング方法は、コンピュータにより実現される多様な動作を実行するためのプログラム命令を含むコンピュータ読取可能な記録媒体を含む。当該記録媒体は、プログラム命令、データファイル、データ構造などを単独または組み合わせて含むこともでき、記録媒体およびプログラム命令は、本発明の目的のために特別に設計されて構成されたものでもよく、コンピュータソフトウェア分野の技術を有する当業者にとつて公知であり使用可能なものであってもよい。コンピュータ読取可能な記録媒体の例としては、ハードディスク、フロッピー(登録商標)ディスク及び磁気テープのような磁気

50

媒体、CD-ROM、DVDのような光記録媒体、フロプティカルディスクのような磁気-光媒体、およびROM、RAM、フラッシュメモリなどのようなプログラム命令を保存して実行するように特別に構成されたハードウェア装置が含まれる。また、記録媒体は、プログラム命令、データ構造などを保存する信号を送信する搬送波を含む光または金属線、導波管などの送信媒体もある。プログラム命令の例としては、コンパイラによって生成されるような機械語コードだけでなく、インタプリタなどを用いてコンピュータによって実行され得る高級言語コードを含む。上述したハードウェア装置は、本発明の動作を行うため1つ以上のソフトウェアモジュールとして作動するよう構成され、その逆も同様である。

## 【0143】

本発明に係るフラッシュメモリ装置および/または、メモリコントローラは、多様な形態のパッケージを用いて実現されてもよい。例えば、本発明に係るフラッシュメモリ装置および/または、メモリコントローラは、POP(Package on Package)、Ball grid arrays(BGAs)、Chip scale packages(CSPs)、Plastic Leaded Chip Carrier(PLCC)、Plastic Dual In-Line Package(PDIP)、Die in Waffle Pack、Die in Wafer Form、Chip On Board(COB)、Ceramic Dual In-Line Package(CERDIP)、Plastic Metric Quad Flat Pack(MQFP)、Thin Quad Flatpack(TQFP)、Small Outline(SOIC)、Shrink Small Outline Package(SSOP)、Thin Small Outline(TSOP)、Thin Quad Flatpack(TQFP)、System In Package(SIP)、Multi Chip Package(MCP)、Wafer-level Fabricated Package(WFP)、Wafer-Level Processed Stack Package(WSP)、などのようなパッケージを用いて実現されてもよい。

## 【0144】

フラッシュメモリ装置とメモリコントローラはメモリカードを構成してもよい。このような場合、メモリコントローラは、USB、MMC、PCI-E、SATA、PATA、SCSI、ESDI、およびIDEなどのような多様なインターフェースプロトコルの中の1つによって外部(例えば、ホスト)と通信するように構成してもよい。

## 【0145】

フラッシュメモリ装置は、電力が遮断されても格納されたデータを維持することができる不揮発性メモリ装置である。セルラーフォン、PDAデジタルカメラ、ポータブルゲームコンソール、およびMP3Pのようなモバイル装置の使用増加によって、フラッシュメモリ装置はデータストレージだけでなくコードストレージとしてより広く用いられてもよい。フラッシュメモリ装置は、また、HDTV、DVD、ルータ、およびGPSのようなホームアプリケーションに用いられてもよい。

## 【0146】

本発明に係るコンピュータシステムは、バスに電気的に接続されたマイクロプロセッサ、ユーザインターフェース、ベースバンドチップセットなどのモデム、メモリコントローラ、およびフラッシュメモリ装置を含む。フラッシュメモリ装置には、マイクロプロセッサによって処理された/処理されるN-ビットデータ(Nは1または、それよりも大きい整数)がメモリコントローラを介して格納されるであろう。本発明に係るコンピュータシステムがモバイル装置である場合、コンピュータシステムの動作電圧を供給するためのバッテリが追加的に提供されるであろう。

## 【0147】

本発明に係るコンピュータシステムには、応用チップセット、カメライメージプロセッサ(Camera Image Processor: CIS)、モバイルDRAMな

10

20

30

40

50

どがさらに提供され得ることは、この分野の通常の知識を有する者であれば自明である。メモリコントローラとフラッシュメモリ装置は、例えば、データを格納するために不揮発性メモリを用いるSSD (Solid State Drive / Disk) を構成してもよい。

【0148】

上述したように、本発明は、たとえ限定された実施形態と図面によって説明したが、本発明は、上記の実施形態に限定されることなく、本発明が属する分野における通常の知識を有する者であれば、このような基材から多様な修正および変形が可能である。

【0149】

したがって、本発明の範囲は説明された実施形態に限定されて決められてはならず、後述する特許請求の範囲だけでなく、この特許請求の範囲と均等なものなどによって定められなければならない。

【符号の説明】

【0150】

110 データ格納部

120 インデックス格納部

130 第1計数部

140 プログラミング部

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図 8】

[Fig. 8]

【図 9】

[Fig. 9]

【図 10】

---

フロントページの続き

(72)発明者 キョン・レ・チョ

大韓民国・446-712・キョンギ-ド・ヨンイン-シ・ギフン-グ・ノンソ-ドン・サン・1

4-1・サムスン・アドヴァンスド・インスティテュート・オブ・テクノロジー内

(72)発明者 ジュン・ジン・コン

大韓民国・446-712・キョンギ-ド・ヨンイン-シ・ギフン-グ・ノンソ-ドン・サン・1

4-1・サムスン・アドヴァンスド・インスティテュート・オブ・テクノロジー内

(72)発明者 スン・ファン・ソン

大韓民国・446-712・キョンギ-ド・ヨンイン-シ・ギフン-グ・ノンソ-ドン・サン・1

4-1・サムスン・アドヴァンスド・インスティテュート・オブ・テクノロジー内

(72)発明者 ユン・ドン・パク

大韓民国・446-712・キョンギ-ド・ヨンイン-シ・ギフン-グ・ノンソ-ドン・サン・1

4-1・サムスン・アドヴァンスド・インスティテュート・オブ・テクノロジー内

(72)発明者 ジョン・ハン・キム

大韓民国・446-712・キョンギ-ド・ヨンイン-シ・ギフン-グ・ノンソ-ドン・サン・1

4-1・サムスン・アドヴァンスド・インスティテュート・オブ・テクノロジー内

(72)発明者 ジェ・ホン・キム

大韓民国・446-712・キョンギ-ド・ヨンイン-シ・ギフン-グ・ノンソ-ドン・サン・1

4-1・サムスン・アドヴァンスド・インスティテュート・オブ・テクノロジー内

(72)発明者 ヨン・ファン・イ

大韓民国・446-712・キョンギ-ド・ヨンイン-シ・ギフン-グ・ノンソ-ドン・サン・1

4-1・サムスン・アドヴァンスド・インスティテュート・オブ・テクノロジー内

(72)発明者 ヒソク・ウン

大韓民国・446-712・キョンギ-ド・ヨンイン-シ・ギフン-グ・ノンソ-ドン・サン・1

4-1・サムスン・アドヴァンスド・インスティテュート・オブ・テクノロジー内

審査官 菅原 浩二

(56)参考文献 特表2007-510253(JP,A)

特開2006-277785(JP,A)

特開平09-311823(JP,A)

特開2006-1644408(JP,A)

特開2007-048410(JP,A)

特開2009-104729(JP,A)

特開2004-192789(JP,A)

特開2007-193911(JP,A)

特開2009-020996(JP,A)

米国特許出願公開第2008/0002464(US,A1)

特表2005-527062(JP,A)

特開2007-188593(JP,A)

特表2003-536188(JP,A)

特開2000-137999(JP,A)

特開2006-318621(JP,A)

特開2006-134482(JP,A)

特開2000-222890(JP,A)

特開2008-010046(JP,A)

特開2005-100527(JP,A)

特開2007-157234(JP,A)

特表2009-516318(JP,A)

特開2004-014043 (JP, A)

特開2006-294126 (JP, A)

特開2007-042222 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 11 C 16 / 02