(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6773561号

(P6773561)

(45) 発行日 令和2年10月21日(2020.10.21)

(24) 登録日 令和2年10月5日(2020.10.5)

|              |                  |

|--------------|------------------|

| (51) Int.Cl. | F 1              |

| G 11 C 11/22 | (2006.01)        |

| G 11 C 7/06  | (2006.01)        |

| G 11 C 7/10  | (2006.01)        |

|              | G 11 C 11/22 270 |

|              | G 11 C 7/06 120  |

|              | G 11 C 7/10 150  |

請求項の数 19 (全 18 頁)

|                    |                               |                                                                                                          |

|--------------------|-------------------------------|----------------------------------------------------------------------------------------------------------|

| (21) 出願番号          | 特願2016-556945 (P2016-556945)  | (73) 特許権者 390020248                                                                                      |

| (86) (22) 出願日      | 平成27年3月10日 (2015.3.10)        | 日本テキサス・インスツルメンツ合同会社<br>東京都新宿区西新宿六丁目24番1号                                                                 |

| (65) 公表番号          | 特表2017-511950 (P2017-511950A) | (73) 特許権者 507107291                                                                                      |

| (43) 公表日           | 平成29年4月27日 (2017.4.27)        | テキサス インスツルメンツ インコーポ<br>レイテッド<br>アメリカ合衆国 テキサス州 75265<br>-5474 ダラス メイル ステイショ<br>ン 3999 ピーオーボックス 655<br>474 |

| (86) 國際出願番号        | PCT/US2015/019734             | (74) 上記1名の代理人 100098497<br>弁理士 片寄 恒三                                                                     |

| (87) 國際公開番号        | W02015/138469                 |                                                                                                          |

| (87) 國際公開日         | 平成27年9月17日 (2015.9.17)        |                                                                                                          |

| 審査請求日              | 平成30年3月1日 (2018.3.1)          |                                                                                                          |

| (31) 優先権主張番号       | 61/950,351                    |                                                                                                          |

| (32) 優先日           | 平成26年3月10日 (2014.3.10)        |                                                                                                          |

| (33) 優先権主張国・地域又は機関 | 米国(US)                        |                                                                                                          |

| (31) 優先権主張番号       | 14/252,551                    |                                                                                                          |

| (32) 優先日           | 平成26年4月14日 (2014.4.14)        |                                                                                                          |

| (33) 優先権主張国・地域又は機関 | 米国(US)                        |                                                                                                          |

最終頁に続く

(54) 【発明の名称】FRAMメモリにおけるインプリント低減のための回路及び方法

## (57) 【特許請求の範囲】

## 【請求項1】

メモリ装置であって、

第1のビット線に結合される第1のメモリセルと第2のビット線に結合される第2のメモリセルとを含むメモリアレイと、

感知增幅器であって、

第1、第2、第3及び第4のトランジスタであって、前記第1及び第2のトランジスタが前記第3及び第4のトランジスタとクロス結合される構成に配置され、前記第1及び第2のトランジスタが第1の導電型であり、前記第3及び第4のトランジスタが第2の導電型である、前記第1、第2、第3及び第4のトランジスタと、

前記第1及び第3のトランジスタの第1の共通ドレイン端子に結合される入力と前記第1のビット線に結合される出力とを有する第1のインバータであって、第1の制御信号線と第2の制御信号線との間に直列に結合される第5及び第6のトランジスタを含み、前記第5及び第6のトランジスタの一方が前記第1の導電型であり、前記第5及び第6のトランジスタの他方が前記第2の導電型である、前記第1のインバータと、

前記第2及び第4のトランジスタの第2の共通ドレイン端子に結合される入力と前記第2のビット線に結合される出力とを有する第2のインバータであって、前記第1の制御信号線と前記第2の制御信号線との間に直列に結合される第7及び第8のトランジスタを含み、前記第7及び第8のトランジスタの一方が前記第1の導電型であり、前記第7及び第8のトランジスタの他方が前記第2の導電型である、前記第2のインバータと、

10

20

を含む、前記感知増幅器と、

前記第1及び第2のビット線と第1及び第2のデータ線との間にそれぞれ結合される第1及び第2のパストランジスタであって、前記第1及び第2のビット線上的差動電圧を前記第1及び第2のデータ線に印加するように活性化される、前記第1及び第2のパストランジスタと、

を含み、

前記感知増幅器が、

読み出し動作に応答して、前記第1のビット線上の第1のデータ信号と前記第2のビット線上の第2のデータ信号との間の差電圧を増幅し、

前記差電圧の増幅の後に、前記第1のビット線上の前記第1のデータ信号を反転させ、前記第2のビット線上の前記第2のデータ信号を反転させるように、前記第1の制御信号線に供給される基準電圧と前記第2の制御信号線に供給される供給電圧とに応答して前記第1及び第2のインバータを活性化する、

ように構成され、

前記第1及び第2のインバータが前記第1及び第2のパストランジスタの活性化に続いて活性化される、メモリ装置。

#### 【請求項2】

請求項1に記載のメモリ装置であって、

前記第1の導電型がn型であり、前記第2の導電型がp型であり、

前記第1及び第2のトランジスタがnチャネルトランジスタであり、前記第3及び第4のトランジスタがpチャネルトランジスタである、メモリ装置。

#### 【請求項3】

請求項1に記載のメモリ装置であって、

前記第1のビット線と前記第1の共通ドレイン端子との間に結合される第1のスイッチングトランジスタと、

前記第2のビット線と前記第2の共通ドレイン端子との間に結合される第2のスイッチングトランジスタと、

を更に含む、メモリ装置。

#### 【請求項4】

請求項3に記載のメモリ装置であって、

前記第1及び第2のスイッチングトランジスタが第1の導電型である、メモリ装置。

#### 【請求項5】

請求項1に記載のメモリ装置であって、

前記第5のトランジスタのゲート端子と前記第6のトランジスタのゲート端子とが前記第1の共通ドレイン端子に各々結合され、

前記第7のトランジスタのゲート端子と前記第8のトランジスタのゲート端子とが前記第2の共通ドレイン端子に各々結合される、メモリ装置。

#### 【請求項6】

請求項1に記載のメモリ装置であって、

前記読み出し動作の完了の前に、前記反転された第1のデータ信号により示されるデータ状態が前記第1のメモリセルに書き込まれ、前記反転された第2のデータ信号により示されるデータ状態が前記第2のメモリセルに書き込まれる、メモリ装置。

#### 【請求項7】

請求項6に記載のメモリ装置であって、

前記メモリアレイが強誘電体メモリアレイを含む、メモリ装置。

#### 【請求項8】

請求項7に記載のメモリ装置であって、

前記第1及び第2のメモリセルがアクセストランジスタと強誘電体キャパシタとを各々含み、

前記第1及び第2のメモリセルが前記強誘電体メモリアレイの2トランジスタ2キャパ

10

20

30

40

50

シタ ( 2 T - 2 C ) 強誘電体メモリセルの一部である、システム。

【請求項 9】

請求項 8 に記載のメモリ装置であって、

前記 2 T - 2 C 強誘電体メモリセルの各アクセストランジスタに結合される第 1 のワード線と、

前記 2 T - 2 C 強誘電体メモリセルの各強誘電体キャパシタに結合される第 1 のプレート線と、

を更に含む、メモリ装置。

【請求項 10】

請求項 7 に記載のメモリ装置であって、

10

前記第 1 及び第 2 のメモリセルが各々アクセストランジスタと強誘電体キャパシタとを含み、

前記第 1 のメモリセルが前記強誘電体メモリアレイの第 1 の 1 トランジスタ 1 キャパシタ ( 1 T - 1 C ) 強誘電体メモリセルであり、前記第 2 のメモリセルが前記強誘電体メモリアレイの第 2 の 1 T - 1 C 強誘電体メモリセルである、メモリ装置。

【請求項 11】

請求項 10 に記載のメモリ装置であって、

前記第 1 の 1 T - 1 C 強誘電体メモリセルの第 1 のアクセストランジスタに結合される第 1 のワード線と、

前記第 2 の 1 T - 1 C 強誘電体メモリセルの第 2 のアクセストランジスタに結合される第 2 のワード線と、

20

前記第 1 の 1 T - 1 C 強誘電体メモリセルの前記強誘電体キャパシタと前記第 2 の 1 T - 1 C 強誘電体メモリセルの前記強誘電体キャパシタとに結合される第 1 のプレート線と、

、

を更に含む、メモリ装置。

【請求項 12】

請求項 1 に記載のメモリ装置であって、

前記第 1 及び第 2 のビット線が相補ビット線である、メモリ装置。

【請求項 13】

メモリ装置であって、

30

第 1 のビット線に結合される第 1 のメモリセルと第 2 のビット線に結合される第 2 のメモリセルとを含むメモリアレイと、

感知增幅器であって、

第 1 、第 2 、第 3 及び第 4 のトランジスタであって、前記第 1 及び第 2 のトランジスタが前記第 3 及び第 4 のトランジスタとクロス結合される構成に配置され、前記第 1 及び第 2 のトランジスタが第 1 の導電型であり、前記第 3 及び第 4 のトランジスタが第 2 の導電型である、前記第 1 、第 2 、第 3 及び第 4 のトランジスタと、

前記第 1 及び第 3 のトランジスタの第 1 の共通ドレイン端子に結合される入力と前記第 1 のビット線に結合される出力とを有する第 1 のインバータであって、第 1 の制御信号線と第 2 の制御信号線との間に直列に結合される第 5 及び第 6 のトランジスタを含み、前記第 5 及び第 6 のトランジスタの一方が前記第 1 の導電型であり、前記第 5 及び第 6 のトランジスタの他方が前記第 2 の導電型であり、前記第 5 のトランジスタのゲート端子と前記第 6 のトランジスタのゲート端子とが前記第 1 の共通ドレイン端子に各々結合される、前記第 1 のインバータと、

前記第 2 及び第 4 のトランジスタの第 2 の共通ドレイン端子に結合される入力と前記第 2 のビット線に結合される出力とを有する第 2 のインバータであって、前記第 1 の制御信号線と前記第 2 の制御信号線との間に直列に結合される第 7 及び第 8 のトランジスタを含み、前記第 7 及び第 8 のトランジスタの一方が前記第 1 の導電型であり、前記第 7 及び第 8 のトランジスタの他方が前記第 2 の導電型であり、前記第 7 のトランジスタのゲート端子と前記第 8 のトランジスタのゲート端子とが前記第 2 の共通ドレイン端子に各々結合さ

40

50

れる、前記第2のインバータと、

を含む、前記感知増幅器と、

前記第1及び第2のビット線と第1及び第2のデータ線との間にそれぞれ結合される第1及び第2のパストランジスタであって、前記第1及び第2のビット線上の差動電圧を前記第1及び第2のデータ線に印加するように活性化される、前記第1及び第2のパストランジスタと、

を含み、

前記感知増幅器が、

読み出し動作に応答して、前記第1のビット線上の第1のデータ信号と前記第2のビット線上の第2のデータ信号との間の差電圧を増幅し、

前記差電圧の増幅の後に、前記第1のビット線上の前記第1のデータ信号を反転させ、前記第2のビット線上の第2のデータ信号を反転させるように、前記第1の制御信号線に供給される基準電圧と前記第2の制御信号線に供給される供給電圧とに応答して前記第1及び第2のインバータを活性化する、

ように構成され、

前記第1及び第2のインバータが前記第1及び第2のパストランジスタの活性化に続いて活性化される、メモリ装置。

【請求項14】

請求項13に記載のメモリ装置であって、

前記読み出し動作の完了の前に、前記反転された第1のデータ信号によって示されるデータ状態が前記第1のメモリセルに書き込まれ、前記反転された第2のデータ信号によって示されるデータ状態が第2のメモリセルに書き込まれる、メモリ装置。

【請求項15】

請求項13に記載のメモリ装置であって、

前記第1のビット線と前記第1の共通ドレイン端子との間に結合される第1のスイッチングトランジスタと、

前記第2のビット線と前記第2の共通ドレイン端子との間に結合される第2のスイッチングトランジスタと、

を更に含む、メモリ装置。

【請求項16】

請求項13に記載のメモリ装置であって、

前記第5のトランジスタのゲート端子と前記第6のトランジスタのゲート端子とが各々前記第2のトランジスタのゲート端子と前記第4のトランジスタのゲート端子とに結合され、

前記第7のトランジスタのゲート端子と前記第8のトランジスタのゲート端子とが各々前記第1のトランジスタのゲート端子と前記第3のトランジスタのゲート端子とに結合される、メモリ装置。

【請求項17】

電子システムであって、

命令を格納するためのメモリと、

前記メモリによって格納されている命令を実行するためのプロセッサと、

を含み、

前記メモリが、

第1のビット線に結合される第1のメモリセルと第2のビット線に結合される第2のメモリセルとを有するメモリアレイと、

感知増幅器であって、

第1、第2、第3及び第4のトランジスタであって、前記第1及び第2のトランジスタが前記第3及び第4のトランジスタとクロス結合される構成に配置され、前記第1及び第2のトランジスタが第1の導電型であり、前記第3及び第4のトランジスタが第2の導電型である、前記第1、第2、第3及び第4のトランジスタと、

10

20

30

40

50

前記第1及び第3のトランジスタの第1の共通ドレイン端子に結合される入力と前記第1のビット線に結合される出力とを有する第1のインバータであって、第1の制御信号線と第2の制御信号線との間に直列に結合される第5及び第6のトランジスタを含み、前記第5及び第6のトランジスタの一方が前記第1の導電型であり、前記第5及び第6のトランジスタの他方が前記第2の導電型である、前記第1のインバータと、

前記第2及び第4のトランジスタの第2の共通ドレイン端子に結合される入力と前記第2のビット線に結合される出力とを有する第2のインバータであって、前記第1の制御信号線と前記第2の制御信号線との間に直列に結合される第7及び第8のトランジスタを含み、前記第7及び第8のトランジスタの一方が前記第1の導電型であり、前記第7及び第8のトランジスタの他方が前記第2の導電型である、前記第2のインバータと、

を含む、前記感知増幅器と、

前記第1及び第2のビット線と第1及び第2のデータ線との間にそれぞれ結合される第1及び第2のパストランジスタであって、前記第1及び第2のビット線上の差動電圧を前記第1及び第2のデータ線に印加するように活性化される、前記第1及び第2のパストランジスタと、

を含み、

前記感知増幅器が、

読み出し動作に応答して、前記第1のビット線上の第1のデータ信号と前記第2のビット線上の第2のデータ信号との間の差電圧を増幅し、

前記差電圧の増幅の後に、前記第1のビット線上の前記第1のデータ信号を反転させ、前記第2のビット線上の前記第2のデータ信号を反転させるように、前記第1の制御信号線に供給される基準電圧と前記第2の制御信号線に供給される供給電圧とに応答して前記第1及び第2のインバータを活性化する、

ように構成され、

前記第1及び第2のインバータが前記第1及び第2のパストランジスタの活性化に続いて活性化される、電子システム。

#### 【請求項18】

請求項17に記載の電子システムであって、

前記第1のビット線と前記第1の共通ドレイン端子との間に結合される第1のスイッチングトランジスタと、

前記第2のビット線と前記第2の共通ドレイン端子との間に結合される第2のスイッチングトランジスタと、

を更に含む、電子システム。

#### 【請求項19】

請求項17に記載の電子システムであって、

前記第5のトランジスタのゲート端子と前記第6のトランジスタのゲート端子とが各々前記第1の共通ドレイン端子と前記第2のトランジスタのゲート端子と前記第4のトランジスタのゲート端子とに結合され、

前記第7のトランジスタのゲート端子と前記第8のトランジスタのゲート端子とが各々前記第2の共通ドレイン端子と前記第1のトランジスタのゲート端子と前記第3のトランジスタのゲート端子との結合される、電子システム。

#### 【発明の詳細な説明】

##### 【背景技術】

##### 【0001】

電気的に消去可能なプログラマブルリードオンリーメモリ(EEPROM)及びフラッシュEEPROMなどの不揮発性メモリ回路は、コンピュータメモリ、オートモーティブ用途、及びビデオゲームを含む種々の回路用途において、数十年の間広く用いられている。これらの不揮発性メモリ回路の各々が、浮遊ゲート、シリコン窒化物層、プログラム可能な抵抗、又は、動作電圧が取り除かれるときデータ状態を維持するその他の不揮発性メモリ要素など、少なくとも一つの不揮発性メモリ要素を有する。しかし、新たな用途

10

20

30

40

50

の多くが、以前の世代の不揮発性メモリのアクセス時間及びパッキング密度や、バッテリー給電回路のための低電力消費を要する。このような低電力用途に特に魅力的な不揮発性メモリ技術の一つは、不揮発性メモリ要素に強誘電性キャパシタを用いる強誘電性メモリセルである。これらの強誘電性メモリセルの主な利点は、それらが書き込みオペレーションのために必要とするエネルギーが、以前の世代の浮遊ゲートメモリより約3桁小さいという点である。また、それらは浮遊ゲート上にストアされた電荷をプログラム及び消去するため高電圧電力供給を必要としない。そのため、回路複雑性が低減され、信頼性が向上する。

#### 【0002】

強誘電性 (ferroelectric) という用語には若干誤りがある。というのは、最近の強誘電性キャパシタは、鉄の (ferrous) 材料を含んでいないからである。典型的な強誘電性キャパシタは、2つの近接配置された導電性プレート間に形成される強誘電性材料の誘電体を含む。強誘電性材料の確立されたファミリの一つは、ペロブスカイトとして知られており、一般式  $ABO_3$  を有する。このファミリは、式  $Pb(Zr_xTi_{1-x})O_3$  を有するジルコン酸チタン酸鉛 (PZT) を含む。この材料は、適切な電界が格子の中心原子を置換し得る望ましい特性を備えた誘電体である。チタン又はジルコニウムであるこの置換された中心原子は、電界が取り除かれた後置換されたままであり、それにより、実効電荷 (net charge) をストアする。強誘電性材料の別のファミリは、式  $SBBi_2Ta_2O_9$  を有するストロンチウムチタン酸ビスマス (SBT) である。SBTはPZTと比べて幾つかの利点を有する。いずれの強誘電性材料からつくられたメモリも破壊的読み出しオペレーションを有する。従って、メモリセルを読み出す行為は、ストアされたデータを破壊し、そのため、それは、読み出しオペレーションが終了する前に再書き込みされる必要がある。

10

#### 【0003】

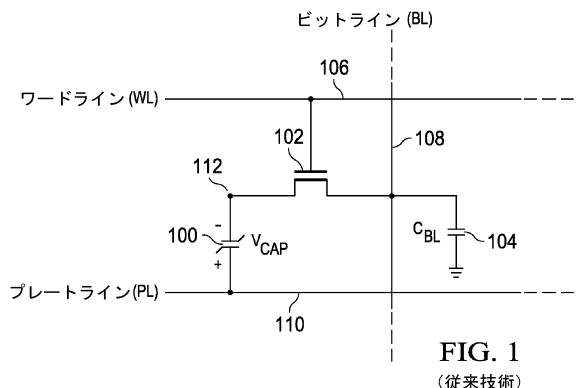

図1は、従来の1トランジスタ1キャパシタ (1T1C) 強誘電性メモリセルを示す。この強誘電性メモリセルは、強誘電性キャパシタ100を除くと、1T1Cダイナミックランダムアクセスメモリ (DRAM) セルに類似する。強誘電性キャパシタ100は、プレートライン110とストレージノード112との間に接続される。アクセストランジスタ102が、ビットライン108とストレージノード112との間に接続される電流経路を有する。アクセストランジスタ102の制御ゲートが、データを読み出すこと及びデータを強誘電性メモリセルに書き込むことを制御するようにワードライン106に接続される。このデータは、セル電圧  $V_{CAp}$  に対応する分極された電荷としてストアされる。ビットラインBLの静電容量は、キャパシタ  $C_{BL}104$  によって表される。

20

#### 【0004】

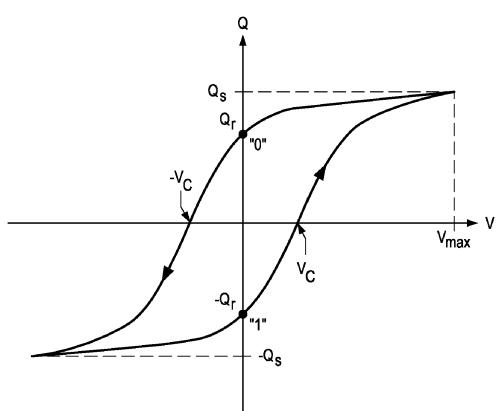

図2において、ヒステリシス曲線が強誘電性キャパシタ100に対応する。ヒステリシス曲線は、縦軸に沿った実効電荷  $Q$  又は分極、及び横軸に沿った印加される電圧を含む。慣例によって、強誘電性キャパシタ電圧の極性は図1に示すように定義される。従って、ストアされる「0」は、アクセストランジスタ端子に関しては、プレートライン端子における正の電圧により特徴付けられる。ストアされる「1」は、アクセストランジスタ端子に関しては、プレートライン端子における負の電圧により特徴付けられる。強誘電性キャパシタに電圧  $V_{max}$  を印加することによって、「0」が書き込みオペレーションにストアされる。これは、飽和電荷  $Q_s$  を強誘電性キャパシタにストアする。しかし、強誘電性キャパシタは、スイッチング構成要素と並列に線形構成要素を含む。従って、電界が取り除かれるとき、線形構成要素は放電するが、残存電荷  $Q_r$  がスイッチング構成要素に残る。ストアされた「0」は、強誘電性キャパシタに  $-V_{max}$  を印加することによって「1」として再書き込みされる。これは、強誘電性キャパシタの線形及びスイッチング構成要素を  $-Q_s$  の飽和電荷まで充電する。ストアされた電荷は、強誘電性キャパシタの電圧が取り除かれたとき、 $-Q_r$  まで戻る。抗電ポイント (coercive points)  $V_c$  及び  $-V_c$  は、ストアされたデータ状態を劣化させ得るヒステリシス曲線上の最小電圧である。例えば、 $V_c$  の強誘電性キャパシタへの印加は、「0」をストアするために充分ではない場合でも

30

40

50

ストアされた「1」を劣化し得る。そのため、強誘電性キャパシタがアクセスされていない限り、これらの抗電ポイント近辺の電圧を避けることが特に重要である。また、強誘電性キャパシタの電力サプライ電圧は、データ損失を避けるためスタンバイ又はスリープモードの間これらの抗電電圧を超える必要がある。

#### 【0005】

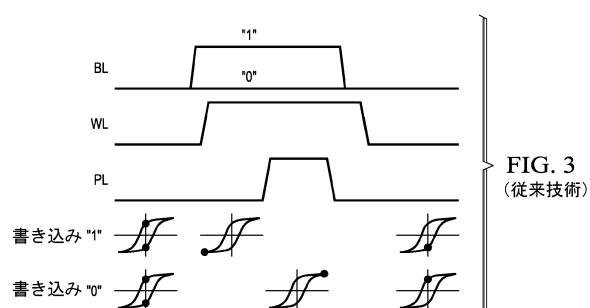

図3は、図1にあるような強誘電性メモリセルのための典型的な書き込みシーケンスを示す。初期的に、ビットライン(BL)、ワードライン(WL)、及びプレートライン(PL)は、全て低である。ヒステリシス曲線の上側ローは、書き込み「1」を図示し、下側ローは書き込み「0」を表す。「1」又は「0」が初期的に各例示のメモリセルにストアされる。ビットラインBL及びワードラインWLが高であり、プレートラインPLが低であるとき、書き込み「1」が実施される。これは、強誘電性キャパシタに負の電圧を印加し、それを $-Q_s$ まで充電する。プレートラインPLが高に向かうとき、強誘電性キャパシタの電圧は0Vであり、ストアされた電荷が $-Q_r$ に戻る。書き込みサイクルの終わりに、ビットラインBL及びプレートラインPL両方が低に向かい、ストアされた電荷 $-Q_r$ が強誘電性キャパシタに残る。代替として、書き込み「0」は、ビットラインBLが低のままでありプレートラインPLが高に向かうとき起こる。これは、強誘電性キャパシタに正の電圧を印加し、それを、ストアされた「0」を表す $Q_s$ まで充電する。プレートラインPLが低に向かうとき、強誘電性キャパシタの電圧は0Vであり、ストアされた電荷は、ストアされた「0」を表す $Q_r$ に戻る。

#### 【0006】

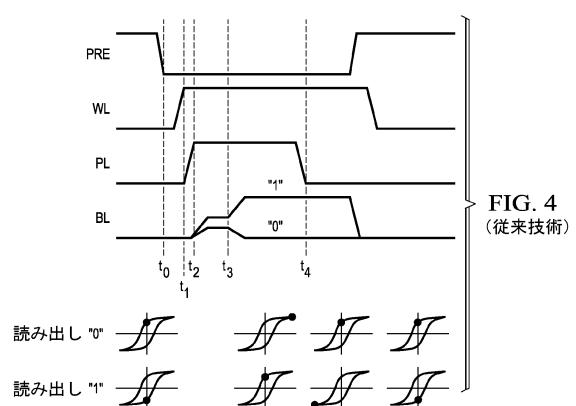

図1における強誘電性メモリセルのための読み出しオペレーションが図4に図示されている。ヒステリシス曲線の上側ローは、読み出し「0」を図示する。ヒステリシス曲線の下側ローは、読み出し「1」を図示する。ワードラインWL及びプレートラインPLは初期的に低である。ビットラインBLは低にプリチャージされる。時間 $t_0$ で、ビットラインプリチャージ信号PREが低に向かい、ビットラインBLを浮遊させる。時間 $t_1$ にワードラインWLが高に向かう。時間 $t_2$ に、プレートラインPLが高に向かう。これは、各メモリセルにそれぞれのビットラインと電荷を共有させ得る。ストアされた「1」が、一層多くの電荷を寄生ビットライン静電容量 $C_{BL}$ と共有し得、時間 $t_3$ において図示するように、ストアされた「0」より大きなビットライン電圧を生成し得る。基準電圧(図示せず)が、アクセスされたビットラインの各相補ビットラインにおいて生成される。この基準電圧は、「1」及び「0」電圧間にある。アクセスされたビットラインと相補ビットラインとの間の差電圧を増幅するため時間 $t_3$ に感知増幅器がアクティブにされる。それぞれのビットライン電圧がフルに増幅されるとき、読み出し「0」曲線セル電荷は $Q_r$ から $Q_s$ まで増大されている。比較のため、読み出し「1」データ状態は、ストアされた「1」からストアされた「0」まで変更されている。そのため、読み出し「0」オペレーションは非破壊的であるが、読み出し「1」オペレーションは破壊的である。時間 $t_4$ において、プレートラインPLが低に向かい、読み出し「1」セルに $-V_{max}$ を印加し、それにより $-Q_s$ をストアする。同時に、ゼロ電圧が読み出し「0」セルに印加され、電荷 $Q_r$ がリストアされる。読み出しサイクルの終わりに、信号PREが高に向かい、両方のビットラインBLをゼロボルト又は接地までプリチャージする。そのため、ゼロボルトが読み出し「1」セルに印加され、 $-Q_r$ がリストアされる。

#### 【0007】

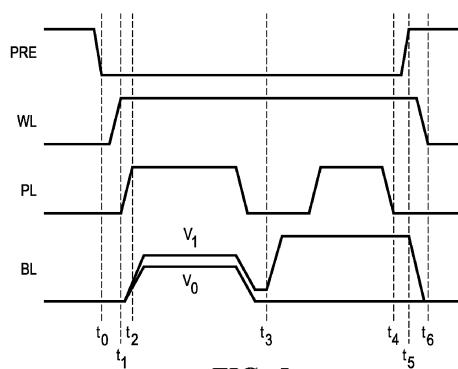

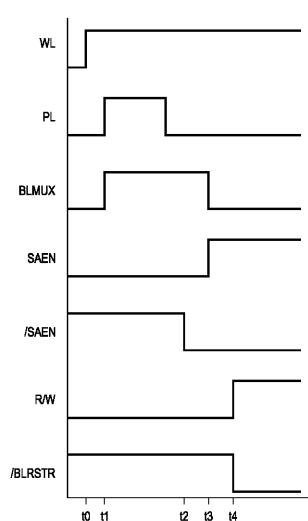

図5を参照すると、強誘電性メモリ回路のためのパルス感知読み出しオペレーションが図示されている。読み出しオペレーションは、プリチャージ信号PREが低に向かう時間 $t_0$ で始まり、ビットラインBLを浮遊させる。ワードラインWL及びプレートラインPLは初期的に低であり、ビットラインBLは低にプリチャージされる。時間 $t_1$ に、ワードラインWLが高に向かい、それにより強誘電性キャパシタをそれぞれのビットラインに結合する。その後、時間 $t_2$ にプレートラインPLが高に向かい、それにより各メモリセルにそれぞれのビットラインと電荷を共有させる。強誘電性メモリセルは、それらのそれぞれのビットラインBLと電荷を共有し、それぞれの差電圧をつくる。ここで、 $V_1$ はデ

10

20

30

40

50

ータ「1」を表し、 $V_0$ はデータ「0」を表す。その後、プレートラインPLは時間 $t_3$ より前に低に向かい、同相差電圧がゼロ近くに向かう。感知するために利用し得る差電圧は、時間 $t_3$ の $V_1$ と $V_0$ の一方と、時間 $t_3$ の $V_1$ と $V_0$ のほぼ中間にある基準電圧(図示せず)との間の差である。差電圧はそれぞれの感知増幅器により時間 $t_3$ に増幅され、フルピットラインBL電圧がつくられる一方、プレートラインPLは低である。そのため、データ「1」セルがフルにリストアされる一方、プレートラインPLは低であり、データ「1」ピットラインBLは高である。その後、プレートラインPLは高に向かい、一方、データ「0」ピットラインBLは低のままである。そのため、データ「0」セルがリストアされる。時間 $t_4$ でプレートラインPLが低に向かい、 $t_5$ でプリチャージ信号PRE時間が高に向かう。プリチャージ信号PREの高レベルは、ピットラインを接地又は $V_{SS}$ までプリチャージする。ワードラインWLは時間 $t_6$ に低に向かい、それにより、強誘電性キャパシタをピットラインから隔離し、パルス感知サイクルが終了する。

## 【0008】

強誘電性メモリの前述の読み出し、書き込み、及びリストアオペレーションの各々は、強誘電性キャパシタ100内の保持された分極ドメインを誘導する。これは特に、 $+/-V_{max}$ で強誘電性キャパシタに最大電界が印加されるときに当てはまる。この現象は、大抵、インプリントと称され、反対のデータ状態を読み出すときメモリセル(図1)信号マージンを劣化させ得る。例えば、「0」がメモリセルに頻繁に書き込まれ、その後「1」の書き込みが続くとき、残存電荷が $Q_r$ (図2)よりも正に残り得、それにより「1」信号マージンを劣化させ得る。同様に、「1」がメモリセルに頻繁に書き込まれ、その後「0」の書き込みが続くとき、残存電荷が $Q_r$ よりも負に残り得、それにより「0」信号マージンを劣化させる。

## 【発明の概要】

## 【0009】

記載される例において、メモリ回路を動作させる方法が、真のデータを複数のビットに書き込むこと、及び第1のデータ状態を、真のデータを示す信号ビットに書き込むことを含む。真のデータは読み出され、相補データが複数のビットに書き込まれる。第2のデータ状態が、相補データを示す信号ビットに書き込まれる。

## 【図面の簡単な説明】

## 【0010】

【図1】従来の強誘電性メモリセルの回路図である。

## 【0011】

【図2】図1の強誘電性キャパシタ100のヒステリシス曲線である。

## 【0012】

【図3】図1の強誘電性メモリセルへの書き込みオペレーションのタイミング図である。

## 【0013】

【図4】図1の強誘電性メモリセルからの読み出しオペレーションのタイミング図である。

。

## 【0014】

【図5】パルス感知読み出しサイクルのタイミング図である。

## 【0015】

【図6A】例示の実施例の1T1C強誘電性メモリセルのコラムの概略図である。

## 【0016】

【図6B】例示の実施例の2T2C強誘電性メモリセルのコラムの概略図である。

## 【0017】

【図7A】図6A及び6Bの強誘電性メモリ回路と共に用いられ得る例示の実施例の反転感知増幅器回路の概略図である。

## 【0018】

【図7B】図7Aの反転感知増幅器回路のオペレーションのタイミング図である。

## 【0019】

10

20

30

40

50

【図 8 A】データワードの条件付き反転を示す、例示の実施例のメモリ回路の概略図である。

【0020】

【図 8 B】図 8 A の回路のオペレーションの真理表である。

【0021】

【図 8 C】例示の実施例のメモリ回路の概略図であり、誤り検出訂正 (ECC) を備えたデータワードの条件付き反転を示す。

【0022】

【図 9】図 8 A 及び 8 C のメモリ回路と共に用いられ得る排他的 OR (XOR) ゲートの概略図である。

10

【0023】

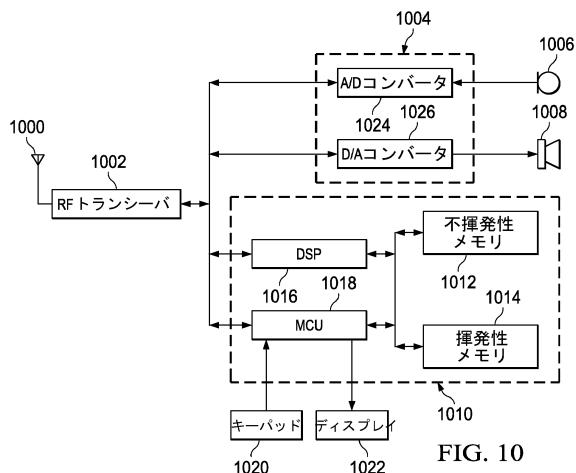

【図 10】例示の実施例を有利に用い得るポータブル電子デバイスの一例としてのワイヤレス電話のブロック図である。

【発明を実施するための形態】

【0024】

例示の実施例は、メモリ回路のインプリント低減において著しい利点を提供する。例示の実施例は、スタティックランダムアクセスメモリ回路、抵抗性ランダムアクセスメモリ回路、磁気ランダムアクセスメモリ回路、又は、バイアスされた信号マージンを複数の非対称読み出し又は書き込みオペレーション後につくり得る任意のその他のメモリ回路など、任意のメモリ回路に適用し得る。

20

【0025】

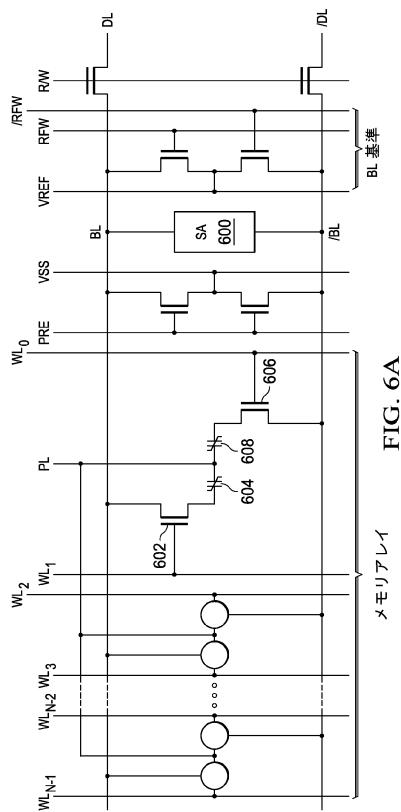

図 6 A は、第 1 の実施例に従った 1 トランジスタ 1 キャパシタ (1T1C) 強誘電性メモリセルのコラムの概略図である。強誘電性メモリアレイは、並列に配されたメモリセルの複数のコラムを含む。強誘電性メモリアレイはまた、N 個の並列ワードライン WL<sub>0</sub> ~ WL<sub>N-1</sub> により画定されるメモリセルの複数のローを含む。メモリセルは、対で配され、隣接するワードライン及び相補ビットライン BL 及び / BL に結合される。例えば、ワードライン WL<sub>0</sub> が、アクセストランジスタ 606 の制御端子に接続される。アクセストランジスタ 606 は、相補ビットライン / BL と強誘電性キャパシタ 608 との間に結合された電流経路を有する。強誘電性キャパシタ 608 は、共通プレートライン端子 PL に結合される。ワードライン WL<sub>1</sub> が、アクセストランジスタ 602 の制御端子に接続される。アクセストランジスタ 602 は、ビットライン BL と強誘電性キャパシタ 604 との間に結合された電流経路を有する。強誘電性キャパシタ 604 もまた、共通プレートライン端子 PL に結合される。コラムは更に、ビットラインプリチャージ回路を含み、ビットラインプリチャージ回路は、プリチャージ信号 PRE の高レベルに応答してビットライン BL 及び / BL を VSS 又は接地までプリチャージするように配された 2 つの n チャネルトランジスタを有する。

30

【0026】

ビットライン基準回路が、読み出しオペレーションの間、ビットライン BL 及び / BL の一方に電圧 VREF を印加するように配される。例えば、ビットライン BL に接続されたメモリセルが選択される場合、相補ビットライン / BL は、制御信号 / RFW の高レベルに応答して基準電圧 VREF を受け取る。同様に、ビットライン / BL に接続されたメモリセルが選択される場合、ビットライン BL は、制御信号 RFW の高レベルに応答して基準電圧 VREF を受け取る。感知增幅器 600 が、制御信号 SAEN 及び / SAEN (図 6 A には図示せず) に応答して読み出しオペレーションの間、ビットライン BL 及び / BL 間の差電圧を増幅する。これらの制御信号は感知增幅器 600 をアクティブにし、感知增幅器 600 は、制御信号 R/W の高レベルに応答して n チャネル読み出し / 書き込みトランジスタを介して、増幅されたデータ信号をデータライン DL 及び / DL に印加する。

40

【0027】

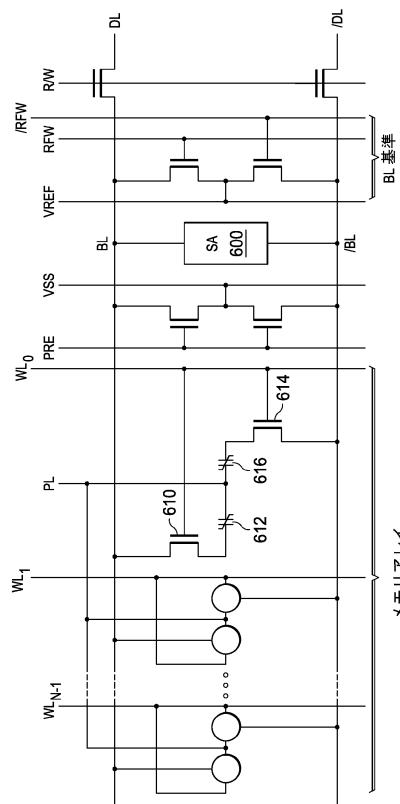

図 6 B は、第 2 の実施例に従った 2 トランジスタ 2 キャパシタ (2T2C) 強誘電性メ

50

モリセルのコラムの概略図である。ここで及び下記説明において、同じ参照番号は実質的に同一の要素を示す。強誘電性メモリアレイが、並列に配されたメモリセルの複数のコラムを含む。強誘電性メモリアレイはまた、N個の並列ワードラインWL<sub>0</sub> ~ WL<sub>N-1</sub>により画定されるメモリセルの複数のローを含む。2T/2Cの実施例において、メモリセルは、対で配され、それぞれのワードライン及び相補ビットラインBL及び/BLに結合される。例えば、ワードラインWL<sub>0</sub>が、アクセストランジスタ610及び614の制御端子に接続される。アクセストランジスタ610は、ビットラインBLと強誘電性キャパシタ612との間に結合された電流経路を有する。アクセストランジスタ614は、相補ビットライン/BLと強誘電性キャパシタ616との間に結合された電流経路を有する。強誘電性キャパシタ612及び616が、共通プレートライン端子PLに結合される。読み出しオペレーションの間、強誘電性キャパシタ612及び616の各々上の電荷が、アクセストランジスタ610及び614を介してそれぞれのビットラインBL及び/BLに印加され、それにより、1T1Cメモリセルよりも大きな信号マージンを提供する。

#### 【0028】

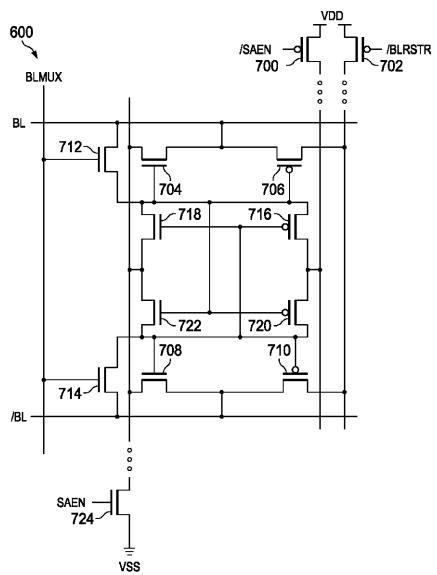

図7Aは、図6A及び図6Bの強誘電性メモリ回路と共に用いられ得る例示の実施例の反転感知增幅器回路600の概略図である。この感知增幅器回路は、Nチャネルトランジスタ718及び722と共にクロス結合構成に配されるPチャネルトランジスタ716及び720を有する感知增幅器を含む。Nチャネル感知增幅器イネーブル(SAEN)トランジスタ724が、Nチャネルトランジスタ718及び722の共通ソース端子と電力サプライ端子VSSとの間に結合される。Pチャネル相補感知增幅器イネーブル(/SAEN)トランジスタ700が、Pチャネルトランジスタ716及び720の共通ソース端子と電力サプライ端子VDDとの間に結合される。Nチャネルスイッチングトランジスタ712が、トランジスタ716及び718の共通ドレイン端子とビットラインBLとの間に結合される。Nチャネルスイッチングトランジスタ714が、トランジスタ708及び710の共通ドレイン端子と相補ビットライン/BLとの間に結合される。スイッチングトランジスタ712及び714は、ビットライン多重化信号BLMUXにより制御される。Pチャネルトランジスタ706及びNチャネルトランジスタ704によって形成される第1のインバータが、トランジスタ716及び718の共通ドレイン端子に結合される入力端子と、ビットラインBLに結合される出力端子とを有する。Pチャネルトランジスタ710及びNチャネルトランジスタ708によって形成される第2のインバータが、トランジスタ720及び722の共通ドレイン端子に結合される入力端子と、相補ビットライン/BLに結合される出力端子とを有する。第1及び第2のインバータは、Nチャネルトランジスタ724及び制御信号SAENと共にPチャネルトランジスタ702及び制御信号/BLRSTRによりイネーブルにされる。

#### 【0029】

図7Aの反転感知增幅器回路600のオペレーションが、図7Bのタイミング図を参照して説明される。初期的に、相補感知增幅器イネーブル信号/SAEN及び相補ビットラインリストア信号/BLRSTRを除いて、図7Bの全ての信号が低である。ビットラインBL及び/BLは、VSSにプリチャージされる。時間t0で、メモリセルのローを選択するためにワードラインWLが高に向かう。ここで、ワードラインWLは、図6A又は図6BのワードラインWL<sub>0</sub> ~ WL<sub>N-1</sub>のうちの任意のワードラインであり得る。時間t1に、選択されたメモリセルからデータを読み出すため、及びビットラインBL及び/BL間の差電圧を生成するために、プレートライン信号PLが高にパルスする。スイッチングトランジスタ712及び714をオンにするためにビットライン多重化信号BLMUXも高に向かい、それにより、ビットラインBL及び/BLを感知增幅器に結合する。時間t2に、差電圧が感知增幅器において充分につくられるときに、Pチャネルトランジスタ700をオンにするため、及び電力サプライVDDからPチャネルトランジスタ716及び720の共通ソース端子へ正の電圧を印加するために、相補感知增幅器イネーブル信号/SAENが低に向かう。この正の電圧は、差電圧の何らかの初期増幅を提供する。時間t3に、スイッチングトランジスタ712及び714をオフにするために制御信号BL

10

20

30

40

50

MUXが低に向かい、それにより、ビットラインBL及び/BLを感知増幅器から隔離する。Nチャネルトランジスタ724をオンにするため、及びトランジスタ704～710によって形成されたインバータをイネーブルするために、感知増幅器イネーブル信号SAE\_Nが高に向かう。Nチャネルトランジスタ724がトランジスタ718及び722の共通ソース端子を電力サプライ端子VSSに結合し、それにより、感知増幅器における差電圧を更に増幅する。時間t4に、増幅された差電圧をデータラインDL及び/DL(図6A又は図6B)に印加するために、読み出し/書き込み信号R/Wが高に向かう。Pチャネルトランジスタ702をオンにするため、及び電力サプライ電圧VDDをPチャネルインバータトランジスタ706及び710の共通ソース端子に印加するために、相補ビットラインリストア信号/BL\_RSTが低に向かう。トランジスタ704～710によって形成されたインバータはその後、選択されたメモリセルに反転データ信号を書き込む。例えば、相補ビットライン/BL(「1」)に対して正の差電圧を生成したビットラインBL上のメモリセルが、相補ビットライン/BL(「0」)に対してビットラインBL上の負の電圧として再書き込みされ得る。これは、トランジスタ704及び706によって形成された第1のインバータが、ビットラインBL上のオリジナルデータ信号を反転させるためである。同様に、トランジスタ708及び710によって形成された第2のインバータが、相補ビットライン/BL上のオリジナルデータ信号を反転させる。

#### 【0030】

反転感知増幅器回路600(図7A)は、幾つかの理由のため非常に有利である。第1に、各メモリセルから読み出されるオリジナルデータ信号が無条件で反対のデータ状態として再書き込みされる。これは、強誘電性キャパシタの分極されたドメインをアーニールすることによりメモリセル内のインプリントを著しく低減する。第2に、差電圧が、充分に増幅され、データラインDL及び/DLに印加されるとすぐに、読み出し/書き込み信号R/Wがアクティブにされるので、反転感知増幅器に速度の不利益がない。第3に、トランジスタ704～710によって形成された感知増幅器は、ビットラインBL及び/BLを直接的にリストアしない。増幅された差電圧は、反転され、それぞれの第1の(704～706)及び第2の(708～710)インバータによりビットラインBL及び/BL上に駆動される。第1及び第2のインバータによるこの付加的なバッファリングが、感知増幅器上の負荷を低減し、そのため、それは、データラインDL及び/DLをより一層容易に駆動する。最後に、ビットライン(BL、/BL)及びデータライン(DL、/DL)の容量性負荷が、それぞれ、インバータ及び感知増幅器間で分けられるので、トランジスタサイズが低減され得、そのため、小さなエリア不利益しか生じない。

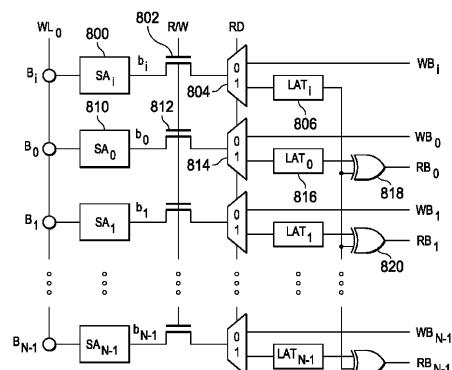

#### 【0031】

図8Aは、例示の実施例のメモリ回路の概略図であり、データワードの条件付き反転を示す。これまでの説明から、反転感知増幅器回路600は無条件に、選択されたメモリセルから読み出されたデータを反転し、反転されたデータを選択されたメモリセルにリストアする。従って、反転感知増幅器からのデータがオリジナルであるか又は反転されたデータであるかの判定に応答して、データは条件付きで反転される。この判定は、信号ビット又は反転ビット(B<sub>i</sub>)によって成される。図8Aのメモリ回路は、ワードラインWL<sub>0</sub>により選択された強誘電性メモリセルB<sub>i</sub>及びB<sub>0</sub>～B<sub>N-1</sub>のローを含む。各強誘電性メモリセルからのデータは、それぞれの感知増幅器により読み出しオペレーションの間増幅される。例えば、信号ビットB<sub>i</sub>が、増幅された信号ビットb<sub>i</sub>を生成するために反転感知増幅器回路800により増幅される。信号ビットb<sub>i</sub>は、読み出し/書き込み(R/W)トランジスタ802を介して多重化回路804に印加される。多重化回路804はその後、制御信号RDの高レベル(「1」)に応答して、それぞれのデータラインからの信号ビットb<sub>i</sub>をラッチ回路806に印加する。ラッチ回路806は、信号ビットb<sub>i</sub>をラッチし、それをXORゲート818及び820などのデータコラムに対応する各排他的OR(XOR)ゲートの一つの端子に印加する。代替として、書き込みオペレーションの間、制御信号RDの低レベルに応答して、書き込み信号ビットWB<sub>i</sub>が多重化回路804を介して、読み出し/書き込みトランジスタ802、感知増幅器回路800、及びそれ

10

20

30

40

50

のビットライン B\_L 又は /B\_L に印加される。

【 0 0 3 2 】

ローの他の強誘電性メモリセルからのデータ信号は同様の方式で動作する。例えば、データビット  $B_0$  が、増幅されたデータビット  $b_0$  を生成するために反転感知増幅器回路 810 により増幅される。データビット  $b_0$  が、読み出し / 書き込み (R / W) トランジスタ 812 を介して多重化回路 814 に印加される。多重化回路 814 はその後、制御信号 RD の高レベル (「1」) に応答して、それぞれのビットラインからのデータビット  $b_0$  をラッチ回路 816 へ印加する。ラッチ回路 816 は、データビット  $b_0$  をラッチし、それを XOR ゲート 818 の一つの端子に印加する。代替として、書き込みオペレーションの間、制御信号 RD の低レベルに応答して、書き込みデータビット WB\_0 が多重化回路 814 を介して、読み出し / 書き込みトランジスタ 812、感知増幅器回路 810、及びそれぞれのビットライン B\_L 又は /B\_L に印加される。

【 0 0 3 3 】

図 8 A のメモリ回路のオペレーションが、図 8 B の真理表を参照して説明される。真理表の左コラムは、READ 又は WRITE オペレーションなど、前の論理オペレーションを示す。真理表の各ローは、論理オペレーション後の図 8 A において識別された信号の論理値を示す。特に、第 1 のローは、第 1 の書き込み後の初期値を示す。信号ビット  $B_i$  は 0 であり、それぞれ、データビット  $B_0$  及び  $B_1$  は 01 である。信号ビット  $b_i$ 、増幅されたデータビット  $b_0$  及び  $b_1$ 、及び読み出しビット  $RB_0$  及び  $RB_1$  は、「X」で示すように「ドゥーナットケア (do not care)」値である。第 2 のローにおける第 1 の読み出しオペレーションの後、それぞれ、信号ビット  $b_i$ 、増幅されたデータビット  $b_0$  及び  $b_1$ 、及び読み出しビット  $RB_0$  及び  $RB_1$  は、00101 である。信号ビット  $b_i$  は、第 1 のローにおける初期書き込みオペレーション後のメモリセル信号ビット  $B_i$  と同じ値を有する。信号ビット  $b_i$  の 0 値は、増幅されたデータビット  $b_0$  及び  $b_1$  (01) が反転されるべきではないことを示す。増幅されたデータビット  $b_0$  及び  $b_1$  (01) との 0 信号ビット  $b_i$  の XOR が、それぞれの XOR ゲート 818 及び 820 において 01 出力を生成する。そのため、読み出しビット  $RB_0$  及び  $RB_1$  はそれぞれ 01 である。第 2 のローにおけるメモリセル信号ビット  $B_i$  及びメモリセルデータビット  $B_0$  及び  $B_1$  は各々、上述したようにそれぞれの反転感知増幅器により反転状態 (110) で再書き込みされる。

【 0 0 3 4 】

第 3 のローにおける第 2 の読み出しオペレーションの後、それぞれ、信号ビット  $b_i$ 、増幅されたデータビット  $b_0$  及び  $b_1$ 、及び読み出しビット  $RB_0$  及び  $RB_1$  は、11001 である。信号ビット  $b_i$  及び増幅されたデータビット  $b_0$  及び  $b_1$  は、第 2 のローにおけるメモリセル信号ビット  $B_i$  及びメモリセルデータビット  $B_0$  及び  $B_1$  と同じ値を有する。これらは第 1 のロー (001) のオリジナル書き込みデータからの反転されたデータ状態である。信号ビット  $b_i$  の 1 値は、増幅されたデータビット  $b_0$  及び  $b_1$  (10) が反転される必要があることを示す。増幅されたデータビット  $b_0$  及び  $b_1$  (10) との 1 信号ビット  $b_i$  の XOR が、それぞれの XOR ゲート 818 及び 820 において 01 出力を生成する。そのため、読み出しビット  $RB_0$  及び  $RB_1$  はそれぞれ 01 である。メモリセル信号ビット  $B_i$  及びメモリセルデータビット  $B_0$  及び  $B_1$  は各々、上述したようにそれぞれの反転感知増幅器により反転状態 (001) で再書き込みされる。

【 0 0 3 5 】

第 3 及び第 4 の読み出しオペレーションは、上述したものと同じである。各ローにおいて、読み出しデータビット  $RB_0$  及び  $RB_1$  は、第 1 のローにおいてメモリセルデータビットに元々書き込まれたように 01 である。各偶数読み出しオペレーションは、オリジナルデータ (001) をメモリセル信号及びデータビットに再書き込みする。しかし、各奇数読み出しは、反転されたデータ (110) をメモリセル信号及びデータビットに再書き込みする。上述のように、これは幾つかの理由で非常に有利である。第 1 に、各メモリセルから読み出されるオリジナルデータ信号は、反対のデータ状態として無条件で再書き込

みされる。これは、強誘電性キャパシタの分極されたドメインをアニールすることによりメモリセル内のインプリントを著しく低減する。第2に、読み出し経路において著しい速度の不利益がない。これは、XORゲートが、読み出しデータ経路における増幅されたデータビット  $b_0$  及び  $b_1$  をバッファするためにも用いられるためである。差電圧が、充分に増幅され、付加的なゲート遅延なしにデータライン D\_L 及び / D\_L に印加されるとすぐに、読み出し / 書き込み信号 R / W がアクティブにされる。第3に、読み出し及び書き込みデータ間で区別するために多重化回路が必要とされるので、書き込みデータ経路は影響を受けない。最後に、反転感知増幅器回路 600 及び 818 ~ 820 などの XOR ゲートの最小の付加的回路複雑性で実装が達成される。

【0036】

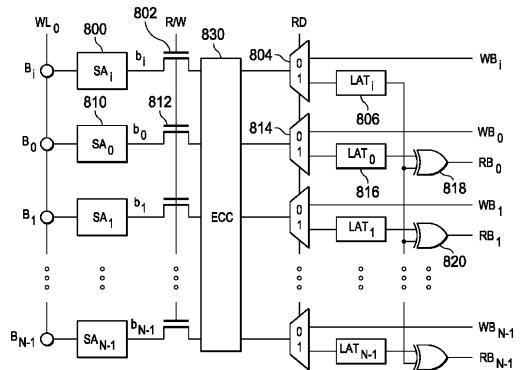

10

図 8C は、例示の実施例のメモリ回路の概略図であり、誤り検出訂正又は誤り補正符号 (ECC) を備えたデータワードの条件付き反転を示す。この回路は、読み出し / 書き込みトランジスタ (802 及び 812 など) と多重化回路 (804 及び 814 など) との間に ECC 回路 830 が付加されることを除き、図 8A の回路に類似する。ECC 回路は、1950 年にリチャード・ハミングによって考案されたシングル誤り訂正ダブル誤り検出 (SECDED) ハミング符号を用い得る。ハミング符号は、パリティビットをデータビットに付加し、ダブルビット誤りを検出するため、及びシングルビット誤りを補正するために有効である。ECC 回路 830 は、好ましくは、所望のワードサイズに対応する符号を含む。各有効コードワード C に対し、反転データワードを備えた SECDED のために、有効反転コードワード~C が用いられ得る。ここで、有効コードワードは、データワード上の SECDED など、特定の誤り検出及び補正オペレーションを行なうものである。

【0037】

20

他の符号は、当業界で既知であるように、コードワード C 及び~C 両方が有効であるという特性を満足させる限り、SECDED を実施するために ECC 回路において用い得る。また、ダブル誤り補正及びトリプル誤り検出 (DECDED) など、シングルデータワードにおいて複数のビット誤りを補正するために ECC 回路 830 において BCH 符号などの巡回誤り補正符号が用いられ得る。BCH 符号は、1959 年にアレクシス・オッカングム (Alexis Hocquenghem) が最初に考案し、その後それとは別に、1960 年にラージ・ボース (Raj Bose) 及びディー・ケイ・レイ・チョードリ (D. K. Ray-Chaudhuri) が考案した。BCH という符号名は考案者のイニシャルに由来する。BCH 符号は、当業界で既知であり、衛星通信、コンパクトディスクプレーヤ、DVD、ディスクドライブ、ソリッドステートドライブ、及び 2 次元バーコードにおいて用いられる。

【0038】

30

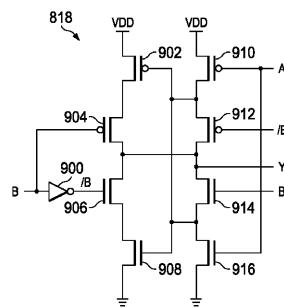

図 9 は、図 8A 及び図 8C のメモリ回路と共に用いられ得る排他的 OR (XOR) ゲート 818 の概略図である。ここで、A 及び B は、2 つの XOR 入力信号であり、Y は出力信号である。XOR ゲートは、直列接続されるトランジスタ 902 ~ 908 によって形成される左ブランチ、及び直列接続されるトランジスタ 910 ~ 916 によって形成される右ブランチを含む。インバータ 900 が、B 入力信号を受け取り、相補入力信号 / B を生成する。オペレーションにおいて、入力信号 B が高であるとき、トランジスタ 904 及び 906 は、いずれもオフであり、左ブランチをディセーブルする。B の高状態及び / B の対応する低状態は、それぞれ、N チャネルトランジスタ 914 及び P チャネルトランジスタ 912 をオンにする。右ブランチはその後、入力信号 A を有するシンプルなインバータとして動作する。そのため、B が高であるとき、Y は A の反転である。代替として、B が低であり、/ B が高であるとき、トランジスタ 912 及び 914 は、いずれもオフであり、右ブランチをディセーブルする。B の低状態及び / B の対応する高状態は、それぞれ、P チャネルトランジスタ 904 及び N チャネルトランジスタ 906 をオンにする。トランジスタ 910 及び 916 は、トランジスタ 902 及び 908 の制御ゲートにおいて相補信号 / A を生成するように第 1 のインバータとして動作する。トランジスタ 902 及び 908 はその後、入力信号 / A を有するシンプルなインバータとして動作する。そのため、B が低であるとき Y が A に等しい。

40

50

## 【0039】

図10は、不揮発性メモリアレイにおいて例示の実施例を有利に利用し得るポータブル電子デバイスの一例としてのワイヤレス電話のブロック図である。ワイヤレス電話は、アンテナ1000、無線周波数トランシーバ1002、ベースバンド回路1010、マイクロホン1006、スピーカー1008、キーパッド1020、及びディスプレイ1022を含む。ワイヤレス電話は、当業界で既知の再充電可能なバッテリー(図示せず)により電力供給されることが好ましい。アンテナ1000は、ワイヤレス電話に、当業界で既知の方式でワイヤレス電話通信のため無線周波数環境と相互作用させ得る。無線周波数トランシーバ1002は、アンテナ1000を介して無線周波数信号を送信及び受信する。送信された信号は、ベースバンド回路1010から受信された音声/データ出力信号により変調される。受信された信号は、復調され、音声/データ入力信号としてベースバンド回路1010に提供される。アナログ部1004が、アナログ音声信号を受け取るためにマイクロホン1006に接続されるアナログデジタルコンバータ1024を含む。アナログデジタルコンバータ1024は、これらのアナログ音声信号をデジタルデータに変換し、それらをデジタルシグナルプロセッサ1016に印加する。アナログ部1004はまた、スピーカー1008に接続されるデジタルアナログコンバータ1026を含む。スピーカー1008は、音声出力をユーザーに提供する。デジタル部1010は、一つ又は複数の集積回路において具現化され、マイクロコントローラユニット1018、デジタルシグナルプロセッサ1016、不揮発性メモリ回路1012、及び揮発性メモリ回路1014を含む。不揮発性メモリ回路1012は、読み出し専用メモリ(ROM)、強誘電性メモリ(FRAM又はFRAM)、フラッシュメモリ、又は当業界で既知のその他の不揮発性メモリを含み得る。揮発性メモリ回路1014は、ダイナミックランダムアクセスメモリ(DRAM)、スタティックランダムアクセスメモリ(SRAM)、又は当業界で既知のその他の揮発性メモリ回路を含み得る。マイクロコントローラユニット1018は、ユーザーからの電話番号入力及び制御入力を受け取るためにキーパッド1020と相互作用する。マイクロコントローラユニット1018は、ダイヤルされた番号、バッテリー残存寿命などの電話の現在の状態、及び受信した英数字メッセージを表示するためにディスプレイ1022に駆動機能を提供する。デジタルシグナルプロセッサ1016は、送信エンコード、受信デコード、誤り検出及び補正、エコー相殺、及び音声バンドフィルタリングのためのリアルタイム信号処理を提供する。マイクロコントローラユニット1018及びデジタルシグナルプロセッサ1016両方が、プログラム命令及びユーザープロファイルデータのために不揮発性メモリ回路1012とインターフェースする。マイクロコントローラユニット1018及びデジタルシグナルプロセッサ1016もまた、信号処理、音声認識処理、及び他の用途のため揮発性メモリ回路1014とインターフェースする。

## 【0040】

例示の実施例は、スタティックランダムアクセスメモリ回路、抵抗性ランダムアクセスメモリ回路、磁気ランダムアクセスメモリ回路、又はバイアスされた信号マージンを複数の非対称読み出し又は書き込みオペレーション後につくり得る任意のその他のメモリ回路などの任意のメモリ回路に適用され得る。

## 【0041】

本発明の特許請求の範囲内で、説明した例示の実施例に変形が成され得、他の実施例が可能である。

【図1】

【図2】

【図3】

【図4】

【図5】

【図 6 A】

FIG. 6A

【図 6 B】

FIG. 6B

【図 7 A】

FIG. 7A

【図 7 B】

FIG. 7B

【図 8 A】

FIG. 8A

【図 8 B】

| 論理状態     | $B_1$ | $B_0$ | $B_1$ | $b_1$ | $b_0$ | $b_1$ | $RB_0$ | $RB_1$ |

|----------|-------|-------|-------|-------|-------|-------|--------|--------|

| 書き込み後    | 0     | 0     | 1     | X     | X     | X     | X      | X      |

| 第1の読み出し後 | 1     | 1     | 0     | 0     | 0     | 1     | 0      | 1      |

| 第2の読み出し後 | 0     | 0     | 1     | 1     | 1     | 0     | 0      | 1      |

| 第3の読み出し後 | 1     | 1     | 0     | 0     | 0     | 1     | 0      | 1      |

| 第4の読み出し後 | 0     | 0     | 1     | 1     | 1     | 0     | 0      | 1      |

FIG. 8B

【図 8 C】

FIG. 8C

【図 9】

FIG. 9

【図 10】

FIG. 10

---

フロントページの続き

前置審査

(72)発明者 ホセ エイ ロドリゲス ラトーレ

アメリカ合衆国 75243 テキサス州 ダラス, エイピーティー 4218, グリーンヴィル アヴェニュー 11911

(72)発明者 ヒュー ピー マクアダムス

アメリカ合衆国 75071 テキサス州 マッキニー, カウンティ ロード 206, 5416

(72)発明者 マニッシュ ゴエル

アメリカ合衆国 75024 テキサス州 プラノ, ヘルストン ドライブ 4417

審査官 堀田 和義

(56)参考文献 特開2002-184172(JP,A)

特開平4-286795(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 11 C 11/22

G 11 C 7/06

G 11 C 7/10