(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2015-0131195

(43) 공개일자 2015년11월24일

- (51) 국제특허분류(Int. Cl.)

*H01L 29/78* (2006.01) *H01L 21/02* (2006.01)

*H01L 29/66* (2006.01)

- (52) CPC특허분류

*H01L 29/7803* (2013.01)

*H01L 21/02068* (2013.01)

- (21) 출원번호 10-2015-7028652

- (22) 출원일자(국제) 2014년03월13일

심사청구일자 없음

- (85) 번역문제출일자 2015년10월12일

- (86) 국제출원번호 PCT/US2014/0266668

- (87) 국제공개번호 WO 2014/160453

국제공개일자 2014년10월02일

- (30) 우선권주장

61/778,698 2013년03월13일 미국(US)

- (71) 출원인

디3 세미컨덕터 엘엘씨

미국 텍사스 75001 애디슨 이. 벨트우드 파크웨이

15050

- (72) 발명자

해링تون 토마스 이.

미국 텍사스 75001 애디슨 이. 벨트우드 파크웨이

15050

- (74) 대리인

박장원

전체 청구항 수 : 총 37 항

(54) 발명의 명칭 수직 전계 효과 디바이스들의 온도 보상을 위한 디바이스 아키텍처 및 방법

### (57) 요 약

접합 온도에 따라 온-저항에서의 감소된 편차를 제공하는 전계 효과 디바이스가 개시된다. 전계 효과 디바이스는 소스 접합, 게이트 접합 및 드레인 접합을 가지며, 드레인 접합에 인접하는 저항성 박막을 포함하고, 여기서 저항성 박막은 저항이 부 온도 계수를 갖는 물질을 포함한다. 이러한 물질은 도핑된 폴리실리콘, 비정질 실리콘, 실리콘-크롬, 및 실리콘-니켈로 구성되는 그룹으로부터의 하나 이상의 물질들 중에서 선택되는데, 전계 효과 디바이스에 대한 원하는 저항 및 온도 프로파일을 생성하기 위해 두께 및 도핑 레벨과 같은 물질 특성들이 선택된다. 개시되는 전계 효과 디바이스에 대한 온-저항의 온도 편차는 저항성 박막이 없는 유사한 전계 효과 디바이스에 대한 온도 편차와 비교해 감소된다.

**대 표 도** - 도2a

(52) CPC특허분류

*H01L 29/66712* (2013.01)

---

## 명세서

### 청구범위

#### 청구항 1

반도체 디바이스(semiconductor device)로서

기판(substrate)과;

상기 기판 상에 구성되며 드레인 영역(drain region)을 갖는 수직 전계 효과 디바이스(vertical field effect device)와; 그리고

상기 드레인 영역에 인접하는 부 온도 계수 저항기(negative temperature coefficient resistor)를 포함하는 것을 특징으로 하는 반도체 디바이스.

#### 청구항 2

제1항에 있어서,

상기 부 온도 계수 저항기는 폴리실리콘(polysilicon)인 것을 특징으로 하는 반도체 디바이스.

#### 청구항 3

제2항에 있어서,

상기 폴리실리콘은 입방 센티미터(cubic centimeter) 당 약  $1\times10^{17}$ 개의 원자들 내지 약  $1\times10^{21}$ 개의 원자들로 도핑(doping)되는 것을 특징으로 하는 반도체 디바이스.

#### 청구항 4

제2항에 있어서,

상기 폴리실리콘은 비소(arSENIC), 인(phosphorous), 및 봉소(boron)로 이루어진 그룹 중 하나로 도핑되는 것을 특징으로 하는 반도체 디바이스.

#### 청구항 5

제1항에 있어서,

상기 부 온도 계수 저항기는 비정질 실리콘(amorphous silicon)인 것을 특징으로 하는 반도체 디바이스.

#### 청구항 6

제5항에 있어서,

상기 비정질 실리콘은 입방 센티미터 당 약  $1\times10^{17}$ 개의 원자들 내지 약  $1\times10^{21}$ 개의 원자들로 도핑되는 것을 특징으로 하는 반도체 디바이스.

#### 청구항 7

제5항에 있어서,

상기 비정질 실리콘은 비소, 인, 및 봉소로 이루어진 그룹 중 하나로 도핑되는 것을 특징으로 하는 반도체 디바이스.

#### 청구항 8

제1항에 있어서,

상기 부 온도 계수 저항기는 실리콘-크롬(silicon-chromium)인 것을 특징으로 하는 반도체 디바이스.

**청구항 9**

제8항에 있어서,

상기 실리콘-크롬은 약 40% 내지 약 80%의 실리콘인 것을 특징으로 하는 반도체 디바이스.

**청구항 10**

제1항에 있어서,

상기 부 온도 계수 저항기는 실리콘-니켈(silicon-nickel)인 것을 특징으로 하는 반도체 디바이스.

**청구항 11**

제10항에 있어서,

상기 실리콘-니켈은 약 40% 내지 약 80%의 실리콘인 것을 특징으로 하는 반도체 디바이스.

**청구항 12**

제1항에 있어서,

상기 부 온도 계수 저항기의 두께는 약 25 옹스트롬(angstroms) 내지 약 2000 옹스트롬인 것을 특징으로 하는 반도체 디바이스.

**청구항 13**

제1항에 있어서,

상기 수직 전계 효과 디바이스는 MOSFET(Metal Oxide Silicon Field Effect transistor)인 것을 특징으로 하는 반도체 디바이스.

**청구항 14**

제1항에 있어서,

상기 수직 전계 효과 디바이스는 전하 보상 MOSFET(charge compensated MOSFET)인 것을 특징으로 하는 반도체 디바이스.

**청구항 15**

MOSFET(Metal Oxide Silicon Field Effect transistor)로서,

상기 MOSFET은 n+ 소스 영역(source region), p- 채널(channel), JFET(Junction Field Effect Transistor) 영역, n- 드리프트 영역(drift region) 및 부 온도 계수 저항 층(negative temperature coefficient resistance layer)을 구비하며, 상기 MOSFET의 온-저항(on-resistance)은 아래의 방정식에 의해 정의되고,

$$R_{dsOn} = R_n + R_{ch} + R_a + R_j + R_d + R_s + R_{NTC}$$

여기서,

$R_{dsOn}$  = 상기 MOSFET의 온-저항,

$R_n$  = 상기 n+ 소스 영역의 저항,

$R_{ch}$  = 상기 p- 채널의 저항,

$R_a$  = 상기 n- 드리프트 영역의 표면 저항(surface resistance),

$R_j$  = 상기 JFET 영역의 저항,

$R_d$  = 상기 n- 드리프트 영역의 저항,

$R_s$  = 상기 n+ 드레인 영역의 저항, 그리고

$R_{NTC}$  = 상기 부 온도 계수 저항 층의 저항인 것을 특징으로 하는 MOSFET.

### 청구항 16

제15항에 있어서,

상기  $R_{NTC}$ 의 범위는 약 -25°C 내지 약 125°C에서 약 1.6 오옴(ohms) 내지 약 1.0 오옴인 것을 특징으로 하는 MOSFET.

### 청구항 17

제15항에 있어서,

상기  $R_{DS(on)}$ 의 범위는 약 -25°C 내지 약 125°C에서 약 2.4 오옴 내지 약 3.2 오옴인 것을 특징으로 하는 MOSFET.

### 청구항 18

제15항에 있어서,

상기  $R_{DS(on)}$ 은 약 125°C의 온도 편차에 대해 약 0.8 오옴의 총 저항 편차를 나타내는 것을 특징으로 하는 MOSFET.

### 청구항 19

수직 전계 효과 디바이스로서,

정 온도 계수 디바이스(positive temperature coefficient device)와; 그리고

상기 정 온도 계수 디바이스와 물리적으로 접촉하며 직렬로 연결된 부 온도 계수 저항기를 포함하는 것을 특징으로 하는 수직 전계 효과 디바이스.

### 청구항 20

제19항에 있어서,

상기 정 온도 계수 디바이스는 MOSFET인 것을 특징으로 하는 수직 전계 효과 디바이스.

### 청구항 21

상기 부 온도 계수 저항기는 폴리실리콘인 것을 특징으로 하는 수직 전계 효과 디바이스.

### 청구항 22

제19항에 있어서,

상기 부 온도 계수 저항기는 비정질 실리콘인 것을 특징으로 하는 수직 전계 효과 디바이스.

### 청구항 23

제19항에 있어서,

상기 부 온도 계수 저항기는 실리콘-크롬인 것을 특징으로 하는 수직 전계 효과 디바이스.

### 청구항 24

제19항에 있어서,

상기 부 온도 계수 저항기는 실리콘-니켈인 것을 특징으로 하는 수직 전계 효과 디바이스.

### 청구항 25

n+ 기판 상에 n- 에피택셜 층(epitaxial layer)을 갖는 웨이퍼 위에 반도체 디바이스를 제조하는 방법으로서,

상기 n- 에피택셜 층 상에 수직 전계 효과 디바이스를 구성하는 단계와;

상기 n+ 기판 상에 부 온도 계수 저항성 층을 도포(applying)하는 단계와;

상기 부 온도 계수 저항성 층을 도핑하는 단계와;

상기 부 온도 계수 저항성 층에 금속 층을 도포하는 단계를 포함하는 것을 특징으로 하는 반도체 디바이스를 제조하는 방법.

### 청구항 26

제25항에 있어서,

상기 구성하는 단계는 또한 MOSFET를 구성하는 것을 포함하는 것을 특징으로 하는 반도체 디바이스를 제조하는 방법.

### 청구항 27

n+ 기판 상에 n- 에피택셜 층을 갖는 웨이퍼 위에 반도체 디바이스를 제조하는 방법으로서,

상기 n- 에피택셜 층 상에 수직 전계 효과 디바이스를 구성하는 단계와;

상기 n+ 기판 상에 부 온도 계수 저항성 층을 도포하는 단계와;

상기 부 온도 계수 저항성 층을 어닐링(annealing)하는 단계와; 그리고

상기 부 온도 계수 저항성 층에 금속 층을 도포하는 단계를 포함하는 것을 특징으로 하는 반도체 디바이스를 제조하는 방법.

### 청구항 28

제27항에 있어서,

상기 구성하는 단계는 또한 MOSFET를 구성하는 것을 포함하는 것을 특징으로 하는 반도체 디바이스를 제조하는 방법.

### 청구항 29

n- 논-에피택셜 웨이퍼(non-epitaxial wafer) 상에 반도체 디바이스를 제조하는 방법으로서,

상기 웨이퍼의 제 1 면 상에 수직 전계 효과 디바이스를 구성하는 단계와;

상기 웨이퍼의 제 2 면에 n+ 영역을 주입하는 단계와;

상기 n+ 영역을 어닐링하는 단계와;

상기 n+ 영역 상에 부 온도 계수 저항성 막을 도포하는 단계와;

상기 부 온도 계수 저항성 막을 주입 도핑(implant doping)하는 단계와;

상기 부 온도 계수 저항성 막을 어닐링하는 단계와; 그리고

상기 제 2 면을 금속화하는 단계를 포함하는 것을 특징으로 하는 반도체 디바이스를 제조하는 방법.

### 청구항 30

제29항에 있어서,

상기 어닐링하는 단계는 또한 레이저 어닐링(laser annealing)을 포함하는 것을 특징으로 하는 반도체 디바이스를 제조하는 방법.

### 청구항 31

n- 논-에피택셜 웨이퍼 상에 반도체 디바이스를 제조하는 방법으로서,

상기 웨이퍼의 제 1 면 상에 수직 전계 효과 디바이스를 구성하는 단계와;

상기 웨이퍼의 제 2 면에 n+ 영역을 주입하는 단계와;

상기 n+ 영역을 어닐링하는 단계와;

상기 n+ 영역 상에 부 온도 계수 저항성 막을 도포하는 단계와;

상기 부 온도 계수 저항성 막을 주입 도핑하는 단계와;

상기 부 온도 계수 저항성 막을 어닐링하는 단계와; 그리고

상기 제 2 면을 금속화하는 단계를 포함하는 것을 특징으로 하는 반도체 디바이스를 제조하는 방법.

### 청구항 32

n- 논-에피택셜 웨이퍼 상에 반도체 디바이스를 제조하는 방법으로서,

상기 웨이퍼의 제 1 면 상에 수직 전계 효과 디바이스를 구성하는 단계와;

상기 웨이퍼의 제 2 면에 n+ 드레인 영역을 주입하는 단계와;

상기 제 2 면 상에 부 온도 계수 저항성 막을 도포하는 단계와;

상기 n+ 드레인 영역 및 상기 부 온도 계수 저항성 막을 어닐링하는 단계와; 그리고

상기 제 2 면을 금속화하는 단계를 포함하는 것을 특징으로 하는 반도체 디바이스를 제조하는 방법.

### 청구항 33

제32항에 있어서,

상기 부 온도 계수 저항성 막을 도포한 이후에, 상기 부 온도 계수 저항성 막을 주입 도핑하는 것을 특징으로 하는 반도체 디바이스를 제조하는 방법.

### 청구항 34

n- 논-에피택셜 웨이퍼 상에 반도체 디바이스를 제조하는 방법으로서,

상기 웨이퍼의 제 1 면 상에 수직 전계 효과 디바이스를 구성하는 단계와;

상기 웨이퍼의 제 2 면 상에 폴리실리콘 부 온도 계수 저항성 막을 도포하는 단계와;

상기 부 온도 계수 저항성 막을 통해 n+ 영역을 주입하는 단계와;

상기 n+ 영역과 상기 부 온도 계수 저항성 막을 동시에 어닐링하는 단계와; 그리고

상기 부 온도 계수 저항성 막을 금속화하는 단계를 포함하는 것을 특징으로 하는 반도체 디바이스를 제조하는 방법.

### 청구항 35

제34항에 있어서,

상기 n+ 영역을 주입한 이후에, 상기 부 온도 계수 저항성 막을 주입 도핑하는 단계를 더 포함하는 것을 특징으로 하는 반도체 디바이스를 제조하는 방법.

### 청구항 36

반도체 디바이스를 제조하는 방법으로서,

상기 반도체 디바이스에 대한 합성 온-저항(composite on-resistance)을 특정하는 단계와;

상기 반도체 디바이스에 대한 요구된 온-저항 편차(on-resistance variation)를 특정하는 단계와;

일 세트의 비-합성 반도체 디바이스들(non-composite semiconductor devices)에 대한 평균 디바이스 온-저항(average device on-resistance)을 결정하는 단계와;

저항성 박막(resistive thin film)에 대한 온도 의존성 곡선(temperature dependence curve)을 결정하는 단계

와;

상기 온도 의존성 곡선에 근거하여 임의의 물질을 선택하는 단계와;

상기 물질에 대한 시트 저항(sheet resistive)을 결정하는 단계와;

상기 저항성 박막에 대한 일 세트의 원하는 특성(property)들을 결정하는 단계와;

웨이퍼의 제 1 면 상에 수직 전계 효과 디바이스를 구성하는 단계와;

상기 웨이퍼의 제 2 면에 상기 저항성 박막을 도포하는 단계와; 그리고

상기 저항성 박막을 도핑하는 단계를 포함하는 것을 특징으로 하는 반도체 디바이스를 제조하는 방법.

### 청구항 37

제36항에 있어서,

상기 저항성 박막을 어닐링하는 단계를 더 포함하는 것을 특징으로 하는 반도체 디바이스를 제조하는 방법.

### 발명의 설명

#### 기술 분야

[0001] 본 발명은 일반적으로 수직 MOSFET(Metal Oxide Silicon Field Effect transistor)의 저항의 온도 편차를 감소시키기 위한 방법 및 기법에 관한 것이다.

#### 배경 기술

[0002] 여러 해 동안, 고성능 전력 전자기기의 제조자 및 개발자는 전력-처리 밀도를 향상시키고 개개의 전자 컴포넌트들의 디바이스 열 방산(heat dissipation)을 관리하기 위해 노력해 오고 있다.

[0003] 수직 MOSFET들은 온도에 따라 단조적으로(monotonically) 그리고 슈퍼-리니어하게(super-linearly) 증가하는 온-저항(on-resistance) ("RdsOn")을 갖는다. 온-저항이 증가함에 따라, 소정의 드레인 전류( $I_d$ )에 대해 소비되는 전력(이것은 전력 방정식: 전력 =  $I_d^2 \times RdsOn$ 을 따름)도 증가한다. 전력 소비는 또한 MOSFET 접합 온도가 증가하게 하고, 이것은 온-저항을 또한 증가시킨다. 만약 열 방산이 충분하다면, RdsOn은 MOSFET 내에서의 열 평형(thermal equilibrium)에 도달할 때까지 증가할 것이다. 만약 열 방산 시스템이 충분하지 못하다면, MOSFET은 열 폭주(thermal runaway)를 겪게 될 것이다.

[0004] 현대의 수직 MOSFET 디바이스들에서 RdsOn이 감소하면 결과적으로 전력 공급 효율이 상당량 증가하게 된다. 그러나, RdsOn은 또한 온도에 따라 증가한다. 이러한 디바이스들을 포함하는 시스템들, 특히 다양한 둑티 사이클(duty cycles) 및 다양한 주위 온도(ambient temperatures)에서 동작하는 시스템들은 온도에 따라 감소된 편차를 보여주는 RdsOn으로부터 큰 혜택을 받게 된다.

### 발명의 내용

#### 과제의 해결 수단

[0005] 본 개시내용은 저항의 온도 편차를 감소시키는 전계-효과 디바이스 아키텍처이다. 특히, 본 개시내용은 온도 증가로 인한 RdsOn의 편차를 감소시키기 위한 방법 및 장치를 제공한다.

[0006] 바람직한 실시예에 따르면, 온도에 따라 더 안정적인 저항 편차를 획득하기 위해 부 온도 계수(Negative Temperature Coefficient, "NTC")를 갖는 저항기가 수직 MOSFET과 직렬로 연결된다. 또한, 온도에 따른 디바이스 저항의 편차가 상당량 감소된다.

[0007] 바람직한 실시예에서, n+ 도핑된 베이스 기판(n+ doped base substrate)을 갖는 에피택셜 Si 웨이퍼(epitaxial Si wafer) 상에 MOSFET 수직 전계-효과 디바이스가 구성된다.

[0008] 또 하나의 다른 실시예에서, n- 도핑된 기판을 갖는 논-에피택셜 Si 웨이퍼(non-epitaxial Si wafer) 상에 MOSFET 수직 전계-효과 디바이스가 구성된다.

[0009] 본 발명의 장치는 공핍 모드(depletion mode) 혹은 인핸스먼트 모드(enhancement mode)에서 동작하는 n-채널 디바이스 및 p-채널 디바이스 모두에서 적용가능하다.

### 도면의 간단한 설명

[0010] 도 1a는 종래의 전계-효과 디바이스를 예시한다.

도 1b는 종래의 전계 효과 디바이스의 온-저항에 대한 저항성 경로를 예시한다.

도 2a는 통합된 부 온도 계수 저항기를 갖는 전계-효과 디바이스의 바람직한 실시예를 예시한다.

도 2b는 통합된 부 온도 계수 저항기를 갖는 전계 효과 디바이스의 바람직한 실시예의 온-저항에 대한 저항성 경로를 예시한다.

도 3은 종래 기술의 수직 전계 효과 디바이스에 대한 접합 온도에 따른 정규화된 온-저항의 예시적 그래프, 통합된 NTC 저항기를 갖는 수직 전계 효과 디바이스의 바람직한 실시예에 대한 접합 온도에 따른 정규화된 온-저항의 예시적 그래프, 그리고 독립된 부 온도 계수 저항기의 온도 의존성 곡선이다.

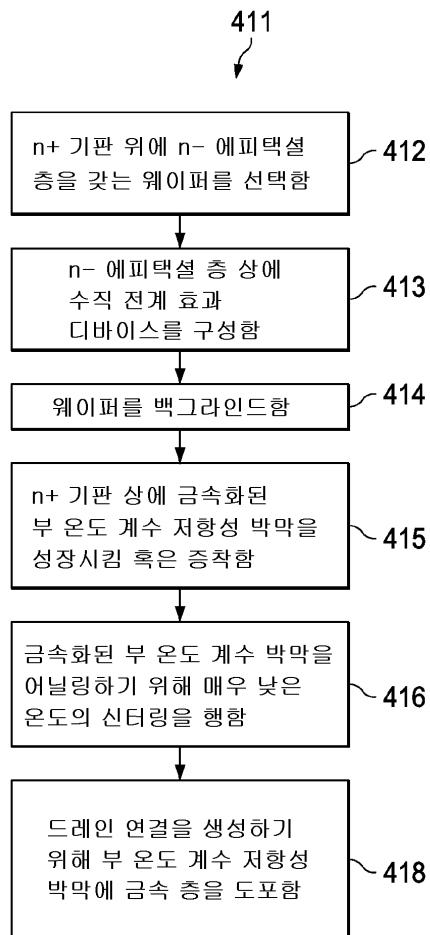

도 4a는 온도에 따른 온-저항의 감소된 편차를 갖는 수직 전계 효과 디바이스를 구성하기 위한 방법의 바람직한 실시예의 흐름도이다.

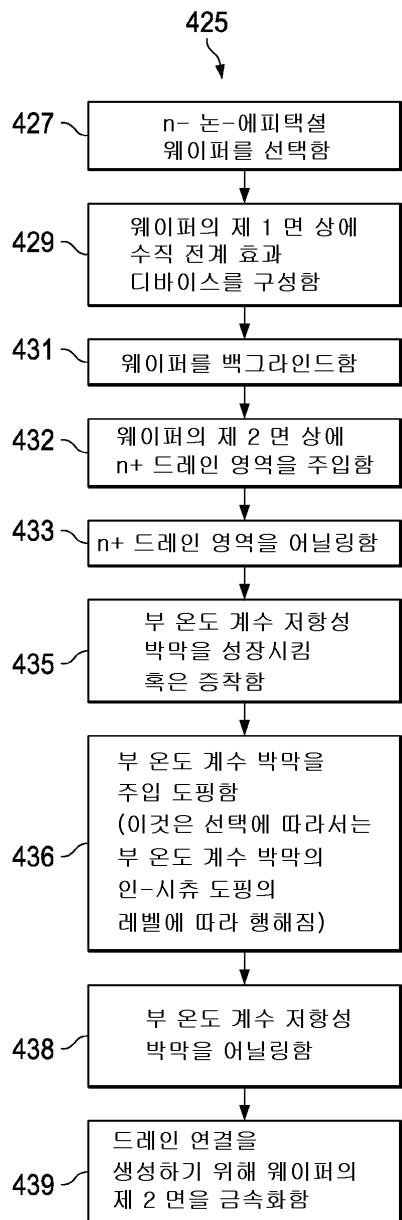

도 4b는 온도에 따른 온-저항의 감소된 편차를 갖는 수직 전계 효과 디바이스를 구성하기 위한 방법의 다른 실시예의 흐름도이다.

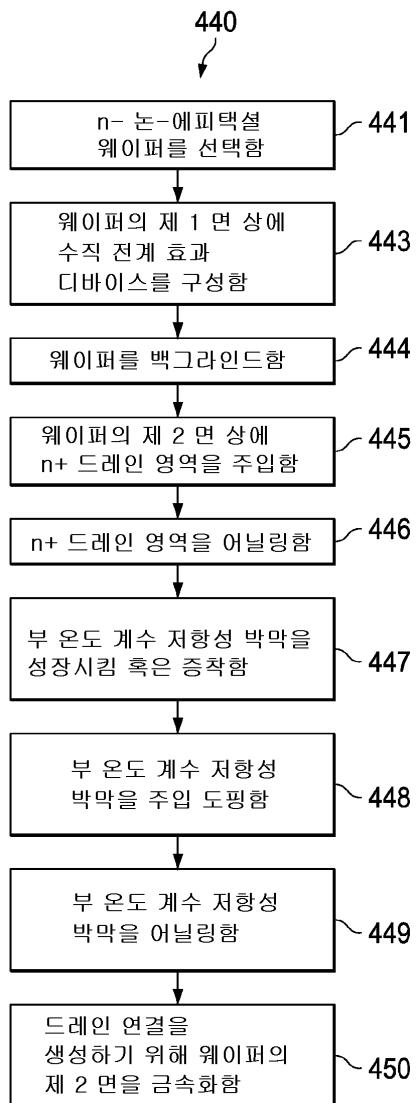

도 4c는 온도에 따른 온-저항의 감소된 편차를 갖는 수직 전계 효과 디바이스를 구성하기 위한 방법의 다른 실시예의 흐름도이다.

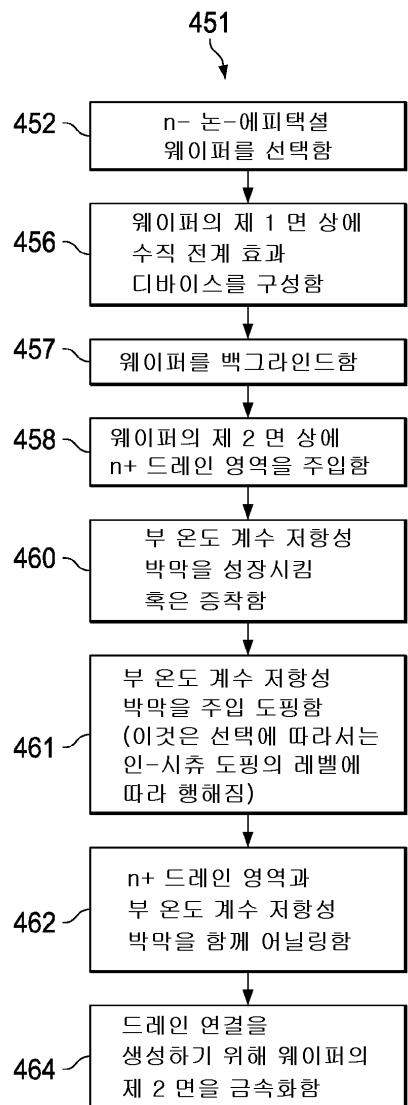

도 4d는 온도에 따른 온-저항의 감소된 편차를 갖는 수직 전계 효과 디바이스를 구성하기 위한 방법의 다른 실시예의 흐름도이다.

도 4e는 온도에 따른 온-저항의 감소된 편차를 갖는 수직 전계 효과 디바이스를 구성하기 위한 방법의 다른 실시예의 흐름도이다.

도 4f는 온도에 따른 온-저항의 감소된 편차를 갖는 수직 전계 효과 디바이스를 구성하기 위한 방법의 다른 실시예의 흐름도이다.

도 5는 부 온도 계수 저항기를 구성하기 위한 방법의 바람직한 실시예의 흐름도이다.

### 발명을 실시하기 위한 구체적인 내용

[0011] 수직 반도체 디바이스들은 반도체 구조들(예컨대, MOSFET들, IGBT들 및 다이오드들)이며, 여기서 전류 흐름의 주된 방향은 수직 방향인바, 즉 상부로부터 하부로의 방향, 혹은 하부로부터 상부로의 방향, 혹은 이들 방향 모두를 말한다. 개개의 전력 반도체 디바이스들은 종종 이러한 수직 아키텍처로 구축된다.

[0012] "온-저항"(RdsOn)은 반도체 디바이스의 전극에 전압 및/또는 전류가 인가됨으로써 "온-상태(on-state)"로 바이어스(bias)될 때의 반도체 디바이스의 저항이다. 예를 들어, MOSFET은 게이트 전극, 소스 전극, 및 드레인 전극을 가지며, 드레인 전극과 소스 전극 간에는 드레인-소스 전압(Vds)이 인가되고, 게이트 전극과 소스 전극 간에는 게이트-소스 전압(Vgs)이 인가된다. "온-상태"는 소스 전극으로부터 드레인 전극으로의 전류(Id)가 게이트-소스 전압에 의해 인에이블(enable)된 것을 의미한다. 예를 들어, 전력 MOSFET에 있어서, RdsOn은 다음과 같이 정의된다.

$$RdsOn = Id / Vds$$

방정식 1

[0013] 여기서, 드레인-소스 전압(Vds)은 전형적으로 0.1V 내지 5V의 값으로 설정되고, 게이트-소스 전압(Vgs)은 전형적으로 10V로 설정된다.

[0014] 비-전하 보상 수직 전계 효과 디바이스들(non-charge compensated vertical field effect devices) 및 전하-보상 수직 전계 효과 디바이스들(charge-compensated vertical field effect devices)(예를 들어, 슈퍼-접합 MOSFET들(super-junction MOSFETS))은 일부 다른 수직 반도체 디바이스들과 같이, 정 온도 계수 디바이스들(positive temperature coefficient devices)이다. 일반적으로, 정 온도 계수 디바이스들은 온도 증가에 따라

증가하는 디바이스 저항을 갖는다.

[0016] 역으로, NTC 디바이스들은 온도 증가에 따라 감소하는 저항을 갖는다. NTC 디바이스의 일 예는 NTC 저항기이다.

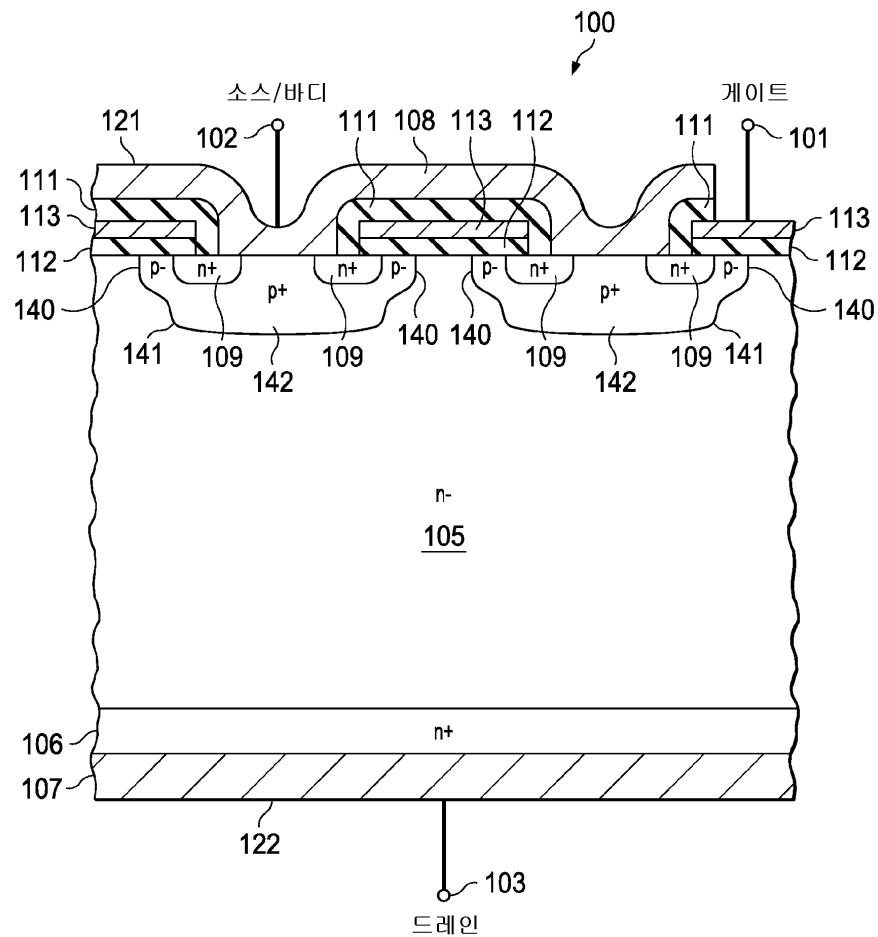

[0017] 도 1a는 종래 기술에서 알려진 바와 같은 수직 MOSFET 디바이스(100)의 단면도를 보여준다. 수직 전계-효과 디바이스(100)는 상부 표면(121) 및 하부 표면(122)을 구비하고, 소스 전극(102), 드레인 전극(103), 및 게이트 전극(101)을 포함한다. 게이트 전극은 소스 전극(102)과 드레인 전극(103) 간의 전류 흐름을 제어한다. 수직 전계-효과 디바이스(100)는 또한 "n<sup>+</sup>" 드레인 영역(106)을 포함하며, 드레인 전극(103)의 형성을 위해 하부 표면에 인접하는 금속 층(107)을 갖는다. n<sup>+</sup> 드레인 영역(106)은 "n<sup>-</sup>" 드리프트 영역(drift region)(105)과 접촉한다. n<sup>-</sup> 드리프트 영역(105)은 또한 "p<sup>-</sup>" 타입 바디 영역(body region)(140)과 접촉한다.

[0018] n<sup>+</sup> 소스 영역(109)은 "p" 타입 바디 영역들에 인접한다. p 타입 바디 영역들은 p- 바디(140), "p<sup>+</sup>" 바디(141), 및 p<sup>+</sup> 바디-접촉 영역(142)을 포함한다. p<sup>+</sup> 바디-접촉 영역(142)은 소스 금속 층(108)에 접촉하고, 소스 금속 층(108)은 n<sup>+</sup> 소스 영역, p 타입 바디 영역들, 및 드레인 전극(103) 간에 형성되는 기생 양극성 접합 트랜지스터(parasitic bipolar junction transistor)의 우발적 예기(excitation)를 피하기 위해 n<sup>+</sup> 소스 영역(109)을 p<sup>+</sup> 바디-접촉 영역(142)에 전기적으로 단락시킨다. 소스 금속 층(108)은 또한 소스 전극(102)과 접촉한다. n<sup>-</sup> 드리프트 영역(105)은 p-타입 바디 영역들(140, 141, 142) 아래에 있음과 아울러 n<sup>+</sup> 드레인 영역(106)에 인접한다.

[0019] 게이트 영역(113)은 절연 옥사이드 층(insulation oxide layer)(112)과 접촉하고, 절연 옥사이드 층(112)은 n- 드리프트 영역(105), p- 바디 영역(140), n<sup>+</sup> 소스 영역(109) 및 절연 층(111)에 인접한다. 게이트 영역(113)은 게이트 물질로 채워지며 게이트 옥사이드 층(112)에 인접한다. 게이트 영역(113)은 게이트 전극(101)과 전기적으로 접촉한다. 게이트 옥사이드 층(112)은 또한 n<sup>-</sup> 드리프트 영역(105)에 인접한다. MOSFET 디바이스들에서 일반적으로 사용되는 게이트 물질은 다결정성 실리콘(polycrystalline silicon)(폴리실리콘(polysilicon))이다.

[0020] 도 1b는 종래 기술의 디바이스의 온-저항에 대한 경로를 보여준다. 방정식 1에서와 같은 온-저항은 디바이스의 온-상태 동안 소스와 드레인 간의 총 저항이다. 온-저항에 대한 경로가 경로(150)에서 보여지고 있다. 수직 전계 효과 디바이스(100)에 있어서, 온-저항은 다음과 같이 일련의 저항 결합으로 주어진다.

$$R_{dsOn} = R_n + R_{ch} + R_a + R_j + R_D + R_S \quad \text{방정식 2}$$

[0021] 여기서, R<sub>dsOn</sub>은 온-저항이고, R<sub>n</sub>(151)은 n<sup>+</sup> 소스 영역(109)의 저항이고, 그리고 R<sub>ch</sub>(152)는 p-타입 바디 영역(140)의 p- 부분에 형성된 채널의 저항이다. R<sub>a</sub>(153)는 인가되는 게이트-소스 전압에 의해 변조되는 n- 드리프트 영역의 표면 저항이다. JFET 영역(130)은 p 타입 바디 (p- 바디) 영역(140)의 표면들(132) 사이에 있는 n- 드리프트 영역(105)의 일부분이다. 드레인 전압이 공급됨에 따라, 공핍 영역이 표면들(132)에서의 접합부로부터 바깥쪽을 향해 확장하고, 이것은 저항(R<sub>j</sub>)을 유발 및 증가시키는데 왜냐하면 표면들(132) 사이에 있는 n- 드리프트 영역의 압축(constriction)때문이다. R<sub>j</sub>(154)는 JFET 영역의 저항이다. R<sub>D</sub>(155)는 JFET 영역(130)과 n<sup>+</sup> 드레인 영역(106)의 상부 간의 저항이다. R<sub>D</sub>는 n- 드리프트 영역의 저항이며, 고전압 MOSFET에서 R<sub>dsOn</sub>의 가장 지배적 인자이다. R<sub>S</sub>(156)는 n<sup>+</sup> 드레인 영역의 저항이다. R<sub>S</sub>는 또한, 브레이크다운 전압(breakdown voltage)이 약 50V 아래에 있는 저전압 MOSFET에서, 온-저항에 큰 영향을 미친다. 추가적인 온-저항이 다양한 영역들 간의 비-이상적 접촉으로부터 일어날 수 있고, 뿐만 아니라 디바이스를 패키지에 연결하기 위해 사용되는 전극 리드(electrode lead)들로부터 일어날 수 있다.

[0023] R<sub>dsOn</sub>은 온도에 따라 증가하는데, 왜냐하면 온도가 증가함에 따라 정공들 및 전자들의 이동도가 감소하기 때문이다. n- 채널 전력 MOSFET 디바이스의 R<sub>dsOn</sub>은 다음과 같은 방정식으로 추정될 수 있다.

$$R_{dsOn}(T) = R_{dsOn}(300^{\circ}\text{K}) \left(\frac{T}{300}\right)^{\beta} \quad \text{방정식 3}$$

[0024] 여기서, T는 디바이스 온도(단위: 켈빈(Kelvin))이고, β는 온도 계수이고, R<sub>dsOn</sub>(T)은 디바이스 온도(T)에서의 온-저항이다. 온도 계수는 양의 값이고 일반적으로 그 범위는 MOSFET 디바이스들에 대해 2.0 내지 2.5이다.

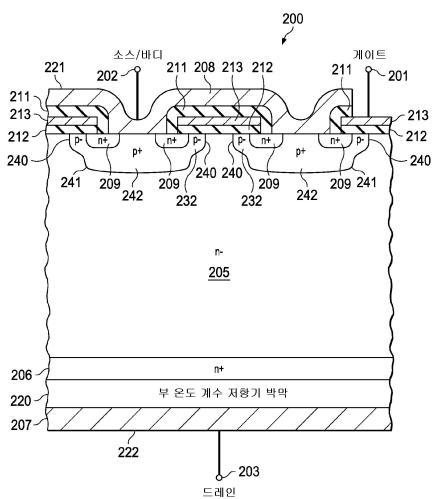

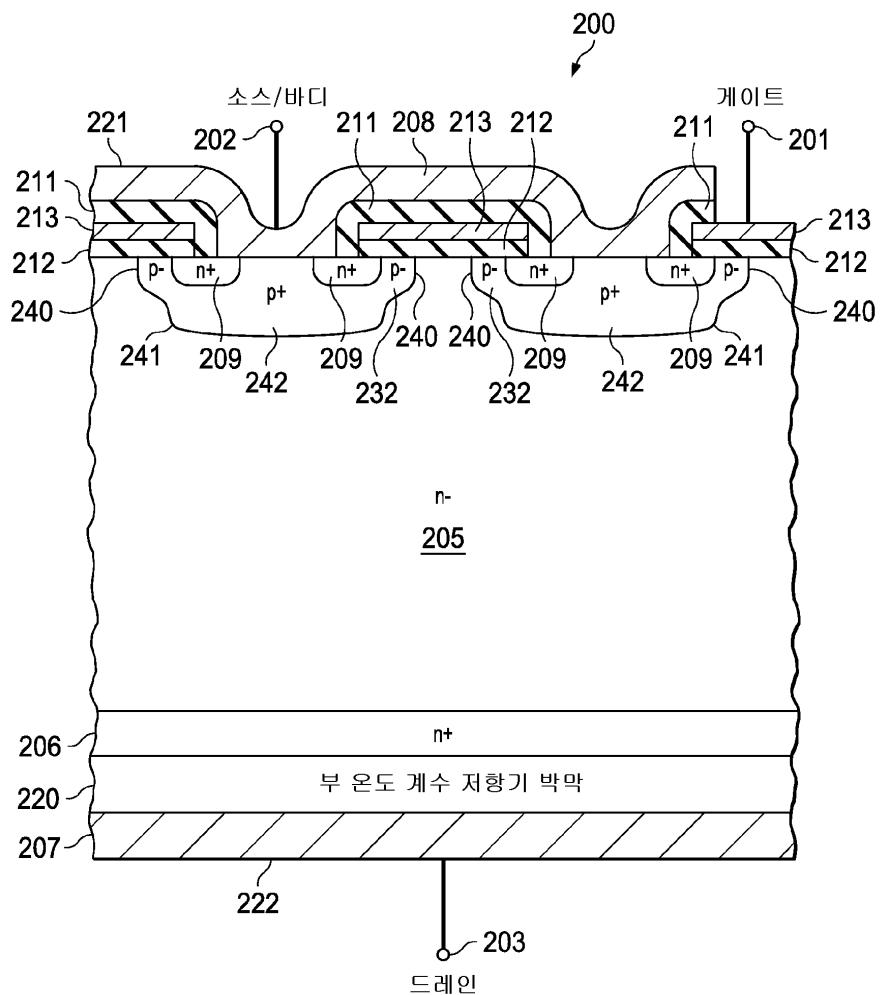

[0025] 도 2a는 R<sub>dsOn</sub> 온도 보상을 갖는 수직 전계 효과 디바이스(200)의 바람직한 실시예의 단면도를 보여준다. 상부 표면(221) 및 하부 표면(222)이 제공되며, 소스 전극(202), 드레인 전극(203), 및 게이트 전극(201)이 포함되어

있다. 게이트 전극(201)은 소스 전극(202)과 드레인 전극(203) 간의 전류 흐름을 제어한다. 디바이스(200)는 또한 n+ 드레인 영역(206)을 포함한다. n+ 드레인 영역(206)에 인접하여 저항성 층(220)이 존재한다. 저항성 층(220)은 부 온도 계수를 나타낸다. 저항성 층(220)에 인접하여 금속 층(207)이 존재한다. 금속 층(207)은 드레인 전극(203)에 부착된다. n+ 드레인 영역(206)은 n- 드리프트 영역(205)과 접촉한다. n- 드리프트 영역(205)은 p 타입 바디 영역들(240, 241, 242)과 접촉한다.

[0027] n+ 소스 영역(209)은 p 타입 바디 영역들에 인접한다. p 타입 바디 영역들은 p- 바디(240), p+ 바디(241), 및 p+ 바디 접촉 영역(242)을 포함한다. p+ 바디-접촉 영역(242)은 소스 금속 층(208)에 접촉하고, 소스 금속 층(208)은 n+ 소스 영역(209)을 p 타입 바디 영역들(240, 241, 242)에 전기적으로 단락시킨다. 소스 전극(202)은 소스 금속 층(208)에 부착된다.

[0028] 게이트 영역(213)은 게이트 옥사이드 층(212)에 인접하고, 게이트 옥사이드 층(212)은 n- 드리프트 영역(205), p- 바디 영역(240), n+ 소스 영역(209) 및 절연 층(211)에 인접한다. 게이트 영역(213)은 게이트 전극(201)과 전기적으로 접촉한다. 게이트 옥사이드 층(212)은 또한 n- 드리프트 영역(205)에 인접한다.

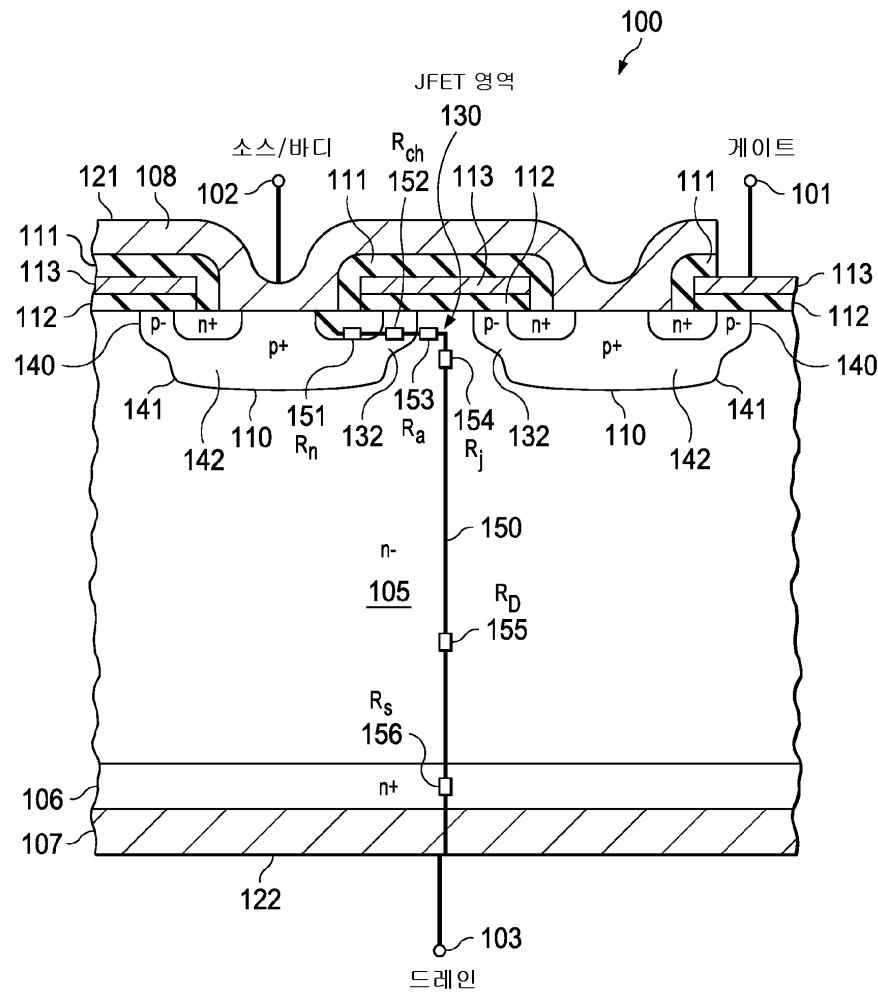

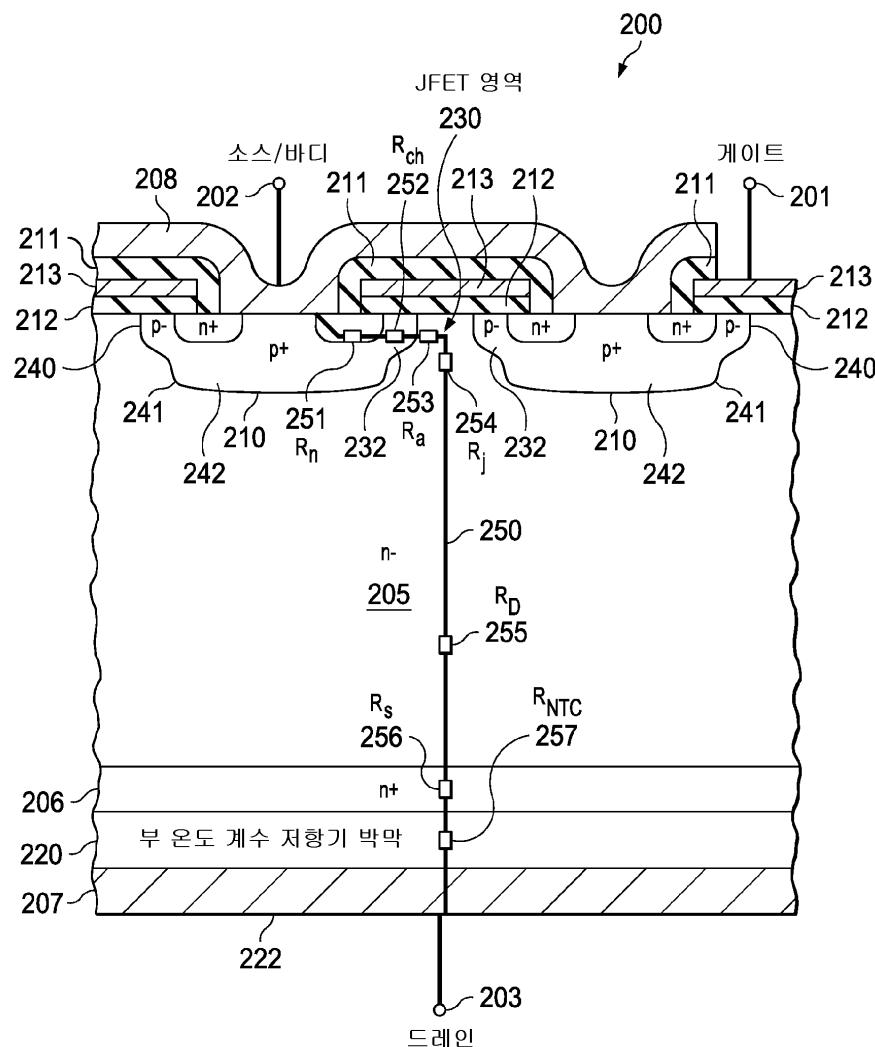

[0029] 도 2b는 바람직한 디바이스 실시예의 온-저항에 대한 경로(250)를 보여준다. 디바이스(200)에 대해, 온-저항은 다음과 같은 방정식으로 주어진다.

$$R_{dsOn} = R_n + R_{CH} + R_a + R_j + R_D + R_S + R_{NTC} \quad \text{방정식 4}$$

[0030]

[0031] 여기서,  $R_{dsOn}$ 은 온-저항이고,  $R_n$ (251)은 n+ 소스 영역(209)의 저항이고,  $R_{ch}$ (252)는 p- 바디 영역(240)에 형성된 채널의 저항이다. JFET 영역(230)은 p 타입 바디 (p- 바디) 영역(240)의 표면들(232) 사이에 있는 n- 드리프트 영역(205)의 일부분이다. 드레인 전압이 공급됨에 따라, 공핍 영역이 표면들(232)에서의 접합부로부터 바깥쪽을 향해 확장하고, 이것은 저항( $R_j$ )을 생성 및 증가시키는데 왜냐하면 표면들(232) 사이에 있는 n- 드리프트 영역의 압축때문이다.  $R_j$ (254)는 JFET 영역의 저항이다.  $R_D$ (255)는 JFET 영역(230)과 n+ 드레인 영역(206)의 상부 간의 n- 드리프트 영역 저항이다.  $R_a$ (253)는 인가되는 게이트-소스 전압에 의해 변조되는 n- 드리프트 영역의 표면 저항이다.  $R_S$ (256)는 n+ 드레인 영역의 저항이다.  $R_{NTC}$ (257)는 부온도 계수를 갖는 저항성 층(220)의 저항인바, 온도 증가에 따라  $R_{NTC}$ (257)의 저항에서의 감소가 일어나는 특징이 있다.

[0032] 수직 MOSFET 디바이스의 바람직한 실시예에서, MOSFET과 직렬로 연결되는 NTC 저항기를 부가함으로써 온도에 따른  $R_{dsOn}$  저항의 편차 감소가 달성된다.

[0033] 바람직한 실시예에서, NTC 저항기는 저항성 층(220)에 의해 제공되며, 이러한 NTC 저항기는 인-시츄(in-situ)로 도핑되는 폴리실리콘(혹은 예를 들어, 스퍼터링(sputtering)에 의해 증착되는 비정질 실리콘)으로 만들어지는 박막(thin film)으로 구성된다. 또 하나의 다른 실시예에서, 저항성 층(220)은, 주입에 의해 도핑되고 후속적으로 어닐링되는 폴리실리콘(혹은 비정질 실리콘)으로 구성되는 박막이며, 여기서 폴리실리콘 혹은 비정질 실리콘 층의 두께는 대략 100 앙스트롬(angstroms) 내지 대략 4000 앙스트롬의 범위 내에 있다.

[0034] 폴리실리콘 혹은 비정질 실리콘 박막의 도핑 레벨은 바람직하게는 약  $1e17 \text{ atoms/cm}^3$  내지 약  $1e21 \text{ atoms/cm}^3$ 의 범위 내에 있다. 이러한 값들은 ± 5%만큼 변할 수 있다. 폴리실리콘 혹은 비정질 실리콘 박막 내의 도펜트(dopant)들은, 베이스 온도(base temperature)(예컨대, 25°C)에서의 저항성 층에 대해 원하는 저항 값, 그리고 저항 값의 원하는 부 온도 계수를 달성하기 위해 요구되는 바에 따라, 비소(arsenic), 인(phosphorus), 봉소(boron) 혹은 이러한 원소들의 임의의 조합으로 구성되는 원소들의 그룹으로부터 선택된다.

[0035] 또 하나의 다른 실시예에서, 저항성 층(220)은 실리콘-크롬(silicon-chromium)으로 만들어지는 금속화된 저항성 박막이다. 실리콘-크롬 막의 실리콘 퍼센티지는 바람직하게는 약 40% 내지 약 80%의 범위 내에 있다. 이러한 값들은 ± 5%만큼 변할 수 있다. 실리콘-크롬 막의 두께는, 베이스 온도(예컨대, 25°C)에서의 저항성 층에 대해 원하는 시트 저항 값(sheet resistance value), 그리고 저항 값의 원하는 부 온도 계수를 달성하기 위해 요구되는 바에 따라, 대략 25 옹스트롬 내지 대략 2000 옹스트롬의 범위 내에 있다. 이러한 값들은 ± 10%만큼 변할 수 있다.

[0036] 또 하나의 다른 실시예에서, 저항성 층(220)은 실리콘-니켈(silicon-nickel)로 만들어지는 금속화된 저항성 박막이다. 실리콘-니켈 막의 실리콘 퍼센티지(silicon percentage)는 바람직하게는 약 40% 내지 약 80%의 범위 내에 있다. 실리콘-니켈 막의 두께는, 베이스 온도(예컨대, 25°C)에서의 저항성 층에 대해 원하는 시트 저항 값,

그리고 저항 값의 원하는 부 온도 계수를 달성하기 위해 요구되는 바에 따라, 대략 25 옹스트롬 내지 대략 2000 옹스트롬의 범위 내에 있다. 이러한 값들은 ± 10%만큼 변할 수 있다.

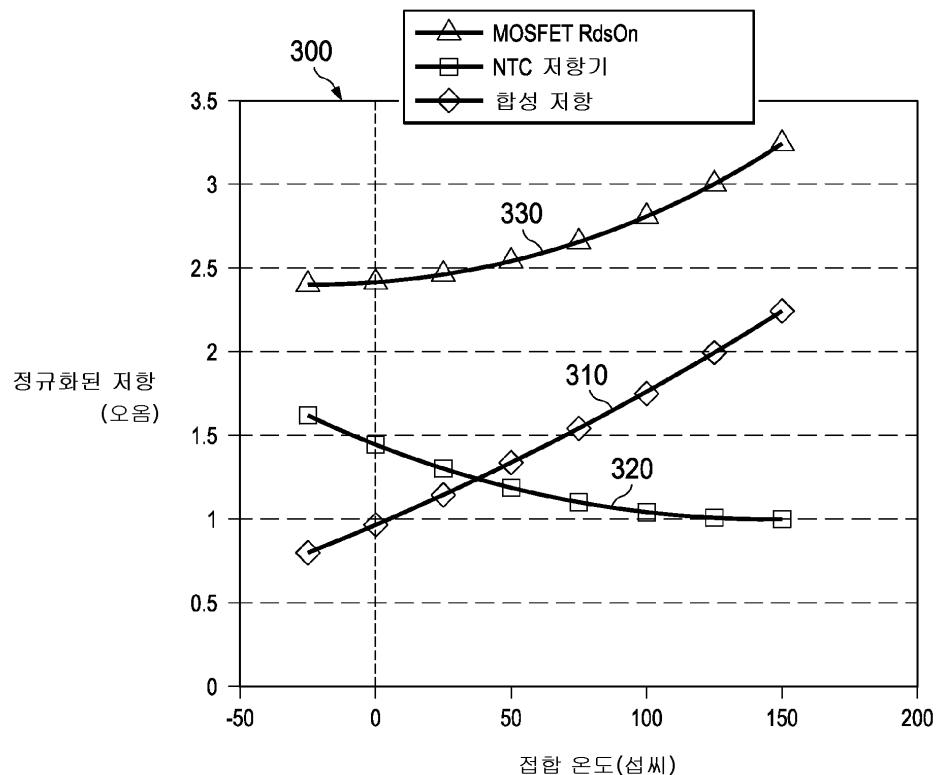

[0037] 도 3은 수직 전계-효과 디바이스 내에 저항성 층(220)을 포함하는 효과의 예를 예시적으로 보여주는 그래프이다. 그래프(300)는 디바이스의 접합 온도에 따른 저항(단위: 오옴)을 도시한 것이다. 그래프(300)는 3 개의 곡선을 포함한다. 이들 곡선들은 약 -25°C 내지 약 150°C 범위 내에 있는 접합 온도에 대해 도시된 것이다. 곡선(310)은  $\beta=2.0$ 에 대해서 방정식 3을 따르는 온도 의존성을 보여주는 MOSFET 디바이스의 온-저항을 도시한 것이고, 그 온도 의존성은 -25°C에서의 약 0.8 오옴으로부터 150°C에서의 약 2.25 오옴에 이르는 범위를 갖는다. 저항 값들은 ± 5%만큼 변할 수 있다. 곡선(320)은 부 온도 계수 저항성 층의 저항을 도시한 것이다. 저항성 층은 -25°C에서의 약 1.6 오옴으로부터 125°C의 온도 및 그 이상에서의 약 1.0 오옴의 접근값(asymptotic value)에 이르는 범위를 갖는 온도 의존성을 보여준다. 곡선(330)은 MOSFET 디바이스와 직렬로 접촉하고 있는 저항성 층을 갖는 합성 디바이스의 합성 온-저항을 도시한 것이다. 합성 온-저항은 -25°C에서의 약 2.4 오옴으로부터 150°C에서의 약 3.2 오옴에 이르는 범위를 갖는 온도 의존성을 보여주고 있는바, 온도 범위 -25°C에서 150°C에 걸친 총 저항 편차는 0.8 오옴이다. 이러한 예에서, NTC 저항기(220)를 갖는 MOSFET의 합성 저항( $R_{dsOn}$ )은 NTC 저항기가 없는 MOSFET과 비교하여 더 평평하고 안정된 저항 프로파일을 보여주고 있다. 이러한 예에서의 합성 저항은 25°C와 150°C 간에 약 32%만큼 변했고, 반면 비-합성 MOSFET의  $R_{dsOn}$ 은 거의 95%만큼 변했다. 따라서, 합성 디바이스의 온도에 따른 온-저항( $R_{dsOn}$ )의 편차는 저항성 층이 없는 MOSFET 디바이스에 대한 온-저항의 온도 편차와 비교해 약 50%만큼 감소된다.

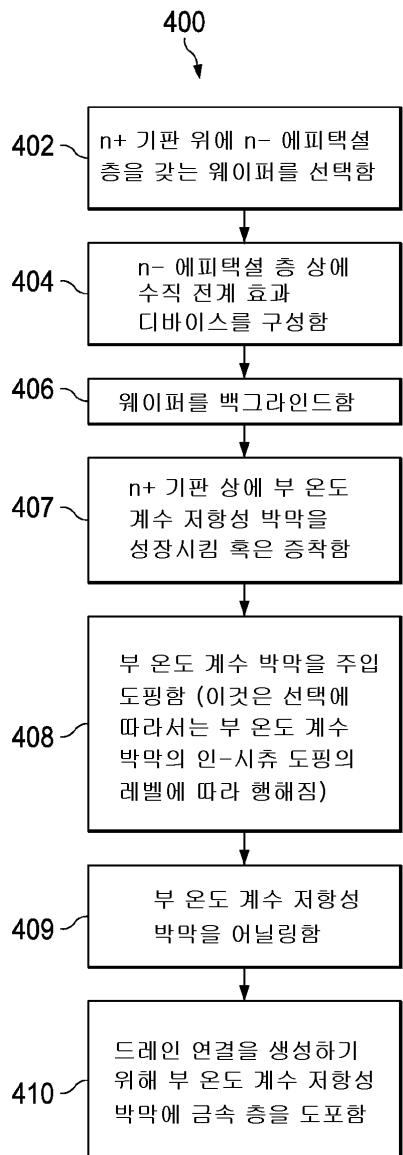

[0038] 도 4a를 참조하면, 전계 효과 디바이스 및 기판의 바람직한 실시예를 구성하는 바람직한 방법(400)이 설명된다. 단계(402)에서, n<sup>+</sup> 기판의 상부 상에 n<sup>-</sup> 에피택셜 층을 갖는 웨이퍼가 반도체 기판으로서 선택된다. 이러한 웨이퍼에서, n<sup>-</sup> 에피택셜 층은 에피택셜 층 성장 동안 정당한 n<sup>-</sup> 레벨까지 도핑된다. 단계(404)에서, 수직 전계 효과 디바이스가 n<sup>-</sup> 에피택셜 층 상에 구성된다. 바람직한 실시예에서, MOSFET은 수직 전계 효과 디바이스이다.

[0039] 단계(406)에서는, 웨이퍼 두께를 감소시키기 위해 제 2 면 상에 백그라인드(backgrind)가 행해진다.

[0040] 단계(407)에서, NTC 저항성 박막이 n<sup>+</sup> 기판 상에 성장 혹은 증착된다. 예를 들어, NTC 저항성 박막은 제 2 면 상에 증착 혹은 성장되는 폴리실리콘으로 만들어질 수 있거나, 또는 스퍼터링 혹은 다른 방법에 의해 증착되는 비정질 실리콘으로 만들어질 수 있다. NTC 저항성 박막은 인-시츄로 도핑될 수 있다.

[0041] 단계(408)에서는, NTC 저항성 박막이 인-시츄로 도핑되었는지 여부에 따라 그리고 이러한 도핑이 원하는 부 온도 계수 특성들을 달성하기에 충분한지 여부에 따라, NTC 저항성 박막이 원하는 부 온도 계수의 저항을 갖도록 하기 위해 NTC 저항성 박막은 주입에 의해 더 도핑될 수 있다. 단계(409)에서, NTC 저항성 박막은 (예를 들어, 레이저 어닐링 혹은 RF 어닐링에 의해) 어닐링된다.

[0042] 단계(410)에서는, 드레인 연결을 생성하기 위해 NTC 저항성 박막에 금속 층이 도포된다.

[0043] 도 4b를 참조하면, 전계 효과 디바이스 및 기판의 바람직한 실시예를 구성하는 다른 방법(411)이 설명된다. 단계(412)에서, n<sup>+</sup> 기판의 상부 상에 n<sup>-</sup> 에피택셜 층을 갖는 웨이퍼가 반도체 기판으로서 선택된다. 단계(413)에서, 수직 전계 효과 디바이스가 n<sup>-</sup> 에피택셜 층 상에 구성된다. 바람직한 실시예에서, MOSFET은 수직 전계 효과 디바이스이다. 단계(414)에서는, 제 2 면 상에 백그라인드가 행해진다. 단계(415)에서는, NTC 저항성 박막이 n<sup>+</sup> 기판 상에서 성장 혹은 증착된다. NTC 저항성 박막은 원하는 부 온도 계수를 달성하기 위해 인-시츄로 도핑되는 실리콘-니켈 혹은 실리콘-크롬으로부터 만들어지는 금속화된 저항성 박막이다. 단계(416)에서는, 금속화된 NTC 저항성 박막에 대해, 금속화된 박막의 어닐링을 위해 저온 신타팅(low temp sintering)이 행해질 수 있다. 단계(418)에서는, 드레인 연결을 생성하기 위해 NTC 저항성 박막에 금속 층이 도포된다.

[0044] 도 4c를 참조하여, 수직 전계 효과 디바이스를 구성하는 다른 방법(425)이 설명될 것이다. 단계(427)에서, 기판에 대해 n<sup>-</sup> 논-에피택셜 웨이퍼(non-epitaxial wafer)가 선택된다.

[0045] 단계(429)에서, 수직 전계 효과 디바이스가 제 1 면 상에 구성된다. 단계(431)에서, 제 2 면 상에 백그라인드가 행해진다. 단계(432)에서, n<sup>+</sup> 드레인 영역이 제 2 면 상에 주입된다. 단계(433)에서, n<sup>+</sup> 드레인 영역이 어닐링된다. 단계(435)에서, NTC 저항성 박막이 제 2 면 상에 성장 혹은 증착되며, 여기서 저항성 막은 인-시츄로 도핑될 수 있다. 단계(436)에서는, NTC 저항성 박막이 인-시츄로 도핑되었는지 여부에 따라 그리고 이러한 도핑이 원하는 부 온도 계수 특성들을 달성하기에 충분한지 여부에 따라, NTC 저항성 막이 주입에 의해 더 도핑될 수 있다. 단계(438)에서는, NTC 저항성 박막이 어닐링된다. 단계(439)에서는, 드레인 연결을 생성하기 위해 제 2 면이 금속화된다.

- [0046] 도 4d를 참조하면, 수직 전계 효과 디바이스를 구성하는 다른 방법(440)이 설명된다. 단계(441)에서, 기판에 대해 n- 논-에피택셜 웨이퍼가 선택된다.

- [0047] 단계(443)에서, 수직 전계 효과 디바이스가 제 1 면 상에 구성된다. 단계(444)에서, 제 2 면 상에 백그라인드가 행해진다.

- [0048] 단계(445)에서, n+ 드레인 영역이 제 2 면 상에 주입된다. 단계(446)에서, n+ 드레인 영역이 어닐링된다. 단계(447)에서, NTC 저항성 박막이 제 2 면 상에 성장 혹은 증착된다. 단계(448)에서는, 원하는 부 온도 계수 특성을 달성하기 위해 NTC 저항성 박막이 주입을 통해 도핑된다. 단계(449)에서는, NTC 저항성 박막이 어닐링된다. 단계(450)에서는, 드레인 연결을 생성하기 위해 제 2 면이 금속화된다.

- [0049] 도 4e를 참조하여, 수직 전계 효과 디바이스를 구성하는 다른 방법(451)이 설명될 것이다. 단계(452)에서, 기판에 대해 n- 논-에피택셜 웨이퍼가 선택된다.

- [0050] 단계(456)에서, 수직 전계 효과 디바이스가 제 1 면 상에 구성된다. 단계(457)에서, 제 2 면 상에 백그라인드가 행해진다. 단계(458)에서, n+ 드레인 영역이 제 2 면 상에 주입된다. 단계(460)에서, NTC 저항성 박막이 제 2 면 상에 성장 혹은 증착되며, 여기서 박막은 인-시츄로 도핑될 수 있다. 단계(461)에서는, 저항성 박막이 인-시츄로 도핑되는지 여부에 따라 그리고 이러한 도핑이 원하는 부 온도 계수 특성을 달성하기에 충분한지 여부에 따라, NTC 저항성 막이 주입에 의해 더 도핑될 수 있다. 단계(462)에서는, n+ 드레인 영역과 NTC 저항성 박막이 함께 어닐링된다. 단계(464)에서는, 드레인 연결을 생성하기 위해 제 2 면이 금속화된다.

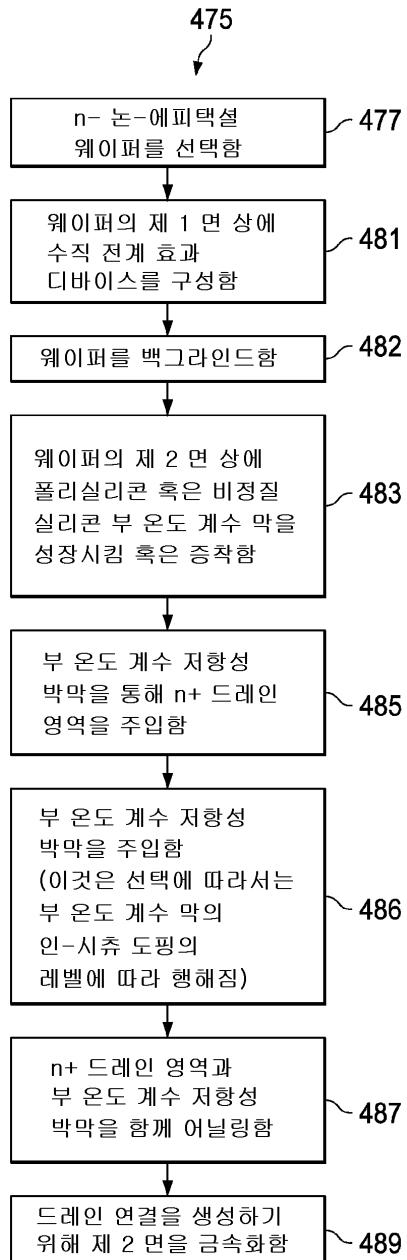

- [0051] 도 4f를 참조하여, 수직 전계 효과 디바이스를 구성하는 다른 방법(475)이 설명될 것이다. 단계(477)에서, 기판에 대해 n- 논-에피택셜 웨이퍼가 선택된다. 단계(481)에서, 수직 전계 효과 디바이스가 제 1 면 상에 구성된다. 단계(482)에서, 백그라인드가 행해진다.

- [0052] 단계(483)에서, 폴리실리콘 혹은 비정질 실리콘 NTC 저항성 막이 n- 기판 상에 성장 혹은 증착된다. 단계(485)에서, n+ 드레인 영역이 NTC 막을 통해 주입된다. NTC 막을 통해 n+ 드레인 영역을 주입하는 것에 대한 한 가지 이점은 NTC 막의 유효 깊이가 n+ 드레인 주입의 깊이에 의해 설정될 것이라는 점이다. 이것은 결과적으로 n+ 이온 주입의 정밀한 깊이 제어가 가능하기 때문에 웨이퍼에 걸쳐 유효 NTC 막 두께를 매우 균일하게 할 것이다. 단계(486)에서는, NTC 막이 인-시츄로 도핑되는지 여부에 따라 그리고 이러한 도핑이 원하는 부 온도 계수 특성을 달성하기에 충분한지 여부에 따라, NTC 저항성 막이 주입에 의해 더 도핑될 수 있다. 단계(487)에서는, NTC 드레인 영역과 NTC 막이 함께 어닐링된다. 단계(439)에서는, 드레인 연결을 생성하기 위해 제 2 면이 금속화된다.

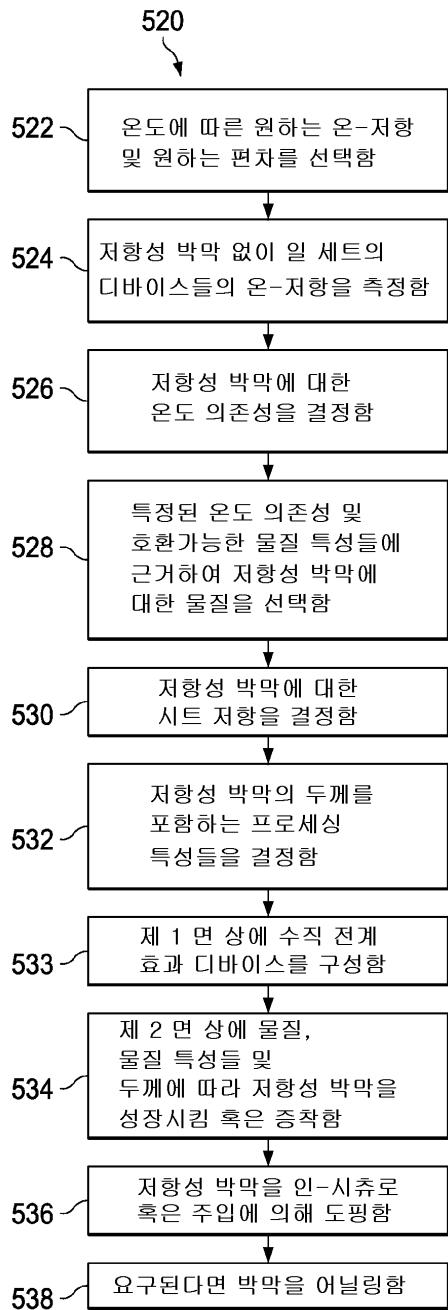

- [0053] 도 5를 참조하면, 저항성 박막을 선택 및 형성하는 방법(520)이 설명된다. 단계(522)에서는, 합성 디바이스에 대한 합성 온-저항이, 온도에 따른 온-저항의 원하는 편차와 함께 특정된다. 단계(524)에서, 일 세트의 디바이스들에 대해 접합 온도의 범위에 걸쳐 일 세트의 온-저항 값들이 측정되고 디바이스 온-저항을 결정하기 위해 평균화된다. 단계(526)에서는, 특정된 합성 온-저항으로부터 디바이스 온-저항을 뺏으로써 저항성 박막의 온도 의존성 곡선이 결정된다.

- [0054] 단계(528)에서는, 온도 의존성 곡선에 근거하여, 아울러 온도 팽창 계수를 포함하는 반도체 기판과의 물리적 호환가능성에 근거하여, 저항성 박막에 대한 물질이 선택되고 또한 특정된다. 이러한 물질은 특정 도핑 레벨을 갖는 도핀트들을 포함할 수 있다. 단계(530)에서는, 이러한 물질에 대해 저항성 박막에 대한 시트 저항이 결정된다.

- [0055] 단계(532)에서는, 저항성 박막을 생성하기 위해 일 세트의 원하는 프로세싱 특성들이 결정된다. 일 세트의 원하는 프로세싱 특성들은, 저항성 박막의 원하는 성분, 도핑 타입 및 레벨, 그리고 두께를 포함하고, 이것은 25°C에서의 특정된 저항을 시트 저항으로 나눔으로써 결정된다. 단계(533)에서, 수직 전계 디바이스가 웨이퍼의 제 1 면 상에 구성된다.

- [0056] 단계(534)에서는, 물질 특성, 프로세싱 특성 및 원하는 성분, 도핑 타입 및 레벨, 그리고 웨이퍼의 면 상의 두께에 따라 저항성 박막이 성장 혹은 증착되고 프로세싱된다.

- [0057] 단계(536)에서, 박막은 인-시츄로 혹은 주입에 의해 도핑된다. 단계(538)에서, 박막은 (어닐링이 요구된다면) 어닐링된다.

- [0058] 본 방법의 바람직한 실시예에서, 저항성 박막의 물질은 폴리실리콘, 비정질 실리콘, 실리콘-크롬, 실리콘-니켈 혹은 이들 물질의 임의의 조합을 포함하는 물질들의 그룹으로부터 선택된다. 또 하나의 다른 실시예에서는, 부

온도 계수의 저항을 달성하기 위한 물질 및 프로세싱 특성들이 도출될 수 있다면 상이한 물질이 선택될 수 있다.

[0059]

제 1 실시예에서는, 폴리실리콘 혹은 비정질 실리콘이 저항성 박막에 대한 물질로서 선택되고, 폴리실리콘은 인-시츄로 도핑된다. 제 2 바람직한 실시예에서는, 폴리실리콘 혹은 비정질 실리콘이 저항성 박막에 대한 물질로서 선택되고, 폴리실리콘 혹은 비정질 실리콘은 주입에 의해 도핑되고 후속적으로 어닐링된다. 제 1 실시예 및 제 2 실시예에서, 폴리실리콘 혹은 비정질 실리콘 박막의 도핑 레벨은  $1e17 \text{ atoms/cm}^3$  내지  $1e21 \text{ atoms/cm}^3$ 의 범위 내에 있도록 선택되고, 폴리실리콘 혹은 비정질 실리콘 박막 내의 도편트들은 베이스 온도( $25^\circ\text{C}$ )에서의 저항성 층에 대해 원하는 저항 값, 그리고 원하는 온도 의존성 곡선을 달성하기 위해 요구되는 바에 따라, 비소, 인, 붕소 혹은 이러한 원소들의 임의의 조합으로 구성되는 원소들의 그룹으로부터 선택된다.

[0060]

제 3 실시예에서는, 실리콘-크롬이 저항성 박막의 물질로서 선택된다. 실리콘-크롬 막의 실리콘 페센티지는 40% 내지 80%의 범위 내에서 선택되고, 이러한 박막은 베이스 온도(예를 들어,  $25^\circ\text{C}$ )에서의 저항성 층에 대해 원하는 시트 저항 값, 그리고 원하는 온도 의존성 곡선을 달성하기 위해 요구되는 바에 따라, 대략 25A 내지 대략 2000A의 범위 내에 있는 두께로 성장된다.

[0061]

제 4 실시예에서는, 실리콘-니켈이 저항성 박막의 물질로서 선택된다. 실리콘-니켈 막의 실리콘 페센티지는 40% 내지 80%의 범위 내에서 선택되고, 이러한 박막은 베이스 온도(예를 들어,  $25^\circ\text{C}$ )에서의 저항성 층에 대해 특정 저항 값, 그리고 원하는 온도 의존성 곡선을 달성하기 위해 요구되는 바에 따라, 대략 25A 내지 대략 2000A의 범위 내에 있는 두께로 성장된다.

[0062]

본 개시내용에서 제시되는 실시예들은 본 발명의 구현가능한 예들을 제공하기 위해 의도된 것이지, 본 발명을 한정하려고 의도된 것이 아니다. 예를 들어, Si 이외에 다른 물질들이 베이스 반도체 물질로서 사용될 수 있다. n<sup>+</sup> 영역들, n-컬럼들, p-컬럼들 및 p-타입 바디에 대한 도핑 레벨의 다양한 범위가 필요에 따라 사용될 수 있다.

도면

도면1

## 도면 1b

## 도면2a

## 도면2b

## 도면3

## 도면4a

## 도면4b

## 도면4c

## 도면4d

## 도면4e

## 도면4f

## 도면5