(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7159517号**

**(P7159517)**

(45)発行日 令和4年10月25日(2022.10.25)

(24)登録日 令和4年10月17日(2022.10.17)

(51)国際特許分類

|         |                 |     |         |       |       |

|---------|-----------------|-----|---------|-------|-------|

| G 0 6 F | 11/10 (2006.01) | F I | G 0 6 F | 11/10 | 6 3 2 |

| G 0 1 S | 13/34 (2006.01) |     | G 0 1 S | 13/34 |       |

| G 0 1 S | 7/35 (2006.01)  |     | G 0 1 S | 7/35  |       |

請求項の数 22 (全26頁)

(21)出願番号 特願2018-534798(P2018-534798)

(86)(22)出願日 平成28年12月30日(2016.12.30)

(65)公表番号 特表2019-505906(P2019-505906

A)

(43)公表日 平成31年2月28日(2019.2.28)

(86)国際出願番号 PCT/US2016/069562

(87)国際公開番号 WO2017/117557

(87)国際公開日 平成29年7月6日(2017.7.6)

審査請求日 令和1年12月22日(2019.12.22)

(31)優先権主張番号 14/985,851

(32)優先日 平成27年12月31日(2015.12.31)

(33)優先権主張国・地域又は機関

米国(US)

(73)特許権者 507107291

テキサス インスツルメンツ インコーポ

レイテッド

アメリカ合衆国 テキサス州 75265

- 5474 ダラス メイル ステイション

3999 ピーオーボックス 655474

(74)代理人 230129078

弁護士 佐藤 仁

(72)発明者 サンディープ ラオ

インド 560098 バンガロール,

シープイ ラマナガル, ナガヴァパルヤ

メイン ロード 8/9, プレスティージ

グリーンウッズ, メイプル エイ 129

カーティック ラマスプラマニアン

インド 560038 バンガロール,

最終頁に続く

(54)【発明の名称】 信号処理システムにおけるデータメモリ保護

**(57)【特許請求の範囲】****【請求項1】**

信号処理システムであって、

前記信号処理システムにより受信される少なくとも1つのデジタル信号の信号処理に対応するデータを記憶するように構成されるデータメモリ構成要素と、

前記データメモリ構成要素に関連し、複数のパリティビットを記憶するように構成されるパリティメモリ構成要素であって、前記複数のパリティビットが、前記データメモリ構成要素におけるメモリワードの複数のグループのメモリワードの各グループのためのグループパリティビットのセットを含む、前記パリティメモリ構成要素と、

前記データメモリ構成要素に結合され、前記少なくとも1つのデジタル信号を受信可能なプロセッサであって、前記少なくとも1つのデジタル信号の前記信号処理を行ない、前記データメモリ構成要素に記憶されるデータにおけるエラーについて前記複数のパリティビットをチェックするように構成される、前記プロセッサと、

前記パリティメモリ構成要素と前記プロセッサとに結合され、前記信号処理の間に前記データメモリ構成要素におけるメモリワードのアドレスと前記プロセッサによって前記メモリワードから読み出される又は前記メモリワードに書き込まれるデータとを受信可能なパリティ管理構成要素であって、前記メモリワードから読み出される値又は前記メモリワードに書き込まれる値とグループパリティビットとの間のXOR演算を実行することによつて、前記値に基づいて前記メモリワードのアドレスに対応する前記パリティメモリ構成要素に記憶される前記複数のパリティビットにおいて前記グループパリティビットを更新

するように構成され、信号処理の間に各メモリワードが同じ回数読み出されて書き込まれる、前記パリティ管理構成要素と、

を含む、信号処理システム。

**【請求項 2】**

請求項 1 に記載の信号処理システムであって、

前記複数のグループが、単一ソフトエラーがグループ毎に 1 つのメモリワードにのみ影響を及ぼし得る、メモリワードの非重複グループである、信号処理システム。

**【請求項 3】**

請求項 1 に記載の信号処理システムであって、

前記信号処理システムがレーダシステムであり、前記少なくとも 1 つのデジタル信号が

、前記レーダシステムの複数の受信チャネルによって生成される複数のデジタル中間周波数 ( I F ) 信号であり、各受信チャネルが、チャーブのフレームの送信からの反射信号を受信し、前記反射信号のサンプルのデジタル I F 信号を生成するように構成される、信号処理システム。 10

**【請求項 4】**

請求項 1 に記載の信号処理システムであって、

グループパリティビットの各セットが、メモリワードの各ビット位置のためのパリティビットから成る、信号処理システム。

**【請求項 5】**

請求項 1 に記載の信号処理システムであって、

グループパリティビットの各セットがメモリワードの各ビット位置のための P パリティビットから成り、P の値がグループにおけるワードの数 N に依存し、P と N とが 1 より大きい正の整数である、信号処理システム。 20

**【請求項 6】**

請求項 5 に記載の信号処理システムであって、

前記パリティ管理構成要素が、或るグループにおけるメモリワードの順序性に基づいて、前記グループのメモリワードに対応するグループパリティビットのサブセットを決定するように構成される、信号処理システム。

**【請求項 7】**

請求項 6 に記載の信号処理システムであって、

前記パリティ管理構成要素が、或るグループのメモリワードに対応するグループパリティビットの前記サブセットを決定するように構成されるパリティ識別回路を含み、

前記パリティ識別回路が、

前記メモリワードの順序性のバイナリ表現を受信するように結合される第 1 の構成要素であって、前記順序性の前記バイナリ表現の最も左の非ゼロビットのインデックスの第 1 のバイナリ表現を出力するように構成される、前記第 1 の構成要素と、

前記第 1 のバイナリ表現を受信するために前記第 1 の構成要素に結合され、前記順序性のバイナリ表現を受信するように結合される第 1 の加算器であって、前記第 1 のバイナリ表現と前記順序性の前記バイナリ表現との和の第 2 のバイナリ表現を出力するように構成される、前記第 1 の加算器と、 40

前記第 2 のバイナリ表現を受信するために前記第 1 の加算器に結合される第 2 の構成要素であって、前記第 2 のバイナリ表現の最も左の非ゼロビットのインデックスの第 3 のバイナリ表現を出力するように構成される、前記第 2 の構成要素と、

前記第 3 のバイナリ表現を受信するために前記第 2 の構成要素に結合され、前記順序性のバイナリ表現を受信するように結合される第 2 の加算器であって、前記第 3 のバイナリ表現と前記順序性の前記バイナリ表現との和の第 4 のバイナリ表現を出力するように構成される、前記第 2 の加算器と、

を含む、信号処理システム。

**【請求項 8】**

請求項 1 に記載の信号処理システムであって、

10

20

30

40

50

前記パリティ管理構成要素が、前記データの受信毎に、前記データに基づいて、前記メモリワードのアドレスに対応する前記パリティメモリ構成要素に記憶される前記複数のパリティビットにおいて前記グループパリティビットを更新するように更に構成される、信号処理システム。

**【請求項 9】**

信号処理システムであって、

前記信号処理システムにより受信される少なくとも1つのデジタル信号の信号処理に対応するデータを記憶するように構成されるデータメモリ構成要素と、

前記データメモリ構成要素に関連し、複数のパリティビットを記憶するように構成されるパリティメモリ構成要素であって、前記複数のパリティビットが、前記データメモリ構成要素におけるメモリワードの複数のグループのメモリワードの各グループのためのグループパリティビットのセットを含む、前記パリティメモリ構成要素と、

10

前記データメモリ構成要素に結合され、前記少なくとも1つのデジタル信号を受信可能なプロセッサであって、前記少なくとも1つのデジタル信号の前記信号処理を行ない、前記データメモリ構成要素に記憶されるデータにおけるエラーについて前記複数のパリティビットをチェックするように構成される、前記プロセッサと、

前記パリティメモリ構成要素と前記プロセッサとに結合され、前記信号処理の間に前記データメモリ構成要素におけるメモリワードのアドレスと前記プロセッサによって前記メモリワードから読み出される又は前記メモリワードに書き込まれるデータとを受信可能なパリティ管理構成要素であって、前記データの受信毎に、前記データに基づいて、前記メモリワードのアドレスに対応する前記パリティメモリ構成要素に記憶される前記複数のパリティビットにおいてグループパリティビットを更新するように構成される、前記パリティ管理構成要素と、

20

を含み、

前記複数のメモリワードの或るメモリワード位置（又はアドレス又は場所）に対するデータの各書き込みに対して、前記メモリワードの或るグループに対応するグループパリティビットが前記データに基づいて更新され、前記メモリワード位置（又はアドレス又は場所）からの前記データの单一読み出しが行なわれ、前記グループパリティビットが前記データに基づいて更新されるように、前記信号処理が、前記データメモリ構成要素の複数のメモリワードの各メモリワードを書き込む及び読み出すように構成される、信号処理システム。

30

**【請求項 10】**

請求項9に記載の信号処理システムであって、

前記パリティ管理構成要素が、パリティ更新がイネーブルされるかを示すパリティイネーブルフラグを受信するように結合され、

パリティ更新がイネーブルされた状態でのメモリワード位置（又はアドレス又は場所）へのデータの各書き込みに対し、前記メモリワード位置（又はアドレス又は場所）からの前記データの单一読み出しが、パリティ更新がイネーブルされた状態で実施されることを確実にするために、前記信号処理が前記パリティイネーブルフラグの値を管理するように構成される、信号処理システム。

40

**【請求項 11】**

信号処理システムであって、

前記信号処理システムにより受信される少なくとも1つのデジタル信号の信号処理に対応するデータを記憶するように構成されるデータメモリ構成要素と、

前記データメモリ構成要素に関連し、複数のパリティビットを記憶するように構成されるパリティメモリ構成要素であって、前記複数のパリティビットが、前記データメモリ構成要素におけるメモリワードの複数のグループのメモリワードの各グループのためのグループパリティビットのセットを含む、前記パリティメモリ構成要素と、

前記データメモリ構成要素に結合され、前記少なくとも1つのデジタル信号を受信可能なプロセッサであって、前記少なくとも1つのデジタル信号の前記信号処理を行ない、前

50

記データメモリ構成要素に記憶されるデータにおけるエラーについて前記複数のパリティビットをチェックするように構成される、前記プロセッサと、

前記パリティメモリ構成要素と前記プロセッサとに結合され、前記信号処理の間に前記データメモリ構成要素におけるメモリワードのアドレスと前記プロセッサによって前記メモリワードから読み出される又は前記メモリワードに書き込まれるデータとを受信可能なパリティ管理構成要素であって、前記データの受信毎に、前記データに基づいて、前記メモリワードのアドレスに対応する前記パリティメモリ構成要素に記憶される前記複数のパリティビットにおいてグループパリティビットを更新するように構成される、前記パリティ管理構成要素と、

を含み、

前記信号処理システムがレーダシステムであり、前記少なくとも1つのデジタル信号が、前記レーダシステムの複数の受信チャネルによって生成される複数のデジタル中間周波数（IF）信号であり、各受信チャネルが、チャーブのフレームの送信からの反射信号を受信し、前記反射信号のサンプルのデジタルIF信号を生成するように構成され、

前記信号処理が、前記複数のデジタルIF信号に対応する第1のデータを前記データメモリにおける複数のメモリワード位置（又はアドレス又は場所）に書き込むように構成されて、前記複数のメモリワード位置（又はアドレス又は場所）の各メモリワードに対し、前記パリティ管理構成要素が、前記メモリワード位置（又はアドレス又は場所）において書き込まれた前記第1のデータに基づいて前記メモリワードの或るグループに対応する前記複数のパリティビットにおける前記グループパリティビットを更新し、

前記信号処理が、更に、前記複数のメモリワード位置（又はアドレス又は場所）から前記第1のデータを読み出すように構成されて、前記複数のメモリワード位置（又はアドレス又は場所）の各メモリワードに対し、前記パリティ管理構成要素が、前記メモリワード位置（又はアドレス又は場所）から読み出された前記第1のデータに基づいて前記メモリワードの前記グループに対応する前記グループパリティビットを更新する、信号処理システム。

### 【請求項12】

請求項11に記載の信号処理システムであって、

前記信号処理が、

前記複数のデジタルIF信号に対応する第2のデータを前記データメモリにおける前記複数のメモリワード位置（又はアドレス又は場所）に書き込むように構成されて、前記複数のメモリワード位置（又はアドレス又は場所）における各メモリワードに対し、前記メモリワードの前記グループに対応するグループパリティビットが、前記メモリワード位置（又はアドレス又は場所）に書き込まれた前記第2のデータに基づいて更新され、

前記複数のメモリワード位置（又はアドレス又は場所）から前記第2のデータを読み出すように構成されて、前記複数のメモリワード位置（又はアドレス又は場所）における各メモリワードに対し、前記メモリワードの前記グループに対応する前記グループパリティビットが、前記メモリワード位置（又はアドレス又は場所）から読み出された前記第2のデータに基づいて更新され、更に、

前記第1のデータを生成するために前記第2のデータに対して信号処理を行うように構成される、信号処理システム。

### 【請求項13】

信号処理システムにおけるデータメモリ保護のための方法であって、

前記信号処理システムのデータメモリのメモリワードを複数のグループに分割することであって、前記データメモリに関連する複数のパリティビットが、前記複数のグループの各グループのためのグループパリティビットのセットを含む、前記分割することと、

前記信号処理システムにより受信される少なくとも1つのデジタル信号に対して信号処理を行なうことであって、前記データメモリの複数のメモリワードの或るメモリワード位置（又はアドレス又は場所）に対するデータの各書き込みに対し、前記メモリワード位置（又はアドレス又は場所）の或るグループに対応するグループパリティビットが前記データ

10

20

30

40

50

タに基づいて更新され、前記メモリワードからの前記データの单一読み出しが行なわれて前記グループパリティビットが前記データに基づいて更新されるように、前記データメモリの前記複数のメモリワードの各メモリワードが書き込み及び読み出しされる、前記信号処理を行なうことと、

前記複数のパリティビットに基づいてソフトエラーが生じたか否かを判定することと、

を含む、方法。

#### 【請求項 14】

請求項 13 に記載の方法であって、

前記複数のグループが、単一ソフトエラーがグループ毎に 1 つのメモリワードにのみ影響を及ぼし得る、メモリワードにおける非重複グループである、方法。 10

#### 【請求項 15】

請求項 14 に記載の方法であって、

グループパリティビットの各セットが、メモリワードの各ビット位置のためのパリティビットから成る、方法。

#### 【請求項 16】

請求項 14 に記載の方法であって、

グループパリティビットの各セットがメモリワードの各ビット位置のための P パリティビットから成り、P の値がグループにおけるワードの数 N に依存し、P と N とが 1 より大きい正の整数である、方法。 20

#### 【請求項 17】

請求項 16 に記載の方法であって、

グループのメモリワードに対応するグループパリティビットのサブセットが、前記グループにおける前記メモリワードの順序性に基づいて決定される、方法。

#### 【請求項 18】

請求項 13 に記載の方法であって、

前記信号処理を行なうことが、前記グループパリティビットを変更することなく、前記メモリワード位置（又はアドレス又は場所）からの前記データの読み出しを可能にするために、パリティ更新をディセーブルすることを含む、方法。 30

#### 【請求項 19】

請求項 13 に記載の方法であって、

前記信号処理システムが、レーダーシステムであり、前記少なくとも 1 つのデジタル信号が、前記レーダーシステムにおける複数の受信チャネルによって生成される複数のデジタル中間周波数（IF）信号である、方法。

#### 【請求項 20】

請求項 19 に記載の方法であって、

前記信号処理を行なうことが、

前記デジタル IF 信号の信号処理に対応する第 1 のデータを複数のメモリワード位置（又はアドレス又は場所）に書き込むことであって、前記複数のメモリワード位置（又はアドレス又は場所）における各メモリワードに対し、前記メモリワードの或るグループに対応するグループパリティビットが更新される、前記書き込むことと、 40

前記複数のメモリワード位置（又はアドレス又は場所）から前記第 1 のデータを読み出すことであって、前記複数のメモリワード位置（又はアドレス又は場所）における各メモリワードに対し、前記メモリワードの前記グループに対応する前記グループパリティビットが更新される、前記読み出すことと、

を含む、方法。

#### 【請求項 21】

請求項 20 に記載の方法であって、

前記信号処理を行なうことが、

前記デジタル IF 信号の信号処理に対応する第 2 のデータを前記複数のメモリワード位置（又はアドレス又は場所）に書き込むことであって、前記複数のメモリワード位置（又

はアドレス又は場所)における各メモリワードに対し、前記メモリワードの前記グループに対応するグループパリティビットが更新される、前記書き込むことと、

前記複数のメモリワード位置(又はアドレス又は場所)から前記第2のデータを読み出すことであって、前記複数のメモリワード位置(又はアドレス又は場所)における各メモリワードに対し、前記メモリワードの前記グループに対応する前記グループパリティビットが更新される、前記読み出すことと、

前記第1のデータを生成するために前記第2のデータに対して信号処理を行うことと、

を更に含む、方法。

#### 【請求項22】

信号処理システムにおけるデータメモリ保護のための方法であって、

10

前記信号処理システムのデータメモリのメモリワードを複数のグループに分割することであって、前記データメモリに関連する複数のパリティビットが、前記複数のグループの各グループのためのグループパリティビットのセットを含む、前記分割することと、

前記信号処理システムにより受信される少なくとも1つのデジタル信号に対して信号処理を行なうことであって、前記データメモリの複数のメモリワードの或るメモリワード位置(又はアドレス又は場所)に対するデータの各書き込みに対し、前記メモリワード位置(又はアドレス又は場所)の或るグループに対応するグループパリティビットが前記データに基づいて更新され、前記メモリワードからの前記データの单一読み出しが行なわれて前記グループパリティビットが前記データに基づいて更新されるように、前記データメモリの前記複数のメモリワードの各メモリワードが書き込み及び読み出しされる、前記信号処理を行なうことと、

20

を含む、方法。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本願は、概して、信号処理システムに関し、詳細には、信号処理システムにおいて信号データメモリを保護することに関する。

##### 【背景技術】

##### 【0002】

オートモーティブ応用例において埋め込み周波数変調連続波(FMCW)レーダシステムの使用が急速に発展している。例えば、埋め込みFMCWレーダシステムは、アダプティブクルーズコントロールや、衝突警告、死角警告、車線変更アシスト、駐車アシスト、後方衝突警告など、車両に関連する多くの応用例において用いられる。オートモーティブ応用例において用いられるために、埋め込みFMCWレーダシステムは、厳格な機能安全要件を満たすことが要求される。自動車レーダにおける機能安全性は、レーダにおける構成要素の故障に起因する、人に対する危害の防止策である。これらの要件を満たすことは、レーダシステムにおいて種々の保護メカニズムを含むことを必要とする。こうした保護メカニズムは、レーダシステムに組み込まれる任意のプロセッサ、デジタル論理、及びメモリなどの構成要素の動作不良に起因する故障を最小化するか又はなくす。また、厳格な機能安全要件を伴う環境において用いられる場合、その他の信号処理システムが、同様の保護メカニズムを含み得る。

30

##### 【発明の概要】

##### 【0003】

説明される例は、レーダシステムなどの信号処理システムにおける信号データメモリの保護のための方法及び装置に関する。一つの態様において、信号処理システムが、少なくとも一つのデジタル信号の信号処理に対応する値をストアするように構成されるデータメモリ構成要素と、データメモリ構成要素に関連する複数のパリティビットと、少なくとも一つのデジタル信号を受信するように結合されるプロセッサと、複数のパリティビットに結合され、データメモリ構成要素におけるメモリワードのアドレスを、及び、信号処理の間、プロセッサによってメモリワードから読み出されるか又はメモリワードに書き込まれ

40

50

る値を受信するように結合される、パリティ管理構成要素とを含む。複数のパリティビットは、データメモリ構成要素におけるメモリワードの複数のグループのメモリワードの各グループについて、グループパリティビットのセットを含む。プロセッサは、少なくとも一つのデジタル信号の信号処理を行なうように、及び、メモリエラーについて複数のパリティビットをチェックするように構成される。パリティ管理構成要素は、値に基づいて、メモリワードのアドレスに対応する複数のパリティビットにおけるグループパリティビットを更新するように構成される。

#### 【0004】

一つの態様において、信号処理システムにおけるデータメモリ保護のための方法が、信号処理システムのデータメモリのメモリワードを複数グループに分割すること、少なくとも一つのデジタル信号に対して信号処理を行なうこと、及び、複数のパリティビットに基づいて、ソフトエラーが生じたか否かを判定することを含む。複数グループに分割することにおいて、データメモリに関連する複数のパリティビットは、複数のグループの各グループについて、グループパリティビットのセットを含む。信号処理を行なうことにおいて、データメモリの複数のメモリワードの各メモリワードが書き込み及び読み出しされ、そのため、複数のメモリワードの或るメモリワードに対する或る値の各書き込みに対して、メモリワードの或るグループに対応するグループパリティビットがその値に基づいて更新され、メモリワードからの値の单一読み出しが行なわれ、グループパリティビットがその値に基づいて更新される。

10

#### 【図面の簡単な説明】

20

#### 【0005】

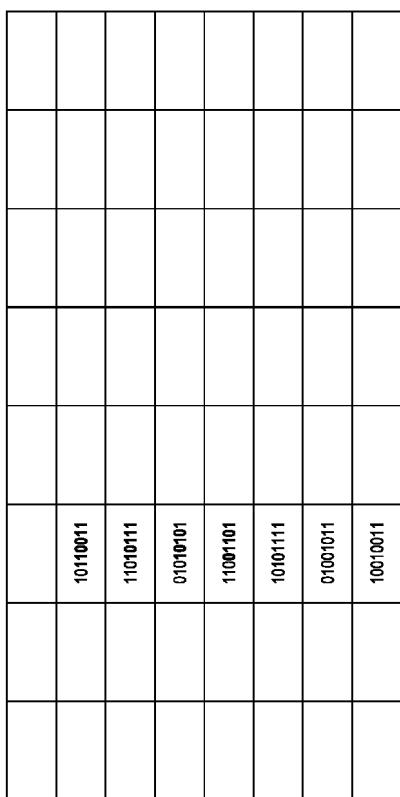

【図1】メモリ上の單一ソフトエラーの影響を図示する例である。

#### 【0006】

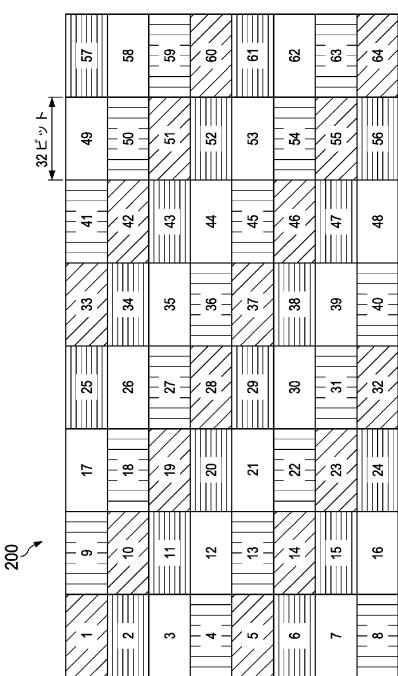

【図2】対角線状グルーピングを備えるレーダデータメモリを図示する例である。

#### 【0007】

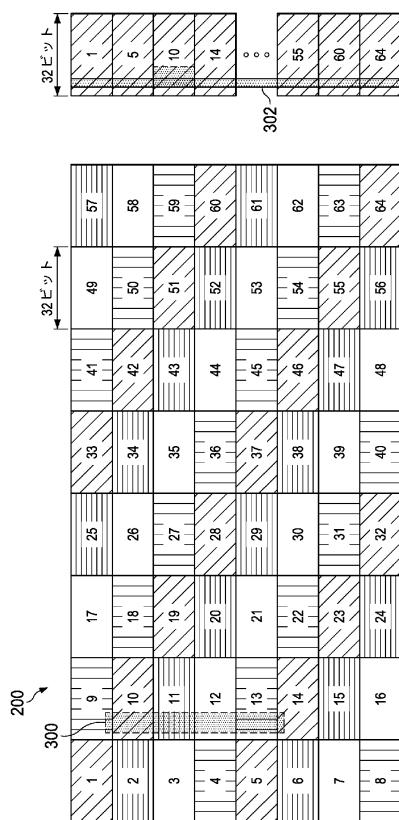

【図3】一つのソフトエラー発生に対する保護のため、図2のレーダデータメモリに対するパリティビット割り当てを図示する例である。

#### 【0008】

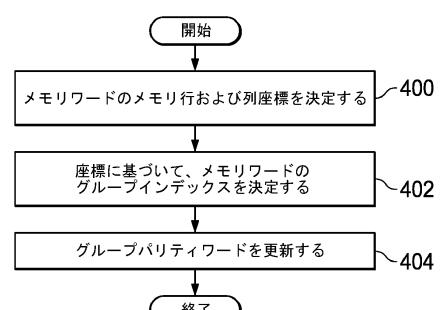

【図4】レーダデータメモリのパリティワードを更新するための方法のフローチャートである。

30

#### 【0009】

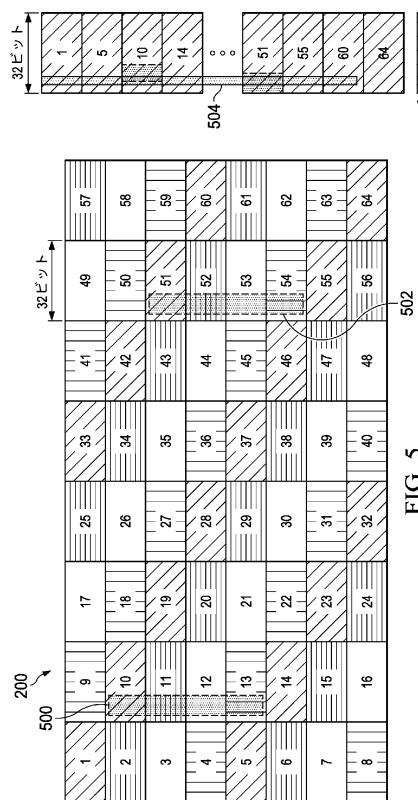

【図5】2つのソフトエラー発生に対する保護のため、図2のレーダデータメモリに対するパリティビット割り当てを図示する例である。

#### 【0010】

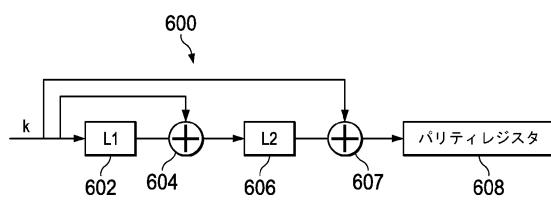

【図6】パリティ識別回路のブロック図である。

#### 【0011】

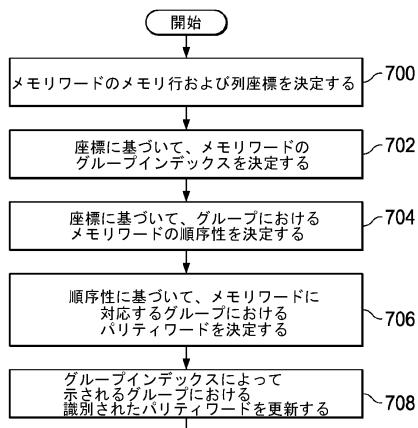

【図7】レーダデータメモリのパリティワードを更新するための方法のフローチャートである。

#### 【0012】

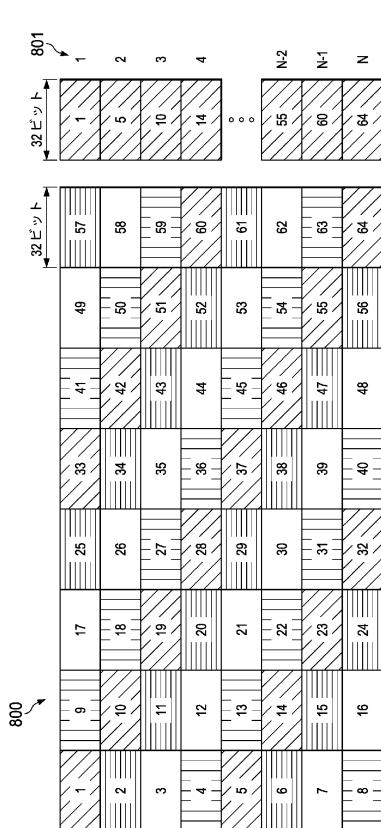

【図8】或るグループにおけるメモリワードの順序性を図示する例である。

40

#### 【0013】

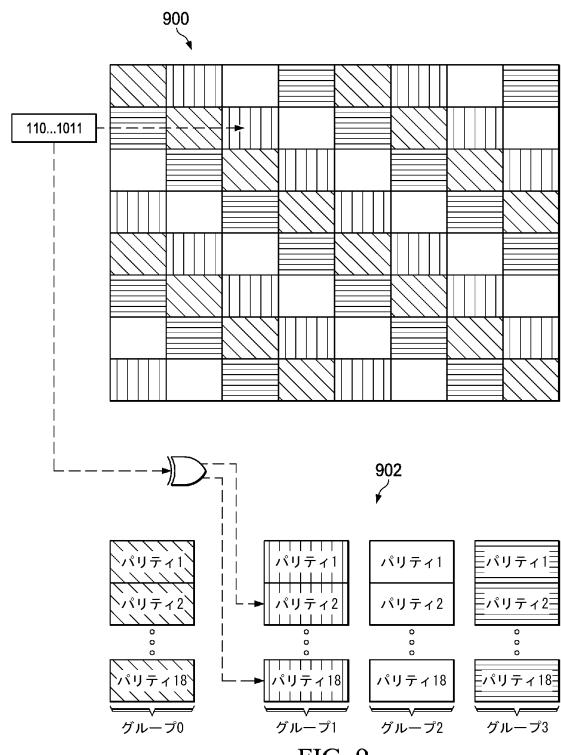

【図9】図7の方法を図示する例である。

#### 【0014】

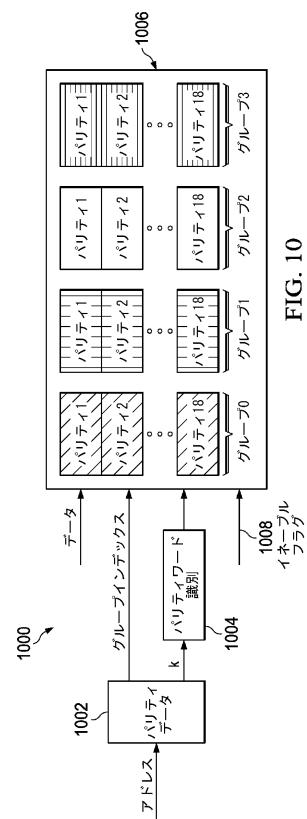

【図10】例示のパリティ管理構成要素のブロック図である。

#### 【0015】

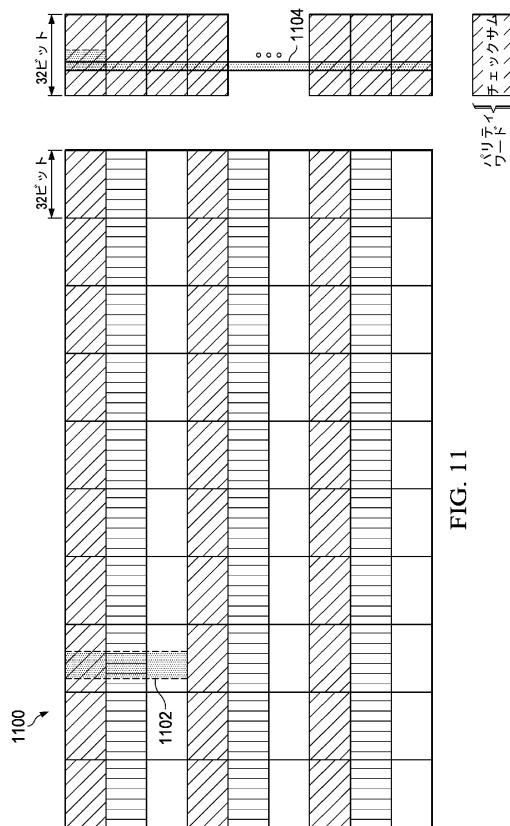

【図11】行方向のメモリグルーピングを備える、一つのソフトエラー発生に対する保護のための、レーダデータメモリに対するパリティビット割り当てを図示する例である。

#### 【0016】

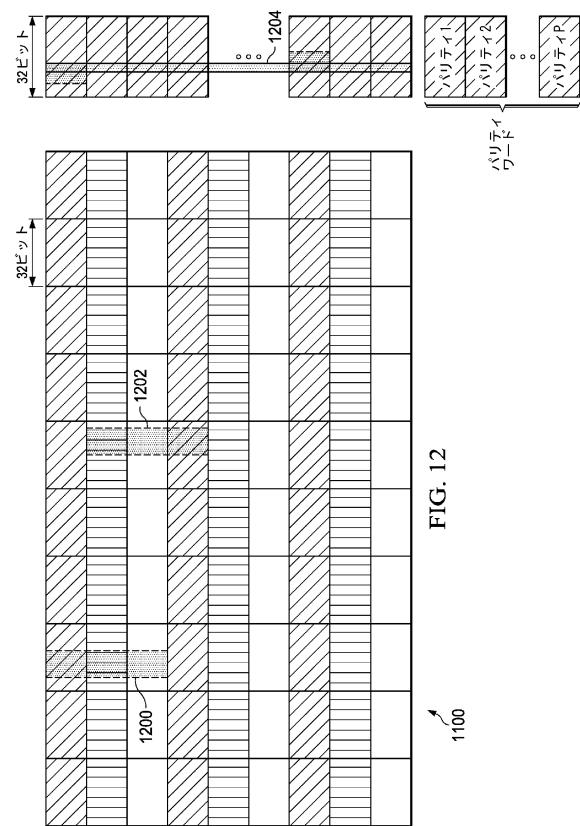

【図12】行方向のメモリグルーピングを備える、2つのソフトエラー発生に対する保護のための、レーダデータメモリに対するパリティビット割り当てを図示する例である。

50

**【 0 0 1 7 】**

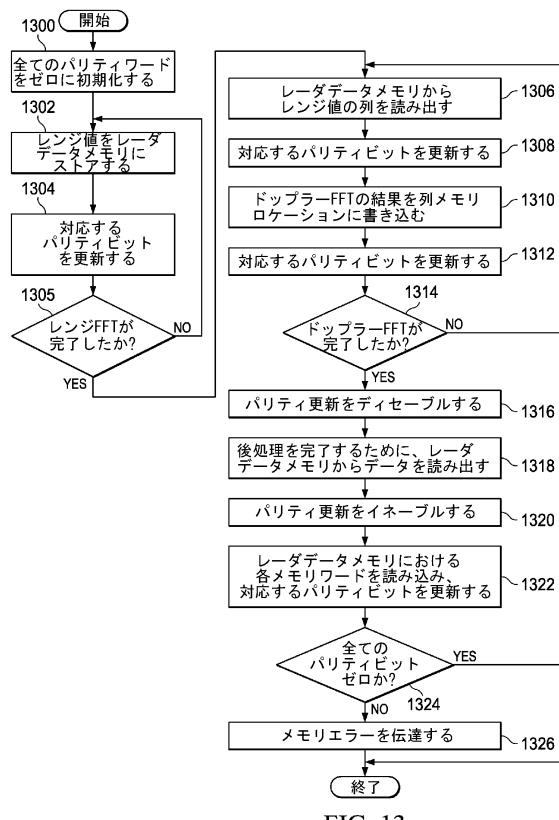

【図13】レーダシステムにおけるレーダデータメモリの保護のための方法のフローチャートである。

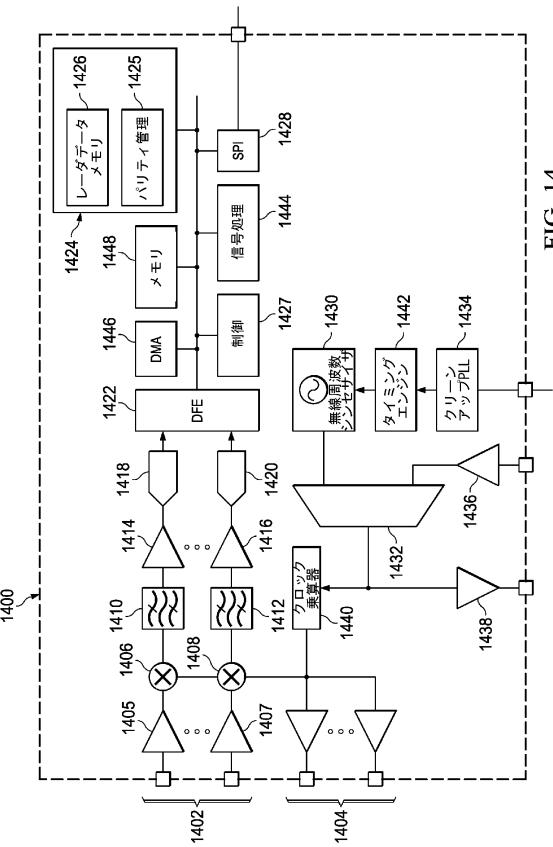

**【 0 0 1 8 】**

【図14】例示の周波数変調連続波(FMCW)レーダシステムのブロック図である。

**【発明を実施するための形態】****【 0 0 1 9 】**

種々の図面における同様の要素は、一貫性のため、同様の参照数字によって表記される。

**【 0 0 2 0 】**

周波数変調連続波(FMCW)レーダは、一つ又は複数の送信アンテナを介して、チャーブと呼ばれる無線周波数(RF)周波数ランプを送信する。また、複数のチャーブが、フレームと呼ばれる単位で送信され得る。送信されたチャーブは、レーダの視野(FOV)における任意のオブジェクトから反射され、一つ又は複数の受信アンテナによって受信される。各受信アンテナに対して受信された信号は、中間周波数(IF)信号にダウンコンバートされ、その後、デジタル化される。デジタル化されたサンプルは、前処理され、本願においてレーダデータメモリと呼ばれるメモリにストアされる。全フレームのためのデータがレーダデータメモリにストアされた後、データは、FOVにおける任意のオブジェクトを検出するために、及び、検出されたオブジェクトのレンジ、速度、及び、到来角を識別するために、後処理される。

10

**【 0 0 2 1 】**

前処理は、データを周波数ドメインに変換するために、各反射されたチャーブのデジタル化されたサンプルに対してレンジ高速フーリエ変換(FFT)を実施することを含み得る。ピーク値が、オブジェクトのレンジ(距離)に対応する。この処理は、通常、インラインで実施され、そのため、レンジFFTが、前のチャーブのデジタル化されたサンプルに対して実施される一方で、現在のチャーブのためにサンプルが集められている。各受信アンテナのためのレンジFFTの結果は、更なる処理のためにレーダデータメモリに保存される。K1レンジ結果が、チャーブのためにストアされる。それゆえ、K2チャーブがフレーム内にある場合、K1×K2レンジ値のアレイが、レンジFFTによって生成される。このアレイにおいて、K1列の各々は、K2チャーブの特定のレンジ値に対応する。K1×K2レンジ値が、システムにおける各受信チャンネルのために生成される。

20

**【 0 0 2 2 】**

各レンジに対し、フレームにおけるチャーブの対応するレンジ値の各々にわたってドップラーフ FFTが実施される。従って、K1×K2アレイのK1列の各々に対してドップラーフ FFTが実施される。その結果のK1×K2レンジドップラーアレイにおけるピークは、潜在的なオブジェクトのレンジ及び相対的速度(速度)に対応する。ドップラーフ FFTを実施するために、レンジ値の各列がレーダデータメモリから読み出され、列のレンジ値に対してドップラーフ FFTが実施される。ドップラーフ FFT値は、同じ列メモリロケーションにストアされ得る。

30

**【 0 0 2 3 】**

ドップラーフ FFTの後、FOVにおけるオブジェクトを検出するために、及び、検出されたオブジェクトのレンジ、速度、及び、到来角を識別するために、その後処理、例えば、オブジェクト検出及び角度推定が、レーダデータメモリにストアされたK1否かを判定K2レンジドップラーアレイに対して実施され得る。後処理が完了した後、レーダデータメモリにおけるデータは捨てられてよい。

40

**【 0 0 2 4 】**

ドップラーフ FFT、角度推定、オブジェクト検出等などの後処理が開始され得る前に、フレームに対応する全てのデジタル化されたデータは、レーダデータメモリ内にある必要がある。また、分解能予想、すなわち、チャーブ毎のデジタル化されたサンプルの数によって制御されるレンジ分解能、フレーム毎のチャーブの数によって制御される速度分解能、及び、受信アンテナの数によって制御される角度分解能が、レーダデータメモリのサイ

50

ズに直接影響する。オートモーティブレーダ応用例空間において、必要とされる現在のレーダデータメモリサイズは、約 1 ~ 2 メガバイト (MB) であり、分解能増加が要求されるにつれて、将来、増加することが予測される。

#### 【0025】

上述されたように、オートモーティブ応用例における埋め込みレーダシステムの使用のための機能安全要件は、システムの種々の構成要素のための保護メカニズムの組み込みを要する。レーダデータメモリは、効果的な保護メカニズムを必要とする構成要素の一つである。メモリロケーションにおける一つ又は複数のビットの値を変化させるソフトエラーは、懸念されるメモリエラーの一つのカテゴリである。ソフトエラーは、放射又は放射性粒子がメモリセルとぶつかりセルの状態を変化させる、すなわち「1」が「0」に又はその逆に変化することによって生じ得る。

10

#### 【0026】

ソフトエラー保護のための現在の産業的解決策は、誤り訂正符号 (ECC) メモリを用いることである。ECC メモリにおいて、メモリにおける各ワードは、パリティビットのセットによって保護される。特定のメモリワードにデータが書き込まれる度、このデータに対応するパリティ値が、計算され、関連するパリティビットにストアされる。メモリワードが読み出されるとき、パリティ値が、再計算され、ストアされたパリティ値に対して検証される。ストアされたパリティ値と再計算されたパリティ値との如何なる差もビットエラーの存在を示す。

20

#### 【0027】

用いられる特定のパリティコードに依って、パリティビットは、ビットエラーを検出するため、或いは、ビットエラーを検出及び訂正するために用いられ得る。いくつかの典型的な ECC メモリは、拡張ハミング符号パリティスキームを用い、拡張ハミング符号パリティスキームは、単一ビットエラーを訂正し、1ワードにおいて最大 2 つのビットエラーを検出する能力を備える。拡張ハミング符号スキームに必要とされるパリティビットの数は、メモリワードの長さに依る。例えば、16ビットメモリワードは、6 パリティビットを必要とし、32ビットメモリワードは 7 パリティビットを必要とする。

#### 【0028】

ECC メモリにおけるメモリワードのサイズは、データが読み出される / 書き込まれると予測される最小単位として選ばれる。レーダデータメモリの文脈では、メモリワードサイズは、複合サンプルの典型サイズに基づき、例えば 32 ビットである。それゆえ、レーダデータメモリのために拡張ハミング符号パリティスキームを実装することは、32 ビット毎に 7 ビットのオーバーヘッドを必要とし得、これは、約 22 % のオーバーヘッドである。従って、約 400KB (キロバイト) のオーバーヘッドが、2MB のレーダデータメモリに必要とされ得る。これは、コスト重視の埋め込みレーダの解決策にとって、著しい量のオーバーヘッドである。

30

#### 【0029】

例示の実施形態は、最小オーバーヘッドを有する、レーダデータメモリ保護のための代替の技法を提供する。このメモリ保護技法は、レーダデータメモリに関する 2 つの主要な観察結果に基づく。一方の観察結果は、レーダデータメモリへのほとんどのアクセスがランダムでないことである。むしろ、チャーブのフレームに対応する受信された信号の前処理の間、明確に定義された書き込みフェーズが存在し、この書き込みフェーズにおいて、レンジ値がメモリにストアされる。この書き込みフェーズの後、ストアされたレンジ値の後処理の間、読み出しフェーズが続く。読み出しフェーズにおいて、全てのレンジ値が読み出されるが、値がストアされたのと同じ順序で読み出されるのではない。他方の観察結果は、エラー訂正が、レーダデータメモリにとっては比較的重要でないことである。レーダデータメモリにおいて読み出される及び書き込まれるデータは、チャーブの一つのフレームから次のフレームへ独立しているので、エラー検出は充分である。後処理の間にメモリエラーが検出される場合、メモリにおけるデータは捨てられてよい。

40

#### 【0030】

50

レーダデータメモリ保護技法の実施形態は、ECCメモリにおけるような、各メモリワードのためのパリティビットのセットを必要とするのではなく、パリティビットの共通セットを用いて、全レーダデータメモリの保護を提供する。これらの共通パリティビットは、レーダデータメモリにおけるワードがレーダデータ処理の一部として読み出される又は書き込まれる度に更新され得る。本願においてより詳細に説明されるように、この保護技法により、メモリエラーがない場合にレーダデータをストアするために用いられるレーダデータメモリにおける各ワードが、同じ回数書き込み及び読み出しされる限り、共通パリティビットが、チャーブのフレームに対応するレーダデータの処理の最後にゼロであることが保証される。処理の最後の、共通パリティビットのいずれかにおける非ゼロ値は、少なくとも一つのメモリエラーを示す。

10

#### 【0031】

レーダデータメモリ保護の実施形態において、レーダデータメモリが、非重複グループに分割され、各グループが、共通パリティビットにおけるパリティビットのセットによって保護される。いくつかの実施形態において、グルーピングは、単一ソフトエラーが、グループ毎に最大一つのワードに影響を及ぼすことを保証するように選択される。用いられるパリティチェック技法は、それから保護するべきソフトエラーの数に基づく。例えば、本願において一層詳細に説明されるように、単一ソフトエラー保護が必要とされる場合、シンプルなチェックサムスキームが用いられ得、一方で、2つのソフトエラーに対する保護が必要とされる場合、ハミング符号スキームが用いられ得る。

20

#### 【0032】

上述したように、ソフトエラーは、メモリにおける放射誘導されたビットフリップである。図1の例に示すように、単一ソフトエラーが、行方向及び列方向の両方の、メモリにおける複数の隣接ビットにおいてビットエラーを起こし得、それゆえ、単一ワードにおける複数の隣接ビット（及び複数の列方向の隣接ワード）が、単一ソフトエラーによって影響を及ぼされ得る。図1の例では、単一ソフトエラーが、各ワードにおいて4つの影響を受けた隣接ビットを有する、4つの列方向の隣接8ビットワードに影響を及ぼしている。図1の例は、影響を受ける隣接ビットの最大数、及び、影響を受ける列方向の隣接ワードの最大数が4であると想定している。

#### 【0033】

レーダデータメモリ保護の幾つかの実施形態において、レーダデータメモリは、M個の非重複グループに分割され、ここで、Mの値は、単一ソフトエラーが、グループ毎に一つ以下のワードに影響を及ぼすように選ばれる。幾つかの実施形態において、単一ワードにおける隣接ビットの最大数、及び、単一ソフトエラーによって影響を及ぼされる列方向の隣接ワードの最大数は同じであり、Mは、この最大数であるように設定される。幾つかの実施形態において、影響を及ぼされる隣接ビットの最大数、及び、影響を及ぼされる列方向の隣接ワードの最大数は同じでなく、Mは、これら2つの数の大きい方であるように設定される。影響を及ぼされる隣接ビットの最大数、及び、影響を及ぼされる列方向の隣接ワードの最大数は、小型化のレベルが上がるにつれて大きくなり得る。従って、Mの値は、メモリデバイス及びメモリアーキテクチャの物理的性質などの要因に依る。

30

#### 【0034】

説明を簡潔にするため、レーダデータメモリ保護を、まず、図2、図3、図5、及び、図8～図10の例に関連して説明する。これらの例は、M=4、32ビットメモリワード、及び、1サイクルに最大4つの連続32ビットワードを伝送し得る直接メモリアクセス(DMA)コントローラを想定している。これらの例において、各セルは32ビットワードを表し、セルは、グループ割り当てを示すために「網掛け」されている。メモリストール及びスループットロスを避けるため、行方向及び列方向両方の4つの隣接ワードが異なるグループにあるように、ワードは対角線状にグルーピングされる。この例において示される対角線状のグルーピングは、左上から右下である。このようなグルーピングにより、パリティワードが、メモリサイクル毎に2回以上更新される必要がないことが保証される。図2は、対角線状グルーピングを備えるレーダデータメモリ200を図示する例である

40

50

。各メモリセルは、グループ割り当てを示すために「網掛け」されている。また、各メモリセルは、説明のために番号付けされている。

#### 【 0 0 3 5 】

M個のグループの各々が、パリティビットのセットによって保護される。パリティビットのセットは、本願においてグループパリティビットと呼ぶこともある。各グループに必要とされるパリティビットの数、及び、メモリアクセスの間、パリティビットがどのように更新されるかは、レーダシステムの特定の応用例の機能安全要件に依る。幾つかの実施形態において、メモリ保護は、チャープのフレームのためのレーダデータの処理の間の単一ソフトエラー発生に対して保護する。そのような実施形態において、或るグループに割り当てられるワードの各ビット位置の保護のために、パリティビットが割り振られる。例えば、32ビットメモリワードでは、32個のビット位置が存在し、そのため、各グループに32ビットパリティワードが必要とされる。それゆえ、M個の32ビットパリティワードが必要とされる。また、図4の方法に関連して一層詳細に説明するように、関連するパリティワードにストアされた値は、本質的にメモリグループのチェックサムである。

10

#### 【 0 0 3 6 】

図3は、レーダデータメモリ200のためのこのパリティビット割り当てを図示する例である。この例では、メモリワード1、5、10、14、…、55、60、64は、同じグループに割り当てられている。M×M領域300は、単一ソフトエラーによって影響を及ぼされ得るメモリの例示の部分を図示する。領域300が示すように、このようにしてレーダデータメモリをM個のグループに分割することは、単一ソフトエラーが、グループ毎に一ワードにしか影響を及ぼさないことを保証する。図3の右側に、このグループのためのメモリワードが、例示のため垂直にスタックされており、関連する32ビットパリティワードがこのスタックの下に示されている。また、グループの各ワードにおける例示のビット位置のビットの例示の列302が、パリティワードにおける関連するパリティビットと共に示されている。

20

#### 【 0 0 3 7 】

図4は、単一ソフトエラーに対する上述のメモリ保護を想定した、レーダデータメモリのパリティワードを更新するための方法のフローチャートである。この方法は、レーダデータメモリにおけるメモリワードの読み出し又は書き込みのために実施される。メモリワードがアクセスされるとき、メモリワードのレーダデータメモリにおける行及び列座標は、メモリワードのアドレスに基づいて決定される(400)。アドレスの行番号が、R = floor(Address / NumColumns)として計算され得、アドレスの列番号が、C = mod(Address, NumColumns)として計算され得、ここで、NumColumnsは、レーダデータメモリにおける列の数であり、関数modは、モジュロ演算子を指し、mod(a, b)の結果は、aをbで除算した余りである。前述の式において、メモリワードは、行の端から端へ水平にアドレスされると想定される。また、メモリワードのアドレス、行番号R、及び、列番号Cは、ゼロから数えられる。メモリの列及び行の数は、メモリ設計によって決定される。

30

#### 【 0 0 3 8 】

その後、メモリワードのグループインデックスが、行及び列座標に基づいて決定される(402)。グループが、0、1、…、M-1でインデックスされると想定すると、メモリワードのグループを識別するインデックスgroup\_idxは、

$$group\_idx = mod(R - mod(C, M), M)$$

40

によって計算され得、ここで、Rはメモリ行番号であり、Cはメモリワードのメモリ列番号である。その後、グループインデックスによって識別されたグループパリティワードは更新される(404)。より具体的には、グループインデックスによって識別されたパリティワードは、メモリワードのデータと、識別されたパリティワードの現在のコンテンツとのXOR演算を実施することによって更新される。

#### 【 0 0 3 9 】

幾つかの実施形態において、メモリ保護は、チャープのフレームのためのレーダデータ

50

の処理の間の 2 つのソフトエラー発生に対して保護する。それゆえ、各グループにおいて最大 2 つのワードが、ソフトエラーによって影響を及ぼされ得る。図 5 は、レーダデータメモリ 200 が、 $M \times M$  領域 500 及び  $M \times M$  領域 502 により示される 2 つのソフトエラーによって影響を及ぼされることを図示する例である。この例では、各グループからの 2 つのワードが影響を及ぼされる。そのような実施形態において、或るグループに割り当てられるワードの各ビット位置の保護のために、P 個のパリティビットの一セットが割り振られる。例えば、32 ビットメモリワードでは、32 個のビット位置が存在し、そのため、各グループに P 個の 32 ビットパリティワードが必要とされる。それゆえ、 $M \times P$  個の 32 ビットパリティワードが必要とされる。本願において一層詳細に説明されるよう 10 に、P 個のパリティビットは、最大 2 つのビットエラーを検出するハミング符号に対応する。

#### 【0040】

図 5 は、このパリティビット割り当てを図示する。この例では、メモリワード 1、5、10、14、…、55、60、64 は、同じグループに割り当てられている。図 5 の右側に、このグループのためのメモリワードが、例示のため垂直にスタックされており、関連する P 個の 32 ビットパリティワードが、このスタックの下に示されている。また、グループの各ワードにおける例示のビット位置のビットの例示の列 504 が、パリティワードにおける関連するパリティビットと共に示されている。グループにおけるビットの各そのような列は、P 個のパリティビットの列によって保護される。それゆえ、グループにおける各列は、N データビットのハミング符号ワードとして見ることができ、ここで、N は、グループにおけるメモリワードの数であり、P はパリティビットの数である。それゆえ、或るグループの 32 個の列は、各々が最大 2 つのエラーを検出し得る、32 個のハミング符号ワードとして見ることができる。 20

#### 【0041】

ハミング符号が選ばれるのは、ハミング符号が、所与の入力ビットストリームにおいて最大 2 つのビットエラーを検出し得るからである。N ビットの所与の入力ビットストリームのために、ハミング符号は P 個のパリティビットを計算する。パリティビットの数 P は、入力ビットの数 N に依存し、任意の適切な値の P が用いられ得る。幾つかの実施形態において、P の値は、次の関係： $N > 2^P - P - 1$  を満たす、最小の P として選ばれる。 30

#### 【0042】

ハミングエンコーダを、概して、N 個の入力ビットが、エンコーダに演繹的に利用可能であり、パリティビットを決定するために用いられ得ると想定して説明する。しかし、レーダデータメモリ保護の実施形態において、そうでない場合もある。ハミング符号への入力ストリームは、N ワードのストリーム、すなわち、或るグループにおけるワードである。それゆえ、パリティビットは、N 個の入力ワードにおける個々のメモリワードがアクセスされるように決定される必要がある。また、メモリアクセスパターンは予め決定されておらず、これは、或るグループにおけるワードが、任意の特定の順にアクセスされることが想定され得ないことを意味する。それゆえ、レーダメモリ保護の実施形態は、或るグループの全ての N 個のワードが所与の時間に利用可能であること、又は、N 個のワードが任意の特定の順にアクセスされることを想定しない、ハミング符号のパリティビットを更新するための技法を実装する。 40

#### 【0043】

P 個のパリティビットを計算するために N 個の入力ビットのシーケンスを取り入れるハミングエンコーダを考慮されたい。ハミング符号は、パリティビットを計算するプロセスにおいて、入力ビットシーケンスにおけるすべてのビットが、少なくとも 2 つのパリティビットを含む P 個のパリティビットの一意のサブセットを更新するために必要とされるという特性を有する。例えば、第 1 の入力ビットは、パリティビット 1 及び 2 を更新し、第 2 の入力ビットはパリティビット 1 及び 3 を更新し、第 3 の入力はパリティビット 2 及び 3 を更新し、第 4 の入力ビットは、パリティビット 1、2、及び 3 を更新する等である。このように、特定の入力ビットによって更新されるパリティビットのサブセットは、そうした入力ビットの順序性 (ordinality) に依存する。 50

**【0044】**

より具体的には、Gを、数の順序付けられたシーケンスとし、ここで、シーケンスにおける各数は、2つ以上の1ビットを含むバイナリ表現を有し、すなわち、 $G = \{3, 5, 6, 7, 9, 10, 11, 12, 13, 14, 15, 17, \dots\}$ である。このシーケンスは、本質的に、2の幂でない全ての数である。入力ストリームにおけるk番目のビットに関するパリティビットのセットは、G(k)のバイナリ表現によって、すなわち、シーケンスGにおけるk番目の位置の数のバイナリ表現によって与えられ、 $k > 0$ である。例えば、 $k = 5$ である場合、 $G(k) = 9 = 1001$ であり、それゆえ、5番目の入力ビットはパリティビット1及び4に関連することを示す。

**【0045】**

10

また、 $G(k)$ は、

$$G(k) = L(L(k) + k) + k$$

によって計算され得、ここで、 $L(n)$ は、nのバイナリ表現の最も左の非ゼロビットのインデックスを出力する関数である。例えば、 $L(9)$ は4であり、 $L(18)$ は5である。 $k = 4$ の場合、 $L(k) = 3$ 、 $L(L(k) + k) = L(3 + 4) = L(7) = 3$ 、及び、 $L(L(k) + k) + k = 3 + 4 = 7$ である。それゆえ、 $G(4) = 7$ であり、また、7のバイナリ表現が0111であることから考慮すると、これは、更新されるべきパリティビットは、パリティビット1、2、及び、3であることを示す。

**【0046】**

20

図6はパリティ識別回路600を図示する。パリティ識別回路600は、前述の式によつて $G(k)$ を決定するために、レーダシステムにおいて実装され得る。識別回路600への入力は、kのバイナリ表現であり、出力は、Pビットパリティレジスタ608である。構成要素L1 602及びL2 606は、各々、それぞれの構成要素への入力のバイナリ表現の最も左の非ゼロビットのインデックスのバイナリ表現を出力する。構成要素L1 602及びL2 606間に結合される加算器604は、L1構成要素602の出力をkのバイナリ表現に加算し、その結果をL2構成要素606に提供する。構成要素L2 606の出力に結合される加算器607は、L2構成要素606の出力をkのバイナリ表現に加算し、その結果をパリティレジスタ608に提供する。構成要素L1 602及びL2 606は、任意の適切な回路設計を用いて実装され得る。用いられるいくつかの適切な回路設計が、1994年3月のIEEE Transactions on Very Large Scale Integration(VLSI)Systems, Vol.2., No.1, 124~128頁のV.Oklobdzijaの「先行ゼロ検出器回路のアルゴリズム及び新規設計：論理合成との比較」において説明されている。

30

**【文献】**V.Oklobdzija, "An Algorithmic and Novel Design of a Leading Zero Detector Circuit:Comparison with Logic Synthesis", IEEE Transactions on Very Large Scale Integration(VLSI)Systems, Vol.2., No.1, March 1994, pp.124-128

**【0047】**

40

L1 602への入力はkであり、L2 606への入力は、L1の出力にkを加えたものである。L2 606の出力は、再びkに加算されて、最終結果、すなわち、 $G(k)$ を生成する。この最終結果のビット表現は、パリティレジスタ608にストアされる。パリティレジスタ608における非ゼロビットのインデックスは、順序性kの入力ビットに関連するパリティビットを識別する。例えば、 $k = 5$ の場合、パリティレジスタ608は、ビットシーケンス10010···0を含み得、それゆえ、パリティビット1及び4が、第5の入力ビットに関連することを示す。

**【0048】**

前述の記載は、N個の入力ビットのシーケンスに基づいてP個のパリティビットを更新することを図示した。レーダデータメモリのケースでは、N個の入力メモリワードに関連するP個のパリティワードが更新され、ここで、Nは、或るグループにおけるメモリワードの数である。図6の方法に関連して一層詳細に説明されるように、或るグループのN個のワードの或るワードがアクセスされるとき、そのワードに関連するP個のパリティワー

50

ドのパリティワードのサブセットが、そのグループにおけるワードの順序性が決定された後、上述のビット識別プロセスと同様の方式で識別され得る。従って、 $G(k)$ は、或るグループのためのパリティワードのうちのどれが更新されるべきかを識別し、ここで、 $k$ は、グループにおけるワードの順序性である。

#### 【0049】

図7は、上述のハミング符号を想定してレーダデータメモリのパリティワードを更新するための方法のフローチャートである。この方法は、レーダデータメモリにおけるメモリワードの読み出し又は書き込みのために実施される。この方法は、図8及び図9の例に関連して説明され、先の例のグルーピングを想定する。図7を参照すると、メモリワードがアクセスされるとき、すなわち、例えば図8のレーダデータメモリ800といったレーダデータメモリにおいて、読み出される又は書き込まれるとき、メモリワードのレーダデータメモリにおける行及び列座標が、メモリワードのアドレスに基づいて決定される(700)。行及び列座標の決定は上記されている。

10

#### 【0050】

メモリワードのグループインデックスが、行及び列座標に基づいて決定される(702)。グループが0、1、…、 $M - 1$ とインデックスされると想定すると、メモリワードのグループを識別するインデックス $group\_idx$ は、

$$group\_idx = mod(R - mod(C, M), M)$$

によって計算され得、ここで、 $R$ はメモリ行番号であり、 $C$ はメモリワードのメモリ列番号である。

20

#### 【0051】

ワードが割り当てられるグループにおけるメモリワードの順序性 $k$ が、行及び列座標に基づいて決定される(704)。順序性 $k$ は、

$$k = (numRows / M) \times C + floor(R / M) + 1$$

によって計算され得、ここで $C$ はメモリワードの列座標であり、 $R$ はメモリワードの行座標であり、 $numRow$ は、レーダデータメモリにおける行の数である。図8の例は、レーダデータメモリ800のためのグループにおけるワードの順序性1、2、…、N801を図示する。

30

#### 【0052】

メモリワードに対応するグループパリティワードのパリティワードのサブセットが、メモリワードの順序性 $k$ を考慮して決定される(706)。従って、 $G(k)$ が決定される。幾つかの実施形態において、 $G(k)$ は、 $G(k)$ のための前述の式によって計算され得る。幾つかの実施形態において、 $G(k)$ は、図6のパリティ識別回路など、パリティ識別回路によって決定され得る。

#### 【0053】

その後、識別されたパリティワードが更新される(708)。上記したように、グループパリティワードの特定のパリティワードは、 $G(k)$ のバイナリ表現の非ゼロビット位置によって識別される。 $G(k)$ 及びグループインデックスを考慮して、グループパリティワードにおける識別されたパリティワードは、メモリワードのデータと識別されたパリティワードの現在の内容とのXOR演算を実施することによって更新される。

40

#### 【0054】

図9は、前述の方法を図示する例である。図9は、グループに分割されるレーダデータメモリ900、及び、各グループに関連するパリティワード902を示す。32ビットワードを想定すると、例えば、110…1011が、特定のアドレスでレーダデータメモリに書き込まれるべきである。前述の方法のステップに従って、このアドレスは、この値がストアされるべきメモリワードの行及び列を識別するために用いられる。グループ内のメモリワードの順序性 $k$ 、及びグループ識別子は、行及び列に基づいて決定される。この例では、メモリワードは、1のグループインデックスを備えるグループに属するものとして識別される。その後、順序性 $k$ は、ワードをメモリに書き込むことに基づいて更新されるべきグループに対応するパリティワードのサブセットを識別するために用いられる。

50

その後、識別されたパリティワードは、識別されたパリティワードの各々とデータ値 110 . . . 1011とのXOR演算を実施することによって更新される。

#### 【0055】

図10は、2つのソフトエラーからレーダデータメモリを保護するための上述の技法の実施形態を実装する、例示のパリティ管理構成要素1000を図示するブロック図である。この例は、M = 4、メモリワードは32ビット、及び、2MBのレーダデータメモリサイズを想定している。例えば、N = 2MB / 4 / M = 131072であり、Pの値は、上述の関係、すなわち P = 18、に従って選ばれ得る。P = 18と仮定すると、総計  $M \times 18 = 72$  パリティワード又は288バイトのために、グループ毎に18個の32ビットパリティワードが必要とされる。

10

#### 【0056】

パリティ管理構成要素1000は、パリティデータ構成要素1002、パリティワード識別構成要素1004、及びパリティメモリ1006を含む。パリティデータ構成要素1002は、読み出される又は書き込まれる、レーダデータメモリにおけるワードのアドレスADDRを受信する。パリティデータ構成要素1002は、アドレスによって識別されるメモリロケーションの行及び列座標を決定するための機能を含む。パリティデータ構成要素1002はさらに、メモリワードのグループインデックスと、行及び列座標に基づいてワードが割り当てられるグループにおけるメモリワードの順序性kとを決定するための機能を含む。パリティデータ構成要素1002は、メモリアドレスのグループインデックスを提供するためにパリティメモリ1006に、及び、メモリアドレスの順序性kのバイナリ表現を提供するためにパリティワード識別構成要素1004に結合される。対角線状グループ割り当てを想定した、行及び列座標、グループインデックス、及び、順序性の決定は上記されている。

20

#### 【0057】

パリティワード識別構成要素1004は、順序性kに基づいて、更新されるべきグループにおけるパリティワードを識別するための機能、すなわち、G(k)を決定するための機能を含む。順序性に基づくパリティワードの識別は上記されている。幾つかの実施形態において、パリティ識別構成要素1004は、図6の回路要素を含む。パリティ識別構成要素1004は、G(k)のバイナリ値を提供するために、パリティメモリ1006に結合される。

30

#### 【0058】

パリティメモリ1006は、72パリティワードをストアするための充分なメモリを含み、グループインデックスに基づいてグループに割り当てられるパリティワードのサブセットと、パリティワード識別構成要素によって提供されるバイナリ値に基づいて更新されるべき、そのグループにおける特定のワードとを識別するための機能を含む。パリティメモリ1006はさらに、アドレスADDRに対応する、及び、XORに対応するデータを受信するための機能を含み、データは、グループインデックスと、バイナリ値における非ゼロビットとによって識別されるパリティワードを有する。

#### 【0059】

パリティメモリ1006は、イネーブルフラグ1008の値を受信するように結合されてもよい。このフラグの値は、パリティが現在のメモリアクセスのために更新されるべきか否かを示す。上記したように、レーダデータメモリ保護は、チャーブのフレームに対応するデータ処理の間、各メモリロケーションが、等しい回数読み出される及び書き込まれることを想定する。より具体的には、パリティが更新される間のメモリワードへの値の各書き込みのために、パリティが同じく更新される間、メモリワードからその値の单一読み出しが実施されなければならない。後処理の間、例えば、ドップラーFFTの後、対応するパリティビットを更新することなく、データのいくつかを読み出す必要があり得る。そのような事例では、このフラグの値は、パリティ更新がないことを示すように設定される。

40

#### 【0060】

上述の例示の図は、レーダデータメモリワードのグループ化について対角線状パター

50

ンを想定した。単一ソフトエラーがグループ毎に最大 1 ワードに影響を及ぼし得るという特性が保持される場合、その他のグルーピング技法が用いられ得る。図 1 1 及び図 1 2 は、 $M = 4$  であり、メモリワードが行ごとにグループに割り当てられる 32 ビットメモリワードを想定した、レーダデータメモリ 1100 のための代替のグルーピングパターンを図示する例である。

#### 【 0 0 6 1 】

図 1 1 は、この行方向のグルーピングパターンを用いる単一ソフトエラー発生に対する保護のためのパリティビット割り当てを図示する例である。この例では、行 1、4、及び 7 におけるメモリワードが、同じグループにある。 $M \times M$  領域 1102 は、単一ソフトエラーによって影響を及ぼされ得るメモリの例示の部分を図示する。図 3 の例と同様、パリティビットが、32 ビット位置の各々の保護のために割り振られている。図 1 1 の右側に、例示のグループのためのメモリワードが、例示のため垂直にスタックされており、関連する 32 ビットパリティワードが、そのスタックの下に示されている。また、グループの各ワードにおける例示のビット位置でのビットの例示の列 1104 が、パリティワードにおける関連するパリティビットと共に示されている。単一ソフトエラー保護のための図 4 の方法は、グループインデックスが決定される方式への改変を伴って、行方向のグルーピングと共に用いられ得る。

10

#### 【 0 0 6 2 】

図 1 2 は、行方向のグルーピングパターンを用いる、2 つのソフトエラーに対する保護のためのパリティビット割り当てを図示する例である。この例では、行 1、4、及び 7 におけるメモリワードが、同じグループにある。 $M \times M$  領域 1200 及び  $M \times M$  領域 1202 は、2 つのソフトエラーによって影響を及ぼされ得るメモリの例示の部分を図示する。図 5 の例と同様、P 個のパリティビットの一セットが、或るグループに割り当てられるワードの各ビット位置の保護のために割り振られる。図 1 2 の右側に、例示のグループのためのメモリワードが、例示のため垂直にスタックされ、このグループに対応する 32 ビットパリティワードが、スタックの下に示されている。また、グループの各ワードにおける例示のビット位置でのビットの例示の列 1204 が、パリティワードにおけるパリティビットと共に示されている。2 つのソフトエラーからの保護のための図 7 の方法は、グループインデックス及び順序性の式に対する幾つかの変更を伴って、行方向のグルーピングと共に用いられ得る。より具体的には、グループインデックスは、

20

```

g r o u p _ i d x = m o d ( R , M )

```

30

によって計算され得、順序性 k は、

```

k = N u m C o l u m n s x f l o o r ( R / M ) + C

```

によって計算され得る。

40

#### 【 0 0 6 3 】

図 1 3 は、図 1 4 のレーダシステムなどのレーダシステムにおけるレーダデータメモリを保護するための方法のフローチャートである。この方法は、チャープのフレームに対するレーダデータの処理の間に実施され得る。レーダデータメモリにデータをストアする前に、全てのパリティワードがゼロに初期化される (1300)。デジタル化 I/F 信号の前処理が実施されるとき、すなわち、レンジ値を生成するために、入力されるデジタル化サンプルにレンジ FFT が適用されるとき、各レンジ値は、レーダデータメモリにおけるメモリワードにストアされ (1302)、メモリワードに対応するパリティビットが更新される (1304)。レンジ FFT が完了する (1305) まで、すなわち、前処理が完了するまで、レンジ値のストア及びパリティ更新は続く。

#### 【 0 0 6 4 】

フレームに対応するレンジ値の全てがレーダデータメモリにストアされた (1305) 後、後処理が開始される。後処理の間、ドップラー FFT が実施され、ドップラー FFT では、レンジ値の各列がレーダデータメモリから読み出され (1306)、レンジ値に対してドップラー FFT が実施され、結果のドップラー FFT 値が、レンジ値の列をストアしたメモリロケーションにおけるレーダデータメモリに書き込まれる (1310)。レン

50

ジ値の列の各メモリワードに対応するパリティビットは、レンジ値の列が読み出されるときに更新される(1308)。同様に、ドップラーFFTの値がストアされる各メモリワードに対応するパリティビットは、その値がメモリワードに書き込まれるときに更新される(1312)。

#### 【0065】

ドップラーFFTが完了した(1314)後、パリティ更新はディセーブルされ(1316)、例えば、オブジェクトを検出し、検出されたオブジェクトのレンジ、速度、及び、到來角を識別するなどの後処理を完了するために、データのいくつかが、レーダデータメモリから読み出される(1318)。後処理が完了した後、パリティ更新がイネーブルされる(1320)。

10

#### 【0066】

その後、前処理及び後処理の間、レーダデータをストアするために用いられた、レーダデータメモリにおける各メモリワードが読み出され(1322)、対応するパリティビットの更新をトリガする(1322)。このステップが完了した後、メモリワードは、パリティ更新のため、同じ回数読み出される及び書き込まれる。その後、パリティビットは、メモリエラーについてチェックされる(1324)。全てのパリティビットがゼロである場合(1324)、エラーは生じていない。ゼロでない場合は、メモリエラーが伝達される(1326)。

#### 【0067】

説明されたような単一ソフトエラーメモリ保護の実施形態が、レーダシステムによって実装される場合、メモリワードに対応するパリティビットの更新は、図4の方法を用いて実施され得る。本願で説明されるような2つのソフトエラーメモリ保護の実施形態がレーダシステムによって実装される場合、メモリワードに対応するパリティビットの更新は、図7の方法を用いて実施され得る。

20

#### 【0068】

図14は、本願で説明されるようなレーダデータメモリ保護を実施するように構成される、例示のFMCWレーダシステム1400のブロック図である。この実施形態において、レーダシステムは、埋め込み応用例において用いるために適したレーダ集積回路(IC)である。レーダIC1400は、FMCW信号を送信するための複数の送信チャネル1404、及び、反射された送信信号を受信するための複数の受信チャネル1402を含み得る。受信チャネル及び送信チャネルの任意の適切な数と、受信チャネルの数及び送信チャネルの数とは異なり得る。

30

#### 【0069】

送信チャネルが、適切なトランスマッタ及びアンテナを含む。受信チャネルが、適切なレシーバ及びアンテナを含む。また、受信チャネル1402の各々は、同一であり、受信された無線周波数(RF)信号を增幅するための低ノイズ増幅器(LNA)1405、1407、送信された信号を、受信された信号と混合して中間周波数(IF)信号(あるいは、デチャーブされた信号、ビート信号、又は、未加工レーダ信号とも呼ばれる)を生成するためのミキサ1406、1408、ビート信号をフィルタするためのベースバンドバンドパスフィルタ1410、1412、フィルタされたIF信号を増幅するための可変利得増幅器(VGA)1414、1416、及び、アナログIF信号をデジタルIF信号に変換するためのアナログ・デジタルコンバータ(ADC)1418、1420を含む。

40

#### 【0070】

受信チャネル1402は、デジタルフロントエンド(DFE)構成要素1422に結合されて、デジタルIF信号をDFE1422に提供する。DFEは、サンプリングレートを低減させ、信号をベースバンドにするために、デジタルIF信号に対してデシメーションフィルタリングを実施するための機能を含む。また、DFE1422は、例えば、DCオフセット除去など、デジタルIF信号に対して他の動作を行ない得る。DFE1422は、DFE1422の出力を信号プロセッサ構成要素1444に伝送するために、信号プロセッサ構成要素1444に結合される。

50

**【 0 0 7 1 】**

信号プロセッサ構成要素 1444 は、レーダシステム 1400 の F O V における任意のオブジェクトを検出するため、及び、検出されたオブジェクトのレンジ、速度、及び、到來角を識別するために、レーダデータのフレームのデジタル I F 信号に対して信号処理を行なうように構成される。信号プロセッサ構成要素 1444 は、信号処理の間、データをレーダデータメモリ 1426 に読み出す及び書き込むために(1426)、レーダデータストレージ構成要素 1424 に結合される。

**【 0 0 7 2 】**

上述の前処理及び後処理などの信号処理を行なうために、信号プロセッサ構成要素 1444 は、メモリ構成要素 1448 にストアされたソフトウェア命令を実行する。これらのソフトウェア命令は、チャープのフレームに対応するデータを処理した後、メモリエラーについて、レーダデータストレージ構成要素 1424 のパリティビットをチェックするための命令を含み得る。また、メモリエラーが示される場合、ソフトウェア命令は、信号処理の結果を無視させ得る。

10

**【 0 0 7 3 】**

信号プロセッサ構成要素 1444 は、任意の適切なプロセッサ、又は、プロセッサの組み合わせであり得る。例えば、信号プロセッサ構成要素 1444 は、デジタル信号プロセッサ、MCU、FFT エンジン、DSP + MCU プロセッサ、フィールドプログラマブルゲートアレイ(FPGA)、又は、特定用途向け集積回路(ASSIC) であり得る。

**【 0 0 7 4 】**

レーダデータストレージ構成要素 1424 は、本願で説明するレーダデータメモリ保護技法の実施形態に従って、保護されるレーダデータストレージを提供する。レーダデータストレージ構成要素 1424 は、パリティ管理構成要素 1425、及び、レーダデータメモリ構成要素 1426 を含む。レーダデータメモリ構成要素 1426 は、例えばスタティック RAM など、任意の適切なランダムアクセスメモリ(RAM) であり得る。レーダデータメモリ構成要素 1426 は、チャープの最大の予測されるフレームに対応するレーダデータをストアするための充分なメモリを含む。

20

**【 0 0 7 5 】**

パリティ管理構成要素 1425 は、レーダデータメモリ構成要素 1426 のためのパリティ更新を実装する。幾つかの実施形態において、パリティ管理構成要素 1425 は、レーダデータメモリ構成要素 1426 における単一ソフトエラーに対する保護のために、上述のパリティスキームの実施形態を実装する。そのような実施形態では、パリティビットが、或るグループに割り当てられるメモリワードの各ビット位置の保護のために割り振られる。それゆえ、メモリワードが  $N_w$  ビットである場合、1 グループに  $N_w$  個のパリティビットが必要とされる。パリティ管理構成要素 1425 は、各グループのための  $N_w$  ビットパリティ情報のための充分なストレージを含む。また、パリティ管理構成要素 1425 は、図 4 のパリティワードを更新するための方法の実施形態を実装するための機能を含む。

30

**【 0 0 7 6 】**

幾つかの実施形態において、パリティ管理構成要素 1425 は、レーダデータメモリ構成要素 1426 における 2 つのソフトエラーに対する保護のための上述のパリティスキームの実施形態を実装する。そのような実施形態では、上記したように、或るグループに割り当てられるメモリワードの列の各ビット位置列の保護のために、パリティビットの列が割り振られる。それゆえ、メモリワードが  $N_w$  ビットである場合、1 グループにパリティビットの  $N_w$  列が必要とされる。パリティビットの列におけるパリティビット  $P$  の数は、グループにおけるメモリワードの数に依存する。 $P$  の値の選択については前述している。それゆえ、1 グループに  $P \times N_w$  パリティビットが必要とされる。パリティ管理構成要素 1425 は、各グループのための、 $P \times N_w$  ビットパリティ情報のための充分なストレージを含む。また、パリティ管理構成要素 1425 は、図 7 のパリティワードを更新するための方法の実施形態を実装するための機能を含む。幾つかの実施形態において、パリティ管理構成要素 1425 は、レーダデータメモリ構成要素 1426 におけるメモリの量のた

40

50

めに適切に構成される、図 10 のパリティ管理構成要素 1000 によって実装され得る。

#### 【0077】

幾つかの実施形態において、パリティ管理構成要素 1425 は、イネーブルフラグ（図示せず）のための入力を含む。そのような実施形態では、パリティ更新が実施されるべきでないことを示すようにこのフラグが設定されない限り、パリティ管理構成要素 1425 は、レーダデータメモリ構成要素 1426 のワードが読み出される又は書き込まれるときにパリティ更新を行なう。各メモリワードに対応するパリティビットが、等しい数の読み出し及び書き込みによって更新されることを確実にするために、信号処理構成要素 1444 によって実行される信号処理ソフトウェアは、チャーブのフレームに対応するデータの処理の間、必要に応じてこのフラグを設定し得る。例えば、図 13 の方法に関連して説明されるように、パリティ更新は、後処理の部分の間、ディセーブルされ得る。10

#### 【0078】

オンチップメモリ構成要素 1448 は、例えば、レーダ I C 1400 上のプロセッサによって実行されるソフトウェアプログラムをストアするために、レーダ I C 1400 の種々の構成要素間でデータを通信するために役立ち得るオンチップストレージ（例えば、コンピュータ読み出し可能媒体）を提供する。オンチップメモリ構成要素 1448 は、リードオンリメモリ、及び / 又は、例えばスタティック RAM などのランダムアクセスメモリ（RAM）などの、任意の適切な組み合わせを含み得る。

#### 【0079】

ダイレクトメモリアクセス（DMA）構成要素 1446 は、レーダデータメモリ 1426 と信号プロセッサ構成要素 1444 との間のデータ伝送を行なうために、レーダデータストレージ構成要素 1424 に結合される。20

#### 【0080】

制御構成要素 1427 は、レーダ I C 1400 の動作を制御するための機能を含む。例えば、制御構成要素 1427 は、レーダ I C 1400 の動作を制御するためにソフトウェアを実行する MCU を含み得る。

#### 【0081】

シリアルペリフェラルインターフェース（SPI）1428 は、レーダ信号処理の結果を外部通信するためのインターフェースを提供する。例えば、信号プロセッサ構成要素 1444 によって実施された信号処理の結果は、例えば、オブジェクトトラッキング、オブジェクトの移動のレート、移動の方向などの、特定用途向け処理のために別のプロセッサに通信され得る。30

#### 【0082】

プログラム可能タイミングエンジン 1442 は、レーダフレームにおけるチャーブのシーケンスのためのチャーブパラメータ値を制御モジュール 1427 から受信するため、及び、このパラメータ値に基づいて、フレームにおけるチャーブの送信及び受信を制御するチャーブ制御信号を生成するための機能を含む。例えば、チャーブパラメータは、レーダシステムアーキテクチャによって定義され、イネーブルするべきトランスマッタ、チャーブ周波数開始値、チャーブ周波数スロープ、アナログ デジタル（ADC）サンプル時間、ランプ終了時間、トランスマッタ開始時間等を示すためのトランスマッタイネーブルパラメータを含み得る。40

#### 【0083】

無線周波数シンセサイザ（RF SYNTH）1430 は、タイミングエンジン 1442 からのチャーブ制御信号に基づいて、送信のための FMCW 信号を生成するための機能を含む。幾つかの実施形態において、RF SYNTH 1430 は、電圧制御発振器（VCO）を備える位相ロックループ（PLL）を含む。

#### 【0084】

マルチブレクサ 1432 は、RF SYNTH 1430 及び入力バッファ 1436 に結合される。マルチブレクサ 1432 は、入力バッファ 1436 において受信される信号か、RF SYNTH 1430 によって生成される信号を選択するように構成され得る。例えば50

、出力バッファ 1438 は、マルチプレクサ 1432 に結合され、マルチプレクサ 1432 によって選択された信号を、別のレーダ I C の入力バッファに送信するために用いられる。

#### 【 0085 】

クロック乗算器 1440 は、送信信号の周波数を、ミキサ 1406、1408 の周波数まで増加させる。クリーンアップ PLL (位相ロックループ) 1434 は、外部低周波数基準クロック (図示せず) の信号の周波数を、RFSYNTH 1430 の周波数まで増加させるように、及び、クロック信号からの基準クロック位相雑音をフィルタするように動作する。

#### 【 0086 】

レーダデータメモリワードのグループの数が 4 である、すなわち、 $M = 4$  と想定して、例示の実施形態を本願において説明してきたが、グループの数が 4 つ以上又は 4 つ以下のその他の実施形態も可能である。

#### 【 0087 】

また、メモリワードにおけるビットのサブセットがアクセスされるように、ビットパッキング又はメモリ圧縮は用いられない想定して、例示の実施形態を本願で説明してきたが、ビットパッキング / メモリ圧縮が用いられるその他の実施形態が可能である。例えば、パリティ更新のために用いられるデータは、全パリティワードを用いる XOR 演算を可能にするためにゼロ充填され得る。例えば、32 ビットワードのビット 8 ~ 15 がアクセスされる場合、パリティ更新のために用いられる 32 ビットデータは、その他のビット位置にゼロを有するこれらのビットを含んでもよい。別の例において、アクセスされるビットに対応するパリティビットのみが更新される。例えば、32 ビットワードのビット 8 ~ 15 がアクセスされる場合、1 つ又は複数のパリティワードのビット 8 ~ 15 が更新される。

#### 【 0088 】

左上から右下への対角線状グルーピングを想定して、その他の例示の実施形態を本願で説明してきたが、対角線状グルーピングが左下から右上であるその他の実施形態が可能である。

#### 【 0089 】

いくつかの例示の実施形態では、レーダシステムは、車両における埋め込みレーダシステムであるが、監視及びセキュリティ応用例や、工場又は倉庫におけるロボット操縦など、埋め込みレーダシステムのその他の応用例のための、その他の実施形態が可能である。

#### 【 0090 】

FMCW レーダシステムの文脈において、更なる例示の実施形態を本願で説明してきたが、各メモリワードが、等しい回数、書き込み及び読み出しされるようにレーダ信号の信号処理が実施されるその他のレーダシステムのための、その他の実施形態が可能である。

#### 【 0091 】

FMCW レーダシステムの文脈において、メモリ保護のさらなる例示の実施形態を本願で説明してきたが、安全性が重視される応用例において用いられるその他の信号処理システムのためのその他の実施形態が可能であり、こういった応用例では、大量のデータが信号処理のためにストアされ、信号処理に対応するデータアクセスは、(幾つかの実施形態では) パリティイネーブルフラグを用いて、或いは、(幾つかの実施形態では) パリティイネーブルフラグを用いることなく、メモリワード毎に、等しい回数の読み出し及び書き込みアクセスが保証され得るようなものである。

#### 【 0092 】

幾つかの例示の実施形態では、メモリは、単一ソフトエラーがグループ毎に一つのメモリワードのみに影響を及ぼすようにグルーピングされ、チェックサムベースの技法が、単一ソフトエラーに対する保護のために用いられ、ハミング符号技法が、2 つのソフトエラーに対する保護のために用いられる。しかし、より効率の低いメモリワードグルーピングが用いられるその他の実施形態が可能である。例えば、単一ソフトエラーが或るグループ

10

20

30

40

50

において 2 つのメモリワードに影響を及ぼすように、グルーピングが用いられ得る。幾つかの実施形態において、單一ソフトエラーから保護するためにハミング符号が用いられ得る。

【 0 0 9 3 】

方法のステップが、本願において順次提示及び説明され得るが、図示され本願で説明されるステップの一つ又は複数が、同時に実施されてもよく、組み合されてもよく、及び／又は、図示され及び／又は本願で説明される順とは異なる順で実施されてもよい。

【 0 0 9 4 】

レーダシステムにおける構成要素は、異なる名称で呼ばれることがあり、及び／又は、説明される機能から逸脱することなく、本願において示されないやり方で組み合わされ得る。この記載において、用語「結合する（c o u p l e）」及びその派生語は、間接的、直接的、光学的、及び／又は、ワイヤレス電気接続を意味することが意図される。例えば、第 1 のデバイスが第 2 のデバイスに結合する場合、そのような接続は、直接的な電気接続を介するもの、他のデバイス又は接続を介した間接的な電気接続を介するもの、光学電気接続を介するもの、及び／又は、ワイヤレス電気接続を介するものであり得る。

10

【 0 0 9 5 】

特許請求の範囲内で、説明された実施形態における改変が可能であり、その他の実施形態が可能である。

20

30

40

50

【図面】

【図 1】

FIG. 1

【図 2】

FIG. 2

10

20

【図 3】

FIG. 3

【図 4】

パリティワード

チェックサム

30

40

50

【図 5】

FIG. 5

【図 6】

FIG. 6

10

20

30

40

【図 7】

FIG. 7

【図 8】

FIG. 8

50

【図 9】

【図 10】

10

20

30

40

【図 11】

【図 12】

50

【図 1 3】

【図 1 4】

10

20

30

40

50

---

フロントページの続き

インディラナガル セカンド ステージ , フィフティーンス クロス 82 , シトラス コート 003

(72)発明者 ブライアン ポール ギンスバーグ

アメリカ合衆国 75013 テキサス州 アレン , ウィンダム ウェイ 910

審査官 坂東 博司

(56)参考文献 特開平03-290745 (JP, A)

特開2006-318461 (JP, A)

特開昭61-050295 (JP, A)

特開平11-312396 (JP, A)

特開2008-117395 (JP, A)

特開平02-077846 (JP, A)

米国特許出願公開第2015/0220385 (US, A1)

米国特許出願公開第2014/0059301 (US, A1)

米国特許出願公開第2008/0250270 (US, A1)

米国特許出願公開第2005/0268019 (US, A1)

米国特許出願公開第2005/0149839 (US, A1)

米国特許第09003264 (US, B1)

米国特許第08028216 (US, B1)

欧州特許出願公開第02876460 (EP, A1)

(58)調査した分野 (Int.Cl. , DB名)

G 06 F 11 / 10

G 01 S 13 / 34

G 01 S 7 / 35