(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2015-204301

(P2015-204301A)

(43) 公開日 平成27年11月16日(2015.11.16)

(51) Int.Cl.

|      |        |           |

|------|--------|-----------|

| HO1L | 21/28  | (2006.01) |

| HO1L | 29/41  | (2006.01) |

| HO1L | 21/329 | (2006.01) |

| HO1L | 29/868 | (2006.01) |

| HO1L | 29/861 | (2006.01) |

F 1

|      |       |

|------|-------|

| HO1L | 21/28 |

| HO1L | 29/44 |

| HO1L | 29/91 |

| HO1L | 29/91 |

|         |

|---------|

| 3 O 1 R |

| S       |

| A       |

| C       |

テーマコード(参考)

4 M 1 O 4

審査請求 未請求 請求項の数 8 O L (全 9 頁)

(21) 出願番号

特願2014-81239(P2014-81239)

(22) 出願日

平成26年4月10日(2014.4.10)

(71) 出願人 000006013

三菱電機株式会社

東京都千代田区丸の内二丁目7番3号

(74) 代理人 100082175

弁理士 高田 守

(74) 代理人 100106150

弁理士 高橋 英樹

(74) 代理人 100148057

弁理士 久野 淑己

(72) 発明者 加地 考男

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

(72) 発明者 多留谷 政良

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

最終頁に続く

(54) 【発明の名称】半導体装置および半導体装置の製造方法

## (57) 【要約】

【課題】良好な電気特性を得つつ、シリコン基板に形成された保護膜などの機能が損なわれるのを抑制し、Si-Ti面の剥離を抑制することもできる半導体装置および半導体装置の製造方法を提供する。

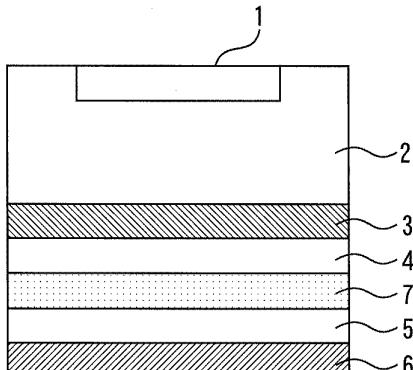

【解決手段】N型シリコン基板2は、一方の面にP型シリコンからなりN型シリコン基板2とPN接合を形成するアノード層1を有し、他方の面にN型シリコン層からなるカソード層3を有する。半導体装置10は、さらに、カソード層3の上に形成されチタンからなりSi-Ti接合を形成する第1電極膜4と、第1電極膜4の上に形成されAl-SiからなりTi-Al-Si接合を形成する第2電極膜7と、第2電極膜の上に形成されNiからなりAl-Si-Ni接合を形成する第3電極膜5と、第3電極膜5の上に形成されAuからなる第4電極膜6を備える。

【選択図】図1

- 1 : P-Si (アノード)

- 2 : N-Si

- 3 : N-Si (カソード)

- 4 : Ti

- 5 : Ni

- 6 : Au

- 7 : Al-Si

**【特許請求の範囲】****【請求項 1】**

一方の面にN型シリコン層を備え、他方の面側にPN接合、電極膜、および保護膜の少なくとも1つを備えるシリコン基板を準備する工程と、

前記N型シリコン層の上に、チタンからなる第1電極膜を形成することでSi-Ti接合を形成する工程と、

前記第1電極膜の上に、Al-Siからなる第2電極膜を形成する工程と、

前記第2電極膜の上に、Niからなる第3電極膜を形成する工程と、

前記第3電極膜を形成した後の前記シリコン基板を加熱する工程と、

を備え、

前記N型シリコン層と前記第1電極膜の間にチタンシリサイドが形成されていない半導体装置の製造方法。

**【請求項 2】**

前記第3電極膜を形成する前に、前記第2電極膜の上にチタンを用いた第5電極膜を形成する工程を更に備える請求項1に記載の半導体装置の製造方法。

**【請求項 3】**

前記シリコン基板は、一方の面にP型シリコンからなるアノード層を有し、他方の面に前記N型シリコン層からなるカソード層を有するN型シリコン基板である請求項1または2に記載の半導体装置の製造方法。

**【請求項 4】**

前記シリコン基板は、P型シリコン基板であり、一方の面に前記N型シリコン層を有し、他方の面に他のN型シリコン層を有する請求項1または2に記載の半導体装置の製造方法。

**【請求項 5】**

一方の面にN型シリコン層を備え、他方の面側にPN接合、電極膜、および保護膜の少なくとも1つを備えるシリコン基板と、

チタンからなり、前記N型シリコン層の上に形成されてSi-Ti接合を形成し、前記N型シリコン層との間にチタンシリサイドを有さない第1電極膜と、

Al-Siからなり、前記第1電極膜の上に形成された第2電極膜と、

前記第2電極膜の上に形成され、Niからなる第3電極膜と、

を備える半導体装置。

**【請求項 6】**

前記第3電極膜と前記第2電極膜との間に設けられ、チタンで構成された第5電極膜を、更に備える請求項5に記載の半導体装置。

**【請求項 7】**

前記シリコン基板は、一方の面にP型シリコンからなるアノード層を有し、他方の面に前記N型シリコン層からなるカソード層を有するN型シリコン基板である請求項5または6に記載の半導体装置。

**【請求項 8】**

前記シリコン基板は、P型シリコン基板であり、一方の面に前記N型シリコン層を有し、他方の面に他のN型シリコン層を有する請求項5または6に記載の半導体装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、半導体装置および半導体装置の製造方法に関する。

**【背景技術】****【0002】**

従来、例えば、下記の特許文献1、2に開示されているように、シリコン基板に多層電極膜を設けた半導体装置が知られている。例えば特許文献1の図6を参照すると、シリコン基板の表面に、Tiなどのバリアメタルと、Al-Si合金などのAl合金電極と、Ni

10

20

30

40

50

電極と、 $A_u$ 電極とが積層された構造が記載されている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2013-194291号公報

【特許文献2】特開2010-129585号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

N型シリコン(Si)にチタン(Ti)からなる電極を設けてSi-Ti接合を形成すると、良好なオーミックコンタクト性が得られる。強固なSi-Ti接合を得るために、理想的には、700程度の高温プロセスを用いチタンシリサイドなどの反応層を得ることが好ましい。しかし、このような高温プロセスを行うと、半導体基板に既に形成された素子構造部、電極膜、および保護膜の機能が損なわれるという問題がある。これに対し、どのような高温プロセスを行わずにチタンシリサイドなどの反応層が形成されていないSi-Ti接合を用いることも考えられる。しかしながら、その場合には、チタン電極に更に他の電極膜を重ねて多層電極膜を形成した後に、この多層電極膜に熱処理工程(200度以上)を加えると、多層電極膜の応力によりSi-Ti界面剥離が発生するという問題があった。

10

【0005】

本発明は、上述のような課題を解決するためになされたもので、良好な電気特性を得つつ、シリコン基板に形成された保護膜などの機能が損なわれるのを抑制し、Si-Ti面の剥離を抑制することもできる半導体装置および半導体装置の製造方法を提供することを目的とする。

20

【課題を解決するための手段】

【0006】

本発明にかかる半導体装置の製造方法は、一方の面にN型シリコン層を備え、他方の面側にPN接合、電極膜、および保護膜の少なくとも1つを備えるシリコン基板を準備する工程と、前記N型シリコン層の上に、チタンからなる第1電極膜を形成する工程と、前記第1電極膜の上に、Al-Siからなる第2電極膜を形成する工程と、前記第2電極膜の上に、Niからなる第3電極膜を形成する工程と、前記第3電極膜を形成した後の前記シリコン基板を加熱する工程と、を備え、前記N型シリコン層と前記第1電極膜の間にチタンシリサイドが形成されていない。

30

【0007】

本発明にかかる半導体装置は、一方の面にN型シリコン層を備え、他方の面側にPN接合、電極膜、および保護膜の少なくとも1つを備えるシリコン基板と、チタンからなり、前記N型シリコン層の上に形成され前記N型シリコン層との間にチタンシリサイドを有さない第1電極膜と、Al-Siからなり、前記第1電極膜の上に形成された第2電極膜と、前記第2電極膜の上に形成され、Niからなる第3電極膜と、を備える。

40

【発明の効果】

【0008】

本発明によれば、Si-Ti接合によるオーミックコンタクトを得つつ、高温プロセスが要求されるチタンシリサイドは形成しないことでシリコン基板上の保護膜などの機能が低下するのを回避し、かつ、Si-Ti界面剥離抑制用にAl-Siからなる第2電極膜を挿入している。これにより、良好な電気特性を得つつ、シリコン基板に形成された保護膜などの機能が損なわれるのを抑制し、Si-Ti面の剥離を抑制することもできる。

【図面の簡単な説明】

【0009】

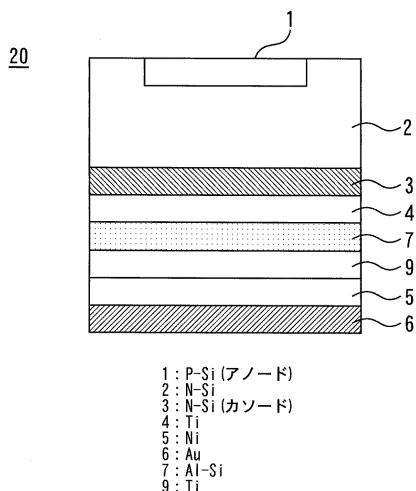

【図1】本発明の実施の形態1にかかる半導体装置を示す図である。

50

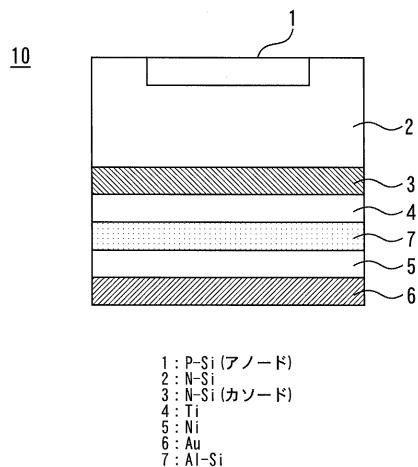

【図2】本発明の実施の形態1にかかる半導体装置の作用効果の説明用の図である。

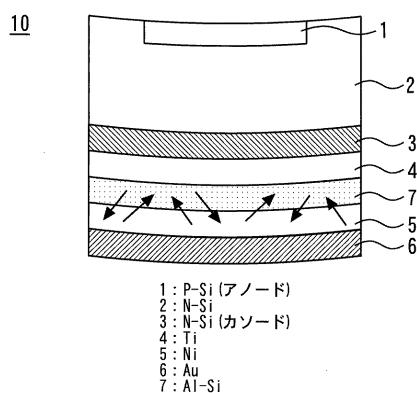

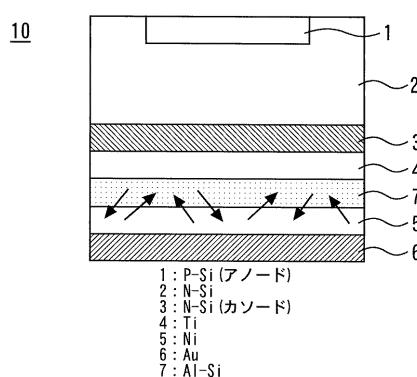

【図3】本発明の実施の形態1にかかる半導体装置の作用効果の説明用の図である。

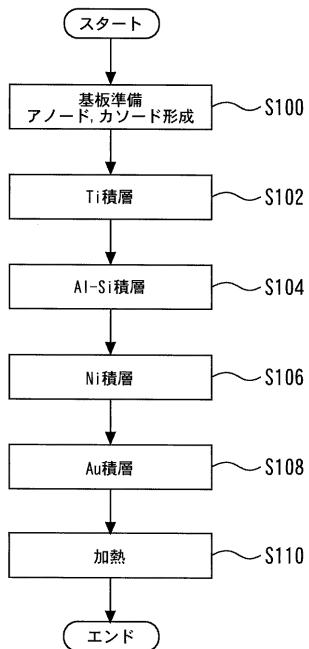

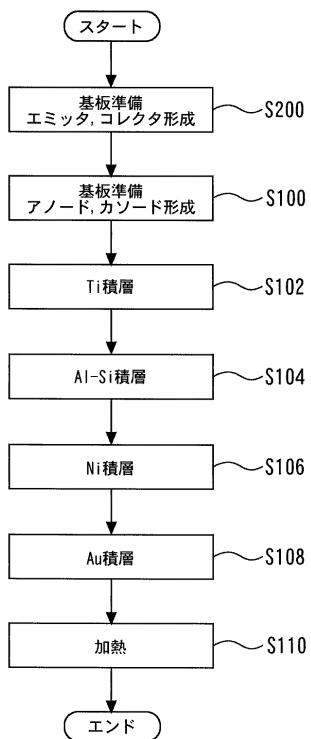

【図4】実施の形態1にかかる半導体装置の製造方法を示すフローチャートである。

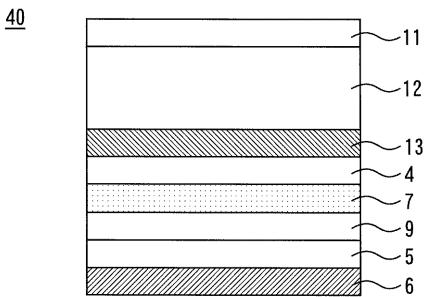

【図5】本発明の実施の形態2にかかる半導体装置を示す図である。

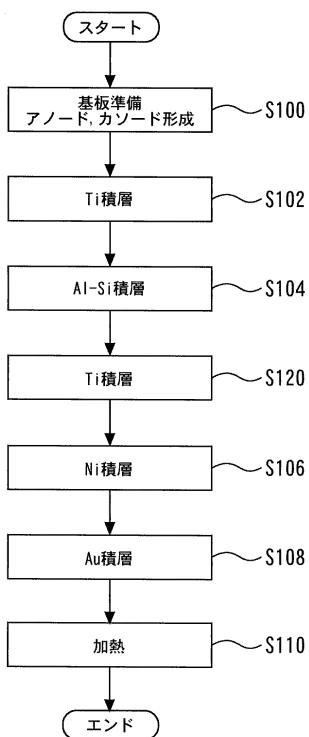

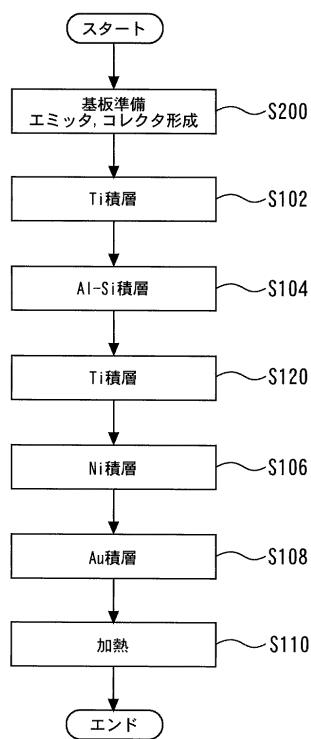

【図6】実施の形態2にかかる半導体装置の製造方法を示すフローチャートである。

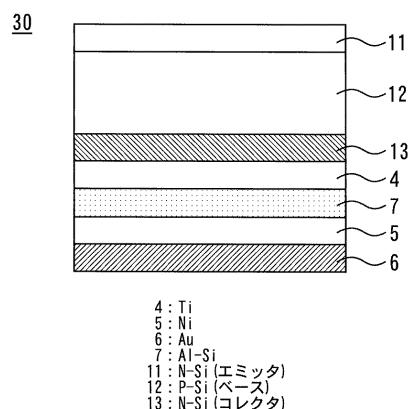

【図7】本発明の実施の形態3にかかる半導体装置を示す図である。

【図8】実施の形態3にかかる半導体装置の製造方法を示すフローチャートである。

【図9】本発明の実施の形態4にかかる半導体装置を示す図である。

【図10】実施の形態4にかかる半導体装置の製造方法を示すフローチャートである。

【発明を実施するための形態】

【0010】

10

実施の形態1.

図1は、本発明の実施の形態1にかかる半導体装置10を示す図である。半導体装置10は、N型シリコン基板2を備えている。N型シリコン基板2は、一方の面にP型シリコンからなりN型シリコン基板2とPN接合を形成するアノード層1を有し、他方の面にN型シリコン層からなるカソード層3を有する。半導体装置10は、さらに、カソード層3の上に形成されチタンからなりSi-Ti接合を形成する第1電極膜4と、第1電極膜4の上に形成されAl-SiからなりTi-AlSi接合を形成する第2電極膜7と、第2電極膜の上に形成されNiからなりAlSi-Ni接合を形成する第3電極膜5と、第3電極膜5の上に形成されAuからなる第4電極膜6を備える。これらの電極膜により「多層電極膜」が形成されている。半導体装置10は、N型シリコン基板2の表面と裏面とにそれぞれ電極を有するダイオードである。図示しないが、アノード層1の上にさらに電極膜および保護膜が設けられていても良い。

20

【0011】

図2および図3は、本発明の実施の形態1にかかる半導体装置10の作用効果を説明するための図である。図2および図3に示す矢印は、Al-Siからなる第2電極膜7とNiからなる第3電極膜5との間で互いに及ぼしあう力を模式的に図示している。実施の形態1では、Si-Ti接合(つまりカソード層3と第1電極膜4との間の接合)とNi(つまり第3電極膜5)の間にAl-Siからなる第2電極膜7を形成している。これにより、チタンシリサイドなどの反応層を形成させずに電極形成後の熱処理(例えば200度以上)を実施しても、図2および図3に示すようにSi-Tiに加わる応力を緩和でき、熱処理後もSi-Ti面剥離を抑制可能である。以上説明したように、本実施の形態によれば、アノード層1側の面に形成された構成(すなわちPN接合、電極膜、および保護膜)の機能を損なうことがなく、良好な電気特性を有するSi-Ti接合を維持しつつ、電極形成後の熱工程の際に多層電極膜に発生する応力によるSi-Ti界面剥離を抑制することができる。

30

【0012】

図4は、本発明の実施の形態1にかかる半導体装置10の製造方法を示すフローチャートである。先ず、N型シリコン基板2を準備し、このN型シリコン基板2にアノード層1およびカソード層3をそれぞれ形成する工程を実施する(ステップS100)。アノード層1には、他の電極膜および保護膜が設けられても良い。次に、カソード層3の上に、チタンからなる第1電極膜4を形成する工程を実施する(ステップS102)。次に、第1電極膜4の上に、Al-Siからなる第2電極膜7を形成する工程を実施する(ステップS104)。次に、第2電極膜7の上に、Niからなる第3電極膜5を形成する工程を実施する(ステップS106)。次に、第3電極膜5の上に、Auからなる第4電極膜6を形成する工程を実施する(ステップS108)。その後、多層電極形成後の熱処理(例えば200度以上)を実施する(ステップS110)。これらの工程により、図1を用いて説明した半導体装置10が得られる。

40

【0013】

強固なSi-Ti間の結合を得るためにチタンシリサイドなどの反応層を形成する方法があるが、その形成は700程度の高温プロセスが必要となる。アノード層1とアノ-

50

ド層 1 側に設けられた図示しない電極膜および保護膜とが N 型シリコン基板 2 に形成された後でこのような高温プロセスを実施すると、それらの有すべき機能が損なわれてしまうという問題がある。そこで、本実施の形態では、そのような高温プロセスを実施しないようしている。

#### 【 0 0 1 4 】

仮にチタンシリサイドがない状態で多層電極形成後に熱処理を実施すると、T i からなる第 1 電極膜 4 に形成されている N i からなる第 3 電極膜 5 においてグレイン成長などによる不可逆な変化により応力が発生し、この応力が熱処理後も残存する。本実施の形態によれば、第 2 電極膜 7 が設けられているので S i - T i に加わる応力を緩和でき、上述したチタンシリサイドなどの反応層を形成させなくとも熱処理後における S i - T i 面剥離を抑制可能である。10

#### 【 0 0 1 5 】

実施の形態 2 .

図 5 は、本発明の実施の形態 2 にかかる半導体装置 2 0 を示す図である。半導体装置 2 0 は、第 3 電極膜 5 と第 2 電極膜 7 との間に設けられ、チタンで構成された第 5 電極膜 9 を、更に備える。これ以外の構成は実施の形態 1 の半導体装置 1 0 と同じである。A 1 - S i とはんだけは合金層の形成が困難であり、はんだけ A 1 - S i に拡散するとオーミック不良および密着強度低下による剥離が発生する。その対策として、はんだけの合金層形成膜として N i 電極膜を有しオーミック電極へのはんだけ拡散防止のバリアメタル層として T i 電極膜を有する多層電極が用いられている。実施の形態 1 の半導体装置 1 0 に、A 1 - S i からなる第 2 電極膜 7 と N i からなる第 3 電極膜 5 の間に、A 1 - S i へのはんだけ拡散防止のため、T i からなる第 5 電極膜 9 を設けている。これにより、良好な電気特性を有する S i - T i 接合を維持しつつ、S i - T i 接合と N i の間に A 1 - S i を形成することができる。電極形成後の熱工程による多層電極膜から発生する応力による S i - T i 界面剥離抑制に加え、A 1 - S i へのはんだけ拡散を防止することによりはんだけ接合性悪化を抑制できる。20

#### 【 0 0 1 6 】

図 6 は、本発明の実施の形態 2 にかかる半導体装置 2 0 の製造方法を示すフローチャートである。第 3 電極膜 5 を形成するステップ S 1 0 4 の工程の前に、第 2 電極膜 7 の上にチタンからなる第 5 電極膜 9 を形成する工程（ステップ S 1 2 0 ）を更に備える。これ以外は図 4 のフローチャートに示す製造方法と同じである。30

#### 【 0 0 1 7 】

実施の形態 3 .

図 7 は、本発明の実施の形態 3 にかかる半導体装置 3 0 を示す図である。半導体装置 3 0 は N P N トランジスタである。半導体装置 3 0 は、一方の面に N 型シリコンからなるエミッタ層 1 1 を有し他方の面に N 型シリコンからなるコレクタ層 1 3 を有する P 型シリコン基板 1 2 を備える。P 型シリコン基板 1 2 がベース層となることで、エミッタ層 1 1 およびコレクタ層 1 3 を含む N P N トランジスタが構成される。図 8 は、半導体装置 3 0 の製造方法を示すフローチャートである。図 4 のステップ S 1 0 0 に代えて、P 型シリコン基板 1 2 の一方の面上に N 型シリコンからなるエミッタ層 1 1 を設け、他方の面上に N 型シリコンからなるコレクタ層 1 3 を設ける。これにより、実施の形態 1 と同様に、良好な電気特性を得つつ、P 型シリコン基板 1 2 に形成された保護膜などの機能が損なわれるのを抑制し、S i - T i 面の剥離を抑制することができる。40

#### 【 0 0 1 8 】

実施の形態 4 .

図 9 は、本発明の実施の形態 4 にかかる半導体装置 4 0 を示す図である。半導体装置 4 0 は、半導体装置 3 0 に T i からなる第 5 電極膜 9 を追加したものである。それ以外の構成は半導体装置 3 0 と同じである。図 1 0 は、半導体装置 4 0 の製造方法を示すフローチャートである。図 8 のフローチャートに、実施の形態 2 にかかるステップ S 1 2 0 を追加したものである。これにより、電極形成後の熱工程による多層電極膜から発生する応力に50

による Si - Ti 界面剥離抑制に加え、Al - Si へのはんだ拡散を防止することにより、はんだ接合性悪化を抑制できる。

【符号の説明】

【0019】

1 アノード層、2 N型シリコン基板、3 カソード層、4、5、6、7、9 電極膜

、10、20、30、40 半導体装置、11 エミッタ層、12 P型シリコン基板、

13 コレクタ層

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図 8】

【図 9】

4 : Ti

5 : Ni

6 : Au

7 : Al-Si

9 : Ti

11 : N-Si (エミッタ)

12 : P-Si (ベース)

13 : N-Si (コレクタ)

【図 10】

---

フロントページの続き

(72)発明者 吉浦 康博

東京都千代田区丸の内二丁目 7 番 3 号 三菱電機株式会社内

F ターム(参考) 4M104 AA01 BB14 CC01 FF02 FF17 GG02 GG06 HH05 HH08 HH15