(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6246509号

(P6246509)

(45) 発行日 平成29年12月13日(2017.12.13)

(24) 登録日 平成29年11月24日(2017.11.24)

(51) Int.Cl.

F 1

G 11 C 11/16 (2006.01)

G 11 C 13/00 (2006.01)G 11 C 11/16 230

G 11 C 13/00 400B

G 11 C 13/00 400G

請求項の数 10 (全 30 頁)

(21) 出願番号 特願2013-136299 (P2013-136299)

(22) 出願日 平成25年6月28日 (2013.6.28)

(65) 公開番号 特開2014-10885 (P2014-10885A)

(43) 公開日 平成26年1月20日 (2014.1.20)

審査請求日 平成28年6月27日 (2016.6.27)

(31) 優先権主張番号 13/538,869

(32) 優先日 平成24年6月29日 (2012.6.29)

(33) 優先権主張国 米国(US)

(73) 特許権者 390019839

三星電子株式会社

Samsung Electronics

Co., Ltd.

大韓民国京畿道水原市靈通区三星路129

129, Samsung-ro, Yeongtong-gu, Suwon-si, Gyeonggi-do, Republic

of Korea

(74) 代理人 100110364

弁理士 実廣 信哉

最終頁に続く

(54) 【発明の名称】 抵抗性メモリの感知增幅回路

## (57) 【特許請求の範囲】

## 【請求項 1】

第1出力信号を出力する第1差動出力端子と、

前記第1出力信号と反対である第2出力信号を出力する第2差動出力端子と、

抵抗性メモリセルと連関されたビットラインに連結された第1入力端子と、

参照メモリセルと連関された参照ラインに連結された第2入力端子と、

前記第2入力端子及び前記第1差動出力端子に連結され、参照ライン電流を通過させる

第1トランジスターと、

前記第1入力端子及び前記第1差動出力端子に連結され、前記第1トランジスターと直列に配列され、ビットライン電流を通過させる第2トランジスターと、

パワー供給電圧と接地電圧との間の電圧レベルを有する中間パワー供給電圧ノードに連結されたプリチャージ部分と、を含み、

前記プリチャージ部分は前記第1差動出力端子及び前記中間パワー供給電圧ノードに連結された第1プリチャージトランジスター及び前記第2差動出力端子及び前記中間パワー供給電圧ノードに連結された第2プリチャージトランジスターを含み、

前記プリチャージ部分は感知增幅回路のプリチャージ段階の間に動作し、前記第1差動出力端子の電圧レベルは前記参照ライン電流と前記ビットライン電流との間のデルタ平均電流にしたがって変化する抵抗性メモリの感知增幅回路。

## 【請求項 2】

前記ビットラインは前記参照ラインと連関された前記参照ライン電流の少なくとも一部

を再使用する請求項 1 に記載の抵抗性メモリの感知増幅回路。

**【請求項 3】**

前記第 2 トランジスターのドレーンは第 1 差動出力端子と第 1 トランジスターのドレーンに連結され、

前記第 2 トランジスターのソースは前記抵抗性メモリセルと連関された前記ビットラインに連結され、

前記第 1 差動出力端子はハイインピーダンス出力端子となり、

前記ハイインピーダンス出力端子の電圧レベルは前記感知増幅回路の増幅段階に応答して変化する請求項 1 又は 2 に記載の抵抗性メモリの感知増幅回路。

**【請求項 4】**

前記第 1 プリチャージトランジスターはプリチャージコントロール信号を受信し、前記プリチャージコントロール信号に応答して前記感知増幅回路の前記プリチャージ段階の間に前記参照メモリセルと連関された前記ビットライン及び前記参照ラインをプリチャージし、

前記第 2 プリチャージトランジスターは前記プリチャージコントロール信号を受信し、前記プリチャージコントロール信号に応答して前記感知増幅回路の前記プリチャージ段階の間に前記第 2 差動出力端子と連関された寄生キャパシタンスをプリチャージする請求項 1 に記載の抵抗性メモリの感知増幅回路。

**【請求項 5】**

前記第 1 及び第 2 差動出力端子に連結されたラッチ回路をさらに含み、

前記ラッチ回路は、

パワー供給電圧ノードに連結され、第 1 ラッチコントロール信号に応答して前記感知増幅回路のラッチ段階を活性化する第 1 ラッティイネーブルトランジスターと、

前記第 1 ラッティイネーブルトランジスター及び前記第 1 差動出力端子に連結された第 1 ラッチトランジスターと、

前記第 1 ラッティイネーブルトランジスター及び前記第 2 差動出力端子に連結された第 2 ラッチトランジスターと、

接地電圧ノードに連結され、第 2 ラッチコントロール信号に応答して前記感知増幅回路のラッチ段階を活性化する第 2 ラッティイネーブルトランジスターと、

前記第 2 ラッティイネーブルトランジスター及び前記第 1 差動出力端子に連結された第 3 ラッチトランジスターと、

前記第 2 ラッティイネーブルトランジスター及び前記第 2 差動出力端子に連結された第 4 ラッチトランジスターを含み、

前記第 1 乃至第 4 ラッチトランジスターは前記ラッチ段階の間に前記第 1 及び第 2 ラッチコントロール信号の各々によってターンオンされた前記第 1 及び第 2 ラッティイネーブルトランジスターに応答して前記抵抗性メモリセルに格納されたビット値にしたがって前記第 1 又は第 2 差動出力端子での論理値 “0” 又は論理値 “1” を各々ラッチする請求項 1 に記載の抵抗性メモリの感知増幅回路。

**【請求項 6】**

前記第 1 ラッティイネーブルトランジスターは PMOS トランジスターであり、

前記第 2 ラッティイネーブルトランジスターは NMOS トランジスターであり、

前記第 1 及び第 2 ラッチトランジスターは各々 PMOS トランジスターであり、

前記第 3 及び第 4 ラッチトランジスターは各々 NMOS トランジスターである請求項 5 に記載の抵抗性メモリの感知増幅回路。

**【請求項 7】**

前記第 1 ラッチトランジスターのソースは前記第 1 ラッティイネーブルトランジスターのドレーンに連結され、

前記第 2 ラッチトランジスターのソースは前記第 1 ラッティイネーブルトランジスターのドレーンに連結され、

前記第 3 ラッチトランジスターのソースは前記第 2 ラッティイネーブルトランジスターの

10

20

30

40

50

ドレーンに連結され、

前記第4ラッチトランジスターのソースは前記第2ラッチイネーブルトランジスターのドレーンに連結され、

前記第1ラッチトランジスターのゲートは前記第2差動出力端子に連結され、

前記第2ラッチトランジスターのゲートは前記第1差動出力端子に連結され、

前記第3ラッチトランジスターのゲートは前記第2差動出力端子に連結され、

前記第4ラッチトランジスターのゲートは前記第1差動出力端子に連結され、

第1及び第3ラッチトランジスターの各ドレーンは第1差動出力端子に連結され、

第2及び第4ラッチトランジスターの各ドレーンは第2差動出力端子に連結される請求項5に記載の抵抗性メモリの感知增幅回路。

10

#### 【請求項8】

前記抵抗性メモリセルは少なくともSTT-MRAMセル、MRAMセル、メモリスタRAMセル、又はCBRAMセルの中でいずれか1つを含む請求項1に記載の抵抗性メモリの感知增幅回路。

#### 【請求項9】

前記抵抗性メモリセルはSTT-MRAMセルである請求項1に記載の抵抗性メモリの感知增幅回路。

#### 【請求項10】

前記抵抗性メモリセルに連結されたソースラインをさらに含み、

前記ソースラインが接地電圧ノードに連結される時、前記感知增幅回路は第1トランジスターの特性を含み、

20

前記ソースラインがパワー供給電圧ノードに連結される時、前記感知增幅回路は前記第1トランジスターの特性と比較してスワップされる第2トランジスターの特性を含む請求項1に記載の抵抗性メモリの感知增幅回路。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は抵抗性メモリの感知增幅回路に関する。

##### 【背景技術】

##### 【0002】

30

本発明は抵抗性メモリの感知增幅回路に関し、さらに具体的には電流再使用機能(`current re-using capabilities`)、高いノイズ耐性特性、そして読み出し及び/又は再使用動作モード(`read / re-write operation modes`)を有する抵抗性メモリの感知增幅回路に関する。

##### 【0003】

抵抗性メモリは他の次世代不揮発性メモリの中でも、市場でより広く使用されることと予想される。抵抗性メモリは、例えば、STT-MRAM(`spin transfer torque magnetoresistive random-access memory`)、MRAM(`magnetoresistive random-access memory`)、memristor RAM、ReRAM、CBRAM等を含むことができる。

40

##### 【0004】

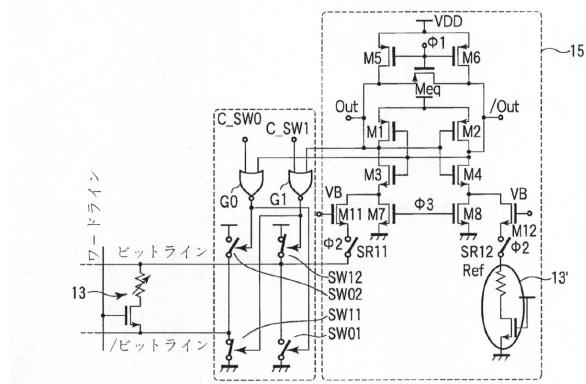

図1Aは従来技術による感知増幅器を示す回路図である。図1Aを参照すれば、ラッチ回路は各々読み出し電流ソース(`read current source`、IR1)及び参照電流ソース(`reference current source`、IR2)に対応するM1、M2、M3、M4のMOSトランジスター及びM5、M6のMOSトランジスターで構成される。感知増幅器はM7、M8のMOSトランジスターで構成される読み出し回路15の動作は(a)プリ-チャージモード(`pre-charge mode`)、(b)増幅モード(`amplification mode`)、(c)ラッチ及び再読み出しモード(`latch + rewrite mode`)を含む。各モードは図1B~1Dに参

50

考として図示されている。初期状態で、スイッチコントローラからのコントロール信号 1、2、3 はロー状態（“L”）に設定される。

#### 【0005】

図 1 B ~ 1 D は従来技術において、互に異なる状態での動作を示す図 1 A の等価回路である。

#### 【0006】

図 1 B はプリ - チャージモードでの等価回路を示す。コントロール信号 2 は読み出し電流バス (read current path) に対するプリ - チャージを開始するため 10 にハイ（“H”）に設定される。プリ - チャージ電流はプリ - チャージトランジスター M5、M6 (PMOSトランジスター) から MRAMセル 13 と参照セル 13' 方向に流れ、図 1 A のラッチ回路の一部であり、交差して連結されたトランジスター M3、M4 (NMOSトランジスター) とクランプトランジスター M11、M12 (NMOSトランジスター) を流れる。プリ - チャージモードと安定モード (stable mode) で、読み出しデータ (Out、/Out) はプリ - チャージトランジスター M5、M6 と等化トランジスター Meq (PMOSトランジスター) によって、パワー供給電圧 VDD に近い電圧に設定される。したがって、トランジスター M1、M2 はオフ状態になり、トランジスター M1 ~ M4 を含むラッチ回路は動作しない。

#### 【0007】

図 1 C は増幅モードでの等価回路を示す。コントロール信号 1 はハイ（“H”）に設定され、トランジスター M5、M6、Meq はターンオフされる。データ (Out、/Out) はパワー供給電圧 VDD からトランジスター M1、M2 まで減少し、トランジスター M1 ~ M4 を含むラッチ回路の正のフィードバック (positive feedback) による増幅、そしてデータ (Out、/Out) が決定される。この時、読み出し電流バスはラッチ回路のドライブ電流バス (drive current path) と同じであり、コントロール信号 1 はハイ（“H”）になって、動作が連続的にプリ - チャージモードから増幅モードに変化される。たとえ増幅モード間の全般的な回路が図示されているが、図 1 C ではクランプトランジスター M11、M12 が図示されない。

#### 【0008】

図 1 D はラッチ及び再書き込みモードでの等価回路である。図 1 D に示したように、出力 (Out、/Out) の間の電圧差が十分に大きい時、トランジスター M7、M8 をブースティングするようにコントロール信号 3 がハイ（“H”）に設定され、トランジスター M1 ~ M4 を含むラッチ回路の増幅が加速される。ラッチ回路からの出力、データ (Out、/Out) が決定される時、再書き込み動作が遂行される。

#### 【0009】

従来の抵抗性メモリで使用される感知増幅技術は問題が発生することができる。例えば、従来の感知増幅器は複数のビットラインと複数の参照ラインに使用される並列電流によって過渡な正の電流を使用しなければならない。結果的に、電流消耗量が許容値を超過され得る。また、従来の感知増幅技術のノイズ減少 (noise immunity) は許容値より低いことがあり得る。

#### 【0010】

また、抵抗性メモリの感知増幅器技術を改善しようとする時、特別な問題が発生することができる。例えば、MRAMメモリセルにおいて、メモリセルに格納されたデータが“1”であるか、“0”であるかを判別する時、MRAMセルに過渡な電流が流れれば、読み出しディスターブ (read disturb) 問題が発生する。言い換えれば、メモリセルに格納された値が意図せずに“1”から“0”に、又はその反対に変更されてしまうことがある。

#### 【0011】

読み出しディスターブを避けるための 1 つの方案は感知増幅器の読み出し電流を減少させることである。しかし、このような方法は応答時間の遅くなること、出力信号レベルの減少、データ読み出し比率の減少、望まない電磁気ノイズ及び他のディスターブに対する敏感度

10

20

30

40

50

の増加のような意図しなかった問題を発生させ得る。このようなパフォーマンス劣化は望まないことである。さらに、このような電磁気ノイズはそれ自体にセル又は感知増幅器の出力信号のデータが変わってしまう場合があり得る。

#### 【0012】

したがって、低い電力消耗及び強いノイズ減少特性を有し、低い供給電圧でも速く応答する読み出し／再書き込み機能を提供する抵抗性メモリの感知増幅器が要求される。

#### 【発明の概要】

#### 【発明が解決しようする課題】

#### 【0013】

本発明の目的は電流再使用機能 (current re-using capabilities)、高いノイズ耐性特性、そして読み出し及び／又は再使用動作モード (read / re-write operation modes) を有する抵抗性メモリの感知増幅回路を提供することにある。10

#### 【課題を解決するための手段】

#### 【0014】

本発明による抵抗性メモリの感知増幅回路は、第1出力信号を出力する第1差動出力端子と、前記第1出力信号と反対である第2出力信号を出力する第2差動出力端子と、抵抗性メモリセルと連関されたビットラインに連結された第1入力端子と、参照メモリセルと連関された参照ラインに連結された第2入力端子と、前記第2入力端子及び前記第1差動出力端子に連結され、参照ライン電流を通過させる第1トランジスターと、前記第1差動出力端子に連結され、前記第1トランジスターと直列に配列され、ビットライン電流を通過させる第2トランジスターと、を含み、前記第1差動出力端子の電圧レベルは前記参照ライン電流と前記ビットライン電流との間のデルタ平均電流にしたがって変化する。20

#### 【0015】

本発明にしたがう実施形態において、抵抗性メモリに格納されたビット情報を感知する方法、感知増幅回路のプリチャージ段階で、プリチャージ部分によって少なくともビットライン又は参照ラインをプリチャージする段階と、前記感知増幅回路の増幅段階で、参照ライン電流を前記参照ラインを通じて流れるようにし、ビットライン電流を前記ビットラインを通じて流れるようにする段階と、前記感知増幅回路の前記増幅段階で、前記参照ライン電流及び前記ビットライン電流の間のデルタ平均電流に応答して第1差動出力端子での電圧変化をもたらす段階と、を含む。また、感知増幅回路のラッチ段階で、ラッチ回路によって前記第1差動出力端子又は第2差動出力端子での論理値“0”又は論理値“1”を各々ラッチする段階をさらに含む。30

#### 【0016】

本発明において、メモリ装置、複数のワードラインと、前記ワードラインと交差するように配列された複数のビットラインと、前記ワードライン及び前記ビットラインが交差する部分に配列された抵抗性メモリセルを各々含む複数のメモリブロックと、前記複数のメモリブロックの少なくとも1つのブロックでの、対応するビットライン及び対応するメモリセルと各々連関された複数の感知増幅器と、前記複数の感知増幅器に連結され、少なくとも前記感知増幅器の各増幅段階の間に参照ライン電流を複写する電流ミラー回路と、を含み、前記ビットラインは前記複写された参照電流の一部を再使用する。40

#### 【発明の効果】

#### 【0017】

本発明による抵抗性メモリの感知増幅回路は、電流再使用機能 (current re-using capabilities)、高いノイズ耐性特性、そして読み出し及び／又は再使用動作モード (read / re-write operation modes) を有する。

#### 【図面の簡単な説明】

#### 【0018】

【図1A】従来技術による感知増幅器を示す回路図である。

50

【図 1 B】従来技術において、互に異なる状態での動作を示す図 1 A の等価回路である。

【図 1 C】従来技術において、互に異なる状態での動作を示す図 1 A の等価回路である。

【図 1 D】従来技術において、互に異なる状態での動作を示す図 1 A の等価回路である。

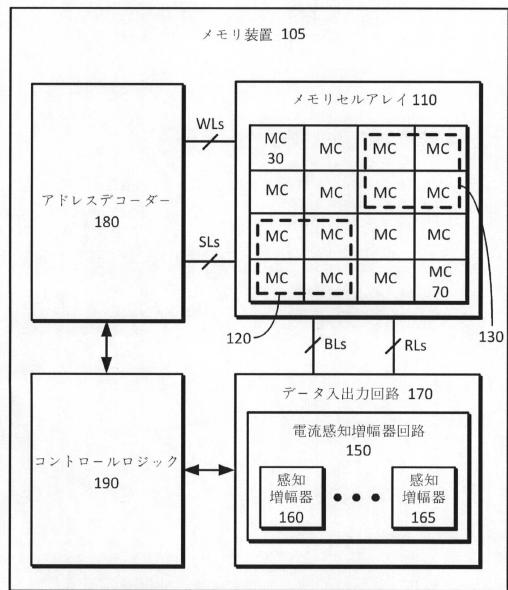

【図 2】本発明の実施形態による感知增幅回路を含むメモリ装置の実施形態を示す図面である。

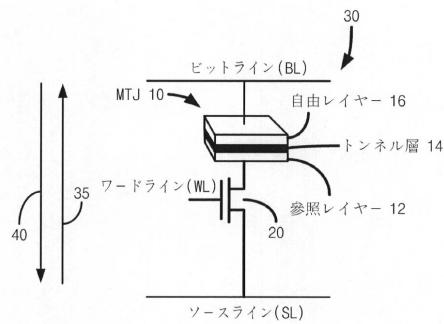

【図 3 A】図 2 のメモリ装置のメモリセルアレイに含まれた S T T - M R A M メモリセルを例示的に示す図面である。

【図 3 B】図 2 のメモリ装置のメモリセルアレイに含まれた S T T - M R A M メモリセルを例示的に示す図面である。

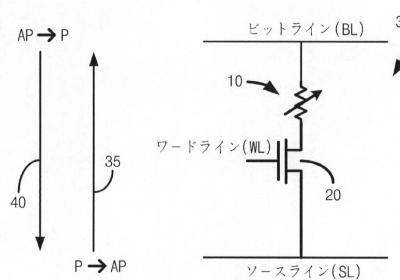

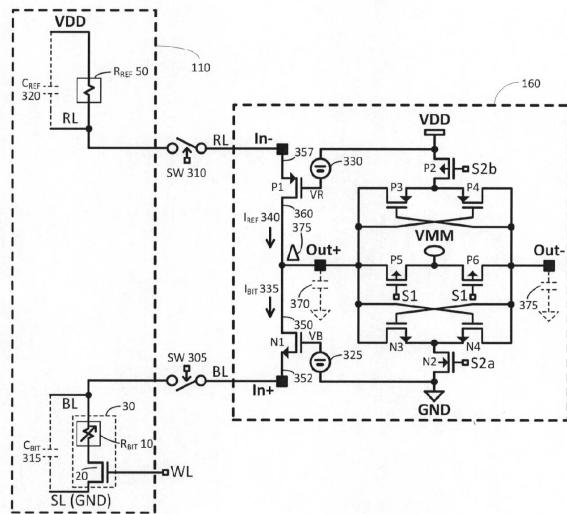

【図 4 A】本発明にしたがう図 2 のメモリ装置のメモリセルと連関された図 2 の感知增幅器の一例を示す図面である。 10

【図 4 B】図 4 A の感知增幅器に連結されて使用されるコントロール信号を生成するコントロール信号回路の一例を示す図面である。

【図 5】“準備”又は“ブリ・チャージ”段階の動作と連関された図 4 A の感知增幅器の等価回路の一例を示す図面である。

【図 6】“セット”又は“増幅”段階の動作と連関された図 4 A の感知增幅器の等価回路の一例を示す図面である。

【図 7】“進行”又は“ラッチ”段階と連関された図 4 A の感知增幅器の等価回路の一例を示す図面である。

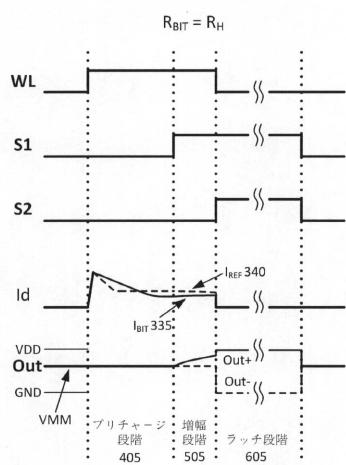

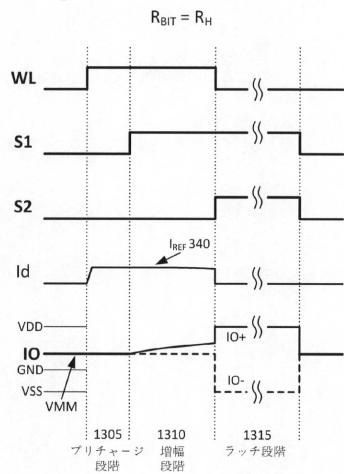

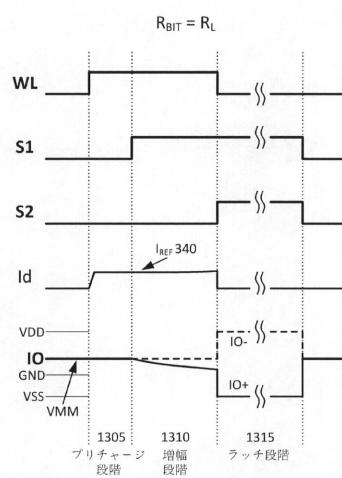

【図 8】本発明の一実施形態にしたがってメモリセル抵抗が“H”値である  $R_H$  に以前に設定されている時、図 4 A の感知增幅器の互に異なる段階での波形の一例を示す図面である。 20

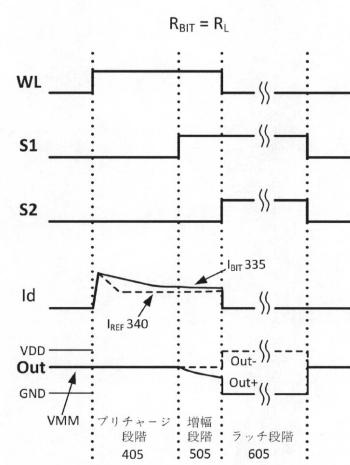

【図 9】本発明の一実施形態にしたがってメモリセル抵抗が“L”値である  $R_L$  に以前に設定されている時、図 4 A の感知增幅器の互に異なる段階での波形の一例を示す図面である。

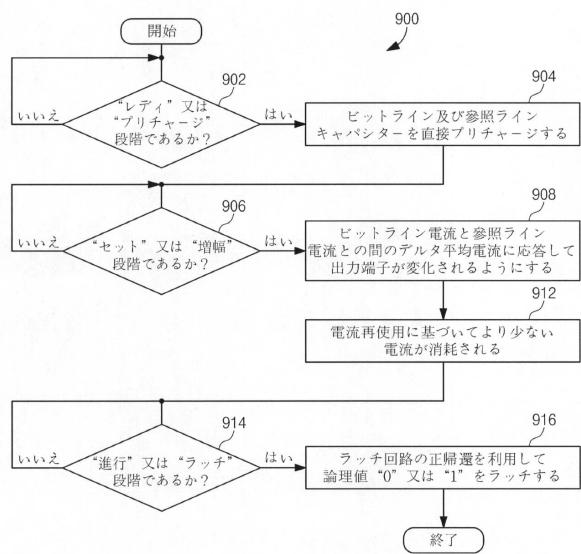

【図 10】本発明にしたがう感知增幅器を使用する抵抗性メモリのデータ感知動作を示す順序図である。

【図 11 A】本発明の他の実施形態による電流ミラーと連関された図 2 の感知增幅器の一実施形態を示す図面である。

【図 11 B】図 11 A の回路のためのラッティネーブルコントロール信号を生成するコントロール信号回路の一例を示す図面である。 30

【図 12 A】本発明の実施形態による読み出し／再書き込み機能を含む感知增幅器の一例を示す図面である。

【図 12 B】図 12 A の回路のためのラッティネーブルコントロール信号を生成するコントロール信号回路の一例を示す図面である。

【図 13 A】本発明の実施形態によるメモリセル抵抗が以前にハイに設定されている時、図 12 A の感知增幅器の互に異なる段階と連関された波形図を例示的に示す図面である。

【図 13 B】本発明の実施形態によるメモリセル抵抗が以前にローに設定されている時、図 12 A の感知增幅器の互に異なる段階と連関された波形図を例示的に示す図面である。

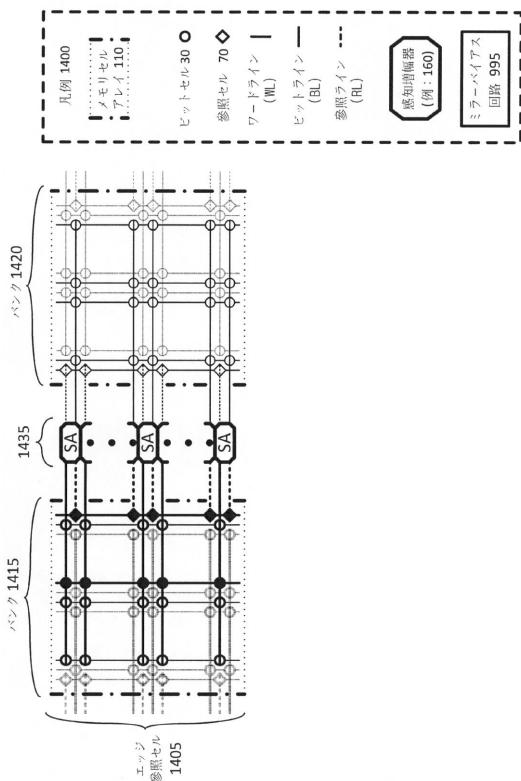

【図 14 A】本発明の他の実施形態によるエッジ-参照セル配列又はパターンでのメモリセルアレイ及び連関されたメモリブロックのレイアウトの実施形態を示す図面である。 40

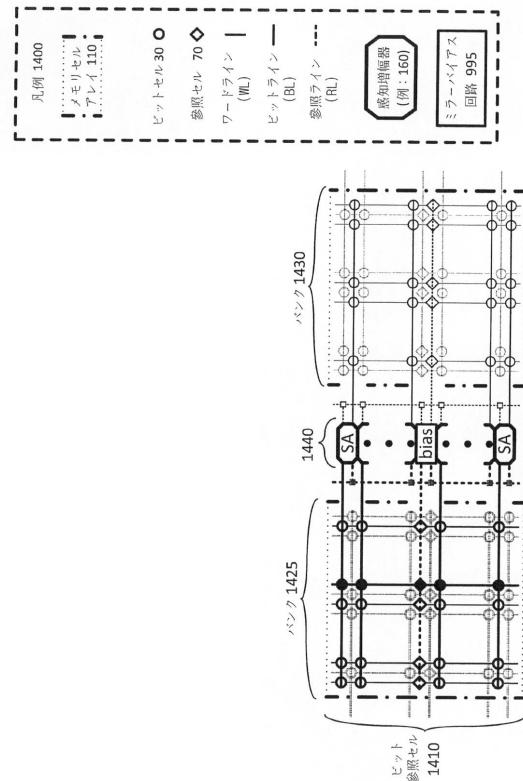

【図 14 B】本発明の他の実施形態によるビット-参照セル配列又はパターンでのメモリセルアレイ及び連関されたメモリブロックのレイアウトの実施形態を示す図面である。

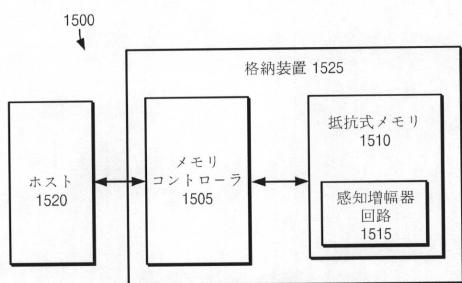

【図 15】本発明の実施形態に他の抵抗性メモリ装置の多様な適用例を示す図面である。

【図 16】本発明の実施形態による抵抗性メモリ装置を含むコンピューティングシステムに関する図面である。

【図 17】本発明の実施形態による抵抗性メモリを含むコンピューティングシステムを示す図面である。

【図 18】フラッシュメモリを代替する抵抗性メモリを使用したストレージクラスメモリを含むメモリシステムの本発明にしたがう一実施形態を示す図面である。 50

【図19】同期式DRAMを代替する抵抗性メモリを使用したストレージクラスメモリを含むメモリシステムの本発明にしたがう一実施形態を示す図面である。

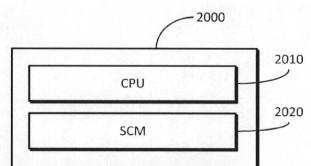

【図20】同期式DRAM及びフラッシュメモリを代替して抵抗性メモリを使用するストレージクラスメモリを含むメモリシステムの本発明にしたがう一実施形態を示す図面である。

**【発明を実施するための形態】**

**【0019】**

本発明の長所及び特徴、そしてそれを達成する方法は添付される図面と共に詳細に記載されている実施形態を通じて説明される。しかし、本発明はここで説明される実施形態に限定されなく、他の形態に具体化されることもあり得る。本実施形態は本発明が属する技術分野で通常の知識を有する者に本発明の技術的思想を容易に実施できるように詳細に説明するために提供される。10

**【0020】**

図面において、本発明の実施形態は図示された特定形態に限定されることではなく、説明を明確するために誇張されている部分もある。また、明細書全体にかけて同一の参照番号で表示された部分は同一の構成要素を示す。

**【0021】**

本明細書で“及び／又は”という表現は前後に羅列された構成要素の中で少なくとも1つを含む意味に使用される。また、‘連結される／結合される’という表現は他の構成要素と直接的に連結させるか、或いは他の構成要素を通じて間接的に連結されることを含む意味として使用される。本明細書で单数形は文句で特別に言及しない限り複数形も含む。また、明細書で使用される“含む”又は“含む”と言及された構成要素、段階、動作及び素子は1つ以上の他の構成要素、段階、動作、素子及び装置の存在又は追加を意味する。20

**【0022】**

図2は本発明の実施形態による感知增幅回路150を含むメモリ装置105の実施形態を示す図面である。図2を参照すれば、メモリ装置105はメモリセルアレイ110、データ入出力回路170、アドレスデコーダー180、及び制御ロジック190を含む。データ入出力回路170は感知增幅回路150を含み、感知增幅回路150は本発明の実施形態にしたがってメモリセルアレイ110に格納されたビット情報をセンシングするか、或いは読み出す動作を遂行する。30

**【0023】**

図2を参照すれば、メモリセルアレイ110は複数のメモリセル30を含み、各メモリセルは1つ又はその以上のデータビットを格納する。メモリセルMCは複数のワードラインWLS、複数のソースラインSLS、そして複数のビットラインBLSに連結される。ビットラインBLSはワードラインWLSと交差するように配置される。また、メモリセルの中で一部は参照メモリセル70であり得る。参照メモリセル70は複数の参照ラインRLSに連結される。参照メモリセルは以下でさらに詳細に説明される。

**【0024】**

メモリセルはワードラインとビットラインが交差する位置(図示せず)に配置され得る。メモリセル30はメモリブロック120、130のようにメモリブロックにグループ化され得る。例えば、1Mbのメモリブロックにおいて、1000個のワードラインと100個のビットラインがメモリブロックと連関され得る。したがって、このようなブロックと連関された各ビットラインは連関された1000個のメモリセルを有することができる。しかし、これは例示的なことであり、いずれか適当な数字のワードライン、ビットライン及び／又はメモリセルが各ブロックと連関され得る。感知增幅回路150は複数の感知增幅器(例えば、160、165)を包含することができる。各感知增幅器はメモリブロック(例えば、120、130)の中で対応するいずれか1つのメモリブロックのビットラインと連関され得る。即ち、各ビットラインBLSはそれと連関された対応する感知增幅器(例えば、160、165)を有することができる。40

**【0025】**

50

アドレスデコーダー 180 はワードライン W L s とソースライン S L s を通じてメモリセルアレイ 110 に連結される。アドレスデコーダー 180 はコントロールロジック 190 の制御に応答して動作する。アドレスデコーダー 180 は入力アドレスをデコーディングしてワードライン W L s 及びソースライン S L s へ提供する。アドレスデコーダー 180 はコントロールロジック 190 からパワー（例えば、電圧又は電流）を受信し、選択されたワードライン又は非選択されたワードラインへこれを提供する。

#### 【0026】

データ入出力回路 170 はビットライン B L s を通じてメモリセルアレイ 110 に連結される。さらに具体的に、各感知增幅器（例えば、160、165）はメモリブロック（例えば、120、130）の中で対応するいずれか 1 つのメモリブロックのビットラインに連結され得る。データ入出力回路 170 はコントロールロジック 190 の制御に応答して動作する。データ入出力回路 170 はアドレスデコーダー 180 からのビットライン選択信号（図示せず）に応答してビットラインを選択する。データ入出力回路 170 はコントロールロジック 190 からパワー（例えば、電圧又は電流）を受信し、選択されたビットラインへこれを提供する。

#### 【0027】

コントロールロジック 190 はメモリ装置 105 の全般的な動作を制御する。コントロールロジック 190 は外部パワー及び / 又はコントロール信号を受信する。コントロールロジック 190 は外部電圧を利用して内部動作に必要であるパワーを生成することができる。コントロールロジック 190 は前記コントロール信号に応答して読み出し、書き込み、及び / 又は消去動作を制御する。

#### 【0028】

図 3 A 及び図 3 B は図 2 のメモリ装置 105 のメモリセルアレイ 110 に含まれた S T T - M R A M メモリセル 30 を例示的に示す図面である。

#### 【0029】

一実施形態において、メモリセルアレイ 110 は複数の S T T - M R A M ( spin transfer torque magnetoresistive random-access memory ) メモリセルを包含することができる。しかし、本発明の実施形態はこれに限定されなく、S T T 以外の M R A M 、メモリスト R A M ( memristor RAM ) 、 C B R A M 等にも適用されることが理解できる。

#### 【0030】

図 3 A はマグネチックトンネル接合 ( magnetic tunnel junction 、以下 M T J ) 10 及びこれと連関された選択トランジスター 20 を示す。 M T J 10 は S T T - M R A M タイプメモリセルで多様な抵抗を形成し、選択トランジスター 20 は M T J 10 と共に S T T - M R A M セル 30 を形成する。 M T J 10 は基準層 ( reference or pinned layer 12 ) 、自由層 16 、そして基準層 12 と自由層 16 との間に位置するトンネル層 14 を含む。トランジスター 20 は P M O S トランジスターに比べて高い電流ドライブ ( current drive ) 、低い閾値電圧、そして小さい面積を有する N M O S トランジスターの特性によって普通 N M O S トランジスターが使用される。 M R A M セル 30 に “ 1 ” を書き込むのに使用される電流は “ 0 ” を書き込むのに使用される電流と異なり得る。このような 2 つの書き込み動作の間の電流流れ方向の非対称性はトランジスター 20 のゲート - ソース電圧 ( gate-to-source voltage ) の非対称に生ずることができる。

#### 【0031】

以下では、 M T J の自由層及び基準層が平衡状態 P である時、該当 M R A M セルはロジック “ 0 ” 状態であると定義される。 M T J の自由層及び基準層が平衡状態 P であれば、低い抵抗を有する。反対に、 M T J の自由層及び基準層が反平衡状態 A P である時、該当 M R A M セルはロジック “ 1 ” 状態であると定義される。 M T J の自由層及び基準層が反平衡状態 A P であれば、高い抵抗を有する。但し、これは例示的なことであり、他の実施形態において、反平衡状態 A P である時、該当 M R A M セルはロジック “ 0 ” 状態である

10

20

30

40

50

と定義され、平衡状態 P である時、該当 M R A M セルはロジック “ 1 ” 状態であると定義され得る。また、図 3 A に示したように、以下では M T J 1 0 の基準層が選択トランジスターと対向すると仮定される。

#### 【 0 0 3 2 】

したがって、上述したように、上方に向かう矢印 3 5 方向にしたがう電流の流れは( i ) 平衡状態 P から反平衡状態 A P にスイッチングして “ 1 ” を書き込むか、或いは( i i ) 以前の設定された M T J の反平衡状態 A P を安定化することができる。これと類似して、下方に向かう矢印 4 0 方向にしたがう電流の流れは( i ) 反平衡状態 A P から平衡状態 P にスイッチングして “ 0 ” を書き込むか、或いは( i i ) 以前の設定された M T J の平衡状態 P を安定化することができる。但し、これは例示的なことであり、他の実施形態では先に実施形態と反対に M T J の自由層が選択トランジスターと対向することができる。この場合に、たとえ図示されずが、上方に向かう矢印 3 5 方向にしたがう電流の流れは( i ) 反平衡状態 A P から平衡状態 P にスイッチするか、或いは( i i ) 以前の設定された M T J の平衡状態 P を安定化することができる。これと類似に、下方に向かう矢印 4 0 方向にしたがう電流の流れは( i ) 平衡状態 A P から反平衡状態 A P にスイッチするか、或いは( i i ) 以前の設定された M T J の反平衡状態 A P を安定化することができる。

10

#### 【 0 0 3 3 】

図 3 B は図 3 A の M R A M セル 3 0 の M T J 1 0 を格納されたデータにしたがって可変する抵抗を有する格納素子として表現した図面である。M T J 1 0 は( i ) 電流の流れが矢印 3 5 方向である時、その状態を平衡状態 P から反平衡状態 A P に変更し、及び / 又は( i i ) 電流の流れが矢印 4 0 方向である時、その状態を反平衡状態 A P から平衡状態 P に変更する。

20

#### 【 0 0 3 4 】

M T J 1 0 を反平衡状態 A P から平衡状態 P に又はその反対にスイッチするのに必要である電圧は臨界値 V c を超過しなければならない。この電圧に対応する電流は臨界電流又はスイッチング電流 I c であると称される。一般動作モードで、低い抵抗の平衡状態 P から高い抵抗の反平衡状態 A P に遷移するために、正の電圧である V c が提供されて少なくともスイッチング電流 I c 以上の電流レベルがメモリセルへ流れる。一旦、反平衡状態 A P であれば、提供される電圧を除去することは M T J 1 0 の状態に影響を及ぼない。これと同様に、一般動作モードで反平衡状態 A P から平衡状態 P に遷移するために、負の電圧である V c が提供されて少なくともスイッチング電流 I c 以上の電流レベルがメモリセルへ反対方向に流れる。一旦、平衡状態 P であれば、提供される電圧を除去することは M T J 1 0 の状態に影響を及ぼない。

30

#### 【 0 0 3 5 】

言い換えるれば、M T J 1 0 は高い抵抗又は論理 “ 1 ” 状態に対応する反平衡状態から平衡状態にスイッチできることができる、これによって “ 0 ” ( 例えは、低い抵抗又は論理 “ 0 ” 状態 ) を格納することができる。M T J 1 0 が初期に論理 “ 1 ” 又は反平衡状態であると仮定すれば、一般モードで “ 0 ” を格納するために臨界電流 I c と同一であるか、或いは大きい電流が矢印 4 0 方向に選択トランジスター 2 0 を通じて流れなければならない。このために、選択トランジスター 2 0 のソースノード ( S L 又はソースライン ) は抵抗バス ( 図示せず ) を通じて接地電圧に連結され、正の電圧が選択トランジスター 2 0 のゲートノード ( W L 又はワードライン ) へ提供され、正の電圧が選択トランジスター 2 0 のドレーンノード ( B L 又はビットライン ) へ提供される。

40

#### 【 0 0 3 6 】

先に説明されたように、M T J 1 0 はまた平衡状態から反平衡状態にスイッチされ、これによって、“ 1 ” を格納できる。M T J 1 0 が初期に論理 “ 0 ” 又は平衡状態であると仮定すれば、一般モードで “ 1 ” を格納するために臨界電流 I c と同一であるか、或いは大きい電流が矢印 3 5 方向に選択トランジスター 2 0 を通じて流れなければならない。このために、ソースノード ( S L 又はソースライン ) には抵抗バス ( 図示せず ) を通じて正の電圧に提供され、ゲートノード W L には正の電圧が提供され、ドレーンノード B L は抵

50

抗パス（図示せず）を通じて接地電圧に連結される。

【0037】

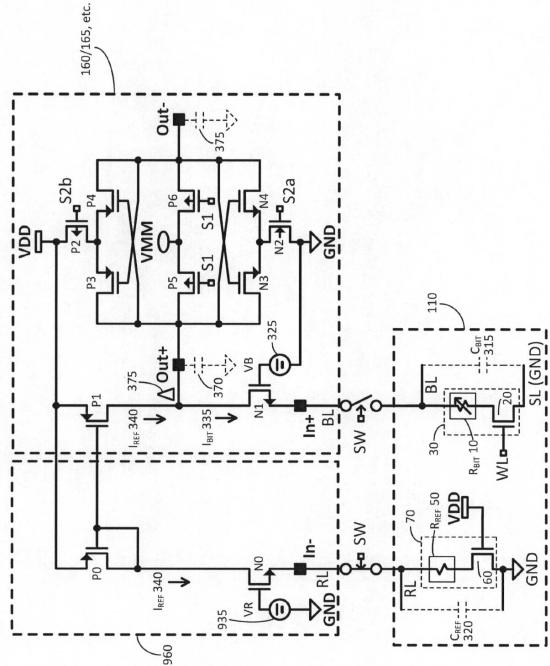

図4Aは本発明にしたがう図2のメモリ装置105のメモリセル30と連関された図2の感知増幅器160の一例を示す図面である。たとえ1つのメモリセル30が図示されているが、適當な数字のメモリセルが感知増幅器160に連結させるか、或いは連関されることが理解できる。

【0038】

本発明の実施形態は低い電流消耗特性、強いノイズ耐性（noise immunity）を有し、低い供給電圧でも動作でき、速い速度に動作し、読み出し／再書き込み動作が可能である抵抗性メモリのための感知増幅器を含む。

10

【0039】

感知増幅器160は第1出力信号を出力する第1差動出力端子Out+及び第1出力信号と反対である第2出力信号を出力する第2差動出力端子Out-を含む。出力信号はメモリセル30に格納されたビットデータにしたがって論理値“0”又は論理値“1”の中でいずれか1つに対応する。

【0040】

第1入力端子In+は抵抗性メモリセル30と連関されたビットライン9、BLに連結される。第2入力端子In-は参照抵抗R<sub>REF</sub>、50と連関された参照ラインRLに連結される。参照抵抗R<sub>REF</sub>、50はメモリセル30が論理値“0”（例えば、R<sub>BIT</sub>がR<sub>L</sub>と同一である時）又は論理値“1”（例えば、R<sub>BIT</sub>がR<sub>H</sub>と同一である時）を格納しているか否かを判断する時、参照として使用される。たとえば、図4Aには図示しないが、他の実施形態としてPMOS選択トランジスターが参照抵抗R<sub>REF</sub>、50に連結されることが理解できる。メモリセル30の選択トランジスター20のゲート端子は対応するワードラインWLに連結される。

20

【0041】

参照抵抗R<sub>REF</sub>、50は所定抵抗を有するようにデザインされることができる。例えば、参照抵抗R<sub>REF</sub>、50はR<sub>BIT</sub>の高抵抗R<sub>H</sub>と低抵抗R<sub>L</sub>との間の中間値を有することができる。一実施形態として、参照抵抗R<sub>REF</sub>は $2 / (1 / R_H + 1 / R_L)$ の抵抗であり得る。参照抵抗R<sub>REF</sub>が $2 / (1 / R_H + 1 / R_L)$ の抵抗にデザインされる時、電圧発生器325によって生成された電圧VBは電圧発生器330によって生成された電圧VRと同一であるか、或いは実質的に同一である。

30

【0042】

他の実施形態において、参照抵抗R<sub>REF</sub>はR<sub>H</sub>又はR<sub>L</sub>の中でいずれか1つの抵抗を有することができる。参照抵抗R<sub>REF</sub>がR<sub>H</sub>の抵抗を有する時、参照ライン電流I<sub>REF</sub>、340は電圧発生器330によって生成されてトランジスターP1のゲート端子に提供される電圧VRによって調整され得る。同時に、ビットライン電流I<sub>BIT</sub>、335は電圧発生器325によって生成されてトランジスターN1のゲート端子に提供される電圧VBによって調整され得る。この実施形態において、電圧VRは電圧VBに比べて大きい。

【0043】

参照抵抗R<sub>REF</sub>がR<sub>L</sub>の抵抗を有する時、参照ライン電流I<sub>REF</sub>、340は電圧発生器330によって生成されてトランジスターP1のゲート端子に提供される電圧VRによって調整され得る。同時に、ビットライン電流I<sub>BIT</sub>、335は電圧発生器325によって生成されてトランジスターN1のゲート端子に提供される電圧VBによって調整され得る。この実施形態において、電圧VBは電圧VRに比べて大きい。

40

【0044】

感知増幅器160の動作を説明するために、参照抵抗R<sub>REF</sub>は $2 / (1 / R_H + R_L)$ の抵抗を有すると仮定される。また、電圧VBは電圧VRと同一であるか、或いは実質的に同一であると仮定される。

【0045】

50

メモリセル回路及び連関された導電ラインによって、所謂寄生キャパシタンス (parasitic capacitance) であるビットラインキャパシター  $C_{B\text{IT}}$ 、315がビットラインBLとソースラインSLとの間に存在することができる。これと類似に、所謂寄生キャパシタンスである参照ラインキャパシター  $C_{REF}$ 、320が参照ラインRLと正のパワー供給電圧ノードVDDとの間に存在することができる。ビットラインキャパシター315と参照ラインキャパシター320は感知増幅器160のプリ-チャージ段階の間に以下で説明されるようにプリ-チャージされる。スイッチ305、310はメモリセルアレイ110のメモリセル又は参照セルを感知増幅器160に連結されるか、或いは連結を遮断する。

## 【0046】

10

感知増幅器は次の3つの主要段階で動作する。即ち、A) “準備 (ready)” 又は “プリ-チャージ (pre-charge)” 段階、B) “セット (set)” 又は “増幅 (amplification)” 段階、C) “進行 (go)” 又は “ラッチ (latch)” 段階。多様な動作段階は以下でさらに詳細に説明される。

## 【0047】

感知増幅器160は第1トランジスターP1を含み、第1トランジスターP1はパワー(例えば、VDD)、参照ラインRL、第1差動出力端子Out+に連結される。第1トランジスターP1は参照ライン電流  $I_{REF}$ 、340を導電する。感知増幅器160はまた第2トランジスターN1を含み、第2トランジスターN1はビットラインBL、第1差動出力端子Out+に連結される。第2トランジスターN1はビットライン電流  $I_{BIT}$ 、335を導電する。

20

## 【0048】

感知増幅器160は内部供給電圧ノードVMMに連結されたプリ-チャージ部分をさらに含む。プリ-チャージ部分は、例えば、第1プリ-チャージトランジスターP5及び第2プリ-チャージトランジスターP6を包含でき、第1プリ-チャージトランジスターP5は第1差動出力端子Out+及び内部供給電圧ノードVMMに連結され、第2プリ-チャージトランジスターP6は第2差動出力端子Out-及び内部供給電圧ノードVMMに連結される。プリ-チャージ部分は感知増幅器のプリ-チャージ段階の間に動作する。トランジスターP5、P6は、例えば、エンハンスマントモードPMOSローディングタ입トランジスター(enhancement mode PMOS loading transistor)、デジタルモードオン/オフタイプトランジスター(digital mode on/off type transistor)であり得る。但し、これは例示的なことであり、他のMOSトランジスターが本発明にしたがって使用され得ることが理解できる。

30

## 【0049】

内部パワー供給電圧ノードVMMはパワー供給電圧VDDと接地電圧GNDの間の電圧レベルを有する。一実施形態において、内部パワー供給電圧ノードVMMの電圧レベルはパワー供給電圧VDDの1/2又はこれに類似なレベルであり得る。他の実施形態において、内部パワー供給電圧ノードVMMの電圧レベルはパワー供給電圧VDDの2/3又はこれに類似なレベルであり得る。但し、これは例示的なことであり、適当な内部供給電圧レベルが使用され得ることが理解できる。内部パワー供給電圧ノードVMMはまた1つ又はその以上の信号又は感知増幅器160の素子のためにACグラウンド(AC ground)に動作できる。

40

## 【0050】

“準備”又は“プリ-チャージ”段階の動作の間に、プリ-チャージトランジスターP5、P6は各々ゲートを通じてコントロール信号S1を受信する。プリ-チャージ信号S1は図2のコントロールロジック190によって生成され得る。プリ-チャージトランジスターP5はプリ-チャージコントロール信号S1に応答して感知増幅器の“準備”又は“プリ-チャージ”段階でビットライン電流  $I_{BIT}$ 、335の少なくとも一部を生成し、ビットライン電流  $I_{BIT}$ 、335はトランジスターN1を通じて少なくともメモリセ

50

ル 3 0 と連関されたビットライン B L 及びビットラインキャパシター C<sub>B I T</sub>、 3 1 5 をプリ - チャージする。加えて、第 1 差動出力端子 Out + と連関された寄生キャパシタンス 3 7 0 が充電される。さらに、プリ - チャージトランジスター P 5 はプリ - チャージコントロール信号 S 1 に応答して感知増幅器の“準備”又は“プリ - チャージ”段階で参照ライン電流 I<sub>R E F</sub>、 3 4 0 の少なくとも一部を生成し、参照ライン電流 I<sub>R E F</sub>、 3 4 0 はトランジスター P 1 を通じて少なくとも参照ライン R L 及び参照ラインキャパシター C<sub>R E F</sub>、 3 2 0 をプリ - チャージする。プリ - チャージトランジスター P 6 はプリ - チャージコントロール信号 S 1 を受信し、プリ - チャージコントロール信号 S 1 に応答して感知増幅器の“準備”又は“プリ - チャージ”段階で少なくとも第 2 差動出力端子 Out - と連関された寄生キャパシタンス 3 7 5 をプリ - チャージする。

10

### 【 0 0 5 1 】

“セット”又は“增幅”段階での動作の間に、感知増幅器はメモリセル 3 0 に格納されたビットデータを感知する。第 1 差動出力端子 Out + はハイインピーダンス (high impedance) 出力端子 Out + である。ハイインピーダンス出力端子の電圧レベルは参照ライン電流 I<sub>R E F</sub>、 3 4 0 及びビットライン電流 I<sub>B I T</sub>、 3 3 5 の間のデルタ平均電流 3 7 5 に応答して変化する。即ち、参照ライン電流 I<sub>R E F</sub>、 3 4 0 及びビットライン電流 I<sub>B I T</sub>、 3 3 5 の大きさ (magnitude) に差異があり得る。このような差異はデルタ平均電流 3 7 5 であると称され得る。デルタ平均電流 3 7 5 はメモリセル 3 0 に格納されたビット値にしたがって、ハイ - インピーダンス出力端子 Out + の電圧レベルが同一の方向に又は異なる方向に変化 (swinging) するようになる。電圧変化 (voltage swing) は“セット”又は“增幅”段階での負 (negative) の抵抗支援に依存しなく、これはトランジスター P 3、 P 4 又はラッチ素子によって提供される。出力電圧の装着時間 (settling time)、ノイズ耐性 (noise immunity)、信号平均 (signal averaging) 等は少なくとも出力端子 3 7 0、 3 7 5 の寄生キャパシタンス C<sub>B I T</sub>、 3 1 5 の寄生キャパシタンス及び / 又は C<sub>R E F</sub>、 3 2 0 の寄生キャパシタンスの少なくとも一部分に依存する。寄生キャパシタンスが接地されなければ、出力電圧の変化はスパイク及び他のノイズ干渉 (noise interference) に敏感であり得る。さらに、電流及び信号平均 (averaging) は回路のノイズ耐性特性を強化することができる。出力電圧の正確性はメモリセル 3 0 に格納されたビット値に依存し、これは R<sub>B I T</sub>、 1 0 が R<sub>H</sub> 又は R<sub>L</sub> であるか否かである R<sub>B I T</sub>、 1 0 の抵抗に依存する。

20

### 【 0 0 5 2 】

ハイインピーダンス出力端子の電圧変化 (voltage swing) はデルタ平均電流 3 7 5 とハイインピーダンス出力端子 Out + と連関された寄生キャパシタンスの乗算によってもたらすことができる。トランジスター P 1 は出力端子 Out + のインピーダンスを増加させることができ、これはより著しい電圧変化をもたらすことができる。参照ライン R L とビットライン B L が直列に配列されているので、ビットライン B L は少なくとも一部の参照ライン電流 I<sub>R E F</sub>、 3 4 0 を再使用し、したがって、少なくとも“セット”又は“增幅”段階の動作の間に消耗される電流量を減少させる。この段階での総電流消耗量の減少は半分に至ることができる（例えば、このような電流再使用回路及び特性を有しない感知増幅器に比べて 50 % の電流消耗量が減少する）。さらに具体的に、仮に I<sub>R E F</sub>、 3 4 0 が I<sub>B I T</sub>、 3 3 5 より大きければ、ハイ - インピーダンス出力端子 Out + の電圧レベルは高い電圧に変化 (swinging) し、これはメモリセル 3 0 に論理値 “1” が格納されていることを示す。反対に、I<sub>R E F</sub>、 3 4 0 が I<sub>B I T</sub>、 3 3 5 より小さければ、ハイ - インピーダンス出力端子 Out + の電圧レベルは低い電圧に変化し、これはメモリセル 3 0 に論理値 “0” が格納されていることを示す。

40

### 【 0 0 5 3 】

少なくとも感知増幅器の“セット”又は“增幅”段階の間に、R<sub>B I T</sub>、 1 0 = R<sub>L</sub>（低い抵抗）である時、トランジスター N 1 はトライオード領域 (triode region) モードに動作し、反面トランジスター P 1 は飽和領域 (saturation re

50

g i o n ) モードに動作する。反対に、少なくとも感知増幅器の“セット”又は“増幅”段階の間に、 $R_{B I T}$ 、 $10 = R_H$ （高い抵抗）である時、トランジスターN 1は飽和領域(saturation region)モードに動作し、反面トランジスターP 1はトリオード領域(triode region)モードに動作する。トランジスターN 1はメモリセル3 0に格納されたデータを読み出すか、或いは読み出し動作を試圖する時発生できるメモリセル3 0のデータ変化(又はdestructive write)の可能性を減らすために使用され得る。このような読み出し動作でのデータの変化は読み出ディスクターブ(read disturb)と称され、読み出ディスクターブの頻度はトランジスターN 1の存在によって減少され得る。

## 【0054】

10

さらに具体的に、トランジスターN 1のドレーン端子3 5 0は直接第1差動出力端子Out +及びトランジスターP 1のドレーン端子3 6 0に連結される。トランジスターN 1のソース端子3 5 2はメモリセル3 0と連関されたビットラインBLに連結される。トランジスターP 1のソース端子3 5 7は参照抵抗 $R_{REF}$ 、5 0と連関された参照ラインRLに連結される。トランジスターN 1は望ましくはNMOSトランジスターであり得る。トランジスターP 1は望ましくはPMOSトランジスターであり得る。但し、これは例示的なことであり、他のタイプのMOSトランジスターが本発明に使用され得ることが理解できる。

## 【0055】

20

点線で図示された接地状態である寄生キャパシター3 7 0、3 7 5はビットライン及び参照電流の平均(averaging)に寄与する。結果的に、ノイズ耐性(noise immunity)が強化され、ノイズスパイク(spikes of noise)、ノイズのスイッチング(switching noise)、又は他の電磁気妨害要素が感知増幅器1 6 0によって遂行されるか、或いは出力された信号に対する妨害(disruption)をもたらす可能性が減る。高い信号パワー、改善されたノイズ耐性、改善された論理出力信号の信頼度は本実施形態の特性からの結果の長所のうちの一部である。

## 【0056】

“進行”又は“ラッチ”段階の動作の間に、感知増幅器は以下で説明されるように、感知増幅器1 6 0の第1又は第2差動出力端子(Out +、Out -)の論理値“0”又は論理値“1”をラッチする。感知増幅器1 6 0は交差連結されたラッチ回路を含み、ラッチ回路はラッチトランジスターP 3、P 4、N 3、N 4を含む。交差連結されたラッチ回路は第1及び第2差動出力端子(Out +、Out -)に連結される。

30

## 【0057】

交差連結されたラッチ回路は選択的に第1ラッチイネーブルトランジスターP 2を含む。例示的に、第1ラッチイネーブルトランジスターP 2は複数の感知増幅器(例えば、図2の1 6 0、1 6 5)各々に対してグローバルに適用され得る。即ち、1つの第1グローバルラッチイネーブルトランジスターP 2がメモリ装置1 5 0の感知増幅器のラッチ回路各々をイネーブル(enable)するのに使用され得る。

## 【0058】

40

交差連結されたラッチ回路は選択的に第2ラッチイネーブルトランジスターN 2を含む。例示的に、第2ラッチイネーブルトランジスターN 2は複数の感知増幅器(例えば、図2の1 6 0、1 6 5)各々に対してグローバルに適用され得る。即ち、1つの第2グローバルラッチイネーブルトランジスターN 2は第1ラッチイネーブルトランジスターP 2と共にメモリ装置1 5 0の感知増幅器のラッチ回路各々をイネーブル(enable)するのに使用され得る。

## 【0059】

ラッチイネーブルトランジスターP 2、N 2は各々ラッチコントロール信号S 2 b及びラッチコントロール信号S 2 aに応答して感知増幅器1 6 0の“進行”又は“ラッチ”段階を活性化する。一実施形態において、ラッチコントロール信号S 2 b、S 2 aは図2の

50

コントロールロジック 190 によって生成され得る。第 1 ラッチイネーブルトランジスター P2 は正のパワー供給電圧ノード VDD に連結される。第 2 ラッチイネーブルトランジスター N2 は接地電圧ノード GND に連結される。

#### 【 0060 】

ラッチ回路は第 1 ラッチイネーブルトランジスター P2 及び第 1 差動出力端子 Out+ に連結された第 1 ラッチトランジスター P3 を含む。第 2 ラッチトランジスター P4 は第 1 ラッチイネーブルトランジスター P2 及び第 2 差動出力端子 Out- に連結される。第 3 ラッチトランジスター N3 は第 2 ラッチイネーブルトランジスター N2 及び第 1 差動出力端子 Out+ に連結される。第 4 ラッチトランジスター N4 は第 2 ラッチイネーブルトランジスター N2 及び第 2 差動出力端子 Out- に連結される。

10

#### 【 0061 】

“進行”又は“ラッチ”段階の動作の間にラッチイネーブルトランジスター P2、N2 は各々ラッチコントロール信号 S2b、S2a に応答してターンオンされ、これによってラッチトランジスターは正のフィードバック (positive feedback) に基づいて、各々抵抗性メモリセル 30 に格納されたビット値にしたがう第 1 又は第 2 差動出力端子 Out+、Out- の論理値“0”又は論理値“1”をラッチする。

#### 【 0062 】

さらに具体的に、第 1 ラッチトランジスター P3 のソース端子は第 1 ラッチイネーブルトランジスター P2 のソース端子に直接連結される。これと類似に、第 2 ラッチトランジスター P4 のソース端子は第 1 ラッチイネーブルトランジスター P2 のソース端子に直接連結される。また、第 3 ラッチトランジスター N3 のソース端子は第 2 ラッチイネーブルトランジスター N2 のドレーン端子に直接連結される。これと類似に、第 4 ラッチトランジスター N4 のソース端子は第 2 ラッチイネーブルトランジスター P2 のドレーン端子に直接連結される。第 1 ラッチトランジスター P3 のゲート端子は第 2 差動出力端子 Out- に連結される。第 2 ラッチトランジスター P4 のゲート端子は第 1 差動出力端子 Out+ に連結される。第 3 ラッチトランジスター N3 のゲート端子は第 2 差動出力端子 Out- に連結される。第 4 ラッチトランジスター N4 のゲート端子は第 1 差動出力端子 Out+ に連結される。

20

#### 【 0063 】

第 1 及び第 3 ラッチトランジスター P3、N3 の各ドレーン端子は第 1 差動出力端子 Out+ に連結される。第 2 及び第 4 ラッチトランジスター P4、N4 の各ドレーン端子は第 2 差動出力端子 Out- に連結される。第 1 ラッチイネーブルトランジスター P2 は望ましくエンハンスマントモード PMOS ローディングタイプトランジスター (enhancement mode PMOS loading transistor)、デジタルモードオン／オフタイプトランジスター (digital mode on/off type transistor) であり得る。第 2 ラッチイネーブルトランジスター N2 は望ましくエンハンスマントモード NMOS ローディングタイプトランジスター (enhancement mode PMOS loading transistor)、デジタルモードオン／オフタイプトランジスター (digital mode on/off type transistor) であり得る。

30

#### 【 0064 】

第 1 及び第 2 ラッチトランジスター P3、P4 は望ましく各々 PMOS タイプトランジスターであり得る。第 3 及び第 4 ラッチトランジスター N3、N4 は望ましく各々 NMOS タイプトランジスターであり得る。但し、これは例示的なことであり、他の MOS トランジスターが本発明にしたがって使用され得ることが理解できる。

40

#### 【 0065 】

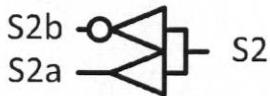

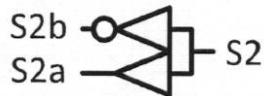

図 4B は図 4A の感知増幅器に連結されて使用されるコントロール信号 S2b、S2a を生成するコントロール信号回路の一例を示す図面である。コントロール信号回路はコントロール信号 S2 を受信し、コントロール信号 S2 を利用してコントロール信号 S2b、S2a を生成することができる。コントロール信号 S2b はコントロール信号 S2 に比例

50

して反転された信号である。コントロール信号 S<sub>2a</sub> はコントロール信号 S<sub>2</sub> に対応する。図 4B のコントロール信号回路は図 2 に図示されたメモリ装置 105 のコントロールロジック 190 に包含され得る。

#### 【0066】

図 5 乃至図 7 は図 4A の感知增幅器 160 の各段階の動作の動作を示す等価回路である。図 8 は本発明の一実施形態にしたがってメモリセル抵抗 R<sub>BIT</sub> が “H” 値である R<sub>H</sub> に以前に設定されている時、図 4A の感知增幅器 160 の互に異なる段階での波形 (waveform) の一例を示す図面である。図 9 は本発明の一実施形態にしたがってメモリセル抵抗 R<sub>BIT</sub> が “L” 値である R<sub>L</sub> に以前に設定されている時、図 4A の感知增幅器 160 の互に異なる段階での波形 (waveform) の一例を示す図面である。詳細な説明は図 5 乃至図 9 を参照して説明される。10

#### 【0067】

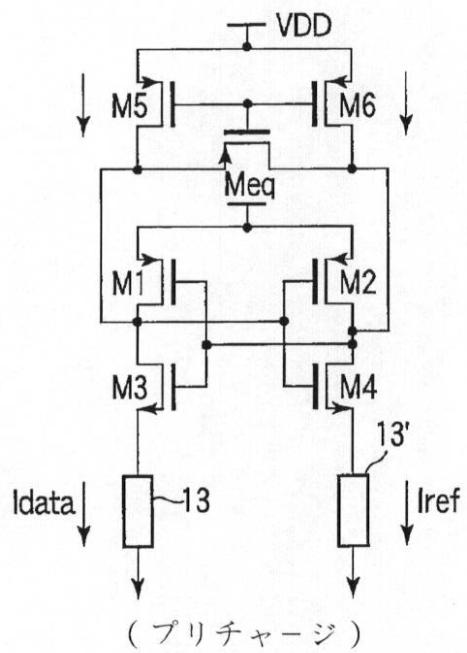

図 5 は “準備” 又は “プリ - チャージ” 段階 405 の動作と関連された図 4A の感知增幅器 160 の等価回路の一例を示す図面である。

#### 【0068】

スイッチ 305、310 は閉じられていると仮定され、これによって感知增幅器 160 がメモリセル 30 及び参照抵抗 R<sub>REF</sub>、50 に連結される。感知增幅器 160 の “準備” 又は “プリ - チャージ” 段階で、ワードライン WL はハイ状態 “H” に遷移され、プリ - チャージコントロール信号 S<sub>1</sub> はロー状態 “L” であり、ラッチイネーブル信号 S<sub>2</sub> はロー状態 “L” である。ラッチイネーブル信号 S<sub>2</sub> がロー状態 “L” であるので、ラッチイネーブルコントロール信号 S<sub>2b</sub> は “H” 状態であり、ラッチイネーブルコントロール信号 S<sub>2a</sub> は “L” 状態である。20

#### 【0069】

したがって、第 1 プリ - チャージトランジスター P<sub>5</sub> 及び第 2 プリ - チャージトランジスター P<sub>6</sub> はプリ - チャージコントロール信号 S<sub>1</sub> に応答して完全にターンオンされ、内部パワー供給電圧ノード V<sub>MM</sub> に対する導電経路を形成する。したがって、プリ - チャージトランジスター P<sub>5</sub> はビットライン電流 I<sub>BIT</sub>、335 の少なくとも一部を生成し、ビットライン電流 I<sub>BIT</sub>、335 はトランジスター N<sub>1</sub> を通じてメモリセル 30 と連関されたビットライン BL 及びビットラインキャパシター C<sub>BIT</sub>、315 及び第 1 差動出力端子 Out+ と連関された寄生キャパシタンス 370 をプリチャージする。さらに、プリ - チャージトランジスター P<sub>5</sub> は参照ライン電流 I<sub>REF</sub>、340 の少なくとも一部を生成し、参照ライン電流 I<sub>REF</sub>、340 はトランジスター P<sub>1</sub> を通じて少なくとも参照ライン RL 及び参照ラインキャパシター C<sub>REF</sub>、320 をプリチャージする。プリ - チャージトランジスター P<sub>6</sub> は少なくとも第 2 差動出力端子 Out- と連関された寄生キャパシタンス 375 をプリチャージする。30

#### 【0070】

トランジスター P<sub>1</sub>、N<sub>1</sub> はゲート電圧 VR、VB に応答して各々ターンオンされる。しかし、ラッチ回路はラッチイネーブルトランジスター P<sub>2</sub>、N<sub>2</sub> がターンオフされ、他のラッチトランジスターはフローティング状態 (floating state) であるので、この段階では動作せず、したがって、図 5 の等価回路では省略された。したがって、プリ - チャージ電流はラッチ回路のいずれのトランジスターを通じて流れず、これによつて応答時間が改善される。40

#### 【0071】

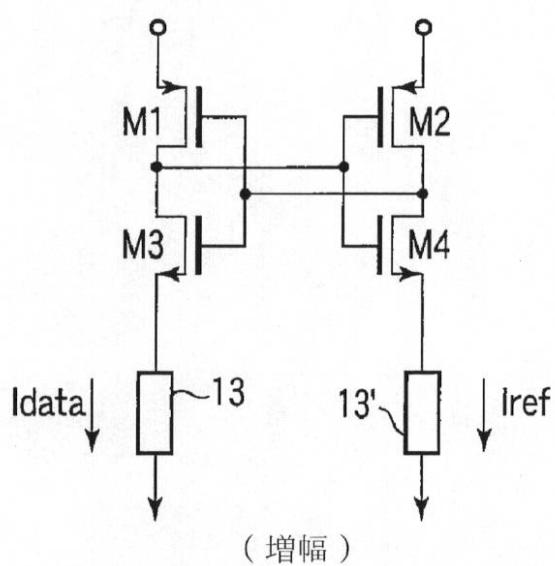

図 6 は “セット” 又は “増幅” 段階 505 の動作と連関された図 4A の感知增幅器 160 の等価回路の一例を示す図面である。スイッチ 305、310 は閉じられていると仮定され、したがって、感知增幅器 160 はメモリセル 30 及び参照抵抗 R<sub>REF</sub>、50 に連結される。感知增幅器 160 の “セット” 又は “増幅” 段階で、ワードライン WL は “H” 状態を維持し、プリ - チャージコントロール信号 S<sub>1</sub> は “H” 状態に遷移され、ラッチイネーブル信号 S<sub>2</sub> は “L” 状態を維持する。第 1 プリ - チャージトランジスター P<sub>5</sub> 及び第 2 プリ - チャージトランジスター P<sub>6</sub> はしたがって、各々プリ - チャージコントローラー

ル信号 S 1 に応答してターンオフされ、したがって、図 6 の等価回路に示したようにスイッチングがオープン (open) される。また、ラッチイネーブルトランジスター P 2、N 2 が相変わらず、この段階でもオフ状態であるので、ラッチトランジスターは動作しない。

#### 【 0 0 7 2 】

“セット”又は“增幅”段階 505 の間に、初期の差動出力端子 Out+、Out- の電圧レベルは VMM 又はこれと類似のレベルで同一である。以後、上述したように、参照ライン電流  $I_{REF}$ 、340 とビットライン電流  $I_{BIT}$ 、335 のデルタ平均電流 375 はメモリセル 30 に格納されたビット値にしたがって、ハイ - インピーダンス出力端子 Out+ の電圧レベルが同一の方向に又は異なる方向に変化 (swinging) するようになる。第 2 差動出力端子 Out- の電圧レベルはこの段階で寄生キャパシタンス 375 によって VMM 又はこれと類似なレベルを維持する。10

#### 【 0 0 7 3 】

仮に  $I_{REF}$  340 が  $I_{BIT}$  335 より大きければ、ハイ - インピーダンス出力端子 Out+ の電圧レベルは高くなるように変化し、これはメモリセル 30 も論理値 “1” が格納されていることを示す。反対に、仮に  $I_{REF}$  340 が  $I_{BIT}$  335 より小さければ、ハイ - インピーダンス出力端子 Out+ の電圧レベルは低くなるように変化し、これはメモリセル 30 に論理値 “0” が格納されていることを示す。“セット”又は“增幅”段階の最後には、出力端子 (Out+, Out-) の出力電圧レベルの間の差異は出力信号をラッチするのに十分であるように大きくなる。20

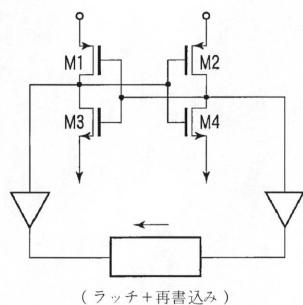

#### 【 0 0 7 4 】

図 7 は“進行”又は“ラッチ”段階 605 と連関された図 4 A の感知增幅器の等価回路の一例を示す図面である。スイッチ 305、310 は閉じられていると仮定され、したがって、感知增幅器 160 がメモリセル 30 及び参照抵抗  $R_{REF}$ 、50 に連結される。感知增幅器 160 の“進行”又は“ラッチ”段階で、ワードライン WL は “L” 状態に遷移し、プリ - チャージコントロール信号 S 1 は “H” 状態を維持し、ラッチイネーブル信号 S 2 は “H” 状態に遷移する。ラッチイネーブル信号 S 2 が “H” 状態に遷移するので、ラッチイネーブルコントロール信号 S 2 b は “L” 状態に遷移し、ラッチイネーブルコントロール信号 S 2 a は “H” 状態に遷移する。第 1 プリ - チャージトランジスター P 5 及び第 2 プリ - チャージトランジスター P 6 はターンオフ状態を維持し、したがって、図 7 に示したようにオープンされたスイッチングとして表現される。ラッチイネーブルトランジスター P 2、N 2 及びラッチトランジスター P 3、P 4、N 3、N 4 は各々ラッチイネーブルコントロール信号 S 2 b、S 2 a に応答して動作することができ、したがって、ラッチ回路は出力信号をラッチすることができる。30

#### 【 0 0 7 5 】

全体ラッチ回路（例えば、ラッチトランジスターである P 3、P 4、N 3、N 4 で構成される）は差動出力端子 Out+ の電圧レベル及び VMM である差動出力端子 Out- の電圧レベルの差異に基づいて差動出力端子で論理値 “0” 又は論理値 “1” をラッチするのに使用される。このような電圧レベルが差異及びラッチの正のフィードバックに基づいて、出力値がラッチすることができる。40

#### 【 0 0 7 6 】

メモリセル 30 に格納されたデータが論理値 “0” であるか又は論理値 “1” であるかにしたがって、ラッチ回路が異なりに動作することができる事が理解できる。例えば、仮にメモリセルが  $R_L$  状態（論理値 “0”）であれば、 $I_{BIT}$  335 は  $I_{REF}$  340 に比べて大きくて、これは出力端子 Out+ の電圧レベルが低く変化するようになる。したがって、このような場合に、正のフィードバックに基づいてラッチトランジスター P 4 はターンオン、ラッチトランジスター P 3 はターンオフ、ラッチトランジスター N 4 はターンオフ、ラッチトランジスター N 3 はターンオンされ、これによって、差動出力端子 Out+ で論理値 “0” がラッチされる。反対に、仮にメモリセルが  $R_H$  状態（論理値 “1”）であれば、 $I_{BIT}$  335 は  $I_{REF}$  340 に比べて小さく、これは出力端子 Out- 50

<sup>+</sup>の電圧レベルが高くなるように変化するようにする。したがって、このような場合に、正のフィードバックに基づいてラッチトランジスターP 4はターンオフ、ラッチトランジスターP 3はターンオン、ラッチトランジスターN 4はターンオン、ラッチトランジスターN 3はターンオフされ、これによって差動出力端子Out<sup>+</sup>で論理値“1”がラッチされる。

#### 【0077】

図10は本発明にしたがう感知增幅器160を使用する抵抗性メモリ30のデータ感知動作を示す順序図900である。902段階で、“準備”又は“プリ・チャージ”段階に進入するか否かに対する判断が遂行される。仮にはい(YES)であれば、先に説明されたビットラインと参照ラインキャパシターがプリ・チャージされる904段階が進行される。そうでなく、仮にいいえ(NO)であれば、再び開始段階に戻る。

10

#### 【0078】

906段階で、“セット”又は“増幅”段階505へ進入するか否かに対する判断が遂行される。仮にYESであれば、908段階が進行され、“セット”又は“増幅”段階の間に、ビットライン電流と参照ライン電流との間のデルタ平均電流に応答して出力端子Out<sup>+</sup>の電圧レベルと同一の方向又は異なる方向に変化するようになる。また、先に説明されたように912段階で、電流再使用に基づいてより少ない電流が消耗され、これによつて感知增幅器の電流消耗特性が改善される。反対に、仮にいいえ(NO)であれば、判断及び感知增幅器動作に戻つて、906段階が再び遂行される。

20

#### 【0079】

914段階で、“進行”又は“ラッチ”段階の動作に进入するか否かに対する判断が遂行される。仮にはい(YES)であれば、916段階へ進行し、先に説明されたように、ラッチ回路の正のフィードバックを利用して論理値“0”又は論理値“1”がラッチされる。反対に、仮にいいえ(NO)であれば、914段階に戻るか、或いは他の判断及び感知增幅器動作が遂行される。

20

#### 【0080】

図11Aは本発明の他の技術的思想の実施形態による電流ミラー(current mirror、960)と連関された図2の感知增幅器160、165の一実施形態を示す図面である。先に説明されたように、感知增幅回路(150、図2)は複数の感知增幅器を包含することができる。各感知增幅器は少なくとも1つのメモリプロック(120、130、図2)の対応するビットラインと対応するメモリセルと連関され得る。電流ミラーリー回路960は複数の感知增幅器(例えば、160、165)に連結される。電流ミラーリー回路960は少なくとも各感知增幅器の“セット”又は“増幅”段階の間に、参照ライン電流I<sub>REF</sub>340を複写(mirror)する。各感知增幅器のビットラインBLは複写された参照ライン電流の少なくとも一部を再使用する。

30

#### 【0081】

複数の感知增幅器は先に説明されたように各々対応するビットライン及び対応するメモリセルに連結されたハイ・インピーダンス出力端子を包含することができる。対応するビットラインはビットライン電流I<sub>BIT</sub>335を導電(conduct)する。ハイ・インピーダンス出力端子の電圧レベルは複写された参照ライン電流とビットライン電流との間のデルタ平均電流375に応答して変化(swing)する。

40

#### 【0082】

感知增幅器(例えば、160、165)の各々は先に詳細に説明されたようにラッチ回路(例えば、P3、P4、N3、N4で構成される)を含む。メモリ装置105は第1グローバルラッチイネーブルトランジスターP2及び第2グローバルラッチイネーブルトランジスターN2をさらに含み、第1グローバルラッチイネーブルトランジスターP2及び第2グローバルラッチイネーブルトランジスターN2は各々ラッチコントロール信号S2b、S2aに応答して各感知增幅器のラッチ段階を活性化する。

#### 【0083】

電流ミラーリー回路960は電流ミラートランジスターP0、N0を含む。トランジスター

P<sub>1</sub>のゲートは電流ミラートランジスターP<sub>0</sub>のゲートに連結される。電圧ソース935はゲート電圧V<sub>R</sub>を電流ミラートランジスターN<sub>0</sub>のゲートへ提供する。電流ミラートランジスターは複数の感知增幅器各々にI<sub>R\_E\_F</sub>340を複写することができる。

#### 【0084】

電流ミラー回路960は参照メモリセル70と連関された参照ラインR<sub>L</sub>と連結される。電流ミラー回路960は各感知增幅器のプリ-チャージ段階の間に、参照メモリセル70と連関された参照ラインR<sub>L</sub>をプリ-チャージする。電流ミラー回路960は少なくとも各感知增幅器の増幅段階の間に、参照ライン電流I<sub>R\_E\_F</sub>、340を複写する。また、電流ミラー回路960は参照メモリセル70と連関された参照ラインR<sub>L</sub>をプリチャージする。参照メモリセル70が選択トランジスター60と参照抵抗R<sub>R\_E\_F</sub>、50を包含するので、メモリセル30とさらに改善されたマッチング(matching)が可能であり、これによって、マッチング感度(matching sensitivity)が改善される。結果的に、I<sub>R\_E\_F</sub>とI<sub>B\_I\_T</sub>との間の差異は主にR<sub>R\_E\_F</sub>とR<sub>B\_I\_T</sub>との間の差によることである。他の要素と他の動作モードは先に説明されたことと類似であり、したがって、詳細な説明は省略される。10

#### 【0085】

図11Bはコントロール信号回路の一例として、図4Bと同一であり、図11Aの回路のためのラッティネーブルコントロール信号を生成する。したがって、図11Bの詳細な説明は省略される。

#### 【0086】

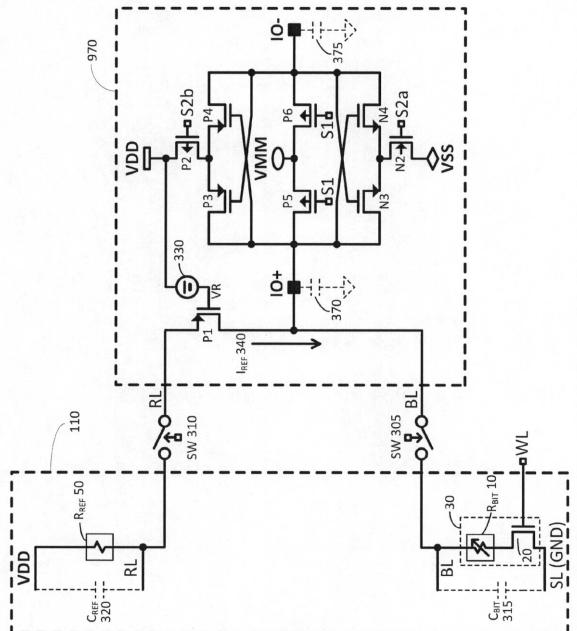

図12Aは本発明の実施形態による読み出し／再書き込み(read/re-write)機能を含む感知增幅器970の一例を示す図面である。感知增幅器970は図2及び図4Aの感知增幅器160と類似であり、したがって、同一であるか、或いは類似な要素に対する説明は簡略説明をするために省略される。図13Aは本発明の実施形態によるメモリセル抵抗が以前にハイ(high)に設定されている時、図12Aの感知增幅器の互に異なる段階と連関された波形図を例示的に示す図面である。図13Bは本発明の実施形態によるメモリセル抵抗が以前にロー(low)に設定されている時、図12Aの感知增幅器の互に異なる段階と連関された波形図を例示的に示す図面である。図12A、図13A、図13Bを参照して説明される。20

#### 【0087】

先に説明された感知增幅器と比較して幾つかの構造的差異点がある。具体的に、感知增幅器970はトランジスターN<sub>1</sub>を包含しない。また、接地電圧ノードGNDの代わりに、負(negative)のパワー供給電圧ノードVSSがラッティネーブルトランジスターN<sub>2</sub>に連結される。例えば、もし正のパワー供給電圧ノードVDDが1.2Vの電圧レベルを供給したら、負のパワー供給電圧ノードVSSは-1.2Vの電圧レベルを供給することができる。さらに、入力及び出力端子は入出力(IO)端子(IO+、IO-)に結合された。30

#### 【0088】

動作特性と関連して、動作の多様な段階の動作は追加された読み出し／再書き込み機能にもかかわらず、先に説明されたことと類似である。差異は増幅段階の間のIO+端子の電圧変化(swing)がデルタ平均電流ではない総ビット抵抗によって増加された参照電流I<sub>R\_E\_F</sub>340(例えば、R<sub>B\_I\_T</sub>10によって増加されたI<sub>R\_E\_F</sub>340によって直接的に決定される。トランジスターN<sub>1</sub>のようなビットライン上のアクティブ装置の不存在によって、IO+端子とメモリセル10の間に直接経路(direct path)が存在する。この実施形態で、寄生キャパシタンス370はビットキャパシタンスC<sub>B\_I\_T</sub>、315と併合されて、共にIO+端子で電圧レベルの定着時間(settling time)を増加させる。これによって、スパイク又は他の可能であるノイズ妨害を減少させる(この時、ビットキャパシタンスC<sub>B\_I\_T</sub>315は例えば、寄生キャパシタンス370に比べて10倍以上であり得る)。即ち、IO+端子の電圧レベルは本質的に参照電流I<sub>R\_E\_F</sub>340とRC回路によって決定される。40

## 【0089】

一実施形態として、仮に  $R_{BIT} = R_L$  であれば、IO+端子は増幅段階の間にVMMより低い値に低くなり、ラッチ段階の間にVSS電圧レベルに低くなつて、メモリ抵抗  $R_{BIT}$  10に  $R_L$  の値を明確に再書き込みする動作を遂行する。反対に、仮に  $R_{BIT} = R_H$  であれば、IO+端子は増幅段階の間に、VMMより高い値に高くなり、ラッチ段階の間にVDD電圧レベルに至つて、メモリ抵抗  $R_{BIT}$  10に  $R_H$  の値を明確に再書き込みする動作を遂行する。再書き込み動作が無ければ、 $R_{BIT}$  10の値が意図せないように変更される可能性がある。このような障害 (disturbance) を避けるために、すべての読み出し動作の後に再書き込み動作を遂行することによって、 $R_{BIT}$  に格納された値が正確な値を維持している可能性を高くすることができる。

10

## 【0090】

図12Bはコントロール信号回路の一例として、図4Bと同一であり、図12Aの回路のためのラッチイネーブルコントロール信号を生成する。したがつて、図12Bの詳細な説明は省略される。

## 【0091】

図14Aは本発明の他の実施形態によるエッジ-参照セル (edge-reference cell) 配列又はパターン (例えば、1405) でのメモリセルアレイ (例えば、110) 及び連関されたメモリブロック (例えば、1415、1420) のレイアウトの実施形態を示す図面である。レジェンド1400は配列に使用されるシンボルの説明を提供する。図14Aを参照すれば、共有感知増幅器1435はメモリブロック1415、1420の中でいずれか1つによつて又は2つのメモリブロック1415、1420全てによつて使用される。参照メモリセル70は共有感知増幅器1435に隣接するか、或いは付近に配置され得る。所定の参照メモリセル70はバンク1415及び/又はバンク1420の複数のメモリビットセル30のための参照を提供することができる。

20

## 【0092】

メモリバンク1415からの参照メモリセル70及びメモリバンク1420からの参照メモリセル70は対応する参照ラインを経て共有感知増幅器 (例えば、複数の感知増幅器1435の中でいずれか1つの共有感知増幅器) に連結され得る。即ち、1つの共有感知増幅器は互に異なるバンクからの2又はその以上の参照ライン及び/又は参照メモリセルに連結され得る。これと類似に、メモリバンク1415からのメモリビットセル30及びメモリバンク1420からのメモリビットセル30は対応するビットラインを経て共有感知増幅器 (例えば、複数の感知増幅器1435の中でいずれか1つ) に連結され得る。即ち、1つの共有感知増幅器は互に異なるバンクからの2又はその以上のビットライン及び/又はメモリビットセルに連結され得る。

30

## 【0093】

図14Bは本発明の他の実施形態によるビット-参照セル (bit-reference cell) 配列又はパターン (例えば、1410) でのメモリセルアレイ (例えば、110) 及び連関されたメモリブロック (例えば、1425、1430) のレイアウトの実施形態を示す図面である。図14Aと同様に、レジェンド1400は配列に使用されるシンボルの説明を提供する。図14Bを参照すれば、共有感知増幅器1440はメモリブロック1425、1430の中でいずれか1つによつて又は2つのメモリブロック1425、1430の全てによつて使用される。このレイアウトにおいて、メモリビットセル30は参照メモリセル70に隣接するように配置され得る。

40

## 【0094】

1つのバンク内の1つの共通参照ラインは複数の参照メモリセル70を1つのミラーバイアス回路995及び/又は複数の感知増幅器に連結させることができる。バンク1425の1つの参照メモリセルは第1共通参照ラインを通じてミラーバイアス回路995に連結され得る。バンク1430の1つの参照メモリセルは第2共通参照ラインを通じて同一のミラーバイアス回路995に連結され得る。第1バンク1425の1つのメモリセルは1つの与えられた共有感知増幅器に連結され、第2バンク1430の他のメモリセルは

50

前記与えられた共有感知増幅器に連結され得る。ミラーバイアス回路 995 は前記共有感知増幅器(複数の)に隣接するように配置され得る。

#### 【0095】

メモリバンク 1430 からの参照メモリセル 70 及びメモリバンク 1425 からのメモリビットセル 30 は共通参照ライン及び個別ビットラインを経て各々 1 つの共有感知増幅器(例えば、複数の感知増幅器 1440 の中でいずれか 1 つの共有感知増幅器)に連結され得る。即ち、1 つの共有感知増幅器は互に異なるバンクと連関された 1 つの共通参照ライン及び 1 つの個別ビットラインに連結される。これと類似に、共有感知増幅器は互に異なるバンクと連関された参照セル 70 及びメモリビットセル 30 に連結され得る。即ち、1 つの共有感知増幅器は互に異なるバンクからの参照セル及び/又はメモリビットセルに連結され得る。

10

#### 【0096】

上述した図 4 乃至図 14B を参照すれば、幾つかの実施形態において、ソースライン S<sub>Ls</sub> は接地 GND 電位に連結され、これは図 4 乃至図 14B で説明された回路図で特定された特徴である。しかし、これは例示的なこととして理解できる。例えば、幾つかの実施形態(例えば、図 4 乃至図 11B を参照して説明された実施形態の中でいずれか実施形態)において、ソースライン S<sub>Ls</sub> はパワー供給 VDD 電位に連結でき、レギュラー VDD 電位は接地 GND 電位に連結され得る。このような場合に、各 PMOS タイプトランジスターは NMOS タイプトランジスターに代替され得り、各 NMOS タイプトランジスターは PMOS タイプトランジスターに代替され得る。即ち、ソースライン S<sub>Ls</sub> が VDD 電位に連結される時、感知増幅器はアップサイド(upside)とダウンサイド(downside)の間でスワップ(swap)され、これは NMOS タイプトランジスターが PMOS トランジスターと代替され、PMOS タイプトランジスターが NMOS タイプトランジスターと代替されることを意味する。言い換れば、ソースラインが接地電圧に連結される時、感知増幅器は第 1 トランジスター特性を含み、ソースラインがパワー供給電圧に連結される時、感知増幅器は第 1 トランジスター特性に比べてスワップされた(swapped)第 2 トランジスター特性を含む。また、幾つかの実施形態において、例えば、図 12A 及び図 12B を参照すれば、ソースライン S<sub>Ls</sub> は接地 GND 電位に連結された状態を維持することができ、負のパワー供給電圧ノード VSS はパワー供給電圧ノード VDD と代替することができ、レギュラー VDD 電位は接地 GND 電位に連結することができ、NMOS トランジスターと PMOS トランジスターは上で説明されたようにスワップ(swap)されることがきることが理解できる。

20

#### 【0097】

図 15 は本発明の実施形態に他の抵抗性メモリ装置の多様な適用例を示す図面である。図 15 を参照すれば、メモリシステム 1500 は格納装置 1525 及びホスト 1520 を含む。格納装置 1525 は抵抗性メモリ 1510 及びメモリコントローラ 1505 を含む。

30

#### 【0098】

格納装置 1525 はメモリカード(例えば、SD、MMC 等)のような格納媒体又は携帯可能である格納媒体(例えば、USB メモリ等)を包含することができる。格納装置 1525 はホスト 1520 に連結され得る。格納装置 1525 はホストインターフェイスを通じてホスト 1520 からデータを送信するか、或いはホスト 1520 からデータを受信できる。格納装置 1525 は初期動作を遂行するためにホスト 1520 によってパワーが供給される。抵抗性メモリ 1510 は本発明の実施形態による感知増幅回路 1515 を包含することができる。

40

#### 【0099】

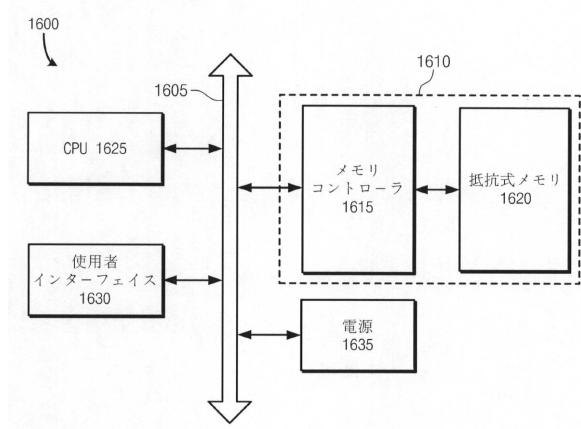

図 16 は本発明の実施形態による抵抗性メモリ装置を含むコンピューティングシステム 1600 に関する図面である。図 16 を参照すれば、コンピューティングシステム 1600 はメモリシステム 1610、パワー供給器 1635、中央処理装置(CPU、1625)、使用者インターフェイス 1630 を含む。メモリシステム 1610 は抵抗性メモリ 1

50

620とメモリコントローラ1615を含む。中央処理装置1625はシステムバス1605に電気的に連結される。

#### 【0100】

抵抗性メモリ1620は本発明の実施形態による感知增幅回路を含む。抵抗性メモリ1620はメモリコントローラ1615を通じてデータを格納する。データは使用者インターフェイス1630から受信されるか、或いは中央処理装置1625によって処理され得る。メモリシステム1600は半導体ディスク装置又はソリッドステートディスク(SSD)として使用され得る。

#### 【0101】

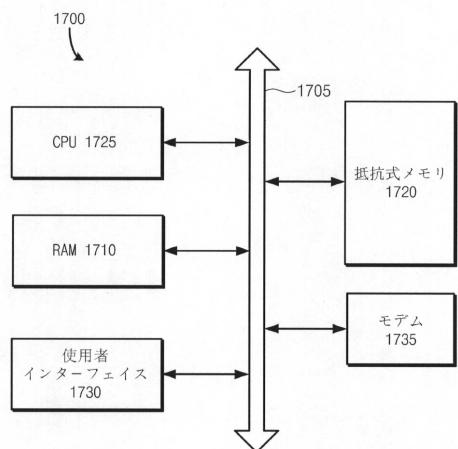

図17は本発明の実施形態による抵抗性メモリを含むコンピューティングシステム1700を示す図面である。図17を参照すれば、コンピューティングシステム1700は抵抗性メモリ装置1720、中央処理装置1725、RAM1710、使用者インターフェイス1730、そしてベースバンドチップセット(baseband chipset)のようなモデム1735を含み、各構成要素は電気的にシステムバス1705に連結される。抵抗性メモリ1720は上述したように本発明にしたがう感知增幅回路を包含することができる。

#### 【0102】

仮にコンピューティングシステム1700がモバイル装置であれば、コンピューティングシステム1700へ電源を供給するバッテリー(図示せず)をさらに包含できる。たとえば図17には図示しないが、コンピューティングシステム1700はアプリケーションチップセット、カーメライメージプロセッサー(CIS)、モバイルDRAM(mobile DRAM)等をさらに包含できる。

#### 【0103】

本発明の実施形態による抵抗性メモリ装置はストレージクラスメモリ(storage class memory、SCM)として使用され得る。“ストレージクラスメモリ”は不揮発性特性とランダム・アクセス特定を全て提供するメモリを指称する。

#### 【0104】

先に説明された抵抗性メモリ(ReRAM)のみでなくPRAM、FeRAM、MRAM等もストレージクラスメモリとして使用され得る。フラッシュメモリの代わりに、ストレージクラスメモリはデータ格納メモリとして使用され得る。さらに、同期式DRAM(synchronous DRAM)の代わりに、ストレージクラスメモリはデータ格納メモリとして使用され得る。さらに、1つのストレージクラスメモリがフラッシュメモリ及び同期式DRAMを代替して使用され得る。

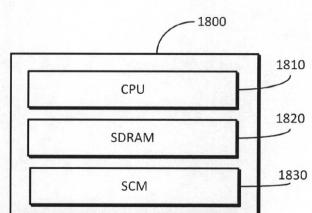

#### 【0105】

図18はフラッシュメモリを代替する抵抗性メモリを使用したストレージクラスメモリを含むメモリシステムの本発明にしたがう一実施形態を示す図面である。図18を参照すれば、メモリシステム1800は中央処理装置1810、同期式DRAM(SDRAM、1820)、ストレージクラスメモリ1830を含む。ストレージクラスメモリ1830はフラッシュメモリの代わりにデータ格納メモリに使用される抵抗性メモリである。

#### 【0106】

ストレージクラスメモリ1830はフラッシュメモリに比べて速い速度でデータにアクセスすることができる。例えば、4GHzの周波数に動作する中央処理装置1810を使用するPCにおいて、ストレージクラスメモリ1830タイプの抵抗性メモリはフラッシュメモリより速いアクセス速度を提供する。したがって、ストレージクラスメモリ1830を含むメモリシステム1800はフラッシュメモリを含むメモリシステムに比べて相対的に速い速度でアクセスすることができる。

#### 【0107】

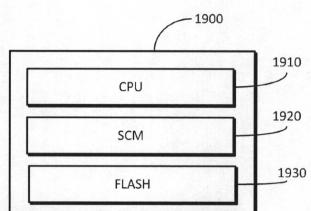

図19は同期式DRAMを代替する抵抗性メモリを使用したストレージクラスメモリを含むメモリシステムの本発明にしたがう一実施形態を示す図面である。図19を参照すれば、メモリシステム1900は中央処理装置1910、ストレージクラスメモリ1920

10

20

30

40

50

、フラッシュメモリ 1930 を含む。ストレージクラスメモリ 1920 は同期式 D R A M ( S D R A M ) の代わりにメーンメモリとして使用され得る。

#### 【 0 1 0 8 】

ストレージクラスメモリ 1920 によって消費されるパワーは同期式 D R A M によって消費されるパワーより小さい。メーンメモリはコンピューティングシステムによって消費されるパワーの 40 % をチャージすることができる。このような理由で、メーンメモリのパワー消費を減らすための技術が発展してきた。D R A M と比較して、クラスメモリ 1920 は平均的に 53 % の直接的なエネルギー消費の減少と 73 % のパワー漏洩によるエネルギー消費の減少効果を有する。したがって、ストレージクラスメモリ 1920 を含むメモリシステム 1900 は同期式 D R A M を含むメモリシステムに比べてパワー消費を減らし得る。10

#### 【 0 1 0 9 】

図 20 は同期式 D R A M 及びフラッシュメモリを代替して抵抗性メモリを使用するストレージクラスメモリを含むメモリシステムの本発明にしたがう一実施形態を示す図面である。図 20 を参照すれば、メモリシステム 2000 は中央処理装置 2010 及びストレージクラスメモリ 2020 を含む。ストレージクラスメモリ 2020 は同期式 D R A M の代わりにメーンメモリとして使用でき、フラッシュメモリの代わりにデータ格納メモリとして使用され得る。メモリシステム 2000 はデータアクセス速度、低い価格、空間使用において、長所を有する。20

#### 【 0 1 1 0 】

本発明の実施形態による抵抗性メモリは P o P ( P a c k a g e o n P a c k a g e ) 、 Ball grid arrays ( B G A s ) 、 Chip scale packages ( C S P s ) 、 Plastic Leaded Chip Carrier ( P L C C ) 、 Plastic Dual In - Line Package ( P D I 2 P ) 、 Die in Waffle Pack 、 Die in Wafer Form 、 Chip on Board ( C O B ) 、 Ceramic Dual In - Line Package ( C E R D I P ) 、 Plastic Metric Quad Flat Pack ( M Q F P ) 、 Thin Quad Flat Pack ( T Q F P ) 、 Small Outline ( S O I C ) 、 Shrink Small Outline Package ( S S O P ) 、 Thin Small Outline ( T S O P ) 、 System In Package ( S I P ) 、 Multi Chip Package ( M C P ) 、 Wafer - Level Fabricated Package ( W F P ) 、 Wafer - Level Processed Stack Package ( W S P ) 等のようなパッケージから選択された少なくとも 1 つのパッケージによってパッケージ化されることができる。30

#### 【 0 1 1 1 】

本発明の実施形態による抵抗性メモリ装置は多様な製品に適用され得る。本発明の実施形態による抵抗性メモリ装置は例えば、メモリカード、 U S B メモリ、ソリッドステートディスク ( S S D ) 等のみでなく、個人用コンピューター、デジタルカメラ、カムコーダー、携帯電話、 M P 3 プレーヤー、 P M P 、 P S P 、 P D A 等のような電子機器に適用され得る。40

#### 【 0 1 1 2 】

前記説明された実施形態は低いパワー供給電圧を利用して感知增幅器を提供する。さらに、前記説明された感知增幅器の実施形態は速い読出し速度、ビットラインと参照ラインとの間の差異（例えば、寄生キャパシタンス等）に対する低い敏感度、信号平均を維持することによる強いノイズ耐性、セルフ - ラッチロジック ( s e l f - l a t c h i n g l o g i c ) を使用する追加的な特性を有する。但し、これは例示的であることであり、互に異なる特性が同一の感知增幅回路に共に適用されることが理解できる。

#### 【 0 1 1 3 】

前記説明された本発明の実施形態は例示的であることであり、本発明はこれに限定されない50

。多様な代替例及び均等例が可能である。本発明の実施形態はメモリアレイ内のM R A M (magnetic random access memory)のタイプ及びその数字によって限定されない。本発明の実施形態は感知増幅回路を動作させるか、或いはM T Jを選択するためのP M O S、N M O S等のようなトランジスターのタイプに限定されない。本発明の実施形態は感知増幅回路のためのコントロールロジックの生成又はロジックカラム選択(logical column selection)等を移行するために含まれたN O R、N A N Dのような論理ゲートのタイプによって限定されない。本発明の実施形態は発明の技術的思想が適用された集積回路のタイプによって適用されない。本発明の実施形態はC M O S、B i p o l a r、B I C M O S等のようにメモリを製造するために含まれたプロセス技術の特定類型によって限定されない。本発明の実施形態は感知増幅回路に直接的に連関されたことと説明されたが、これに限定されない。本発明の技術的思想の実施形態は応答時間、ノイズ耐性特性、低い電圧動作特性、大きい電圧ヘッドルーム(headroom)特性、少ない感知エラー等のような特性を含み、したがって、有用である。

10

#### 【0114】

本発明を逸脱しない範囲内で他の類似であるか、或いは非類似な変更が可能である。したがって、本発明の技術的思想は添付された請求項のみでなく、他の方式の請求項が可能である。

#### 【符号の説明】

#### 【0115】

W L s . . . ワードライン

B L s . . . ビットライン

S L s . . . ソースライン

R L s . . . 参照ライン

M T J . . . マグネチックトンネル接合

A P . . . 反平衡状態

P . . . 平衡状態

S W . . . スイッチ

I R E F . . . 参照ライン電流

I B I T . . . ビットライン電流

R R E F . . . 参照抵抗

R B I T . . . メモリセル抵抗又はビットライン抵抗

C B I T . . . ビットラインキャパシター

C R E F . . . 参照ラインキャパシター

20

30

【図1A】

【図1B】

【図1C】

【図1D】

【図2】

【図3 A】

【図3 B】

【図4 A】

【図5】

【図4 B】

【 四 6 】

【 四 7 】

【 図 8 】

【 义 9 】

【図10】

【図11A】

【図11B】

【図12A】

【図 1 2 B】

【図 1 3 A】

【図 1 3 B】

【図 1 4 A】

【図 1 4 B】

【図15】

【図17】

【図16】

【図18】

【図19】

【図20】

---

フロントページの続き

(72)発明者 ヨンシク・ヨン

アメリカ合衆国・カリフォルニア・95014・クパティーノ・ソレンソン・アヴェニュー・19

400・アパートメント・129

(72)発明者 スホ・チャ

大韓民国・ソウル・グロ-グ・ゲボン-2ドン・323-7

(72)発明者 チャン-キュン・キム

大韓民国・キョンギ-ド・ファソン-シ・バンソン-ドン・(番地なし)・シボム・ハンピット・

マウル・ハンワ・グメグリーン・アパート・21・233-804

審査官 酒井 恭信

(56)参考文献 特開2003-109375(JP,A)

国際公開第2006/064559(WO,A1)

特表2002-541608(JP,A)

特開2003-323791(JP,A)

特開2010-055719(JP,A)

米国特許出願公開第2004/0223393(US,A1)

(58)調査した分野(Int.Cl., DB名)

G 11 C 11/16

G 11 C 13/00