(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6318115号

(P6318115)

(45) 発行日 平成30年4月25日(2018.4.25)

(24) 登録日 平成30年4月6日(2018.4.6)

(51) Int.Cl.

H02M 3/155 (2006.01)

F 1

H02M 3/155

H02M 3/155P

V

請求項の数 12 (全 83 頁)

(21) 出願番号 特願2015-92948 (P2015-92948)

(22) 出願日 平成27年4月30日 (2015.4.30)

(65) 公開番号 特開2016-213920 (P2016-213920A)

(43) 公開日 平成28年12月15日 (2016.12.15)

審査請求日 平成29年5月26日 (2017.5.26)

(73) 特許権者 000003609

株式会社豊田中央研究所

愛知県長久手市横道41番地の1

(73) 特許権者 000003207

トヨタ自動車株式会社

愛知県豊田市トヨタ町1番地

(74) 代理人 110001195

特許業務法人深見特許事務所

(72) 発明者 ゴーテック チャン

愛知県長久手市横道41番地の1 株式会

社豊田中央研究所内

(72) 発明者 柳沢 直樹

愛知県長久手市横道41番地の1 株式会

社豊田中央研究所内

最終頁に続く

(54) 【発明の名称】電源システム

## (57) 【特許請求の範囲】

## 【請求項 1】

負荷と接続された高電圧側の第1の電力線および低電圧側の第2の電力線の間の直流電圧を制御するための電源システムであって、

第1の直流電源と、

第2の直流電源と、

前記第1および第2の直流電源と前記第1および第2の電力線との間で並列に直流電力変換を実行するための電力変換器と、

前記電力変換器における前記直流電力変換を制御するための制御装置を備え、

前記電力変換器は、

10

第1のリアクトルと、

第2のリアクトルと、

前記制御装置からの制御信号に応答したオンオフ制御によって、前記第1および第2のリアクトルのそれぞれを経由する電流経路を切換えるように配置された複数のスイッチング素子とを含み、

前記第1のリアクトルを経由する電流経路は、前記第1および第2の電力線の両方を含まずに前記第1の直流電源および前記第1のリアクトルの間で形成される第1の電流経路と、前記第1および第2の電力線の間に前記第1の直流電源および前記第1のリアクトルを直列に接続する第2の電流経路とを含み、

前記第2のリアクトルを経由する電流経路は、前記第1および第2の電力線の両方を含

20

まずに前記第2の直流電源および前記第2のリクトルの間に形成される第3の電流経路と、前記第1および第2の電力線の間に前記第2の直流電源および前記第2のリクトルを直列に接続する第4の電流経路とを含み、

前記制御装置は、

前記第1の直流電源からの出力を制御する第1の出力デューティ比と、前記第1の出力デューティ比の最大値に相当する電圧幅を有する第1のキャリア波との比較に従って前記第1および第2の電流経路を選択的に形成し、かつ、前記第2の直流電源からの出力を制御する第2の出力デューティ比と、前記第2の出力デューティ比の最大値に相当する電圧幅を有する第2のキャリア波との比較に従って前記第3および第4の電流経路を選択的に形成するように前記複数のスイッチング素子の前記制御信号を生成し、

10

前記第1および第2のキャリア波の各々は、同一周波数でエッジタイミングが同期した、右上がり直線部分を有する第1の鋸歯状波および右下がり直線部分を有する第2の鋸歯状波の一方を選択することによって構成され、

前記制御装置は、前記電力変換器の動作中において、前記第1および第2のキャリア波の各々について、前記第1および第2の鋸歯状波の選択を前記電力変換器の動作状態に応じて切替える、電源システム。

#### 【請求項2】

前記制御装置は、

前記第1のキャリア波において前記第1および第2の鋸歯状波の選択を切換える場合に、前記第1および第2の鋸歯状波の周期と同一長の遷移周期を設けるとともに、前記遷移周期において、前記第1のキャリア波を、前記第1および第2の鋸歯状波と同一周波数の三角波、または、当該三角波の逆相三角波に設定し、さらに、前記遷移周期における前記第1のリクトルの平均電流が当該遷移周期の直前の周期と同等になるように、前記第1の出力デューティ比を変換し、

20

前記第2のキャリア波において前記第1および第2の鋸歯状波の選択を切換える場合に、前記遷移周期を設けるとともに、前記遷移周期において、前記第2のキャリア波を前記三角波または前記逆相三角波に設定し、さらに、前記遷移周期における前記第2のリクトルの平均電流が当該遷移周期の直前の周期と同等になるように、前記第2の出力デューティ比を変換する、請求項1記載の電源システム。

#### 【請求項3】

30

前記制御装置は、前記第1または第2のキャリア波の各々について、前記第1の鋸歯状波から前記第2の鋸歯状波に切換える場合には、前記遷移周期において前記逆相三角波を設定する一方で、前記第2の鋸歯状波から前記第1の鋸歯状波に切換える場合には、前記遷移周期において前記三角波を設定する、請求項2記載の電源システム。

#### 【請求項4】

前記制御装置は、前記第1または第2のキャリア波の各々について、前記第1の鋸歯状波から前記第2の鋸歯状波に切換える場合には、前記遷移周期において前記三角波を設定する一方で、前記第2の鋸歯状波から前記第1の鋸歯状波に切換える場合には、前記遷移周期において前記逆相三角波を設定する、請求項2記載の電源システム。

#### 【請求項5】

40

前記複数のスイッチング素子は、

第1のノードおよび前記第1の電力線の間に電気的に接続された第1のスイッチング素子と、

第2のノードおよび前記第1のノードの間に電気的に接続された第2のスイッチング素子と、

第3のノードおよび前記第2のノードの間に電気的に接続された第3のスイッチング素子と、

前記第2の直流電源の負極端子と電気的に接続された前記第2の電力線と、前記第3のノードとの間に電気的に接続された第4のスイッチング素子とを有し、

前記第1のリクトルは、前記第2のノードと前記第2の電力線との間に、前記第1の

50

直流電源と直列に電気的に接続され、

前記第2のリアクトルは、前記第1および第3のノードの間に、前記第2の直流電源と直列に電気的に接続され、

前記第1の電流経路の形成時には前記第3および第4のスイッチング素子がオンされ、前記第2の電流経路の形成時には前記第1および第2のスイッチング素子がオンされ、前記第3の電流経路の形成時には前記第2および第3のスイッチング素子がオンされ、前記第4の電流経路の形成時には前記第1および第4のスイッチング素子がオンされる、請求項1～3のいずれか1項に記載の電源システム。

#### 【請求項6】

前記複数のスイッチング素子は、

10

第1のノードおよび前記第1の電力線の間に電気的に接続された第1のスイッチング素子と、

第2のノードおよび前記第1のノードの間に電気的に接続された第2のスイッチング素子と、

第3のノードおよび前記第2のノードの間に電気的に接続された第3のスイッチング素子と、

前記第2の直流電源の負極端子と電気的に接続された前記第2の電力線と、前記第3のノードとの間に電気的に接続された第4のスイッチング素子とを有し、

前記第1のリアクトルは、前記第2のノードと前記第1の電力線との間に、前記第1の直流電源と直列に電気的に接続され、

20

前記第2のリアクトルは、前記第1および第3のノードの間に、前記第2の直流電源と直列に電気的に接続され、

前記第1の電流経路の形成時には前記第1および第2のスイッチング素子がオンされ、前記第2の電流経路の形成時には前記第3および第4のスイッチング素子がオンされ、前記第3の電流経路の形成時には前記第2および第3のスイッチング素子がオンされ、前記第4の電流経路の形成時には前記第1および第4のスイッチング素子がオンされる、請求項1～3のいずれか1項に記載の電源システム。

#### 【請求項7】

前記電力変換器は、

30

前記第1の電力線と第1のノードとの間に電気的に接続される第1の半導体素子と、

前記第2の電力線と前記第1のノードとの間に電気的に接続される第2の半導体素子と、

、 第2のノードと、前記第2の電力線との間に電気的に接続される第3の半導体素子と、前記第1の電力線と前記第2のノードとの間に電気的に接続される第4の半導体素子と、

、 前記第1のノードと前記第2のノードとの間に電気的に接続される第5の半導体素子とを含み、

少なくとも前記第2、第4および第5の半導体素子は、前記スイッチング素子を有し、

少なくとも前記第1および第3の半導体素子は、前記第2の電力線から前記第1の電力線へ向かう方向を順方向として配置されたダイオードを有し、

40

前記第1のリアクトルは、前記第1のノードと前記第2の電力線との間に、前記第1の直流電源と直列に電気的に接続され、

前記第2のリアクトルは、前記第2のノードと前記第1の電力線との間に、前記第2の直流電源と直列に電気的に接続され、

前記第1の電流経路の形成時には前記第2の半導体素子によって電流経路が形成され、

前記第2の電流経路の形成時には前記第1の半導体素子によって電流経路が形成され、

前記第3の電流経路の形成時には前記第4の半導体素子によって電流経路が形成され、

前記第4の電流経路の形成時には前記第3の半導体素子によって電流経路が形成され、

前記第5の半導体素子は、前記第1および第4の電流経路が同時に形成される期間、および、前記第2および第3の電流経路が同時に形成される期間において電流経路を形成す

50

る、請求項 1 ~ 3 のいずれか 1 項に記載の電源システム。

**【請求項 8】**

前記第 1 および第 3 の半導体素子の少なくとも一方において、前記ダイオードとは逆方向の電流経路を形成するための前記スイッチング素子が前記ダイオードと並列にさらに設けられ、当該スイッチング素子は、前記制御装置からの信号に応答して、前記第 2 または第 4 の電流経路の形成時にオンするように制御される、請求項 7 記載の電源システム。

**【請求項 9】**

前記第 5 の半導体素子は、

前記第 1 のノードから前記第 2 のノードへ向かう電流経路を前記第 1 および第 2 のノード間に形成するオン状態と当該電流経路を遮断するオフ状態とを前記制御装置からの信号に応答して選択的に形成するための第 1 のサブスイッチング素子と、10

前記第 2 のノードから前記第 1 のノードへ向かう電流経路を前記第 1 および第 2 のノード間に形成するオン状態と当該電流経路を遮断するオフ状態とを前記制御装置からの信号に応答して選択的に形成するための第 2 のサブスイッチング素子とを含む、請求項 7 または 8 記載の電源システム。

**【請求項 10】**

前記第 1 および第 2 のリアクトルは、単一の複合磁気部品によって一体的に構成され、前記複合磁気部品は、

前記第 1 のリアクトルを構成するための、電気的に直列接続された第 1 および第 2 の巻線と、20

前記第 1 のリアクトルを構成するための第 3 の巻線と、

非線形磁性材料で構成されたコアとを含み、

前記コアは、前記第 1 の巻線が巻回される第 1 の磁脚部と、前記第 2 の巻線が巻回される第 2 の磁脚部と、前記第 3 の巻線が巻回される第 3 の磁脚部と、前記第 1 から第 3 の磁脚部の間に磁気経路を形成するための第 4 の磁脚部とを含むように構成される、請求項 1 記載の電源システム。

**【請求項 11】**

前記第 1 のリアクトルおよび前記第 2 のリアクトルの動作状態が、電流の増加に応じて、前記第 1 および第 2 のリアクトルが磁気的に非干渉な状態で動作する非磁気結合モードから前記第 1 および第 2 のリアクトルが磁気的に干渉した状態で動作する磁気結合モードへ変化し、30

前記非磁気結合モードにおいては、前記第 1 および第 2 の磁脚部における透磁率が同等である一方で、前記磁気結合モードにおいては、前記第 1 および第 2 の磁脚部の一方での透磁率が、前記第 1 および第 2 の磁脚部の他方の透磁率よりも低い、請求項 10 記載の電源システム。

**【請求項 12】**

前記第 1 および第 2 の直流電源の各々が力行動作する場合において、前記第 1 のリアクトルを通過する電流によって前記第 1 の巻線および前記第 2 の巻線からそれぞれ発生される第 1 の磁界および第 2 の磁界と、前記第 2 のリアクトルを通過する電流によって前記第 3 の巻線から発生される第 3 の磁界とが、前記第 1 または第 2 の磁脚部のいずれか一方の磁脚部では強め合う一方で他方の磁脚部では弱め合い、かつ、前記第 1 および第 2 の磁界が前記第 3 の磁脚部では互いに弱め合うように、前記第 1 から第 3 の巻線は前記第 1 から第 3 の磁脚部にそれぞれ巻回される、請求項 10 または 11 記載の電源システム。40

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

この発明は、電源システムに関し、より特定的には、パルス幅変調（P W M）制御を用いて、2つの直流電源と負荷との間で2つのリアクトルを通過する電流を介して直流電力変換を実行するための電源システムに関する。

**【背景技術】**

10

20

30

40

50

**【 0 0 0 2 】**

複数の電源と負荷との間に接続された電力変換器を用いて、複数の電源を組み合わせて負荷へ電力を供給するハイブリッド電源システムが用いられている。

**【 0 0 0 3 】**

たとえば、特開2013-13234号公報（特許文献1）には、複数のスイッチング素子のスイッチングパターンを切換えることによって、動作モードを切換えることが可能な電力変換器の構成が記載されている。そして、動作モードには、2つの直流電源を並列に使用する状態で直流電力変換を行なうモード（並列接続モード）が含まれる。当該並列接続モードでは、2つの直流電源のそれぞれについて、出力制御のためのデューティ比とキャリア波との比較によるPWM制御によって、複数のスイッチング素子のオンオフが制御される。10

**【 0 0 0 4 】**

特許文献2には、特許文献1に記載された電力変換器等に使用される2個のリアクトルを一体的に構成するために磁気部品の構造が記載されている。

**【先行技術文献】****【特許文献】****【 0 0 0 5 】**

【特許文献1】特開2013-13234号公報

【特許文献2】特開2013-198246号公報

**【発明の概要】****【発明が解決しようとする課題】****【 0 0 0 6 】**

特許文献1には、2つのリアクトルを流れる電流の位相を制御することによって、複数のスイッチング素子での電力損失を低減することが記載されている。具体的には、それぞれのリアクトル電流の間で、上昇タイミングまたは下降タイミング（すなわち、変曲点）が同一タイミングとなるように電流位相を制御することが記載されている。20

**【 0 0 0 7 】**

しかしながら、特許文献1では、2つの直流電源のそれぞれのPWM制御に用いられるキャリア信号間の位相差を制御する、キャリア位相制御によって上記の電流位相を実現する。このため、PWM制御でのデューティ比が変化する毎に、位相差を変化させが必要となる。この結果、キャリア位相制御のための演算負荷が大きくなるため、演算遅れの影響によってキャリア位相差が不適切となることにより、リアクトル電流が変動する虞がある。30

**【 0 0 0 8 】**

また、特許文献1には、リアクトル電流間で一致させるべき変曲点を、上昇タイミング（極小点）および下降タイミング（極大点）のいずれとするかについても、電力変換器の動作状態、具体的には、各直流電源が回生および力行のいずれで動作しているかに応じて変化することが記載されている。このため、キャリア位相の変化量が大きくなることによって、過渡的にリアクトル電流が変動する虞がある。

**【 0 0 0 9 】**

この発明はこのような問題点を解決するためになされたものであって、この発明の目的は、2つの直流電源と負荷との間で2つのリアクトルを通過する電流を介して直流電力変換を実行する電源システムにおいて、PWM制御の演算負荷を増大することなく、リアクトル電流間で変曲点のタイミングを一致させる電流位相制御を簡易に実行することによって、電源システムの性能を向上することである。40

**【課題を解決するための手段】****【 0 0 1 0 】**

この発明のある局面では、電源システムは、負荷と接続された高電圧側の第1の電力線および低電圧側の第2の電力線の間の直流電圧を制御する。電源システムは、第1の直流電源と、第2の直流電源と、第1および第2の直流電源と第1および第2の電力線との間50

で並列に直流電力変換を実行するための電力変換器と、電力変換器における直流電力変換を制御するための制御装置を備える。電力変換器は、第1のリクトルと、第2のリクトルと、複数のスイッチング素子とを含む。複数のスイッチング素子は、制御装置からの制御信号に応答したオンオフ制御によって、第1および第2のリクトルのそれぞれを経由する電流経路を切換えるように配置される。第1のリクトルを経由する電流経路は、第1および第2の電流経路を含む。第1の電流経路は、第1および第2の電力線の両方を含まずに第1の直流電源および第1のリクトルの間に形成される。第2の電流経路は、第1および第2の電力線の間に第1の直流電源および第1のリクトルを直列に接続する。第2のリクトルを経由する電流経路は、第3および第4の電流経路を含む。第3の電流経路は、第1および第2の電力線の両方を含まずに第2の直流電源および第2のリクトルの間に形成される。第4の電流経路は、第1および第2の電力線の間に第2の直流電源および第2のリクトルを直列に接続する。第1の直流電源からの出力を制御する第1の出力デューティ比と、第1の出力デューティ比の最大値に相当する電圧幅を有する第1のキャリア波との比較に従って第1および第2の電流経路を選択的に形成し、かつ、第2の直流電源からの出力を制御する第2の出力デューティ比と、第2の出力デューティ比の最大値に相当する電圧幅を有する第2のキャリア波との比較に従って第3および第4の電流経路を選択的に形成するように複数のスイッチング素子の制御信号を生成する。第1および第2のキャリア波の各々は、同一周波数でエッジタイミングが同期した、右上がり直線部分を有する第1の鋸歯状波および右下がり直線部分を有する第2の鋸歯状波の一方を選択することによって構成される。制御装置は、電力変換器の動作中において、第1および第2のキャリア波の各々について、第1および第2の鋸歯状波の選択を電力変換器の動作状態に応じて切替える。10

#### 【0011】

好ましくは、制御装置は、第1のキャリア波において第1および第2の鋸歯状波の選択を切換える場合に、第1および第2の鋸歯状波の周期と同一長の遷移周期を設けるとともに、遷移周期において、第1のキャリア波を、第1および第2の鋸歯状波と同一周波数の三角波、または、当該三角波の逆相三角波に設定し、さらに、遷移周期における第1のリクトルの平均電流が、当該遷移周期の直前の周期と同等になるように、第1の出力デューティ比を変換する。さらに、制御装置は、第2のキャリア波において第1および第2の鋸歯状波の選択を切換える場合に、遷移周期を設けるとともに、遷移周期において、第2のキャリア波を三角波または逆相三角波に設定し、さらに、遷移周期における第2のリクトルの平均電流が、当該遷移周期の直前の周期と同等になるように、第2の出力デューティ比を変換する。20

#### 【0012】

さらに好ましくは、制御装置は、第1または第2のキャリア波の各々について、第1の鋸歯状波から第2の鋸歯状波に切換える場合には、遷移周期において逆相三角波を設定する一方で、第2の鋸歯状波から第1の鋸歯状波に切換える場合には、遷移周期において三角波を設定する。あるいは、制御装置は、第1または第2のキャリア波の各々について、第1の鋸歯状波から第2の鋸歯状波に切換える場合には、遷移周期において三角波を設定する一方で、第2の鋸歯状波から第1の鋸歯状波に切換える場合には、遷移周期において逆相三角波を設定する。30

#### 【0013】

好ましくは、複数のスイッチング素子は、第1から第4のスイッチング素子を有する。第1のスイッチング素子は、第1のノードおよび第1の電力線の間に電気的に接続される。第2のスイッチング素子は、第2のノードおよび第1のノードの間に電気的に接続される。第3のスイッチング素子は、第3のノードおよび第2のノードの間に電気的に接続される。第4のスイッチング素子は、第2の直流電源の負極端子と電気的に接続された第2の電力線と、第3のノードとの間に電気的に接続される。第1のリクトルは、第2のノードと第1または第2の電力線との間に、第1の直流電源と直列に電気的に接続される。第2のリクトルは、第1および第3のノードの間に、第2の直流電源と直列に電気的に接続される。40

接続される。第1のリアクトルが第2のノードと第2の電力線との間に接続された構成では、第1の電流経路の形成時には第3および第4のスイッチング素子がオンされ、第2の電流経路の形成時には第1および第2のスイッチング素子がオンされ、第3の電流経路の形成時には第2および第3のスイッチング素子がオンされ、第4の電流経路の形成時には第1および第4のスイッチング素子がオンされる。第1のリアクトルが第1のノードと第2の電力線との間に接続された構成では、第1の電流経路の形成時には第1および第2のスイッチング素子がオンされ、第2の電流経路の形成時には第3および第4のスイッチング素子がオンされ、第3の電流経路の形成時には第2および第3のスイッチング素子がオンされ、第4の電流経路の形成時には第1および第4のスイッチング素子がオンされる。

## 【0014】

10

また好ましくは、電力変換器は、第1から第5の半導体素子を含む。第1の半導体素子は、第1の電力線と第1のノードとの間に電気的に接続される。第2の半導体素子は、第2の電力線と第1のノードとの間に電気的に接続される。第3の半導体素子は、第2のノードと、第2の電力線との間に電気的に接続される。第4の半導体素子は、第1の電力線と第2のノードとの間に電気的に接続される。第5の半導体素子は、第1のノードと第2のノードとの間に電気的に接続される。少なくとも第2、第4および第5の半導体素子は、スイッチング素子を有する。少なくとも第1および第3の半導体素子は、第2の電力線から第1の電力線へ向かう方向を順方向として配置されたダイオードを有する。第1のリアクトルは、第1のノードと第2の電力線との間に、第1の直流電源と直列に電気的に接続される。第2のリアクトルは、第2のノードと第1の電力線の間に、第2の直流電源と直列に電気的に接続される。第1の電流経路の形成時には、第2の半導体素子によって電流経路が形成され、第2の電流経路の形成時には第1の半導体素子によって電流経路が形成される。第3の電流経路の形成時には第4の半導体素子によって電流経路が形成され、第4の電流経路の形成時には第3の半導体素子によって電流経路が形成される。第5の半導体素子は、第1および第4の電流経路が同時に形成される期間、および、第2および第3の電流経路が同時に形成される期間において電流経路を形成する。

## 【0015】

20

さらに好ましくは、第1および第3の半導体素子の少なくとも一方において、ダイオードとは逆方向の電流経路を形成するためのスイッチング素子がダイオードと並列にさらに設けられ、当該スイッチング素子は、制御装置からの信号に応答して、第2または第4の電流経路の形成時にオンするように制御される。

## 【0016】

30

あるいは、さらに好ましくは、第5の半導体素子は、第1および第2のサブスイッチング素子を有する。第1のサブスイッチング素子は、第1のノードから第2のノードへ向かう電流経路を第1および第2のノード間に形成するオン状態と当該電流経路を遮断するオフ状態とを制御装置からの信号に応答して選択的に形成するように構成される・第2のサブスイッチング素子は、第2のノードから第1のノードへ向かう電流経路を第1および第2のノード間に形成するオン状態と当該電流経路を遮断するオフ状態とを制御装置からの信号に応答して選択的に形成するように構成される。

## 【0017】

40

好ましくは、第1および第2のリアクトルは、単一の複合磁気部品によって一体的に構成される。複合磁気部品は、第1～第3の巻線とコアとを含む。第1および第2の巻線は、電気的に直列接続されて、第1の電流が通過する。第1および第2の巻線は、電気的に直列に接続されて第1のリアクトルを構成する。第3の巻線は、第2のリアクトルを構成する。コアは、非線形磁性材料で構成される。コアは、第1の巻線が巻回される第1の磁脚部と、第2の巻線が巻回される第2の磁脚部と、第3の巻線が巻回される第3の磁脚部と、第1から第3の磁脚部の間に磁気経路を形成するための第4の磁脚部とを含むように構成される。

## 【0018】

さらに好ましくは、第1のリアクトルおよび第2のリアクトルの動作状態は、電流増加

50

に応じて、第1および第2のリアクトルが磁気的に非干渉な状態で動作する非磁気結合モードから第1および第2のリアクトルが磁気的に干渉した状態で動作する磁気結合モードへ変化する。そして、非磁気結合モードにおいては、第1および第2の磁脚部における透磁率が同等である一方で、磁気結合モードにおいては、第1および第2の磁脚部の一方での透磁率が、第1および第2の磁脚部の他方の透磁率よりも低い。

#### 【0019】

あるいは、さらに好ましくは、第1および第2の直流電源の各々が力行動作する場合において、第1のリアクトルを通過する電流によって第1の巻線および第2の巻線からそれぞれ発生される第1の磁界および第2の磁界と、第2のリアクトルを通過する電流によって第3の巻線から発生される第3の磁界とが、第1または第2の磁脚部のいずれか一方の磁脚部では強め合う一方で他方の磁脚部では弱め合い、かつ、第1および第2の磁界が第3の磁脚部では互いに弱め合うように、第1から第3の巻線は第1から第3の磁脚部にそれぞれ巻回される。

10

#### 【発明の効果】

#### 【0020】

この発明によれば、2つの直流電源と負荷との間で2つのリアクトルを通過する電流を介して直流電力変換を実行する電源システムにおいて、PWM制御の演算負荷を増大することなく、リアクトル電流間で変曲点のタイミングを一致させる電流位相制御を簡易に実行することによって、電源システムの性能を向上することができる。

#### 【図面の簡単な説明】

20

#### 【0021】

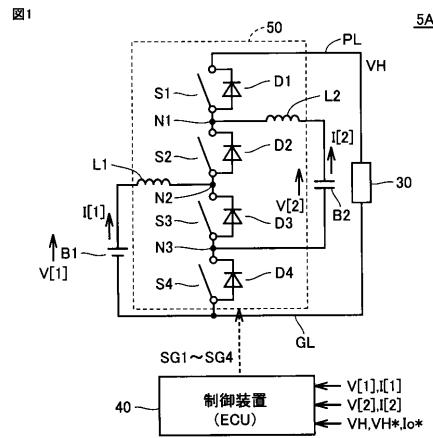

【図1】実施の形態1に従う電源システムの構成を示す回路図である。

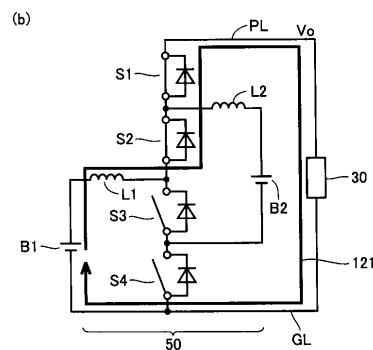

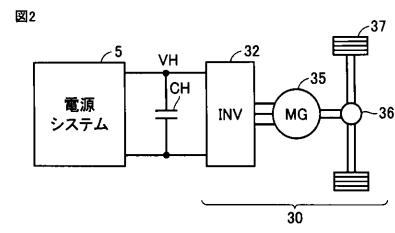

【図2】図1に示された負荷の構成例を示す概略図である。

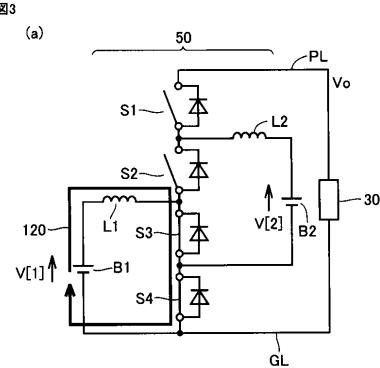

【図3】図1に示された電力変換器の電流経路を説明する第1の回路図である。

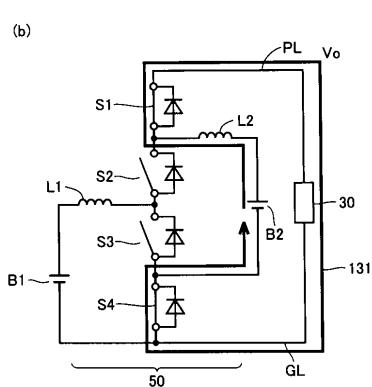

【図4】図1に示された電力変換器の電流経路を説明する第2の回路図である。

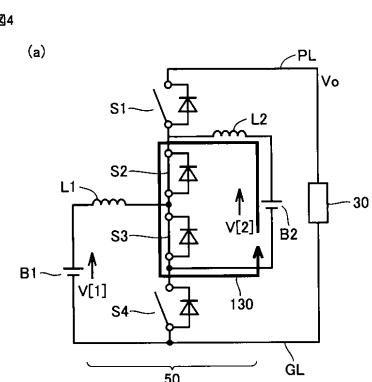

【図5】図1に示された電力変換器の制御構成を説明する機能ブロック図である。

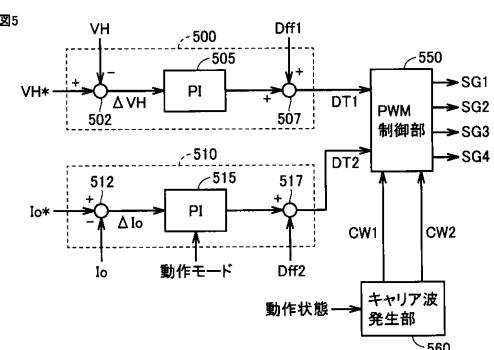

【図6】比較例として示されるキャリア位相制御が適用されたパラレル制御モードでの動作例を説明する波形図である。

【図7】パラレル接続モードにおけるキャリア位相制御の動作例を説明するための電流波形図である。

30

【図8】図7の所定期間ににおける電流経路を説明する回路図である。

【図9】リアクトル電流の方向に応じた電流位相の制御例を説明するための図表である。

【図10】本実施の形態に従う電源システムで適用されるPWM制御のキャリア波モードを説明するための第1の波形図である。

【図11】本実施の形態に従う電源システムで適用されるPWM制御のキャリア波モードを説明するための第2の波形図である。

【図12】本実施の形態に従う電源システムで適用されるPWM制御のキャリア波モードを説明するための第3の波形図である。

【図13】本実施の形態に従う電源システムで適用されるPWM制御のキャリア波モードを説明するための第4の波形図である。

40

【図14】4個のキャリア波モードにおけるこぎり波の波形およびリアクトル電流の位相パターンとの対応を説明する図表である。

【図15】実施の形態1に従うPWM制御でのキャリア波モードの切替え時における問題点を説明するための動作波形図である。

【図16】本実施の形態1の変形例に従うPWM制御におけるキャリア波モード切替え時の第1の制御例を説明する波形図である。

【図17】本実施の形態1の変形例に従うPWM制御における遷移周期でのデューティ比変換を説明するための波形図である。

【図18】図16に示された第1の制御例に従う遷移周期でのキャリア波の設定の一覧を説明する図表である。

50

【図19】本実施の形態1の変形例に従うPWM制御におけるキャリア波モード切替え時の第2の制御例を説明する波形図である。

【図20】図19に示された第1の制御例に従う遷移周期でのキャリア波の設定の一覧を説明する図表である。

【図21】図1に示された電力変換器が有する複数の動作モードの一覧を示す図表である。

【図22】図1に示された電力変換器の回路構成の変形例を示す回路図である。

【図23】実施の形態2に従う電源システムの構成を説明する回路図である。

【図24】図23に示した電力変換器のパラレル昇圧モードにおける第1の等価回路図である。

10

【図25】図24に示した等価回路図における各直流電源の下アームオン時の電流経路を示す回路図である。

【図26】図24に示した等価回路図における各直流電源の上アームオン時の電流経路を示す回路図である。

【図27】図24に示した電力変換器のパラレル昇圧モードにおける第2の等価回路図である。

【図28】図27に示した等価回路図における各直流電源の下アームオン時の電流経路を示す回路図である。

【図29】図27に示した等価回路図における各直流電源の上アームオン時の電流経路を示す回路図である。

20

【図30】第1アームおよび第2アームを用いる昇圧チョッパ回路の各アームオンオフとスイッチング素子のオンオフとの対応関係が示される。

【図31】図23に示した電力変換器のパラレル昇圧モードにおいて各スイッチング素子をオンオフ制御するためのゲート論理式の一覧を示す図表である。

【図32】図23に示された電力変換器のパラレル接続モードにおける制御動作の比較例を説明するための波形図が示される。

【図33】図23に示した電力変換器のパラレル昇圧モードにおけるスイッチングパターンの一覧を示す図表である。

【図34】図23に示した電力変換器において第1アームを用いる昇圧チョッパ回路の等価回路図である。

30

【図35】図34中の点線で囲まれた部分の拡大図である。

【図36】図23に示した電力変換器において第2アームを用いる昇圧チョッパ回路の等価回路図である。

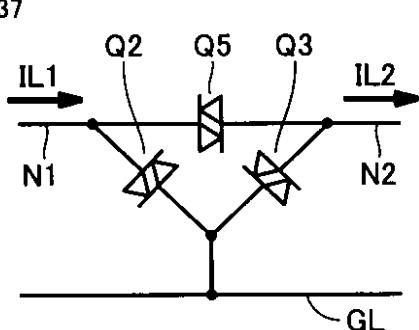

【図37】図36中の点線で囲まれた部分の拡大図である。

【図38】図23に示された電力変換器におけるリアクトル電流の向きの組み合わせを説明する概念図である。

【図39】両方の直流電源が力行動作する場合の電流挙動例を示す波形図である。

【図40】図37に示された等価回路で形成され得る3通りの電流経路を説明するための回路図である。

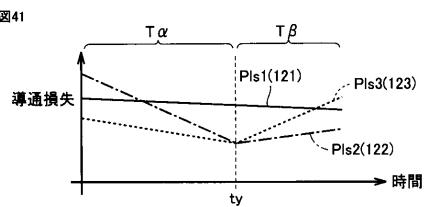

【図41】図40に示された3つの電流経路のそれぞれにおける導通損失の推移を示す波形図である。

40

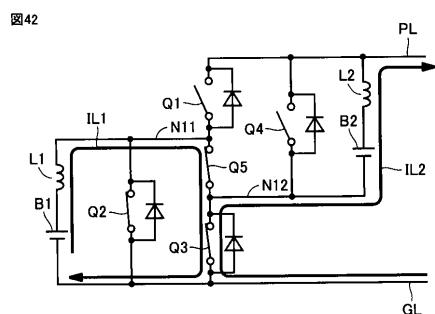

【図42】図23に示された電力変換器において図39および図41中の第1の期間に形成される電流経路を説明するための回路図である。

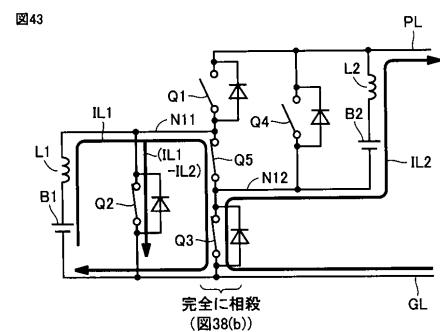

【図43】図23に示された電力変換器において図39および図41中の第2の期間に形成される電流経路を説明するための回路図である。

【図44】実施の形態1に従う電力変換器を図36と同等に動作させたときの電流経路を説明するための回路図である。

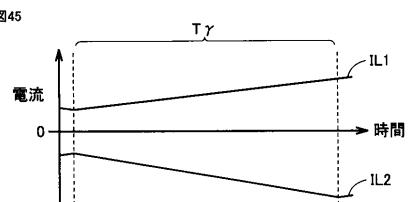

【図45】図23に示された電力変換器において一方の直流電源が力行動作するとともに他方の直流電源が回生動作する場合の電流挙動例を示す波形図である。

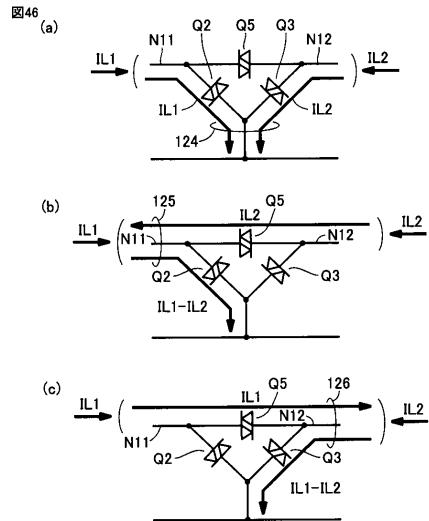

【図46】図45に示された期間において形成され得る3通りの電流経路を説明するため

50

の回路図である。

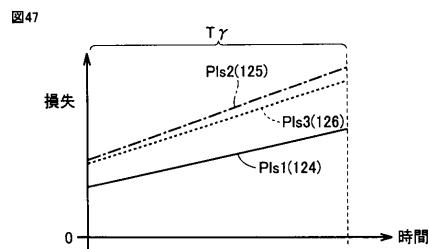

【図47】図46に示された3つの電流経路のそれぞれにおける導通損失の推移を示す波形図である。

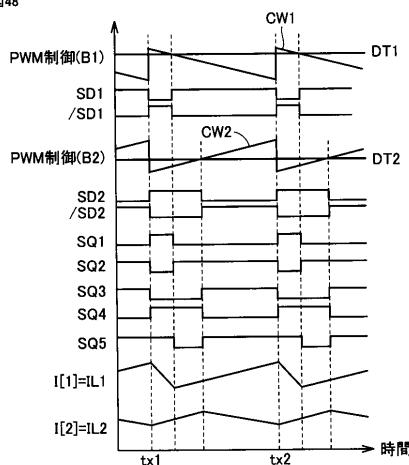

【図48】実施の形態2に従う電力変換器に対する、実施の形態1と同様のPWM制御の適用を説明するための波形図である。

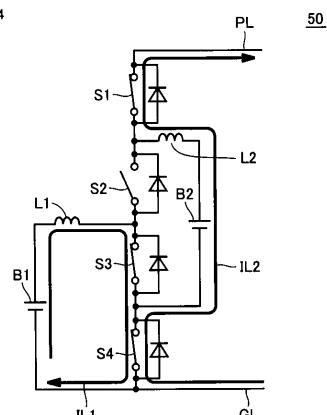

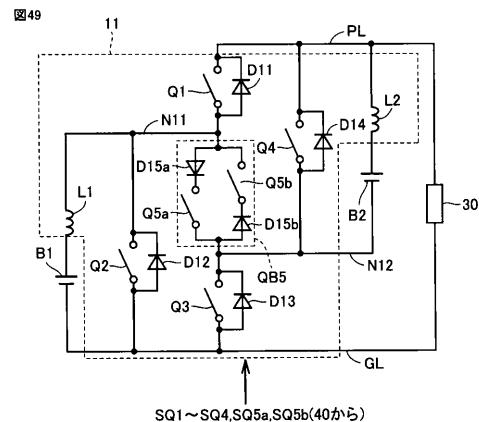

【図49】実施の形態2に従う電力変換器の变形例の構成を説明するための回路図である。

【図50】図49に示された電力変換器のパラレル昇圧モードにおける各スイッチング素子のオンオフ制御のためのゲート論理式の一覧を示す図表である。

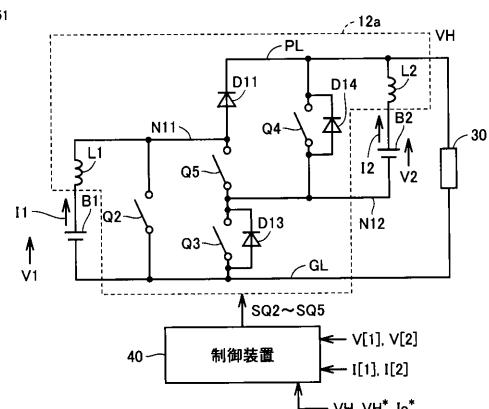

【図51】第1の直流電源を回生充電しない場合における図23に示した電力変換器の構成からの变形例を示す回路図である。

10

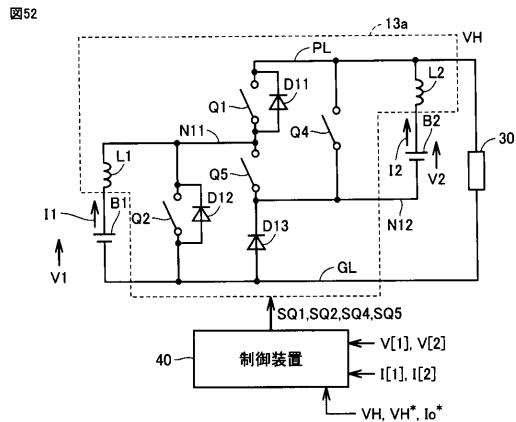

【図52】第2の直流電源を回生充電しない場合における図23に示した電力変換器の構成からの变形例を示す回路図である。

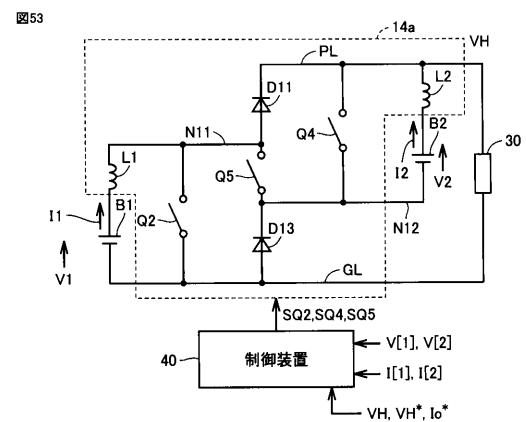

【図53】第1および第2の直流電源を回生充電しない場合における図23に示した電力変換器の構成からの变形例を示す回路図である。

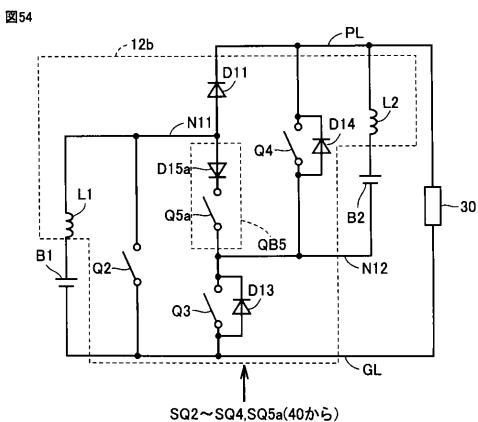

【図54】第1の直流電源を回生充電しない場合における図49に示された電力変換器の構成からの变形例を示す回路図である。

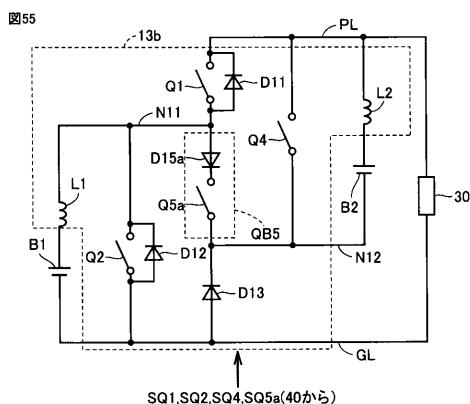

【図55】第2の直流電源を回生充電しない場合における図49に示された電力変換器の構成からの变形例を示す回路図である。

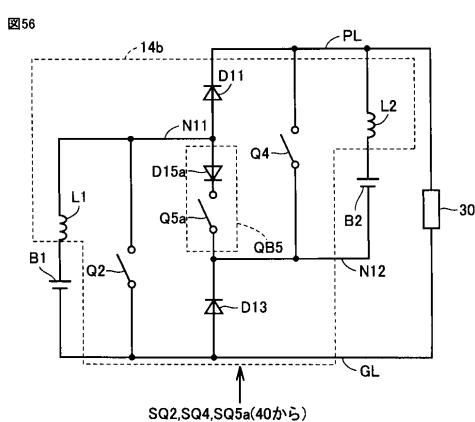

【図56】第1および第2の直流電源を回生充電しない場合における図49に示された電力変換器の構成からの变形例を示す回路図である。

20

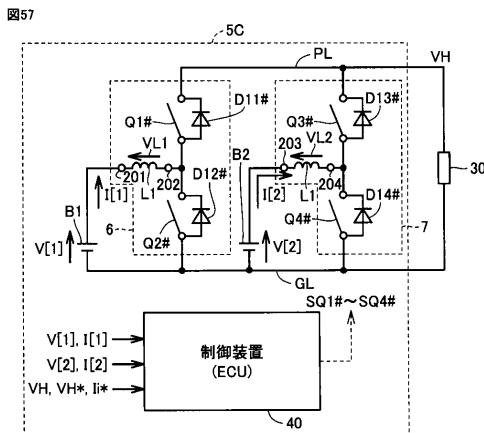

【図57】実施の形態3に従う電源システムの構成例を示す回路図である。

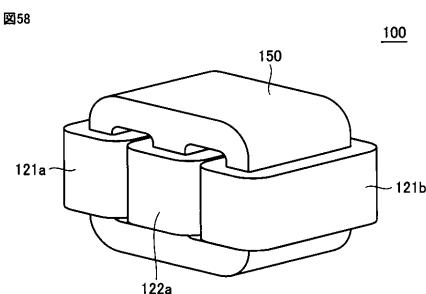

【図58】図57に示された2個のリアクトルを一体的に構成するための磁気結合リアクトルの概略的な外観図の一例である。

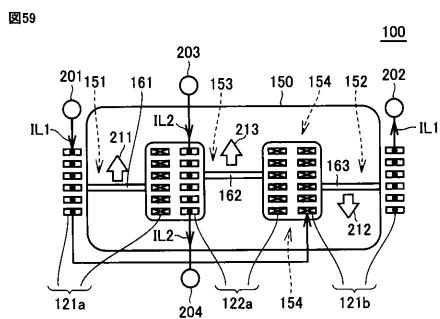

【図59】図58に示した磁気結合リアクトルの構造をさらに説明するための概念的な断面図である。

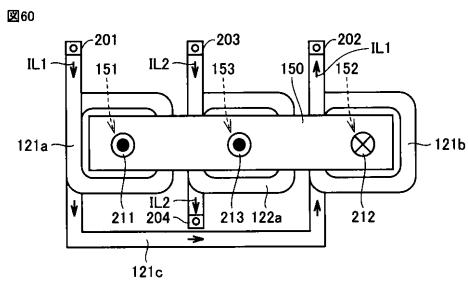

【図60】図59に示した各巻線の巻回態様の一例を説明するための概念図である。

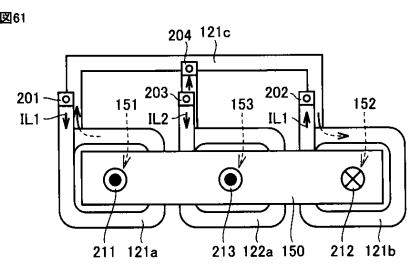

【図61】図59に示した各巻線の巻回態様の他の例を説明するための概念図である。

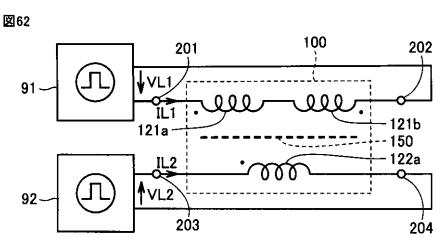

【図62】図59に示した磁気結合リアクトルの電気的な等価回路図である。

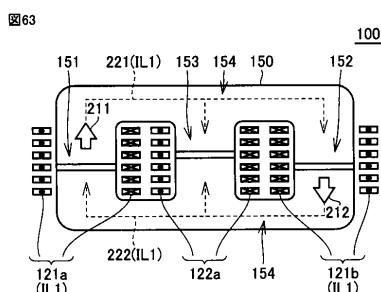

【図63】コア内部における各巻線からの発生磁束の関係について説明するための概念的な第1の断面図である。

30

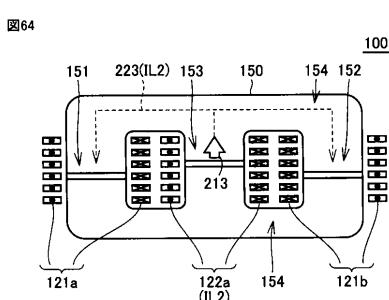

【図64】コア内部における各巻線からの発生磁束の関係について説明するための概念的な第2の断面図である。

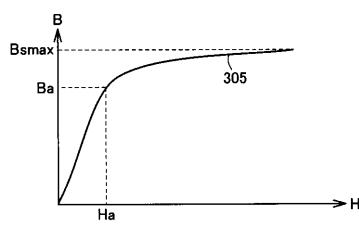

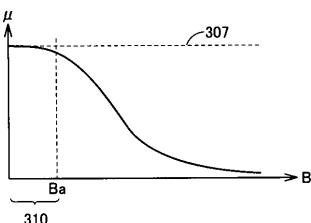

【図65】強磁性体の一般的な磁化曲線(B-H曲線)を示す概念図である。

【図66】図65に示した磁化曲線における磁束密度の変化に対する透磁率の変化特性を示す概念図である。

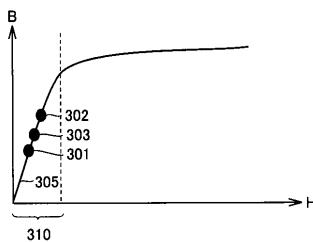

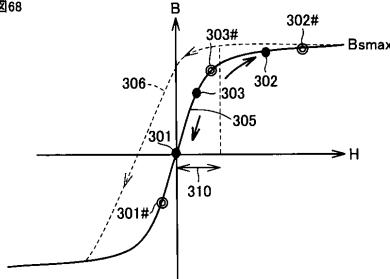

【図67】リアクトル電流が小さい領域におけるコアの各磁脚部の磁気的な動作点を説明する概念図である。

【図68】リアクトル電流が大きい領域におけるコアの各磁脚部の磁気的な動作点を説明する概念図である。

40

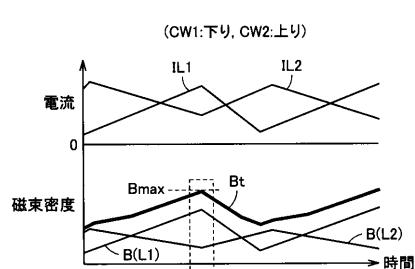

【図69】リアクトル電流の位相と磁束密度との関係を説明するための概念的な波形図である。

【図70】図57に示された電源システムにおける電流位相制御の例を説明する波形図である。

【図71】実施の形態3に従う電源システムにおける電流位相制御の他の例を説明する波形図である。

【図72】実施の形態3に従う電源システムにおける電流位相制御のさらに他の例を説明する波形図である。

【図73】実施の形態3に従う電源システムにおけるリアクトル電流の位相を制御したときの第1の動作例を示す波形図である。

50

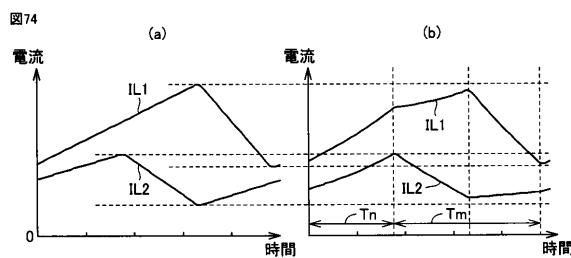

【図74】実施の形態3に従う電源システムにおけるリアクトル電流の位相を制御したときの第2の動作例を示す波形図である。

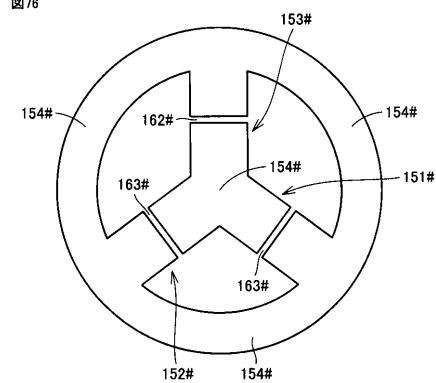

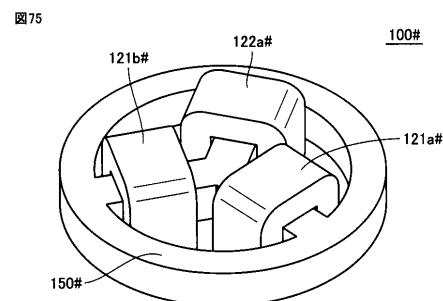

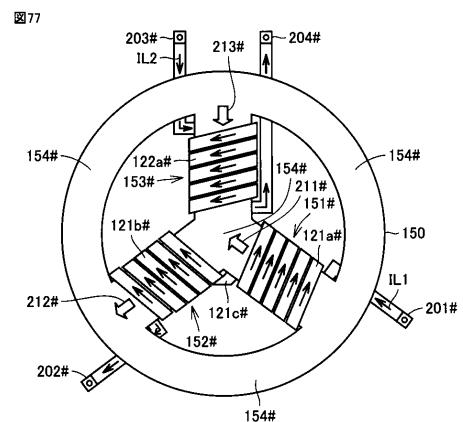

【図75】変形例に従う磁気結合リアクトルの概略的な外観図である。

【図76】図75に示した磁気結合リアクトルのコアの外観図である。

【図77】図75に示した磁気結合リアクトルにおける各巻線の巻回態様を説明するための概略的な平面図である。

#### 【発明を実施するための形態】

##### 【0022】

以下に、本発明の実施の形態について図面を参照して詳細に説明する。なお、以下では、図中の同一または相当部分には同一符号を付して、その説明は原則的に繰返さないものとする。10

##### 【0023】

###### [実施の形態1]

###### (回路構成)

図1は、本発明の実施の形態1に従う電源システムの構成例を示す回路図である。本実施の形態1に従う電源システム5Aは、特許文献1に示された電源システムと回路構成が共通する。

##### 【0024】

図1を参照して、電源システム5Aは、直流電源B1と、直流電源B2と、負荷30と、制御装置40と、電力変換器50とを備える。20

##### 【0025】

本実施の形態1において、直流電源B1およびB2は、二次電池や電気二重層キャパシタ等の蓄電装置によって構成される。たとえば、直流電源B1は、リチウムイオン二次電池やニッケル水素電池のような二次電池で構成される。また、直流電源B2は、たとえば、電気二重層キャパシタやリチウムイオンキャパシタ等の出力特性に優れた直流電圧源要素により構成される。

##### 【0026】

なお、直流電源B1およびB2を同種の蓄電装置によって構成することも可能である。また、直流電源B1およびB2の容量についても特に限定されることはなく、直流電源B1およびB2は、各々を同等の容量で構成してもよく、一方の直流電源の容量を他方の直流電源の容量より大きくしてもよい。30

##### 【0027】

電力変換器50は、高電圧側の電力線PLおよび低電圧側の電力線GLの間の直流電圧VH(以下、出力電圧VHとも称する)を制御するように構成される。電力線GLは、代表的には接地配線で構成される。電力線PLおよびGLは、負荷30と接続される。

##### 【0028】

負荷30は、電力線PLおよびGLを経由して、電力変換器50の出力電圧VHを受けて動作する。出力電圧VHの電圧指令値VH\*は、負荷30の動作に適した電圧に設定される。電圧指令値VH\*は、負荷30の状態に応じて可変に設定されてもよい。さらに、負荷30は、回生発電等によって、直流電源B1および/またはB2の充電電力を発生可能に構成されてもよい。40

##### 【0029】

図2は、負荷30の構成例を示す概略図である。

図2を参照して、負荷30は、たとえば電動車両の走行用電動機を含むように構成される。負荷30は、平滑コンデンサCHと、インバータ32と、モータジェネレータ35と、動力伝達ギヤ36と、駆動輪37とを含む。

##### 【0030】

モータジェネレータ35は、車両駆動力を発生するための走行用電動機であり、たとえば、複数相の永久磁石型同期電動機で構成される。モータジェネレータ35の出力トルクは、減速機や動力分割機構によって構成される動力伝達ギヤ36を経由して、駆動輪3750

へ伝達される。駆動輪 3 7 に伝達されたトルクにより電動車両が走行する。また、モータジェネレータ 3 5 は、電動車両の回生制動時には、駆動輪 3 7 の回転力によって発電する。この発電電力は、インバータ 3 2 によって A C / D C 変換される。この直流電力は、電源システム 5 A に含まれる直流電源 B 1 , B 2 の充電電力として用いることができる。なお、図 2 の構成例は、出力電圧 V H は、モータジェネレータ 3 5 に生じる誘起電圧よりも高い電圧に制御することが必要である。

#### 【 0 0 3 1 】

モータジェネレータの他にエンジン（図示せず）が搭載されたハイブリッド自動車では、このエンジンおよびモータジェネレータ 3 5 を協調的に動作させることによって、電動車両に必要な車両駆動力が発生される。この際には、エンジンの回転による発電電力を用いて直流電源 B 1 , B 2 を充電することも可能である。10

#### 【 0 0 3 2 】

このように、電動車両は、走行用電動機を搭載する車両を包括的に示すものであり、エンジンおよび電動機により車両駆動力を発生するハイブリッド自動車と、エンジンを搭載しない電気自動車および燃料電池車との両方を含むものである。

#### 【 0 0 3 3 】

再び図 1 を参照して、電力変換器 5 0 は、電力用半導体スイッチング素子 S 1 ~ S 4 と、リクトル L 1 , L 2 とを含む。本実施の形態において、電力用半導体スイッチング素子（以下、単に「スイッチング素子」とも称する）としては、I G B T ( Insulated Gate Bipolar Transistor ) 、電力用 M O S ( Metal Oxide Semiconductor ) トランジスタあるいは電力用バイポーラトランジスタ等を用いることができる。スイッチング素子 S 1 ~ S 4 に対しては、逆並列ダイオード D 1 ~ D 4 が配置されている。20

#### 【 0 0 3 4 】

スイッチング素子 S 1 ~ S 4 は、制御装置 4 0 からの制御信号 S G 1 ~ S G 4 に応答して、オンオフを制御することが可能である。すなわち、スイッチング素子 S 1 ~ S 4 は、制御信号 S G 1 ~ S G 4 が論理ハイレベル（以下、「H レベル」）のときにオンする一方で、論理ローレベル（以下、「L レベル」）のときにオフする。

#### 【 0 0 3 5 】

スイッチング素子 S 1 は、電力線 P L およびノード N 1 の間に電気的に接続される。リクトル L 2 および直流電源 B 2 は、ノード N 1 とノード N 3 との間に直列に、電気的に接続される。たとえば、リクトル L 2 は、ノード N 1 と直流電源 B 2 の正極端子との間に電気的に接続されるとともに、直流電源 B 2 の負極端子は、ノード N 3 と電気的に接続される。30

#### 【 0 0 3 6 】

スイッチング素子 S 2 は、ノード N 1 および N 2 の間に電気的に接続される。リクトル L 1 および直流電源 B 1 は、ノード N 2 および電力線 G L の間に直列に、電気的に接続される。たとえば、リクトル L 1 は、直流電源 B 1 の正極端子およびノード N 1 の間に電気的に接続されるとともに、直流電源 B 1 の負極端子は、電力線 G L と電気的に接続される。

#### 【 0 0 3 7 】

スイッチング素子 S 3 は、ノード N 2 および N 3 の間に電気的に接続される。スイッチング素子 S 4 は、ノード N 3 および電力線 G L の間に電気的に接続される。電力線 G L は、負荷 3 0 および、直流電源 B 1 の負極端子と電気的に接続される。40

#### 【 0 0 3 8 】

制御装置 4 0 は、たとえば、図示しない C P U ( Central Processing Unit ) およびメモリを有する電子制御ユニット（ E C U ）によって構成される。制御装置 4 0 は、メモリに記憶されたマップおよびプログラムに基づいて、各センサによる検出値を用いた演算処理を行なうように構成される。あるいは、制御装置 4 0 の少なくとも一部は、電子回路等のハードウェアにより所定の数値・論理演算処理を実行するように構成されてもよい。

#### 【 0 0 3 9 】

10

20

30

40

50

制御装置 40 は、出力電圧 V H を制御するために、スイッチング素子 S 1 ~ S 4 のオンオフを制御する制御信号 S G 1 ~ S G 4 を生成する。

#### 【 0 0 4 0 】

なお、図 1 では図示を省略しているが、直流電源 B 1 の電圧（以下、V [ 1 ] と表記する）および電流（以下、I [ 1 ] と表記する）、直流電源 B 2 の電圧（以下、V [ 2 ] と表記する）および電流（以下、I [ 2 ] と表記する）、ならびに、出力電圧 V H の検出器（電圧センサ、電流センサ）が設けられている。これらの検出器の出力は、制御装置 40 へ与えられる。

#### 【 0 0 4 1 】

図 1 の構成において、電力線 P L は「第 1 の電力線」に対応し、電力線 G L は「第 2 の電力線」に対応する。さらに、スイッチング素子 S 1 ~ S 4 は、「第 1 のスイッチング素子」～「第 4 のスイッチング素子」にそれぞれ対応し、リアクトル L 1 および L 2 は、「第 1 のリアクトル」および「第 2 のリアクトル」にそれぞれ対応する。10

#### 【 0 0 4 2 】

（パラレル昇圧モードでの回路動作）

次に、電力変換器 50 のパラレル昇圧モードでの制御動作について説明する。パラレル昇圧モードは、特許文献 1 での「パラレル接続モード」と同等である。

#### 【 0 0 4 3 】

図 1 を参照して、電力変換器 50 は、直流電源 B 1 および直流電源 B 2 の各々に対応して昇圧チョッパ回路を備えた構成となっている。すなわち、直流電源 B 1 に対しては、スイッチング素子 S 1, S 2 を上アームとする一方で、スイッチング素子 S 3, S 4 を下アームとする電流双方向の第 1 の昇圧チョッパ回路が構成される。直流電源 B 2 に対しては、スイッチング素子 S 1, S 4 を上アームとする一方で、スイッチング素子 S 2, S 3 を下アームとする電流双方向の第 2 の昇圧チョッパ回路が構成される。20

#### 【 0 0 4 4 】

図 3 および図 4 には、電力変換器 50 の電流変換回路が示される。図 3 には、直流電源 B 1 およびリアクトル L 1 に対する第 1 の昇圧チョッパ回路での電流経路が示され、図 4 には、直流電源 B 2 およびリアクトル L 2 に対する第 2 の昇圧チョッパ回路での電流経路が示される。

#### 【 0 0 4 5 】

図 3 ( a ) を参照して、第 1 の昇圧チョッパ回路の下アームを構成するスイッチング素子 S 3, S 4 がオンすると、直流電源 B 1 からの電流によってリアクトル L 1 にエネルギーを蓄積する電流経路 120 が形成される。すなわち、直流電源 B 1 に対しては、電力線 P L および G L を含まずに、直流電源 B 1 およびリアクトル L 1 を含むループ状の電流経路 120 が形成される。電流経路 120 は「第 1 の電流経路」に対応する。30

#### 【 0 0 4 6 】

図 3 ( b ) を参照して、スイッチング素子 S 3, S 4 をオフするとともにスイッチング素子 S 1, S 2 をオンすると、ダイオード D 1, D 2 ( または、スイッチング素子 S 1, S 2 ) を経由して、リアクトル L 1 に蓄積されたエネルギーおよび直流電源 B 1 からのエネルギーを、電力変換器 50 から負荷 30 へ供給する電流経路 121 を形成することができる。すなわち、直流電源 B 1 に対して、電力線 P L および G L の間に直流電源 B 1 およびリアクトル L 1 を直列に接続される電流経路 121 が形成される。電流経路 121 は「第 2 の電流経路」に対応する。40

#### 【 0 0 4 7 】

なお、図 3 ( b ) の回路状態では、第 1 の昇圧チョッパ回路の上アームを構成するスイッチング素子 S 1, S 2 をオンすることによって、回生電流（電流経路 121 の逆方向電流）についても経路を確保することができる。すなわち、スイッチング素子 S 1, S 2 をオンすることにより、スイッチングパターンを切換えることなく、力行電流（B 1 の放電）および回生電流（B 1 の充電）の両方に対応することができる。

#### 【 0 0 4 8 】

10

20

30

40

50

直流電源B1からの出力は、下アームのオンにより電流経路120が形成される期間（下アームオン期間）と、上アームのオンにより電流経路121が形成される期間（上アームオン期間）とが交互に繰り返されることによって制御される。以下では、下アームオン期間および上アームオン期間の和（すなわち、スイッチング周期）に対する、下アームオン期間の時比率を「デューティ比」とも称する。

#### 【0049】

図4(a)を参照して、第2の昇圧チョッパ回路の下アームを構成するスイッチング素子S2,S3がオンすると、直流電源B2からの電流によってリアクトルL2にエネルギーを蓄積する電流経路130が形成される。すなわち、直流電源B2に対して、電力線PLおよびGLを含まずに、直流電源B1およびリアクトルL1を含むループ状の電流経路130が形成される。電流経路130は「第3の電流経路」に対応する。10

#### 【0050】

図4(b)を参照して、スイッチング素子S2,S3をオフするとともにスイッチング素子S1,S4をオンすると、ダイオードD1,D4（または、スイッチング素子S1,S4）を経由して、リアクトルL2に蓄積されたエネルギーおよび直流電源B2からのエネルギーを、電力変換器50から負荷30へ供給する電流経路131を形成することができる。すなわち、直流電源B2に対しては、電力線PLおよびGLの間に直流電源B2およびリアクトルL2を直列に接続される電流経路131が形成される。電流経路131は「第4の電流経路」に対応する。

#### 【0051】

なお、図4(b)の回路状態では、第2の昇圧チョッパ回路の上アームを構成するスイッチング素子S1,S4をオンすることによって、回生電流（電流経路131の逆方向電流）についても経路を確保することができる。すなわち、スイッチング素子S1,S4をオンすることにより、スイッチングパターンを切換えることなく、力行電流（B2の放電）および回生電流（B2の充電）の両方に対応することができる。20

#### 【0052】

直流電源B2からの出力についても、電流経路130が形成される下アームオン期間と、電流経路131が形成される上アームオン期間とが交互に繰り返されることによって制御される。

#### 【0053】

このように、第1および第2の昇圧チョッパ回路を並列動作させると（パラレル昇圧モード）には、第1の昇圧チョッパ回路によって直流電源B1および電力線PL,GLの間に形成される第1の電力変換経路と、第2の昇圧チョッパ回路によって直流電源B2および電力線PL,GLの間に形成される第2の電力変換経路との両方に、スイッチング素子S1～S4の各々が含まれる。ここで、上記第1の電力変換経路は、リアクトルL1を流れるリアクトル電流IL1の経路に相当し、上記第2の電力変換経路は、リアクトルL2を流れるリアクトル電流IL2の経路に相当する。なお、リアクトル電流IL1は直流電源B1の電流I[1]に相当し、リアクトル電流IL2は直流電源B2の電流I[2]に相当する。30

#### 【0054】

##### （パラレル昇圧モードでの制御動作）

図5は、本実施の形態に従う電源システムにおける電力変換器制御のための機能ブロック図である。なお、図5を始めとする以下の機能ブロック図中に示される各ブロックの機能は、制御装置40において、所定のプログラムの実行によるソフトウェア処理および/または専用の電子回路等によるハードウェア処理によって実現されるものとする。

#### 【0055】

図5を参照して、制御装置40は、直流電源B1の出力を制御するための出力制御部500と、直流電源B2の出力を制御するための出力制御部510とを有する。出力制御部500は、直流電源B1のデューティ比DT1を生成する。出力制御部510は、直流電源B2のデューティ比DT2を出力する。40

## 【0056】

たとえば、出力制御部500は、直流電源B1の出力を、出力電圧VHを電圧指令値VH\*に設定するように制御する。出力制御部500は、偏差演算部502と、PI制御部505と、加算部507とを有する。

## 【0057】

偏差演算部502は、電圧指令値VH\*に対する出力電圧VHの電圧偏差VH( $VH = VH^* - VH$ )を算出する。PI制御部505は、電圧偏差VHに対するPI(比例積分)制御によってフィードバック制御量を設定する。加算部507は、PI制御部505からのフィードバック制御量と、フィードフォワード制御量Dff1とを加算してデューティ比DT1を算出する。

10

## 【0058】

フィードフォワード制御量Dff1は、出力電圧VHと直流電源B1の電圧V[1]との電圧比により(1)式に従って設定される。すなわち、Dff1は、昇圧チョッパ回路の理論昇圧比に従って設定されるデューティ比を示している。

## 【0059】

$$Dff1 = 1 - (V[1] / VH^*) \quad \dots (1)$$

このように、直流電源B1からの出力を制御するためのデューティ比DT1は、直流電圧VHに対する直流電源B1の電圧V[1]の比が低くなる程、大きく設定されることが理解される。

## 【0060】

たとえば、出力制御部510は、直流電源B2の出力を、電流指令値Io\*に従って制御する。出力制御部510は、偏差演算部512と、PI制御部515と、加算部517とを有する。

20

## 【0061】

特許文献1にも記載されるように、パラレル昇圧モードでは、直流電源B1,B2間の電力配分を制御することができるので、出力制御部510によって制御される直流電源B2について電力指令値P2\*を設定することができる。これにより、電力変換器50から負荷30へ入出力される合計電力に対する、直流電源B1,B2間の配分を制御することが可能となる。このとき、図5の構成例では、電流指令値Io\* = P2\* / V[2]により設定することができる。

30

## 【0062】

偏差演算部512は、電流指令値Io\*に対する電流Ioの電流偏差Io( $Io = Io^* - Io$ )を算出する。たとえば、図5のように、直流電源B2を電流制御する構成では、電流Io = I[2]である。

## 【0063】

PI制御部515は、電流偏差Ioに対するPI(比例積分)制御によってフィードバック制御量を設定する。加算部517は、PI制御部515からのフィードバック制御量と、フィードフォワード制御量Dff2とを加算してデューティ比DT2を算出する。

## 【0064】

フィードフォワード制御量Dff2は、出力電圧VHと直流電源B2の電圧V[2]との電圧比により(2)式に従って設定される。すなわち、Dff2は、昇圧チョッパ回路の理論昇圧比に従って設定されるデューティ比を示している。

40

## 【0065】

$$Dff2 = 1 - (V[2] / VH^*) \quad \dots (2)$$

このように、直流電源B2からの出力を制御するためのデューティ比DT2は、定性的には、直流電圧VHに対する直流電源B2の電圧V[2]の比が低くなる程、大きく設定されることが理解される。

## 【0066】

なお、直流電源B1およびB2の出力制御は、図5での例示に限定されず、デューティ比DT1, DT2の算出は、出力電圧VHを電圧指令値VH\*に制御する機能を有する限

50

り、任意の態様で実行することができる。

#### 【0067】

アレンジの一例として、出力電圧  $V_H$  を電圧指令値  $V_H^*$  に制御するために電力変換器 50 から入出力される必要電力  $P_r$  の算出に基づいて、直流電源 B1, B2 の出力を電力制御（電流制御）することも可能である。具体的には、当該必要電力  $P_r$  を直流電源 B1, B2 の間で配分した電力指令値  $P_1^*$ ,  $P_2^*$  に従って、直流電源 B1 および B2 の出力電力を制御することが可能である ( $P_r = P_1^* + P_2^*$ )。パラレル昇圧モードでは、電力指令値  $P_1^*$ ,  $P_2^*$  間の配分を自由にすることができます。

#### 【0068】

この場合には、図 5 の制御構成において、出力制御部 500, 510 は、電力指令値  $P_1^*$ ,  $P_2^*$  から求められた、電流指令値  $I_1^*$  ( $I_1^* = P_1^* / V[1]$ ) および  $I_2^*$  ( $I_2^* = P_2^* / V[2]$ ) を基準値とする電流  $I[1]$ ,  $I[2]$  のフィードバック制御によって、デューティ比  $D_T 1$ ,  $D_T 2$  を算出することができます。10

#### 【0069】

キャリア波発生部 560 は、直流電源 B1 の制御に用いるキャリア波 CW1 および直流電源 B2 の制御に用いる CW2 を発生する。キャリア波 CW1 および CW2 は、スイッチング周波数に相当する同一周波数を有する。PWM 制御部 550 は、デューティ比  $D_T 1$ ,  $D_T 2$  およびキャリア波 CW1, CW2 から、電力変換器 50 のスイッチング素子 S1 ~ S4 を制御するための制御信号 SG1 ~ SG4 を生成する。20

#### 【0070】

##### ( PWM 制御の詳細 )

電力変換器 50 のパラレル昇圧モードにおける基本的な制御動作は、特許文献 1 のパラレル昇圧モードでの制御動作と同等である。さらに、特許文献 1 には、リアクトル電流の位相調整によってスイッチング素子 S1 ~ S4 での電力損失を低減するための手法として、直流電源 B1 および直流電源 B2 の PWM 制御にキャリア波の位相制御（以下、「キャリア位相制御」とも称する）を適用することが記載されている。20

#### 【0071】

本実施の形態に従う電源システムの電力変換器に対する PWM 制御に対する比較例として、まず、当該キャリア位相制御について説明する。

#### 【0072】

##### ( 1 ) キャリア位相制御の適用

図 6 は、比較例として示されるキャリア位相制御が適用されたパラレル制御モードでの動作例を説明する波形図である。30

#### 【0073】

図 6 を参照して、キャリア位相制御では、直流電源 B1 の PWM 制御に用いられるキャリア波 CW1 と、直流電源 B2 の PWM 制御に用いられるキャリア波 CW2 とには、同一周波数の三角波が用いられる。

#### 【0074】

キャリア波 CW1, CW2 の周期は、各スイッチング素子のスイッチング周波数に相当する。キャリア波 CW1, CW2 の電圧幅（ピクトゥピーク）は、デューティ比  $D_T 1 = 1.0$  および  $D_T 2 = 1.0$  に対応する電圧に設定される。40

#### 【0075】

直流電源 B1 の出力を制御するためのデューティ比  $D_T 1$  と、キャリア波 CW1 との電圧比較に基づいて、制御パルス信号 SD1 が生成される。制御パルス信号 SD1 は、デューティ比  $D_T 1$  を示す電圧が、キャリア波 CW1 の電圧よりも高いときに H レベルに設定される一方で、キャリア波 CW1 の電圧よりも低いときに L レベルに設定される。制御パルス信号 SD1 の周期（H レベル期間 + L レベル期間）に対する H レベル期間の比、すなわち、制御パルス信号 SD1 のデューティ比は、 $D_T 1$  と同等である。

#### 【0076】

制御パルス信号 / SD1 は、制御パルス信号 SD1 の反転信号である。デューティ比 D50

T 1 が高くなると、制御パルス信号 S D 1 の H レベル期間が長くなる。反対に、デューティ比 D T 1 が低くなると、制御パルス信号 S D 1 の L レベル期間が長くなる。

#### 【 0 0 7 7 】

制御パルス信号 S D 1 は、上述した第 1 の昇圧チョッパ回路の下アーム（スイッチング素子 S 3 , S 4 ）のオンオフを制御する信号に対応する。一方、制御パルス信号 / S D 1 は、第 1 の昇圧チョッパ回路の上アーム（スイッチング素子 S 1 , S 2 ）のオンオフを制御する信号に対応する。

#### 【 0 0 7 8 】

同様に、直流電源 B 2 の出力を制御するためのデューティ比 D T 2 と、キャリア波 C W 2 との電圧比較に基づいて、制御パルス信号 S D 2 および、その反転信号 / S D 2 が生成される。制御パルス信号 S D 2 のデューティ比は D T 2 と同様であり、制御パルス信号 / S D 2 のデューティ比は ( 1 . 0 - D T 2 ) と同等である。すなわち、デューティ比 D T 2 が高くなると、制御パルス信号 S D 2 の H レベル期間が長くなり、反対に、デューティ比 D T 2 が低くなると、制御パルス信号 S D 2 の L レベル期間が長くなる。

#### 【 0 0 7 9 】

制御パルス信号 S D 2 は、上述した第 2 の昇圧チョッパ回路の下アーム（スイッチング素子 S 2 , S 3 ）のオンオフを制御する信号に対応する。一方、制御パルス信号 / S D 2 は、第 2 の昇圧チョッパ回路の上アーム（スイッチング素子 S 1 , S 4 ）のオンオフを制御する信号に対応する。

#### 【 0 0 8 0 】

制御信号 S G 1 ~ S G 4 は、特許文献 1 に記載されるように、制御パルス信号 S D 1 ( / S D 1 ) および S D 2 ( / S D 2 ) の論理演算に基づいて設定される。

#### 【 0 0 8 1 】

具体的には、スイッチング素子 S 1 は、第 1 の昇圧チョッパ回路（図 3 ）および第 2 の昇圧チョッパ回路（図 4 ）の各々で上アームを形成するので、制御信号 S G 1 は、制御パルス信号 / S D 1 および制御パルス信号 / S D 2 の論理和によって生成される。

#### 【 0 0 8 2 】

スイッチング素子 S 2 は、第 1 の昇圧チョッパ回路（図 3 ）では上アームを形成し、第 2 の昇圧チョッパ回路（図 4 ）では下アームを形成する。したがって、制御信号 S G 2 は、制御パルス信号 / S D 1 および制御パルス信号 / S D 2 の論理和によって生成される。

#### 【 0 0 8 3 】

同様にして、スイッチング素子 S 3 は、第 1 の昇圧チョッパ回路（図 3 ）および第 2 の昇圧チョッパ回路（図 4 ）の両方で下アームを形成するので、制御信号 S G 3 は、制御パルス信号 S D 1 および制御パルス信号 / S D 2 の論理和によって生成される。

#### 【 0 0 8 4 】

また、スイッチング素子 S 4 は、第 1 の昇圧チョッパ回路（図 3 ）では下アームを形成し、第 2 の昇圧チョッパ回路（図 4 ）では上アームを形成するので、制御信号 S G 4 は、制御パルス信号 S D 1 および制御パルス信号 / S D 2 の論理和によって生成される。

#### 【 0 0 8 5 】

制御信号 S G 1 ~ S G 4 に基づいてスイッチング素子 S 1 ~ S 4 をオンオフすることにより、リクトル電流 I L 1 および I L 2 が図 6 に示すように制御される。リクトル電流 I L 1 は直流電源 B 1 の電流 I [ 1 ] に相当し、リクトル電流 I L 2 は直流電源 B 2 の電流 I [ 2 ] に相当する。すなわち、リクトル電流 I L 1 および I L 2 の平均値は、デューティ比 D T 1 および D T 2 によってそれぞれ制御される。

#### 【 0 0 8 6 】

一方で、キャリア波 C W 1 , C W 2 を構成する三角波の間の位相差 を変化させることにより、電流平均値を変えることなく、リクトル電流 I L 1 およびリクトル電流 I L 2 の位相関係（電流位相）が変化する。したがって、キャリア位相制御によって、キャリア波 C W 1 , C W 2 間の位相差 を適切に調整することにより、電力変換器 5 0 のパラレル昇圧モードにおける、スイッチング素子 S 1 ~ S 4 の電力損失を低減することができる

10

20

30

40

50

。

**【0087】**

以下では、代表的な例として、直流電源B1およびB2の両方が力行状態、すなわちリクトル電流IL1>0かつリクトル電流IL2>0である状態での制御について説明する。

**【0088】**

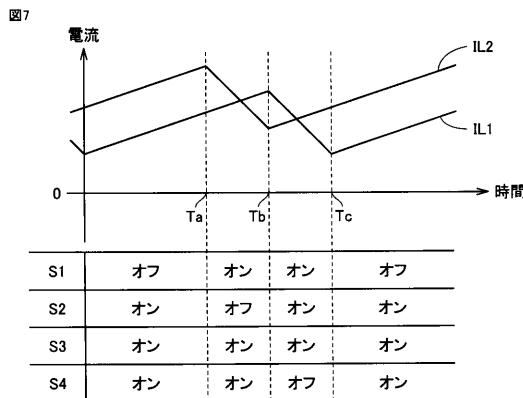

図7は、パラレル昇圧モードにおけるキャリア位相制御の動作例を説明するための電流波形図である。図8は、図7の所定期間における電力変換器50での電流経路を説明する回路図である。

**【0089】**

図7を参照して、時刻Taまでは、スイッチング素子S2～S4がオンされるので、直流電源B1,B2の両方に対して、昇圧チョッパ回路の下アーム（第1および第3の電流経路）がオンされた状態となる。このため、リクトル電流IL1およびIL2の両方は上昇する。

**【0090】**

時刻Taにおいて、スイッチング素子S2がターンオフされることにより、直流電源B2に対して昇圧チョッパ回路の下アーム（第3の電流経路）がオフされた状態となるので、リクトル電流IL2が上昇から下降に転じる。すなわち、リクトル電流IL2は極大となる。スイッチング素子S2のターンオフと入替わりに、スイッチング素子S1がターンオンされる。

**【0091】**

時刻Ta以降では、直流電源B1に対して昇圧チョッパ回路の下アーム（第1の電流経路）がオンされ、直流電源B2に対して昇圧チョッパ回路の下アームがオフされた状態となる。すなわち、リクトル電流IL2が上昇する一方で、リクトル電流IL1が下降する。このとき、電力変換器50での電流経路は、図8(a)のようになる。

**【0092】**

図8(a)から理解されるように、時刻Ta以降では、スイッチング素子S4には、リクトル電流IL1およびIL2の差電流が通過することになる。すなわち、スイッチング素子S4の通過電流が小さくなる。

**【0093】**

再び図7を参照して、時刻Tb以降の状態から、スイッチング素子S4がターンオフすると、直流電源B1に対して昇圧チョッパ回路の下アームがオフされた状態となるので、リクトル電流IL1が上昇から下降に転じる。すなわち、リクトル電流IL1は極大となる。また、スイッチング素子S2がターンオンすると、直流電源B2に対して昇圧チョッパ回路の下アームがオンされた状態となるので、リクトル電流IL2が再び下降から上昇に転じる。すなわち、リクトル電流IL2は極小となる。

**【0094】**

これにより、電力変換器50での電流経路が、図8(a)の状態から、図8(b)の状態に変化する。図8(b)の状態では、スイッチング素子S2には、リクトル電流IL1およびIL2の差電流が通過することになるため、スイッチング素子S2の通過電流が小さくなる。

**【0095】**

さらに、図8(a)の状態でスイッチング素子S4をターンオフさせることにより、スイッチング素子S4のターンオフ時の電流が低減してソフトスイッチングとなり、スイッチング損失を低減できる。また、図8(b)の状態でスイッチング素子S2をターンオンさせることにより、スイッチング素子S2のターンオン時の電流が低減してソフトスイッチングとなり、スイッチング損失を低減できる。

**【0096】**

したがって、図7に示されるように、リクトル電流IL1が上昇から下降に転じるタイミングと、リクトル電流IL2が下降から上昇に転じるタイミングとが一致するよう

10

20

30

40

50

に、電流位相、すなわち、キャリア波 C W 1 , C W 2 の位相差  $\phi$  を調整する。すなわち、リアクトル電流 I L 1 の変曲点（極大点）と、リアクトル電流 I L 2 の変曲点（極小点）とが同一タイミングとなるように位相差  $\phi$  を調整する。これにより、図 7 の時刻 T b において、スイッチング素子 S 2 がターンオンされるとともに、スイッチング素子 S 4 がターンオフされる。

#### 【 0 0 9 7 】

再び図 7 を参照して、時刻 T c では、スイッチング素子 S 1 がターンオフされるとともに、スイッチング素子 S 4 がターンオンされる。これにより、直流電源 B 1 に対して昇圧チョッパ回路の下アームがオフされた状態となるので、リアクトル電流 I L 1 が下降から上昇に転じる。すなわち、リアクトル電流 I L 2 は極小となる。スイッチング素子 S 2 のターンオフと入替わりに、スイッチング素子 S 1 がターンオンされることにより、直流電源 B 1 , B 2 の各々に対して昇圧チョッパ回路の下アームがオンされた状態となる。したがって、上述した時刻 T a 以前の状態が再現されて、リアクトル電流 I L 1 および I L 2 の両方が上昇する。

#### 【 0 0 9 8 】

このように、直流電源 B 1 および B 2 の両方が力行状態であるときには、リアクトル電流 I L 1 の極大点と、リアクトル電流 I L 2 の極小点とが図中の時刻 T b で重なるような電流位相となるように、キャリア波 C W 1 , C W 2 間の位相差  $\phi$  を調整する。これにより、時刻 T b におけるスイッチング素子 S 2 のターンオン損失およびスイッチング素子 S 4 のターンオフ損失を低減できる。

#### 【 0 0 9 9 】

このように、図 6 における  $\phi = \phi^*$  となるように位相差  $\phi$  を最適化することで、スイッチング素子 S 1 ~ S 4 での損失を低減するように、リアクトル電流 I L 1 , I L 2 の位相を制御することができる。

#### 【 0 1 0 0 】

図 6 から理解されるように、このような位相差  $\phi^*$  では、制御パルス信号 S D 1 の立下りタイミング（または立上りタイミング）と、制御パルス信号 S D 2 の立上りタイミング（または立下りタイミング）とが重なることになる。

#### 【 0 1 0 1 】

制御パルス信号 S D 1 , S D 2 の波形は、デューティ比 D T 1 , D T 2 によって変化する。したがって、キャリア位相制御による最適な位相差  $\phi^*$  についても、デューティ比 D T 1 , D T 2 に応じて変化する。このため、特許文献 1 のキャリア位相制御では、デューティ比 D T 1 , D T 2 と、最適な位相差  $\phi^*$  との関係を予め求めるとともに、その対応関係に従って、デューティ比 D T 1 , D T 2 が変化する毎に位相差  $\phi$  を変化させる必要がある。この結果、キャリア位相制御のための制御装置 4 0 での演算負荷が大きくなる点が課題となる。

#### 【 0 1 0 2 】

もし、演算負荷の影響で位相差  $\phi$  の制御が遅れると、リアクトル電流 I L 1 , I L 2 の挙動が不安定になることが懸念される。あるいは、制御装置 4 0 のスペックに従って P W M 制御の制御周期が制約を受ける虞がある。反対に、P W M 制御の制御周期を確保するために、制御装置 4 0 に高いスペックが要求される可能性もある。

#### 【 0 1 0 3 】

また、特許文献 1 にも記載されるように、リアクトル電流 I L 1 , I L 2 の好ましい位相関係は、たとえば、直流電源 B 1 , B 2 が力行（放電）/回生（充電）のいずれで動作しているか、すなわち、電力変換器 5 0 のリアクトル電流 I L 1 , I L 2 の方向（正／負）の組み合わせに応じて異なる。

#### 【 0 1 0 4 】

図 9 は、リアクトル電流の方向に応じた電流位相の制御例を説明するための図表である。

#### 【 0 1 0 5 】

10

20

30

40

50

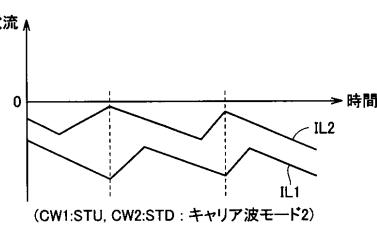

図9を参照して、リアクトル電流が  $I_L 1 > 0$ ,  $I_L 2 > 0$  である状態Aでは、上述した、直流電源B1およびB2の両方が力行状態である。この場合には、図6～8で説明したように、リアクトル電流については  $I_L 1$  の極大点(山)と、 $I_L 2$  の極小点(谷)とが同一タイミングとなる電流位相(以下、「位相パターンA」とも称する)とすることにより、スイッチング素子S1～S4での電力損失を減少できる。

#### 【0106】

同様に、リアクトル電流が  $I_L 1 < 0$ ,  $I_L 2 < 0$  である状態Bでは、直流電源B1およびB2の両方が回生状態である。この場合には、リアクトル電流  $I_L 1$ ,  $I_L 2$  の方向が状態Aと逆になるため、 $I_L 1$  の極小点(谷)と、 $I_L 2$  の極大点(山)とが同一タイミングとなる電流位相(以下、「位相パターンB」とも称する)とすることにより、スイッチング素子S1～S4での電力損失を減少できる。10

#### 【0107】

また、リアクトル電流が  $I_L 1 < 0$ ,  $I_L 2 > 0$  である状態Cでは、直流電源B1が回生状態である一方で、直流電源B2は力行状態である。この状態では、 $I_L 1$  の極大点(山)と、 $I_L 2$  の極大点(山)とが同一タイミングとなる電流位相(以下、「位相パターンC」とも称する)とすることにより、スイッチング素子S1～S4での電力損失を減少できる。

#### 【0108】

同様に、リアクトル電流が  $I_L 1 > 0$ ,  $I_L 2 < 0$  である状態Dでは、直流電源B1が力行状態である一方で、直流電源B2は回生状態である。この状態では、 $I_L 1$  の極小点(谷)と、 $I_L 2$  の極小点(谷)とが同一タイミングとなる電流位相(以下、「位相パターンD」とも称する)とすることにより、スイッチング素子S1～S4での電力損失を減少できる。20

#### 【0109】

このように、電力変換器50の動作状態の1つである、リアクトル電流  $I_L 1$ ,  $I_L 2$  の方向(正/負)に応じて、スイッチング素子S1～S4での電力損失を減少するための好ましい電流位相が、上記4パターンの間で変化する。

#### 【0110】

また、リアクトル電流  $I_L 1$ ,  $I_L 2$  の方向(正/負)の同一の組み合わせに対して、上記4パターンの電流位相を適用すると、各スイッチング素子S1～S4での電力損失、すなわち、発熱量が変化することが理解される。したがって、時分割で電流位相のパターンを切換えると、スイッチング素子S1～S4間で発熱量を均一化できる可能性がある。この場合には、電力変換器50の動作状態の1つである、スイッチング素子S1～S4の温度に応じて、好ましい電流位相が上記4パターンの間で変化する。30

#### 【0111】

したがって、電源システム5Aの動作中において、電力変換器50の動作状態に応じて、リアクトル電流  $I_L 1$ ,  $I_L 2$  の位相を位相パターンA～Dの間で切り替える電流位相制御によって、電力損失低減による高効率化、あるいは、素子温度抑制による高出力化を通じて電源システム5Aの性能を向上することができる。

#### 【0112】

しかしながら、三角波のキャリア位相制御によって上記電流位相制御を行うと、パターン切替えの際には、キャリア位相差の変化が大きくなる。このため、上述した演算負荷の高さの影響も考慮すれば、リアクトル電流の過渡的な挙動が不安定となって、電流変動が過大となることが懸念される。40

#### 【0113】

##### (2) 本実施の形態に従うPWM制御

上記のような、キャリア位相制御による問題点を解決するために、本実施の形態では、以下に説明するように、のこぎり波をキャリア波として用いるPWM制御によって、リアクトル電流  $I_L 1$ ,  $I_L 2$  の電流位相のパターン切替えを伴う電流位相制御を実現する。

#### 【0114】

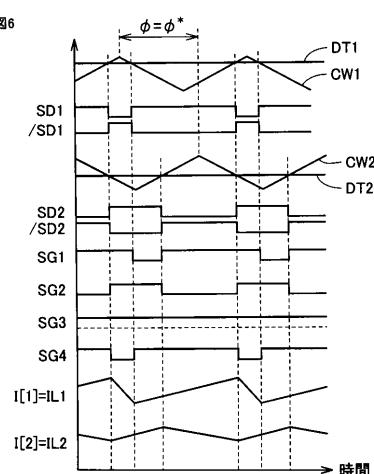

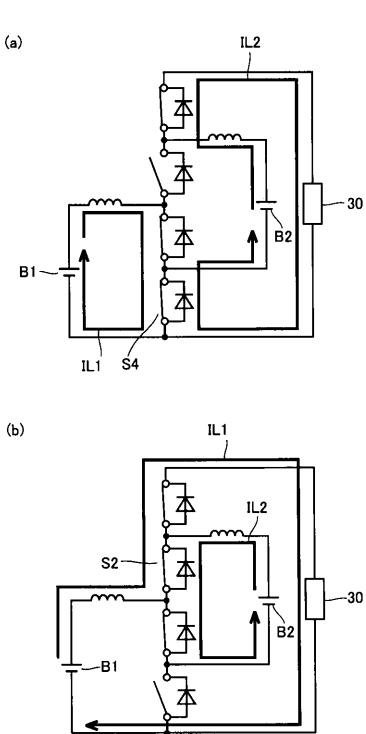

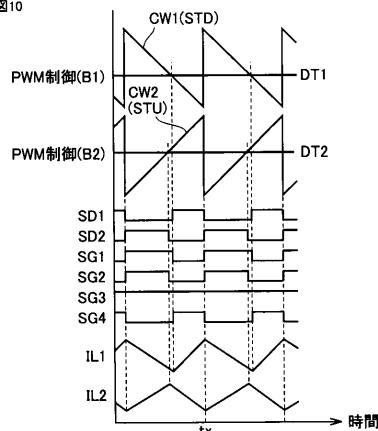

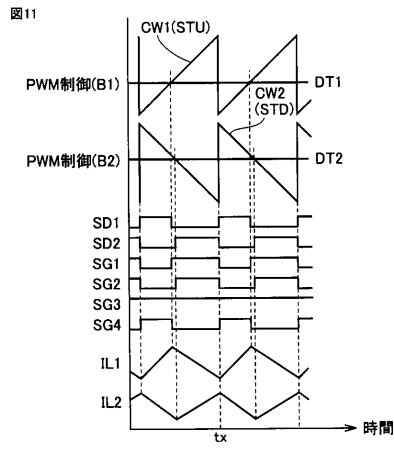

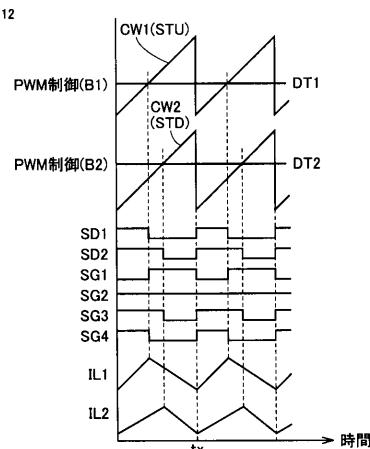

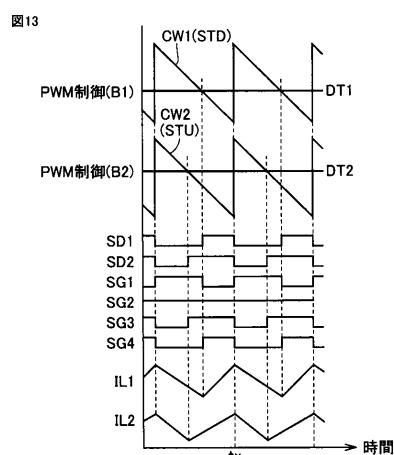

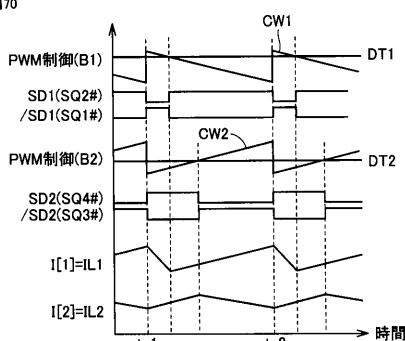

図10～図13は、本実施の形態に従う電源システムで適用されるPWM制御のキャリア波モードを説明するための波形図である。

#### 【0115】

図10～図13を参照して、本実施の形態に従う電源システムでは、同一周波数で位相（エッジタイミング）が同期した2つのこぎり波によって、キャリア波CW1およびCW2を構成する。図10～図13では、キャリア波CW1およびCW2以外については、図6と同様である。すなわち、制御パルス信号SD1, SD2に基づくスイッチング素子S1～S4のオンオフ制御は、図6と同様に実行される。

#### 【0116】

のこぎり波には、右下り形状および右上り形状の2種類の波形が存在する。したがって、図14に示されるように、のこぎり波の波形の組み合わせによって、キャリア波CW1, CW2には4個のモードが存在することが理解される。図10～図13には、図14に示されたキャリア波モード1～4のそれぞれのときのPWM波形が示される。

#### 【0117】

図10を参照して、キャリア波モード1では、キャリア波CW1が右下り形状ののこぎり波STDによって構成される、キャリア波CW2は右上り形状ののこぎり波STUによって構成される。

#### 【0118】

図6で説明したのと同様に、制御パルス信号SD1は、キャリア波CW1およびデューティ比DT1の電圧比較に従って生成される。同様に、制御パルス信号SD2は、キャリア波CW2およびデューティ比DT2の電圧比較に従って生成される。制御パルス信号SD1, SD2に従って設定される制御信号SG1～SG4によるスイッチング素子S1～S4の制御によって、制御パルス信号SD1のHレベル期間では、リアクトル電流IL1が上昇し、制御パルス信号SD1のLレベル期間では、リアクトル電流IL1が低下する。同様に、制御パルス信号SD2のHレベル期間では、リアクトル電流IL2が上昇し、制御パルス信号SD2のLレベル期間では、リアクトル電流IL2が低下する。

#### 【0119】

キャリア波CW1およびCW2は、同一周波数でエッジタイミングが同期しているので、周期の切替わりタイミングである時刻txにおいて、制御パルス信号SD1, SD2のレベルが遷移する。このタイミングで、リアクトル電流IL1, IL2は変曲点を有することになる。すなわち、キャリア波CW1, CW2の1周期毎に、図9に示された位相パターンA～Dのように、リアクトル電流IL1, IL2の変曲点を同一タイミングとすることができます。さらに、位相パターンA～Dは、キャリア波CW1, CW2を構成するのこぎり波の波形の組み合わせによって選択することができる。

#### 【0120】

図10に示されるように、右下り形状ののこぎり波（以下、単に「下りのこぎり波」とも称する）STDによって制御されるリアクトル電流IL1は、時刻txで極大点（山）を有することになる。一方で、右上り形状ののこぎり波（以下、単に「上りのこぎり波」とも称する）STUによって制御されるリアクトル電流IL2は、時刻txで極小点（谷）を有する。したがって、キャリア波モード1を適用すれば、図9の位相パターンAを実現するように電流位相を制御できる。なお、上りのこぎり波STUは、「第1の鋸歯状波」に対応し、下りのこぎり波STDは、「第2の鋸歯状波」に対応する。

#### 【0121】

図11および図14を参照して、キャリア波モード2では、キャリア波CW1が上りのこぎり波STUによって構成される一方で、キャリア波CW2は下りのこぎり波STDによって構成される。

#### 【0122】

この結果、図10と同様の時刻txにおいて、リアクトル電流IL1が極小点（谷）を有する一方で、リアクトル電流IL2は極大点（山）を有する。したがって、図11に示されるように、キャリア波モード2を適用すれば、図9の位相パターンBを実現するよう

10

20

30

40

50

に電流位相を制御できる。

**【0123】**

図12および図14を参照して、キャリア波モード3では、キャリア波CW1およびCW2の両方が上りのこぎり波STUによって構成される。

**【0124】**

この結果、図10および図11と同様の時刻 $t_x$ において、リアクトル電流IL1およびIL2の両方が極小点(谷)を有する。したがって、図12に示されるように、キャリア波モード3を適用すれば、図9の位相パターンCを実現するように電流位相を制御できる。

**【0125】**

図13および図14を参照して、キャリア波モード4では、キャリア波CW1およびCW2の両方が下りのこぎり波STDによって構成される。

**【0126】**

この結果、図10～図12と同様の時刻 $t_x$ において、リアクトル電流IL1およびIL2の両方が極大点(山)を有する。したがって、図13に示されるように、キャリア波モード4を適用すれば、図9の位相パターンDを実現するように電流位相を制御できる。

**【0127】**

このように、本実施の形態1に従う電源システムによれば、キャリア波CW1, CW2にのこぎり波を適用することによって、リアクトル電流IL1, IL2の間で変曲点を同一タイミングに一致させる電流位相制御を、キャリア位相差の調整のような複雑な演算処理を行うことなく、簡易な制御処理で実現することができる。さらに、リアクトル電流IL1, IL2の位相パターンA～Dの選択についても、のこぎり波の波形の選択によって、簡易に実現することができる。具体的には、キャリア波発生部560(図6)が、電力変換器50の動作状態(リアクトル電流IL1, IL2の方向および/またはスイッチング素子S1～S4の温度等)に応じて、図14に示されたキャリア波モードの選択を伴ってキャリア波CW1, CW2を発生することにより、位相パターンA～Dの選択が可能となる。

**【0128】**

図1に示された電力変換器50では、スイッチング素子S1～S4のオンオフ制御に応じて、スイッチング素子S1～S4の少なくともいずれかにリアクトル電流IL1, IL2の両方が流れる。このため、図9に示された位相パターンA～Dを電力変換器50の動作状態に応じて切替える電流位相制御により、高効率化あるいは高出力化を図ることができる。

**【0129】**

したがって、図1に示された電力変換器50を含む電源システム5Aでは、本実施の形態に従うPWM制御によって直流電源B1, B2の出力を制御することによって、簡易な制御処理によって、リアクトル電流を大きく変動させることなく、性能を向上させることができる。

**【0130】**

[実施の形態1の変形例]

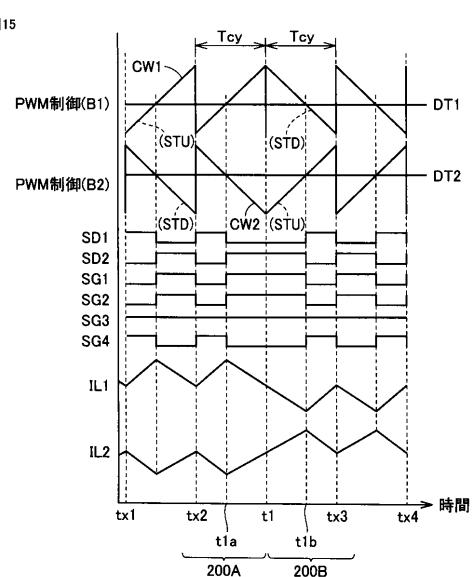

実施の形態1に従うPWM制御では、位相パターンを切替える際には、キャリア波CW1, CW2の周期間で、のこぎり波の波形を変化するためのキャリア波モードの切替えが必要である。実施の形態1の変形例では、キャリア波モードの切替え時における好ましい制御について、さらに説明する。

**【0131】**

図15は、実施の形態1に従うPWM制御でのキャリア波モードの切替え時における問題点を説明するための動作波形図である。

**【0132】**

図15を参照して、キャリア波CW1およびCW2の周期 $T_{cy}$ 毎に、リアクトル電流IL1, IL2の変曲点が同一タイミングで発生する。時刻 $t_1$ 以前では、キャリア波モ

10

20

30

40

50

ード 2 が適用されるので、時刻  $t \times 1$ ,  $t \times 2$ において、リアクトル電流  $I_L 1$  の極小点（谷）とリアクトル電流  $I_L 2$  の極大点（山）とが一致する。すなわち、電流位相は、位相パターン B に制御される。

#### 【0133】

時刻  $t_1$ において、電力変換器 50 の動作状態に応じて、位相パターン B から位相パターン A に電流位相制御が切替えられる。これに応じて、時刻  $t_1$ 以降では、キャリア波モードが切替えられる。具体的には、キャリア波 CW1 を下りのこぎり波 STD で構成し、キャリア波 CW2 を上りのこぎり波 STU で構成するキャリア波モード 1 が新たに選択される。

#### 【0134】

時刻  $t_1$ の直前の周期 200A と、時刻  $t_1$ 直後の周期 200Bとの間では、切替え時点（時刻  $t_1$ ）を挟んで、キャリア波 CW1 およびキャリア波 CW2 の両方の波形が対称となる。この結果、リアクトル電流  $I_L 1$  は、通常の 2 倍の期間にわたって低下を続けるとともに、リアクトル電流  $I_L 2$  は通常の 2 倍の期間にわたって上昇する。これにより、リアクトル電流の変動が大きくなる。

#### 【0135】

さらに、周期 200Bにおいて、デューティ比 DT1 および DT2 が変化していないにも関わらず、リアクトル電流  $I_L 1$  の平均値が低下するとともに、リアクトル電流  $I_L 2$  の平均値が上昇することが理解される。周期 200Bにおいても、直流電源 B1 および B2 の各々に対する、下アームオン期間および上アームオン期間の比は変わらないが、リアクトル電流  $I_L 1$ ,  $I_L 2$  が同一方向に連続的に変化する期間長が変化することから、平均電流が変化してしまう。

#### 【0136】

この結果、周期 200B の次の周期でも、リアクトル電流  $I_L 1$ ,  $I_L 2$  の平均値は、時刻  $t_1$ 以前から変化してしまう。以降でのフィードバック制御によってデューティ比 DT1, DT2 が調整されることによって、リアクトル電流  $I_L 1$ ,  $I_L 2$  の平均値は適正値に復帰することができるが、キャリア波モードの切替に伴って電流変動が生じることは好ましくない。

#### 【0137】

このように、キャリア波モードの切替え時に、切替え時点（時刻  $t_1$ ）を挟んでキャリア波の波形が対称形となると、リアクトル電流の過渡的な変動が大きくなることが懸念される。

#### 【0138】

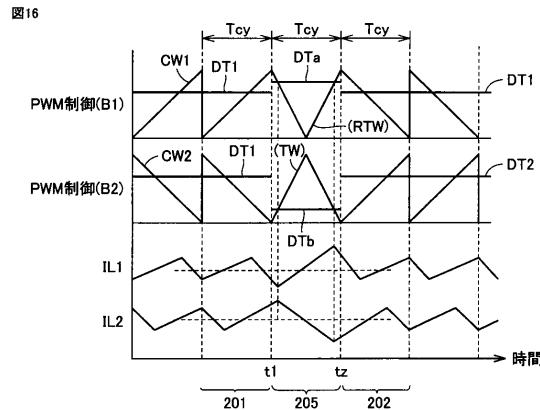

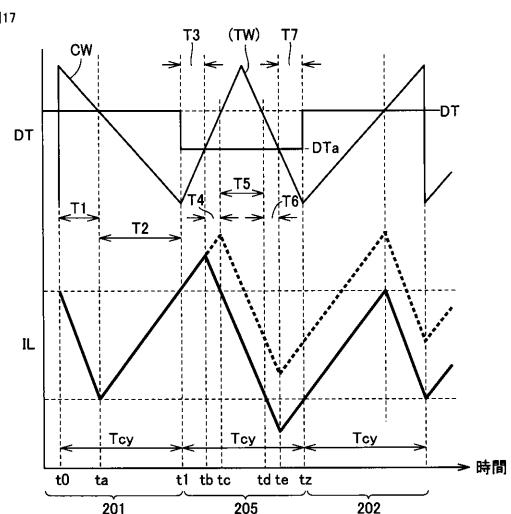

図 16 には、本実施の形態 1 の変形例に従う PWM 制御におけるキャリア波モード切替え時の第 1 の制御例を説明する波形図が示される。

#### 【0139】

図 16 を参照して、実施の形態 1 の変形例では、キャリア波モードを切替える周期 200A および 200B の間に、遷移周期 205 が設けられる。遷移周期 205 では、キャリア波モードの切替えによってのこぎり波の波形が切替えられるときには、のこぎり波と同一周期 Tcy を有する三角波 TW または逆相三角波 RTW がキャリア波に適用される。

#### 【0140】

図 16 の例では、図 15 と同様に、時刻  $t_1$ からキャリア波モード 2 からキャリア波モード 1 への切替えが行なわれる際に、下りのこぎり波 STD から上りのこぎり波 STU への切替えの際には三角波 TW がキャリア波に適用される。一方で、上りのこぎり波 STU から下りのこぎり波 STD への切替えの際には逆相三角波 RTW が適用される。このため、遷移周期 205 において、キャリア波 CW1 は逆相三角波 RTW によって構成され、キャリア波 CW2 は三角波 TW によって構成される。

#### 【0141】

三角波 TW および逆相三角波 RTW は、のこぎり波と同一周期を有するので、遷移周期 205 が適用される時刻  $t_1$  ~  $t_2$  間において、デューティ比 DT1, DT2 とキャリア

10

20

30

40

50

波 C W 1 , C W 2 との電圧高低関係が 2 回変化する。この結果、リアクトル電流 I L 1 , I L 2 にも変曲点が 2 回生じる。

#### 【 0 1 4 2 】

この結果、キャリア波モードを切替える際における、連続的な電流上昇または低下の期間が図 15 と比較して短くなる。したがって、リアクトル電流 I L 1 , I L 2 の変動を軽減することができる。

#### 【 0 1 4 3 】

一方で、三角波 T W または逆相三角波 R T W をキャリア波として適用する場合には、同一のデューティ比 D T 1 , D T 2 に対して、図 15 と同様に、リアクトル電流 I L 1 , I L 2 の平均値が変化してしまう。このため、リアクトル電流 I L 1 , I L 2 の平均値を変化させないためには、三角波 T W または逆相三角波 R T W を適用する場合にデューティ比の変換が必要となる。10

#### 【 0 1 4 4 】

図 17 は、三角波 T W をキャリア波として適用する場合におけるデューティ比変換を説明するための波形図である。

#### 【 0 1 4 5 】

図 17 には、デューティ比 D T に対して、三角波 T W が適用された遷移周期 2 0 5 における変換デューティ比 D T a の導出が示される。図 17 において、デューティ比 D T は、D T 1 および D T 2 を包括に表記するものであり、リアクトル電流 I L は、I L 1 および I L 2 を包括的に表記するものである。20

#### 【 0 1 4 6 】

変換デューティ比 D T a は、デューティ比 D T 1 に従う周期 2 0 0 A および変換デューティ比 D T a に従う遷移周期 2 0 5 の間で、リアクトル電流 I L の平均値が変わらないように設定される。

#### 【 0 1 4 7 】

図 17 を参照して、遷移周期 2 0 5 の直前の周期 2 0 0 A および直後の周期 2 0 0 B において、キャリア波 C W は、下りのこぎり波 S T D および上りのこぎり波 S T U である。周期 2 0 0 A において、時刻 t 0 ~ t a の間（期間長 T 1 ）では C W > D T であるので、リアクトル電流 I L は低下する。なお、当該期間では、リアクトル電流 I L 1 に対しては電流経路 1 2 1 ( 図 3 ( b ) ) が形成され、リアクトル電流 I L 2 に対しては電流経路 1 3 1 ( 図 4 ( b ) ) が形成される。30

#### 【 0 1 4 8 】

一方で、時刻 t a ~ t 1 の間（期間長 T 2 ）では、C W < D T となるのでリアクトル電流 I L は上昇する。当該期間では、リアクトル電流 I L 1 に対しては電流経路 1 2 0 ( 図 3 ( a ) ) が形成され、リアクトル電流 I L 2 に対しては電流経路 1 3 0 ( 図 4 ( a ) ) が形成される。

#### 【 0 1 4 9 】

ここで、デューティ比 D T および周期 T c y を用いると、 $T_2 = T_c \times D_T$  、かつ、 $T_1 = T_c \times (1 - D_T)$  となる。そして、周期 T c y 離れた時刻 t 0 と t 1 とでリアクトル電流 I L は等しい。40

#### 【 0 1 5 0 】

まず、遷移周期 2 0 5 において、周期 2 0 1 と同等のデューティ比 D T 1 を三角波 T W と比較したときのリアクトル電流 I L の波形が点線で示される。この場合には、D T 1 = T W となる時刻 t c および t d においてリアクトル電流 I L に変曲点が生じる。T W > D T 1 となる時刻 t c ~ t d の期間長 T 5 ( すなわち、上アームオンの期間長 ) は、周期 2 0 1 での期間長 T 2 と同等である。

#### 【 0 1 5 1 】

しかしながら、周期 2 0 5 では、時刻 t 1 以降も下アームオンによる電流上昇期間が継続するため、上アームオンの期間長が周期 2 0 1 と同等に確保されても、リアクトル電流 I L の平均値は、周期 2 0 1 よりも上昇してしまう。したがって、リアクトル電流 I L の50

平均値を周期 201 と同等にするためには、変換デューティ比 DTa を以下のように求める必要がある。

#### 【0152】

遷移周期 205 ( 時刻  $t_1 \sim t_z$  ) において、変換デューティ比 DTa に対して、時刻  $t_1 \sim t_b$  の間 ( 期間長  $T_3$  ) は、  $DTa > CW$  であるので、リアクトル電流  $I_L$  は上昇する。当該期間では、リアクトル電流  $I_L$  1 に対しては電流経路 120 ( 図 3 ( a ) ) が形成され、リアクトル電流  $I_L$  2 に対しては電流経路 130 ( 図 4 ( a ) ) が形成される。

#### 【0153】

変換デューティ比 DTa を三角波 TW と比較したときには、時刻  $t_b \sim t_e$  の間は  $CW > DTa$  であるので、リアクトル電流  $I_L$  は低下する。時刻  $t_e \sim t_z$  ( 期間長  $T_7$  ) では、再び、  $DTa > CW$  となるので、時刻  $t_1 \sim t_b$  と同様にリアクトル電流  $I_L$  は上昇する。三角波 TW の波形から、  $T_3 = T_7$  が成立する。また、  $T_3 + T_7 = T_c \times DTa$  であるので、  $T_3 = T_7 = (T_c / 2) \times DTa$  と示されることが理解される。

#### 【0154】

上述したように、時刻  $t_c \sim t_d$  までの期間長  $T_5$  は、周期 201 での上アームオン期間長  $T_1$  と同等である。したがって、時刻  $t_c$  におけるリアクトル電流  $I_L$  ( 以下、  $I_L(t_c)$  とも表記する ) が時刻  $t_0, t_1$  でのリアクトル電流  $I_L$  ( 以下、  $I_L(t_0), I_L(t_1)$  とも表記する ) と同等であるようにすると、時刻  $t_d$  でのリアクトル電流  $I_L$  も、時刻  $t_a$  と同等となる。

#### 【0155】

三角波 TW の対称性から、  $T_3 : T_4 = T_7 : T_6$  となる。このため、  $I_L(t_c) = I_L(t_1) (= I_L(t_0))$  が実現されると、周期 205 が終了され、かつ、周期 202 が開始される時刻  $t_z$  におけるリアクトル電流  $I_L$  を、周期 201 での最小値 ( 時刻  $t_a$  ) と同等とすることができる。上りのこぎり波が適用される周期 202 では、周期 202 が開始される時刻  $t_z$  において、リアクトル電流  $I_L$  は最小値となる。この結果、周期 201、遷移周期 205 および周期 202 の各々において、リアクトル電流  $I_L$  の平均値を同等とすることができます。

#### 【0156】

時刻  $t_1$  の前後で、リアクトル電流  $I_L$  の上昇時の傾きおよび低下時の傾きは変わらない。したがって、電流波形の相似性から、  $I_L(t_c) = I_L(t_1)$  とするためには、  $T_1 : T_2 = T_4 : T_3$  が成立するように、変換デューティ比 DTa を定めればよいことが理解される。ここで、  $T_1 : T_2 = (1 - DT) : DT$ 、および、  $T_3 = (T_c / 2) \times DTa$  から下記 (1) 式が成立する。

#### 【0157】

$$(1 - DT) : DT = T_4 : (T_c / 2) \times DTa \quad \dots (1)$$

(1) 式を変形すると、下記 (2) 式が得られる。

#### 【0158】

$$T_4 = (DTa / DT) \times (1 - DT) \times (T_c / 2) \quad \dots (2)$$

また、時刻  $t_b \sim t_d$  では、三角波 TW の対称性から、下記 (3) 式が成立する。

#### 【0159】

$$T_4 \times 2 + T_5 = (1 - DTa) \times T_c \quad \dots (3)$$

式 (3) に式 (2) を代入し、さらに、周期 200A および遷移周期 205 の間で、電流変化量が同一である  $T_1 = T_5$  となるから、  $T_5 = T_c \times (1 - DT)$  を代入すると、(4) 式が得られる。

#### 【0160】

$$DTa / DT \times (1 - DT) + (1 - DT) = (1 - DTa) \quad \dots (4)$$

式 (4) を DTa について解くと、  $DTa = DT^2$  ( DT の 2 乗 ) が得られる。

#### 【0161】

同様に、リアクトル電流  $I_L$  の平均値が周期 201 と同等となるように、逆相三角波 R

10

20

30

40

50

$T_W$  が適用された遷移周期 205 における変換デューティ比  $D_T b$  を求めると、詳細な導出は省略するが、 $D_T b = 1 - (1 - D_T)^2$  が得られる。

#### 【0162】

以上より、図 16 に示した第 1 の制御例に従う遷移周期でのキャリア波の設定の一覧は、図 18 に示すようになる。

#### 【0163】

図 18 を参照して、キャリア波の切替モードは、切替え前のキャリア波モードおよび切替え後のキャリア波モードを続けて表記した 2 桁の整数で示される。たとえば、図 16 に示した、キャリア波モード 2 からキャリア波モード 1 への切替え時には、切替モード 21 が適用される。したがって、4 個のキャリア波モードに対して、切替モードは  $3 \times 4 = 12$  個存在する。10

#### 【0164】

図 18 には、各切替モードにおける、キャリア波 CW1, CW2 および、適用されるデューティ比  $D_T 1$ ,  $D_T 2$  が示される。上述のように、デューティ比  $D_T 1$ ,  $D_T 2$  は、遷移周期 205 においても直前の周期 200A とリアクトル電流 IL1, IL2 の平均値を同等とするための換算値である。

#### 【0165】

キャリア波 CW1 について、切替え前後とも下りのこぎり波が適用される、切替モード 14 および切替モード 41 では、遷移周期 205 において、キャリア波 CW1 の変更は必要ない。このため、キャリア波 CW1 には、下りのこぎり波 STD が適用される。同様に、切替え前後とも上りのこぎり波が適用される、切替モード 23 および切替モード 32 では、キャリア波 CW1 には、上りのこぎり波 STU が適用される。これらの切替モードでは、デューティ比の変換は不要であるので、 $D_T 1 = D_T 1$  に設定される。20

#### 【0166】

キャリア波 CW1 について、切替え前に下りのこぎり波が適用される一方で切替え後には上りのこぎり波が適用される、切替モード 12、切替モード 13、切替モード 42、および、切替モード 43 では、図 16 でのキャリア波 CW2 と同様に、三角波 TW が適用される。この場合には、デューティ比換算により、 $D_T 1 = D_T a = (D_T 1)^2$  (すなわち、 $D_T 1^2$ ) に設定される。

#### 【0167】

一方で、切替え前に上りのこぎり波が適用される一方で切替え後には下りのこぎり波が適用される、切替モード 21、切替モード 24、切替モード 31、および、切替モード 34 では、図 16 でのキャリア波 CW1 と同様に、逆相三角波 RTW が適用される。この場合には、デューティ比換算により、 $D_T 1 = D_T b = 1 - (1 - D_T 1)^2$  (すなわち、 $1 - (1 - D_T 1)^2$ ) に設定される。30

#### 【0168】

キャリア波 CW2 についても、キャリア波 CW1 と同様に、切替え前後とも下りのこぎり波が適用される、切替モード 24 および切替モード 42 では、遷移周期 205 におけるキャリア波 CW2 は、下りのこぎり波 STD で構成される。また、切替え前後とも上りのこぎり波が適用される、切替モード 13 および切替モード 31 では、キャリア波 CW2 は、上りのこぎり波 STU で適用される。これらの切替モードでは、 $D_T 2 = D_T 2$  に設定される。40

#### 【0169】

一方で、切替え前に下りのこぎり波が適用される一方で切替え後には上りのこぎり波が適用される、切替モード 21、切替モード 23、切替モード 41、および、切替モード 43 では、図 16 でのキャリア波 CW2 と同様に、三角波 TW が適用される。 $D_T 2 = D_T a = (D_T 2)^2$  (すなわち、 $D_T 2^2$ ) に設定される。

#### 【0170】

これに対して、切替え前に上りのこぎり波が適用される一方で切替え後には下りのこぎり波が適用される、切替モード 12、切替モード 14、切替モード 32、および、切替モ50

ード 3 4 では、図 1 6 でのキャリア波 C W 1 と同様に、逆相三角波 R T W が適用される。そして、 $D T 2 = D T b = 1 - (1 - D T 2)^2$  (すなわち、 $1 - (1 - D T 2)^2$ ) に設定される。

#### 【 0 1 7 1 】

このようにすると、リアクトル電流 I L 1 , I L 2 の位相関係を変える電流位相制御のためにキャリア波モードを切替える場合に、リアクトル電流 I L 1 , I L 2 の平均値を維持した上で、リアクトル電流 I L 1 , I L 2 の変動を抑制することができる。

#### 【 0 1 7 2 】

なお、キャリア波モード切替え時における三角波および逆相三角波の適用は、図 1 6 の例と反対にすることも可能である。

10

#### 【 0 1 7 3 】

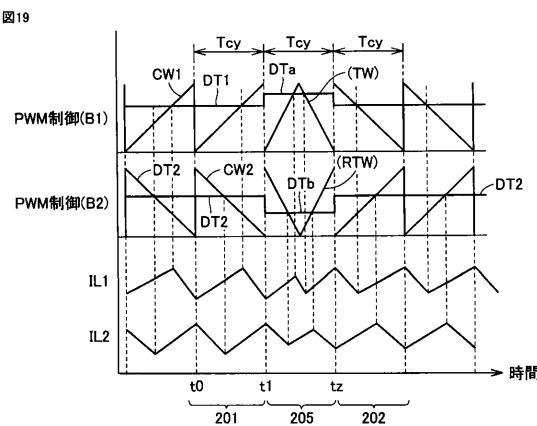

図 1 9 には、本実施の形態 1 の変形例に従う P W M 制御におけるキャリア波モード切替え時の第 2 の制御例を説明する波形図が示される。図 1 9 においても、図 1 6 と同様に、キャリア波モード 2 からキャリア波モード 1 への切替えが示される。

#### 【 0 1 7 4 】

図 1 9 を参照して、第 2 の制御例では、第 1 の制御例とは反対に、上りのこぎり波 S T U から下りのこぎり波 S T D の切替え時には、三角波 T W がキャリア波に適用されるとともに、下りのこぎり波 S T D から上りのこぎり波 S T U の切替え時には、逆相三角波 R T W がキャリア波に適用される。これにより、図 1 6 の例とは反対に、遷移周期 2 0 5 において、キャリア波 C W 1 は三角波 T W によって構成され、キャリア波 C W 2 は逆相三角波 R T W によって構成される。

20

#### 【 0 1 7 5 】

図 1 9 に示した第 2 の制御例に従う遷移周期でのキャリア波の設定の一覧は、図 2 0 に示すようになる。

#### 【 0 1 7 6 】

図 2 0 を参照して、キャリア波 C W 1 について、切替モード 1 4 および切替モード 4 1 では、切替え前後とも下りのこぎり波が適用されるため、図 1 8 と同様に、キャリア波 C W 1 には下りのこぎり波 S T D が適用されて、 $D T 1 = D T 1$  に設定される。同様に、切替モード 2 3 および切替モード 3 2 では、キャリア波 C W 1 には上りのこぎり波 S T U が適用されて、 $D T 1 = D T 1$  に設定される。

30

#### 【 0 1 7 7 】

一方で、キャリア波 C W 1 について、切替え前に下りのこぎり波が適用される一方で切替え後には上りのこぎり波が適用される、切替モード 1 2 、切替モード 1 3 、切替モード 4 2 、および、切替モード 4 3 では、図 1 8 とは反対に逆相三角波 R T W が適用される。この場合には、 $D T 1 = 1 - (1 - D T 1)^2$  (すなわち、 $1 - (1 - D T 1)^2$ ) に設定される。

#### 【 0 1 7 8 】

また、切替え前に上りのこぎり波が適用される一方で切替え後には下りのこぎり波が適用される、切替モード 2 1 、切替モード 2 4 、切替モード 3 1 、および、切替モード 3 4 では、図 1 8 とは反対に三角波 T W が適用される。そして、 $D T 1 = (D T 1)^2$  (すなわち、 $D T 1^2$ ) に設定される。

40

#### 【 0 1 7 9 】

同様に、キャリア波 C W 2 についても、切替え前後とも下りのこぎり波が適用される、切替モード 2 4 および切替モード 4 2 では、遷移周期 2 0 5 において、キャリア波 C W 2 は、下りのこぎり波 S T D で構成されて、 $D T 2 = D T 2$  に設定される。また、切替え前後とも上りのこぎり波が適用される、切替モード 1 3 および切替モード 3 1 においても、遷移周期 2 0 5 において、キャリア波 C W 2 は、上りのこぎり波 S T U で構成されて、 $D T 2 = D T 2$  に設定される。

#### 【 0 1 8 0 】

一方で、切替え前に下りのこぎり波が適用される一方で切替え後には上りのこぎり波が

50

適用される、切替モード21、切替モード23、切替モード41、および、切替モード43では、図18とは反対に、逆相三角波RTWがキャリア波CW2に適用される。そして、 $DT_2 = DT_b = 1 - (1 - DT_2)^2$ （すなわち、 $1 - (1 - DT_2)^2$ ）に設定される。

#### 【0181】

また、切替え前に上りのこぎり波が適用される一方で切替え後には下りのこぎり波が適用される、切替モード12、切替モード14、切替モード32、および、切替モード34では、三角波TWがキャリア波CW2に適用される。そして、 $DT_2 = DT_a = (DT_2)^2$ （すなわち、 $DT_2^2$ ）に設定される。

#### 【0182】

再び図19を参照して、第2の制御例においても、遷移周期205内で、リアクトル電流IL1, IL2の変曲点が2回生じることが理解できる。さらに、第2の制御例では、上りのこぎり波STUと三角波TWとの位相関係、ならびに、下りのこぎり波STDと逆相三角波RTWとの位相関係から、遷移周期205の開始タイミング（時刻t1）においても、リアクトル電流IL1, IL2に変曲点を生じさせることができる。

#### 【0183】

同様に、遷移周期205の終了タイミング（時刻tz）においても、三角波TWと下りのこぎり波STDと三角波TWとの位相関係、ならびに、逆相三角波RTWと上りのこぎり波STUとの位相関係から、リアクトル電流IL1, IL2に変曲点を生じさせることができるとする。

#### 【0184】

この結果、第2の制御例に従って遷移周期205を設定することにより、リアクトル電流IL1, IL2の変曲点の数を増やすことができるので、リアクトル電流IL1, IL2の平均値を維持した上で、リアクトル電流IL1, IL2の変動をさらに抑制することができる。

#### 【0185】

[実施の形態1のその他の変形例]

(パラレル昇圧モード以外の動作モード)

実施の形態1およびその変形例1で説明した電力変換器50については、特許文献1および記載されるように、パラレル昇圧モードとはDC/DC変換の態様が異なる、他の動作モードを適用することができる。

#### 【0186】

図21には、電力変換器50が有する複数の動作モードの一覧が示される。

図21を参照して、動作モードは、実施の形態1およびその変形例1に記載したパラレル昇圧モード（以下、PBモードとも称する）に加えて、特許文献1にも接続されたシリーズ昇圧モード（以下、SBモードとも称する）と、「直流電源B1による単独昇圧モード（以下、aBモード）」と、「直流電源B2による単独昇圧モード（以下、bBモード）」とをさらに含む。

#### 【0187】

SBモードは、特許文献1における「シリーズ接続モード」と同等である。特許文献1にも記載されるように、直流電源B1およびB2を直列接続した状態でDC/DC変換を実行することによって、昇圧比の低下による電力変換効率の向上を図ることができる。スイッチング素子S1～S4のオンオフ制御の詳細は、特許文献1でのシリーズ接続モードと同様に実行することができるので、詳細な説明は繰り返さない。なお、特許文献1には、キャリア位相制御の適用によってシリーズ昇圧モードでの制御動作を簡易にできることが記載されているが、三角波のキャリア位相制御に代えて、実施の形態1またはその変形例に従って、のこぎり波を適用したPWM制御を行っても同等の効果を得ることができる。

#### 【0188】

aBモードでは、直流電源B1のみを用いてDC/DC変換（昇圧）が実行される。a

10

20

30

40

50

B モードでは、出力電圧 V H が直流電源 B 2 の電圧 V [ 2 ] よりも高く制御されている限りにおいて、直流電源 B 2 は、電力線 P L と電気的に切り離された状態を維持されて不使用とされる。

#### 【 0 1 8 9 】

同様に、b B モードでは、直流電源 B 2 のみを用いて D C / D C 変換（昇圧）が実行される。b B モードでは、出力電圧 V H が直流電源 B 1 の電圧 V [ 1 ] よりも高く制御されている限りにおいて、直流電源 B 1 は、電力線 P L と電気的に切り離された状態を維持されて不使用とされる。

#### 【 0 1 9 0 】

P B モード、S B モード、a B モードおよびb B モードでは、たとえば、図 5 の制御構成を共有して、直流電源 B 1 および／または B 2 の出力が制御される。出力制御のための P W M 制御に従ってスイッチング素子 S 1 ~ S 4 の周期的なオンオフ制御を実行することによって、出力電圧 V H は電圧指令値 V H \* に従って制御される。10

#### 【 0 1 9 1 】

このように、本実施の形態 1 およびその変形例に従う電源システムでは、パラレル昇圧モードの他にも、効率に優れる S B モード（シリーズ昇圧モード）や、一方の電源のみを用いる a B モードおよび b B モードを選択することができるので、直流電源 B 1 および B 2 の利用効率を高めることができる。

#### 【 0 1 9 2 】

a B モードでは、電力変換器 5 0 において、スイッチング素子 S 3 および S 4 を下アームとして共通にオンオフ制御する。さらに、スイッチング素子 S 1 および S 2 についても、上アームとして共通にオンオフ制御することができる。20

#### 【 0 1 9 3 】

したがって、a B モードでは、図 5 の構成において、出力制御部 5 1 0 の動作をオフして、出力制御部 5 0 0 によって、V H 制御のためのデューティ比 D T 1 が算出される。さらに、デューティ比 D T 1 を用いた P W M 制御による制御パルス信号 S D 1 に従って、下アーム（スイッチング素子 S 3 , S 4 ）のオン期間およびオフ期間（スイッチング素子 S 1 , S 2 のオン期間）を、繰り返し設けることによって、出力電圧 V H を電圧指令値 V H \* に従って制御することができる。

#### 【 0 1 9 4 】

b B モードにおいても同様に、図 5 の構成において、出力制御部 5 1 0 によって算出されたデューティ比を、直流電源 B 2 の出力を制御するためのデューティ比 D T 2 として用いることで、出力電圧 V H を電圧指令値 V H \* に従って制御することができる。さらに、電力変換器 5 0 において、スイッチング素子 S 2 および S 3 を下アームとして共通にオンオフ制御するとともに、スイッチング素子 S 1 および S 4 について、上アームとして共通にオンオフ制御することができる。したがって、デューティ比 D T 2 を用いた P W M 制御による制御パルス信号 S D 2 に従って、下アーム（スイッチング素子 S 2 , S 3 ）のオン期間およびオフ期間（スイッチング素子 S 1 , S 4 のオン期間）を、繰り返し設けることによって、出力電圧 V H を電圧指令値 V H \* に従って制御することができる。30

#### 【 0 1 9 5 】

再び、図 2 1 を参照して、複数の動作モードは、スイッチング素子 S 1 ~ S 4 のオンオフを固定する「直結モード」をさらに含む。直結モードには、「並列直結モード（以下、P D モード）」と、「シリーズ直結モード（以下、S D モード）」と、「直流電源 B 1 の直結モード（以下、a D モード）」と、「直流電源 B 2 の直結モード（以下、b D モード）」とが含まれる。40

#### 【 0 1 9 6 】

P D モードでは、スイッチング素子 S 1 , S 2 , S 4 をオンに固定する一方で、スイッチング素子 S 3 がオフに固定される。これにより、直流電源 B 1 および B 2 を負荷 3 0 （電力線 P L , G L 間）に並列に接続した状態が維持される。この結果、出力電圧 V H は、直流電源 B 1 , B 2 の出力電圧 V [ 1 ] , V [ 2 ] （厳密には V [ 1 ] , V [ 2 ] のうち50

の高い方の電圧)と同等となる。 $V[1], V[2]$ 間の電圧差は直流電源B1, B2に短絡電流を生じさせてるので、当該電圧差が小さいときに限定して、PDモードを適用することができる。

#### 【0197】

SDモードでは、スイッチング素子S2, S4がオフに固定される一方で、スイッチング素子S1, S3がオンに固定される。これにより、直流電源B1およびB2を負荷30(電力線PL, GL間)に直列に接続した状態が維持される。この結果、出力電圧VHは、直流電源B1, B2の出力電圧 $V[1], V[2]$ の和と同等となる( $VH = V[1] + V[2]$ )。

#### 【0198】

aDモードでは、スイッチング素子S1, S2がオンに固定される一方で、スイッチング素子S3, S4がオフに固定される。これにより、直流電源B2は電力線PLから切り離された状態となり、出力電圧VHは、直流電源B1の電圧 $V[1]$ と同等となる( $VH = V[1]$ )。aDモードでは、直流電源B2は、電力線PLと電気的に切り離された状態を維持されて不使用とされる。なお、 $V[2] > V[1]$ の状態でaDモードを適用すると、スイッチング素子S2を介して直流電源B1からB2に短絡電流が生じる。このため、aDモードの適用には、 $V[1] > V[2]$ が必要条件となる。

#### 【0199】

同様に、bDモードでは、スイッチング素子S1, S4がオンに固定される一方で、スイッチング素子S2, S3がオフに固定される。これにより、直流電源B1は電力線PLから切り離された状態となり、出力電圧VHは、直流電源B2の電圧 $V[2]$ と同等となる( $VH = V[2]$ )。bDモードでは、直流電源B1は、電力線PLと電気的に切り離された状態を維持されて不使用とされる。なお、 $V[1] > V[2]$ の状態でbDモードを適用すると、ダイオードD2を介して直流電源B1からB2に短絡電流が生じる。このため、bDモードの適用には、 $V[2] > V[1]$ が必要条件となる。

#### 【0200】

直結モードに含まれる、PDモード、SDモード、aDモードおよびbDモードの各々では、出力電圧VHは、直流電源B1, B2の電圧 $V[1], V[2]$ に依存して決まるため、直接制御することができなくなる。このため、直結モードに含まれる各モードでは、出力電圧VHが負荷30の動作に適した電圧に設定できなくなることにより、負荷30での電力損失が増加する虞がある。

#### 【0201】

一方で、直結モードでは、スイッチング素子S1～S4がオンオフされないため、電力変換器50の電力損失が大幅に抑制される。したがって、負荷30の動作状態によっては、直結モードの適用によって、負荷30の電力損失増加量よりも電力変換器50での電力損失減少量が多くなることにより、電源システム5A全体での電力損失が抑制できる可能性がある。

#### 【0202】

このように、本実施の形態1およびその変形例1に従う電源システム5Aでは、キャリア波としてのこぎり波を用いた電流位相制御が適用されるパラレル昇圧モードを含む、図21に示された複数の動作モードを、負荷30および/または電力変換器50の動作状態に応じて適切に切換えることによって、DC/DC変換を実行できる。この結果、電力損失の小さい全電圧シリーズ(SR)モードの他、他の動作モードを適切に選択することによって、電源システム5A全体での高効率化を図ることができる。

#### 【0203】

(電力変換器の回路構成アレンジ)

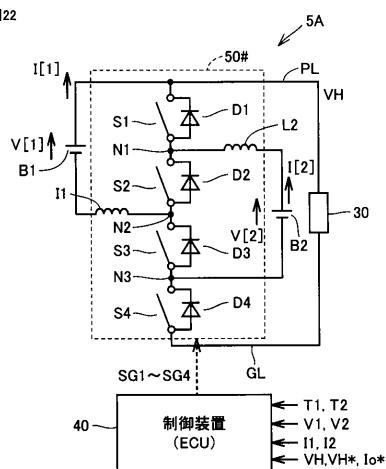

図22は、実施の形態1およびその変形例に従う電力変換器50の回路構成の変形例を示す回路図である。

#### 【0204】

図22を参照して、電力変換器50は、図1に示された電力変換器50と比較して、

10

20

30

40

50

直流電源B1およびリアクトルL1が、ノードN2および電力線GLの間ではなく、電力線PLおよびノードN2の間に直列に接続される点で異なる。電力変換器50のその他の構成は、電力変換器50と同様であるのでその説明は繰返さない。

#### 【0205】

電力変換器50においては、電力変換器50と比較した回路の対称性から、直流電源B1に対する上アームと下アームとを入れ替えて、電力変換器50と同様のDC/DC変換を実行できることが理解される。

#### 【0206】

具体的には、電力変換器50では、スイッチング素子S1, S2を直流電源B1の下アームとし、スイッチング素子S3, S4を直流電源B1の上アームとするように制御することが必要である。この結果、電力変換器50の各動作モードにおいて、スイッチング素子S1は、電力変換器50のスイッチング素子S4と同等のパターンでオンオフ制御され、スイッチング素子S2は、電力変換器50のスイッチング素子S3と同等のパターンでオンオフ制御される。同様に、電力変換器50のスイッチング素子S3は、電力変換器50のスイッチング素子S2と同等のパターンでオンオフ制御され、スイッチング素子S4は、電力変換器50のスイッチング素子S1と同等のパターンでオンオフ制御される。

10

#### 【0207】

たとえば、電力変換器50のパラレル昇圧モードでは、スイッチング素子S1およびS2をオンすることにより、図3(a)の電流経路120に相当する、直流電源B1およびリアクトルL1を含むループ状の電流経路を形成することができる。また、スイッチング素子S3およびS4をオンすることにより、図3(b)の電流経路121に相当する、電力線PLおよびGL間に直流電源B1およびリアクトルL1を直列に接続する電流経路を形成することができる。

20

#### 【0208】

なお、直流電源B2に対しては、電力変換器50と同様に、スイッチング素子S2およびS3をオンすることによって図4(a)の電流経路130を形成することができる。また、スイッチング素子S1およびS4をオンすることによって、図4(b)の電流経路131を形成することができる。

#### 【0209】

30

このようにすると、電力変換器50についても、電力変換器50と同様に、パラレル昇圧モードを含む、図21に示された各動作モードによって、DC/DC変換を実行することができる。パラレル昇圧においては、実施の形態1およびその変形例1に従う、のこぎり波を用いたPWM制御を適用して各直流電源からの出力を制御することにより、リアクトル電流の位相を簡易に制御することができる。

#### 【0210】

以上説明したように、実施の形態1およびその変形例1に従う電源システムでは、電力変換器50, 50を包括すると、スイッチング素子S1～S4に対して、直流電源B1およびリアクトルL1は、電力線PLまたはGLと、ノードN2との間に直列に電気的に接続される。一方で、直流電源B2およびリアクトルL2は、ノードN1とN3との間に直列に電気的に接続される。

40

#### 【0211】

また、電力変換器50, 50の各々において、リアクトルL1および直流電源B1の接続順序を入れ換ても、電気的には等価な回路構成が維持される。同様に、リアクトルL2および直流電源B2の接続順序を入れ換ても、電気的には等価な回路構成が維持される。

#### 【0212】

##### [実施の形態2]

実施の形態2では、電力変換器50, 50とは異なる構成を有する電力変換器に対して、実施の形態1で説明したPWM制御を適用する例について説明する。

50

(電力変換器の回路構成)

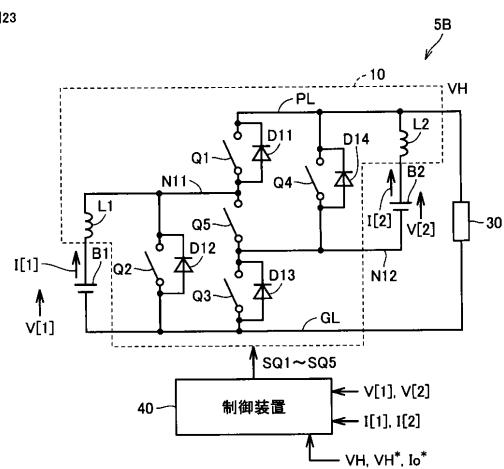

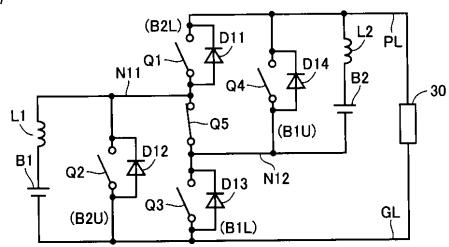

図23は、本発明の実施の形態2に従う電源システム5Bの構成を説明する回路図である。

【0213】

図23を図1と比較して、実施の形態2に従う電源システム5Bは、図1に示された電源システム5Aと比較して、電力変換器50に代えて電力変換器10を備える点で異なる。電源システム5Bの、その他の部分の構成は、電源システム5Aと同様である。

【0214】

すなわち、電源システム5Bについても、負荷30と接続された電力線PLおよびGLと、直流電源B1およびB2との間で、DC/DC変換を実行するように構成される。

10

【0215】

電力変換器10についても電力変換器50と同様に、負荷30への出力電圧VHを、電圧指令値VH\*に従って制御する。

【0216】

図23を参照して、電力変換器10は、高電圧側の電力線PLおよび低電圧側の電力線GLの間の直流電圧(出力電圧)VHを制御するように構成される。

【0217】

電力変換器10は、スイッチング素子Q1～Q5と、リクトルL1, L2とを含む。スイッチング素子Q1～Q5は、制御装置40からの制御信号SQ1～SQ5にそれぞれ応答して、オンオフを制御することが可能である。具体的には、スイッチング素子Q1～Q5は、制御信号SQ1～SQ5がHレベルのときにオン状態となって、電流経路を形成可能な状態となる。一方で、スイッチング素子Q1～Q5は、制御信号SQ1～SQ5がLレベルのときにオフ状態となって、当該電流経路を遮断する状態となる。

20

【0218】

スイッチング素子Q1～Q4に対しては、逆並列ダイオードD11～D14がそれぞれ配置されている。ダイオードD11～D14は、順バイアス時に、電力線GLから電力線PLへ向かう方向(図中、下から上へ向かう方向)の電流経路を形成するように配置される。一方で、ダイオードD11～D14は、逆バイアス時には、当該電流経路を非形成とする。具体的には、ダイオードD11は、ノードN1から電力線PLへ向かう方向を順方向とするように接続され、ダイオードD12は、電力線GLからノードN11へ向かう方向を順方向とするように接続される。同様に、ダイオードD13は、電力線GLからノードN12へ向かう方向を順方向とするように接続され、ダイオードD14は、ノードN12から電力線PLへ向かう方向を順方向とするように接続される。

30

【0219】

スイッチング素子Q1は、電力線PLおよびノードN11の間に電気的に接続される。リクトルL1および直流電源B1は、ノードN11および電力線GLの間に直列に、電気的に接続される。たとえば、リクトルL1は、直流電源B1の正極端子およびノードN11の間に電気的に接続されるとともに、直流電源B1の負極端子は、電力線GLと電気的に接続される。スイッチング素子Q2は、ノードN11および電力線GLの間に電気的に接続される。なお、リクトルL1および直流電源B1の接続順序を入れ換えて、電気的には等価な回路構成が維持される。

40

【0220】

スイッチング素子Q3は、ノードN12および電力線GLの間に電気的に接続される。スイッチング素子Q4は、電力線PLおよびノードN12の間に電気的に接続される。スイッチング素子Q5は、ノードN11およびN12の間に電気的に接続される。リクトルL2および直流電源B2は、電力線PLおよびノードN12の間に直列に、電気的に接続される。たとえば、リクトルL2は、直流電源B2の正極端子および電力線PLの間に電気的に接続されるとともに、直流電源B2の負極端子は、ノードN12と電気的に接続される。なお、リクトルL2および直流電源B2の接続順序を入れ換えて、電気的には等価な回路構成が維持される。

50

**【0221】**

図23の構成例では、ノードN11は「第1のノード」に対応し、ノードN12は「第2のノード」に対応する。さらに、スイッチング素子Q1およびダイオードD1は「第1の半導体素子」に対応し、スイッチング素子Q2およびダイオードD2は「第2の半導体素子」に対応し、スイッチング素子Q3およびダイオードD3は「第3の半導体素子」に対応する。さらに、スイッチング素子Q4およびダイオードD4は「第4の半導体素子」に対応し、スイッチング素子Q5は、「第5の半導体素子」に対応する。また、リアクトルL1およびL2は、「第1のリアクトル」および「第2のリアクトル」にそれぞれ対応する。図1の例では、スイッチング素子Q1～Q5のオンオフ制御により、第1～第5の半導体素子の各々において、電流経路の形成および遮断を制御することができる。

10

**【0222】**

## (パラレル昇圧モードでの回路動作)

実施の形態1およびその変形例1と同等のPWM制御が適用される、電力変換器10のパラレル昇圧モードでの回路動作および制御について、詳細に説明する。以下の説明で明らかになるように、電力変換器10は、パラレル昇圧モードにおけるスイッチング素子での損失が電力変換器50よりも小さいという特徴を有する。なお、電力変換器10についても、電力変換器50と同様に、パラレル昇圧モード以外の動作モードを有するが、本実施の形態では、実施の形態1またはその変形例に従う、のこぎり波を適用したPWM制御の適用が好ましいパラレル昇圧モードについて説明する。

**【0223】**

20

電力変換器10は、パラレル昇圧モードにおいては、直流電源B1およびB2の各々に対して2つの昇圧チョッパ回路を並列に動作させる態様により動作する。すなわち、電力変換器10は、電力変換器50でのパラレル昇圧モードと同様に、直流電源B1およびB2と電力線PL, GL(負荷30)との間で並列なDC/DC変換を行なうことにより、電圧指令値VH\*に従って出力電圧VHを制御する。

**【0224】**

再び図23を参照して、電力変換器10においては、スイッチング素子Q5をオンした場合と、オフした場合との間で、直流電源B1およびB2に対して形成される昇圧チョッパ回路が異なることが特徴である。

**【0225】**

30

電力変換器10において、スイッチング素子Q5のオフ時には、ノードN11およびN12が電気的に切り離される。このときの電力変換器10の等価回路が図24に示される。

**【0226】**

図24を参照して、スイッチング素子Q5のオフ時には、直流電源B1に対して、スイッチング素子Q2およびダイオードD12を下アームとし、スイッチング素子Q1およびダイオードD11を上アームとする昇圧チョッパ回路が形成される。同様に、直流電源B2に対して、スイッチング素子Q4およびダイオードD14を下アームとし、スイッチング素子Q3およびダイオードD13を上アームとする昇圧チョッパ回路が形成される。

**【0227】**

40

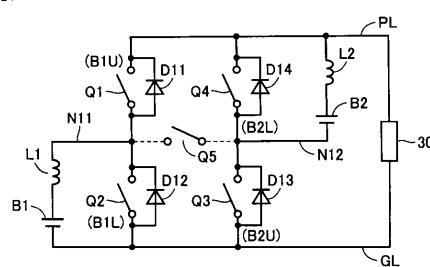

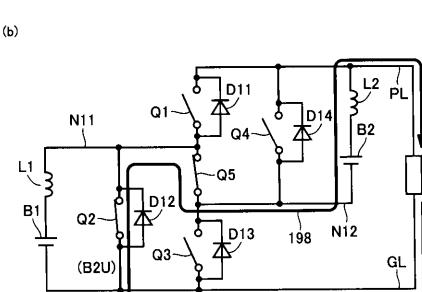

図25には、図24に示した等価回路において、直流電源B1, B2の下アームオン時における電流経路が示される。

**【0228】**

図25を参照して、スイッチング素子Q2をオンすることにより、直流電源B1の出力によりリアクトルL1にエネルギーを蓄積するための電流経路191が形成される。これにより、直流電源B1に対しては、電力線PLおよびGLを含まずに、直流電源B1およびリアクトルL1を含むループ状の電流経路191が形成される。すなわち、電流経路191は「第1の電流経路」に対応する。

**【0229】**

同様に、スイッチング素子Q4をオンすることにより、直流電源B2の出力によりリア

50

クトル L 2 にエネルギーを蓄積するための電流経路 192 が形成される。これにより、直流電源 B 2 に対しては、電力線 P L および G L を含まずに、直流電源 B 2 およびリアクトル L 2 を含むループ状の電流経路 192 が形成される。電流経路 192 は「第 3 の電流経路」に対応する。

#### 【 0 2 3 0 】

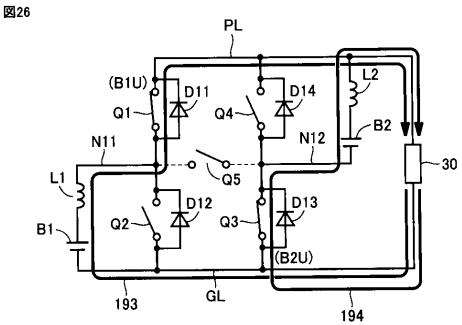

図 26 には、図 25 に示した等価回路図において、直流電源 B 1, B 2 の上アームオン時における電流経路が示される。

#### 【 0 2 3 1 】

図 26 を参照して、スイッチング素子 Q 2 をオフすることにより、スイッチング素子 Q 1 またはダイオード D 1 1 を経由して、リアクトル L 1 の蓄積エネルギーを直流電源 B 1 からのエネルギーとともに電力線 P L へ出力するための電流経路 193 が形成される。ここで、スイッチング素子 Q 1 および Q 2 を相補的にオンオフすることにより、スイッチング素子 Q 2 のオフ期間にスイッチング素子 Q 1 がオンされる。スイッチング素子 Q 1 は、直流電源 B 1 に対応して形成される昇圧チョッパ回路の上アームに相当する。これにより、直流電源 B 1 に対して、電力線 P L および G L の間に直流電源 B 1 およびリアクトル L 1 を直列に接続される電流経路 193 が形成される。すなわち、電流経路 193 は「第 2 の電流経路」に対応する。

#### 【 0 2 3 2 】

同様に、スイッチング素子 Q 4 をオフすることにより、スイッチング素子 Q 3 またはダイオード D 1 3 を経由して、リアクトル L 2 の蓄積エネルギーを直流電源 B 2 からのエネルギーとともに電力線 P L へ出力するための電流経路 194 が形成される。スイッチング素子 Q 3 および Q 4 を相補的にオンオフすることにより、スイッチング素子 Q 4 のオフ期間にスイッチング素子 Q 3 がオンする。スイッチング素子 Q 3 は、直流電源 B 2 に対応して形成される昇圧チョッパ回路の上アームに相当する。これにより、直流電源 B 2 に対しては、電力線 P L および G L の間に直流電源 B 2 およびリアクトル L 2 を直列に接続される電流経路 194 が形成される。すなわち、電流経路 194 は「第 4 の電流経路」に対応する。

#### 【 0 2 3 3 】

図 25 および図 26 から理解されるように、電流経路 191 および 193 を交互に形成することによって、直流電源 B 1 および電力線 P L, G L の間の D C / D C 変換が実行される。同様に、電流経路 192 および 194 を交互に形成することによって、直流電源 B 2 および電力線 P L, G L の間の D C / D C 変換が実行される。

#### 【 0 2 3 4 】

以下では、直流電源 B 1 に対応して形成される昇圧チョッパ回路の上アームを「B 1 U アーム」とも称し、下アームを「B 1 L アーム」と称する。同様に、直流電源 B 2 に対応して形成される昇圧チョッパ回路の上アームを「B 2 U アーム」とも称し、下アームを「B 2 L アーム」とも称する。

#### 【 0 2 3 5 】

なお、図 25 から理解されるように、B 1 L アームおよび B 2 L アームの形成時には、ノード N 1 2 から N 1 1 へ向かう電流経路が形成されると、電力線 P L から電力線 G L への短絡経路が形成されてしまうため、当該電流経路を遮断する必要がある。同様に、図 26 から理解されるように、B 1 U アームおよび B 2 U アームの形成時には、ノード N 1 1 から N 1 2 へ向かう電流経路が形成されると、電力線 P L から電力線 G L への短絡経路が形成されてしまうため、当該電流経路を遮断する必要がある。したがって、B 1 L アームおよび B 2 L アームの形成時、および、B 1 U アームおよび B 2 U アームの形成時の各々では、スイッチング素子 Q 5 をオフすることによって、上記短絡経路の形成を回避することができる。

#### 【 0 2 3 6 】

一方で、電力変換器 10 では、スイッチング素子 Q 5 のオン時には、ノード N 1 1 および N 1 2 が電気的に接続される。このときの電力変換器 10 の等価回路が図 27 に示され

る。

**【0237】**

図27を参照して、直流電源B1に関して、スイッチング素子Q5によってノードN12がノードN11と電気的に接続されるので、ノードN12および電力線GLの間に接続されたスイッチング素子Q3を、直流電源B1の下アーム(B1Lアーム)として昇圧チョッパ回路を形成することができる。同様に、ノードN12および電力線PLの間に電気的に接続されたスイッチング素子Q4を直流電源B1の上アーム(B1Uアーム)として、昇圧チョッパ回路を形成することができる。

**【0238】**

また、直流電源B2に対しては、ノードN11および電力線PLの間に接続されたスイッチング素子Q1を下アーム(B2Lアーム)とし、スイッチング素子Q2を上アーム(B2Uアーム)とした昇圧チョッパ回路を形成することができる。

10

**【0239】**

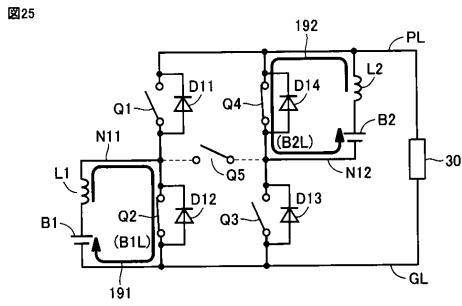

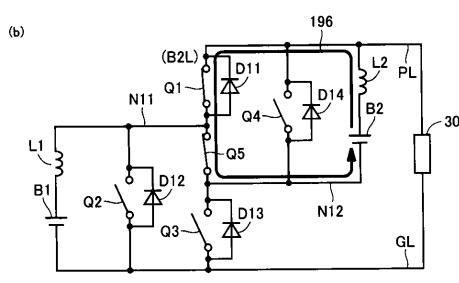

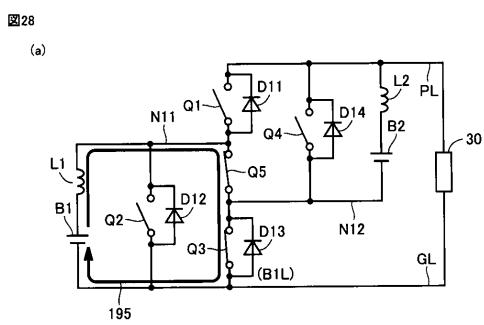

図28には、図27に示した等価回路図において、直流電源B1,B2の下アームオン時ににおける電流経路が示される。

**【0240】**

図28(a)を参照して、スイッチング素子Q3,Q5をオンすることにより、直流電源B1の出力によりリアクトルL1にエネルギーを蓄積するための電流経路195が形成される。一方で、図28(b)に示されるように、スイッチング素子Q1,Q5をオンすることにより、直流電源B2の出力によりリアクトルL2にエネルギーを蓄積するための電流経路196が形成される。

20

**【0241】**

図29には、図27に示した等価回路図において、直流電源B1,B2の上アームオン時ににおける電流経路が示される。

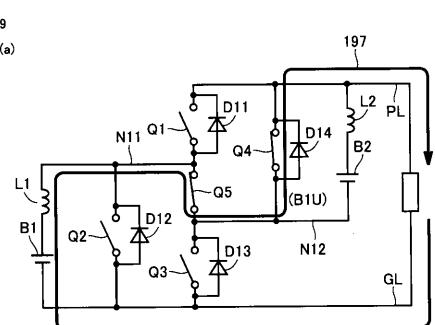

**【0242】**

図29(a)を参照して、直流電源B1に関して、スイッチング素子Q5がオンされた状態でスイッチング素子Q3をオフすることにより、スイッチング素子Q4またはダイオードD14を経由してリアクトルL1の蓄積エネルギーを直流電源B1からのエネルギーとともに電力線PLへ出力するための電流経路197が形成される。上述のように、スイッチング素子Q3およびQ4は相補的にオンオフされるので、スイッチング素子Q3によってB1Lアームを形成するとともに、スイッチング素子Q4によってB1Uアームを形成することができる。

30

**【0243】**

図29(b)を参照して、直流電源B2に関しては、スイッチング素子Q5がオンされた状態でスイッチング素子Q1をオフすることにより、スイッチング素子Q2またはダイオードD12を経由してリアクトルL2の蓄積エネルギーを直流電源B2からのエネルギーとともに電力線PLへ出力するための電流経路198が形成される。上述のように、スイッチング素子Q1およびQ2は相補的にオンオフされるので、スイッチング素子Q1によってB2Lアームを形成するとともに、スイッチング素子Q2によってB2Uアームを形成することができる。

40

**【0244】**

図30には、スイッチング素子Q5のオフ時およびオン時にそれぞれ形成される昇圧チョッパ回路の各アームとスイッチング素子のオンオフとの対応関係が示される。

**【0245】**

図30を参照して、スイッチング素子Q5のオフ時(図24～図26)に形成される昇圧チョッパ回路における各アームを「第1アーム」と称し、スイッチング素子Q5のオン時(図27～図29)に形成される昇圧チョッパ回路の各アームを「第2アーム」と称することとする。

**【0246】**

スイッチング素子Q5のオフ時、すなわち第1アームの形成時には、直流電源B1に対

50

して、上述のように、スイッチング素子Q2のオンによってB1Lアームがオンされる一方で、スイッチング素子Q1のオン（スイッチング素子Q2のオフ）によってB1Uアームがオンされる。また、直流電源B2に対しては、スイッチング素子Q4のオンによってB2Lアームがオンされる一方で、スイッチング素子Q3のオン（スイッチング素子Q4のオフ）によってB2Uアームがオンされる。

#### 【0247】

一方で、スイッチング素子Q5のオン時、すなわち第2アームの形成時には、直流電源B1に対して、上述のように、スイッチング素子Q3のオンによってB1Lアームがオンされる一方で、スイッチング素子Q4のオン（スイッチング素子Q3のオフ）によってB1Uアームがオンされる。また、直流電源B2に対しては、スイッチング素子Q1のオンによってB2Lアームがオンされる一方で、スイッチング素子Q2のオン（スイッチング素子Q1のオフ）によってB2Uアームがオンされる。10

#### 【0248】

このように、第1アームおよび第2アームのいずれにおいても、スイッチング素子Q1およびQ2を相補的にオンオフするとともに、スイッチング素子Q3およびQ4を相補的にオンオフすることにより、直流電源B1およびB2の各々に対して、上アームおよび下アームが交互にオンオフすされるように制御することができる。

#### 【0249】

実施の形態2に従う電力変換器10のパラレル昇圧モードでは、図30に示された第1アームおよび第2アームを併用してDC/DC変換を実行する。ただし、図30に示したように、各スイッチング素子Q1～Q5は、直流電源B1、B2の一方に対して第1アームとして動作するとともに、直流電源B1、B2の他方に対して第2アームとして動作する。このような、第1アームおよび第2アーム間の干渉により、第2アームを適用できる期間が限定される点に留意する必要がある。20

#### 【0250】

具体的には、直流電源B1、B2の一方について第2アームをオンすると、直流電源B1、B2の他方に対しては、上下反対側の第1アームがオンされることになる。たとえば、スイッチング素子Q3、Q5をオンして第2アームのうちのB1Lアームをオンすると（図28（a））、スイッチング素子Q3のオンに応じて、図26と同様に、直流電源B2に対しては第1アームのうちのB2Uアームがオンされる。反対に、スイッチング素子Q4、Q5のオンによって第2アームのうちのB1Uアームをオンすると（図29（a））、図25と同様に、直流電源B2に対しては第1アームのうちのB2Lアームがオンする。30

#### 【0251】

図28（a）、（b）からも理解されるように、第2アームの形成時に、B1LアームおよびB2Lアームの両方をオンした場合には、オン状態のスイッチング素子Q1、Q3、Q5を経由して、電力線PLおよびGL間に短絡経路が形成されてしまう。このため、上述のように、B1LアームおよびB2Lアームの両方をオンする場合には、スイッチング素子Q5のオフによって、第1アーム（図25、図26）を適用することが必要である。40

#### 【0252】

同様に、図29（a）、（b）からも理解されるように、第2アームの形成時に、B1UアームおよびB2Uアームの両方をオンした場合には、オン状態のスイッチング素子Q4、Q5、Q2を経由して、電力線PLおよびGL間に短絡経路が形成されてしまう。このため、上述のように、B1LアームおよびB2Lアームの両方をオンする場合には、スイッチング素子Q5のオフによって、第1アーム（図25、図26）を適用することが必要である。

#### 【0253】

したがって、第2アームを使用できる期間は、直流電源B1、B2の間で、上アームへの指令（オン／オフ）と下アームへの指令（オン／オフ）とが異なる期間に限定される。50

すなわち、直流電源 B 1 に対して上アームオンが指令されている一方で直流電源 B 2 に対して下アームオンが指令されている期間、または、直流電源 B 1 に対して下アームオンが指令されている一方で直流電源 B 2 に対して上アームオンが指令されている期間に限って、第 2 アームを使用することができる。

#### 【 0 2 5 4 】

図 3 1 には、電力変換器 1 0 のパラレル昇圧モードにおけるスイッチング素子 Q 1 ~ Q 5 の各々についてのオンオフ制御のためのゲート論理式が示される。

#### 【 0 2 5 5 】

電力変換器 1 0 のパラレル昇圧モードでは、スイッチング素子 Q 2 は、制御パルス信号 S D 1 に対応してオンオフ制御されるとともに、スイッチング素子 Q 1 は、制御パルス信号 / S D 1 に応答してオンオフされる。さらに、スイッチング素子 Q 4 は、制御パルス信号 S D 2 に応じてオンオフ制御されるとともに、スイッチング素子 Q 3 は制御パルス信号 / S D 2 に応答してオンオフされる。さらに、スイッチング素子 Q 5 は、制御パルス信号 S D 1 および S D 2 の排他的論理和 ( X O R ) に従ってオンオフ制御される。10

#### 【 0 2 5 6 】

制御パルス信号 S D 1 および S D 2 の論理レベルが等しいとき（すなわち、S D 1 = S D 2 = H レベル、または、S D 1 = S D 2 = L レベル）である場合には、スイッチング素子 Q 5 はオフされる。すなわち、スイッチング素子 Q 2 , Q 4 のオンオフ状態が同一であるときには、スイッチング素子 Q 5 がオフされる。このとき、直流電源 B 1 , B 2 のそれぞれに対して、第 1 アームを用いた昇圧チョッパ回路が構成される。20

#### 【 0 2 5 7 】

したがって、第 1 アームを用いる場合には、制御パルス信号 S D 1 および S D 2 の論理レベルが等しいので、スイッチング素子 Q 2 , Q 4 は共通にオンオフされることが理解される。さらに、スイッチング素子 Q 1 , Q 3 についても共通にオンオフされる。さらに、スイッチング素子 Q 1 , Q 3 のペアと、スイッチング素子 Q 2 , Q 4 のペアとは、相補的にオンオフされることになる。したがって、スイッチング素子 Q 1 および Q 2 の相補的なオンオフ、ならびに、スイッチング素子 Q 3 および Q 4 の相補的なオンオフは確保されている。

#### 【 0 2 5 8 】

一方で、制御パルス信号 S D 1 および S D 2 の論理レベルが異なる場合（すなわち、S D 1 = H レベル , S D 2 = L レベル、または、S D 1 = L レベル , S D 2 = H レベル）には、スイッチング素子 Q 5 がオンされる。すなわち、スイッチング素子 Q 2 , Q 4 のオンオフ状態が異なるときには、スイッチング素子 Q 5 がオンされる。このとき、直流電源 B 1 , B 2 のそれぞれに対して、第 2 アームを用いた昇圧チョッパ回路が構成される。30

#### 【 0 2 5 9 】

したがって、第 2 アームを用いる場合には、スイッチング素子 Q 2 , Q 3 が共通にオンオフされるとともに、スイッチング素子 Q 1 , Q 4 が共通にオンオフされる。そして、スイッチング素子 Q 1 , Q 3 のペアと、スイッチング素子 Q 2 , Q 4 のペアとは、相補的にオンオフされることになる。したがって、第 2 アームの使用時にも、スイッチング素子 Q 1 および Q 2 の相補的なオンオフ、ならびに、スイッチング素子 Q 3 および Q 4 の相補的なオンオフは確保されている。40

#### 【 0 2 6 0 】

このように、図 3 1 に示した論理演算式に従って、スイッチング素子 Q 1 ~ Q 5 のオンオフを、制御パルス信号 S D 1 , S D 2 に応じて制御することにより、第 1 アームを用いる昇圧チョッパ回路と、第 2 アームを形成する用いる昇圧チョッパ回路とを自動的に選択しながら、パラレル昇圧モードにおける D C / D C 変換を実行することができる。特に、スイッチング素子 Q 5 によるノード N 1 1 , N 1 2 間の電流経路の形成 / 遮断の制御によって、電力線 P L , G L 間に短絡経路が形成されることを回避しながら、第 1 アームおよび第 2 アームを切換えることができる。

#### 【 0 2 6 1 】

50

20

30

40

50

なお、制御パルス信号 S D 1 ( / S D 1 ) , S D 2 ( / S D 2 ) は、電力変換器 5 0 のパラレル昇圧モードと同様に、図 5 の制御構成によって生成することができる。さらに、P W M 制御部 5 5 0 ( 図 5 ) が図 3 1 に示されたゲート論理式に従って、制御信号 S Q 1 ~ S Q 5 を生成する。

#### 【 0 2 6 2 】

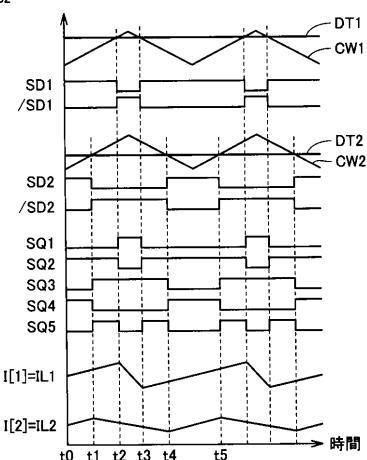

図 3 2 には、電力変換器 1 0 のパラレル接続モードにおける制御動作の比較例を説明するための波形図が示される。図 3 2 では、実施の形態 1 での図 6 と同様に、三角波によって構成されたキャリア波を用いた P W M 制御を比較例として説明する。

#### 【 0 2 6 3 】

図 3 2 を参照して、直流電源 B 1 に対して、制御パルス信号 S D 1 ( / S D 1 ) は、キャリア波 C W 1 とデューティ比 D T 1 との電圧比較に基づく P W M 制御によって生成される。図 3 1 のゲート論理式に示されたように、直流電源 B 1 の出力制御のための制御パルス信号 S D 1 , / S D 1 に基づいて、スイッチング素子 Q 1 , Q 2 のオンオフが制御される。

#### 【 0 2 6 4 】

同様に、直流電源 B 2 に対しても、デューティ比 D T 2 とキャリア波 C W 2 との電圧比較に基づく P W M 制御によって、制御パルス信号 S D 2 ( / S D 2 ) が生成される。図 3 1 のゲート論理式に示されたように、直流電源 B 2 の出力制御のための制御パルス信号 S D 2 , / S D 2 に基づいて、スイッチング素子 Q 3 , Q 4 のオンオフが制御される。

#### 【 0 2 6 5 】

スイッチング素子 Q 5 は、リアクトル電流 I L 1 が上昇する一方でリアクトル電流 I L 2 が低下する期間、および、リアクトル電流 I L 2 が上昇する一方でリアクトル電流 I L 1 が低下する期間でオンされる。すなわち、スイッチング素子 Q 5 は、リアクトル電流 I L 1 について電流経路 1 9 1 が形成される一方で、リアクトル電流 I L 2 について電流経路 1 9 4 が形成される期間、および、リアクトル電流 I L 1 について電流経路 1 9 3 が形成される一方で、リアクトル電流 I L 2 について電流経路 1 9 2 が形成される期間にオンされている。

#### 【 0 2 6 6 】

制御信号 S Q 1 ~ S Q 5 は、図 3 1 に示されたゲート論理式に従って、上記 P W M 制御によって得られた制御パルス信号 S D 1 ( / S D 1 ) , S D 2 ( / S D 2 ) に応じて生成される。ここで、制御パルス信号 S D 1 の H / L レベルと、制御パルス信号 S D 2 の H / L レベルとの組合せに応じて、スイッチング素子 Q 1 ~ Q 5 のオンオフの組み合わせ(スイッチングパターン)は、図 3 3 に示す 4 通りに限定される。

#### 【 0 2 6 7 】

図 3 3 は、パラレル昇圧モードにおけるスイッチング素子 Q 1 ~ Q 5 のスイッチングパターンの一覧を示す図表である。

#### 【 0 2 6 8 】

図 3 2 を参照して、時刻 t 0 ~ t 1 間では、S D 1 = S D 2 = H レベルである。このとき、図 3 3 に示されるように、制御信号 S Q 1 = S Q 3 = S Q 5 = L レベルとなる一方で、S Q 2 = S Q 4 = H レベルとなる。したがって、スイッチング素子 Q 5 がオフされて、第 1 アームを用いた昇圧チョッパ回路が形成される下で、スイッチング素子 Q 1 , Q 3 がオフする一方で、スイッチング素子 Q 2 , Q 4 がオンする。

#### 【 0 2 6 9 】

このとき、図 3 0 から理解されるように、第 1 アームのうちの B 1 L アームおよび B 2 L アームがオンされる。すなわち、直流電源 B 1 および B 2 の各々に対して下アームオンが指令される。したがって、時刻 t 0 ~ t 1 間では、リアクトル電流 I L 1 および I L 2 の両方が上昇する。なお、電力変換器 1 0 の回路構成から明らかなどおり、リアクトル電流 I L 1 は直流電源 B 1 の電流 I [ 1 ] に相当し、リアクトル電流 I L 2 は直流電源 B 1 の電流 I [ 2 ] に相当する。

#### 【 0 2 7 0 】

10

20

30

40

50

再び図32を参照して、時刻 $t_1$ において制御パルス信号SD2がHレベルからLレベルへ変化するため、時刻 $t_1 \sim t_2$ 間では、SD1 = Hレベル、かつ、SD2 = Lレベルである。このとき、図15に示されるように、制御信号SQ2 = SQ3 = SQ5 = Hレベルとなる一方で、SQ1 = SQ4 = Lレベルとなる。したがって、スイッチング素子Q5がオンされて、第2アームを用いた昇圧チョッパ回路が形成される下で、スイッチング素子Q2, Q3がオンする一方で、スイッチング素子Q1, Q4がオフする。

#### 【0271】

このとき、図30から理解されるように、第1アームのうちのB1LアームおよびB2Uアームがオンされる。すなわち、直流電源B1に対して下アームオンが指令される一方で、直流電源B2に対して上アームオンが指令される。したがって、時刻 $t_1 \sim t_2$ 間では、リアクトル電流IL1が上昇する一方で、リアクトル電流IL2は低下する。

10

#### 【0272】

再び図32を参照して、時刻 $t_2$ において制御パルス信号SD1がHレベルからLレベルへ変化するため、時刻 $t_2 \sim t_3$ 間では、SD1 = SD2 = Lレベルである。このとき、図33に示されるように、制御信号SQ2 = SQ4 = SQ5 = Lレベルとなる一方で、SQ1 = SQ3 = Hレベルとなる。したがって、スイッチング素子Q5がオフされて第1アームを用いる昇圧チョッパ回路が形成される下で、スイッチング素子Q1, Q3がオンする一方で、スイッチング素子Q2, Q4がオフする。

#### 【0273】

このとき、図30から理解されるように、第1アームのうちのB1UアームおよびB2Uアームがオンされる。すなわち、直流電源B1およびB2の各々に対して上アームオンが指令される。したがって、時刻 $t_2 \sim t_3$ 間では、リアクトル電流IL1およびIL2の両方が低下する。

20

#### 【0274】

再び図32を参照して、時刻 $t_3$ において制御パルス信号SD1がLレベルからHレベルへ変化するため、時刻 $t_3 \sim t_4$ 間では、SD1 = Hレベル、かつ、SD2 = Lレベルである。したがって、時刻 $t_0 \sim t_1$ 間におけるスイッチングパターンが再現されることにより、第1アームの使用下で、リアクトル電流IL1が上昇する一方で、リアクトル電流IL2が低下するように、スイッチング素子Q1～Q5が制御される。

#### 【0275】

なお、図32の動作例では、DT1 > DT2であるため、時刻 $t_0 \sim t_1$ 間とは反対にSD1 = Lレベル、かつ、SD2 = Hレベルとなる期間が存在していないが、当該期間においては、図33に示されるように、制御信号SQ1 = SQ4 = SQ5 = Hレベルとなる一方で、SQ2 = SQ3 = Lレベルとなる。したがって、スイッチング素子Q5がオンされて、第2アームを用いる昇圧チョッパ回路が形成される下で、スイッチング素子Q1, Q4がオンする一方で、スイッチング素子Q2, Q3がオフする。

30

#### 【0276】

このとき、図30から理解されるように、第2アームのうちのB1UアームおよびB2Lアームがオンされる。すなわち、直流電源B2に対して下アームオンが指令される一方で、直流電源B1に対して上アームオンが指令される。したがって、当該期間では、リアクトル電流IL2が上昇する一方で、リアクトル電流IL1が低下するように、スイッチング素子Q1～Q5が制御されることが理解される。

40

#### 【0277】

図32での時刻 $t_4$ 以降についても、デューティ比DT1, DT2に応じたPWM制御によって、図33に示されたスイッチングパターンに従って、スイッチング素子Q1～Q5を同様に制御することができる。

#### 【0278】

このように、実施の形態2に従う電力変換器10によれば、パラレル昇圧(PB)モードにおいて、直流電源B1, B2の出力制御のデューティ比DT1およびDT2に応じて、図31に示したゲート論理式に従って、スイッチング素子Q1～Q5がオンオフ制御さ

50

れる。これにより、第1アームを用いる昇圧チョッパ回路が形成される期間と、第2アームを用いる昇圧チョッパ回路が形成される期間とを自動的に切換えながら、直流電源B1およびB2が、電力線PL, GLに対して並列にDC/DC変換を実行することができる。

#### 【0279】

特に、電力変換器10のPBモードにおいても、電力変換器50と同様に、直流電源B1およびB2間の電力配分を制御するとともに、出力電圧VHを電圧指令値VH\*に制御することができる。

#### 【0280】

(パラレル昇圧モードにおける電力変換器の電力損失)

10

次に、電力変換器10のパラレル昇圧モードにおける電力損失低減効果について詳細に説明する。

#### 【0281】

電力変換器10は、スイッチング素子Q5のオフ時、すなわち、第1アームを用いる昇圧チョッパ回路が形成されている場合には、図29に示したように、2個の昇圧チョッパ回路を並列接続した回路構成となる。このときのスイッチング素子Q1～Q5による電力損失は、昇圧チョッパ回路2個分の電力損失と同等であることが理解される。

#### 【0282】

一方で、電力変換器50(図1)では、特許文献1のパラレル接続モードと同様のパラレル昇圧(PB)モードにおいて、一部のスイッチング素子に2つの直流電源のDC/DC変換の電流が重畠して流れることにより、導通損失が増加することが懸念される。すなわち、電力変換器50のパラレル接続モードでは、スイッチング素子での電力損失が、昇圧チョッパ回路2個分の電力損失よりも高くなってしまう虞がある。

20

#### 【0283】

これに対して、電力変換器10では、以下に説明するように、上述した第2のアームを用いる昇圧チョッパ回路が形成される期間が設けられることにより、スイッチング素子の導通損失を低減することができる。

#### 【0284】

再び図33を参照して、電力変換器10においてスイッチング素子Q5がオンされる場合、すなわち、第2のアームを用いる昇圧チョッパ回路が形成される期間には、スイッチング素子Q2, Q3, Q5がオン(Q1, Q4はオフ)されるパターンと、スイッチング素子Q1, Q4, Q5がオン(Q2, Q3はオフ)されるパターンとの2つのパターンのみが存在する。すなわち、第2アームを用いる場合には、直流電源B1, B2の間で、異なるアームがオンされる。

30

#### 【0285】

図27から理解されるように、スイッチング素子Q1, Q4, Q5がオンされた場合(第2アーム使用時)には、スイッチング素子Q1およびQ4は、直流電源B1の上アームとして、スイッチング素子Q5を経由して、ノードN11および電力線PLの間に電気的に並列接続される構成となる。さらに、スイッチング素子Q1およびQ4は、直流電源B2の下アームとしては、スイッチング素子Q5およびリクトルL2を経由して、直流電源B2の正極端子および負極端子間に電気的に並列接続される。

40

#### 【0286】

また、スイッチング素子Q2, Q3, Q5がオンされた場合には、スイッチング素子Q2およびQ3は、直流電源B2の上アームとして、スイッチング素子Q5を経由して、ノードN2および電力線GLの間に電気的に並列接続される構成となる。さらに、スイッチング素子Q2およびQ3は、直流電源B1の下アームとしては、スイッチング素子Q5およびリクトルL1を経由して、直流電源B1の正極端子および負極端子間に電気的に並列接続される。

#### 【0287】

このため、スイッチング素子Q1～Q5が、線形特性を有する半導体素子、たとえば、

50

立上がり電圧が0であり、かつ、オン状態における順方向電流 - 電圧特性が線形である、電界効果トランジスタやショットキバリアダイオードで構成される場合には、B1Lアーム、B1Uアーム、B2LアームおよびB2Uアームの各々について、2個のスイッチング素子による電流経路が並列に存在することになる。この結果、並列回路における分流効果によって、各スイッチング素子の通過電流が、第1のアーム形成を有する昇圧チョッパ回路の形成時、すなわち、各アームが1個のスイッチング素子で構成される場合と比較して低減する。これにより電流量に依存する、スイッチング素子の導通損失を低減することができる。

#### 【0288】

一方で、スイッチング素子Q1～Q5が、ダイオードやIGBT(Insulated Gate Bipolar Transistor)のような非線形特性を有する半導体素子で構成される場合には、単純な分流効果によらないメカニズムで導通損失の低減が実現される。以下では、そのメカニズムについて詳細に説明する。10

#### 【0289】

上述のように、第2アームを用いる場合には、スイッチング素子Q1, Q4, Q5がオン(Q2, Q3はオフ)されるパターンと、スイッチング素子Q2, Q3, Q5がオン(Q1, Q4はオフ)されるパターンとの2つのパターンしか存在しない。電力変換器10の回路構成の対称性から、上記のいずれのパターンでも生じる現象は同じであるので、以下では、スイッチング素子Q2, Q3, Q5がオン(Q1, Q4はオフ)されるパターン、すなわち、B1LアームおよびB2Uアームがオンされる場合の動作について説明する20。

#### 【0290】

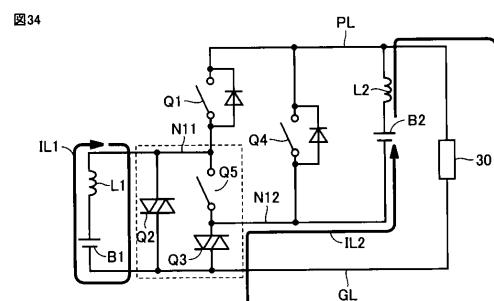

まず比較のために、第1アームを用いる昇圧チョッパ回路において、B1LアームおよびB2Uアームをオンする場合を考える。この場合には、スイッチング素子Q1, Q3, Q5がオフされる一方で、スイッチング素子Q2およびQ3がオンされる。図34には、このときの等価回路図が示される。

#### 【0291】

図34を参照してスイッチング素子Q2およびQ3は、対応の制御信号SQ2およびSQ3がHレベルに設定されることにより電流経路を形成可能な状態に制御されている。すなわち、スイッチング素子Q2, Q3は、双方向にダイオードが並列接続された状態と等価である。一方で、スイッチング素子Q5はオフ状態とされているため、ノードN11およびN12間の電流経路は遮断されている。30

#### 【0292】

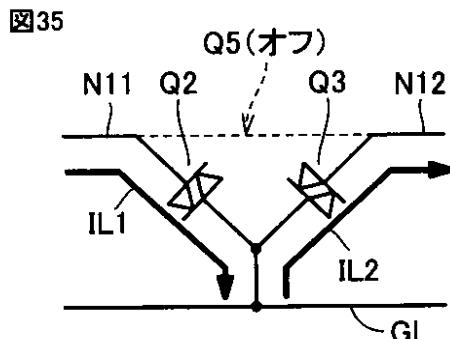

図35は、図34中の点線で囲まれた部分の拡大図である。

図35を参照して、スイッチング素子Q2によるB1Lアームのオンに応じて、直流電源B1からリアクトルL1を通過したリアクトル電流IL1は、スイッチング素子Q2によって形成された、ノードN11から電力線GLへの電流経路を流れる。

#### 【0293】

また、スイッチング素子Q3によるB2Uアームのオンに応じて、直流電源B2からリアクトルL2を通過したリアクトル電流IL2は、スイッチング素子Q3によって形成された、電力線GLからノードN12への電流経路を流れる。このように、第1アーム形成時(Q5オフ時)においてB1LアームおよびB2Uアームがオンされる場合には、スイッチング素子Q2にリアクトル電流IL1が流れ、スイッチング素子Q3に電流IL2が流れる。40

#### 【0294】

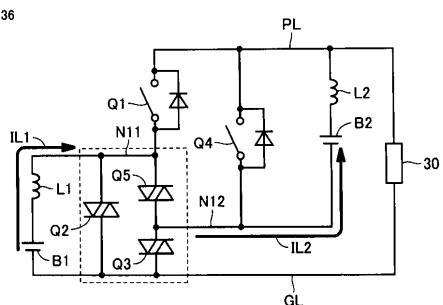

図36は、第2アームを用いる昇圧チョッパ回路においてB1LアームおよびB2Uアームがオンされた場合の等価回路図である。

#### 【0295】

図36を参照して、第2アームを用いる場合には、制御信号SQ2, SQ3, SQ5がHレベルに設定されることにより、スイッチング素子Q2, Q3, Q5の各々は、双方向

10

20

30

40

50

に電流経路を形成可能な状態、すなわち、双方向にダイオードが並列接続された状態となる。

#### 【0296】

図37は、図36における点線で囲んだ部分の等価回路図である。

図37を参照して、第2アームが用いられる場合には、図35とは異なり、スイッチング素子Q5によってもノードN11およびN12間に電流経路を形成することが可能である。したがって、リアクトル電流IL1およびIL2の経路は、ノードN11,N12の電位関係によって変化する。

#### 【0297】

図35および図37にも示したように、非線形特性を有するスイッチング素子（たとえばIGBT）は、オン状態では、ダイオードと同等の特性を有する。一般的に知られているように、ダイオードは電流・電圧特性が非線形であり、電流が流れる導通状態に遷移するためには、立上がり電圧以上の順方向電圧が印加されることが必要になる。10

#### 【0298】

また、ダイオードにおいて、電流増加に対する順方向電圧増加の感度は低く、立上がり電圧の2倍以上の順方向電圧を生じさせるには、大きな電流が必要であることが知られている。すなわち、導通して電流が通流されている状態のダイオードの各々には、ほぼ同じ大きさの順方向電圧が発生している。

#### 【0299】

ダイオードの上記性質のため、図37に示した等価回路において、ループ状に接続されたスイッチング素子Q2,Q3,Q5のすべてに電流が流れている状態（導通状態）は発生しない。なぜなら、ほぼ同等の3つの電圧がループ状の閉路を形成するとすれば、それぞれの電圧がどのような向きであっても、キルヒホフ電圧則が成立しないからである。20

#### 【0300】

したがって、図37に示された等価回路中において、スイッチング素子Q2,Q3,Q5のうちの少なくとも2つのスイッチング素子までしか導通状態となることができない。したがって、図37の等価回路では、スイッチング素子Q2,Q3,Q5間の単純な分流効果による導通損失の低減は期待することができない。

#### 【0301】

しかしながら、スイッチング素子Q2,Q3,Q5の導通パターンの組合せ毎に導通損失は異なるため、最も損失の低い組み合わせに従う導通経路を選択することで、導通損失を低減することが可能である。特に、電力変換器10では、上記のような導通損失を低減するための導通経路の選択は、センサ等を用いた制御を行なうことなく、スイッチング素子Q2,Q3,Q5のすべてをオンしておくだけで、自動的に損失が最小となる導通経路が選択される点が特徴である。以下、この損失低減メカニズムをさらに詳細に説明する。30

#### 【0302】

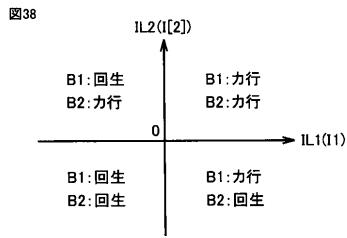

まず、電力変換器10において、リアクトル電流IL1およびIL2の方向の組合せは、図38に示す4通りに区別される。

#### 【0303】

図38を参照して、リアクトル電流IL1およびIL2の正／負の組合せから、電力変換器10の動作領域は、直流電源B1およびB2の両方が力行動作する領域( $IL1 > 0$ , $IL2 > 0$ )と、直流電源B1が回生動作する一方で直流電源B2が力行動作する領域( $IL1 < 0$ , $IL2 > 0$ )と、直流電源B1,B2の両方が回生動作をする領域( $IL1 < 0$ , $IL2 < 0$ )と、直流電源B1が力行動作する一方で直流電源B2が回生動作する領域( $IL1 > 0$ , $IL2 < 0$ )に分けられる。40

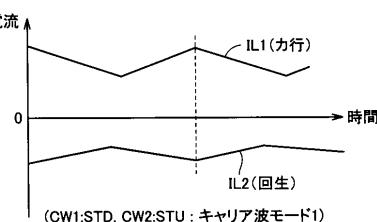

#### 【0304】

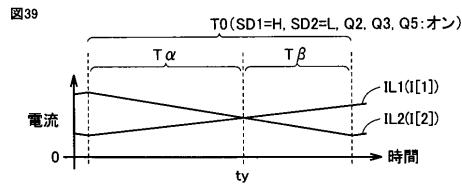

まず、直流電源B1およびB2の両方が力行動作する場合、すなわち図38の第1象限における電力変換器10の動作を説明する。この場合における、リアクトル電流IL1およびIL2の波形例が図39に示される。

#### 【0305】

図39を参照して、リアクトル電流IL1およびIL2が正であって( IL1 > 0 , IL2 > 0 )、かつ、B1Lアームがオン( SD1 = H レベル )される一方で、B2Uアームがオフ( SD2 = L レベル )される期間T0における電流波形が示される。すなわち、期間T0において、制御パルス信号SD1 = H レベルおよびSD2 = L レベルであるから、スイッチング素子Q2 , Q3 , Q5がオンされている。

#### 【0306】

したがって、期間T0では、リアクトル電流IL1が上昇する一方で、リアクトル電流IL2が低下する。期間T0は、リアクトル電流IL1およびIL2の大小が逆転する時刻tyを境界として、IL2 > IL1である期間T<sub>1</sub>および、IL1 > IL2である期間T<sub>2</sub>に分割される。

10

#### 【0307】

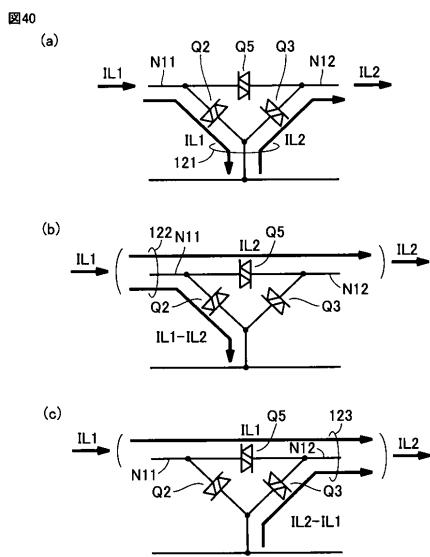

上述のように、スイッチング素子Q2 , Q3 , Q5をオンする場合にも、スイッチング素子Q2 , Q3 , Q5のすべてが同時に導通状態とはならない。したがって、図37の等価回路で形成され得る電流経路は、図40の(a)~(c)の3通りのいずれかとなる。

#### 【0308】

図40(a)を参照して、スイッチング素子Q2およびQ3が導通状態となるときには、電流経路121が形成される。電流経路121は、リアクトル電流IL1がスイッチング素子Q2を流れる電流経路と、リアクトル電流IL2がスイッチング素子Q3を流れる電流経路とを含む。この結果、スイッチング素子Q2 , Q3 , Q5による導通損失の和P<sub>1s1</sub>は、下記(5)式で示される。

20

#### 【0309】

$$P_{1s1} = V_{fe} \times ( |IL1| + |IL2| ) \dots \quad (5)$$

式(5)において、V<sub>fe</sub>は、オン状態のスイッチング素子に相当する各ダイオードの順方向電圧である。V<sub>fe</sub>は、正の一一定値とみなすことができる。

#### 【0310】

図40(b)を参照して、スイッチング素子Q2およびQ5が導通状態となるときには、電流経路122が形成される。電流経路122は、スイッチング素子Q2を電流(IL1 - IL2)が流れる電流経路と、リアクトル電流IL2がスイッチング素子Q5を流れる電流経路とを含む。このときのスイッチング素子Q2 , Q3 , Q5による導通損失P<sub>1s2</sub>は、下記(6)式で示される。

30

#### 【0311】

$$P_{1s2} = V_{fe} \times ( |IL2| + |IL1 - IL2| ) \dots \quad (6)$$

図40(c)を参照して、スイッチング素子Q3およびQ5が導通状態となるときには、電流経路123が形成される。電流経路123は、スイッチング素子Q3を電流(IL2 - IL1)が流れる電流経路と、リアクトル電流IL1がスイッチング素子Q5を流れる電流経路とを含む。このときのスイッチング素子Q2 , Q3 , Q5による導通損失P<sub>1s3</sub>は、下記(7)式で示される。

#### 【0312】

$$P_{1s3} = V_{fe} \times ( |IL1| + |IL2 - IL1| ) \dots \quad (7)$$

図40(a)に示された電流経路121は、図34に示された、第1アームを用いる昇圧チヨッパ回路においてB1LアームおよびB2Uアームをオンするときの電流経路と同じである。したがって、図40(a)における導通損失は、第1アームの形成時と同等である。

40

#### 【0313】

図41は、図40(a)~(c)に示された電流経路121~123のそれぞれにおける導通損失P<sub>1s1</sub>~P<sub>1s3</sub>の推移を示す波形図である。

#### 【0314】

図41を参照して、図39に示されるようにリアクトル電流IL1およびIL2が推移することに伴い、導通損失P<sub>1s1</sub>~P<sub>1s3</sub>は、いずれも正であるIL1およびIL2の変化に応じて、式(5)~(7)に従って変化する。

50

**【0315】**

$I_L 2 > I_L 1$  である期間  $T$  では、式(5)～式(7)の比較から理解されるとおり、電流経路 123 (図40(c)) が形成されるときにおける導通損失  $P_{1s3}$  が、電流経路 121, 122 が形成されるときの導通損失  $P_{1s1}, P_{1s2}$  よりも小さくなる。

**【0316】**

これに対して、 $I_L 1 > I_L 2$  となる期間  $T$  においては、電流経路 122 (図40(b)) による導通損失  $P_{1s2}$  が電流経路 121, 123 を形成したときの導通損失  $P_{1s1}$  および  $P_{1s3}$  よりも小さくなる。

**【0317】**

ここで、期間  $T$  ( $I_L 1 < I_L 2$ ) に形成され得る電流経路について考察する。まず 10 、図40(a) に示された電流経路 121 の場合、スイッチング素子 Q5 に、スイッチング素子 Q2 および Q5 の順方向電圧の和が印加されることになる。この順方向電圧の和は、スイッチング素子 Q3 の立上がり電圧を超えてしまうため、この現象は、スイッチング素子 Q3 が導通していない事象と矛盾する。したがって、期間  $T$  において、図40(a) に示された電流経路 121 が形成されることはない。

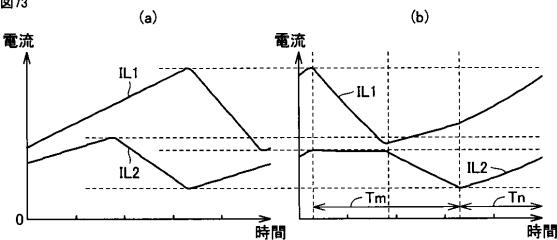

**【0318】**