(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2014-0040216

(43) 공개일자 2014년04월02일

- (51) 국제특허분류(Int. Cl.)

*H01L 31/068* (2006.01) *H01L 31/18* (2006.01)

- (21) 출원번호 10-2014-7000725

- (22) 출원일자(국제) 2012년06월15일

심사청구일자 없음

- (85) 번역문제출일자 2014년01월10일

- (86) 국제출원번호 PCT/US2012/042736

- (87) 국제공개번호 WO 2012/174421

국제공개일자 2012년12월20일

- (30) 우선권주장

13/160,721 2011년06월15일 미국(US)

- (71) 출원인

베리안 세미콘덕터 이큅먼트 어소시에이츠, 잉크.

미국 01930 매사추세츠주 글로스터 도리 로드 35

- (72) 발명자

그래프, 존, 더블유.

미국 01907 매사추세츠 스왑스켓 워커 로드 25

- (74) 대리인

특허법인에이아이피

전체 청구항 수 : 총 9 항

(54) 발명의 명칭 폴리실리콘 에미터 솔라 셀들에 대한 패턴화된 도핑

### (57) 요 약

폴리실리콘 솔라 셀의 개선된 제조 방법이 개시된다. n-형 및 p-형 영역들을 갖는 폴리실리콘 층을 생성하기 위하여, 층이 일 유형의 도펜트(dopant)가 존재하는 상태에서 성장된다. 도핑된 폴리실리콘 층이 생성된 후, 반대되는 도펜트 전도성의 이온들이 폴리실리콘 층의 부분들에 선택적으로 주입된다. 이러한 선택적인 주입은 샐도우 마스크를 사용하여 수행될 수 있다.

**대 표 도** - 도3d

## 특허청구의 범위

### 청구항 1

제 1 표면 및 제 2 표면을 갖는 기판을 사용하는 솔라 셀 생산 방법으로서,

상기 기판의 상기 제 2 표면 상에 터널 산화물 층(tunnel oxide layer)을 형성하는 단계;

그 안에 내포된 제 1 도편트를 갖는 폴리실리콘 층을 상기 터널 산화물 층 상에 형성하는 단계로서, 상기 폴리실리콘 층은 제 1 전도성 유형을 갖는, 단계;

상기 폴리실리콘 층의 영역들을 이온 빔으로부터 블로킹(block)하기 위하여, 상기 폴리실리콘 층과 상기 이온 빔 사이에 마스크를 위치시키는 단계;

주입되는 영역들의 상기 전도성을 제 2 전도성으로 변화시키기에 충분한 양의 제 2 도편트의 이온들을 상기 폴리실리콘 층의 영역들 새로 주입하고, 그럼으로써 제 1 전도성을 갖는 제 1 주입된 영역들 및 상기 제 1 주입된 영역들과 반대되는 전도성을 갖는 제 2 주입된 영역들을 형성하는 단계로서, 상기 제 2 도편트는 상기 제 1 전도성과 반대되는 제 2 전도성을 갖는, 단계를 포함하는, 솔라 셀 생산 방법.

### 청구항 2

청구항 1에 있어서,

상기 폴리실리콘 층은, 실레인(silane)을 포함하는 가스 및 다이보레인(diborane), 포스핀(phosphine) 및 아르신(arsine)으로 구성된 그룹으로부터 선택된 도편트 가스의 증착에 의해 형성되는, 솔라 셀 생산 방법.

### 청구항 3

청구항 2에 있어서,

상기 도편트 가스는 다이보레인을 포함하며, 상기 제 2 도편트는 V족 원소를 포함하는, 솔라 셀 생산 방법.

### 청구항 4

청구항 2에 있어서,

상기 도편트 가스는 포스핀 또는 아르신을 포함하며, 상기 제 2 도편트는 III족 원소를 포함하는, 솔라 셀 생산 방법.

### 청구항 5

청구항 1에 있어서,

상기 주입하는 단계 이후 상기 기판을 열적으로 처리하는 단계를 더 포함하며,

상기 처리는 500°C 및 600°C 사이의 온도에서 수행되는, 솔라 셀 생산 방법.

### 청구항 6

청구항 1에 있어서,

상기 제 1 주입된 영역들 및 상기 제 2 주입된 영역들의 각각이 접촉하는 것을 방지하기 위하여, 상기 제 1 주입된 영역들과 상기 제 2 주입된 영역들 사이에 트렌치(trench)를 생성하는 단계를 더 포함하는, 솔라 셀 생산 방법.

### 청구항 7

제 1 표면 및 제 2 표면을 갖는 기판을 사용하는 솔라 셀 생산 방법으로서,

상기 기판의 상기 제 2 표면 상에 터널 산화물 층을 형성하는 단계;

상기 터널 산화물 층 상에 폴리실리콘 층을 형성하는 단계;

제 1 전도성을 갖는 제 1 도편트의 이온들을 상기 폴리실리콘 층 내에 주입하는 단계;

상기 폴리실리콘 층의 영역들을 이온 범으로부터 블로킹하기 위하여, 상기 폴리실리콘 층과 상기 이온 범 사이에 마스크를 위치시키는 단계;

상기 주입된 영역들의 상기 전도성을 제 2 전도성으로 변화시키기에 충분한 양의 제 2 도편트의 이온들을 상기 폴리실리콘 층의 영역들 내로 주입하고, 그럼으로써 제 1 전도성을 갖는 제 1 주입된 영역들 및 상기 제 1 주입된 영역들과 반대되는 전도성을 갖는 제 2 주입된 영역들을 형성하는 단계로서, 상기 제 2 도편트는 상기 제 1 전도성과 반대되는 제 2 전도성을 갖는, 단계를 포함하는, 솔라 셀 생산 방법.

## 청구항 8

청구항 7에 있어서,

상기 제 1 주입된 영역들 및 상기 제 2 주입된 영역들의 각각이 접촉하는 것을 방지하기 위하여, 상기 제 1 주입된 영역들과 상기 제 2 주입된 영역들 사이에 트렌치를 생성하는 단계를 더 포함하는, 솔라 셀 생산 방법.

## 청구항 9

제 1 표면 및 제 2 표면을 갖는 기판을 사용하는 솔라 셀 생산 방법으로서,

상기 기판의 상기 제 2 표면 상에 터널 산화물 층을 형성하는 단계;

상기 터널 산화물 층 상에 폴리실리콘 층을 형성하는 단계;

상기 폴리실리콘 층의 영역들을 이온 범으로부터 블로킹하기 위하여, 상기 폴리실리콘 층과 상기 이온 범 사이에 제 1 마스크를 위치시키는 단계;

제 1 전도성을 갖는 제 1 도편트의 이온들을 상기 폴리실리콘 층 내에 주입하고, 그럼으로써 제 1 주입된 영역들을 생성하는 단계;

상기 폴리실리콘 층의 영역들을 이온 범으로부터 블로킹하기 위하여, 상기 폴리실리콘 층과 상기 이온 범 사이에 제 2 마스크를 위치시키는 단계;

상기 제 1 전도성과 반대되는 제 2 전도성을 갖는 제 2 도편트의 이온들을 주입하고, 그럼으로써 상기 제 1 주입된 영역들과 반대되는 전도성을 갖는 제 2 주입된 영역들을 형성하는 단계를 포함하며,

상기 제 1 주입된 영역들과 상기 제 2 주입된 영역들이 접촉하지 않도록, 상기 제 2 마스크가 상기 제 1 마스크에 대해 정렬되는, 솔라 셀 생산 방법.

## 명세서

### 배경기술

[0001] 이온 주입은 작업물 내로 전도성-변화 불순물들을 도입하기 위한 표준 기술이다. 이온 소스 내에서 희망되는 불순물 재료가 이온화되며, 이온들이 규정된 이온 범을 형성하기 위해 가속되고, 이온 범이 작업물의 표면으로 보내진다. 범의 활성 이온들이 대량의 작업물 재료 내에 침투하고, 희망되는 전도성의 영역을 형성하기 위하여 작업물 재료의 결정 격자 내에 끼워 넣어진다.

[0002] 솔라 셀들은 실리콘 작업물들을 사용하는 디바이스의 일 예이다. 고-성능 솔라 셀들의 제조 또는 생산에 대한 임의의 절감된 비용 또는 고-성능 솔라 셀들에 대한 임의의 효율성 개선이 솔라 셀들의 전세계적인 구현에 긍정적인 영향을 줄 수 있다. 이는 이러한 청정 에너지 기술의 더 광범위한 적용가능성을 가능하게 할 것이다.

[0003] 솔라 셀들은 전형적으로 기판 재료로서 주로 실리콘을 사용하는 다른 반도체 디바이스들에 대해 사용되는 것과 동일한 프로세스들을 사용하여 제조된다. 반도체 솔라 셀은, 반도체 재료의 광자들의 흡수를 통해 생성되는 전하 캐리어들을 분리하는 내장 전기장을 갖는 단순한 디바이스이다. 이러한 전기장은 전형적으로 반도체 재료의 차등 도핑에 의해 생성되는 p-n 접합(다이오드)의 형성을 통해 생성된다. 반대 극성의 불순물들로 반도체 기판의 일부분(예를 들어, 표면 영역)을 도핑하는 것이 p-n 접합을 형성하며, 이는 광을 전기로 변환하는 광전지 디바이스로서 사용될 수 있다.

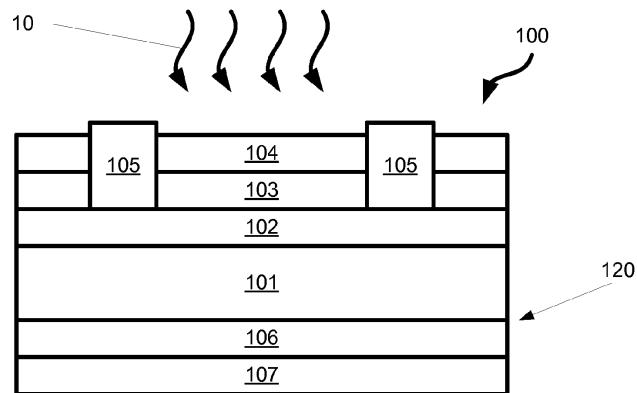

[0004] 도 1은 p-n 접합(120)이 조사 표면(illuminated surface)으로부터 떨어져 위치되는 대표적인 솔라 셀(100)의

단면을 도시한다. 화살표들에 의해 나타나는 것과 같이 광자들(10)은 상부(또는 조사) 표면을 통해 솔라 셀(100)에 진입한다. 이러한 광자들은, 기판(100)을 관통하는 광자들의 수를 최대화하고 기판으로부터 다시 반사되는 광자들의 수를 최소화하도록 설계된 반사방지 코팅(anti-reflective coating: ARC)(104)을 통해 이동한다. ARC(104)는  $\text{SiN}_x$  층으로 이루어질 수 있다. ARC(104) 아래에 패시베이션 층(passivation layer)(103)이 존재할 수 있으며, 이는 이산화 실리콘으로 이루어질 수 있다. 물론, 다른 유전체들이 사용될 수 있다. 솔라 셀(100)의 후면 상에 알루미늄 에미터 영역(106) 및 알루미늄 층(107)이 존재한다. 이러한 설계는 일 예에 있어 알루미늄 백 에미터 셀(Al back emitter cell)로서 지칭될 수 있다.

[0005] 내부적으로, 솔라 셀(100)이 p-n 접합(120)을 갖도록 형성된다. 이러한 접합이 솔라 셀(100)의 하부 표면에 대체로 평행한 것으로 도시되지만, 접합이 표면에 평행하지 않은 다른 구현예들이 존재할 수 있다. 일부 실시예들에 있어, 솔라 셀(100)은 n-형 기판(101)을 사용하여 제조된다. 광자들(10)은 전면 표면 필드(front surface field: FSF)(102)로서도 알려진 n+ 도핑된 영역을 통해 솔라 셀(100)에 진입한다. 충분한 에너지(반도체의 밴드갭(bandgap) 이상의)를 갖는 광자들은 반도체 재료의 가전자대(valence band) 내의 전자들을 전도대(conduction band)로 상승시키는(promote) 것을 가능하게 한다. 이러한 자유 전자와 연관된 것이 가전자대 내의 대응하는 포지티브하게 대전된 홀(positively charged hole)이다. 외부 부하를 구동하는 광전류를 생성하기 위하여, 이러한 전자-홀(e-h) 쌍들이 분리되어야 한다. 이는 p-n 접합(120)에서의 내장(built-in) 전기장을 통해 이루어진다. 따라서 p-n 접합(120)의 공핍 영역에서 생성되는 임의의 e-h 쌍들은, 디바이스의 공핍 영역으로 확산하는 임의의 다른 소수 캐리어(minority carrier)들로서 분리된다. 입사 광자들(10)의 대부분이 솔라 셀(100)의 표면 영역들 근처에서 흡수되기 때문에, 에미터 내에서 생성되는 소수 캐리어들이 공핍 영역으로 확산해야 하며, 다른 면에 걸쳐 스윕(sweep)된다.

[0006] 일부 광자들(10)은 전면 표면 필드(102)를 통해 이동하며, p-형 에미터(106)에 진입한다. 이러한 광자들(10)은 p-형 에미터(106) 내의 전자들을 여기시킬 수 있으며, 이들은 전면 표면 필드(102) 내로 자유롭게 이동한다. 연관된 홀들은 에미터(106) 내에 남아 있다. 이러한 p-n 접합(120)의 존재에 의해 유발되는 전하 분리의 결과로서, 광자들(10)에 의해 생성되는 여분의 캐리어들(전자들 및 홀들)이 그 후 회로를 완성하기 위해 외부 부하를 구동하는데 사용될 수 있다.

[0007] 전면 표면 필드(102)를 통해 베이스(base)를 외부 부하를 통해 에미터(106)에 외부적으로 연결함으로써, 전류를 전도하고 그에 따라 파워를 제공하는 것이 가능하다. 이를 달성하기 위하여, 전형적으로 금속의 그리고 일부 실시예들에 있어 은인, 접촉부들(105)이 전면 표면 필드(102)의 외부 표면 상에 배치된다.

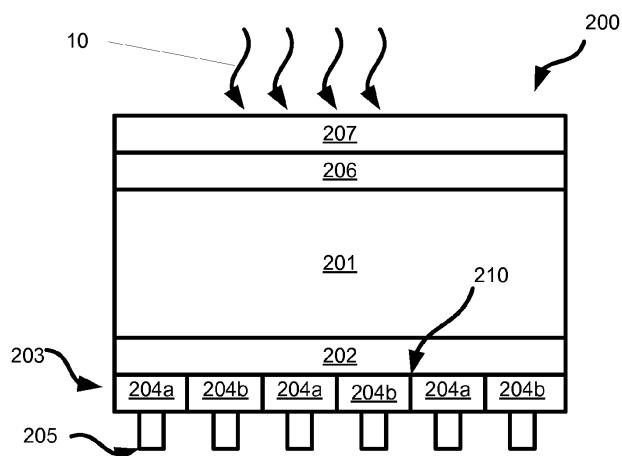

[0008] 도 2는 솔라 셀(200)의 제 2 실시예를 예시한다. 이러한 실시예에 있어, 기판(201) 내에 p-n 접합이 생성되지 않는다. 오히려, 전형적으로 n-형 실리콘 기판인 기판(201)이 얇은 산화물 터널층(thin oxide tunnel layer)(202)에 의해 후방 표면으로부터 분리된다. 터널 산화물 층은, 1 나노미터와 4 나노미터 사이와 같이, 층(202)을 통해 전자들이 터널링(tunneling)할 수 있도록 충분히 얇다. 이러한 층(202)은 이산화 실리콘 또는 다른 적절한 유전체 재료일 수 있다. 폴리실리콘 층(203)이 터널 산화물 층의 대향면 상에 있다. 이러한 층은 서로 인접하여 배치된 n-형 영역들(204a) 및 p-형 영역들(204b)을 갖는다. 이러한 영역들이 만날 때, p-n 접합(210)이 형성된다. 접촉부들(25)이 그 뒤 n-형 영역들(204a) 및 p-형 영역들(204b)에 적용된다. 일부 실시예에 있어, 제 2 터널 산화물 층(206)이 기판(201)의 전면 표면 상에 존재한다. 이러한 실시예에 있어, n-형 폴리실리콘 층(207)이 제 2 터널 산화물 층(206)에 적용될 수 있다.

[0009] 솔라 셀의 이러한 실시예들은 몇가지 이점들을 갖는다. 먼저, 그 효율성이 도 1의 종래의 솔라 셀에 비해 대단히 높을 수 있다. 이는 기판 내의 캐리어들의 감소된 재결합에 기인할 수 있다.

[0010] 그러나 이러한 폴리실리콘 솔라 셀의 생산은 다수의 프로세스 단계들을 요구하며 시간 소모적이고 비용이 비싸다. 따라서, 폴리실리콘 솔라 셀들의 개선된 제조 방법이 요구된다.

## 발명의 내용

### 과제의 해결 수단

[0011] 폴리실리콘 솔라 셀의 개선된 제조 방법이 개시된다. p-형 및 n-형 영역들을 갖는 폴리실리콘 층을 생성하기 위하여, 일 유형의 도펀트가 존재하는 상태에서 층이 성장된다. 도핑된 폴리실리콘 층이 생성된 후, 반대되는 도펀트 전도성의 이온들이 폴리실리콘 층의 부분들 내에 선택적으로 주입된다. 이러한 선택적인 주입은 세도우 마스크를 사용하여 수행될 수 있다.

## 도면의 간단한 설명

[0012]

본 발명의 더 양호한 이해를 위하여, 참조로써 본 명세서에 포함된 첨부된 도면들에 대한 참조가 이루어지며, 도면들 내에서:

도 1은 종래기술의 솔라 셀의 제 1 실시예의 단면 측면도이다;

도 2는 종래기술의 솔라 셀의 제 2 실시예의 단면 측면도이다;

도 3a 내지 도 3e는 일련의 제조 프로세스 단계들의 일 실시예를 예시한다;

도 4a 내지 도 4e는 일련의 제조 프로세스 단계들의 제 2 실시예를 예시한다; 및

도 5a 내지 도 5b는 일련의 제조 프로세스 단계들의 제 3 실시예를 예시한다.

## 발명을 실시하기 위한 구체적인 내용

[0013]

솔라 셀의 실시예들이 본 명세서에서 이온 주입기와 함께 설명된다. 범라인 이온 주입기들, 플라즈마 도핑 이온 주입기들, 또는 플러드(flood) 이온 주입기들이 사용될 수 있다. 이에 더하여, 다른 주입 시스템들이 사용될 수 있다. 예를 들어, 질량 분석기가 없는 이온 주입기 또는 플라즈마 쉬스를 수정함으로써 이온들을 포커싱하는 플라즈마 툴(tool)이 또한 사용될 수 있다. 솔라 셀의 주입 종 부분들에만 포커싱되는 이온 범, 또는 그리드-포커스형 플라즈마 시스템(grid-focused plasma system)들이 또한 본 명세서에 개시되는 실시예들에 대해 사용될 수 있다. 그러나, 기체 확산법(gaseous diffusion), 노 확산법(furnace diffusion), 레이저 도핑, 다른 플라즈마 프로세싱 툴들, 또는 당업계에서 공지된 다른 방법들이 사용될 수 있다. 또한, 주입이 설명되지만, 도핑된 층들의 증착이 또한 수행될 수 있다. 또한, 특정 n-형 및 p-형 도편트들이 열거되지만, 그 대신 다른 n-형 및 p-형 도편트들이 사용될 수 있으며, 본 발명은 열거되는 도편트에 한정되지 않는다. 따라서, 본 발명은 이하에서 설명되는 특정 실시예들에 한정되지 않는다.

[0014]

이상에서 설명된 바와 같이, 폴리실리콘 셀들은 종래의 솔라 셀들에서 불가능한 효율성 이점들을 제공할 수 있다. 그러나, 현재 이러한 폴리실리콘 솔라 셀들에 대한 제조 프로세스들은 비싸고 시간이 많이 소요되어, 그들의 채택에 악영향을 미친다. 이러한 폴리실리콘 솔라 셀들의 제조와 연관된 중요한 이슈들 중 하나는 n-형 영역들 및 p-형 영역들을 갖는 폴리실리콘 층의 형성이다.

[0015]

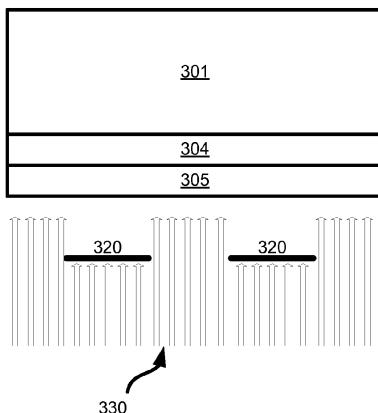

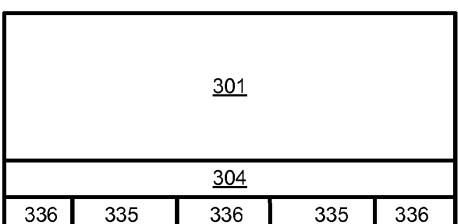

도 3a 내지 도 3e는 폴리실리콘 솔라 셀(300)을 생성하기 위한 일련의 제조 단계들을 도시한다. 도 3a는 기판(301)을 도시한다. 이러한 기판(301)은 n-형 실리콘 기판과 같은 임의의 적절한 기판일 수 있다. 기판(301)은 전면 표면(302) 및 후방 표면(303)을 갖는다. 전면 표면(302)이 태양광에 노출되며, 반면 전기 접촉부들이 후방 표면(303) 상에 생성될 것이다.

[0016]

도 3b는 기판(301)의 후방 표면(303) 상에 형성된 터널 산화물 층(tunnel oxide layer)(304)을 도시한다. 터널 산화물 층은 약 1 nm와 4 nm 사이의 두께일 수 있다. 일부 실시예들에 있어, 열 산화(thermal oxidation)가 터널 산화물 층을 성장시키는 데 사용된다. 이러한 프로세스는 산소(산소 분자 또는 수증기 중 하나)가 기판의 후방 표면과 반응하여 이산화 실리콘을 형성하도록 하기 위하여 800°C 이상의 온도에서 노내에서 수행될 수 있다. 따라서, 습식 및 건식 산화 둘 모두가 사용될 수 있다.

[0017]

도 3c는 터널 산화물(304)에 인접한 폴리실리콘 층(305)을 도시한다. 일 실시예에 있어, 폴리실리콘 층(305)은 저압(1 Torr 미만과 같은) 및 575°C로부터 650°C까지의 범위의 온도에서 실레인( $\text{SiH}_4$ )을 사용하여 증착된다. 이러한 프로세스는 또한 저압 화학 기상 증착(LPCVD)으로서 알려져 있다. 다른 실시예들에 있어, 대기압 화학 기상 증착(APCVD), 플라즈마 증강 CVD(PECVD) 또는 다른 적절한 프로세스가 폴리실리콘 층(305)을 성장시키는데 사용될 수 있다. 이러한 층(305)은 실레인에 더하여 도편트-함유 가스를 도입하는 동안 성장될 수 있다. 일 실시예에 있어, 증착 프로세스 동안 다이보레인( $\text{B}_2\text{H}_6$ )이 도입된다. 이는 폴리실리콘 층이 성장할 때 p-형 도편트들을 폴리실리콘 층에 부가하며, 그럼으로써 폴리실리콘 층(305) 전체에 걸쳐 p-형 영역을 생성한다. 일 예에 있어, 폴리실리콘 층 내의 봉소의 농도는  $1\text{e}17/\text{cm}^3$ 과  $1\text{e}20/\text{cm}^3$  사이이다. 다른 실시예에 있어, 포스핀(phosphine)( $\text{PH}_3$ ) 또는 아르신(arsine)( $\text{AsH}_3$ )이 증착 프로세스 동안 도입되며, 그럼으로써 폴리실리콘 층(305) 전체에 걸쳐 n-형 영역을 생성한다. 일 예에 있어, 폴리실리콘 층 내의 인(또는 비소)의 농도는  $1\text{e}17/\text{cm}^3$ 과  $1\text{e}20/\text{cm}^3$  사이이다. 일 실시예에 있어 이러한 폴리실리콘 층(305)이 50 nm와 500nm 사이의 두께까지

성장되지만, 다른 두께들이 사용될 수 있다.

[0018] 도 3d는 폴리실리콘 솔라 셀(300)의 제조 프로세스의 다음 단계를 도시한다. 새도우 마스크(320)와 같은 마스크가 기판(301)의 후방 표면과 이온 빔(330) 사이에 위치된다. 이러한 마스크(320)는 폴리실리콘 층(305)의 부분들 내로의 이온들의 주입을 방지하는데 사용된다. 이온들은 증착 프로세스 동안 도입된 도편트와 반대되는 전도성 유형을 갖는 종의 이온들이다. 다시 말해서, 증착 동안 붕소-기반 가스가 사용되었다면, V족 원소, 예를 들어, 인과 같은 n-형 도편트의 이온들이 이러한 단계 동안 주입될 것이다. 유사하게, 증착 동안 아르신 또는 포스핀이 도입되었다면, III족 원소, 예를 들어, 붕소와 같은 p-형 도편트의 이온들이 이러한 단계 동안 주입될 것이다.

[0019] 주입되는 반대 전도성의 도편트의 양은 주입되는 영역들을 카운터도핑(counterdope)하기에 충분하다. 다시 말해서, 폴리실리콘 층(305)이 p-형 도편트로 증착된 경우, 주입되는 영역들을 n-형 영역들로 변화시키기 위한 양의 n-형 도편트가 도입된다. 또한, 반대 전도성 유형의 도편트의 양은  $1e17/cm^3$ 과  $1e20/cm^3$  사이의 순 자유 캐리어(net free carrier) 농도를 달성하기에 충분하다.

[0020] 주입된 종의 다수(예를 들어, >90%)가 폴리실리콘 층 내에 존재하고 터널 산화물 내로 또는 기판 내로 침투하지 않도록, 주입 파라미터들이 선택되어야만 한다. 10kV 미만의 주입 에너지들이 바람직하며, 5kV 미만의 주입 에너지들이 특히 바람직하다.

[0021] 일 실시예에 있어, 도 3c에 도시된 바와 같이, 증착 동안 p-형 도편트를 사용하여 폴리실리콘 층이 도핑된 것으로 가정된다. 따라서, 인과 같은, n-형 도편트들의 이온들이 도 3d에서 주입된다. 이러한 단계들의 결과는 마스크(320)에 의해 커버되었던 폴리실리콘 층(305)의 이러한 영역들에서의 p-형 영역들(335)의 생성 및 도 3d에서 주입되었던 폴리실리콘 층(305)의 이러한 영역들에서의 n-형 영역들(336)의 생성이다.

[0022] 다른 실시예에 있어, 도 3c에 도시된 바와 같이, 증착 동안 n-형 도편트를 사용하여 폴리실리콘 층이 도핑된 것으로 가정된다. 따라서, 붕소와 같은, p-형 도편트들의 이온들이 도 3d에서 주입된다. 이러한 단계들의 결과는 마스크(320)에 의해 커버되었던 폴리실리콘 층(305)의 이러한 영역들에서의 n-형 영역들(335)의 생성 및 도 3d에서 주입되었던 폴리실리콘 층(305)의 이러한 영역들에서의 p-형 영역들(336)의 생성이다.

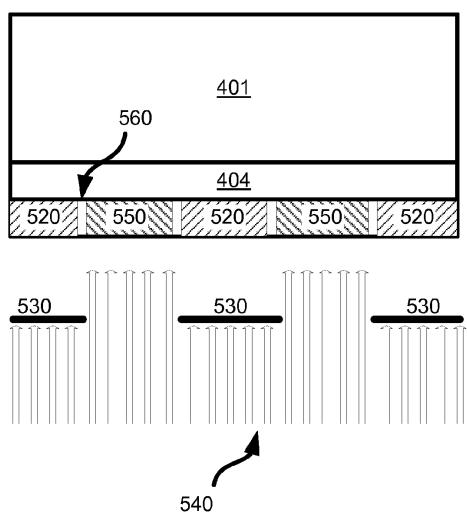

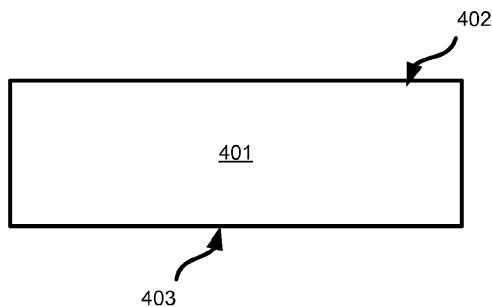

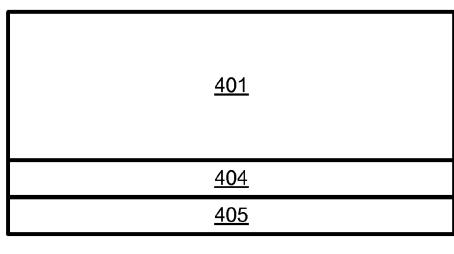

[0023] 도 4a 내지 도 4e는 폴리실리콘 솔라 셀(400)을 생성하기 위한 일련의 제조 단계들을 도시한다. 도 4a는 기판(401)을 도시한다. 이러한 기판(401)은 n-형 실리콘 기판과 같은 임의의 적절한 기판일 수 있다. 기판(401)은 전면 표면(402) 및 후방 표면(403)을 갖는다. 전면 표면(402)이 태양광에 노출되며, 반면 전기 접촉부들이 후방 표면(303) 상에 생성될 것이다.

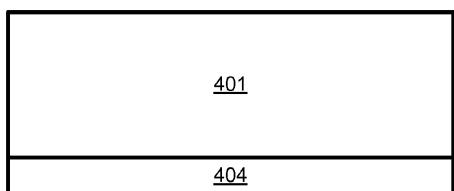

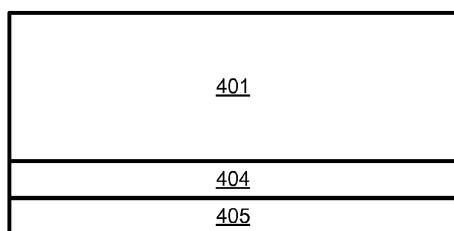

[0024] 도 4b는 기판(401)의 후방 표면(403) 상에 형성된 터널 산화물 층(404)을 도시한다. 터널 산화물 층은 약 1 nm 와 4 nm 사이의 두께일 수 있다. 일부 실시예들에 있어, 열 산화가 터널 산화물을 층을 성장시키는 데 사용된다. 이러한 프로세스는 산소(산소 분자 또는 수증기 중 하나)가 기판의 후방 표면과 반응하여 이산화 실리콘을 형성하도록 하기 위하여 800°C 이상의 온도에서 노내에서 수행될 수 있다. 따라서, 습식 및 건식 산화 물 모두가 사용될 수 있다.

[0025] 도 4c는 터널 산화물(404)에 인접한 폴리실리콘 층(405)을 도시한다. 일 실시예에 있어, 폴리실리콘 층(305)은 저압(1 Torr 미만과 같은) 및 575°C로부터 650°C까지의 범위의 온도에서 실레인(SiH<sub>4</sub>)을 사용하여 증착된다. 이러한 프로세스는 또한 저압 화학 기상 증착(LPCVD)으로서 알려져 있다. 다른 실시예들에 있어, 대기압 화학 기상 증착(APCVD), 플라즈마 증강 CVD(PECVD) 또는 다른 적절한 프로세스가 폴리실리콘 층(405)을 성장시키는데 사용될 수 있다. 이러한 폴리실리콘 층(405)은 증착 동안 도편트 가스들의 도입없이 성장될 수 있으며, 이는 증착의 균일성을 향상시키는 것으로 알려져 있다.

[0026] 도 4d는 폴리실리콘 솔라 셀(400) 제조 프로세스의 다음 단계를 도시한다. 제 1 도편트의 전도성을 갖는 폴리실리콘 층(405)을 생성하기 위하여 제 1 도편트(425)의 이온들이 폴리실리콘 층(405)에 주입된다. 예를 들어, 인 또는 다른 V족 원소가 주입된 경우, 폴리실리콘 층(405)은 n-형이 될 것이다. 반면, 붕소 또는 다른 III족 원소가 주입된 경우, 폴리실리콘 층(405)은 p-형이 될 것이다. 주입된 도편트의 농도는  $1e17/cm^3$ 과  $1e20/cm^3$  사이이다. 이는 폴리실리콘 층(405)의 전체 표면이 주입되는 블랭킷 주입(blanket implant)이다.

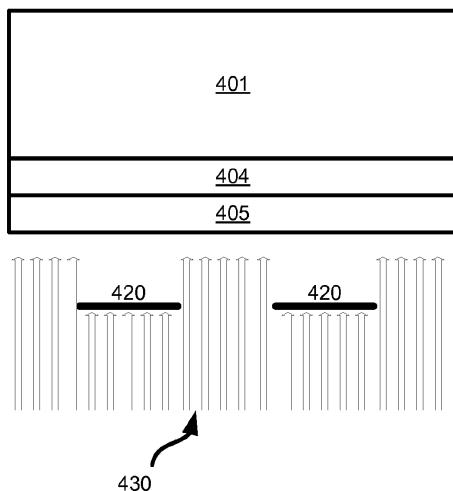

[0027] 도 4e는 폴리실리콘 솔라 셀(400) 제조 프로세스의 다음 단계를 도시한다. 새도우 마스크(420)와 같은 마스크가 기판(401)의 후방 표면과 이온 빔(430) 사이에 위치된다. 이러한 마스크(420)는 폴리실리콘 층(405)의 부분들 내로의 이온들의 주입을 방지하는데 사용된다. 이온들은 도 4d의 주입 프로세스 동안 주입된 도편트와 반대되는

전도성 유형을 갖는 종의 이온들이다. 다시 말해서, 이전에 III족 원소의 이온들이 주입되었다면, V족 원소, 예를 들어, 인과 같은 n-형 도편트의 이온들이 이러한 단계 동안 주입될 것이다. 유사하게, V족 원소가 이전에 주입되었다면, III족 원소, 예를 들어, 붕소와 같은 p-형 도편트의 이온들이 이러한 단계 동안 주입될 것이다.

[0028] 도 4d 및 도 4e에 도시된 단계들이 반대의 순서로 이루어질 수 있다는 것이 주목되어야 한다. 다시 말해서, 패턴화된 주입이 먼저 수행될 수 있고, 블랭킷 주입이 그 뒤에 따라올 수 있다.

[0029] 주입되는 반대 전도성의 도편트의 양은 주입되는 영역들을 카운터도핑하기에 충분하다. 다시 말해서, 폴리실리콘 층(305)이 p-형 도편트로 증착된 경우, 주입되는 영역들을 n-형 영역들로 변화시키기 위한 양의 n-형 도편트가 도입된다.

[0030] 또한, 반대 전도성 유형의 도편트의 양은  $1e17/cm^3$ 과  $1e20/cm^3$  사이의 순 자유 캐리어 농도를 달성하기에 충분하다.

[0031] 주입된 종의 다수(예를 들어, >90%)가 폴리실리콘 층 내에 존재하고 터널 산화물 내로 또는 기판 내로 침투하지 않도록, 주입 파라미터들이 선택되어야만 한다. 10kV 미만의 주입 에너지들이 바람직하며, 5kV 미만의 주입 에너지들이 특히 바람직하다.

[0032] 이온들이 주입된 후, 도편트들을 확산시키고 주입에 의해 초래된 손상을 제거하기 위해 솔라 셀이 열적으로 처리된다. 폴리실리콘의 사용되었기 때문에, 더 낮은 온도의 더 짧은 열적 프로세스들의 지속기간을 이용해 확산이 달성될 수 있다. 예를 들어, 몇 초 내지 몇 분의 지속기간에 대하여 500°C 내지 600°C의 열적 사이클들이 사용될 수 있다. 다른 실시예에 있어, 급속 열처리(rapid thermal anneal: RTP)가 사용될 수 있다.

[0033] 도 3e에 도시된 바와 같이, 고농도로 도핑된 p-형 및 n-형 영역들이 서로 접촉할 때, 터널링 또는 다른 메커니즘들에 기인하는 기생 션팅(parasitic shunting)의 위험이 존재한다는 것이 인식된다. 이는 많은 수의 결함(defect)들을 갖는 폴리실리콘 재료들에서 특히 중요하다. 따라서, 일부 실시예들에 있어, p-형 영역(335)을 n-형 영역들(336)로부터 물리적으로 분리하기 위한 프로세싱 단계가 기생 션팅 경로들을 방지하게 위하여 수행된다. 예를 들어, n-형 영역과 p-형 영역 사이에 트렌치(trench)를 형성하기 위해 레이저가 사용될 수 있다. 대안적으로 트렌치는 습식 화학 에칭을 사용하여 형성될 수 있다.

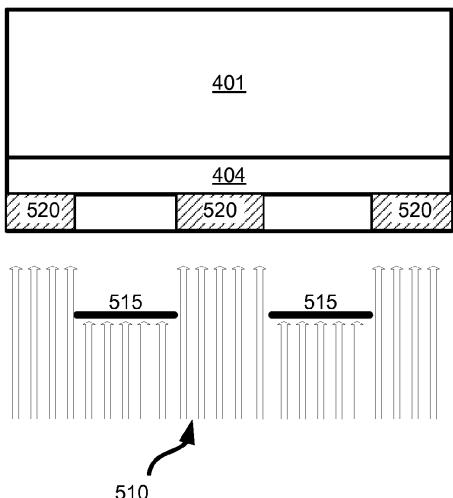

[0034] 다른 실시예에 있어, 기판이 도 4a 내지 도 4c에 도시된 바와 같이 마련된다. 이러한 단계들 다음에, 기판이 그 뒤 도 5a에 도시된 바와 같은 패턴화된 주입을 사용하여 제 1 종의 이온들(510)로 주입된다. 이러한 패턴화된 주입은 제 1 전도성 유형의 종을 주입하기 위하여 제 1 마스크(515)를 사용한다. 일 실시예에 있어, 제 1 종은 인 또는 다른 V족 원소이다. 다른 실시예에 있어, 제 1 종은 붕소 또는 다른 III족 원소이다. 이러한 주입은 주입된 영역들(520)을 생성한다.

[0035] 그 후 제 1 마스크(515)에 정렬된 제 2 마스크(530)를 사용하여 제 2의 패턴화된 주입이 도 5b에 도시된 바와 같이 수행된다. 제 2 종의 이온들(540)을 사용하는 주입은 주입된 영역들(550)을 생성한다. 제 1 종이 V족 원소였던 경우에 있어, 제 2 종은 붕소 또는 다른 III족 원소일 수 있다. 유사하게, 제 1 종이 III족 원소였던 경우에 있어, 제 2 종은 인 또는 다른 V족 원소일 수 있다.

[0036] 이러한 2개의 마스크들은 비-중첩되고 인접한 주입된 영역들(520, 550) 사이의 간극(560)을 보장하도록 설계된다. 이상에서 설명된 바와 같이, n-형 영역들과 p-형 영역들 사이의 존재물 또는 간극은 터널링에 기인하는 기생 션팅을 감소시킨다.

[0037] 본 발명의 범위는 본 명세서에서 설명된 특정 실시예들에 의해 한정되지 않는다. 오히려, 본 명세서에서 설명된 실시예들에 더하여, 본 발명의 다른 다양한 실시예들 및 본 발명에 대한 수정예들이 이상의 설명 및 첨부된 도면들로부터 당업자들에게 자명해질 것이다. 따라서 이러한 다른 실시예들 및 수정예들이 본 발명의 범위 내에 속하도록 의도된다. 더욱이, 본 발명이 특정 목적을 위한 특정 환경에서의 특정 구현예의 맥락에서 본 명세서에서 설명되었지만, 당업자들은 본 발명의 유용성이 이에 한정되지 않으며, 본 발명이 임의의 수의 목적들을 위한 임의의 수의 환경들에서 유익하게 구현될 수 있다는 것을 인식할 것이다. 따라서 이하에서 진술되는 청구항들은 본 명세서에서 설명된 바와 같은 본 발명의 완전한 폭과 사상의 관점에서 이해되어야 할 것이다.

도면

도면1

종래 기술

도면2

종래 기술

도면3a

도면3b

도면3c

도면3d

도면3e

도면4a

도면4b

도면4c

도면4d

도면4e

도면5a

도면5b