(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2009년10월19일

(11) 등록번호 10-0922019

(24) 등록일자 2009년10월08일

(51) Int. Cl.

H04N 5/44 (2006.01) H04N 5/64 (2006.01)

H05K 1/14 (2006.01)

(21) 출원번호 10-2004-7009413

(22) 출원일자 2002년12월11일

심사청구일자 2007년12월06일

(85) 번역문제출일자 2004년06월17일

(65) 공개번호 10-2004-0068261

(43) 공개일자 2004년07월30일

(86) 국제출원번호 PCT/US2002/039503

(87) 국제공개번호 WO 2003/055203

국제공개일자 2003년07월03일

(30) 우선권주장

10/024,981 2001년12월19일 미국(US)

(56) 선행기술조사문헌

JP평성04072970 A

US6151077 A

WO199832277 A1

전체 청구항 수 : 총 17 항

심사관 : 문영재

(54) 신호 제어 라인 공유 장치 및 방법

### (57) 요 약

텔레비전 신호 수신기와 같은 장치는 제 1 회로 보드 및 제 2 회로 보드를 포함한다. 제 1 회로 보드는 메모리와 같은 제 1 디바이스와, 상기 장치의 적어도 하나의 기능을 제어하기 위한 제어 회로를 포함한다. 제 2 회로 보드는 제어 라인을 경유하여 상기 제 1 회로 보드에 동작가능하게 연결된다. 제 2 회로 보드는 제 1 제어 신호 및 제 2 제어 신호를 생성하는 제어기를 포함한다. 제어 라인은, 상기 장치가 제 1 동작 상태일 때 상기 제어기로부터 상기 제 1 제어 신호를 상기 제 1 디바이스로 전송하고, 상기 장치가 제 2 동작 상태일 때 상기 제어기로부터 상기 제어 회로로 상기 제 2 제어 신호를 전송한다.

### 대 표 도

## 특허청구의 범위

### 청구항 1

텔레비전 신호 수신기로서,

상기 수신기의 동작을 제어하기 위한 제어 회로 및 메모리를 포함하는 제 1 회로 보드로서, 상기 제어 회로는 상기 메모리 내에 저장된 동작 데이터에 응답하여 상기 수신기의 동작을 제어하는, 제 1 회로 보드; 및

IIC(inter-integrated circuit) 버스 라인을 통해 상기 제 1 회로 보드와 동작가능하게 연결된 제 2 회로 보드로서, 제 1 동작 상태에서 메모리로부터 데이터를 판독하도록 제어기를 인에이블 시키는 제 1 제어 신호 및 제 2 동작 상태에서 상기 수신기의 동작을 제어하도록 상기 제어 회로를 인에이블 시키는 제 2 제어 신호를 생성시키기 위해 상기 IIC 버스 라인에 연결된 제어기를 포함하는, 제 2 회로 보드를

포함하고,

여기서 상기 메모리와 상기 제어 회로는 상기 IIC 버스 라인에 연결되고, 상기 제어기는 상기 제 1 동작 상태에서 상기 제어 회로에 영향을 끼치지 않으면서 상기 IIC 버스 라인을 경유하여 동작 데이터를 검색하도록 상기 메모리로 상기 제 1 제어 신호를 전송하고, 또한 상기 제어기는 상기 IIC 버스 라인을 경유하여 상기 검색된 동작 데이터에 반응하여 상기 제어 회로를 제어하도록 상기 제어 회로에 상기 제 2 제어 신호를 전송하는,

텔레비전 신호 수신기.

### 청구항 2

제 1 항에 있어서, 상기 제 1 동작 상태는 상기 수신기의 OFF 상태에 대응하며, 상기 제 2 동작 상태는 상기 수신기의 ON 상태에 대응하는, 텔레비전 신호 수신기.

### 청구항 3

제 1 항에 있어서, 상기 제 1 제어 신호는 IIC 표준 컴플라이언트(compliant) 신호에 대응하며, 상기 제 2 신호는 펄스폭 변조(pulse width modulation) 신호인, 텔레비전 신호 수신기.

### 청구항 4

제 1 항에 있어서, 상기 제어 회로는 바이폴라 트랜지스터를 경유하여 상기 IIC 버스 라인에 연결되는, 텔레비전 신호 수신기.

### 청구항 5

신호 처리 장치로서,

메모리 수단과, 수신기의 적어도 하나의 동작을 제어하기 위한 제어 회로 수단을 포함하는 제 1 회로 보드; 및 제어 라인을 통해 상기 제 1 회로 보드와 동작가능하게 연결된 제 2 회로 보드로서, 제 1 동작 상태에서 상기 메모리 수단으로부터 동작 데이터를 판독하도록 제어기 수단을 인에이블시키는 제 1 제어 신호 및 제 2 동작 상태에서 상기 수신기의 동작을 제어하도록 상기 제어 회로 수단을 인에이블시키는 제 2 제어 신호를 생성시키기 위해 상기 제어 라인에 연결된 제어기 수단을 포함하는, 제 2 회로 보드를

포함하고,

여기서 상기 메모리 수단과 상기 제어 회로 수단은 상기 제어 라인에 연결되고, 상기 제어기 수단은 상기 제 1 동작 상태에서 상기 제어 회로 수단에 영향을 끼치지 않으면서 상기 제어 라인을 경유하여 상기 동작 데이터를 검색하도록 상기 메모리 수단으로 상기 제 1 제어 신호를 전송하고, 또한 상기 제어기 수단은 상기 제어 라인을 경유하여 상기 동작 데이터에 반응하여 상기 제어 회로 수단을 제어하도록 상기 제어 회로 수단에 상기 제 2 제어 신호를 전송하는,

신호 처리 장치.

**청구항 6**

삭제

**청구항 7**

제 5 항에 있어서, 상기 동작 데이터는 편향 회로를 제어하기 위한 전압 데이터를 포함하고, 상기 제어 회로 수단은 상기 전압 데이터에 응답하여 상기 편향 회로를 제어하는, 신호 처리 장치.

**청구항 8**

제 7 항에 있어서, 상기 제 1 동작 상태에서 상기 장치는 OFF 상태로 있는 것에 대응하며, 또한 상기 제어기 수단 및 상기 메모리 수단은 대기 전원 공급기에 의해 전원을 공급받으며, 상기 제 2 동작 상태에서 상기 장치는 ON 상태로 있는 것에 대응하는, 신호 처리 장치.

**청구항 9**

삭제

**청구항 10**

제 5 항에 있어서, 상기 제 2 제어 신호는 상기 메모리 수단으로부터 판독된 데이터에 응답하여 상기 수신기의 편향 동작을 제어하도록 상기 제어 회로 수단을 인에이블시키는, 신호 처리 장치.

**청구항 11**

제 5 항에 있어서, 상기 제 1 제어 신호는 버스 표준인 IIC(inter-integrated circuit)에 따르며, 상기 제 2 제어 신호는 펄스폭 변조 신호를 포함하는, 신호 처리 장치.

**청구항 12**

제 5 항에 있어서, 상기 제어 라인은 IIC 버스를 포함하는, 신호 처리 장치.

**청구항 13**

제 5 항에 있어서, 상기 제어 회로 수단은 바이폴라 트랜지스터를 경유하여 상기 제어 라인에 연결되는, 신호 처리 장치.

**청구항 14**

텔레비전 신호 수신기를 동작시키는 방법으로서,

제어 라인을 경유하여 연결된 제 1 회로 보드 및 제 2 회로 보드를 제공하는 단계로서, 상기 제 1 회로 보드는 상기 제 1 회로 보드 상에 포함되고 상기 제어 라인에 연결된 메모리 디바이스 및 제어 회로를 구비하며, 상기 제 2 회로 보드는 상기 제 2 회로 보드 상에 포함되고 상기 제어 라인에 연결된 제어기를 구비하는, 제 1 회로 보드 및 제 2 회로 보드를 제공하는 단계와;

상기 수신기가 제 1 동작 상태일 때, 상기 제 2 회로 보드 상의 상기 제어기로부터 제 1 제어 신호를, 상기 제어 회로에 영향을 끼치지 않고, 상기 메모리 디바이스로부터 동작 데이터를 검색하도록, 상기 제 1 회로 보드 상의 상기 메모리 디바이스에 상기 제어 라인을 경유하여 전송하되, 상기 제 1 제어 신호는 상기 메모리 디바이스로부터 데이터를 판독하도록 상기 제어기를 인에이블 시키는, 제 1 제어 신호 전송 단계; 및

상기 수신기가 제 2 동작 상태일 때, 상기 검색된 동작 데이터에 대한 응답으로 상기 제어기로부터 제 2 제어 신호를, 상기 제 1 회로 보드 상의 상기 제어 회로로 상기 제어 라인을 경유하여 전송하되, 상기 제 2 제어 신호는 상기 수신기의 동작을 제어하도록 상기 제어 회로를 인에이블 시키는, 제 2 제어 신호 전송 단계를 포함하는, 텔레비전 신호 수신기의 동작 방법.

**청구항 15**

제 14 항에 있어서, 상기 제 1 동작 상태는 상기 수신기가 OFF 상태인 것에 대응하고 여기서 상기 제어기 및 상

기 메모리 디바이스는 대기 전원 공급기에 의해 공급되며, 상기 제 2 동작 상태는 상기 수신기가 ON 상태인 것에 대응하는, 텔레비전 신호 수신기의 동작 방법.

#### 청구항 16

삭제

#### 청구항 17

제 14 항에 있어서, 상기 메모리로부터 판독된 데이터에 응답하여 상기 제어 회로를 경유하여 편향 회로를 제어하는 단계를 더 포함하는, 텔레비전 신호 수신기의 동작 방법.

#### 청구항 18

제 14 항에 있어서, 상기 제 1 제어 신호 전송 단계는 버스 표준인 IIC(inter-integrated circuit)에 따라 상기 제 1 제어 신호를 전송하는 단계를 포함하는, 텔레비전 신호 수신기의 동작 방법.

#### 청구항 19

제 14 항에 있어서, 상기 제 2 제어 신호 전송 단계는 펄스폭 변조 신호로서 상기 제 2 제어 신호를 전송하는 단계를 포함하는, 텔레비전 신호 수신기의 동작 방법.

#### 청구항 20

제 14 항에 있어서, 상기 제공하는 단계는 바이폴라 트랜지스터를 통해 상기 제어 라인에 연결된 제어 회로를 구비하는 상기 제 1 회로 보드를 제공하는 단계를 포함하는, 텔레비전 신호 수신기의 동작 방법.

### 명세서

#### 기술 분야

<1>

본 발명은 일반적으로, 텔레비전 신호 수신기와 같은, 복수의 회로 보드들 상에 장착된 소자들을 포함하는 전기 디바이스에 관한 것으로, 더 상세하게는, 신호 제어 라인들이 공유되도록 함으로써 이러한 디바이스 내 회로 보드들 사이에 요구되는 접속 수를 감소시키는 기법에 관한 것이다.

#### 배경 기술

<2>

텔레비전 신호 수신기와 같은 전기 디바이스는 종종 하나 이상의 회로 보드들을 포함한다. 각 회로 보드에는 통상적으로, 다양한 디바이스 동작이 수행될 수 있도록 하는, 접속회로(IC)나 다른 요소들과 같은 전기 소자들이 장착되어 있다. 텔레비전 신호 수신기의 이전 설계에서는 종종 하나의 단일 회로 보드만이 사용되었다. 이러한 이전 설계에 있어서, 일차적인 동기는 보드 사용 면적을 최대화하려는 것이었다. 그러나, 단 하나의 회로 보드만이 사용되었기 때문에, 서로 다른 회로 보드들 사이의 접속에 관하여는 아무런 문제가 없었다.

<3>

그런데 현재의 텔레비전 신호 수신기 설계는, 여러 회로 보드를 사용할 수 있다. 여러 회로 보드의 사용은, 하나의 단일 회로 보드와 비교할 때, 회로 설계가 모듈화되도록 할 수 있기 때문에 특히 매력적이다. 구체적으로, 서로 다른 보드 색션들은 모든 수신기 회로들의 레이아웃을 재조직할 필요없이도 재-설계될 수 있는데, 반면에 하나의 단일 회로 보드만을 사용하는 경우에는 종종 모든 수신기 회로들의 레이아웃을 재조직해야만 한다. 또한, 여러 회로 보드의 사용은 단면 보드가 하나의 회로 그룹을 위해 사용되도록 하면서, 다중-층 보드는 다른 회로들을 위해 사용될 수 있도록 한다.

<4>

이러한 장점들에도 불구하고, 여러 회로 보드의 사용은 서로 다른 보드들 사이의 접속에 관련되어 문제를 발생시킬 수 있다. 구체적으로, 회로 보드들 사이에서 하나의 접속을 제공하는데 사용되는 커넥터(예컨대, 핀)의 수를 최소화시키는 것이 바람직하다. 이러한 커넥터의 수를 최소화하는 것은, 각 커넥터의 비용이 재정적 의미에서 수치화될 수 있기 때문에 특히 바람직하다. 이것은 가전산업과 같은 특정한 산업에서 특히 중요한데, 이러한 산업에서는 경쟁자들 사이에서 제품 비용이 경쟁력이며, 작은 유닛당 비용은 생산된 총 유닛 수의 관점에서 중요할 수 있다. 따라서, 텔레비전 신호 수신기와 같은 장치에서 회로 보드들 사이에 요구되는 접속의 수를 감소시키는 기술에 대한 요구가 있다.

## 발명의 상세한 설명

- <5> 본 발명에 따라, 텔레비전 신호 수신기와 같은 장치는 제 1 회로 보드 및 제 2 회로 보드를 포함한다. 제 1 회로 보드는 메모리와 같은 제 1 전자 디바이스와, 상기 장치의 적어도 하나의 기능을 제어하기 위한 제어 회로와 같은 제 2 전자 디바이스를 포함한다. 제 2 회로 보드는 제어 라인들을 통해 상기 제 1 회로 보드와 동작가능하게 연결된다. 제 2 회로 보드는, 각각 제 1 신호 포맷 및 제 2 신호 포맷에 따라 제 1 제어 신호 및 제 2 제어 신호를 생성하기 위한 제어기를 포함한다. 제어 라인들은 장치가 제 1 동작 상태에 있을 때 제어기로부터 제 1 제어 신호를 제 1 디바이스로 전송하며, 장치가 제 2 동작 상태에 있을 때 제어기로부터 제 2 제어 신호를 제어 회로로 전송한다. 또한 상기 장치에 의해 수행되는 방법도 본 명세서에 개시된다.

- <6> 첨부된 도면을 참조하여 이루어지는 이후의 본 발명의 실시예들에 대한 설명을 참조함으로써, 본 발명의 상기 언급된 특징과 장점 및 다른 특징과 장점, 그리고 이것들을 달성하는 방식은 더 명확해질 것이고, 본 발명이 더 잘 이해될 것이다.

- 실시예**

- <9> 본 명세서에서 설명되는 예시들은 본 발명의 바람직한 실시예들을 보여주며, 이러한 예시들은 어느 방식으로든 본 발명의 범위를 제한하는 것으로 간주되어서는 안된다.

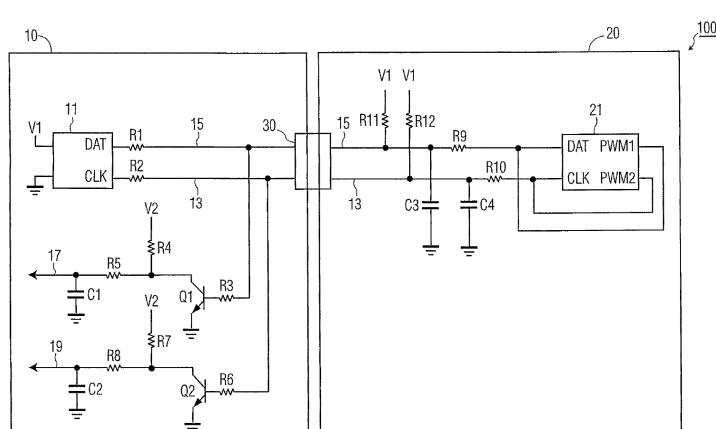

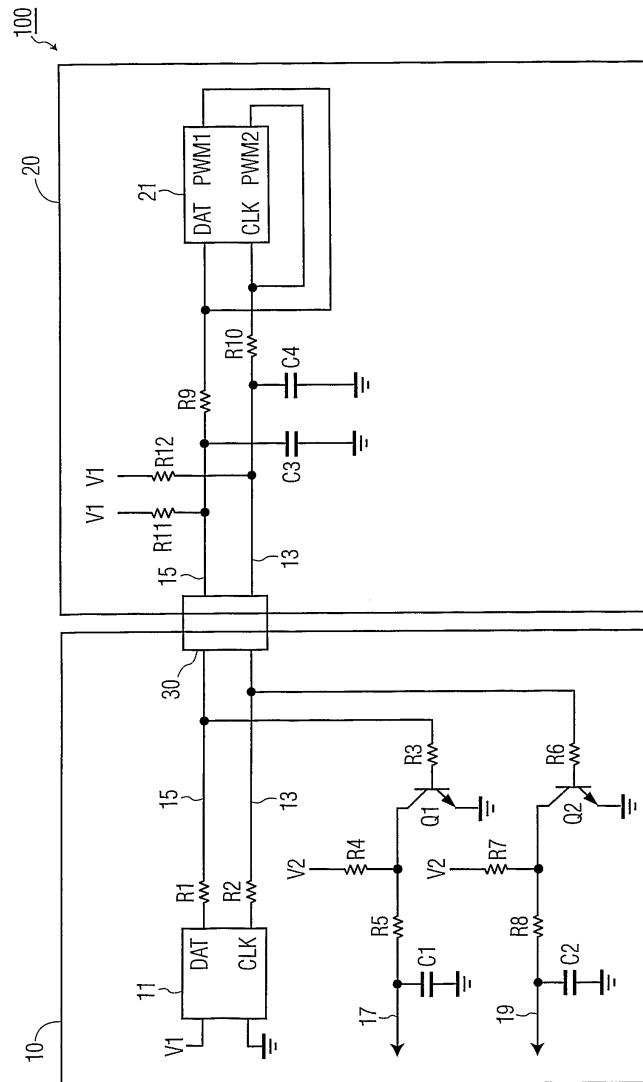

- <10> 이제 도면들을, 더 구체적으로 도 1을 참조하면, 본 발명을 구현하기에 적절한 장치(100)의 관련 부분의 도면이 도시된다. 예시 및 설명을 위해, 도 1의 장치(100)는 텔레비전 신호 수신기로서 표현되어 있다. 그러나, 본 발명의 원리는 여러 회로 보드들을 사용하는 다른 타입의 전자 디바이스에도 응용가능할 수 있다는 점이 주목된다.

- <11> 도 1의 수신기(100)는 제 1 회로보드(10), 제 2 회로 보드(20), 및 보드 커넥터(30)로 이루어져 있다. 예시적인 일 실시예에 따라, 제 1 회로 보드(10)는 수신기(100)의 전력 공급 및 편향 기능과 관련된 동작을 인에이블시키고, 제 2 회로 보드(20)는 수신기(100)의 신호 처리 기능과 관련된 동작을 인에이블시킨다. 제 1 보드(10)는 보드 커넥터(30)를 통해 제 2 회로 보드(20)에 전기적으로 연결되어 있다.

- <12> 제 1 회로 보드(10)는, 수신기(100)의 편향 동작을 제어하는데 사용되는 전압 데이터와 같은 데이터를 저장하는 비휘발성 메모리로서 동작하는 EEPROM (electrically erasable, programmable read-only memory: 전기적 소거 가능하고 프로그래밍 가능한 판독전용 메모리)(11)을 포함한다. EEPROM(11)은 CLK(clock) 단자 및 DAT(data) 단자를 포함하며, 전압 소스 V1에 의해 전원을 공급받는데, 이 전압 소스 V1은 본 예시적인 실시예에서 3.3 볼트이다. CLK 단자는 SCL(serial clock line : 직렬 클록 라인)(13)에 전기적으로 연결되고, DAT 단자는 SDL(serial data line : 직렬 데이터 라인)(15)에 전기적으로 연결된다. 예시적인 일 실시예에 따라, SCL(13)과 SDL(15)은 집합적으로 IIC(inter-integrated circuit)(통상적으로 "I2C"라고 읽음) 버스를 나타내며, 본 명세서에서는 버스 라인들 또는 제어 라인들이라고 지칭될 수 있다.

- <13> 여러 IC 사이에서 제어 신호 및 데이터 신호를 전달하기 위한 IIC 버스의 포맷과 사용은 당업자에게 잘 알려져 있다. 일반적으로, IIC 버스는, 하나의 버스 경로 상에서 둘 이상의 IC가 통신하는 것을 허용하는 2-전송 매체 즉 양방향 디지털 버스이다. "마스터" 동작 모드로 동작하는 IC는 버스 상의 데이터 전달 동작을 개시하며 데이터 전달을 허용하는 클록 신호를 생성시킨다. "슬레이브" 동작 모드로 동작하는 IC는 마스터 IC에 의해 동작되며 통신의 대상이 되고, 이에 의해 슬레이브 IC는 데이터를 송신 또는 수신하는 것 중 어느 하나를 지시받는다. 각 IC는 자기 자신의 고유 어드레스를 가지는데, 여기서 마스터 IC는 통신을 개시 및 종료시킨다. SCL(13) 및 SDL(15)에 의해 대표되는 IIC 버스에 관한 추가적인 상세한 설명은 나중에 본 명세서에서 제공될 것이다.

- <14> 제 1 회로 보드(10)는 또한 8 개의 저항 R1 내지 R8, 2 개의 커패시터 C1 및 C2, 그리고 2 개의 트랜지스터 Q1 및 Q2를 포함한다. 저항 R1 및 R2는 각각 SDL(15) 및 SCL(13) 상에 대한 저항을 생성하도록 제공된다. 본 예시적인 실시예에서, 저항 R1 및 R2는 각각 1 kΩ의 저항을 제공한다. 도 1에서 표시되어 있는 바와 같이, SCL(13) 및 SDL(15)은 제 1 회로 보드(10) 내에서 분기되어 2개의 분리된 제어 채널을 제공한다. 구체적으로 SDL(15)은 분기되어 참조번호 17로 표시된 출력 신호를 생성하는 제 1 제어 채널을 제공하며, SCL(13)은 분기되어 참조번호 19로 표시된 출력 신호를 생성하는 제 2 제어 채널을 제공한다. 출력 신호(17, 19)는 수신기(100)의 편향 동작을 제어한다. 제 1 제어 채널과 제 2 제어 채널을 구성하는 회로는 집합적으로 본 명세서에서 제어 회로라고 지칭될 수 있다.

- <15> 제 1 제어 채널은 저항 R3 내지 R5, 커패시터 C1, 및 트랜지스터 Q1을 포함한다. 저항 R3는 SDL(15)과 트랜지스터

터 Q1의 베이스 접점 사이에 저항을 제공하며,  $10\text{ k}\Omega$ 의 바람직한 값을 가진다. 트랜지스터 Q1은 n-타입 BJT(bipolar junction transistor : 바이폴라 접합 트랜지스터)로서 구현되는 것이 바람직하다. 트랜지스터 Q1의 콜렉터 접점은 제 1 제어 채널에 있어 출력 경로를 제공한다. 저항 R4는 풀-업 저항으로서 동작하며 전압 소스 V2에 전기적으로 연결되는데, 상기 전압 소스 V2는 예시적인 일 실시예에서 5.1 볼트이다. 저항 R4에 있어 바람직한 값은  $1\text{ k}\Omega$ 이다. 저항 R5 및 커패시터 C1은 시간 상수를 확립시키고, 바람직하게는 각각  $1\text{ k}\Omega$  및  $820\text{ nF}$ 의 값을 가진다. 예시적인 실시예에서, 출력 신호(17)는 플라이백 변압기(flyback transformer)(미도시됨)의 전압을 확립시키는데 사용되며, 이 플라이백 변압기의 전압은 수신기(100)의 편향 동작에 사용된다.

<16> 제 2 제어 채널은 저항 R6 내지 R8, 커패시터 C2, 및 트랜지스터 Q2를 포함한다. 저항 R6은 SCL(13)과 트랜지스터 Q2의 베이스 접점 사이에 저항을 제공하며  $10\text{ k}\Omega$ 의 바람직한 값을 가진다. 트랜지스터 Q2는 n-타입 BJT으로서 구현되는 것이 바람직하다. 트랜지스터 Q2의 콜렉터 접점은 제 2 제어 채널에 있어 출력 경로를 제공한다. 저항 R7은 풀-업 저항으로서 동작하며 전압 소스 V2에 전기적으로 연결되는데, 이 전압 소스 V2는 이전에 언급된 바와 같이 5.1 볼트이다. 저항 R7에 있어 바람직한 값은  $1\text{ k}\Omega$ 이다. 저항 R8 및 커패시터 C2는 시간 상수를 확립시키고, 각각  $1\text{ k}\Omega$  및  $820\text{ nF}$ 의 값을 가지는 것이 바람직하다. 예시적인 본 실시예에서, 출력 신호(19)는 플라이백 변압기(미도시됨)의 전압을 제어하는데 사용된다. 또한 저항 R3 및 R6은 IIC 버스의 부하증가/loading)를 방지하기에 충분히 높은 저항을 가지도록 선택되는 것이 바람직하다.

<17> 제 2 회로 보드(20)는 수신기(100)의 여러 동작을 제어하는 마이크로제어기(21)를 포함한다. 제 1 회로 보드(10)의 EEPROM(11)과 유사하게, 마이크로제어기(21)도 역시 CLK 단자 및 DAT 단자를 포함한다. CLK 단자는 SCL(13)에 전기적으로 연결되며, DAT 단자는 SDL(15)에 전기적으로 연결된다. 도 1에는 비록 명시적으로 도시되어 있지 않으나, 마이크로제어기(21)는 전압 소스 V1과 같은 전압 소스에 전기적으로 연결되어 있다. "마이크로제어기"와 "제어기"라는 용어는 본 명세서에서 교환가능하게 사용될 수 있다.

<18> 마이크로제어기(21)는 또한, 제 1 PWM(pulse width modulated : 펄스폭변조) 신호 및 제 2 PWM 신호를 각각 출력하는 제 1 PWM 단자와 제 2 PWM 단자("PWM1" 및 "PWM2")를 포함한다. PWM1 단자 및 PWM2 단자는 각각 SDL(15) 및 SCL(13)에 전기적으로 연결되며, 이에 따라 제 1 PWM 신호 및 제 2 PWM 신호를 제 1 회로 보드(10)의 제 1 제어 채널 및 제 2 제어 채널로 각각 제공한다. 따라서 제 1 PWM 신호는 출력 신호(17)를 생성하는데 사용되고, 제 2 PWM 신호는 출력 신호(19)를 생성하는데 사용된다. PWM 신호가 바람직한 일 실시예에서 이용되고 있지만, 다른 포맷의 신호들도 물론 이용될 수 있다.

<19> 제 2 회로 보드(20)는 또한 4개의 저항 R9 내지 R12, 및 2개의 커패시터 C3 및 C4를 포함한다. 저항 R9 및 커패시터 C3은 SDL(15)로부터 무선 주파수 간섭을 필터링하여 제거하도록 동작하고, 저항 R10 및 커패시터 C4는 SCL(13)로부터 무선 주파수 간섭을 필터링하여 제거하도록 동작한다. 예시적인 일 실시예에서 저항 R9 및 R10은 각각  $1\text{ k}\Omega$ 의 값을 가지며, 커패시터 C3 및 C4 각각은  $100\text{ pF}$ 의 값을 가진다. 저항 R11 및 R12는 풀-업 저항으로서 동작하며, 전압 소스 V1에 전기적으로 연결되는데, 이 전압 소스 V1은 이전에 언급된 바와 같이 3.3 볼트이다. 저항 R11 및 R12 각각은  $10\text{ k}\Omega$ 의 값을 가진다.

<20> 동작시, IIC 버스{즉 SCL(13) 및 SDL(15)}는 마이크로제어기(21)의 두개의 상이한 동작 사이에서 공유된다. 구체적으로, 수신기(100)가 제 1 동작 상태일 때{즉, 수신기(100)가 전원 소스에 연결되었지만 OFF 상태일 때} 마이크로제어기(21)는 마스터 IC로서 동작하고 SCL(13) 및 SDL(15)를 경유하여 EEPROM(11)으로 제 1 제어 신호를 전송함으로써, 슬레이브 IC로서 동작하는 EEPROM(11)으로부터 데이터를 판독한다. 이 경우, DAT 핀은 입력/출력 라인이며 CLK는 출력 핀으로서 동작한다. PWM1 핀 및 PWM2 핀은 입력 라인으로서 동작하거나 또는 고 임피던스 상태로 동작한다. 상기 핀들의 상태는, 예컨대 데이터 지향성 레지스터를 사용하여, 현재 동작 상태에 반응하여 마이크로제어기(21)에 의해 결정된다. 마이크로제어기(21) 및 EEPROM(11)은 제 1 동작 상태 동안에 대기 전원 소스, 즉 전압 소스 V1으로부터 전기 에너지를 받는다. 예시적인 일 실시예에 따라, EEPROM(11)으로부터 마이크로제어기(21)에 의해 판독된 데이터는 수신기(100)의 편향 동작을 제어하는데 사용되는 전압 데이터로 이루어져 있다.

<21> 데이터 판독 동안에, SCL(13)은 클록 신호를 마이크로제어기(21)로부터 EEPROM(11)으로 전달한다. SDL(15)은 직렬 디지털 트랜잭션을 사용하여 데이터를 전송하는데 사용된다. 통상적으로, 하나 이상의 비트가 확인 비트(acknowledgment bits)로서 사용된다. 예시적인 일 실시예에 따르면, SCL(13) 및 SDL(15) 둘 모두 논리 하이(logic high) 상태일 때, 마이크로제어기(21)와 EEPROM(11) 사이에 데이터가 전송될 수 없다. SCL(13)이 논리 하이 상태로 있는 동안에, SDL(15) 상에서 논리 하이 상태로부터 논리 로우(logic low) 상태로의 천이는, IIC 버스를 통한 디지털 데이터의 교환에 있어 시작 조건을 나타낸다. 역으로, SCL(13)이 논리 하이 상태로 있는 동

안에, SDL(15) 상에서 논리 로우 상태로부터 논리 하이 상태로의 천이는 중지 조건을 나타낸다. 예시적인 일 실시예에 따라, 마이크로제어기(21)는 SDL(15) 상에서 전송되는 디지털 데이터의 각각의 비트에 대해 하나의 클록펄스를 생성시키고, SDL(15) 상의 논리 상태는 SCL(13) 상의 클록 신호가 논리 로우 상태인 때에만 변화할 수 있다. 물론, 상기 방식과는 다른 신호 프로토콜이 사용될 수 있다. 마이크로제어기(21)가 EEPROM(11)으로부터 데이터를 판독할 때, 마이크로제어기(21)의 PWM1 단자 및 PWM2 단자는 고-임피던스 상태이며, 저항 R3 및 R6는 제 1 제어 채널 및 제 2 제어 채널의 제어 회로가 SCL(13) 및 SDL(15)의 부하를 증가시키는 것을 막는다. 제 1 동작 상태 동안, 트랜지스터 Q1 및 Q2의 콜렉터들에 인가된 V2는 로우 상태이며, 따라서 Q1 및 Q2에의 신호 인가는 출력신호(17, 19)와 연관되는 제어 회로 상에 아무런 영향도 끼치지 않는다.

<22> 수신기(100)가 제 2 동작 상태{즉, 수신기(100)가 전원 소스에 연결되어 있고 ON 상태}일 때, 마이크로제어기(21)의 DAT 단자 및 CLK 단자는 고-임피던스 상태이며, PWM1 단자 및 PWM2 단자는 각각 제 1 PWM 신호 및 제 2 PWM 신호를 출력하는데 사용될 수 있다. 제 1 PWM 신호 및 제 2 PWM 신호는 본 명세서에서 제 2 제어 신호라고 지칭될 수 있다. PWM1 단자는 SDL(15)에 전기적으로 연결됨으로써, 제 1 회로 보드(10)의 제 1 제어 채널에 제 1 PWM 신호를 제공하여 출력 신호(17)의 생성을 인에이블한다. 유사하게 PWM2 단자는 SCL(13)에 전기적으로 연결됨으로써, 제 1 회로 보드(10)의 제 2 제어 채널에 제 2 PWM 신호를 제공하여 출력 신호(19)의 생성을 인에이블한다. 예시적인 본 실시예에 따라, 제 1 PWM 신호 및 제 2 PWM 신호는, 수신기(100)가 OFF 상태일 때, EEPROM(11)으로부터 판독된 전압 데이터에 따라 마이크로제어기(21)에 의해 생성된다. 앞서 언급된 방식에서, SCL(13) 및 SDL(15)은 마이크로제어기(21)의 2개의 상이한 동작 사이에서 공유된다. 2개의 상이한 동작 동안(상기 2개의 상이한 동작 동안에는 상이한 타입의 신호들이 전송된다)에 사용되는 2개의 상이한 소자들 사이에서 2개의 라인이 공유되도록 허용함으로써, 보드(10)와 보드(20) 사이에 요구되는 커넥터의 수가 감소된다.

<23> 위에 기술된 바와 같이, 제 1 PWM 신호 및 제 2 PWM 신호가 제 1 회로 보드(10)의 제어 회로로 전송될 때, EEPROM(11)은 의도와는 달리 기록될 수 있어 이에 따라 EEPROM(11) 내에 저장되어 있던 데이터가 손상될 수 있다는 잠재적인 문제점이 존재한다. 구체적으로, PWM 신호가 IIC 버스를 통해 전송될 때, 만약 시작 조건{즉, SCL(13)이 논리 하이 상태인 동안에, SDL(15) 상에서 논리 하이 상태로부터 논리 로우 상태로의 천이}이 생성되고, 또한 PWM 신호의 페이징(phasing)에 의해 생성된 어드레스 정보가 EEPROM(11)의 어드레스 정보에 대응하면, EEPROM(11)은 마이크로프로세서(21)에 의해 의도와는 달리 기록될 수 있다. 상기에 대응하는 그러한 신호들의 발생 가능성은 희박하다. 그러나, 이러한 잠재적인 문제를 회피하기 위한 하나의 접근법은 EEPROM(11) 내 다중 위치에 데이터를 중복 저장하는 것이다. 예시적인 본 실시예에 따라, 하나의 주어진 데이터 단위는 EEPROM(11)의 5개의 서로다른 메모리 위치에 중복 저장될 수 있다. 그후 데이터가 판독될 때, 데이터를 판독하는 소자{예컨대 프로세서(21)}는 데이터가 손상되었는지 여부를 결정하기 위하여 통계적인 기준(statistical threshold)을 적용할 것이다. 예컨대, 만약 데이터가 EEPROM(11) 내에서 5개의 서로다른 메모리 위치에 저장되어 있으면, 데이터를 판독하는 소자는 5개의 메모리 위치 중 3개가 동일한 데이터를 제공할 때 해당 데이터가 유효하다고 결정할 수 있다. 다른 통계적인 기준들도 물론 채용될 수 있다.

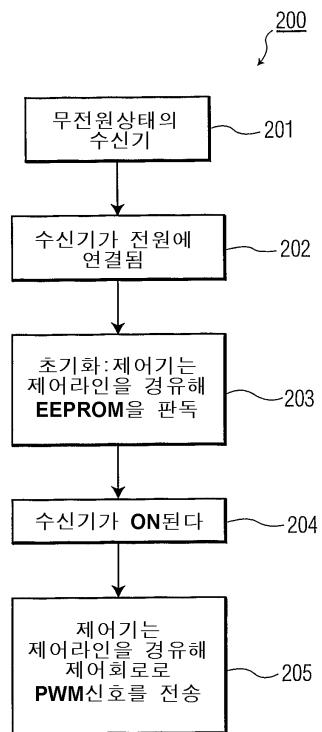

<24> 이제 도 2를 참조하면, 본 발명의 실시를 위한 예시적인 단계들을 보여주는 흐름도(200)가 도시된다. 예시 및 설명을 위하여, 도 2의 단계들은 도 1의 텔레비전 신호 수신기(100)를 참조하여 기술될 것이다.

<25> 단계(201)에서, 수신기(100)는 무전원 상태(unpowered state)이다. 즉, 수신기(100)는 가정용 플러그 콘센트 등과 같은 전기 전원 소스에 연결되어 있지 않다. 단계(202)에서, 수신기(100)는 전기 전원 소스에 연결(예컨대 플러그 인)되어 있으나 ON으로 스위칭되어 있지 않다. 즉, 수신기(100)는 단계(202)에서 제 1 동작 상태로 들어간다. 본 명세서에서 이전에 지적된 바와 같이, 마이크로제어기(21) 및 EEPROM(11)과 같은 수신기(100)의 특정 소자들은, 제 1 동작 상태 동안 대기 전원 소스 즉 전압 소스 V1으로부터 전기 에너지를 받는다.

<26> 단계(202)에서 전원 소스에 연결되는 것에 응답하여, 절차는 단계(203)으로 진행하는데, 여기서 수신기(100)는 초기화 절차를 수행한다. 구체적으로, 이 초기화 절차의 일부로서, 마이크로제어기(21)는 마스터 IC로서 동작하고 SCL(13) 및 SDL(15)을 경유하여 EEPROM(11)으로 제 1 제어 신호를 전송함으로써, 슬레이브 IC로서 동작하는 EEPROM(11)으로부터 데이터를 판독한다. 예시적인 일 실시예에 따라, EEPROM(11)으로부터 마이크로제어기(21)에 의해 판독된 데이터는 수신기(100)의 편향 동작을 제어하는데 사용되는 전압 데이터로 이루어져 있다. 마이크로제어기(21)는 내부 메모리(미도시됨)에 판독된 데이터를 저장하고, 수신기가 플러그 인되어 있거나 또는 다른 방식으로 전원공급되어 있는 한, 이를 유지시킨다.

<27> 다음에, 단계(204)에서, 수신기(100)는 예컨대 핸드-헬드 원격제어유닛과 같은 입력 단말로의 사용자 입력을 통해 ON으로 스위칭된다. 본 명세서에서 이전에 지적된 바와 같이, 수신기(100)가 전원 소스에 연결되어, ON으로

스위칭되어 있을 때, 수신기(100)는 제 2 동작 상태이다. 따라서, 단계(204)는 수신기(100)로 하여금 제 2 동작 상태로 들어가도록 한다. 제 2 동작 상태 동안에, 절차 흐름은 단계(205)로 진행하며, 여기서 마이크로제어기(21)는 제 2 제어 신호들을, 즉 제 1 PWM 신호와 제 2 PWM 신호를, 제 1 회로 보드(10)의 제어 회로로 전송한다. 즉, PWM1 단자는 SDL(15)로 제 1 PWM 신호를 출력하고, 이에 의해 제 1 회로 보드(10)의 제 1 제어 채널로 제 1 PWM 신호를 제공함으로써 출력 신호(17)의 생성을 인에이블한다. 유사하게, PWM2 단자는 SCL(13)로 제 2 PWM 신호를 출력하고, 이에 의해 제 1 회로 보드(10)의 제 2 제어 채널로 제 2 PWM 신호를 제공함으로써 출력 신호(19)의 생성을 인에이블한다. 이전에 지적된 바와 같이, 제 1 PWM 신호 및 제 2 PWM 신호는, 단계(203)에서 EEPROM(11)으로부터 판독된 전압 데이터에 따라 마이크로제어기(21)에 의해 생성될 수 있다. 앞서 언급된 방식에서, SCL(13) 및 SDL(15)은 마이크로제어기(21)의 2개의 상이한 동작 사이에서 공유된다.

<28> 비록 본 발명이 텔레비전 신호 수신기와 관련해서 기술되었으나, 본 발명은 디스플레이 디바이스를 구비하거나 또는 구비하지 않은, 다양한 시스템에 응용가능하며, 본 명세서에서 사용된 바와 같은 어절 "텔레비전 신호 수신기" 또는 "수신기"는, 디스플레이 디바이스를 포함하는 텔레비전 세트 또는 모니터를 포함하는, 그러나 이에 제한되지는 않는, 다양한 타입의 장치들 및 시스템들을 포함하는 것으로 의도되며, 또한 셋톱박스, 비디오 테이프 리코더(VTR), 디지털 다기능 디스크(DVD) 플레이어, 비디오 게임 박스, 개인용 비디오 리코더(PVR) 또는 디스플레이 디바이스를 포함하지 않을 수 있는 다른 장치와 같은 시스템이나 장치들을 포함하는 것으로 의도된다.

<29> 본 발명이 바람직한 설계를 가지는 것으로서 기술되었으나, 본 발명은 본 개시의 원리 및 범위 내에서 더 변형될 수 있다. 예컨대 본 명세서에 개시된 제어 라인은 메모리나 편향 회로가 아닌 다른 디바이스를 제어하기 위하여 장치의 상이한 동작 상태에서 사용될 수 있다. 따라서 본 출원은, 본 출원의 일반적인 원리를 사용하는 본 발명의 임의의 변형, 사용, 또는 적용을 커버하는 것으로 의도된다. 또한 본 출원은 본 발명과 관계있고 첨부된 특허청구범위의 한계안에 포함되는 본 기술분야의 알려지거나 관습적인 실무영역 내에 들어오는 것으로서 본 발명으로부터의 이러한 변형을 커버하는 것으로 의도된다.

### 산업상 이용 가능성

<30> 상술한 바와 같이, 본 발명은 텔레비전 신호 수신기와 같은, 복수의 회로 보드들 상에 장착된 소자들을 포함하는 전기 디바이스에 이용할 수 있는 것으로, 더 상세하게는, 신호 제어 라인들이 공유되도록 함으로써 이러한 디바이스 내 회로 보드들 사이에 요구되는 접속 수를 감소시키는 기법 등에 이용할 수 있다.

### 도면의 간단한 설명

<7> 도 1은 본 발명을 구현하기에 적절한 장치의 관련 부분의 도면.

<8> 도 2는 본 발명을 실현하기 위한 예시적인 단계들을 보여주는 흐름도.

도면

도면1

## 도면2