(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau

(43) International Publication Date

14 October 2004 (14.10.2004)

PCT

(10) International Publication Number

WO 2004/088731 A2

(51) International Patent Classification<sup>7</sup>: H01L 21/00

(21) International Application Number: PCT/US2004/009458

(22) International Filing Date: 29 March 2004 (29.03.2004)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data: 10/402,315 28 March 2003 (28.03.2003) US

(71) Applicant (for all designated States except US): GEORGIA TECH RESEARCH CORPORATION [US/US]; 859 Spring Street, Atlanta, Georgia 30331-0415 (US).

(72) Inventors; and

(75) Inventors/Applicants (for US only): WHITE, George, E. [US/US]; 2836 Saddlebrook Way, Marietta, Georgia 30064 (US). SWANIMATHAN, Madhavan [IN/US]; 1458 Grovehurst Drive, Marietta, Georgia 30062 (US). DALMIA, Sidharth [IN/US]; 115 N. Clublands Ct., Alpharetta, Georgia 30332 (US). SUNDARAM, Venkatesh [IN/US]; 5362 Medlock Corners Drive, Norcross, Georgia 30092 (US).

(74) Agents: GRIFFIN, Malvern, U., III et al.; Sutherland Asbill & Brennan LLP, 999 Peachtree Street, NE, Atlanta, Georgia 30309-3996 (US).

(81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW, MX, MZ, NA, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RU, SC, SD, SE, SG, SK, SL, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, YU, ZA, ZM, ZW.

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HU, IE, IT, LU, MC, NL, PL, PT, RO, SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

Published:

— without international search report and to be republished upon receipt of that report

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

A2

(54) Title: METHODS FOR FABRICATING THREE-DIMENSIONAL ALL ORGANIC INTERCONNECT STRUCTURES

WO 2004/088731

(57) **Abstract:** The present invention comprises methods for making three-dimensional (3-D) liquid crystalline polymer (LCP) interconnect structures using a high temperature single sided liquid crystalline polymer, and low temperature single sided liquid crystalline polymer, whereas both the high temperature LCP and the low temperature LCP are drilled using a laser or mechanical drill or mechanically punch to form a z-axis connection. The single sided Conductive layer is used as a bus layer to form z axis conductive stud within the high temperature and low temperature LCP, followed by deposition of a metallic capping layer of the stud that serves as the bonding metal between the conductive interconnects to form the z-axis electrical connection. High temperature and low temperature LCP circuit layers are etched or built up to form circuit patterns and subsequently bonded together to form final 3-D multilayer circuit pattern whereas the low temperature LCP melts to form both dielectric to dielectric bond to high temperature LCP circuit layer, and dielectric to conductive bond, whereas, metal to metal bonding occurs with high temperature metal capping layer bonding to conductive metal layer. The resultant structure is then packaged using two metallized organic cores that are laminated onto either side of the device using a low temperature adhesive with similar electrical properties and subsequently metallized to form the input output terminals and EM shielding.

METHODS FOR FABRICATING THREE-DIMENSIONAL

ALL ORGANIC INTERCONNECT STRUCTURES

BACKGROUND OF THE INVENTION

I. Field of the Invention

[0001] The present invention generally relates to three-dimensional all organic structures, and more particularly to three-dimensional organic interconnect structures for use in radio frequency and mixed signal module substrates and multilayer high-speed printed circuit boards.

II. Description of Related Art

[0002] Multilayer circuits typically comprise at least one conductive circuit layer bonded or laminated to a dielectric layer. The conductive circuit layer is generally a conductive metal such as copper, and the dielectric layer generally comprises a polymer resin such as epoxy. Depending on the selection of the dielectric layer and its thickness, the circuit can be either stiff or flexible.

[0003] Multilayer organic circuits incorporating thin film technologies are typically fabricated by parallel processing using diclad or monoclad layers that are sandwiched between bond ply materials to form a multilayer circuit construction. The number of metal layers can be as few as two and as many as sixty or more. The requirements for multilayer circuits in high density, high performance applications are becoming ever more demanding for high frequency applications. As a result there exists an unresolved need for a low cost multilayer process that can support both high frequency and high density (e.g., fine line and spaces, small via sizes) multilayer circuit

constructions.

#### SUMMARY OF THE INVENTION

[0004] The present invention comprises three-dimensional (3-D) multilayer circuit structures and methods of fabricating same wherein the circuit structures comprise uncladded high and low temperature organic material, such as liquid crystalline polymers (LCPs), teflon or polyphenyl ether (PPE) based materials, that have equivalent electrical and mechanical properties but differing melt temperatures, which enable a uniform homogeneous electrical circuit that can support high frequency and high bandwidth applications. The two different melt points allow for the stacking and lamination of individual circuitized layers to form multilayer construction, which when combined with a higher temperature metallic alloy provides for a reliable metal to metal joining that occurs at a temperature slightly above that at which the fusion bonding of the dielectric to dielectric and dielectric to metal occurs. Incorporation of resistive and high k particles or deposition resistive and high k films into or onto the high melt point and/or low melt point organic layers allows for the ability to integrate buried passives structures, (e.g., bias, decoupling and filter elements) in a 3-D multilayer construction.

[0005] The incorporation or deposition of the resistive materials into or on the organic layers provides for the ability to form single resistor elements and arrays when combined with a standardized lithographical process for circuit formation. Similarly, the incorporation of high dielectric constant materials or deposition of the same having dielectric constants from 8 to 20,000 provides for single capacitor elements and arrays when combined with standardized lithographical processes for circuit formation. This enables the fabrication of parallel plate capacitors, inter-digitated (comb) capacitors and distributed capacitance layers with capacitance densities well beyond  $1\text{ nf/cm}^2$ .

[0006] The use of uncladded high temperature and low temperature organic layers allow for the fabrication of fine line geometries down to five micron lines and spaces using build up processes that involve depositing a thin metal conductive layer by electroless plating or vacuum deposition, which could be any one of copper, Ni, Au, Pd, Pt. A photoresist is then deposited, lithographically exposed and then developed. A conductor metal layer is then electroplating through the patterned resist, wherein the

conductor metal could be any one of Cu, Ni, Au, Pd, or Pt. While the resist is still in place, an adhesive metal is plated on the previous conductor metal layer. The adhesive metal may be any one of a number of high temperature alloys that will bond at temperatures exceeding the softening point of the organic layers. Such alloys may 5 include, AuSn, PdSn, NiSn.

[0007] The various layers can be selectively interconnected by small via (also referred to herein as z-axis interconnects or studs) formed in the organic layers at the dimensions down to ten micron using laser or reactive ion etch techniques. Single side 10 copper formation on the underside of the LCP layer serves as a stop during via formation using a laser or mechanical drill. The underside copper also serves as a cathode or bus layer to provide for the formation of the z-axis interconnect or metallic stud to form a 3-D interconnect structure. The studs or z-axis interconnects are formed by electroplating either copper, nickel, gold, silver or similar conductive metal. The 15 use of electroplating allows for solid via stud formation for improved conductivity.

[0008] After fabrication of the conductive metal stud within an organic layer, the top of the stud is capped with high melting point metallic alloy that bonds to copper (or other metallic conductor material used) to form 3-D interconnection upon 20 lamination of high temperature and low temperature metallized organic layer, such as an LCP or similar organic material layer.

#### BRIEF DESCRIPTION OF THE SEVERAL VIEWS OF THE DRAWING(S)

25 [0009] Having thus described the invention in general terms, reference will now be made to the accompanying drawings, which are not necessarily drawn to scale, and wherein:

[0010] FIGS. 1A-1E are schematic representations of the incremental steps in 30 the fabrication of a multilayer structure in accordance with an embodiment of the present invention.

[0011] FIG. 2 is a schematic representation of multiple circuitized layers stacked in an alternating sequence of high and low temperature dielectrics.

[0012] FIG. 3 is a schematic representation of a multilayer circuitized structure including an expansion matched rigidizer embodiment of the present invention.

5 [0013] FIG. 4A and B are schematic representations of a multilayer circuitized structure including high k ceramic particles incorporated into an organic layer, or deposited as a film, in accordance with an embodiment of the present invention.

10 [0014] FIG. 5A and B are schematic representations of a multilayer circuitized structure including resistive particles incorporated into an organic layer, or deposited as a resistive film, in accordance with an embodiment of the present invention.

15 [0015] FIG. 6 is a schematic representation of a metalized circuitized structure including high k ceramic particles incorporated into the organic layer or deposited as a film on the organic layer, and a second organic layer including resistive particles incorporated into the second organic layer or deposited as a film on the second organic layer in accordance with an embodiment of the present invention.

20 [0016] FIG. 7 is a schematic representation of a multilayer circuitized structure including layers filled with high k ceramic and resistive particles and/or films deposited with high k ceramic and resistive particles, and a rigidizer layer in accordance with an embodiment of the present invention.

25 [0017] FIG. 8 is a schematic representation of a multilayer circuitized structure illustrating various packaging formats compatible with the present invention.

#### DETAILED DESCRIPTION

[0018] The present inventions now will be described more fully hereinafter with reference to the accompanying drawings, in which some, but not all embodiments of 30 the invention are shown. Indeed, these inventions may be embodied in many different forms and should not be construed as limited to the embodiments set forth herein; rather, these embodiments are provided so that this disclosure will satisfy applicable legal requirements. Like numbers refer to like elements throughout.

[0019] The present invention comprises three-dimensional (3-D) multilayer structures having at least one low temperature organic layer and at least one high temperature organic layer that are processed in a parallel fashion that provides for individual layers to be independently fabricated and tested prior to lamination into a 5 multilayer 3-D circuit. Metal to metal bonding is formed by incorporating a high temperature alloy that melts at a temperature slightly above the fusion point of the low temperature organic layer, but lower in temperature than the high melt point organic layer.

10 [0020] For purposes of the present invention, the organic layer or material may comprise any low cost, high performance organic material, such as polyphenyl ether (PPE) based materials, such as LD621 from Polyclad and N6000 series from Park/Nelco Corporation, Teflon organic from Rogers Corporation, or liquid crystalline polymer (LCP), such as LCP from Rogers Corporation or W.L. Gore & Associates, Inc. 15 These materials provide excellent hermicity and temperature independence, which emulates the performance of ceramic substrates used to construct multilayer ceramic structures.

[0021] Advantageously, the construction of the circuits of the present invention 20 does not require an adhesive or lower melting point dielectric to form the 3-D interconnect. As is known to those skilled in the art, adhesives (which are typically epoxies or polyimides) have dissimilar electrical and mechanical properties that are susceptible to moisture uptake, which degrades performance. In addition, the multilayer 3-D circuits of the present invention are homogeneous (e.g., where the two 25 organic materials have the same thickness, dielectric constant, loss tangent, volume resistivity, matching coefficient of thermal expansion (CTE), and modulus) which is highly desirable for improved performance and design ease in high speed digital and high frequency RF/wireless applications both from an electrical standpoint and mechanical standpoint (e.g., to minimize warpage). From an electrical standpoint, the 30 homogeneous construction provides smoother transitions and signal propagation in the z-axis direction, and facilitates the design of matched impedance networks since the dielectric constant and loss are the same, layer to layer.

[0022] The present invention includes the incorporation of high  $k$  and resistive particles in the organic layers and/or the deposition of high  $k$  and resistive films, which represents additional advantages in design flexibility in realizing RF circuits that require RC, LC, and RLC networks. Thus, filters, couplers, duplexers, baluns, mixers, etc. can be integrally fabricated. Such structures are possible because the host matrix material (e.g., filled LCP) is the same as the insulating low temperature and high temperature dielectrics. The low and/or high temperature LCP layer either can be filled with high  $k$  dielectric particles or incorporate a high  $k$  deposited thin film, which then can be incorporated into the circuit to form embedded decoupling, bandpass filters, low pass filters, baluns, couplers, etc., and baseband circuits such as capacitors, blocking filters, etc. Incorporation of the high  $k$  particles may be achieved by introducing a surfactant onto high  $k$  particles, such as Barium titinate, lead magnesium nitrate or titantium dioxide to minimize particle clustering, followed by drying and then subsequent introduction in the organic melt prior to drawing and pressing the cladded organic layer into finished sheets. The resultant high  $k$  layers sandwiched between copper sheets or planes can serve as embedded decoupling layers that can be processed in the multilayer stack for noise suppression and other benefits. The amount of high  $k$  particle incorporated into the organic layer will determine the resultant dielectric constant values and mechanical integrity. Typical volume fraction will vary from 10% to 50%. Additionally, high  $k$  organic layers that are either deposited or filled enable passive components and arrays that can support applications beyond 6 GHz, and are process compatible for the 3-D multilayer build up described herein. This is achieved, at least in part, by lithographically defining the top and bottom conductor layers to form a parallel plate construction. The filled organic as well as the non-filled organic is sandwich between the lithographically defined top and bottom conductor layers.

[0023] The present invention also provides for the incorporation of resistive particles in the organic laminates or the deposition of resistive thin films on organic laminates, which enables passive components and arrays that provide for the formation of RC, and RLC networks. The resistive particles may include, for example, carbon, silicon carbide, rhuthenium oxide, copper, silver, or combinations thereof, that can be incorporated into the organic melt up to 50% volume, while resistive thin films could include NiP, TaN, NiCr, NiWP, ZnO, etc. A resistive circuit is completed upon deposition and circuitization of metal contacts to form terminals, thereby forming

planar and annular resistors and resistor networks. In addition, resistor networks are formed by plating, sputtering, evaporating or chemical vapor deposition of metals and/or metallic alloys on finished organic laminates to form low and high value resistors and resistor networks upon circuitization of metallic terminals to form planar 5 and annular resistors and resistor networks. The resistor devices or elements can also be fabricated by laminating, electroplating, vacuum deposition, or printing of resistive films on the organic laminates. Upon putting down the resistive film, a metallic layer is deposited on the resistive film and the resistor and/or resistor networks are defined via a print and etch technique. In defining resistors or resistive networks using filled 10 resistive organic layers, the filled organic layers are metallized either by plating, lamination or vacuum deposition. The conductors can then be lithographically defined to form the metallic terminals of the resistors.

[0024] The thin film of high  $k$  or resistive material can be fabricated on an 15 organic layer using known techniques. For example, a layer of high  $k$  material can be deposited by CVD or sputtering and then lithographically defined into a desired design. Likewise, a layer of resistive material can be deposited by evaporation, CVS or sputtering and then lithographically defined. In either case, the thickness of the thin film will vary based upon the desired performance characteristics sought.

20 [0025] A 3-D multilayer circuit in accordance with the present invention can be fabricated in either sequential mode or reel to reel. In a sequential mode, a high temperature unclad or single sided organic laminate from 1-10 mils in thickness is initially obtained. For the unclad example, one side is metallized by, for example, 25 sputtering or chemical-electro deposition of a thin conductive film, such as copper, nickel or gold. The other side is then drilled to form a via that terminates at the polymer-metal interface. Upon appropriate surface treatment (e.g., by plasma or chemical etching), the via is then metallized by electroless plating and capped with an adhesive metal, such as gold-tin. The bottom layer, which served as the conductive 30 layer or bus layer, is then circuitized to form a single metal layer circuit. Upon completion of the circuit, other layers (e.g., alternating layers of high and low melting point material) are combined so that 3-D connections are formed by the vias h/l stackup. The layers are stacked in a lamination press, whose temperature and pressure conditions will vary due to a number of known factors, such as the number of layers

and the adhesive metal composition. As an example, the layers may be laminated together in a press applying 75-500 psi at 270-280°C for 5-20 minutes. Within this stack could be one or more high k dielectric layers and resistive layers. The stack is taken up in temperature and pressure and laminated to fuse the low temperature dielectric to the high temperature dielectric, the low temperature dielectric to the metal, and the metal alloy to the trace metal on the organic layer.

[0026] The 3-D metal layer circuit can also be processed onto an expansion matched CTE (coefficient of thermal expansion) core or substrate. The core material and the dielectric material can be tailored to have the same thermal expansivity, which provides for little to no warpage for improved reliability. In addition, the CTE match of core and dielectric can be tailored to that of silicon devices, which can be subsequently joined to the 3-D interconnect in the absence of underfill.

15 Illustrative Embodiments

[0027] The following is an illustrative embodiment of a method of fabricating a multilayer organic structure according to the present invention utilizing LCP as the organic material, followed by several alternative embodiments.

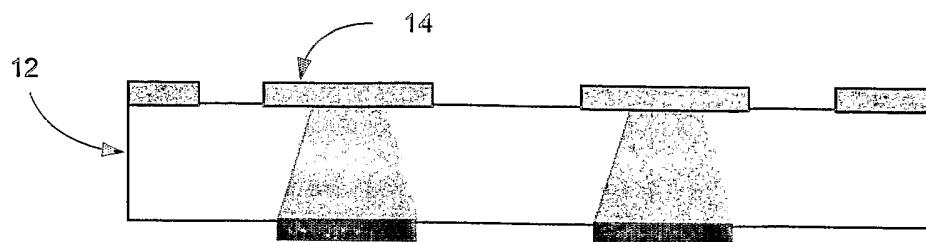

20 [0028] FIG. 1A is a schematic representation of an unclad high temperature or low temperature LCP dielectric film 12, in accordance with an embodiment of the present invention. In a preferred embodiment, the high and low temperature LCP film has a CTE between 2 and 20 ppm/°C.

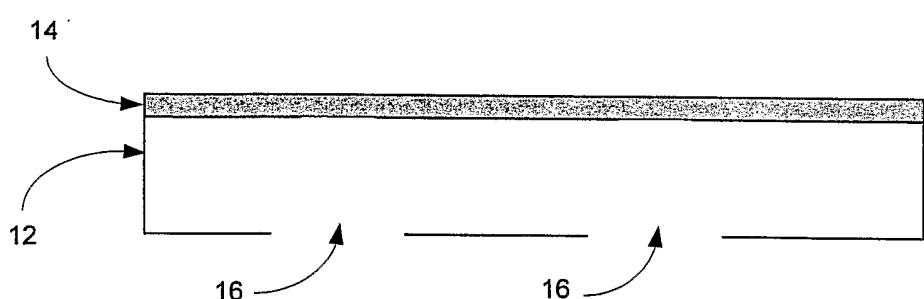

25 [0029] Next, as illustrated in FIG. 1B, a metalized layer 14 has been fabricated on the high temperature or low temperature LCP dielectric film 12, in accordance with an embodiment of the present invention. Metallization of the LCP film 12 can be accomplished by electroless and electroplating, sputtering, evaporation, or chemical vapor deposition. Metallization can be an adhesive metal such as copper, chromium, 30 titanium, or platinum, followed by deposition of either copper, nickel, gold, or palladium. The thickness is preferably between 0.5 microns to 200 microns.

[0030] Next, as illustrated in FIG. 1C, the high temperature or low temperature LCP dielectric film 12 that has been drilled either by laser, mechanical, punch, etch,

reactive ion etch to form vias 16 down to the underside of the metallization. Suitable lasers include UV, CO<sub>2</sub>, excinor, or YAG, and the drilling can be accomplished using computer numeric control (CNC) or using a patterned mask for image transfer.

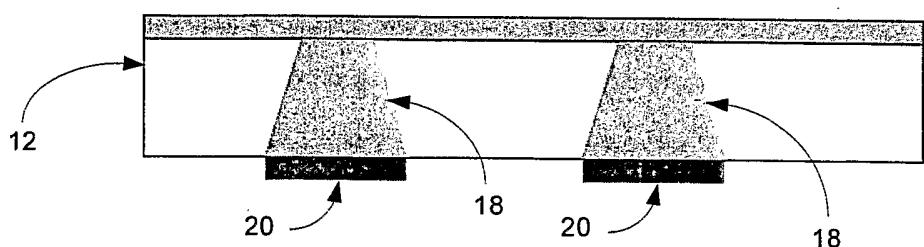

5 [0031] As illustrated in FIG. 1D, the metallized vias 16 have been plated, sputtered, or filled with conductive paste or evaporated, to form a conductive via stud 18 within the via 16, followed by the fabrication of an adhesive capping layer 20, which comprises a high melting point alloy that forms metal to metal joining. The solid via studs 18 form the z-axis interconnect between the layer of the stack up, while the 10 adhesive caps 20 serve to form the reliable metal to interconnect bond. The cap is preferably a metallic solder of a binary alloy that melts at a temperature above that of the fusion point of the high temperature and low temperature LCP layers.

15 [0032] Next, as illustrated in FIG. 1E, the metalized layer 14 fabricated (e.g., printed and etched to form a single sided circuit layer) on either a high temperature or low temperature LCP dielectric film 12 is circuitized (e.g., etched). Circuitization of the LCP sheets can also be accomplished in an additive or semi additive method, where the defined circuit layer is formed by plating through a patterned photoresist. Followed by stripping of the resist and removal of the conductive bus layer used for the 20 electroplating.

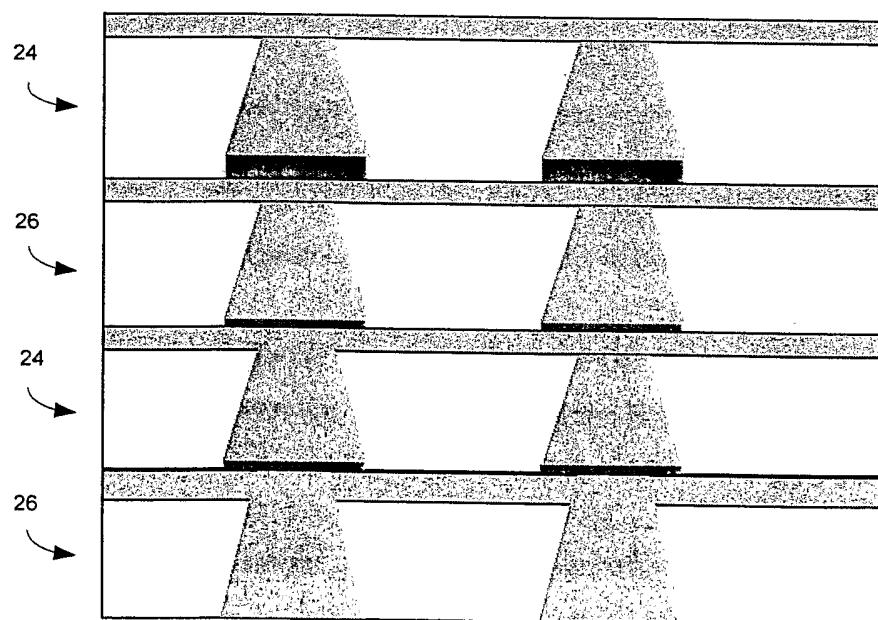

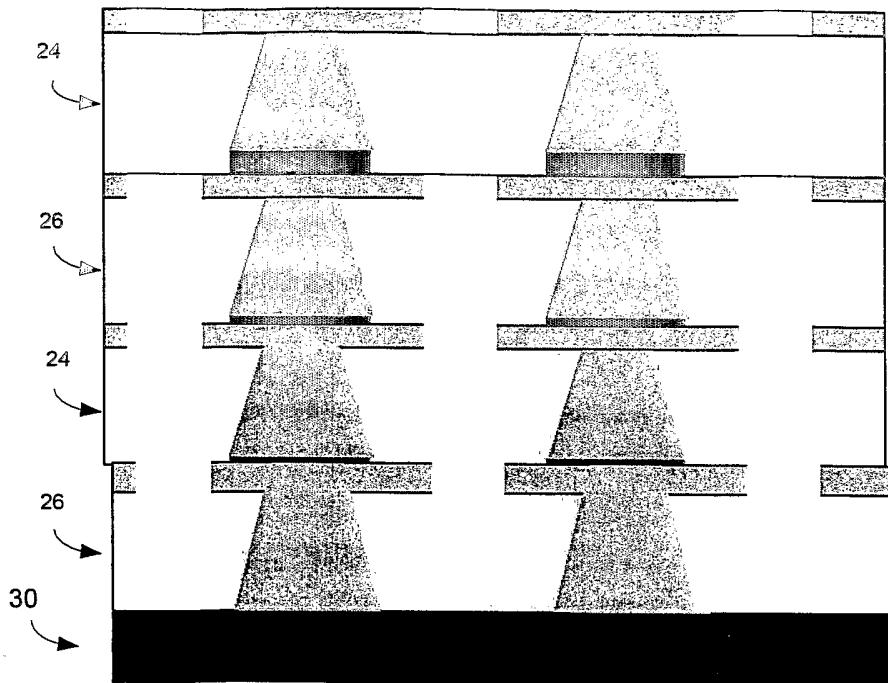

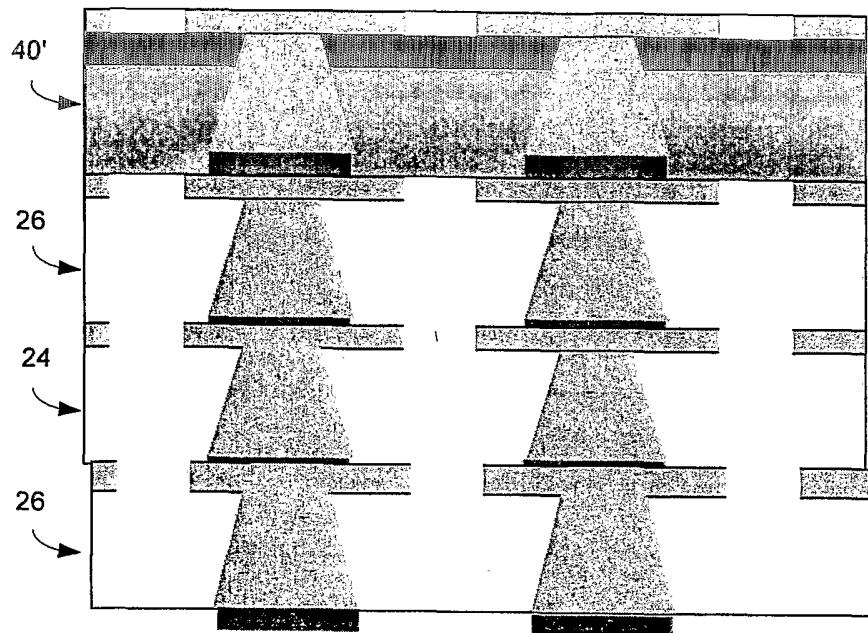

25 [0033] FIG. 2 is a schematic representation of multiple circuitized layers that have been stacked in an alternating sequences of aligned high temperature circuitized dielectric layers 24 and low temperature circuitized dielectric layers 26, which are fusion bonded at temperatures and pressures sufficient enough to form a multilayer flex circuit construction, in accordance with an embodiment of the present invention.

30 [0034] FIG. 3 is a schematic representation of circuitized layers that have been stacked in alternating sequences of high temperature circuitized dielectric layers 24 and low temperature circuitized dielectric layers 26 with a matched coefficient of thermal expansion (CTE) rigidizer 30, which can be either metallic or other inorganic, and which is fusion bonded to form a multilayer rigid circuit construction. The rigidizer can be disposed above or below the circuitized layers, as shown, or alternatively, the rigidizer can be aligned and placed between circuitized layers, where the circuit layers

are stacked on either side of the rigidizer, followed by lamination of the entire stack up to form a multilayer rigidized circuit construction. Depending on the material comprising the rigidizer, it can also serve as a heat sink, ground or power plane, or EMI shielding. Examples of suitable materials include copper-invar-copper (CIC) or

5 aluminum silicon carbide.

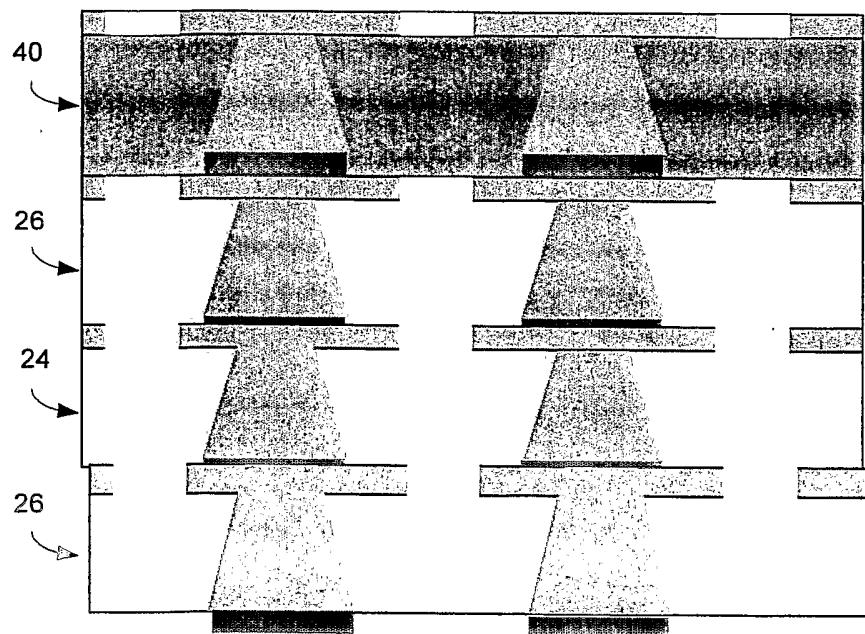

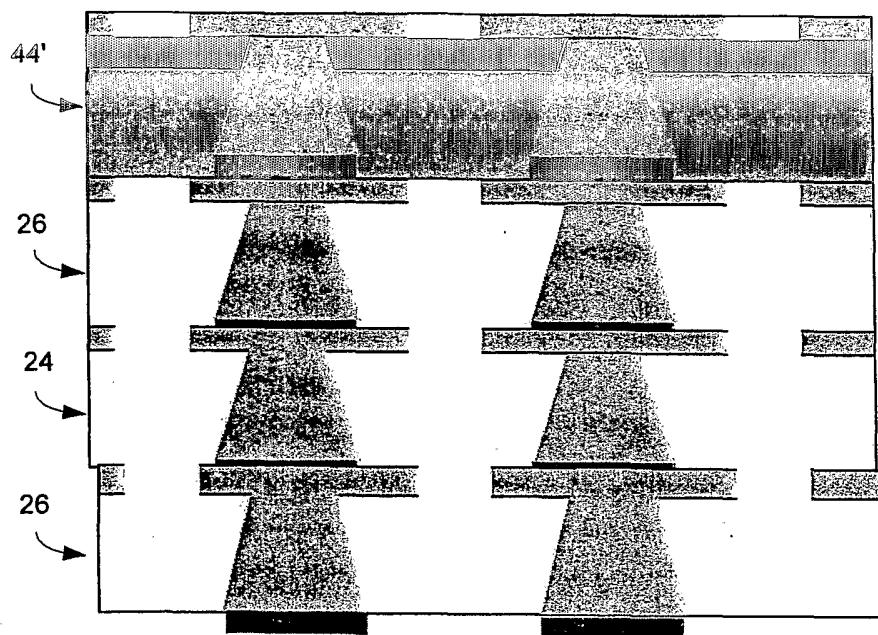

[0035] FIG. 4A is a schematic representation of circuitized layers that have been stacked in alternating sequences of high temperature circuitized dielectric layers 24 and low temperature circuitized dielectric layers 26 with an LCP layer 40 filled with high k ceramic particles. Alternatively, a high k film 40' can be deposited on LCP layer, as shown in FIG. 4B. The LCP layer 40 is fusion bonded in the multilayer stackup and circuitized to form a multilayer flex circuit construction with embedded inductors and capacitors in accordance with an embodiment of the present invention.

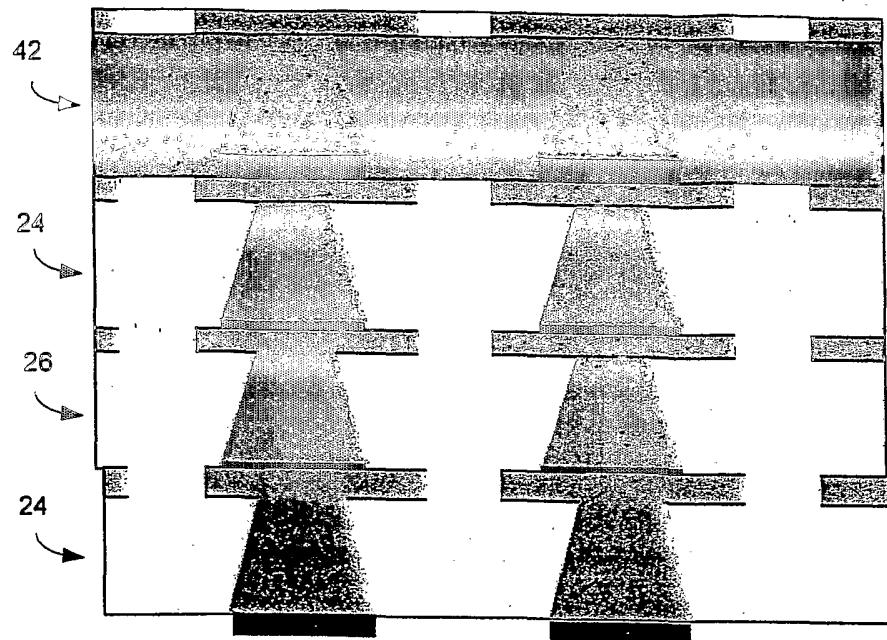

15 [0036] FIG. 5A is a schematic representation of circuitized layers that have been stacked in alternating sequences of high temperature circuitized dielectric layers 24 and low temperature circuitized dielectric layers 26 with an LCP film 42 filled with resistive particles. Alternatively, a resistive films 42' (such as NiCr, TaN, NiP, or NiWP) can be deposited on the LCP layer as illustrated in FIG. 5B. The LCP layer is 20 fusion bonded to form a multilayer flex circuit construction with embedded resistors (R), inductors (L) and capacitors (C).

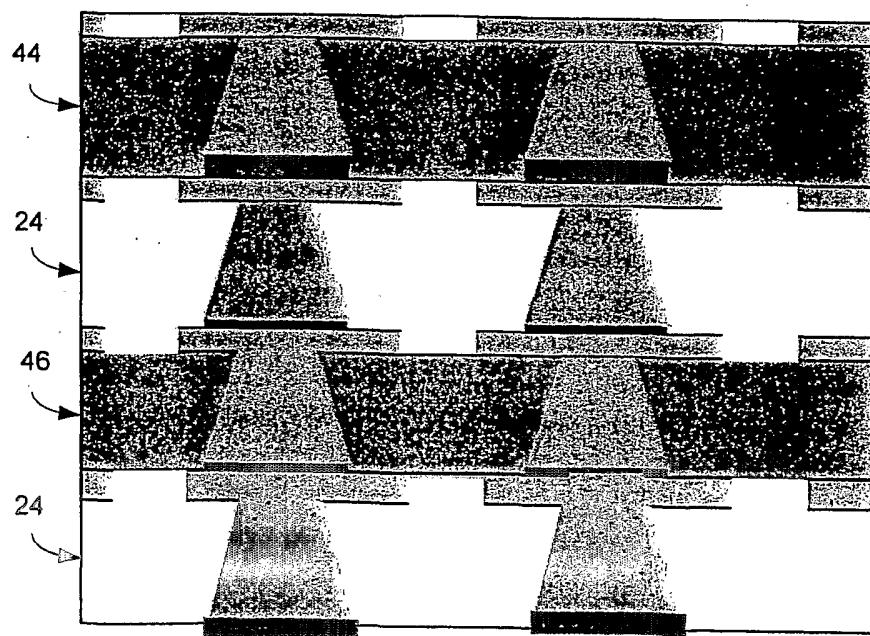

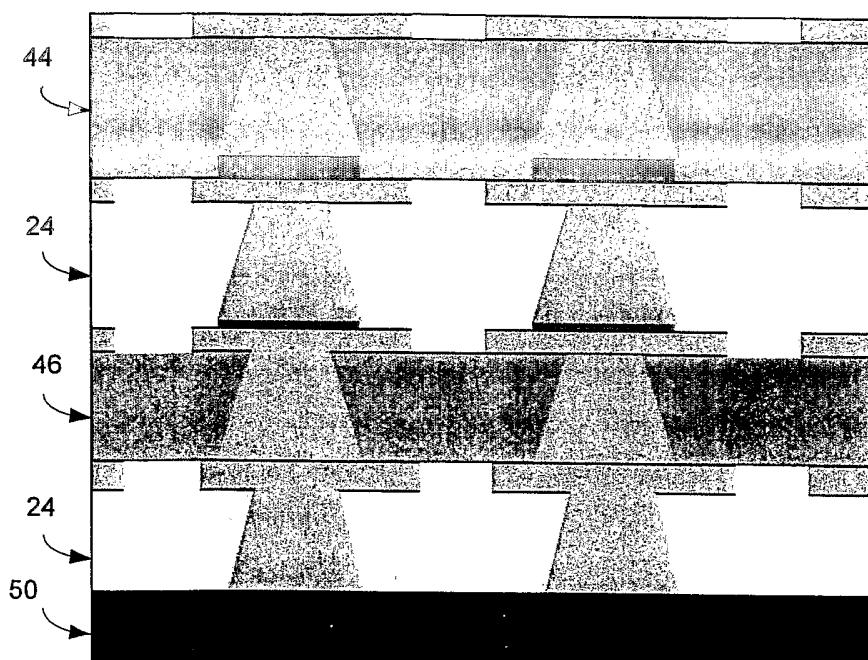

25 [0037] FIG. 6 is a schematic representation of circuitized layers that have been stacked in alternating sequences of high temperature circuitized dielectric layers 24 and low temperature circuitized dielectric layers 26 that includes a layer 44 that includes a deposited high k dielectric film or is LCP filled with high k ceramic particles, and in a separate discrete level of the stack, a layer 46 that includes a deposited resistive film 46 or is filled LCP with resistive particles, wherein the stack is fusion bonded to form a multilayer flex circuit construction with embedded R, L and C's.

30

[0038] FIG. 7 is a schematic representation of a rigid multilayer circuit of FIG. 6 with a metallic, inorganic or organic rigidizer 50. The rigidizer 50 can be located on either side of the multilayer circuit stackup or within the multilayer stack up to form a rigid multilayer circuit construction with embedded components such as R, L, and C's.

Through vias that are filled with plated copper or conductor paste can be used to connect circuit layers on opposite sides of the rigidizer. The multilayer substrate or module can be used for interconnecting a vast array of active and passive components either through direct attached methods or surface mount technologies.

5

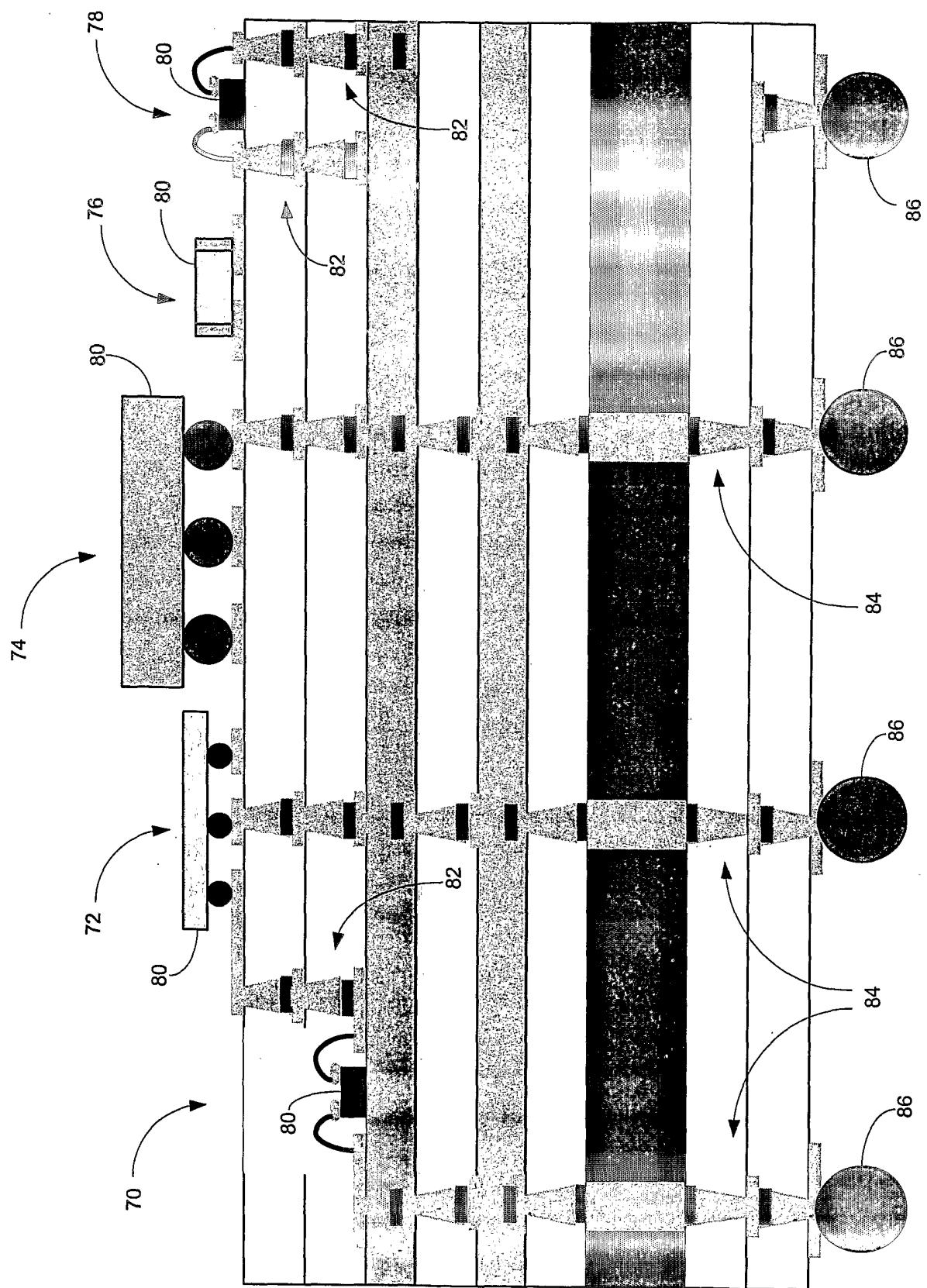

[0039] The multilayer 3D interconnect structure described herein can support the packaging and interconnection of various active and passive components in addition to the passive components embedded in the structure to form functional modules or system boards for digital, RF/wireless, or mixed signal modules. The ability to tailor the expansion of the multilayer circuit, described above, enables the packaging of different active chips such as silicon CMOS, SoI, SiGe, GaAs, and surface mount passive components in a highly reliable platform. For example, FIG. 8 is a schematic representation of a multilayer circuitized structure including various illustrative packaging formats supported by the present invention. Suitable packaging formats include, but are not limited to, flip-chip, wafer level packages (WLP), chip scale packages (CSP), ball grid array (BGA), wire bonded devices and various surface mount devices (SMD or SMT).

[0040] The formats illustrated in FIG. 8 include cavity flip chip or wirebond 70, flip chip wafer level packaging 72, BGA/CSP 74, SMD/SMT 76 and wire bond 78. The chips and/or package components 80 can be attached on a top surface of the multilayer circuit or within cavities formed inside the multilayer circuit using routing, punching, laser machining or other standard processes known to those skilled in the art. These cavities can be single level or multilevel and can be interconnected to other circuit layers using microvias or plated through holes. Using microvias 82 and plated through holes 84, the packaged components 80 on the top side of the module or in cavities can be interconnected to each other, to the embedded passive layers that include capacitors, inductors, resistors, etc., or to the BGA pads 80 on the bottom side of the module. The side walls of the module substrate can be covered with conductor like Cu, Ni, Au or other absorbing materials to provide shielding from EMI and other external radiation. This shielding can be formed with electroless and electroplating, vacuum deposition, lamination or other deposition methods known to those skilled in the art. The assembled multilayer module substrate can form a system board for a

system or can be terminated with ball grid array on the bottom side or wirebonded from the top side for further interconnection to other components on a system board.

[0041] Many modifications and other embodiments of the inventions set forth

5 herein will come to mind to one skilled in the art to which these inventions pertain

having the benefit of the teachings presented in the foregoing descriptions and the

associated drawings. Therefore, it is to be understood that the inventions are not to be

limited to the specific embodiments disclosed and that modifications and other

embodiments are intended to be included within the scope of the appended claims.

10 Although specific terms are employed herein, they are used in a generic and descriptive

sense only and not for purposes of limitation.

## THAT WHICH IS CLAIMED:

1. A method of fabricating 3-D multilayer interconnect structures, comprising:

- 5 providing a first single sided circuitized layer of a first melting point having a first conductive layer;

- providing a second single sided circuitized layer of a second melting point including at least one metal filled z-axis via connection stud;

- capping the z-axis stud of the second organic layer with a high temperature bonding material; and

- 10 bonding the low temperature organic layer to the high temperature organic layer;

- wherein the first organic layer forms a fusion bond with the second organic layer, and the cap on the second organic layer forms a metal to metal bond with the conductive layer first organic layer.

2. The method of claim 1, wherein the conductive layer comprises at least one of copper, aluminum, gold, nickel, iron, silver, zinc, chromium and a combination thereof.

- 20 3. The method of claim 1, wherein at least one conductive layer on one of the low temperature and high temperature organic layers serves as a bus layer prior to the z-axis via stud formation.

- 25 4. The method of claim 1, wherein the first melting point is less than the second melting point.

5. The method of claim 1, wherein the first melting point is greater than the second melting point.

- 30 6. The method of claim 1, wherein the cap on the vias of the second organic LCP layer is a metallic solder of a binary alloy that melts above a fusion point of the first and second organic layers.

7. The method of claim 1, wherein the first conductive layer has a thickness from approximately 0.5 microns to 200 microns.

8. The method of claim 1, wherein the first and second organic layers are 5 laminated together in a stack to form a three-dimensional (3-D) circuit.

9. The method of claim 8, wherein the 3-D circuit is a flexible circuit.

10. The method of claim 8, wherein the 3-D circuit is a rigid circuit.

11. The method of claim 8, wherein the coefficient of thermal expansion of the completed 3-D circuit in the x and y directions are substantially matched.

12. The method of claim 8, wherein the coefficient of thermal expansion of 15 the first and second organic layers is between 2 and 20 ppm/ $^{\circ}$ C.

13. The method of claim 1, wherein the second organic layer is sufficiently filled with high k dielectric constant particles to achieve a suitable high k film for high value capacitors and resonator structures.

20

14. The method of claim 1, wherein the second organic layer includes a thin film of high k dielectric constant material.

15. The method of claim 1, wherein the second organic layer is sufficiently 25 filled with resistive particles and circuitized to form a resistor or a resistor network.

16. The method of claim 1, wherein the second organic layer includes a thin film of resistive material.

30

17. The method of claim 1, further comprising an expansion matched core that is bonded to one of the first or second organic layers to provide expansion matching to one of an organic, ceramic and metal substrates.

18. The method of claim 1, wherein the expansion matched core is metallic, and performs thermal and electrical functions.

19. A multilayer liquid crystalline polymer circuit; comprising

5 low temperature liquid crystalline polymer layer (LCP) having a single

circuitized surface;

high temperature liquid crystalline polymer layer having a single circuitized

surface;

at least one z-axis interconnect structure interconnecting the circuitized surfaces

10 of the low temperature and high temperature LCP layers.

20. The circuit of claim 19, wherein at least one of the low temperature and high temperature LCP layers comprises at least one of high k particles and resistive particles.

15

21. The circuit of claim 19, wherein one of the low temperature and high temperature LCP layers includes a z-axis via aligned in the z-axis with one of the z-axis interconnect structure.

FIG. 3

FIG. 4A

FIG. 4B

FIG. 5A

FIG. 6

FIG. 5B

FIG. 7

FIG. 8