(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4046822号

(P4046822)

(45) 発行日 平成20年2月13日(2008.2.13)

(24) 登録日 平成19年11月30日(2007.11.30)

(51) Int.Cl.

H04L 29/08 (2006.01)

F 1

H04L 13/00 307A

請求項の数 15 外国語出願 (全 14 頁)

(21) 出願番号 特願平9-338730

(22) 出願日 平成9年12月9日(1997.12.9)

(65) 公開番号 特開平10-294771

(43) 公開日 平成10年11月4日(1998.11.4)

審査請求日 平成16年11月24日(2004.11.24)

(31) 優先権主張番号 763687

(32) 優先日 平成8年12月11日(1996.12.11)

(33) 優先権主張国 米国(US)

(73) 特許権者 597004720

サン・マイクロシステムズ・インコーポレーテッド

Sun Microsystems, Inc.

アメリカ合衆国 カリフォルニア州 95054 サンタクララ ネットワークサークル 4150

(74) 代理人 100089705

弁理士 社本 一夫

(74) 代理人 100071124

弁理士 今井 庄亮

(74) 代理人 100076691

弁理士 増井 忠式

最終頁に続く

(54) 【発明の名称】データ・バスの動的終端ロジックのための方法および装置

## (57) 【特許請求の範囲】

## 【請求項 1】

ワイヤオアのデータ転送のため特性インピーダンスをもつ双方向データ・バスであって、第1のエンド・ドライバであって、前記データ・バスの第1の端部に結合しており、前記第1エンド・ドライバは、前記第1エンド・ドライバの出力端部と高電圧との間に結合した第1のプルアップ・トランジスタと、前記第1エンド・ドライバの前記出力端部とグランドとの間に結合した第1のプルダウン・トランジスタとを備え、前記第1プルアップ・トランジスタおよび前記第1プルダウン・トランジスタは、それぞれ前記特性インピーダンスに一致するソース・ドレイン間のインピーダンスを有することを特徴とする、第1エンド・ドライバと、第2のエンド・ドライバであって、前記データ・バスの第2の端部に結合しており、前記第2エンド・ドライバは、前記第2エンド・ドライバの出力端部と高電圧との間に結合した第2のプルアップ・トランジスタと、前記第2エンド・ドライバの前記出力端部とグランドとの間に結合した第2のプルダウン・トランジスタとを備え、前記第2プルアップ・トランジスタおよび前記第2プルダウン・トランジスタは、それぞれ前記特性インピーダンスと一致するソース・ドレイン間のインピーダンスを有することを特徴とする、第2エンド・ドライバと、を備えた双方向データ・バス。

## 【請求項 2】

請求項1記載の双方向データ・バスであって、さらに、前記データ・バスの前記第1端部と前記第2端部との間ににおいて前記データ・バスに結合した第1のミッド・ドライバを

備えること、を特徴とする双方向データ・バス。

【請求項 3】

請求項 2 記載の双方向データ・バスにおいて、前記第 1 ミッド・ドライバは、第 3 のプルダウン・トランジスタと、第 3 のプルアップ・トランジスタとのうち、少なくとも第 3 プルダウン・トランジスタを備えたこと、を特徴とする、双方向データ・バス。

【請求項 4】

請求項 3 記載の双方向データ・バスであって、前記第 3 プルダウン・トランジスタは、前記データ・バスとグランドとの間に結合し、前記第 3 プルアップ・トランジスタは、前記データ・バスと電源との間に結合すること、を特徴とする双方向データ・バス。

【請求項 5】

請求項 3 記載の双方向データ・バスであって、さらに、前記データ・バスの前記第 1 端部と前記第 2 端部との間ににおいて前記データ・バスに結合した第 2 のミッド・ドライバを含むこと、を特徴とする双方向データ・バス。

【請求項 6】

請求項 5 記載の双方向データ・バスであって、前記第 2 ミッド・ドライバは、前記データ・バスとグランドとの間に結合した第 4 のプルダウン・トランジスタと、前記データ・バスと電源との間に結合した第 4 のプルアップ・トランジスタとを備えたこと、を特徴とする双方向データ・バス。

【請求項 7】

データ信号を伝送するため特性インピーダンスをもつワイヤオア・データ・バスであつて、

第 1 のドライバであって、前記データ・バスの第 1 の端部に結合しており、前記第 1 ドライバは、第 1 のプルアップ・トランジスタと、第 1 のプルダウン・トランジスタとを備え、前記第 1 プルアップ・トランジスタが前記第 1 ドライバの出力端子と高電圧との間に結合し、前記第 1 プルダウン・トランジスタが前記第 1 ドライバの出力端子とグランドとの間に結合しており、前記第 1 プルアップ・トランジスタおよび前記第 1 プルダウン・トランジスタが、それぞれ前記特性インピーダンスと実質的に一致するソース・ドレイン間のインピーダンスを有すること、を特徴とする第 1 のドライバと、第 2 のドライバであつて、前記データ・バスの第 2 の端部に結合しており、前記第 2 ドライバは、第 2 のプルアップ・トランジスタと、第 2 のプルダウン・トランジスタとを備え、前記第 2 プルアップ・トランジスタが前記第 2 ドライバの出力端子と高電圧との間に結合し、前記第 2 プルダウン・トランジスタが前記第 2 ドライバの出力端子とグランドとの間に結合しており、前記第 2 プルアップ・トランジスタおよび前記第 2 プルダウン・トランジスタが、それぞれ前記特性インピーダンスに一致するソース・ドレイン間のインピーダンスを有すること、を特徴とする第 2 のドライバと、

を備えたワイヤオア・データ・バス。

【請求項 8】

請求項 7 記載のワイヤオア・データ・バスであつて、

前記第 1 ドライバは、第 1 の信号を前記データ・バスに伝送するため、前記第 1 プルアップ・トランジスタを活性化することと前記第 1 プルダウン・トランジスタを活性化することとの間でスイッチングする回路を含み、

前記第 2 ドライバは、第 2 の信号を前記データ・バスに伝送するため、前記第 2 プルアップ・トランジスタを活性化することと前記第 2 プルダウン・トランジスタを活性化することとの間でスイッチングする回路を含むこと、

を特徴とするワイヤオア・データ・バス。

【請求項 9】

請求項 7 記載のワイヤオア・データ・バスであつて、さらに、前記データ・バスの前記第 1 端部と前記第 2 端部との間ににおいて前記データ・バスに結合したミッド・ドライバを含むこと、を特徴とするワイヤオア・データ・バス。

【請求項 10】

10

20

30

40

50

請求項 9 記載のワイヤオア・データ・バスであって、さらに、前記データ・バスに前記ミッド・ドライバと前記第 2 ドライバとの間で結合した第 2 のミッド・ドライバを含むこと、を特徴とするワイヤオア・データ・バス。

【請求項 11】

請求項 10 記載のワイヤオア・データ・バスであって、前記ミッド・ドライバは、前記データ・バスとグランドとの間に結合したプルダウン・トランジスタを含み、前記第 2 ミッド・ドライバは、前記データ・バスとグランドとの間に結合したプルダウン・トランジスタを含むこと、を特徴とするワイヤオア・データ・バス。

【請求項 12】

請求項 11 記載のワイヤオア・データ・バスであって、前記データ・バス上に立ち上りパルスを発生するため、前記ミッド・ドライバは、前記データ・バスと電源との間に結合したプルアップ・トランジスタを含み、前記第 2 ミッド・ドライバは、前記データ・バスと電源との間に結合したプルアップ・トランジスタを含むこと、を特徴とするワイヤオア・データ・バス。

【請求項 13】

データを第 1 のコンピュータと第 2 のコンピュータとの間で転送するため特性インピーダンスをもつ双方向データ・バスを有するコンピュータ・システムであって、

第 1 のエンド・ドライバであって、前記第 1 コンピュータの前記データ・バスの第 1 の端部に結合しており、前記第 1 エンド・ドライバは、前記第 1 エンド・ドライバの出力端部と高電圧との間に結合した第 1 のプルアップ・トランジスタと、前記第 1 エンド・ドライバの前記出力端部とグランドとの間に結合した第 1 のプルダウン・トランジスタとを備え、前記第 1 プルアップ・トランジスタおよび前記第 1 プルダウン・トランジスタは、それぞれ前記特性インピーダンスに一致するソース・ドレイン間のインピーダンスを有することを特徴とする、第 1 エンド・ドライバと、

第 2 のエンド・ドライバであって、前記第 2 コンピュータの前記データ・バスの第 2 の端部に結合しており、前記第 2 エンド・ドライバは、前記第 2 エンド・ドライバの出力端部と高電圧との間に結合した第 2 のプルアップ・トランジスタと、前記第 2 エンド・ドライバの前記出力端部とグランドとの間に結合した第 2 のプルダウン・トランジスタとを備え、前記第 2 プルアップ・トランジスタおよび前記第 2 プルダウン・トランジスタは、それぞれ前記特性インピーダンスに一致するソース・ドレイン間のインピーダンスを有することを特徴とする、第 2 エンド・ドライバと、

を備えたコンピュータ・システム。

【請求項 14】

請求項 13 記載のコンピュータ・システムは、さらに、前記データ・バスの前記第 1 端部と前記第 2 端部との間ににおいて前記データ・バスに結合した第 1 のミッド・ドライバを含み、前記第 1 ミッド・ドライバは、第 3 のプルダウン・トランジスタと、第 3 のプルアップ・トランジスタとのうち、少なくとも第 3 のプルダウン・トランジスタを備え、前記第 3 プルダウン・トランジスタは、前記データ・バスとグランドとの間に結合し、前記第 3 プルアップ・トランジスタは、前記データ・バスと電源との間に結合すること、を特徴とするコンピュータ・システム。

【請求項 15】

請求項 14 記載のコンピュータ・システムであって、さらに、前記第 1 ミッド・ドライバと前記データ・バスの前記第 2 端部との間に結合した第 2 ミッド・ドライバを含み、前記第 2 ミッド・ドライバは、前記データ・バスとグランドとの間に結合した第 4 のプルダウン・トランジスタと、前記データ・バスと電源との間に結合した第 4 のプルアップ・トランジスタとを含むこと、を特徴とするコンピュータ・システム。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は、データ・バス転送に関し、特に、データ・バスの性能を向上させるためのデー

10

20

30

40

50

タ・バスの動的終端ロジックに関するものである。

【0002】

【従来の技術】

コンピュータ技術がとんとん拍子に成長し続けるにつれ、コンピュータ技術のユーザは、これまでよりもさらに小さなパッケージでより一層高速のシステムに対し飽くなき欲求を持っている。より高速のシステムに対ししばしば脆弱なリンクとなるシステムの1つの領域は、データ・バスである。このデータ・バスは、1つのサブシステムから別のサブシステムへのデータの転送を電気信号の形態で提供する。頻繁に、システムのデータ・バスは、データ転送で圧倒され、したがってシステムのボトルネックとなることがある。

【0003】

高性能の双方向データ・バス設計においては、データ転送のボトルネック問題は、同じデータ・バス上でデータ転送を行う多数のデバイス並びに2方向におけるデータ転送により複合的になっている。アドレス・バスの駆動のようなコンピュータ・システムが実行するある種の機能は、双方向バスを利用する。代表的な双方向バス設計例は、双方向データ・バスの一端に各々配置した少なくとも2つのエンド・ドライバをもち、そしてデータ・バス上でのデータ信号のワイヤオア(wire-or)用に構成されている。このワイヤオア構成においては、いずれのエンド・ドライバも、データ・バス上にデータ信号を駆動することができる。これらエンド・ドライバが不活性のときには、データ・バスは、論理的ハイ状態すなわち“1”にプルアップされている。1つのエンド・ドライバが活性でしかもデータ・バスを駆動しているときには、データ・バスは、論理的ロー・レベルすなわち“0”にある。

【0004】

【発明が解決しようとする課題】

これらエンド・ドライバが不活性動作状態と活性動作状態との間で遷移するとき、スイッチング波信号が発生する。このスイッチング波信号を終わらせないと、このスイッチング波信号の反射が起き、これがデータ・バス上においてリンギングを生じさせる。このリンギングは、データ・バス上のデータ信号を乱す(unsettle)。この乱れたデータ・バスは、不安定なデータを発生する。上記の反射からのリンギングが実際にセトリングすると、データ・バス上のデータは、ある一定の論理に安定化する。データ・バス上のリンギングは、望ましくないが、それは、このデータ・バス上でデータ信号を転送する速度を低下させるからである。データ・バスがリンギングからセトリングするのを待つために浪費する時間は、別のデータ転送に使えることが最も好ましい。

【0005】

現在のデータ・バス設計は、終端抵抗器をデータ・バスの各々に取り付けて、スイッチング波信号を終了させるようにしている。この終端抵抗器は、スイッチング波信号を終了させることと、両エンド・ドライバが不活性のときにデータ・バス上に論理的ハイ状態を生成するためプルアップ信号を提供することとの2重の目的で作用している。エンド・ドライバは、通常、オープン・ドレイン・トランジスタまたはオープン・コレクタ・トランジスタであり、これは、トランジスタをCMOS(コンプリメンタリ・メタル・オキサイド・シリコン)プロセスまたはバイポーラ・プロセスのいずれを使って形成するかに依存する。スイッチング波信号を適切に終了させるには、終端抵抗器の抵抗性の値は、データ・バスの特性インピーダンスに設定する。データ・バスの特性インピーダンスに等しい値の終端抵抗器でデータ・バスの各端部を適切に終端すると、反射は起きない。

【0006】

例として、データ・バスが、2つのエンド・ドライバと、そしてそのデータ・バスの各端部に取り付けた2つの終端抵抗器をもつ場合について説明する。その1つのエンド・ドライバが活性となりその間他方のエンド・ドライバが不活性のとき、活性のエンド・ドライバから発生する負のスイッチング波信号(初期のハイ論理状態からロー論理状態への遷移)は、データ・バスの端部に進行し、そしてこれは、データ・バスのその端部にある終端抵抗器が反射なく終了させる。しかし、データ・バスの動作の間ににおいて、それらエンド

10

20

30

40

50

・ドライバでバック・ツー・バック (back to back) のスイッチングが起きる場合がある。バック・ツー・バックのスイッチングは、両エンド・ドライバが活性動作状態と不活性動作状態との間で同時にスイッチングする時に起きる。一方のエンド・ドライバが不活性状態から活性状態にスイッチするとき、負のスイッチング波信号 (ハイ論理状態からロー論理状態への遷移) が発生する。他方のエンド・ドライバが活性状態から不活性状態にスイッチするとき、正のスイッチング波信号 (ロー論理状態からハイ論理状態への遷移) が発生する。負スイッチング波信号は、データ・バスの端部の終端抵抗器に達したときに終了するが、正スイッチング波信号は、データ・バスの特性インピーダンス以外の抵抗値をもつ活性エンド・ドライバから、反射を発生する。この正スイッチング波信号のその反射からは、ワイヤオアのグリッチが生ずる。このワイヤオア・グリッチは、データ・バス上にリンクを生じさせ、そしてデータ・バス上における乱れたデータ信号を発生させる。データ・バス上におけるこのリンクがセトリングするのを待つために、時間が浪費される。

#### 【0007】

さらに、データ・バスは、しばしば、プリント回路ボード上のトレースとして形成され、そしてこれは、データ・バスをサブシステムの種々の回路構成部品ヘルートする。コンピュータのプリント回路ボードは、多数の回路構成部品を互いに結合するため数十のデータ・バスを備えることがある。また、このサブシステムの回路構成部品に対するデータ・バス・アクセスを提供するため、それらエンド・ドライバ間にオーブン・ドレイン構成またはオーブン・コレクタ構成で複数のミッド・ドライバが配置されている。終端抵抗器は、データ・バスの各端部に置くため、現在のデータ・バス設計では、プリント回路ボードにそれら抵抗器を外部から取り付けている。別の回路構成部品および回路に使うことができるプリント回路ボードのこの貴重な領域は、浪費されている。

#### 【0008】

したがって、データ・バスのセトリング時間を改善ししかもコンピュータ・システムのプリント回路ボードまたはその他のサブシステム上における空間を浪費する外部終端抵抗器の設置を取り除いた、データ・バスの作動の方法および装置を提供することが望ましい。

#### 【0009】

##### 【課題を解決するための手段】

本発明は、データ・バス上のデータ信号のセトリング時間の改善をもたらす、データ・バスの動的終端のための装置とデータ・バスを作動する方法とを提供する。この新規なデータ・バス設計は、データ・バス上のデータ信号を終了させる有効性を改善するため、動的終端ロジックをもつデータバス・ドライバに基づいている。したがって、本発明の1側面によれば、ワイヤオアのデータ転送のための双方向データ・バスは、前記データ・バスの第1の端部に結合しており、前記データ・バスの前記第1端部を第1の信号で駆動するように構成した第1のエンド・ドライバを備える。前記データ・バスの第2の端部に結合した第2のエンド・ドライバは、前記第1エンド・ドライバからの前記第1信号を動的に終了するように構成する。前記第2エンド・ドライバは、前記データ・バスの前記特性インピーダンスの抵抗性の値を備えたプルアップ・トランジスタと、前記データ・バスの前記特性インピーダンスの抵抗性の値を備えたプルダウン・トランジスタとを含む。これら終端抵抗器は、前記第2エンド・ドライバと一体化させ、そして前記第1信号を終了させるよう作用する。したがって、前記第2エンド・ドライバが活性か不活性の状態に無関係に、特性インピーダンスの抵抗性値を前記データ・バスに結合することにより、前記第1エンド・ドライバからの前記第1信号を終了させる。

#### 【0010】

本発明の別の側面によれば、前記第2エンド・ドライバは、前記データ・バスを第2の信号で駆動し、前記第1エンド・ドライバは、前記第2エンド・ドライバからの前記第2信号を動的に終了させる。前記第1エンド・ドライバは、前記データ・バスの前記特性インピーダンスの抵抗性の値を備えたプルアップ・トランジスタと、前記データ・バスの前記特性インピーダンスの抵抗性の値を備えたプルダウン・トランジスタとを含む。これら終

10

20

30

40

50

端抵抗器は、前記第1エンド・ドライバと一体化させる。したがって、前記第1エンド・ドライバが活性か不活性の状態に無関係に、特性インピーダンスの抵抗性値を前記データ・バスに結合することにより、前記第2エンド・ドライバからの前記第2信号を終了させる。

#### 【0011】

本発明の別の側面によれば、前記第1エンド・ドライバと前記第2エンド・ドライバとは、前記第1および第2の信号を同時に動的に終了させる。前記第1および第2のエンド・ドライバが連続した同期クロック・サイクル時にスイッチングするときに起きる前記第1および第2のエンド・ドライバのバック・ツー・バックのスイッチングの間、前記第2エンド・ドライバにおいて受けた第1信号と前記第1エンド・ドライバにおいて受けた第2信号とは、それらエンド・ドライバに達したときに、前記データ・バスの前記特性インピーダンスにより終了させる。各前記エンド・ドライバのスイッチング状態に無関係に、前記データ・バスの前記特性インピーダンスを適切な終端のため前記データ・バスに結合することにより反射を防止し、そしてしたがって、スイッチング波信号からの反射がセトリングするのを待つのではなく前記データ・バスをセトリングさせることにより、その他のデータ信号が前記データ・バスをより早く駆動するのを可能にする。

10

#### 【0012】

本発明のさらに別の側面によれば、前記データ・バスに結合した第1のミッド・ドライバは、前記データ・バスを第3の信号で駆動するように構成し、そして前記データ・バスに結合した第2のミッド・ドライバは、前記データ・バスを第4の信号で駆動するように構成する。前記第2エンド・ドライバは、前記第1ミッド・ドライバからの前記第4信号の反射を動的に終了させ、前記第1エンド・ドライバは、前記第2ミッド・ドライバからの前記第3信号の反射を動的に終了させる。したがって、前記ミッド・ドライバのバック・ツー・バックのスイッチングの間、前記ミッド・ドライバの不適切な終端から生じる反射は、前記データ・バスを進行しそして前記エンド・ドライバにて終了する。

20

#### 【0013】

改善したデータ・バスを作動する装置および方法は、動的終端ロジックが提供して、改善したデータバス・セトリング時間のため前記データ・バス上のデータ信号を終了させる。前記データ・バスのための前記終端抵抗器を前記ドライバと一体化させることにより、前記終端抵抗器をコンピュータ・システムのプリント回路ボード等に対し外部的に配置する必要を取り除く。この外部抵抗器の除去からの空間節約は、プリント回路ボード上に別の回路構成部品および回路のための空間をもつともたらし、これはさらに、より小さなパッケージでより多くの機能の一体化を可能にする。さらにまた、前記データ・バスのセトリング時間を短縮することにより、増大したデータ速度のデータ・バス設計をもたらす。コンピュータ・サブシステムのデータ速度を上昇させると、システム全体がデータを処理する速度も増大する。したがって、動的終端ロジックは、プリント回路ボード上の利用可能な空間を増すだけでなく、データ転送を実行するためのシステムのスループットを増大させることになる。

30

#### 【0014】

本発明のその他の側面並びに利点については、図面、以下の詳細な説明および特許請求の範囲を検討すれば、理解することができる。

40

#### 【0015】

##### 【発明の実施の形態】

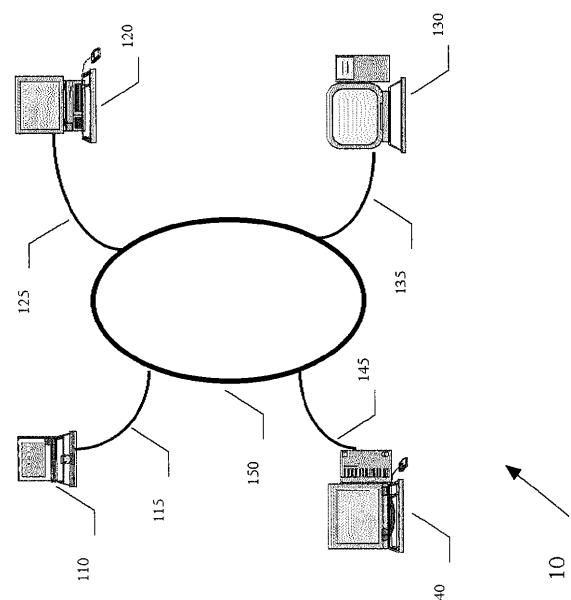

本発明について、図面を参照して説明するが、図1は、コンピュータ・ネットワーク10のシステムを全体的に示している。尚、同一の番号により、本説明を通して同じ要素を表す。コンピュータ・ネットワーク10は、クライアント110、クライアント120、クライアント130、クライアント140、およびインターネット150を含んでいる。インターネット150は、クライアント110, 120, 130および140を結合してクライアント間の通信を可能にする。本発明によれば、インターネット150は、TCP/IP(伝送制御プロトコル/インターネット・プロトコル)を提供する。インターネット

50

およびローカルエリアネットワークを含むTCP/IPを運用するその他の代表的セグメントも、適當である。

【0016】

本発明による双方向データ・バス115, 125, 135および145は、データ・バス性能向上のため動的終端ロジックを提供する。図1においては、データ・バス115, 125, 135および145は、クライアント110, 120, 130および140とインターネット150との間のネットワーク接続を提供する。データ・バス115は、クライアント110がインターネット150にアクセスするためのネットワーク接続を提供する。データ・バス125は、クライアント120がインターネット150にアクセスするためのネットワーク接続を提供する。データ・バス135は、クライアント130がインターネット150にアクセスするためのネットワーク接続を提供する。データ・バス145は、クライアント140がインターネット150にアクセスするためのネットワーク接続を提供する。クライアント110, 120, 130および140は、ロジック回路を含み、これは、インターネット150との間でのデータ転送のための一連の詳細に識別された動作を実行するようにプログラムしてある。データ・バス115, 125, 135および145は、これらデータ・バスの動的終端ロジックを提供するロジック回路を含む。したがって、クライアント110とクライアント120との間のデータ転送は、データ・バス115を介し、インターネット150へ、データ・バス125へ、そしてクライアント120へと起きる。同様に、クライアント120とクライアント110との間のデータ転送は、データ・バス125を介し、インターネット150へ、データ・バス115へ、そしてクライアント110へと起きる。

【0017】

それらクライアント間のデータ転送のその他の変形例には、データ転送を容易にするため2つのクライアント間にデータ・バスを結合することが含まれる。より単純なコンピュータ・ネットワークは、2つのクライアント間ににおいて、動的に終端したデータ・バスを介してデータ転送を提供するものである。内部的なデータ転送もまた1つのクライアント内で起きるため、クライアント110, 120, 130および140は、内部データ転送を容易にするため、本発明による動的に終端したデータ・バスを備える。したがって、動的に終端したロジックをもつデータ・バスは、コンピュータ・ネットワーク10全体にわたって含まれる。

【0018】

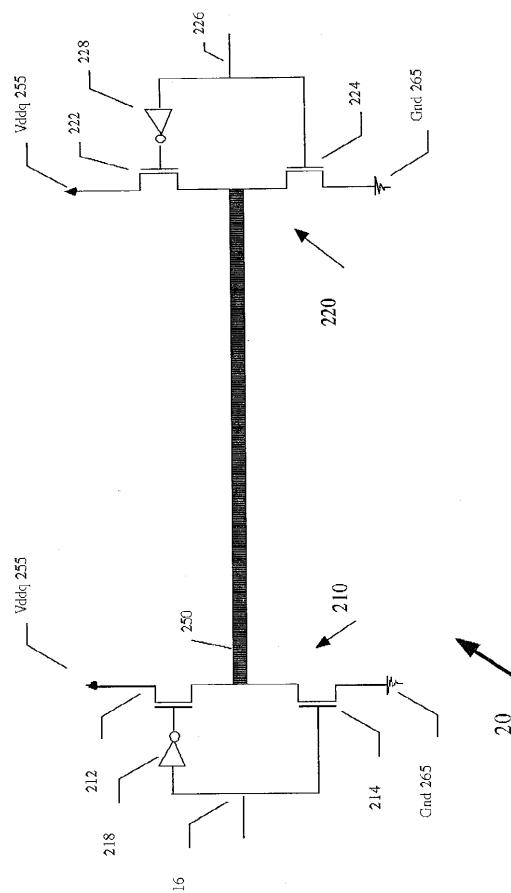

図2は、本発明による動的終端ロジック・データバス20の回路図を示している。この動的終端ロジック・データバス20は、エンド・ドライバ210、エンド・ドライバ220、データ・バス250を備え、これらは、ワイヤオア構成で設定している。エンド・ドライバ210は、データ・バス250に結合し、そしてデータ・バス250に対し駆動出力を与える。同様に、エンド・ドライバ220は、データ・バス250に結合し、そしてデータ・バス250に対し駆動出力を与える。エンド・ドライバ210, 220からのこれら駆動出力は、Vddq電圧と1/2Vddq電圧との間のスイッチング波を与える。Vddq電圧と1/2Vddq電圧とは、それぞれ、データ・バス250上における、ハイ論理状態すなわち“1”と、ロー論理状態すなわち“0”を表している。本発明ではMOSトランジスタを示しているが、トランジスタのその他の変形例も使用することができる。さらに、上記ドライバはスイッチング機能を実行するため、スイッチング機能を容易にするその他のデバイスも、これらトランジスタの代わりにすることができる。

【0019】

エンド・ドライバ210は、MOS(メタル・オキサイド・シリコン)トランジスタ212と、MOSトランジスタ214と、制御入力216と、インバータ218とを含んでいる。トランジスタ212のドレインは、Vddq255に結合し、トランジスタ212のソースは、データ・バス250とトランジスタ214のドレインとに結合している。トランジスタ214のソースは、Gnd265に結合している。インバータ218の出力は、トランジスタ212のゲートに結合している。インバータ218の入力とトランジスタ2

14のゲートに結合した制御入力216は、エンド・ドライバ210を活性化する制御信号を与える。当業者には理解されるように、トランジスタ212とトランジスタ214とはCMOS(コンプリメンタリMOS)で実装して、トランジスタ212とインバータ218とがpチャンネル・トランジスタとなりかつトランジスタ214がnチャンネル・トランジスタとなるようにすることができる。

【0020】

エンド・ドライバ220は、MOSトランジスタ222と、MOSトランジスタ224と、制御入力226と、インバータ228とを含んでいる。トランジスタ222のドレインは、Vddq255に結合し、トランジスタ222のソースは、データ・バス250とトランジスタ224のドレインとに結合している。トランジスタ224のソースは、Gnd265に結合している。インバータ228の出力は、トランジスタ222のゲートに結合している。インバータ228の入力とトランジスタ224のゲートに結合した制御入力226は、エンド・ドライバ220を活性化する制御信号を与える。もちろん、当業者は理解するように、CMOS実装においては、トランジスタ222とインバータ228とがpチャンネル・トランジスタとなりかつトランジスタ224がnチャンネル・トランジスタとなる。

10

【0021】

ワイヤオア・グリッチを防止するには、エンド・ドライバ210と220のトランジスタは、データ・バス250の特性インピーダンスに設定した抵抗値を提供するように形成する。したがって、各エンド・ドライバのそれらトランジスタが活性化したとき、活性化したトランジスタの抵抗値は、データ・バス250の特性インピーダンスと一致する。エンド・ドライバで受けるスイッチング信号波は、データ・バスのこの特性インピーダンスで終了させる。本発明では、データ・バス250の特性インピーダンスを50(オーム)とし、そしてこれにより、エンド・ドライバの活性化したトランジスタの抵抗値は同じく50に設定する。

20

【0022】

エンド・ドライバのバック・ツー・バックのスイッチングの場合においては、動的終端口ジック・データバス20は、エンド・ドライバからのスイッチング信号波を終了させて、データ・バス250への反射の防止を行う。初めに、エンド・ドライバ210は、最初は不活性である。制御入力216は、トランジスタ212をターンオンしトランジスタ214をターンオフする入力を与え、そしてこのことはVddq255をトランジスタ212を介してデータ・バス250に結合する。エンド・ドライバ220は、初期には活性である。制御入力226は、トランジスタ222をターンオフしトランジスタ224をターンオンする入力を与え、そしてこのことはデータ・バス250をトランジスタ224を介してGnd265に結合する。したがって、データ・バス250の初期状態は、ロー論理状態に対応する1/2Vddq電圧である。バック・ツー・バックのスイッチングが起きるとき、制御入力216は、エンド・ドライバ210を活性化する入力を与え、また制御入力226は、エンド・ドライバ220を不活性化する入力を与える。エンド・ドライバ210が活性化すると、トランジスタ212は、ターンオフしかつトランジスタ214がターンオンして、1/2Vddq電圧からGnd電圧への負のスイッチング波信号を発生する。この同じ瞬間あたりにおいて、エンド・ドライバ220が不活性化すると、トランジスタ222は、ターンオンしかつトランジスタ224がターンオフして、1/2Vddq電圧からVddq電圧への正のスイッチング波信号を発生する。

30

【0023】

各スイッチング波信号がデータ・バス250の長さを進行すると、各スイッチング波信号は、データ・バス250の端部においてエンド・ドライバにより終わる。エンド・ドライバ220は、エンド・ドライバ210からの負スイッチング波信号を受け、そしてこの負スイッチング波信号を終了させるが、それは、エンド・ドライバ220の活性化されたトランジスタ222がデータ・バス250の特性インピーダンスと一致した抵抗値をもっているからである。同様に、エンド・ドライバ210は、エンド・ドライバ220からの正

40

50

スイッチング波信号を受け、そしてこの正スイッチング波信号を終了させるが、それは、エンド・ドライバ210の活性化されたトランジスタ214がデータ・バス250の特性インピーダンスと一致した抵抗値をもっているからである。これらエンド・ドライバのこのバック・ツー・バックのスイッチングからは、反射はまったく起きない。データ・バス250は、それらスイッチング波信号がエンド・ドライバに達したときにセトリングする。データ・バス250のセトリング時間は、データ・バス250上で反射が全くないため、ゼロにまで最小化できる。データ・バス250のセトリング時間を最小にすると、データ・バス転送速度の上昇をもたらす。したがって、エンド・ドライバ210とエンド・ドライバ220は、エンド・ドライバが活性化されているかあるいは不活性化されているかに拘わらず、データ・バス250上のスイッチング波信号を動的に終了させる動的終端ロジックを備える。

【0024】

図3は、図2の動的終端ロジック・データバス20の等価回路30の回路図を示している。等価回路30は、エンド・ドライバ210, 220とデータ・バス250の等価回路を含んでいる。エンド・ドライバ210の等価回路は、スイッチ310と、抵抗器212Rと、そして抵抗器214Rとを含んでいる。抵抗器212Rは、Vddq255とスイッチ310との間に結合している。抵抗器214Rは、スイッチ310とGnd265との間に結合している。スイッチ310は、データ・バス250と抵抗器212Rとの間またはデータ・バス250と抵抗器214Rとの間でスイッチ可能である。

【0025】

エンド・ドライバ220の等価回路は、スイッチ320と、抵抗器222Rと、そして抵抗器224Rとを含んでいる。抵抗器222Rは、Vddq255とスイッチ320との間に結合している。抵抗器224Rは、スイッチ320とGnd265との間に結合している。スイッチ320は、データ・バス250と抵抗器222Rとの間またはデータ・バス250と抵抗器224Rとの間でスイッチ可能である。

【0026】

動作においては、スイッチ310は、抵抗器212Rと214Rとの間でスイッチ可能であり、そしてスイッチ320は、抵抗器222Rと224Rとの間でスイッチ可能である。これらスイッチ310, 320の初期位置に依存して、正スイッチング波信号または負スイッチング波信号のいずれかが、スイッチ310またはスイッチ320が1つの位置から別の位置へとスイッチしたときに発生する。スイッチング波信号がデータ・バス250を進行するとき、これを受けるエンド・ドライバは、その受けたスイッチング波信号を、そのスイッチング位置に無関係にデータ・バス250の特性インピーダンスと一致する抵抗値によって終了させる。言い換えれば、エンド・ドライバ210および220は、データ・バス250に対し動的終端ロジックを提供するが、その理由は、エンド・ドライバ210および220のスイッチング位置に独立に、抵抗器212R, 214R, 222R, 224Rの各々が、データ・バス250の特性インピーダンスに対応する抵抗値を与えて、受けたスイッチング波信号を適切に終了させるからである。本発明によれば、データ・バス250の特性インピーダンスと抵抗器212R, 214R, 222R, 224Rの抵抗値とは、各々50Ωである。

【0027】

図4は、ミッド・ドライバ410をもつ動的終端ロジック・データバス20の回路図を示している。ミッド・ドライバ410は、データ・バス250に対し2つより多いドライバをもつ多数負荷構成を提供する。データ・バス250の設計に依存して、1つまたはそれ以上のミッド・ドライバ41をデータ・バス250に結合することができる。ミッド・ドライバ410のインピーダンスは、データ・バス250の特性インピーダンスの1/2に等しい。本実施例では、ミッド・ドライバ410は、オーブンドレイン・トランジスタ412から成っている。このトランジスタ412のドレインは、データ・バス250に結合し、そしてトランジスタ412のソースは、Gnd465に結合している。トランジスタ412のゲートに結合する制御信号414は、ミッド・ドライバ410を活性化し、そし

10

20

30

40

50

てデータ・バス 250 を Gnd 465 にトランジスタ 412 を介して結合するスイッチング機能を提供している。

【0028】

本実施例においては、ミッド・ドライバ 410 のトランジスタ 412 の抵抗値は、25 に構成し、Vddq は 1.5 ボルトに設定している。このミッド・ドライバ 410 を活性化すると、エンド・ドライバ 210 および 220 が不活性化されているときには、データ・バス 250 を駆動しておよそ 0.75 ボルトにする。不活性化されたドライバ 210 および 220 のトランジスタ 212 および 222 は各々 50 Ω に構成ししかも並列に配置しているので、その結果の等価回路は、分圧器を提供してデータ・バス 250 を 0.75 ボルトに設定する。

10

【0029】

初期において、ミッド・ドライバ 410 とエンド・ドライバ 210 および 220 は不活性であるとき、データ・バス 250 は Vddq 255 の電圧にある。ミッド・ドライバ 410 が活性となってデータ・バス 250 を Gnd 465 にトランジスタ 412 を介して接続すると、発生する負スイッチング波信号がデータ・バス 250 を進行し、そしてこれを受けるエンド・ドライバ 210 および 220 にて終了する。データ・バス 250 は、ロー論理状態の 1/2 Vddq 電圧にてセトリングし、したがって負スイッチング波信号からの反射は全く生じない。

【0030】

多数のミッド・ドライバ 410 をデータ・バス 250 上に置いたときには、2つのミッド・ドライバ 410 がバック・ツー・バックでスイッチする場合が起きる。互いに対向するミッド・ドライバ 412 のバック・ツー・バックのスイッチングから発生するスイッチング波信号は、ワイヤオア・グリッチを発生する。このスイッチング波信号は、各ミッド・ドライバ 412 に反射により戻るが、それは、ミッド・ドライバ 412 がそれらスイッチング波信号を適切に終了させないからである。しかし、これら反射されたスイッチング波信号がエンド・ドライバ 210 および 220 に達すると、エンド・ドライバ 210 および 220 が、それら反射されたスイッチング波信号を終了させて、データ・バス 250 をセトリングさせる。

20

【0031】

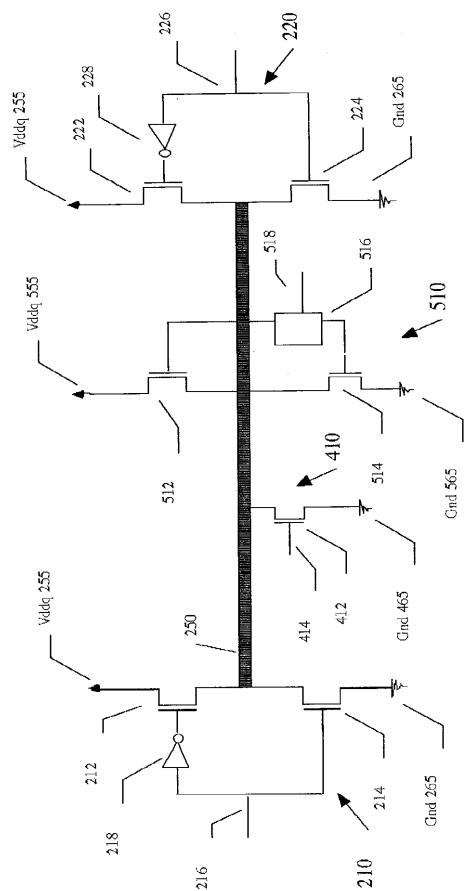

図 5 は、ミッド・ドライバ 510 を備えた代替実施例をもつ動的終端ロジック・データバス 20 の回路図を示している。ミッド・ドライバ 510 は、2つより多いドライバをもつデータ・バス 250 に対し多数負荷構成を提供する。データ・バス 250 の設計に依存して、1つまたはそれ以上のミッド・ドライバ 510 をデータ・バス 250 に結合することができる。このミッド・ドライバ 510 は、トランジスタ 512 と、トランジスタ 514 と、そして制御ロジック 516 とを備えている。トランジスタ 512 のドレインは、Vddq 555 に結合し、そしてトランジスタ 512 のソースは、データ・バス 250 とトランジスタ 514 のドレインに結合している。トランジスタ 514 のソースは、Gnd 565 に結合している。トランジスタ 512 および 514 のゲートは、制御ロジック 516 に結合している。

30

【0032】

制御ロジック 516 は、制御信号 518 を受けて、ミッド・ドライバ 510 の制御を行う。ミッド・ドライバ 510 は、3つの動作モードを備えている。すなわち、1) ミッド・ドライバ 510 が受信モードにあるときの3状態モードと、2) トランジスタ 512 が活性でかつトランジスタ 514 が不活性であるときの Vddq 電圧駆動モードと、3) トランジスタ 512 が不活性でかつトランジスタ 514 が活性であるときの 1/2 Vddq 電圧駆動モード(論理的ロー)と、である。本実施例においては、トランジスタ 512 は、活性のときには、Vddq 555 からデータ・バス 250 への 50 Ω の抵抗値を提供し、そしてトランジスタ 514 は、活性のときには、データ・バス 250 から Gnd 565 への 25 Ω の抵抗値を提供する。

40

【0033】

50

**【発明の効果】**

以上の詳細な説明により、本発明による双方向データ・バスの動的終端ロジックのための装置および方法の実施例について記述したが、上記の説明は、例示に過ぎず、開示した発明を限定するものでないことは、理解されるべきである。明らかなように、当業者には、多くの変更、変形が明白である。したがって、双方向データ・バスの動的終端ロジックのための装置および方法を提供した。この動的終端ロジックは、データ・バスのセトリング時間を減少させ、またデータ・バス性能の上昇をもたらす。ある種の場合には、このデータバス・セトリング時間は、ゼロにまで低減できる。この動的終端ロジックがデータ・バスをセトリングさせると、そのデータ・バスに結合したその他のデータバス・ドライバは、それらの信号によってデータ・バスを駆動することができるようになる。データ・バスが各デバイスを互いに結合してそれらデバイスが1つのユニットとして動作すると仮定すると、データバス・スループットの上昇が、システムの性能をしばしば制限するボトルネックを取り除くことになる。そのシステムは、マイクロチップ・レベル、構成部品レベル、システム・レベル、あるいはネットワーク・レベルのものとすることができます。したがって、本動的終端ロジックは、電気的通信信号の情報転送のためにデータ・バスに頼ったシステムの性能を増大させることができる。10

**【図面の簡単な説明】**

【図1】本発明による、データ・バスの動的終端ロジックをもつコンピュータ・ネットワークのシステム・レベルのブロック図。

【図2】本発明によるエンド・ドライバをもつデータ・バスの回路図。20

【図3】エンド・ドライバをもつデータ・バスの等価回路図。

【図4】ミッド・ドライバをもつデータ・バスの回路図。

【図5】ミッド・ドライバの代替実施例をもつデータ・バスの回路図。

**【符号の説明】**

10 : コンピュータ・ネットワーク

110, 120, 130, 140 : クライアント

150 : インターネット

115, 125, 135, 145 : 双方向データ・バス

210, 220 : エンド・ドライバ

250 : データ・バス

410, 510 : ミッド・ドライバ

30

【図1】

【図2】

【図5】

---

フロントページの続き

(74)代理人 100075236

弁理士 栗田 忠彦

(74)代理人 100075270

弁理士 小林 泰

(72)発明者 レオ・ユアン

アメリカ合衆国カリフォルニア州 94024, ロス・アルトス, カントリー・クラブ・ドライヴ

1497

(72)発明者 チャイム・アミアー

アメリカ合衆国カリフォルニア州 94086, サニーベイル, ヴィセント・ドライヴ 1267

, ナンバー 139

(72)発明者 デレク・シュンタオ・トゥサイ

アメリカ合衆国カリフォルニア州 95131, サンホセ, ガーデン・ビング・サークル 1991

(72)発明者 ドリュー・ジョージ・ダブラー

アメリカ合衆国カリフォルニア州 95129, サンホセ, ブルック・グレン・ドライヴ 1442

(72)発明者 ジョナサン・エリック・スター

アメリカ合衆国カリフォルニア州 95014, カッパーテイー・ノ, スティーブンス・クリーク・ブ

ールヴァード 20350, アパートメント 106

(72)発明者 トラン・サン・ヌグイエン

アメリカ合衆国カリフォルニア州 95132, サンノゼ, ビサニ・アヴェニュー 1786

審査官 安藤 一道

(56)参考文献 特開平07-202863 (JP, A)

特開平09-181596 (JP, A)

特開平09-083411 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H04L 29/08