(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3753845号

(P3753845)

(45) 発行日 平成18年3月8日(2006.3.8)

(24) 登録日 平成17年12月22日(2005.12.22)

(51) Int.C1.

F 1

H01L 29/786 (2006.01)

H01L 21/336 (2006.01)H01L 29/78 627G

H01L 29/78 612B

請求項の数 6 (全 20 頁)

(21) 出願番号 特願平9-262821

(22) 出願日 平成9年9月10日(1997.9.10)

(65) 公開番号 特開平11-87732

(43) 公開日 平成11年3月30日(1999.3.30)

審査請求日 平成16年8月19日(2004.8.19)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 張 宏勇

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 福永 健司

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 松田 成正

最終頁に続く

(54) 【発明の名称】半導体装置の作製方法

## (57) 【特許請求の範囲】

## 【請求項1】

絶縁表面を有する基板上に非晶質半導体膜を形成し、

前記非晶質半導体膜上にマスク絶縁膜を形成し、

前記マスク絶縁膜にパターニングを施して、第1の開口部を形成し、

前記第1の開口部において露出した前記非晶質半導体膜を除去し、

前記マスク絶縁膜にパターニングを施して、第2の開口部を形成し、

前記非晶質半導体膜の前記第2の開口部において露出した領域に、前記非晶質半導体膜の結晶化を助長する触媒元素を保持または添加し、

加熱処理により前記非晶質半導体膜を結晶化して、前記触媒元素が保持または添加された前記領域から結晶成長した第1の領域と、自然核発生により結晶成長した第2の領域とを形成し、

前記第1の領域及び前記第2の領域にそれぞれパターニングを施し、前記第1の領域から駆動回路の薄膜トランジスタの活性層を形成し、前記第2の領域から画素マトリクス回路の薄膜トランジスタの活性層を形成することを特徴とする半導体装置の作製方法。

## 【請求項2】

絶縁表面を有する基板上に非晶質半導体膜を形成し、

前記非晶質半導体膜にパターニングを施して、前記非晶質半導体膜に第1の開口部を形成し、

前記非晶質半導体膜上にマスク絶縁膜を形成し、

10

20

前記マスク絶縁膜にパターニングを施して、第2の開口部を形成し、

前記非晶質半導体膜の前記第2の開口部において露出した領域に、前記非晶質半導体膜の結晶化を助長する触媒元素を保持または添加し、

加熱処理により前記非晶質半導体膜を結晶化して、前記触媒元素が保持または添加された前記領域から結晶成長した第1の領域と、自然核発生により結晶成長した第2の領域とを形成し、

前記第1の領域及び前記第2の領域にそれぞれパターニングを施し、前記第1の領域から駆動回路の薄膜トランジスタの活性層を形成し、前記第2の領域から画素マトリクス回路の薄膜トランジスタの活性層を形成することを特徴とする半導体装置の作製方法。

## 【請求項3】

10

絶縁表面を有する基板上に非晶質半導体膜を形成し、

前記非晶質半導体膜上にマスク絶縁膜を形成し、

前記マスク絶縁膜にパターニングを施して、第1の開口部を形成し、

前記第1の開口部において露出した前記非晶質半導体膜を除去し、

前記マスク絶縁膜にパターニングを施して、第2の開口部を形成し、

前記非晶質半導体膜の前記第2の開口部において露出した領域に、前記非晶質半導体膜の結晶化を助長する触媒元素を保持または添加し、

加熱処理により前記非晶質半導体膜を結晶化して、前記触媒元素が保持または添加された前記領域から結晶成長した第1の領域と、自然核発生により結晶成長した第2の領域とを形成し、

20

前記第1の領域において前記触媒元素を低減または除去させるゲッタリングを行い、

前記第1の領域及び前記第2の領域にそれぞれパターニングを施し、前記第1の領域から駆動回路の薄膜トランジスタの活性層を形成し、前記第2の領域から画素マトリクス回路の薄膜トランジスタの活性層を形成することを特徴とする半導体装置の作製方法。

## 【請求項4】

絶縁表面を有する基板上に非晶質半導体膜を形成し、

前記非晶質半導体膜にパターニングを施して、前記非晶質半導体膜に第1の開口部を形成し、

前記非晶質半導体膜上にマスク絶縁膜を形成し、

前記マスク絶縁膜にパターニングを施して、第2の開口部を形成し、

前記非晶質半導体膜の前記第2の開口部において露出した領域に、前記非晶質半導体膜の結晶化を助長する触媒元素を保持または添加し、

加熱処理により前記非晶質半導体膜を結晶化して、前記触媒元素が保持または添加された前記領域から結晶成長した第1の領域と、自然核発生により結晶成長した第2の領域とを形成し、

30

前記第1の領域において前記触媒元素を低減または除去させるゲッタリングを行い、

前記第1の領域及び前記第2の領域にそれぞれパターニングを施し、前記第1の領域から駆動回路の薄膜トランジスタの活性層を形成し、前記第2の領域から画素マトリクス回路の薄膜トランジスタの活性層を形成することを特徴とする半導体装置の作製方法。

## 【請求項5】

40

請求項1乃至請求項4のいずれか一項において、

前記第1の開口部及び前記第2の開口部はスリット状に形成されていることを特徴とする半導体装置の作製方法。

## 【請求項6】

請求項1乃至請求項5のいずれか一項において、

前記第1の開口部は幅1~5μmのスリット状に形成され、

前記第2の開口部は幅5~20μmのスリット状に形成されることを特徴とする半導体装置の作製方法。

## 【発明の詳細な説明】

## 【0001】

50

**【発明が属する技術分野】**

本願発明は、半導体薄膜を利用した薄膜トランジスタ（TFT）を構成に含む半導体装置およびその作製方法に関する。

**【0002】**

なお、本明細書中において「半導体装置」とは、半導体を利用して機能しうる装置全てを含む。従って、本明細書中に記載されたTFT、半導体素子、電気光学装置及び電子機器は全て半導体装置の範疇に含まれる。

**【0003】****【従来の技術】**

近年、高温ポリシリコン及び低温ポリシリコンを用いた周辺回路一体型のアクティブマトリクス型液晶パネルの商品化が相次いでいる。現状では液晶駆動回路としてシフトレジスタやアナログスイッチ等が内蔵されているが、イメージセンサ、メモリ、MPU、ASIC等を内蔵したインテリジェントパネルの開発が急速に進められている。 10

**【0004】**

この様な駆動回路さらには論理回路をも内蔵するためには個々のTFT特性、特に動作速度を高速なものとし、高速動作の可能な半導体回路を構成する必要がある。そして、そのためには非常に結晶性の高い半導体薄膜を実現することが不可欠である。

**【0005】**

そこで本発明者らは、高い結晶性を有する半導体薄膜を形成する技術として特開平8-78329号公報記載の技術を開示している。同公報記載の技術は、非晶質半導体薄膜に対して選択的に結晶化を助長する触媒元素を導入し、その領域を起点とした結晶成長を行わせる技術が開示されている。 20

**【0006】**

本発明者らは、触媒元素の添加領域を中心として広がる結晶領域を横成長領域と呼び、単に触媒元素を添加して結晶化させた領域とは明確に区別している。この横成長領域は、200 μm程度の長さにまで結晶成長させることができる。 20

**【0007】**

また、横成長領域の特徴は、幅数百nmの棒状または偏平棒状結晶（内部はほぼ単結晶と見なせる結晶性を有する）が、マクロ的には互いに概略平行に並び、特定の方向性をもって結晶成長している点にある。即ち、単結晶ライクな結晶粒が規則性をもって配列しているので非常に高い結晶性が得られる。 30

**【0008】****【発明に至るまでの過程】**

前述の様なアクティブマトリクス型液晶パネル及びインテリジェントパネルにおいて、メモリの記憶セル、液晶パネルの表示セル、イメージセンサの受光セルなどは同一パターンの繰り返しで構成されたマトリクス回路で構成される。これらマトリクス回路の共通の特徴としては、単一セルが小さく、占有面積が大きいことが挙げられる。また、マトリクスの配置（セル間隔、アスペクト比等）は設計事項の制約により自由に調節することができない。 40

**【0009】**

そのため、特開平8-78329号公報記載の技術を利用するにあたって不具合が生じてしまう。それは触媒元素の導入領域が10~20 μmと大きく、結晶化後はその領域を除去しなくてはならないという理由から生じる。

**【0010】**

例えば液晶パネルの表示セルを例にとると、セルピッチ（画素間距離）が30 μm以下と狭くなれば、表示セルのマトリクス回路内に触媒元素の導入領域を形成することは実質的に不可能である。また、200 μm程度に成長させた横成長領域でもマトリクス回路全体をカバーすることはできない。

**【0011】**

以上の様に、マトリクス回路内では触媒元素の導入領域を形成することができず、特開平 50

8-78329 号公報記載の技術を利用することはできない。ところが、幸いにもマトリクス回路を構成する表示セル、記憶セル、受光セル等に配置される TFT はさほど動作速度を要求されない。

#### 【0012】

そのため触媒元素を利用しないで結晶化させたポリシリコン膜、場合によってアモルファスシリコン膜でも十分な機能を得られる。また、触媒元素は結晶化には有効であるが、結晶化後は TFT 特性のバラツキの原因となる恐れがあるので、マトリクス回路の様に極力バラツキを排除すべき回路にとって触媒元素を利用しないで済む利点は大きい。

#### 【0013】

従って、駆動回路や論理回路等の様に高い動作速度を必要とする回路を配置する領域には触媒元素を利用した半導体薄膜を形成し、表示セル等の様にさほど高い動作速度を必要としない回路を配置する領域には触媒元素を利用しないで結晶化させた半導体薄膜を形成する様な構成が望ましいと言える。

#### 【0014】

ところが、半導体回路の集積度は益々向上しているため触媒元素を利用する領域と利用しない領域とが非常に近接して形成されることが多い。従って、100~200  $\mu\text{m}$  程度にまで成長する横成長領域の先端部分が、触媒元素を利用しない領域に入り込んでしまう様な事態が起こりうる。

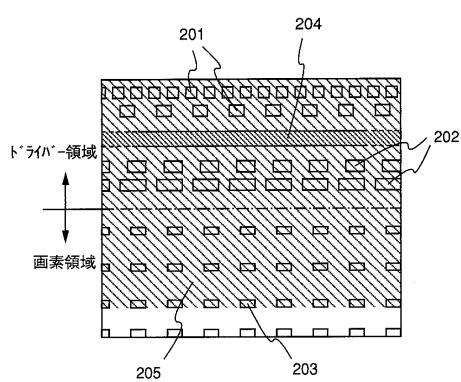

#### 【0015】

この様子を図 2 を用いて説明する。図 2 は熱結晶化工程を終え、横成長領域を形成した時点での様子を表している。図 2 において、201、202 はドライバー回路を構成する TFT (ドライバー TFT) の活性層となる領域、203 は画素マトリクス回路を構成する TFT (画素 TFT) の活性層となる領域、204 は触媒元素の導入領域、205 で示される斜線部は横成長領域である。

#### 【0016】

図 2 に示す様に、ドライバー TFT の活性層となる領域 201、202 のみが含まれる様に横成長領域を形成するつもりであっても、横成長領域 205 の成長距離が長過ぎてしまい、画素 TFT の活性層となる領域 203 の一部までもが横成長領域 205 に含まれてしまっている。

#### 【0017】

この場合、横成長領域に含まれる領域と含まれない領域とでは結晶性の異なる活性層が形成される。即ち、マトリクス回路を構成する領域（触媒元素を使用しない領域）内で活性層の結晶性の均一性が崩れ、バラツキを生じる。

#### 【0018】

また、横成長領域の先端部分が触媒元素を利用しない領域に入り込まない様にマージンをとってしまうと、半導体回路の集積度を低下させることになり好ましいものではない。

#### 【0019】

##### 【発明が解決しようとする課題】

本願発明は以上の様な問題点を鑑みて成された技術であり、横成長領域の成長距離を制御するための技術を提供することを課題とする。そして、同一基板上において、触媒元素を利用する領域と利用しない領域とを高い集積度で形成するための技術を提供することを課題とする。

#### 【0020】

##### 【課題を解決するための手段】

本明細書で開示する発明の構成は、

画素マトリクス回路と当該画素マトリクス回路を駆動する駆動回路とを同一基板上に一体形成した構成を含む半導体装置であって、

前記画素マトリクス回路及び前記駆動回路は複数の TFT から構成され、

前記駆動回路を構成する複数の TFT の活性層のみに当該活性層の結晶化を助長する触媒元素が含まれていることを特徴とする。

10

20

30

40

50

**【0021】**

また、上記構成の半導体装置を実現するためには、

絶縁表面を有する基板上に非晶質半導体膜を形成する工程と、

前記非晶質半導体膜上にマスク絶縁膜を形成する工程と、

前記マスク絶縁膜にパターニングを施し、第1の開口部を形成する工程と、

前記第1の開口部において露出した前記非晶質半導体膜を除去する工程と、

前記マスク絶縁膜に再度のパターニングを施し、第2の開口部を形成する工程と、

前記第2の開口部において露出した前記非晶質半導体膜に当該非晶質半導体膜の結晶化を助長する触媒元素を保持または添加する工程と、

加熱処理により前記非晶質半導体膜の一部を結晶化する工程と、

を含むことを特徴とする半導体装置の作製方法が必要である。

10

**【0022】**

また、他の発明の構成は、

絶縁表面を有する基板上に非晶質半導体膜を形成する工程と、

前記非晶質半導体膜にパターニングを施し、第1の開口部を形成する工程と、

前記第1の開口部において露出した前記非晶質半導体膜を除去する工程と、

前記非晶質半導体膜上にマスク絶縁膜を形成する工程と、

前記マスク絶縁膜にパターニングを施し、第2の開口部を形成する工程と、

前記第2の開口部において露出した前記非晶質半導体膜に当該非晶質半導体膜の結晶化を助長する触媒元素を保持または添加する工程と、

加熱処理により前記非晶質半導体膜の一部を結晶化する工程と、

を含むことを特徴とする。

20

**【0023】**

また、他の発明の構成は、

絶縁表面を有する基板上に非晶質半導体膜を形成する工程と、

前記非晶質半導体膜上にマスク絶縁膜を形成する工程と、

前記マスク絶縁膜にパターニングを施し、第1の開口部を形成する工程と、

前記第1の開口部において露出した前記非晶質半導体膜に不純物元素を添加する工程と、

前記マスク絶縁膜に再度のパターニングを施し、第2の開口部を形成する工程と、

前記第2の開口部において露出した前記非晶質半導体膜に当該非晶質半導体膜の結晶化を助長する触媒元素を保持または添加する工程と、

加熱処理により前記非晶質半導体膜の一部を結晶化する工程と、

を含むことを特徴とする。

30

**【0024】****【発明の実施の形態】**

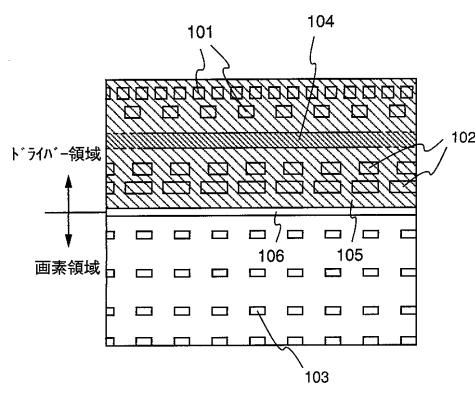

本願発明の実施の形態を図1を用いて説明する。本願発明ではドライバー領域（駆動回路や論理回路を構成する領域）と画素領域（マトリクス回路を構成する領域）との境界にあたる部分に、横成長領域の成長を強制的に制止する領域を設けることに特徴がある。

**【0025】**

図1において、101、102はドライバーTFTの活性層となる領域、103は画素TFTの活性層となる領域、104は触媒元素の導入領域である。

40

**【0026】**

非晶質半導体膜の結晶化工程では、触媒元素の導入領域104から基板と概略平行に棒状または偏平棒状結晶が成長し、横成長領域105を形成する。この時、横成長領域の成長方向の前方、即ち、ドライバー領域と画素領域との境界部分に横成長領域のストッパー領域106を設ける点が本願発明の特徴である。

**【0027】**

このストッパー領域106は、強制的に棒状結晶の成長を終了させるための領域であり、以下の様な方法で形成される。

（1） 非晶質半導体膜そのものを除去し、結晶成長の連続性を妨げる。

50

(2) 意図的に高濃度な不純物領域を形成して結晶成長の連続性を妨げる。

【0028】

この様な構成とすることで、横成長領域105の進行を強制的に制止することが可能となる。そのため、横成長領域105の画素領域内への進行が防がれ、画素領域内における結晶性の均一性を確保することができる。

【0029】

なお、本願発明は横成長領域を利用する領域と利用しない領域との境界を明確にすることを目的としている。従って、画素領域とドライバー領域とを区別するといった特定部分への適用に限定されず、その様な区別が必要となる全ての回路部分に対しても本願発明を適用することは可能である。

10

【0030】

【実施例】

〔実施例1〕

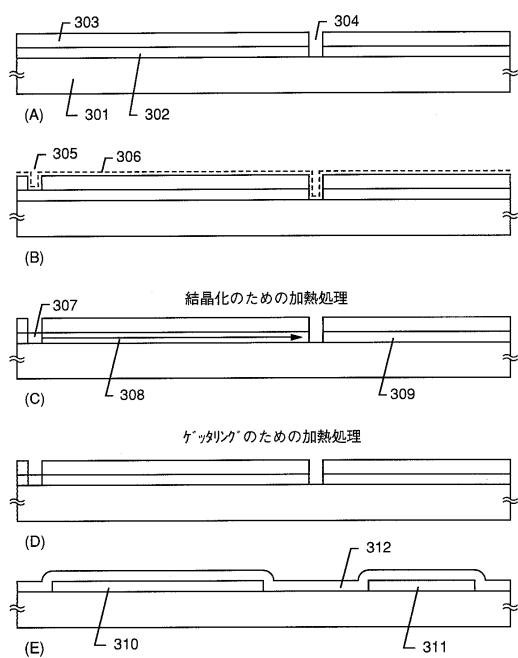

本実施例では、本願発明を利用した半導体装置の作製工程を示す。具体的には同一基板上にドライバー回路と画素マトリクス回路とを一体形成した反射型LCDの作製工程について図3を用いて説明する。

【0031】

まず、石英基板301上に20~100nm厚の非晶質半導体膜302を形成する。石英基板の代わりにシリコン基板またはセラミック基板に下地絶縁膜を設けた基板を用いても良い。また、本実施例では非晶質半導体膜として非晶質珪素膜を用いるが、 $Si_x Ge_{1-x}$  (0<x<1)で示される化合物半導体を用いても良い。

20

【0032】

次に、酸化珪素膜または窒化珪素膜でなるマスク絶縁膜303を50~200nmの厚さに形成する。非晶質珪素膜302とマスク絶縁膜303を連続成膜すると、その界面において結晶成長を阻害しうる界面準位が減るので有効である。そして、パターニングによりマスク絶縁膜303、非晶質珪素膜302を順次エッティングし、ストッパー領域304を形成する。ストッパー領域304は開口幅1~5μmのスリット状に形成すれば良い。(図3(A))

【0033】

なお、上記エッティング工程は、 $CF_4/O_2/SF_6$ 系ガスを用いた一括ドライエッティングを行えば良い。または、マスク絶縁膜303をフッ酸系エッチャントでエッティングし、非晶質珪素膜302を塩素系ガスを用いてドライエッティングするかフッ硝酸を用いてウェットエッティングすれば良い。

30

【0034】

こうして図3(A)の状態が得られたら、マスク絶縁膜303を再びパターニングして開口幅5~20μmのスリット状の開口部305を形成する。そして、重量換算で10~100ppmのニッケルを含んだ酢酸ニッケル塩溶液をスピンドル法により塗布し、ニッケル含有層306を形成する。この技術の詳細は特開平8-78329号公報を参考にすると良い。(図3(B))

【0035】

なお、図3(B)に示す様に、ストッパー領域304内では非晶質珪素膜302の側面が露出してしまい、その部分でニッケル含有層306と接してしまうことになる。しかし、接触する面積が非常に小さいため問題とはならない。

40

【0036】

上述のニッケルは珪素の結晶化を助長する触媒元素として機能する。その様な触媒元素としては、他にもコバルト(Co)、鉄(Fe)、銅(Cu)、パラジウム(Pd)、白金(Pl)、金(Au)、ゲルマニウム(Ge)、鉛(Pb)、錫(Sn)等を用いることが可能である。

【0037】

また、上記触媒元素の添加工程はスピンドル法に限らず、イオン注入法(質量分離を行

50

ったイオン添加)、イオンドーピング法(質量分離を行わないイオン添加)を用いることも可能である。また、CVD法(MOCVD法も含む)、スパッタ法、蒸着法を用いて添加することも可能である。

#### 【0038】

次に、450~500 2時間程度の水素出しの後、不活性雰囲気又は水素雰囲気中において500~700(代表的には550~650)の温度で4~24時間の加熱処理を加えて非晶質珪素膜303の結晶化を行う。本実施例では窒素雰囲気で600 8時間の加熱処理を行う。(図3(C))

#### 【0039】

この時、非晶質珪素膜302の結晶化はニッケルを添加した領域(触媒元素の導入領域)307で発生した核から優先的に進行し、基板301の基板面に対してほぼ平行に成長した結晶領域308が形成される。本発明者らはこの結晶領域308を横成長領域と呼んでいる。横成長領域は比較的揃った状態で個々の結晶が集合しているため、全体的な結晶性に優れるという利点がある。

#### 【0040】

本実施例では横成長領域の進行方向(矢印で示される)の前方にストッパー領域304が形成され、非晶質珪素膜が一旦そこで途切れているのでそれ以上には結晶成長が進行しない。即ち、309で示される領域に横成長領域308が進行することではなく、横成長領域308の成長が強制的に制止される。

#### 【0041】

また、この結晶化工程では600 8時間という加熱処理を施しているので、309で示される領域も自然核発生によって結晶化して結晶領域となる。そのため、横成長領域308とは全く異なる結晶構造をとる。

#### 【0042】

例えば、横成長領域308は棒状結晶が互いに概略平行、且つ、巨視的な方向性をもって並んでいるのに対し、自然核発生による結晶領域309は個々の結晶粒が不規則に存在するだけで何ら規則性が見出せない。この様な結晶構造の差はTEM(透過型電子顕微鏡)観察で確認できる。

#### 【0043】

また、ラマン特性にも差が現れる。横成長領域308と自然核発生による結晶領域309とでラマン特性を比べると、横成長領域308の方がラマン強度が高く、半値幅も狭い。半値幅が狭いということは結晶性が良いということを意味しており、この事からも横成長領域の結晶性の良さが確認できる。

#### 【0044】

また、ストッパー領域304では膜自体の連続性が途切れているため、ニッケルの拡散もそれ以上は進まない。そのため、ストッパー領域304で画素領域を完全に取り囲んでしまえば、画素領域には全くニッケルが存在しない状態を実現することができる。即ち、横成長領域308には少なからずニッケルが存在するが、結晶領域309には全くニッケルは存在しない場合もある。

#### 【0045】

こうして図3(C)の状態が得られる。図3(C)の状態を上面から見ると図1の状態となっている。

#### 【0046】

次に、マスク絶縁膜303をフッ酸系エッチャントを用いて除去する。なお、この時、ストッパー領域304において下地(本実施例では石英)が露出しているので石英自体もエッチャングされ、エッチャング跡が残る。本願発明を利用するとこの様な跡がどうしても形成されてしまうが、この部分は後の層間絶縁膜等で凹凸が吸収されてしまうので問題とはならない。

#### 【0047】

次に、ニッケルを除去するための加熱処理を行う。この加熱処理は処理雰囲気中にハロゲ

10

20

30

40

50

ン元素を含ませ、ハロゲン元素による金属元素のゲッタリング効果を利用するものである。

【0048】

なお、ハロゲン元素によるゲッタリング効果を十分に得るために、上記加熱処理を700を超える温度で行なうことが好ましい。この温度以下では処理雰囲気中のハロゲン化合物の分解が困難となり、ゲッタリング効果が得られなくなる恐れがある。そのため加熱処理温度を好ましくは800～1000（代表的には950）とし、処理時間は0.1～6hr、代表的には0.5～1hrとする。

【0049】

代表的な実施例としては酸素雰囲気中に対して塩化水素（HCl）を0.5～10体積%（本実施例では3体積%）の濃度で含有させた雰囲気中において、950、30分の加熱処理を行えば良い。

【0050】

また、ハロゲン元素を含む化合物としてはHClガス以外にもHF、NF<sub>3</sub>、HBr、Cl<sub>2</sub>、ClF<sub>3</sub>、BCl<sub>3</sub>、F<sub>2</sub>、Br<sub>2</sub>等のハロゲン元素を含む化合物から選ばれた一種または複数種のものを用いることが出来る。

【0051】

この工程においては横成長領域308中のニッケルが塩素の作用によりゲッタリングされ、揮発性の塩化ニッケルとなって大気中へ離脱して除去される。そして、この工程により横成長領域308中のニッケルの濃度は $5 \times 10^{17}$ atoms/cm<sup>3</sup>以下にまで低減される。なお、本発明者らの経験によれば、ニッケル濃度が $5 \times 10^{17}$ atoms/cm<sup>3</sup>以下であればTFT特性に悪影響は出ない。

【0052】

また、この加熱処理によって横成長領域308、自然核発生による結晶領域309自体の結晶性も大幅に向上する。即ち、残存する非晶質成分はほぼ完全に消滅し、非常に高い結晶化率が得られる。また、結晶粒界では不対結合手同士の再結合等の歪み緩和により格子間結合の整合性が高まり、極めてエネルギー障壁の小さい（粒界準位の少ない）結晶領域を得ることができる。

【0053】

次に、得られた結晶領域をパターニングして活性層310、311を形成する。活性層310は横成長領域308のみから形成され、後にドライバ-TFTの活性層を構成する。また、活性層311は自然核発生による結晶領域309のみから形成され、後に画素マトリクス回路の活性層を構成する。

【0054】

活性層310、311を形成したら、珪素を含む絶縁膜でなるゲイト絶縁膜312を形成する。ゲイト絶縁膜312の膜厚は後の熱酸化工程による増加分も考慮して20～250nmの範囲で調節すれば良い。また、成膜方法は公知の気相法（CVD法、スパッタ法等）を用いれば良い。

【0055】

ゲイト絶縁膜312を形成したら、もう一度、700～1100の温度範囲で加熱処理を行う。この加熱処理は先程の加熱処理同様にハロゲン元素を含む雰囲気中で行っても良いし、酸素雰囲気で行っても良い。

【0056】

この加熱処理により活性層310、311とゲイト絶縁膜312との界面では熱酸化反応が進行し、熱酸化膜の分だけゲイト絶縁膜312の膜厚は増加する。この様にして熱酸化膜を形成すると非常に界面準位を減らすことができる。また、活性層端部における熱酸化膜の形成不良（エッジシニング）が防げる。

【0057】

さらに、上記ハロゲン雰囲気における加熱処理を施した後に、窒素雰囲気中で950～1時間程度の加熱処理を行なうことで、ゲイト絶縁膜312の膜質の向上を図ることも有効で

10

20

30

40

50

ある。

【0058】

次に、図示しないアルミニウムを主成分とする金属膜を成膜し、パターニングによって後のゲイト電極の原型（図示せず）を形成する。本実施例では2wt%のスカンジウムを含有したアルミニウム膜を用いる。なお、これ以外にもタンタル膜、導電性を有する珪素膜等を用いることもできる。

【0059】

ここで本発明者らによる特開平7-135318号公報記載の技術を利用する。同公報には、陽極酸化により形成した酸化膜を利用して自己整合的にソース／ドレイン領域と低濃度不純物領域とを形成する技術が開示されている。以下にその技術について簡単に説明する。

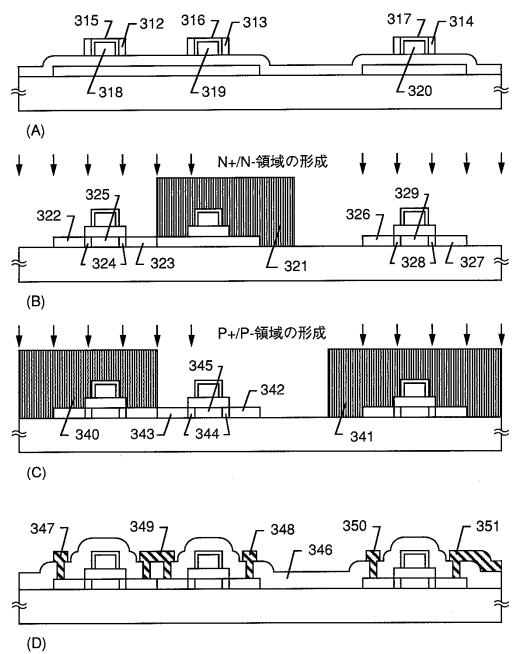

10

【0060】

まず、アルミニウム膜のパターニングに使用したレジストマスク（図示せず）を残したまま3%シウ酸水溶液中で陽極酸化処理を行い、多孔性の陽極酸化膜312～314を形成する。この膜厚が後に低濃度不純物領域の長さになるのでそれに合わせて膜厚を制御する。

【0061】

次に、図示しないレジストマスクを除去した後、エチレングリコール溶液に3%の酒石酸を混合した電解溶液中で陽極酸化処理を行う。この処理では緻密な無孔性の陽極酸化膜315～317が形成される。膜厚は70～120nmで良い。

【0062】

そして、上述の2回に渡る陽極酸化処理の後に残ったアルミニウム膜318～320が実質的にゲイト電極として機能する。（図4（A））

20

【0063】

次にゲイト電極及び多孔性の陽極酸化膜をマスクとしてゲイト絶縁膜312をドライエッティング法によりエッティングする。そして、多孔性の陽極酸化膜312～314を除去する。

【0064】

こうして図4（B）の状態が得られたら、後にPTFT（Pチャネル型TFT）となる領域を隠す様にレジストマスク321を設け、15族から選ばれた元素（代表的にはリン）の添加工程を行う。

30

【0065】

この工程では、まず1回目の不純物添加を高加速電圧で行い、n<sup>-</sup>領域を形成する。この時、加速電圧が80keV程度と高いので不純物元素は露出した活性層表面だけでなく露出したゲイト絶縁膜の端部の下にも添加される。さらに、2回目の不純物添加を低加速電圧で行い、n<sup>+</sup>領域を形成する。この時は加速電圧が10keV程度と低いのでゲイト絶縁膜はマスクとして機能する。

【0066】

以上の工程によりドライバー回路を構成するNTFT（Nチャネル型TFT）のソース領域322、ドレイン領域323、LDD領域324、チャネル形成領域325が形成される。また、同時に画素マトリクス回路を構成するNTFTのソース領域326、ドレイン領域327、LDD領域328、チャネル形成領域329が形成される。

40

【0067】

次に、レジストマスク321を除去し、今度はNTFTを隠す様にして再びレジストマスク340、341を設ける。そして、次に13族から選ばれた元素（代表的にはボロン）の添加工程を行い、PTFTのソース領域342、ドレイン領域343、LDD領域344、チャネル形成領域345を形成する。（図4（C））

【0068】

この場合も前述のNTFTの場合と同様に2回に分けて不純物の添加を行う。また、PTFTはNTFTに比べて劣化に強いので、場合によっては高加速電圧での添加工程のみを高濃度で行い、LDD領域を形成しない構成とすることも可能である。

50

## 【0069】

以上の様にしてソース／ドレイン領域の形成が終了したら、ファーネスアニール、レーザー／アニール、ランプ／アニール等の組み合わせによって不純物元素の活性化を行う。それと同時に添加工程で受けた活性層の損傷も修復される。

## 【0070】

次に、第1の層間絶縁膜346を500 nmの厚さに形成する。層間絶縁膜346としては酸化珪素膜、窒化珪素膜、酸化窒化珪素膜、有機性樹脂膜、或いはそれらの積層膜を用いることができる。

## 【0071】

次に、コンタクトホールを形成した後、ドライバーTFTのソース電極347、348及び共通ドレイン電極349、画素TFTのソース電極350、ドレイン電極351を形成する。（図4（D））

10

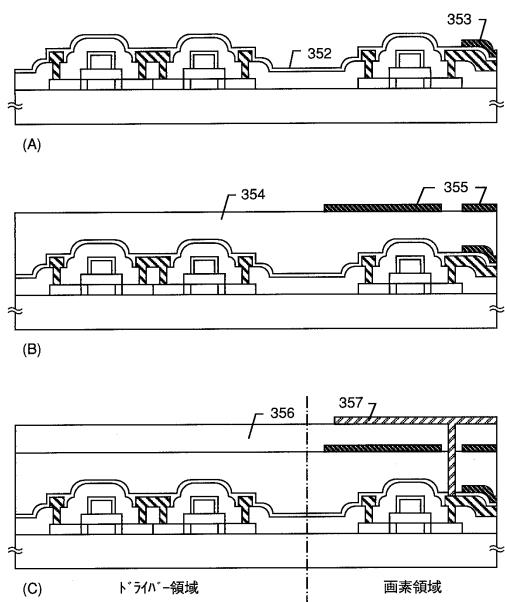

## 【0072】

次に、20～70nm厚の窒化珪素膜352を成膜し、その上に導電膜353を設ける。導電膜353としては、チタン膜やアルミニウムとチタンの積層膜などを用いることができる。導電膜353は画素TFTのドレイン電極351との間で窒化珪素膜352を誘電体として補助容量を形成する。（図5（A））

## 【0073】

次に、有機性樹脂膜でなる第2の層間絶縁膜354を1～2 μmの厚さに形成し、その上にブラックマトリクス355を形成する。ブラックマトリクス355としては、前述の導電膜353と同一材料を用いれば良い。（図5（B））

20

## 【0074】

なお、ブラックマトリクス355は後に画素電極とドレイン電極351とを接続するためのコンタクトホールを形成する位置を除いて、画素領域の全面に配置する。これはブラックマトリクス（遮光膜）としての機能だけでなく、TFTとその上に形成される画素電極との間で電界遮蔽膜をも兼ねるからである。

## 【0075】

本実施例は反射型LCDの例であるので透過型の様に開口率を考慮する必要がない。そのため、本実施例の様に画素電極の下を全体的にブラックマトリクス355で覆う様な構造が可能である。

30

## 【0076】

次に、第3の層間絶縁膜356を形成し、コンタクトホールを形成して画素電極357を形成する。画素電極357としては反射率の高いアルミニウムを主成分とする材料を用いることが好ましい。

## 【0077】

最後に、基板全体を350℃の水素雰囲気で1～2時間加熱し、素子全体の水素化を行うことで膜中（特に活性層中）のダングリングボンド（不対結合手）を終端する。以上の工程によって、図5（C）に示す様な構造のアクティブマトリクス基板を作製することができる。

## 【0078】

40

後は、公知のセル組み工程を行って、反射型LCDを完成させれば良い。本実施例では詳細な説明は省略する。

## 【0079】

本願発明を利用した場合の大きな特徴は、ドライバーTFTの活性層と画素TFTの活性層とで結晶構造が全く異なる点にある。これは、ドライバーTFTのみに特開平8-78329号公報にある様な触媒元素の作用効果を利用し、画素TFTには利用しなかったためである。

## 【0080】

換言すれば、その様にドライバーTFTと画素TFTとで結晶構造の使い分けを明確に行うためには、本願発明が必要不可欠である。即ち、今後微細化がさらに進行した場合、本

50

願発明の様に強制的に横成長領域を制止する技術を利用しなければ、回路の一部のみに横成長領域を用いるという構成は不可能と言える。

【0081】

また、本願発明のもう一つの効果は、画素TFTの活性層には一切触媒元素（本実施例ではニッケル）が存在しない点にある。これは、ニッケルの拡散源である触媒元素の導入領域と画素領域とが物理的に分断されていることによる。

【0082】

仮に画素TFTの活性層（特にチャネル／ドレイン接合部）にニッケル等の金属元素が含まれると、そこをバスとしてオフ電流が増大し、オフ電流のバラツキを招く。しかしながら、本願発明を利用すると画素TFTには一切ニッケルが存在しなくなるので、その様な問題は生じない。

【0083】

また、上述の様な結晶構造の差は、そのままTFTの電気特性の差として現れる。本実施例に従って作製した場合、ドライバーTFTの電界効果移動度（モビリティ）は150～250cm<sup>2</sup>/Vs（NTFT）を達成するが、画素TFTの電界効果移動度は90～110cm<sup>2</sup>/Vs（NTFT）程度と若干低くなる。

【0084】

〔実施例2〕

本実施例では、実施例1とは異なる手段でストッパー領域を形成する場合に例について説明する。

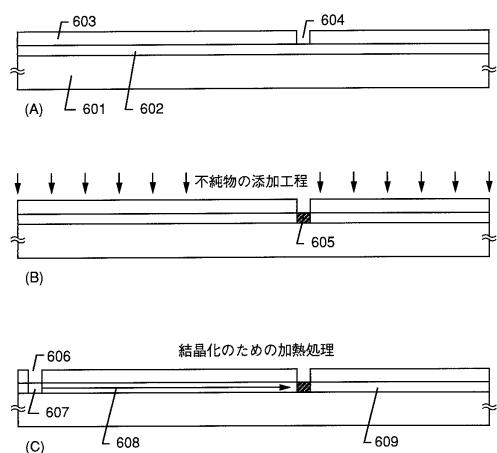

【0085】

まず、実施例1の場合と同様に石英基板601上に非晶質珪素膜602、マスク絶縁膜603を形成する。その後、マスク絶縁膜603のみに開口部604を形成する。（図6（A））

【0086】

その状態でリン、窒素、酸素またはアルゴンから選ばれた一種または複数種の不純物元素を添加する。この不純物元素の添加工程は加速電圧20keV、ドーズ量 $1 \times 10^{15} \sim 1 \times 10^{16}$ atoms/cm<sup>2</sup>程度のイオン注入法またはイオンドーピング法で行えば良い。

【0087】

この不純物元素の添加工程により高濃度に上記不純物元素を含むストッパー領域605が形成される。（図6（B））

【0088】

次に、パターニングにより触媒元素を導入するための開口部606を形成し、ニッケル含有層（図示せず）を形成した後、結晶化のための加熱処理を行う。この工程については実施例1の条件に従えば良い。

【0089】

こうして、触媒元素の導入領域607、横成長領域608が形成される。この時、横成長領域608の結晶成長はストッパー領域605によって強制的に制止され、609で示される領域は自然核発生によって結晶化された領域となる。

【0090】

結晶化が終了したら、触媒元素の導入領域607、ストッパー領域605を完全に取り除いて活性層を形成し、TFTを作製すれば良い。活性層の形成からは実施例1と同様の工程に従えば良いので説明は省略する。

【0091】

実施例1が非晶質珪素膜を除去して物理的にドライバー領域と画素領域とを分断したのに対し、本実施例ではドライバー領域と画素領域との間に高濃度不純物領域を形成して意図的に結晶化を阻害し、横成長領域の成長を強制的に制止する構成を実現している。

【0092】

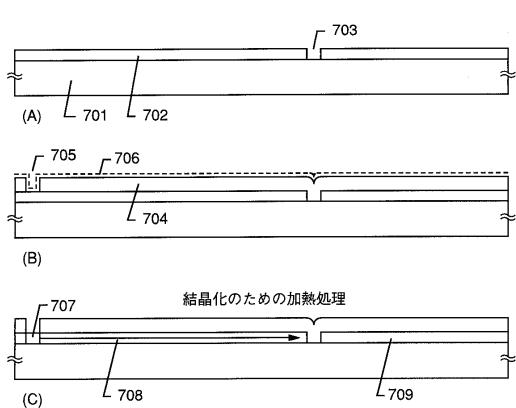

〔実施例3〕

本実施例では実施例1において、マスク絶縁膜の形成順序を変えた例を示す。図7（A）

10

20

40

50

において、701は石英基板、702は非晶質珪素膜、703は非晶質珪素膜702をエッチングして形成したストッパー領域である。

【0093】

本実施例では、図7(A)の状態が得られてからマスク絶縁膜704を形成し、開口部705を設けて触媒元素の含有層706を形成する。(図7(B))

【0094】

そして、結晶化のための加熱処理を実施例1の示した条件に従って行い、触媒元素の導入領域707、横成長領域708、自然核発生による結晶領域709を形成する。(図7(C))

【0095】

本実施例の構成では、ストッパー領域703に現れる非晶質珪素膜702の側面がマスク絶縁膜704によって完全に覆われるので、触媒元素の含有層706がストッパー領域703において非晶質珪素膜702に接触することはない。そのため、画素領域に対する触媒元素の侵入を完全に防ぐことができる。

【0096】

〔実施例4〕

本実施例では、結晶化後の珪素膜の結晶性改善工程をレーザーアニールによって行う場合の例を説明する。

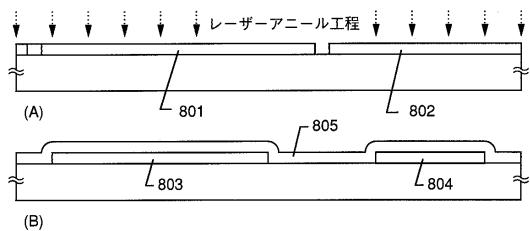

【0097】

まず、実施例1の工程に従って図3(C)の状態を得る。そして、マスク絶縁膜303を除去して、図8(A)の状態を得る。さらに、この状態でパルスレーザー光の照射を行う。パルスレーザー光としては、KrF、ArF、XeCl等のエキシマレーザーを利用すれば良い。

【0098】

レーザー光は線状に加工して、基板の一端から他端に向かって走査する様にして照射する。この時、エネルギー強度は250~350mJ/cm<sup>2</sup>程度で良いが、この値は結晶性珪素膜の膜質によって変化するので、実際には実施者が実験的に最適値を決定する必要がある。

【0099】

また、レーザー光の代わりにそれと同等の強度を持つ強光を照射することで結晶性の改善を行うこともできる。その様な強光としては紫外光ランプや赤外光ランプから発する強光などを用いれば良い。

【0100】

こうしてレーザーアニール工程によって結晶性珪素膜の結晶性を改善したら、パターニングによって活性層803、804を形成し、その上にゲイト絶縁膜805を形成する。(図8(B))

【0101】

なお、ここではレーザーアニールによって結晶性を改善した後に活性層803、804を形成しているが、この順序を入れ換えて構わない。

【0102】

また、実施例1ではゲイト絶縁膜を形成した後に触媒元素のゲッタリングを兼ねた加熱処理を行って結晶性を改善しているので、耐熱性の高い石英基板を用いる必要があった。しかしながら、本実施例の様にレーザーアニールによって結晶性を改善する場合、必ずしも高い温度での加熱処理を必要としないため、石英基板の代わりに下地膜を設けたガラス基板を用いることも可能である。

【0103】

その場合、実施例1において石英基板の代わりに酸化珪素膜でなる下地膜を設けたガラス基板を用いる。その他の工程は実施例1に従えば良い。結晶化のための加熱処理も500~700という様にガラスの歪み点以下の温度であるので問題とはならない。

【0104】

そして、結晶化の後にレーザーアニールによって結晶領域の結晶性を改善し、活性層を形

成してゲイト絶縁膜を形成する。この後の工程は実施例1に従えば良い。なお、この様な工程に従った場合、図3(D)に示した加熱処理による効果の一部(熱酸化膜の形成、ゲイト絶縁膜の膜質改善など)は得られないが、それでも十分実用に耐えうるTFTを作製できる。

【0105】

また、本実施例の構成を実施例2の構成と組み合わせることは容易である。

【0106】

〔実施例5〕

本実施例では、実施例1とは異なる手段で結晶化に利用した触媒元素をゲッタリングする構成を示す。

10

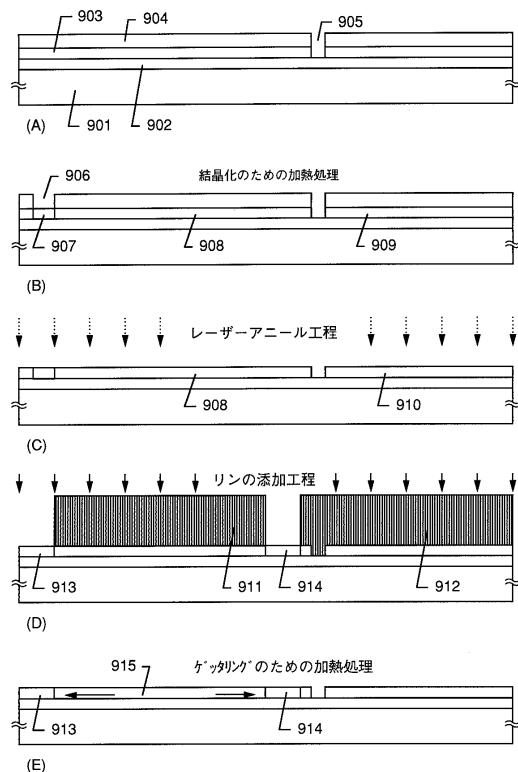

【0107】

図9(A)において、901はガラス基板、902は200nm厚の酸化珪素膜でなる下地膜、903は非晶質珪素膜、904はマスク絶縁膜、905はストッパー領域である。ストッパー領域905の形成方法やその他の膜厚範囲等は実施例1で述べた通りである。

【0108】

次に、マスク絶縁膜904にニッケルを導入するための開口部906を設け、図示しないニッケル含有層を形成して結晶化のための加熱処理を行う。本実施例では450~500℃2時間の水素出しの後、570℃14時間の加熱処理を行う。この工程によってニッケル導入領域907、横成長領域908が形成される。また、この時909で示される領域は温度が570℃と低いため自然核発生が起こらず、完全に非晶質状態のままとなっている。

20

【0109】

次に、マスク絶縁膜904を除去してレーザーニードルを行う。レーザー光の照射は、室温においてパルス周波数30Hz、スキャン速度2mm/sec、エネルギー強度315mJ/cm<sup>2</sup>で行う。また、レーザー光は長さ120mm、幅0.4~1.0mmの線状レーザーに加工されて照射される。この工程により横成長領域908の結晶性が改善されると同時に、非晶質領域909が結晶化され、レーザー光による結晶領域910となる。(図9(C))

【0110】

次に、レジストマスク911と画素領域を完全に覆うレジストマスク912を設け、15族から選ばれた元素(本実施例ではリン)の添加工程を行う。この工程により高濃度にリンを含む領域(以下、ゲッタリング領域と呼ぶ)913、914が形成される。(図9(D))

30

【0111】

この時、リンの添加工程はイオン注入法またはイオンドーピング法を用いる。添加条件はRF電力を20W、加速電圧を5~30keV(代表的には10keV)に設定し、ドーズ量は1×10<sup>13</sup>atoms/cm<sup>2</sup>以上(好ましくは5×10<sup>13</sup>~5×10<sup>15</sup>atoms/cm<sup>2</sup>)とする。

【0112】

次に、レジストマスク911、912を除去した後、ニッケルをゲッタリングするための加熱処理を行う。この加熱処理は不活性雰囲気、水素雰囲気、酸化性雰囲気またはハロゲン元素を含む酸化性雰囲気におけるファーネスアニールで良い。また、処理温度は400~700℃(好ましくは550~650℃)とし、処理時間は2時間以上(好ましくは4~12時間)とすれば良い。

40

【0113】

この工程により横成長領域908に残存していたニッケルは大部分がゲッタリング領域913、914に捕獲され、徹底的にニッケルの除去された結晶領域915を得ることができる。この結晶領域915では、ニッケル濃度が5×10<sup>17</sup>atoms/cm<sup>3</sup>以下にまで低減されている。(図9(E))

【0114】

図9(E)の状態が得られたら、結晶領域915からなる活性層でドライバ-TFTを構成し、結晶領域910からなる活性層で画素TFTを構成すれば良い。TFTの作製工程は実施例1に示した構成にもできるし、他の公知の手段で作製することも可能である。

50

## 【0115】

本実施例の特徴は、まず、画素TFTの活性層がレーザーアニールに特有の結晶構造を有する点にある。即ち、比較的大きな多角形状の結晶粒と結晶粒界付近に存在するリッジの存在が観測される。この結晶構造は横成長領域及び自然核発生による結晶領域の結晶構造とは明らかに異なるものである。

## 【0116】

また、本実施例の場合、ドライバーTFT（横成長領域からなる活性層を有する）と画素TFT（レーザー結晶化された活性層を有する）とではTFTの電気特性が大きく異なる。

## 【0117】

例えば、ドライバーTFTのサブスレッショルド係数（S値）が300～350mV/decadeであるのに対し、画素TFTのS値は450～500mV/decadeと大きい。また、電界効果移動度もドライバーTFTが100～150cm<sup>2</sup>/Vs（NTFT）であるのに対し、画素TFTは60～80cm<sup>2</sup>/Vs（NTFT）とやや低い値となる。

## 【0118】

また、リンによるゲッタリング工程を、ドライバーTFTの活性層を構成する領域（横成長領域）のみ、即ち特定箇所のみに行うという点にも特徴がある。

## 【0119】

なお、本実施例の構成を実施例1～3に示した構成と組み合わせることは容易である。特に、実施例1に示した様なハロゲン元素を用いたゲッタリング工程と組み合わせると、さらに効果的に触媒元素を除去することが可能である。

## 【0120】

## 〔実施例6〕

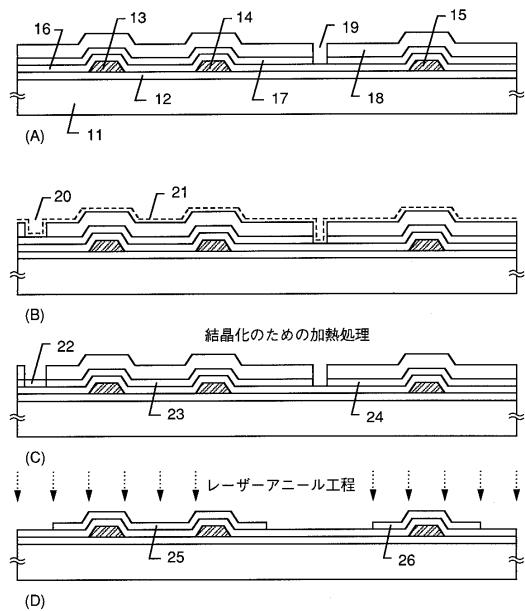

本実施例では、実施例5の構成を基本として、代表的なボトムゲイト型構造である逆スタガ型TFTで回路構成を行う場合の例を説明する。

## 【0121】

まず、ガラス基板11上に下地膜12を設け、ゲイト電極13～15を形成する。ゲイト電極13～15の材料としては、アルミニウムを主成分とする材料、クロム、タンタル、タンゲステン、モリブデン等を用いることができる。

## 【0122】

次に、ゲイト絶縁膜16を形成した後、非晶質珪素膜17、マスク絶縁膜18を設け、実施例1に示した手段によりストッパー領域19を形成する。この場合もストッパー領域19の下部ではゲイト絶縁膜16にエッチング跡が形成されるが問題とはならない。（図10（A））

## 【0123】

次に、ニッケルを導入するための開口部20を設け、ニッケル含有層21を形成する。詳細な実施例1に従えば良い。（図10（B））

## 【0124】

ニッケル含有層21を形成したら、結晶化のための加熱処理を行い、ニッケル導入領域22、横成長領域23、非晶質領域24を形成する。なお、結晶化のための加熱処理は実施例5の条件に従えば良い。（図10（C））

## 【0125】

そして、マスク絶縁膜18を除去した後、横成長領域23のみからなる活性層25、非晶質領域24のみからなる活性層26を形成し、その後、レーザーアニールを行う。レーザーアニールの条件は実施例5に示した条件に従えば良い。（図10（D））

## 【0126】

こうして活性層25の結晶性は改善され、活性層26はレーザー照射によって結晶化される。以上の様にして図10（D）の状態が得られたら、公知の逆スタガ型TFTの作製工程に従って完成させれば良い。

## 【0127】

なお、本実施例は実施例 5 の構成を基本として説明したが、実施例 1 ~ 4 に示したどの構成も逆スタガ型 TFT に適用することは容易である。ただし、高い温度での加熱処理を行う場合、ゲイト電極の耐熱性を考慮する必要があることは言うまでもない。

【実施例 7】

本願発明は特開平8-78329 号公報に記載された技術が適用しうる構成であれば全ての TFT に対して適用することができる。また、その様な TFT で作製する反射型 LCD、透過型 LCD 等に適用することは容易である。

【0128】

また、本願発明は LCD ( 液晶表示装置 ) だけでなく、EL ( エレクトロルミネッセンス ) 表示装置や EC ( エレクトロクロミクス ) 表示装置の様に、TFT をスイッチング素子として使用しうる装置であれば全てに適用できる。 10

【0129】

なお、表示装置の様に電気的信号を光学的信号に変換する或いはその逆を行う装置を電気光学装置と定義する。即ち、本願発明は TFT で構成される全ての電気光学装置に対して適用することが可能である。

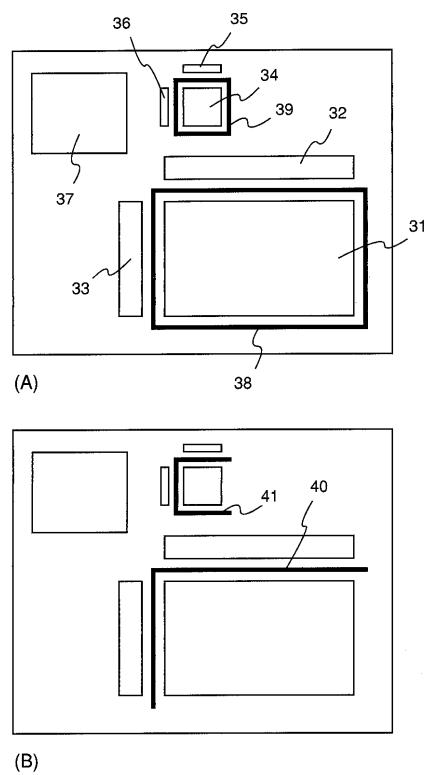

【0130】

また、電気光学装置の範疇にはイメージセンサの如き光電変換層を有する半導体素子も含まれる。例えば、本願発明は図 11 に示す様な構成のイメージセンサ内蔵型 LCD に対して適用すると効果的である。

【0131】

図 11 において、31 はマトリクス回路からなる映像表示部、32、33 は映像表示部用の駆動回路である。また、34 はマトリクス回路からなるエリアセンサの映像読込部 ( 受光部 ) であり、35、36 はエリアセンサ用の駆動回路である。さらに、37 は外部からの信号処理、エリアセンサからの信号処理または映像表示部からの信号処理を行う制御回路である。 20

【0132】

図 11 の様なシステム構成とする場合、映像表示部用の駆動回路 32、33、エリアセンサ用の駆動回路 35、36 及び制御回路 37 は高速動作を必要とするため横成長領域を利用した TFT で構成しなければならない。

【0133】

しかし、映像表示部 31、映像読込部 34 はそれほど高速動作を必要としないため横成長領域を利用することは必ずしも必要ではない。それよりもマトリクス状に百万個を超える TFT を配置するため、個々の TFT の均一性を揃えることが重要な問題となる。 30

【0134】

そこで、図 11 に示す様な配置で横成長領域のストッパー領域 38、39 を設けて結晶化を行うことで、横成長を利用する領域と利用しない領域との区別を明確に行う。この様にすることで、図 11 に示す様に高密度に集積化されたインテリジェントパネルを作製する場合においても、回路設計の自由度を大幅に確保することが可能となる。

【0135】

なお、横成長領域が映像表示部 31 及び映像読込部 34 に到達しない様にすることが重要であるので、図 11 ( B ) の様な構成でストッパー領域 40、41 を配置しても良い。しかし映像表示部 31 及び映像読込部 34 から完全に触媒元素を排除するには図 11 ( A ) の構成が望ましい。 40

【0136】

【実施例 8】

実施例 7 に示した電気光学装置は、様々な電子機器のディスプレイとして利用される。なお、本実施例に挙げる電子機器とは、液晶モジュールに代表される電気光学装置を搭載した製品と定義する。

【0137】

その様な電子機器としては、ビデオカメラ、スチルカメラ、プロジェクター、プロジェク 50

ションＴＶ、ヘッドマウントディスプレイ、カーナビゲーション、パーソナルコンピュータ（ノート型を含む）、携帯情報端末（モバイルコンピュータ、携帯電話等）などが挙げられる。

#### 【0138】

この様に本願発明の適用範囲は極めて広く、あらゆる分野の電子機器に適用することが可能である。他にも電光掲示盤、宣伝公告用ディスプレイなどにも活用することができる。

#### 【0139】

#### 【発明の効果】

本願発明を利用することで、横成長領域を利用する領域と利用しない領域との区別を明確につけることが可能となる。そのため、画素マトリクス回路の様に均一性が最重要課題となる領域に近接する場所にも、問題なく横成長領域を形成することができる。

10

#### 【0140】

また、今後集積度が益々向上して高密度なインテリジェントパネルの要求が高まった時に、回路設計の自由度が大幅に広がり、横成長領域の優れた結晶性を有効に活用することができる。

#### 【図面の簡単な説明】

【図1】 本願発明の構成を説明するための図。

【図2】 従来の構成を説明するための図。

【図3】 TFTの作製工程を示す図。

【図4】 TFTの作製工程を示す図。

20

【図5】 TFTの作製工程を示す図。

【図6】 TFTの作製工程を示す図。

【図7】 TFTの作製工程を示す図。

【図8】 TFTの作製工程を示す図。

【図9】 TFTの作製工程を示す図。

【図10】 TFTの作製工程を示す図。

【図11】 イメージセンサ内蔵型LCDの構成を示す図。

#### 【符号の説明】

101、102 ドライバーTFTの活性層

103 画素TFTの活性層

30

104 触媒元素の導入領域

105 横成長領域

106 ストップペー領域

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図9】

【図8】

【図10】

【図11】

---

フロントページの続き

(56)参考文献 特開平09-162416(JP, A)

特開平06-268212(JP, A)

特開平09-045931(JP, A)

特開平07-176479(JP, A)

特開平05-109737(JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/336

H01L 29/786