(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2010-0090197

(43) 공개일자 2010년08월13일

(51) Int. Cl.

*H01L 27/14* (2006.01)

(21) 출원번호 10-2010-0006789

(22) 출원일자 2010년01월26일

심사청구일자 없음

(30) 우선권주장

JP-P-2009-025346 2009년02월05일 일본(JP)

(71) 출원인

소니 주식회사

일본국 도쿄도 미나토쿠 코난 1-7-1

(72) 발명자

칸베 히데오

일본 도쿄도 미나토쿠 코난 1-7-1 소니 주식회사

내

(74) 대리인

최달용

전체 청구항 수 : 총 16 항

(54) 고체 활상 장치, 고체 활상 장치의 제조 방법, 고체 활상 장치의 구동 방법, 및 전자 기기

### (57) 요 약

고체 활상 장치는: 기판과; 수광 기간에 상기 기판에 제 1의 전위를 인가하고, 비수광 기간에 상기 기판에 제 2의 전위를 인가하는 기판 전압 전원; 및 수광한 광에 응한 신호 전하를 생성하는 수광부와, 상기 신호 전하를 축적 보존하는 축적용량부와, 암전류 억제부와, 상기 신호 전하가 상기 기판의 이면측으로 빠져 나가도록 기판의 전위 분포를 조정하는 전자 셔터 조정층과, 상기 축적용량부에 축적된 신호 전하를 판독하는 판독 게이트부와, 상기 판독 게이트부에 의해 판독된 신호 전하를 수직 방향으로 전송하는 수직 전송 레지스터를 포함하는 복수의 화소를 포함한다.

대 표 도 - 도2

## 특허청구의 범위

### 청구항 1

기판과;

수광 기간에 상기 기판에 제 1의 전위를 인가하고, 비수광 기간에 상기 기판에 제 2의 전위를 인가하는 기판 전압 전원; 및

상기 기판의 표면측에 형성되고, 수광한 광에 응한 신호 전하를 생성하는 수광부와, 상기 수광부에 인접하여 형성되고, 상기 기판에 제 1의 전위가 인가된 때에, 상기 수광부에서 생성된 신호 전하가 전송되고 상기 신호 전하를 축적 보존하는 축적용량부와, 상기 수광부와 상기 축적용량부에 형성된 암전류 억제부와, 상기 기판 내의 상기 수광부에 대향하는 영역으로서, 상기 축적용량부로부터 소정의 오프셋 영역만큼 떨어진 영역에 형성되고, 상기 기판에 제 2의 전위가 인가된 때에 상기 수광부에서 생성된 신호 전하가 상기 기판의 이면측으로 빠져 나가도록 기판의 전위 분포를 조정하는 전자 셔터 조정층과, 상기 축적용량부에 축적된 신호 전하를 판독하는 판독 게이트부와, 상기 판독 게이트부에 의해 판독된 신호 전하를 수직 방향으로 전송하는 수직 전송 레지스터를 포함하는 복수의 화소를 포함하는 것을 특징으로 하는 고체 활상 장치.

### 청구항 2

제 1항에 있어서,

상기 기판은, 제 1 도전형의 반도체 기판과, 상기 반도체 기판상에 형성된 제 2 도전형의 반도체 웰층으로 구성되고,

상기 수광부는, 제 1 도전형의 불순물 영역과 그 상부의 암전류 억제부 및 하부의 제 2 도전형의 불순물 영역의 접합면을 갖고서 상기 반도체 웰층에 형성되고,

상기 축적용량부는, 제 1 도전형의 불순물 영역과 제 2 도전형의 불순물 영역의 접합면을 갖고서 구성되고,

상기 전자 셔터 조정층은, 상기 반도체 기판과 상기 반도체 웰층 사이에, 제 1 도전형의 불순물 영역에 의해 형성되는 것을 특징으로 하는 고체 활상 장치.

### 청구항 3

제 2항에 있어서,

상기 축적용량부의 정전 포텐셜은, 상기 수광부의 정전 포텐셜보다도 깊게 형성되는 것을 특징으로 하는 고체 활상 장치.

### 청구항 4

제 3항에 있어서,

상기 오프셋 영역상부의, 상기 수광부와 상기 축적용량부 사이의 영역의 정전 포텐셜은, 상기 수광 기간과, 상기 비수광 기간에서, 개략 동등한 값을 유지하는 것을 특징으로 하는 고체 활상 장치.

### 청구항 5

제 4항에 있어서,

상기 축적용량부의 광 입사측 상부에 차광층을 가지며, 상기 차광층의 단부는 돌출부를 갖도록 상기 수광부측으로 연장하는 것을 특징으로 하는 고체 활상 장치.

### 청구항 6

제 5항에 있어서,

상기 수광부 및 상기 축적용량부의 상기 암전류 억제부는, 상기 수광부 및 상기 축적용량부의 광 입사측 표면에 형성된 제 2 도전형의 불순물 영역을 포함하는 것을 특징으로 하는 고체 활상 장치.

**청구항 7**

제 5항에 있어서,

상기 수광부의 상기 암전류 억제부는, 상기 수광부의 광 입사측 표면에 형성된 제 2 도전형의 불순물 영역에 의해 구성되고,

상기 전하 축적용량부의 상기 암전류 억제부는, 상기 전하 축적용량부의 광 입사측 상부에 형성된 암전류 억제 전극과, 상기 암전류 억제 전극에 직류 전압을 인가하는 직류 전압 전원에 의해 구성되는 것을 특징으로 하는 고체 활상 장치.

**청구항 8**

제 7항에 있어서,

상기 암전류 억제 전극은, 상기 차광층과 전기적으로 접속되는 것을 특징으로 하는 고체 활상 장치.

**청구항 9**

제 5항에 있어서,

상기 차광층은, 또한, 상기 수직 전송 레지스터부 상부에도 형성되는 것을 특징으로 하는 고체 활상 장치.

**청구항 10**

제 5항에 있어서,

상기 차광층은, 상기 수광부의 개구 영역을 제외한 영역을 덮도록 형성되는 것을 특징으로 하는 고체 활상 장치.

**청구항 11**

제 1 도전형의 반도체 기판을 준비하는 공정;

상기 반도체 기판상에 제 2 도전형의 반도체 웨이팅을 형성하는 공정;

상기 반도체 웨이팅의 표면측에, 수광부, 수광부에 인접하는 축적용량부, 및 판독 게이트부를 통하여 상기 축적용량부에 인접하는 수직 전송 채널을 형성하는 공정;

상기 반도체 웨이팅을 형성하기 전, 또는 후에, 상기 반도체 기판과 상기 반도체 웨이팅 사이의, 상기 수광부에 대향하는 영역으로서, 상기 축적용량부로부터 소망하는 오프셋 영역만큼 떨어진 영역에 제 1 도전형으로 이루어지는 전자 셔터 조정층을 형성하는 공정;

상기 축적용량부 및 수광부 상부의 광 입사측에 암전류 억제부를 형성하는 공정; 및

상기 기판에, 수광 기간과, 비수광 기간에서 다른 전위를 인가하는 기판 전압 전원을 접속하는 공정을 포함하는 것을 특징으로 하는 고체 활상 장치의 제조 방법.

**청구항 12**

제 11항에 있어서,

상기 반도체 웨이팅은, 상기 반도체 기판상에 형성된 제 2 도전형의 에피택셜 성장층에 의해 구성되는 것을 특징으로 하는 고체 활상 장치의 제조 방법.

**청구항 13**

제 12항에 있어서,

상기 반도체 웨이팅은, 상기 반도체 기판상에 제 1 도전형의 에피택셜 성장층을 형성한 후, 상기 에피택셜 성장층의 소망하는 영역에, 제 2 도전형의 불순물을 이온 주입하여 형성되는 것을 특징으로 하는 고체 활상 장치.

**청구항 14**

기판과;

수광 기간에 상기 기판에 제 1의 전위를 인가하고, 비수광 기간에 상기 기판에 제 2의 전위를 인가하는 기판 전압 전원; 및

상기 기판의 표면측에 형성되고, 수광한 광에 응한 신호 전하를 생성하는 수광부와, 상기 수광부에 인접하여 형성되고, 상기 기판에 제 1의 전위가 인가된 때에, 상기 수광부에서 생성된 신호 전하가 전송되고 상기 신호 전하를 축적 보존하는 축적용량부와, 상기 수광부와 상기 축적용량부에 형성된 암전류 억제부와, 상기 기판 내의 상기 수광부에 대향하는 영역으로서, 상기 축적용량부로부터 소정의 오프셋 영역만큼 떨어진 영역에 형성되고, 상기 기판에 제 2의 전위가 인가된 때에 상기 수광부에서 생성된 신호 전하가 상기 기판의 이면측으로 빠져 나가도록 기판의 전위 분포를 조정하는 전자 셔터 조정증과, 상기 축적용량부에 축적된 신호 전하를 판독하는 판독 게이트부와, 상기 판독 게이트부에 의해 판독된 신호 전하를 수직 방향으로 전송하는 수직 전송 레지스터를 포함하는 복수의 화소를 포함하는 고체 활상 장치의 구동 방법으로서,

상기 기판 전압 전원에 의해, 상기 기판에 제 1의 전위를 인가함에 의해, 상기 수광부에서 생성된 신호 전하의 상기 축적용량부로의 전송을 시작하는 단계; 및

상기 기판 전압 전원에 의해, 상기 기판에 제 2의 전위를 인가함에 의해, 상기 수광부에서 생성된 신호 전하의 상기 축적용량부로의 전송을 종료하고, 상기 수광부에서 생성된 신호 전하를 상기 기판측으로 빠져 나가게 하고, 상기 축적용량부에 축적된 신호 전하를 판독하는 단계를 포함하는 것을 특징으로 하는 고체 활상 장치의 구동 방법.

## 청구항 15

제 14항에 있어서,

상기 수광 기간의 시작 및 종료는, 상기 기판에 형성된 전화소의 수광부에서 동시에 이루어지고,

상기 비수광 기간에서는, 축적용량부로부터의 신호 전하의 판독이, 화소마다 순차적으로 행하여지는 것을 특징으로 하는 고체 활상 장치의 구동 방법.

## 청구항 16

광학 렌즈와;

기판과, 수광 기간에 상기 기판에 제 1의 전위를 인가하고, 비수광 기간에 상기 기판에 제 2의 전위를 인가하는 기판 전압 전원과, 상기 기판의 표면측에 형성되고, 수광한 광에 응한 신호 전하를 생성하는 수광부와, 상기 수광부에 인접하여 형성되고, 상기 기판에 제 1의 전위가 인가된 때에, 상기 수광부에서 생성된 신호 전하가 전송되어 상기 신호 전하를 축적 보존하는 축적용량부와, 상기 수광부와 상기 축적용량부에 형성된 암전류 억제부와, 상기 기판 내의 상기 수광부에 대향하는 영역으로서, 상기 축적용량부로부터 소정의 오프셋 영역만큼 떨어진 영역에 형성되고, 상기 기판에 제 2의 전위가 인가된 때에 상기 수광부에서 생성된 신호 전하가 상기 기판의 이면측으로 빠져 나가도록 기판의 전위 분포를 조정하는 전자 셔터 조정증과, 상기 축적용량부에 축적된 신호 전하를 판독하는 판독 게이트부와, 상기 판독 게이트부에 의해 판독된 신호 전하를 수직 방향으로 전송하는 수직 전송 레지스터를 포함하고 구성되고, 상기 광학 렌즈에 집광된 광이 입사된 고체 활상 장치; 및

상기 고체 활상 장치로부터 출력되는 출력 신호를 처리하는 신호 처리 회로를 포함하는 것을 특징으로 하는 전자 기기.

## 명세서

### 기술 분야

[0001] 본 발명은, 고체 활상 장치에 관한 것으로, 특히, CCD(Charge Coupled Device)형의 고체 활상 장치, 고체 활상 장치의 제조 방법, 및 고체 활상 장치의 구동 방법에 관한 것이다. 또한, 그 고체 활상 장치를 이용한 전자 기기에 관한 것이다.

### 배경 기술

[0002] 휴대 전화 등, 소형의 모바일 기기에 사용되는 디지털 카메라 모듈에 이용되는 고체 활상 장치에서는, 메커니컬

셔터를 이용하지 않는, 메커니컬 셔터레스의 디지털 카메라 모듈에 적합한 구성으로 하는 것이 요망되고 있다.

[0003] 그런데, 순차 주사 방식의 CCD형 고체 활상 장치에서는, 모든 화소의 수광부에 축적된 신호 전하를 1회의 판독 동작으로, 차광된 수직 CCD에 전송하여, 1프레임의 판독이 행하여진다(일본 특개평07-336604호 공보). 이에 대해, 인터레이스 주사 방식에서는, 각 화소의 수광부에 축적된 신호 전하를 수직 CCD를 사용하여 교대로 판독한다(일본 특개평02-243073호 공보). 이 경우, 판독 시간 동안 수광부에 입사하고 있는 광의 광전변환에 의해 생성된 신호 전하가 각 화소의 수광부에 축적된 신호 전하에 계속해서 더해지게 된다.

[0004] 이 때문에, 디지털 카메라 기능을 메커니컬 셔터레스로 실현하기 위해서는, 예를 들면 고체 활상 장치로서 CCD 형의 고체 활상 장치를 이용하는 경우, 순차 주사 방식의 CCD를 이용할 필요가 있다.

[0005] 그러나, 순차 주사 방식의 CCD형 고체 활상 장치는, 하나의 수광부마다, 수직 CCD의 1bit분의 전송 스테이지가 필요하기 때문에, 수직 CCD 내의 전송 전극 구조가 복잡하게 되고, 또한, 한번에 수직 CCD로 운반할 수 있는 신호 전하량의 제약도 받기 쉽다. 역으로, 메커니컬 셔터를 이용하는 구성을 전제로 하면, 인터레이스 주사 방식의 CCD형 고체 활상 장치에 있어서, 복수회로 나누어 신호 전하를 운반하는 구성이 가능해지기 때문에, 취급 전하량을 일반적으로 많이 취할 수 있다.

[0006] 한편, 디지털 카메라 모듈에 CMOS형의 고체 활상 장치를 이용하는 경우에는, 수광부에서의 라인 순차 수광과, 전송 트랜지스터에 의한 라인 순차 판독이 가능해진다. 이 때문에, 수광부에서, 수광 기간이 끝나는 대로 라인 순차적으로 신호 전하를 판독함으로써, 계속적으로 수광부에 입사하여 오는 광의 영향을 저감할 수 있다.

[0007] 상술한 바와 같이, CMOS형 고체 활상 장치에서는 라인 순차로 신호 전하의 판독이 행하여지기 때문에, 예를 들면 화면 내의 위의 라인과 아래의 라인에서는, 수광 시간대(수광의 타이밍)가 다르다. 화소수가 많아지면, 필연적으로 전화면의 판독에 긴 시간을 필요로 하게 되는데, 이와 같은 수광 기간의 동시각성(同時刻性)을 갖지 않는 CMOS형의 고체 활상 장치는, 움직이는 피사체의 활상에서, 라인마다 화상 정보에 어긋남이 생겨 베린다.

[0008] 이상과 같은 이유에 의해, 현재 상태의 대부분의 휴대 전화의 카메라에서 CMOS형의 고체 활상 장치가 사용되고 있지만, 메커니컬 셔터를 실장함으로써, 수광 시간대의 어긋남의 효과를 막고 있다. 즉, 메커니컬 셔터를 어느 시간 개방에 하고 있는 사이에, CMOS형의 고체 활상 장치에 수광부에서, 신호 전하의 생성, 축적을 행하고, 메커니컬 셔터를 닫은 후에, 라인 순차로 각 수광부로부터의 신호 판독을 행하고 있다.

[0009] 이상과 같이, 순차 주사 방식의 CCD형 고체 활상 장치는, CCD의 전극 구조가 복잡하게 된다는 문제가 있고, 또한 CMOS형의 고체 활상 장치에서 수광 시간대의 어긋남의 효과를 막기 위해서는, 메커니컬 셔터를 이용하지 않으면 안된다는 문제가 있다.

## 발명의 내용

### 해결하려는 과제

[0010] 상술한 점을 감안하여, 본 발명은, 간단한 구성이며, 또한, 메커니컬 셔터 등의 소자 외부 셔터가 없는 전자 기기에 이용할 수 있는 CCD형의 고체 활상 장치, 고체 활상 장치의 제조 방법, 및 고체 활상 장치의 구동 방법을 제공한다. 또한, 그 고체 활상 장치를 이용한 전자 기기를 제공한다.

### 과제의 해결 수단

[0011] 본 발명의 고체 활상 장치는, 기판과, 수광 기간과 비수광 기간에서 다른 전위를 기판에 인가하는 기판 전압 전원을 갖는다. 또한, 기판에는, 수광부, 축적용량부, 암전류 억제부, 판독 게이트부, 수직 전송 레지스터를 포함하여 구성되는 복수의 화소가 형성된다.

[0012] 수광부는, 기판 표면측에 형성되는 것이고, 수광한 광에 응하여 신호 전하를 생성한다. 축적용량부는, 수광부에 인접하는 영역에 형성되고, 기판에 제 1의 전위가 인가된 때에, 수광부에서 생성된 신호 전하가 전송되고, 상기 신호 전하를 축적 보존하는 것이다.

[0013] 암전류 억제부는, 수광부 및 축적용량부에 형성되는 것이다.

[0014] 전자 셔터 조정층은, 기판 내의 수광부에 대향하는 영역으로서, 축적용량부로부터 소망하는 오프셋 영역만큼 멀어진 영역에 형성된 층이다. 또한, 이 전자 셔터 조정층은, 기판에 제 2의 전위가 인가된 때에 수광부에서 생성된 신호 전하가 기판의 이면측으로 빠져 나가도록 기판의 전위 분포를 조정하는 층이다.

- [0015] 판독 게이트부는, 축적용량부에 축적된 신호 전하를 판독하는 것이다.

- [0016] 수직 전송 레지스터는 판독 게이트부에 의해 판독된 신호 전하를 수직 방향으로 전송하는 것이다.

- [0017] 본 발명의 고체 활상 장치의 제조 방법은, 제 1 도전형의 반도체 기판을 준비하는 공정, 반도체 기판상에 제 2 도전형의 반도체 웨이팅을 형성하는 공정을 갖는다. 또한, 반도체 웨이팅의 표면측에, 수광부, 수광부에 인접하는 축적용량부, 및 판독 게이트부를 통하여 축적용량부에 인접하는 수직 전송 채널을 형성하는 공정을 갖는다. 또한, 반도체 웨이팅을 형성하기 전, 또는 후에, 반도체 기판과 반도체 웨이팅과의 사이의, 수광부에 대향하는 영역으로서, 축적용량부로부터 소망하는 오프셋 영역만큼 멀어진 영역에 제 1 도전형으로 이루어지는 전자 셔터 조정 층을 형성하는 공정을 갖는다. 또한, 축적용량부 및 수광부 상부의 광 입사측에 암전류 억제부를 형성하는 공정을 갖는다. 또한, 기판에, 수광 기간과, 비수광 기간에서 다른 전위를 인가하는 기판 전압 전원을 접속하는 공정을 갖는다.

- [0018] 본 발명의 고체 활상 장치의 구동 방법은, 상술한 본 발명의 고체 활상 장치에 있어서, 기판 전압 전원에 의해, 기판에 제 1의 전위를 인가함에 의해, 수광부에서 생성된 신호 전하의 상기 축적용량부로의 전송을 시작한다. 그리고, 기판 전압 전원에 의해, 반도체 기판에 제 2의 전위를 인가함에 의해, 수광부에서 생성된 신호 전하의 축적용량부로의 전송을 종료함과 함께, 그 후에 수광부에서 생성된 신호 전하를 상기 기판측으로 빠져 나가게 한다.

- [0019] 본 발명의 고체 활상 장치 및 그 구동 방법에서는, 신호 전하의 축적이 이루어지지 않고, 수시로, 축적용량부에 전송되든지, 기판측으로 빠져 나간다. 또한, 기판 전압을 바꿈으로써, 수광부에서 생성된 신호 전하의 축적용량부로의 방류(垂流) 전송, 및 기판측으로의 빠져 나감이 이루어진다.

- [0020] 본 발명의 전자 기기는, 광학 렌즈와, 고체 활상 장치와, 신호 처리 회로를 포함하여 구성된다. 이, 본 발명의 전자 기기에서는, 상술한 본 발명의 고체 활상 장치가 적용된다.

### 발명의 효과

- [0021] 본 발명에 의하면, 비순차 주사 방식이면서, 메커니컬 셔터 등의 소자 외부 셔터가 없는 전자 기기에도 적용할 수 있는 고체 활상 장치를 얻을 수 있다. 이로써, 염가로, 소형화, 및 경량화된 전자 기기를 얻을 수 있다.

### 도면의 간단한 설명

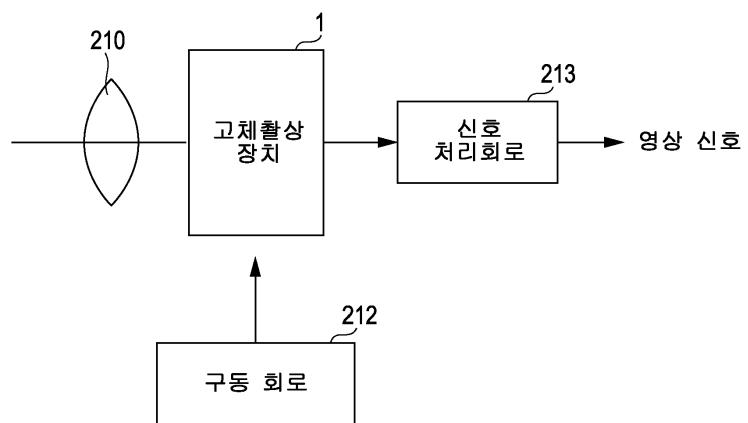

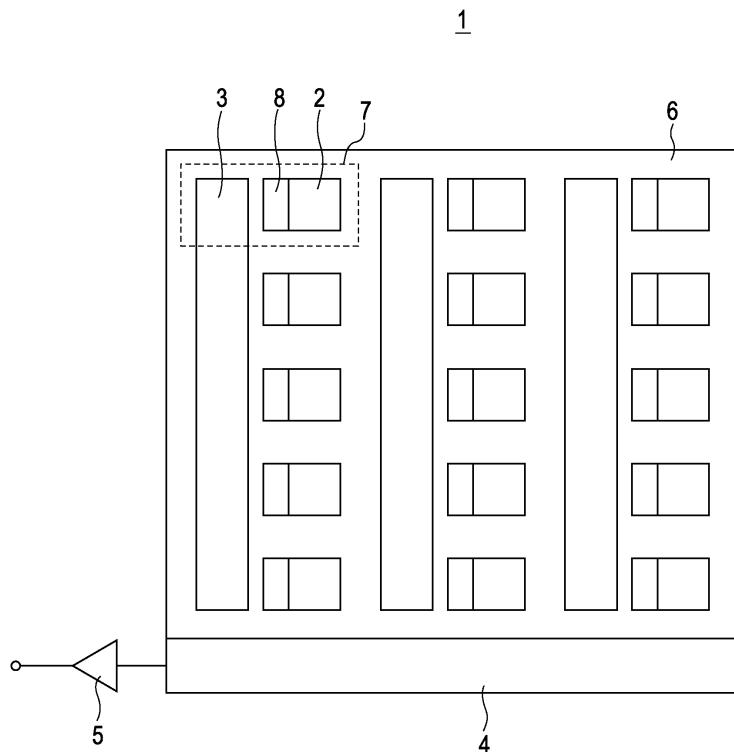

- [0022] 도 1은 본 발명의 제 1의 실시 형태에 관한 고체 활상 장치의 개략 구성도.

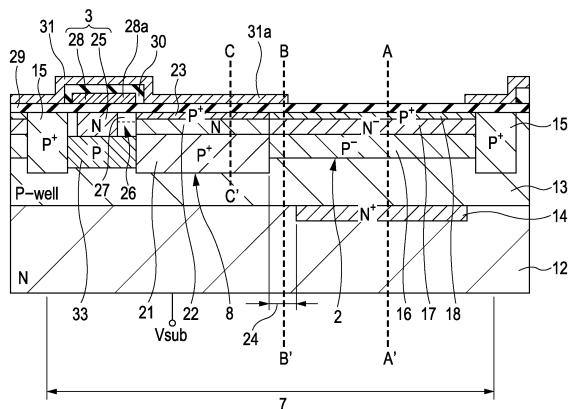

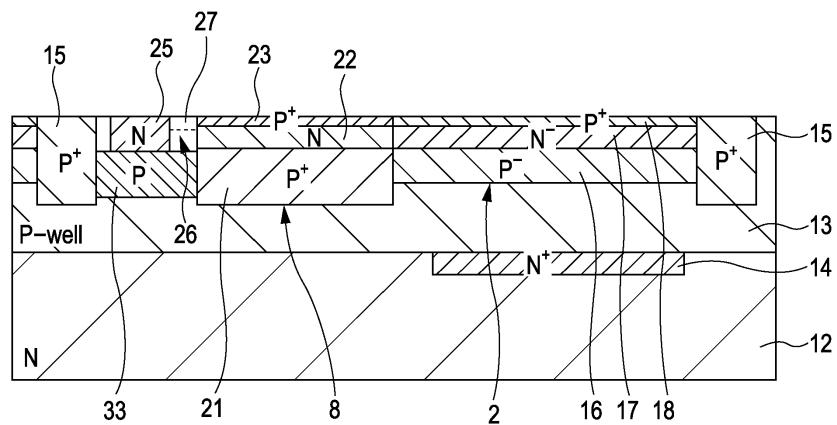

도 2는 본 발명의 제 1의 실시 형태에 관한 고체 활상 장치의 개략 단면 구성도.

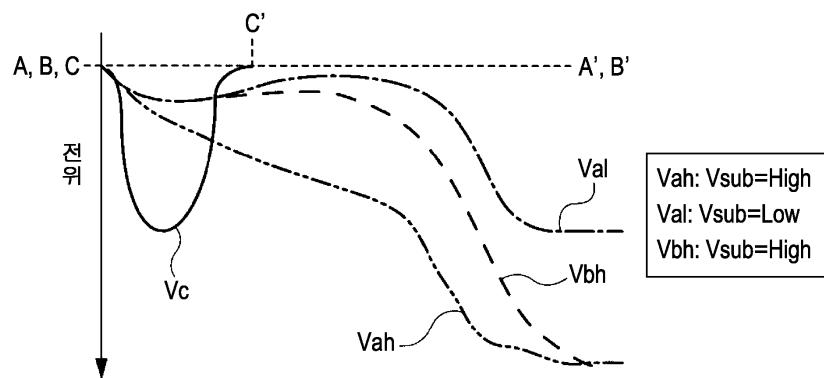

도 3은 본 발명의 제 1의 실시 형태에 관한 고체 활상 장치의 기판의 전위를 도시하는 도면.

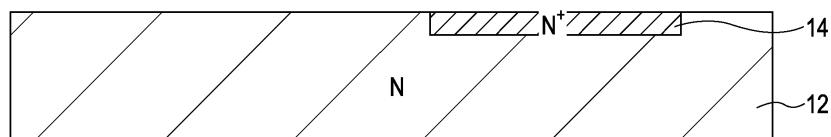

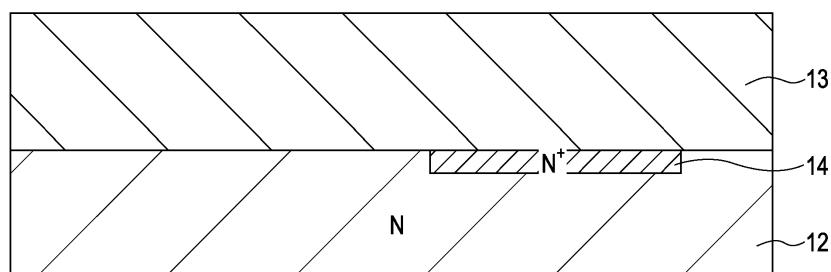

도 4의 A 내지 C는 본 발명의 제 1의 실시 형태에 관한 고체 활상 장치의 제조 공정도(그 1).

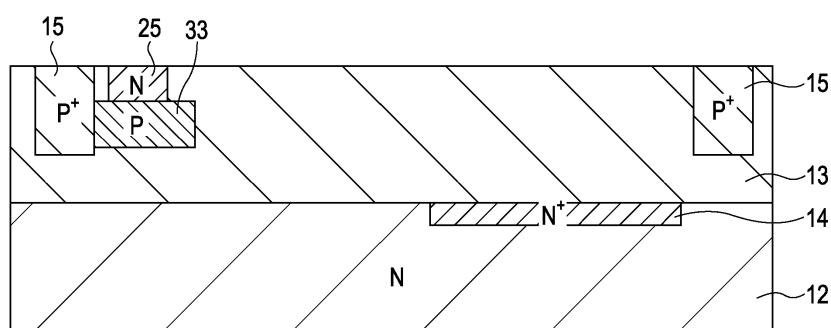

도 5의 D 내지 F는 본 발명의 제 1의 실시 형태에 관한 고체 활상 장치의 제조 공정도(그 2).

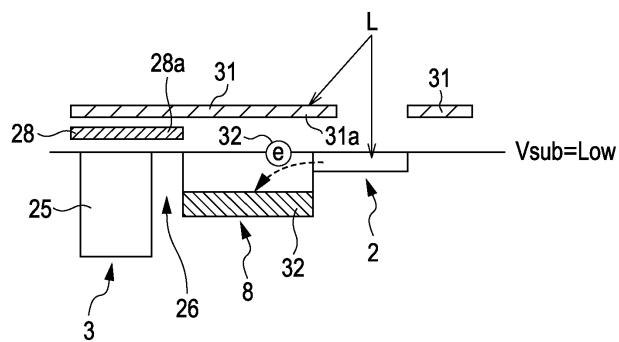

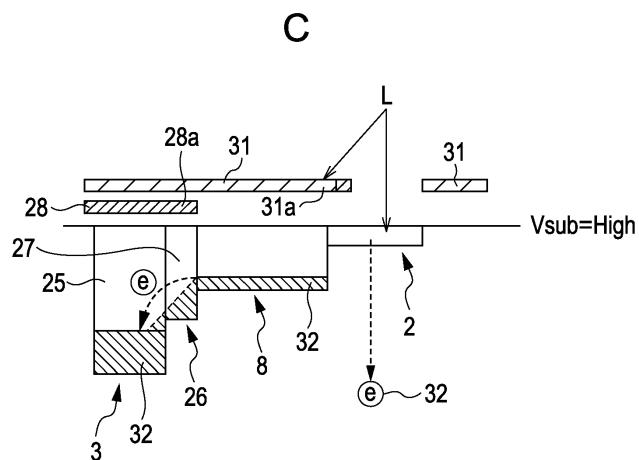

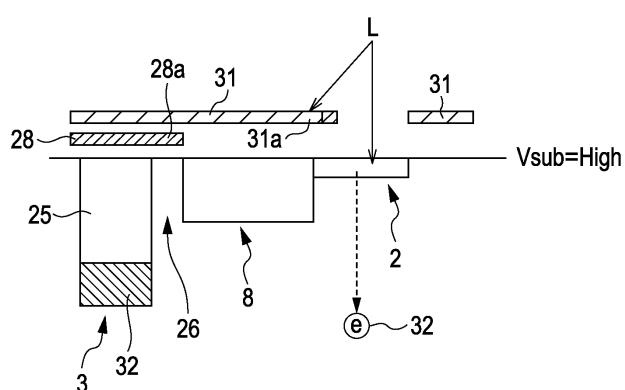

도 6의 A 및 B는 본 발명의 제 1의 실시 형태에 관한 고체 활상 장치의 구동시에 있어서의 신호 전하의 전송의 양상을 도시한 도면(그 1).

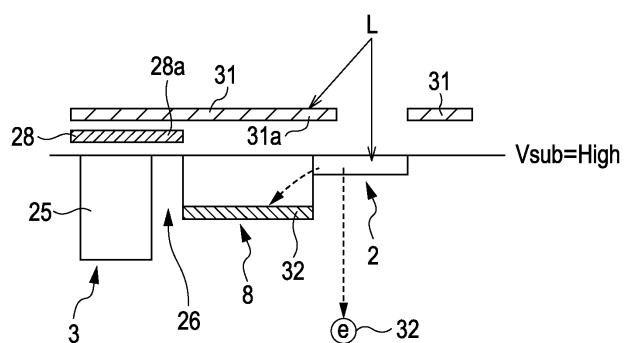

도 7의 C 및 D는 본 발명의 제 1의 실시 형태에 관한 고체 활상 장치의 구동시에 있어서의 신호 전하의 전송의 양상을 도시한 도면(그 2).

도 8은 본 발명의 제 2의 실시 형태에 관한 고체 활상 장치의 개략 단면도.

도 9는 본 발명의 제 3의 실시 형태에 관한 전자 기기의 개략 구성도.

### 발명을 실시하기 위한 구체적인 내용

- [0023] 이하에, 본 발명의 실시 형태에 관한 고체 활상 장치, 고체 활상 장치의 제조 방법, 고체 활상 장치의 구동 방법, 및 전자 기기의 한 예를, 도 1 내지 도 9를 참조하면서 설명한다. 본 발명의 실시 형태는 이하의 순서로 설명한다. 또한, 본 발명은 이하의 예로 한정되는 것이 아니다.

- [0024] 1. 제 1의 실시 형태 : 고체 활상 장치의 예

- [0025] 1.1 고체 활상 장치 전체의 구성

- [0026] 1.2 고체 활상 장치의 단면 구성

- [0027] 1.3 고체 활상 장치의 제조 방법

- [0028] 1.4 고체 활상 장치의 구동 방법

- [0029] 2. 제 2의 실시 형태 : 고체 활상 장치의 예

- [0030] 3. 제 3의 실시 형태 : 전자 기기의 예

- [0031] <1. 제 1의 실시 형태>

- [0032] [1. 1 고체 활상 장치 전체의 구성]

- [0033] 도 1에 본 발명의 제 1의 실시 형태에 관한 CCD형의 고체 활상 장치의 개략 구성도를 도시한다. 도 1에 도시하는 바와 같이, 본 실시 형태의 고체 활상 장치(1)는, 기판(6)에 형성된 복수의 수광부(2)와, 각각의 수광부(2)에 인접하여 형성된 축적용량부(8)와, 수직 전송 레지스터(3)와, 수평전송 레지스터(4) 및 출력 회로(5)를 갖고서 구성되어 있다. 그리고, 하나의 수광부(2) 및 축적용량부(8)와, 그 축적용량부(8)에 인접하는 수직 전송 레지스터(3)에 의해 단위 화소(7)가 구성되어 있다. 본 실시 형태의 고체 활상 장치(1)의 전송 방식은, 수광부(2)와 수직 전송 레지스터(3)로 구성되는 전송부를 나누어서 형성한 IT(Interline Transfer) 방식으로, 주사 방식은, 라인마다 순차 판독을 행하는 인터레이스 주사 방식으로 한다. 단, 인터레이스 주사 방식은, 속아냄 판독, 또는, 1:3, 1:4, 1:5 등 다중 인터레이스 판독을 포함한다.

- [0034] 수광부(2)는, 광전변환 소자, 즉 포토 다이오드에 의해 구성되는 것이고, 신호 전하를 생성하는 것이다. 본 실시 형태에서는, 수광부(2)는, 기판(6)의 수평 방향 및 수직 방향으로, 복수개, 매트릭스형상으로 형성되어 있다.

- [0035] 축적용량부(8)는, 각 수광부(2)에 인접하여 구성되어 있고, 각각의 수광부(2)에서 생성된 신호 전하를 축적하는 것이다.

- [0036] 수직 전송 레지스터(3)는, CCD 구조로 이루어지고, 수직 방향으로 배열된 수광부(2) 및 축적용량부(8)마다, 수직 방향으로 복수 형성된다. 이 수직 전송 레지스터(3)는, 축적용량부(8)에 축적된 신호 전하를 판독하여, 수직 방향으로 전송하는 것이다. 본 실시 형태의 수직 전송 레지스터(3)가 형성되어 있는 전송 스테이지는, 도시하지 않은 전송 구동 펄스 회로로부터 인가되는 전송 구동 펄스에 의해, 예를 들면, 4상(相) 구동되는 구성으로 되어 있다. 또한, 수직 전송 레지스터(3)의 최종단에서는, 전송 구동 펄스가 인가됨에 의해, 최종단에 보존되어 있던 신호 전하는, 수평전송 레지스터(4)에 전송되는 구성으로 되어 있다.

- [0037] 수평전송 레지스터(4)는, CCD 구조로 이루어지고, 수직 전송 레지스터(3)의 최종단의 일단에 형성되는 것이다. 이 수평전송 레지스터(4)가 형성되어 있는 전송 스테이지는, 수직 전송 레지스터(3)에 의해 수직 전송되어 온 신호 전하를, 1수평라인마다 수평 방향으로 전송하는 것이다.

- [0038] 출력 회로(5)는, 수평전송 레지스터(4)에 의해 수평 전송된 신호 전하를 전하 전압 변환함에 의해, 영상 신호로서 출력하는 것이다.

- [0039] 이상의 구성을 갖는 고체 활상 장치(1)에서는, 수광부(2)에 축적된 신호 전하는, 수직 전송 레지스터(3)에 의해, 수직 방향으로 전송되어, 수평전송 레지스터(4) 내로 전송된다. 그리고, 수평전송 레지스터(4) 내로 전송되어 온 신호 전하는, 수평전송 레지스터(4) 내의 신호 전하는, 각각 수평 방향으로 전송되고, 출력 회로(5)를 통하여 영상 신호로서 출력된다.

- [0040] [1. 2 고체 활상 장치의 단면 구성]

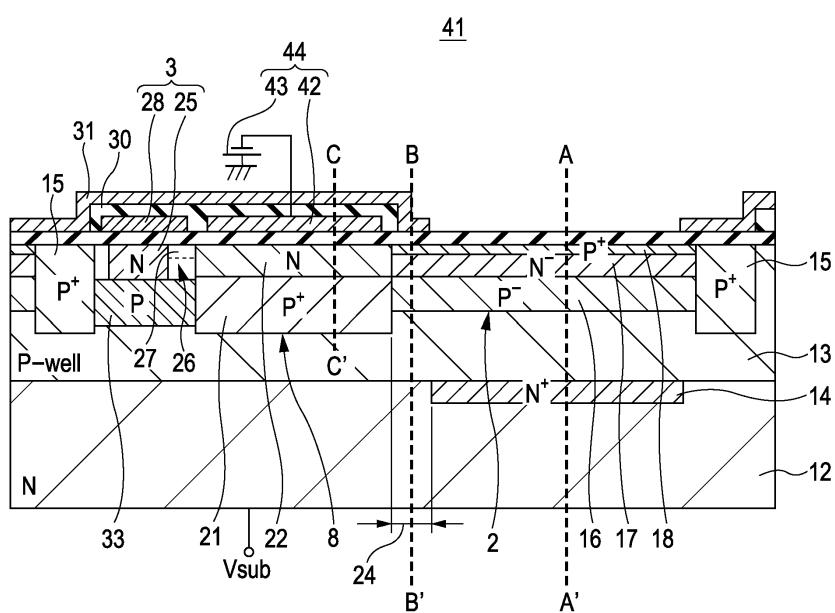

- [0041] 도 2에, 본 실시 형태의 고체 활상 장치(1)에서의 1화소분의 개략 단면 구성을 도시한다. 본 실시 형태에서는, 본 발명에서의 제 1 도전형을 n형으로 하고, 제 2 도전형을 p형으로 하여 설명한다.

- [0042] 본 실시 형태의 고체 활상 장치(1)는, 반도체 기판(12)과, 반도체 웰층(13)과, 도시하지 않은 기판 전압 전원을 포함하여 구성되어 있다. 또한, 반도체 웰층(13)에는, 화소(7)를 구성하는 수광부(2), 축적용량부(8), 판독 게이트부(26), 수직 전송 레지스터(3), 전자 셔터 조정층(14), 제 1 및 제 2의 암전류 억제부(18, 23)가 형성되어 있다.

- [0043] 반도체 기판(12)은, 예를 들면 실리콘으로 이루어지는 n형의 CZ 기판에 의해 구성되어 있다. 또한, 반도체 기판(12)에는, 도시하지 않은 기판 전압 전원이 접속되어 있다. 기판 전압 전원은, 수광부(2)에서의 수광 기간파, 축적용량부(8)로부터 수직 전송 레지스터(3)에의 신호 전하의 편도, 및 수직 전송 레지스터(3)에 의한 신호 전하의 전송 기간에서, 다른 기판 전압(V<sub>sub</sub>)을 반도체 기판(12)에 공급한다. 이 기판 전압 전원은 소자의 외부에 갖을 수가 있지만, 고체 콜상 장치(1) 내부에 기판 전압 발생 회로로서 갖는 구성도 가능하다.

- [0044] 반도체 웨이퍼(13)은, 반도체 기판(12)상에 형성된 P<sup>-</sup>형의 에피택셜층에 의해 구성되어 있다. 본 실시 형태예에서, 반도체 웨이퍼(13)의, 반도체 기판(12)에 면하는 측과는 반대측의 면이, 수광면이 된다.

- [0045] 수광부(2)는, 제 1의 암전류 억제부(18)와 n형의 저농도 불순물 영역(N<sup>-</sup>영역)(17)과, p형의 저농도 불순물 영역(P<sup>-</sup>영역)(16)으로 구성되어 있다. N<sup>-</sup>영역(17)은, 반도체 웨이퍼(13)의 수광면측에 형성되어 있다. P<sup>-</sup>영역(16)은, N<sup>-</sup>영역(17)에 대해 수광면과는 반대측의 영역에, N<sup>-</sup>영역에 접하도록 형성되어 있다. 즉, 본 실시 형태예의 수광부(2)는, N<sup>-</sup>영역(17)과 P<sup>-</sup>영역(16)의 접합면을 갖고서 구성되는 포토 다이오드로 구성되어 있다. 수광부(2)에서는, 수광면으로부터 입사한 광이 접합면에 의해 광전변환하고, 광량에 응한 신호 전하가 생성된다.

- [0046] 축적용량부(8)는, n형의 불순물 영역(N영역)(22)와 p형의 고농도 불순물 영역(P<sup>+</sup>영역)(21)으로 구성되어 있고, 반도체 웨이퍼(13)에 형성된 수광부(2)에 인접하여 형성되어 있다. N영역(22)은, 반도체 웨이퍼(13)의 수광면측으로서, 수광부(2)를 구성하는 N<sup>-</sup>영역(17)에 대해 수평 방향으로 인접하는 영역에 형성되어 있다. P<sup>+</sup>영역(21)은, N영역(22)에 대해 수광면과는 반대측의 영역에, N영역(22)에 접하도록 형성되어 있다. 즉, N영역(22)과 P<sup>+</sup>영역(21)의 접합면에 의해 전위의 우물이 형성되고, 수광부(2)에서의 생성된 신호 전하가, 이 N영역(22)에서의 축적된다. 여기서, 축적용량부(8)의 정전 포텐셜은, 수광부(2)의 정전 포텐셜보다도 깊어지도록 구성되어 있다.

- [0047] 제 1의 암전류 억제부(18)는, 반도체 웨이퍼(13)에 형성된 수광부(2)의 수광면측의 최표면에 형성되어 있다. 또한, 제 2의 암전류 억제부(23)는, 축적용량부(8)의 수광면측의 최표면에 형성되어 있다. 이 제 1 및 제 2의 암전류 억제부(18, 23)는, p형의 고농도 불순물 영역으로 이루어지고, 수광부(2)로부터 축적용량부(8)에 걸쳐서 일체로 형성되어 있다. 제 1 및 제 2의 암전류 억제부(18, 23)에서는, 수광면의 계면에서 발생하는 암전류를 p형의 고농도 불순물 영역의 다수 캐리어인 정공에 의해 흡수한다. 즉, 본 실시 형태예의 수광부(2) 및 축적용량부(8)에서는, HAD(Hole-Accumulation Diode; HAD : 등록 상표) 구조, 이른바 매입 포토 다이오드가 구성되어 있다.

- [0048] 전자 셔터 조정층(14)은, 반도체 기판(12)의, 반도체 웨이퍼(13)에 면하는 측의 수광부(2)에 대향하는 영역에, n형의 고농도 불순물 영역에 의해 형성되어 있다. 또한, 이 전자 셔터 조정층(14)은, 축적용량부(8)가 형성된 영역부터, 수광부(2)측으로, 수평 방향으로 소정의 오프셋 영역(24)만큼 떨어져서 형성되어 있다. 이 오프셋 영역(24)은, 후술하는 바와 같이, 반도체 기판(12), 및 반도체 웨이퍼(13)의 전위 분포가 최적화되도록 결정되는 것이다.

- [0049] 판독 게이트부(26)는, 판독 채널(27)과, 판독 전극(28A)으로 구성된다. 판독 채널(27)은, 반도체 웨이퍼(13) 표면에 형성된 축적용량부(8)에 인접하는 영역에, p형 또는 n형의 저농도 불순물 영역에 의해 형성되어 있다. 또한, 판독 전극(28A)은, 판독 채널(27) 상부에 게이트 절연막(29)을 통하여 형성되어 있다.

- [0050] 수직 전송 레지스터(3)는, 수직 전송 채널(25)과, 수직 전송 전극(28)으로 구성되어 있다. 수직 전송 채널(25)은, 판독 채널(27)에 인접하는 영역에, n형의 농도 불순물 영역에 의해 구성되어 있다. 이들의 수직 전송 채널(25) 아래에는, p형의 불순물 영역에 의해 구성된 전송부 반도체 웨이퍼(33)이 형성되어 있다.

- [0051] 수직 전송 전극(28)은, 반도체 웨이퍼(13)에 형성된 수직 전송 채널(25) 상부에, 게이트 절연막(29)을 통하여 형성되어 있다. 도시하지 않지만, 수직 전송 전극(28)은 수평 방향으로 복수개 형성되어 있고, 축적용량부(8)에 인접하는 부분에서는, 판독 전극(28A)을 겹하도록 형성되어 있다. 수직 전송 레지스터(3)에서는, 판독 게이트부(26)에 의해 수직 전송 채널(25)에 판독된 신호 전하는, 수평 방향으로 형성된 복수개의 수직 전송 전극(28)에, 예를 들면 4상의 수직 전송 펄스가 인가됨에 의해, 순차적으로 수직 방향으로 전송된다.

- [0052] 본 실시 형태예에서는, 게이트 절연막(29)은, 반도체 웨이퍼(13) 상부 전면에 공통으로 형성되어 있다. 그리고, 이들의 화소(7)를 구성하는 수광부(2), 축적용량부(8), 수직 전송 레지스터(3)를 둘러싸는 영역에는, p형의 고농도 불순물 영역에 의해, 인접하는 화소를 분리하는 채널 스탶부(15)가 형성되어 있다.

- [0053] 차광층(31)은, 수직 전송 전극(28) 등의 전극을 포함하는 반도체 웨이퍼(13) 상부의, 수광부(2)의 개구 영역을 제외한 면을, 층간 절연막(30)을 통하여 피복하도록 형성되어 있다. 이때, 축적용량부(8) 상부의 차광층(31)의 단부는, 수광부(2)측에 소정의 영역만큼 연장하는 돌출부(31a)를 갖도록 형성되어 있다.

- [0054] 다음에, 도 3을 이용하여, 본 실시 형태예의 고체 활상 장치(1)가 갖는 포텐셜 프로파일에 관해 설명한다. 이하의 설명에서, 반도체 기판(12)과 반도체 웨이퍼(13)을 구별하지 않고 설명하는 경우에는 「기판」이라고 총칭한다.

- [0055] 도 3은, 도 2의 A-A', B-B', C-C'선상에 따른 기판의 전위를 도시한 전위 분포도이다. A-A'는, 수광부(2)와 전자 셔터 조정층(14)을 포함하는, 기판의 수직 방향에서의 전위 분포이고, B-B'는 수광부(2)와, 오프셋 영역(24)을 포함하는, 기판의 수직 방향에서의 전위 분포이다. 또한, C-C'는, 축적용량부(8)를 포함하는, 기판의 수직 방향에서의 전위 분포이다.

- [0056] 도 3에서 도시하는 1점쇄선은, 기판 전압(Vsub)을 제 1의 전위(이하, Low)로 설정한 때의, A-A'선상에 따른 전위(Val)이다. 또한, 도 3에서 도시하는 2점쇄선은, 기판 전압(Vsub)을 제 1의 전위보다도 높은 전위인 제 2의 전위(이하, High)로 설정한 때의, A-A'선상에 따른 전위(Vah)이다. 또한, 도 3에 도시하는 파선은, 기판 전압(Vsub)을 High로 설정한 때의 B-B'선상에 따른 전위(Vbh)이다. 또한, 도 3에 도시하는 실선은, C-C'선상에 따른 전위(Vc)이다.

- [0057] 도 3에 도시하는 바와 같이, 기판 전압(Vsub)이 Low로 설정되어 있는 경우에는, A-A'선상에 따른 전위(Val)는, 수광부(2)를 구성하는 N<sup>-</sup>영역(17)에서의 전위가 P<sup>-</sup>영역(16)이나 반도체 웨이퍼(13)보다도 깊어지도록 구성되어 있다. 즉, 수광부(2)의 N<sup>-</sup>영역(17)에서, 얇은 전위의 우물이 형성되어 있다. 이 N<sup>-</sup>영역(17)의 불순물 농도는, 종래 사용되고 있는 일반적인 HAD 구조를 갖는 수광부보다도 1V 정도 얕은 포텐셜로 설정되어 있다.

- [0058] 또한, 기판 전압(Vsub)이 Low인 경우, 도시하지 않지만, B-B'선상에 따른 기판의 전위도, A-A'선상에 따른 전위(Val)와 마찬가지가 된다.

- [0059] 다음에, 기판 전압(Vsub)이 High로 설정되어 있는 경우에는, A-A'선상에 따른 전위(Vah)는, n형의 고농도 불순물 영역으로 이루어지는 전자 셔터 조정층(14)의 효과로, 전체적으로 깊은 쪽으로 끌려간다. 그리고, 반도체 기판(12)측을 향하여 보다 깊어지도록, 전위(Vah)가 변화된다. 또한, B-B'선상에서는, 오프셋 영역(24)에 의해 전자 셔터 조정층(14)이 형성되어 있지 않기 때문에, 반도체 기판(12)측에서 약간 전위가 깊어질 뿐으로, 수광부(2) 부근에서의 전위(Vbh)는, 기판 전압(Vsub)이 Low인 때와 개략 동등한 값을 유지하고 있다.

- [0060] 또한, C-C'선상에 따른 전위(Vc)는, 축적용량부(8)를 구성하는 N영역(22)과, 비교적 불순물 농도가 진한 P<sup>+</sup>영역(21)의 접합면의 효과에 의해, 수광부(2)보다도 깊은 전위의 우물이 형성되는 구성으로 되어 있다.

- [0061] [1. 3 고체 활상 장치의 제조 방법]

- [0062] 도 4, 도 5를 이용하여, 이상의 구성을 갖는 고체 활상 장치의 제조 방법을 설명한다. 도 4에서, 도 2에 대응하는 부분에는, 동일 부호를 붙이고 중복 설명을 생략한다.

- [0063] 우선, 도 4의 A에 도시하는 바와 같이, 예를 들면 CZ 기판 등의 n형의 반도체 기판(12)을 준비하고, 그 반도체 기판(12) 상부의 소정의 위치에, n형의 불순물을 고농도로 이온 주입함에 의해, 전자 셔터 조정층(14)을 형성한다.

- [0064] 다음에, 도 4의 B에 도시하는 바와 같이, 에피택셜 성장법을 이용하여, P<sup>-</sup>형의 에피택셜 성장층으로 이루어지는 반도체 웨이퍼(13)을 형성한다.

- [0065] 다음에, 도 4의 C에 도시하는 바와 같이, 반도체 웨이퍼(13)의 수직 전송 레지스터(3)가 형성되는 영역의 소정의 깊이에, p형의 불순물을 이온 주입함에 의해, 전송부(轉送部) 반도체 웨이퍼(33)을 형성한다. 전송부 반도체 웨이퍼(33)상의 소정의 영역에, n형의 불순물을 이온 주입함에 의해, 수직 전송 채널(25)을 형성한다. 또한, 수직 전송 채널(25)에 인접하는 영역에, p형의 불순물을 이온 주입함에 의해, 채널 스트립부(15)를 형성한다.

- [0066] 다음에, 도 5의 D에 도시하는 바와 같이, 반도체 웨이퍼(13) 표면의 소정에 위치에, p형의 불순물, 및 n형의 불순물을 저농도로 이온 주입함에 의해, P<sup>-</sup>영역(16) 및 N<sup>-</sup>영역(17)으로 이루어지는 수광부(2)를 형성한다. 또한, 반도체 웨이퍼(13) 표면의 소정의 위치에, p형의 불순물을 고농도로 이온 주입하고, n형의 불순물을 이온 주입함에

의해,  $P^+$ 영역(21) 및 N영역(22)으로 이루어지는 축적용량부(8)를 형성한다. 그리고, 축적용량부(8) 및 수광부(2)가 형성된 영역의 반도체 웨이퍼(13) 최표면에, p형의 불순물을 고농도로 이온 주입함에 의해, 제 1 및 제 2의 암전류 억제부(18, 23)를 형성한다. 그리고, 축적용량부(8)가 형성된 영역과, 수직 전송 채널(25)이 형성된 영역 사이의 영역이, 판독 게이트부(26)를 구성하는 판독 채널(27)이 된다.

[0067] 다음에, 도 5의 E에 도시하는 바와 같이, 반도체 웨이퍼(13) 상부에 게이트 절연막(29)을 형성하고, 게이트 절연막(29)상에, 수직 전송 전극(28)을 형성한다. 수직 전송 전극(28)은, 수직 전송 채널(25) 상부에, 복수 수평 방향으로 복수개 형성한다. 또한, 도 5의 E에 도시하는 바와 같이, 판독 채널(27)에 인접하는 수직 전송 채널(25) 상부의 수직 전송 전극(28)은, 판독 채널(27) 상부까지 연장하여 형성한다. 이로써, 수직 전송 전극(28)이 판독 전극(28A)을 겹한 구성으로 할 수 있다.

[0068] 그리고, 전극이 형성된 후, 수광부(2)를 제외한 영역에, 충간 절연막(30)을 통하여 차광층(31)을 형성하고, 도 2에 도시하는 고체 활상 장치(1)가 형성된다. 이 차광층(31)은, 소망하는 배선층을 겹하는 구성으로 하여도 좋다.

[0069] 그 후, 차광층(31)의 상층에는, 소망하는 배선층이나, 평탄화막, 컬러 필터, 온 칩 렌즈 등, 종래의 고체 활상 장치와 같은 층이 형성되고, 본 실시 형태예의 고체 활상 장치(1)가 완성된다.

[0070] 본 실시 형태예에서는, 반도체 웨이퍼(13)을,  $P^-$ 형의 에피택셜 성장층에 의해 구성하는 예로 하였지만,  $N^-$ 형의 에피택셜 성장층으로 구성하여도 좋다. 그 경우에는, 상기  $N^-$ 형의 에피택셜 성장층 내에, 매트릭스형상으로 배치된 복수의 화소(7)를 포함하도록 p형의 불순물을 이온 주입하여 P웨이퍼(반도체 웨이퍼(13)에 상당한다)을 형성한다. 또한, 수광부(2)를 구성하는  $P^-$ 영역의 프로파일을 기능 실현상, 본 실시 형태예와 다르도록 할 필요가 있다.

[0071] 또한, 전자 셔터 조정층(14)은, 반도체 웨이퍼(13)을 형성한 후,  $n$ 형의 불순물을 고에너지로 고농도로 이온 주입 함에 의해 형성하여도 좋다. 또한, 본 실시 형태예에서는, 전자 셔터 조정층(14)은, 반도체 기판(12)측에 매입하여 형성하였지만, 반도체 기판(12)에 접하도록 형성하여도 좋다.

[0072] 또한, 본 실시 형태예에서는, 제 1 및 제 2의 암전류 억제부(18, 23)를 한번에 형성하는 예로 하였지만, 나누어서 형성하여도 좋고, 또한, 수직 전송 전극(28)이 형성된 후에 형성하여도 좋다.

[0073] 또한, 본 실시 형태예에서는, 게이트 절연막(29)을, 반도체 웨이퍼(13) 전면에 형성하는 예로 하였지만, 수직 전송 채널(25) 및 판독 채널(27) 상부의 게이트 절연막(29)과, 수광부(2)나, 축적용량부(8)상에 형성되는 다른 절연막을 제각기 형성하여도 좋다.

[0074] 또한, 수광부(2)나, 축적용량부(8)는, 도 5의 E에 도시하는 공정의 후에 형성하여도 좋다.

#### [1. 4 고체 활상 장치의 구동 방법]

[0076] 다음에, 본 실시 형태예의 고체 활상 장치(1)의 구동 방법에 관해 설명한다. 우선, 본 실시 형태예의 고체 활상 장치(1)에서의 실제의 구동에 앞서서, 수광부(2) 및 축적용량부(8)에서의 신호 전하의 생성, 축적의 원리를, 도 3을 이용하여 설명한다.

[0077] 도 3에 도시하는 바와 같이, 기판 전압(V<sub>sub</sub>)이 Low로 설정되어 있는 경우에는, A-A'선상에 따른 전위(V<sub>a1</sub>)는,  $N^-$ 영역(17)에서의 전위가  $P^-$ 영역(16)이나 반도체 웨이퍼(13)보다도 깊게 되어 있다. 또한, 기판 전압(V<sub>sub</sub>)이 Low인 경우, 도시하지 않지만, B-B'선상에 따른 전위도, A-A'선상에 따른 전위(V<sub>a1</sub>)와 마찬가지가 된다. 또한, C-C'선상에 따른 전위(V<sub>c</sub>)는, 축적용량부(8)를 구성하는 N영역(22)과  $P^+$ 영역(21)의 접합면의 효과로, 수광부(2)보다도 깊은 전위의 우물이 형성되어 있다.

[0078] 이 때문에, 기판 전압(V<sub>sub</sub>)이 Low로 설정되어 있을 때 수광부(2)에서 생성된 신호 전하는, 수광부(2)에 축적되는 일 없이, 방류적으로 축적용량부(8)로 전송되고, 축적용량부(8)에서 축적 보존된다.

[0079] 다음에, 기판 전압(V<sub>sub</sub>)이 High로 설정되어 있는 경우에는, A-A'선상에 따른 전위(V<sub>ah</sub>)는,  $n$ 형의 고농도 불순물 영역에 의해 전자 셔터 조정층(14)이 형성되어 있기 때문에, 전위는 전체적으로 깊은 쪽으로 끌려간다. 또한, B-B'선상에서는, 전자 셔터 조정층(14)이 형성되어 있지 않기 때문에, 반도체 기판(12)측에서 약간 전위가 깊어질 뿐이고, 수광부 부근에서의 전위(V<sub>bh</sub>)는, 기판 전압(V<sub>sub</sub>)이 Low인 때와 변하지 않는다.

[0080] 이 때문에, 기판 전압(V<sub>sub</sub>)이 High로 설정되어 있을 때, 수광부(2)에서 생성된 신호 전하는, A-A'선상에 따른

전위(Vah)가, B-B'선상에 따른 전위(Vbh)보다도 깊게 형성되기 때문에, 축적용량부(8)에 전송되지 않는다. 또한, A-A'선상에 따른 전위(Vah)는, 전자 셔터 조정층(14)의 효과로, P<sup>-</sup>형의 반도체 웨이(13)의 배리어 이(가) 압하되고, 반도체 기판(12)측을 향하여 깊게 되어 있다. 이 때문에, 수광부(19)에서 생성된 신호 전하는 반도체 기판(12)측으로 빠져 나간다. 즉, 기판 전압(Vsub)이 High로 설정되어 있는 경우에는, 수광부(2)에서 광전변환된 신호 전하는, 축적용량부(8)에 흘러 들어가지 않고, 반도체 기판(12)측으로 빠져 나간다.

[0081] 또한, 이때, B-B'선상에 따른 전위(Vbh)중, 수광부(2) 부근에서의 전위가 오프셋 영역(24)의 효과에 의해, 기판 전압(Vsub)이 Low인 때와 가까운 값으로 유지된다. 이로써, 축적용량부(20)에 축적 보존된 신호 전하가, 수광부(19)측으로 역류하는 일이 없다. 또한, 이로써, 축적용량부(8)에 축적된 신호 전하는, 기판 전압(Vsub)이 High가 되어도, 수광부(2)에서의 전위(Vc)가 얇은 위치 부근까지의 신호 전하량을 보존할 수 있다.

[0082] 이상의 신호 전하의 생성, 축적의 원리에 의거하여, 본 실시 형태예의 고체 활상 장치의 구동 방법을 도 6, 도 7을 이용하여 설명한다. 도 6, 도 7은, 본 실시 형태예의 고체 활상 장치(1)에서의, 1화소분의, 수광부(2), 축적용량부(8), 판독 게이트부(26), 수직 전송 레지스터(3)에서의 전위의 우물을 개략적으로 도시하고, 신호 전하의 전송의 양상을 개략적으로 도시한 것이다. 도 6, 도 7에서, 도 2에 대응하는 부분에는 동일 부호를 붙이고 중복 설명을 생략한다.

[0083] 우선, 기판 전압(Vsub)을 Low로 한다. 이로써, 신호 전하의 생성 및 축적이 전화소 동시에 시작된다. 이하, 이 동작이 행하여지는 기간을 「수광 기간」이라고 한다.

[0084] 도 6의 A에 도시하는 바와 같이, 수광 기간시에는, 광(L)이 수광부(2)에 입사하고 광전변환함으로써 생성된 신호 전하(32)는, 기판 전압(Vsub)이 Low이기 때문에, 방류적으로 축적용량부(8)에 축적 보존된다. 이로써, 고체 활상 장치(1)의 전화소에서, 동시에 수광부(2)에서 광전변환된 신호 전하(32)가, 축적용량부(8)에 축적 보존된다.

[0085] 또한, 수광 기간중, 강하게 과잉한 광량이 수광부에 입사한 경우에는, 과잉한 광량에 의해 생성된 신호 전하(32)는, 반도체 기판(12)측으로 빠져 나간다.

[0086] 다음에, 도 6의 B에 도시하는 바와 같이, 기판 전압을 High로 한다. 이로써, 신호 전하(32)의 축적이 전화소 동시에 종료하고, 신호 전하의 판독, 전송이 행하여진다. 이하, 이 동작이 행하여지는 기간을 「전송 기간(비수광 기간)」이라고 한다.

[0087] 도 6의 B에 도시하는 바와 같이, 전송 기간시에는, 광(L)이 수광부(2)에 입사하고 광전변환함으로써 생성된 신호 전하(32)는, 기판 전압(Vsub)이 High이기 때문에, 반도체 기판(12)측으로 빠져 나가고 축적용량부(8)에는 전송되지 않는다. 즉, 기판 전압을 High로 함에 의해, 전화소 동시에, 수광 기간이 종료된다.

[0088] 그 후, 도 7의 C에 도시하는 바와 같이, 판독 전극(28A)을 겸하는 수직 전송 전극(28)에 판독 전압을 인가함에 의해, 축적용량부(8)에 축적 보존되어 있던 신호 전하(32)를 수직 전송 채널에 판독한다. 이 축적용량부(8)로부터의 신호 전하(32)의 판독은, 통상의 CCD형의 고체 활상 장치에서의 수광부로부터의 신호 전하의 판독과 같은 인터레이스 주사 방식을 이용한다. 예를 들면 2라인 걸러서의 인터레이스 판독이나 3라인 걸러서, 4라인 걸러서 등의 인터레이스 판독을 행한다. 판독을 기다리게 되는 라인의 화소 신호 전하는 축적용량부에서 판독까지 보존된다.

[0089] 그리고, 도 7의 D에 도시하는 바와 같이, 수직 전송 전극(28)에, 예를 들면 4상의 전송 필스를 인가함에 의해, 수직 전송 채널(25)에 판독된 신호 전하(32)를 수직 방향으로 전송한다. 이 축적용량부(8)로부터의 신호 전하(32)의 판독, 전송은, 통상의 CCD형의 고체 활상 장치에서의 수광부로부터의 신호 전하의 판독, 전송과 같은 인터레이스 주사 방식을 이용한다.

[0090] 예를 들면, 1:2 인터레이스 주사 방식을 이용하는 경우는, 우선, 2N+1(N=0, 1, 2, 3 ...)행(라인)의 화소에서의 신호 전하의 판독, 및 전송이 행하여진다. 그리고, 다음의 필드에서 2N(N=0, 1, 2, 3 ...)행의 화소에서의 신호 전하의 판독, 및 전송이 행하여진다. 이와 같이, 1:2 인터레이스 주사 방식에서는, 2회로 나누어서 전화소의 신호 전하가 판독되고, 전송된다.

[0091] 마찬가지로, 1:3 인터레이스 주사 방식을 이용하는 경우는, 우선, 1번째의 필드에서 3N+1(N=0, 1, 2, 3 ...)행의 화소에서의 신호 전하의 판독, 및 전송을 행한다. 계속해서, 2번째의 필드에서, 3N+2(N=0, 1, 2, 3 ...)행, 3번째의 필드에서, 3N+3(N=0, 1, 2, 3 ...)행의 화소에서의 신호 전하를 차례로 판독, 전송을 행한다. 이와 같이, 1:3 인터레이스 주사 방식에서는, 3회로 나누어서 전화소의 신호 전하가 판독되고, 전송된다.

- [0092] 이와 같이, 판독 회수를 나눔으로써, 라인마다의 신호 전하(32)가 수직 전송시에 사용할 수 있는 전송 스테이지 수를 증가할 수 있기 때문에, 수직 전송 레지스터(3)에서의 취급 전하량을 증가할 수 있다.

- [0093] 본 실시 형태예에서는, 이상과 같은 전송 기간중에서도, 수광부(2)에서는 계속해서 신호 전하가 생성되고 있지만, 기판 전압(Vsub)이 High로 되어 있기 때문에, 이 전송 기간중에 광전변환된 신호 전하는, 수시로, 반도체 기판(12)측으로 빠져 나가고 있다.

- [0094] 수직 전송 레지스터(3)에 의해 수직 방향으로 전송된 신호 전하(32)는, 그 후, 수평전송 레지스터(4)에 의해 수평 방향으로 전송되고, 출력 회로(5)를 통하여 영상 신호가 되어 출력된다.

- [0095] 이와 같이, 본 실시 형태의 고체 활상 장치(1)에서는, 기판 전압(Vsub)을 바꿈으로써, 수광 기간에서 수광부(2)에서 생성된 신호 전하(32)는 방류적으로 축적용량부(8)로 전송되고, 전송 기간에서 수광부(2)에서 생성된 신호 전하는 기판측으로 빠져 나간다. 즉, 전자 셔터 조정층(14) 및 오프셋 영역(24)의 효과에 의해, 기판 전압(Vsub)을 변화시킬 뿐으로, 전자 셔터의 기능을 얻을 수 있다. 이로써, 비순차 주사 방식(본 실시 형태예에서는 인터레이스 주사 방식)이면서, 메카 셔터 등의 소자 외부 셔터가 없는 전자 기기에 적용할 수 있는 CCD형의 고체 활상 장치를 얻을 수 있다.

- [0096] 또한, 도 6의 A에서 도시한 바와 같이, 수광부(2)에서 생성된 신호 전하(32)는, 축적용량부(8)에 방류적으로 전송되기 때문에, 수광부(2)와 축적용량부(8) 사이에 전송 전극이 필요없고, 구조가 간이하다. 이 때문에, 수광부(2)의 개구나, 축적용량부(8) 등의 면적을 크게 취할 수 있고, 감도나 다이내믹 레인지의 증대가 가능해진다. 또한, 수광부(2)와 축적용량부(8) 사이에 전송 전극이 없기 때문에, 신호 전하의 전송중에, 실리콘으로 이루어지는 기판 계면이 공핍화되지 않기 때문에, 암전류의 증가를 억제할 수 있다.

- [0097] 또한, 수광부(2)는, 분광 감도 특성을 확보하기 위해, 공핍층을 늘릴 필요가 있고, 정전 포텐셜이 깊은 위치가 기판 표면부터 깊은 위치에 설정되기 쉽다. 그런데, 축적용량부(8)는, 신호 전하의 축적·보존에 특화할 수 있기 때문에, 정전 포텐셜의 가장 얕은 위치를, 기판 표면부터 얕은 위치에 설정 가능하고, 이로써, 판독 전압의 저전압화가 행하기 쉽다.

- [0098] 또한, 종래의 고체 활상 장치에서는, 수광부에서, 신호 전하의 생성과 축적이 행하여지고 있다. 본 실시 형태의 고체 활상 장치(1)에 의하면, 수광부(2)에서 신호 전하의 축적을 행하지 않기 때문에, 수광부(2)의 정전 포텐셜을, 종래와 같은, 수광부에서 축적도 행하는 수광부의 정전 포텐셜에 비교하여 수볼트 얕게 형성할 수 있다. 이로써, 수광부(2)의 전계를 저감할 수 있다. 이로써, 전계 기인의 암전류 증을 저감할 수 있다.

- [0099] 또한, 본 실시 형태의 고체 활상 장치(1)에서는, 수광부(2) 및 축적용량부(8)에는, HAD 구조에 의한 제 1 및 제 2의 암전류 억제부(18, 23)가 형성되어 있고, 표면이 항상 정공으로 채워지고 있다. 이 때문에, 기판을 구성하는 실리콘이나, 게이트 절연막(29) 등을 구성하는 산화막 계면으로부터 발생하는 암전류를 억제할 수 있다.

- [0100] 또한, 본 실시 형태에 의하면, 축적용량부(8)는 차광층(31)에 의해 차광되어 있다. 이로써, 도 6, 도 7에 도시하는 바와 같이, 수광 기간중, 및 수광 전후의 기간에서도, 광(L)이 축적용량부(8)에 투과하고, 광전변환하는 것을 막고 있다.

- [0101] 또한, 본 실시 형태에 의하면, 차광층(31)이, 축적용량부(8)로부터 수광부(2)측으로 돌출부(31a)를 갖도록 형성되어 있다. 이 때문에, 기판 전압(Vsub)이 High가 되어, 수광 기간이 종료된 후도, 입사하는 광(L)중, 축적용량부(8) 부근에 입사한 광이, 축적용량부(8)에 일종의 스미어로서 들어가는 것이 억제된다.

- [0102] 또한, 본 실시 형태에 의하면, 도 2에 도시하는 바와 같이 축적용량부(8)를 구성하는 N영역(22)의 하부에, 비교적 고농도의 P<sup>+</sup>영역(21)을 갖음으로써, N영역(22)과 P<sup>+</sup>영역(21)의 접합면에 형성되는 공핍층 용량을 증대할 수 있다. 또한 이로써, 축적용량부(8)에의 스미어의 혼입이 억제된다.

- [0103] <2. 제 2의 실시 형태>

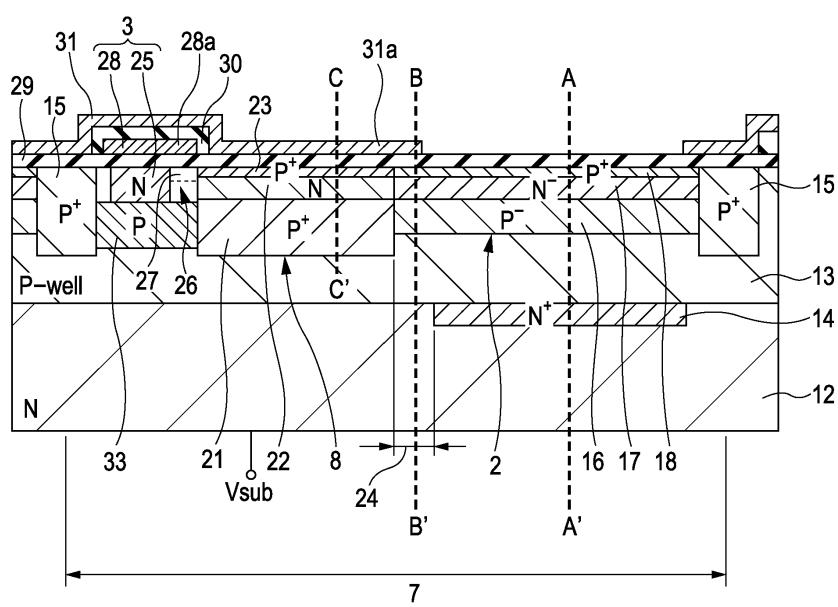

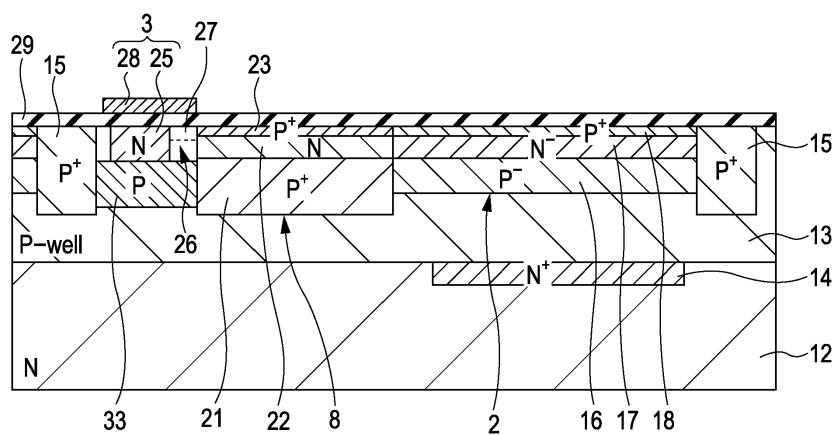

- [0104] 도 8에, 본 발명의 제 2의 실시 형태에 관한 고체 활상 장치의 개략 단면 구성을 도시한다. 도 8에서, 도 2에 대응하는 부분에는 동일 부호를 붙이고 중복 설명을 생략한다.

- [0105] 본 실시 형태의 고체 활상 장치(41)는, 제 1의 실시 형태에서의 고체 활상 장치의, 제 2의 암전류 억제부의 구성을 일부 변경한 예이다.

- [0106] 본 실시 형태에서는, 축적용량부(8)에서의 제 2의 암전류 억제부(44)가, 암전류 억제 전극(42)과 직류 전압

전원(43)으로 구성되어 있다. 암전류 억제 전극(42)은, 반도체 웨이팅(13)의 축적용량부(8) 상부에, 게이트 절연막(29)을 통하여 형성되어 있다.

[0107] 이 고체 활상 장치(41)에서도, 도 7의 A-A', B-B', C-C'선상에 따른 전위는, 제 1의 실시 형태에서 설명한 도 3과 같은 프로파일을 갖는 것이다.

[0108] 또한, 고체 활상 장치(41)에서의 제 2의 암전류 억제부(44)는, 제 1의 실시 형태에서 나타낸 제조 방법에서, 도 5의 E에 도시하는 공정에서 제 2의 암전류 억제부(23)를 형성하지 않고, 도 5의 F에 도시하는 공정에서, 암전류 억제 전극(42)을 형성함에 의해 형성할 수 있다. 그 밖의 제조 공정은, 제 1의 실시 형태와 마찬가지이다.

[0109] 본 실시 형태의 고체 활상 장치(41)에서는, 암전류 억제 전극(42)에 항상 부전압의 바이어스 전압이 인가됨으로써, 축적용량부(8)를 구성하는 N영역(22)의 표면이 반전하고, 정공으로 채워진다. 이로써, 축적용량부(8)의 계면에서 발생하는 암전류가, 항상, 정공에 흡수되기 때문에, 축적용량부(8)에서의 암전류를 억제할 수 있다.

[0110] 본 실시 형태의 고체 활상 장치(41)에서도, 제 1의 실시 형태에서의 고체 활상 장치(1)와 같은 구동 방법으로 구동할 수 있다. 본 실시 형태에서도, 비순차 주사 방식(본 실시 형태에서는 인터레이스 주사 방식)이면서, 메카 셔터 등의 소자 외부 셔터가 없는 전자 기기에 적용할 수 있는 CCD형의 고체 활상 장치를 얻을 수 있다. 그 밖에, 제 1의 실시 형태와 같은 효과를 얻을 수 있다. 또한, 암전류 억제 전극(42)과 차광층(31)을 화소부에서 전기적으로 접속하고 나서 직류 전압 전원(43)에 접속하여도 좋다.

[0111] 상술한 제 1의 실시 형태 및 제 2의 실시 형태에서는, 제 1 도전형을 n형, 제 2 도전형을 p형으로 하여 설명하였지만, 제 1 도전형을 p형, 제 2 도전형을 n형으로 하여 구성하여도 좋다. 그 경우는, 고체 활상 장치에 인가되는 소망하는 펠스는, 상술한 예와는 역극성의 펠스가 인가된다.

[0112] 본 발명은, 고체 활상 장치에의 적용으로 한정되는 것이 아니고, 활상 장치에도 적용 가능하다. 여기서, 활상 장치란, 디지털 스틸 카메라나 비디오 카메라 등의 카메라 시스템이나, 휴대 전화기 등의 활상 기능을 갖는 전자 기기인 것을 말한다. 또한, 전자 기기에 탑재된 상기 모듈형상의 형태, 즉 카메라 모듈을 활상 장치로 하는 경우도 있다.

[0113] 이하에, 본 발명의 고체 활상 장치를 이용한 전자 기기에 관해 설명한다.

[0114] <3. 제 3의 실시 형태>

[0115] 도 9에 본 발명의 제 3의 실시 형태에 관한 전자 기기(200)의 개략 구성을 도시한다.

[0116] 본 실시 형태의 전자 기기(200)는, 상술한 본 발명의 제 1의 실시 형태에서의 고체 활상 장치(1)를 카메라에 이용한 경우의 실시 형태를 도시한다.

[0117] 도 9에, 본 실시 형태에 관한 전자 기기(200)의 개략 단면 구성을 도시한다. 본 실시 형태에 관한 전자 기기(200)는, 정지 화상 촬영이 가능한 디지털 스틸 카메라를 예로 한 것이다.

[0118] 본 실시 형태에 관한 전자 기기(200)는, 고체 활상 장치(1)와, 광학 렌즈(210)와, 구동 회로(212)와, 신호 처리 회로(213)를 갖는다.

[0119] 광학 렌즈(210)는, 피사체로부터의 이미지광(입사광)을 고체 활상 장치(1)의 활상 면상에 결상시킨다. 이로써 고체 활상 장치(1) 내에 일정 기간 해당 신호 전하가 축적된다.

[0120] 구동 회로(212)는, 고체 활상 장치(1)의 전송 동작 신호를 공급한다. 구동 회로(212)로부터 공급되는 구동 신호(타이밍 신호)에 의해, 고체 활상 장치(1)의 신호 전송을 행한다. 신호 처리 회로(213)는, 각종의 신호 처리를 행한다. 신호 처리가 행하여진 영상 신호는, 메모리 등의 기억 매체에 기억되고, 또는 모니터에 출력된다.

[0121] 본 실시 형태의 전자 기기(200)에서는, 고체 활상 장치에서, 전자 셔터 기능을 갖고 있기 때문에, 메카 셔터 등의 광 셔터를, 고체 활상 장치와 별개로 구비할 필요가 없다. 이 때문에, 전자 기기를 염가로 제조할 수 있고, 또한, 전자 기기의 소형화 및 경량화가 실현된다. 또한, 본 실시 형태의 전자 기기에 사용되는 고체 활상 장치는, 암전류의 억제나, 감도의 향상이 도모되어 있기 때문에, 전자 기기에서, 화질의 향상이 도모된다.

[0122] 고체 활상 장치(1)를 적용할 수 있는 전자 기기로서는, 디지털 스틸 카메라로 한정되는 것이 아니고, 휴대 전화기 등의 모바일 기기용 카메라 모듈 등의 활상 장치에 적용 가능하다.

[0123] 본 실시 형태에서는, 고체 활상 장치(1)를 전자 기기에 이용하는 구성으로 하였지만, 전술한 제 2의 실시 형

태에서의 고체 콜상 장치를 이용할 수도 있다.

[0124] 본 발명은 2009년 2월 5일자로 일본특허청에 특허출원된 일본특허원 제2009-025346호를 우선권으로 주장한다.

[0125] 당업자라면, 하기의 특허청구범위 또는 그 등가의 범위 내에서, 설계상의 필요 또는 다른 요인에 따라, 상기 실시예에 대한 여러가지 수정예, 조합예, 부분 조합예 및 변경예를 실시할 수 있을 것이다.

### 부호의 설명

|                        |                        |

|------------------------|------------------------|

| 1 : 고체 콜상 장치           | 2 : 수광부                |

| 3 : 수직 전송 레지스터         | 4 : 수평전송 레지스터          |

| 5 : 출력 회로              | 6 : 기판                 |

| 7 : 화소                 | 8 : 축적용량부              |

| 12 : 반도체 기판            | 13 : 반도체 웨이퍼           |

| 14 : 전자 셔터 조정층         | 15 : 채널 스탭부            |

| 16 : P <sup>-</sup> 영역 | 17 : N <sup>-</sup> 영역 |

| 18 : 제 1의 암전류 억제부      | 19 : 수광부               |

| 20 : 축적용량부             | 21 : P <sup>+</sup> 영역 |

| 22 : N영역               | 23 : 제 2의 암전류 억제부      |

| 24 : 오프셋 영역            | 25 : 수직 전송 채널          |

| 26 : 판독 게이트부           | 27 : 판독 채널             |

| 28 : 수직 전송 전극          | 29 : 게이트 절연막           |

| 30 : 층간 절연막            | 31 : 차광층               |

## 도면

## 도면1

## 도면2

도면3

도면4

A

B

C

도면5

D

E

## 도면6

A

B

## 도면7

## D

## 도면8

도면9