(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6371629号

(P6371629)

(45) 発行日 平成30年8月8日(2018.8.8)

(24) 登録日 平成30年7月20日(2018.7.20)

(51) Int.Cl.

F 1

|      |        |           |      |        |

|------|--------|-----------|------|--------|

| HO4N | 5/378  | (2011.01) | HO4N | 5/378  |

| HO1L | 27/146 | (2006.01) | HO1L | 27/146 |

| GO1T | 7/00   | (2006.01) | GO1T | 7/00   |

| GO1T | 1/20   | (2006.01) | GO1T | 1/20   |

| A61B | 6/00   | (2006.01) | GO1T | 1/20   |

請求項の数 10 (全 37 頁) 最終頁に続く

(21) 出願番号

特願2014-157470 (P2014-157470)

(22) 出願日

平成26年8月1日(2014.8.1)

(65) 公開番号

特開2015-46873 (P2015-46873A)

(43) 公開日

平成27年3月12日(2015.3.12)

審査請求日 平成29年8月1日(2017.8.1)

(31) 優先権主張番号

特願2013-161035 (P2013-161035)

(32) 優先日

平成25年8月2日(2013.8.2)

(33) 優先権主張国

日本国(JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 三宅 博之

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 宮戸 英明

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 松永 隆志

最終頁に続く

(54) 【発明の名称】撮像装置、およびその動作方法

## (57) 【特許請求の範囲】

## 【請求項1】

画素回路と、電流検出回路と、A/Dコンバータと、記憶回路部と、演算回路部と、を有し、

前記画素回路は、トランジスタと、電荷蓄積部と、受光素子と、を有し、

前記記憶回路部は単数または複数であり、

複数の異なる照度において、前記受光素子が前記電荷蓄積部に蓄積する電位の情報が格納された第1のルックアップテーブルと、

前記電荷蓄積部に供給される複数の異なる電位に対し、前記電荷蓄積部にゲートが電気的に接続されるトランジスタの前記電流検出回路およびA/Dコンバータを介した出力値の情報が格納された第2のルックアップテーブルと、

前記演算回路部から出力される画像情報が格納される領域と、

を有することを特徴とする撮像装置。

## 【請求項2】

請求項1において、

前記記憶回路部には前記第2のルックアップテーブルの情報を取得するプログラムが格納されていることを特徴とする撮像装置。

## 【請求項3】

請求項1または2において、

前記画素回路は、第1のトランジスタ、第2のトランジスタ、および第3のトランジス

10

20

タを有し、

前記第1のトランジスタのソースまたはドレインの一方は、前記受光素子の一方の電極と電気的に接続され、

前記第1のトランジスタのソースまたはドレインの他方は、前記電荷蓄積部と電気的に接続され、

前記第2のトランジスタのゲートは、前記電荷蓄積部と電気的に接続され、

前記第2のトランジスタのソースまたはドレインの一方は、前記第3のトランジスタのソースまたはドレインの一方と電気的に接続され、

前記第2のトランジスタのソースまたはドレインの他方は第1の配線に電気的に接続され、

前記第3のトランジスタのソースまたはドレインの他方は第2の配線に電気的に接続され、

前記第1のトランジスタのゲートは第3の配線に電気的に接続され、

前記第3のトランジスタのゲートは第4の配線に電気的に接続され、

前記受光素子の他方の電極は第5の配線に電気的に接続され、

前記電流検出回路は前記第2の配線に電気的に接続されていることを特徴とする撮像装置。

#### 【請求項4】

請求項3において、

前記第2のルックアップテーブルには、前記第5の配線から前記受光素子および前記第1のトランジスタを介して前記電荷蓄積部に供給する複数の異なる電位に対する、前記第2のトランジスタの前記電流検出回路およびA/Dコンバータを介した出力値が格納されていることを特徴とする撮像装置。

#### 【請求項5】

請求項3または4において、

前記プログラムは、前記第1のトランジスタおよび前記第3のトランジスタをオンし、前記第5の配線に複数の異なる電位を供給し、当該複数の異なる電位に対する前記第2のトランジスタの前記電流検出回路およびA/Dコンバータを介した出力を取得する動作を行うことを特徴とする撮像装置。

#### 【請求項6】

請求項1または2において、

前記画素回路は、第1のトランジスタ、第2のトランジスタ、第3のトランジスタ、および第4のトランジスタを有し、

前記第1のトランジスタのソースまたはドレインの一方は、前記受光素子の一方の電極と電気的に接続され、

前記第1のトランジスタのソースまたはドレインの他方は、前記電荷蓄積部と電気的に接続され、

前記第2のトランジスタのゲートは、前記電荷蓄積部と電気的に接続され、

前記第2のトランジスタのソースまたはドレインの一方は、前記第3のトランジスタのソースまたはドレインの一方と電気的に接続され、

前記第4のトランジスタのソースまたはドレインの一方は、前記電荷蓄積部と電気的に接続され、

前記第2のトランジスタのソースまたはドレインの他方は第1の配線に電気的に接続され、

前記第3のトランジスタのソースまたはドレインの他方は第2の配線に電気的に接続され、

前記第4のトランジスタのソースまたはドレインの他方は、第7の配線と電気的に接続され、

前記第1のトランジスタのゲートは第3の配線に電気的に接続され、

前記第3のトランジスタのゲートは第4の配線に電気的に接続され、

10

20

30

40

50

前記第4のトランジスタのゲートは第5の配線に電気的に接続され、

前記受光素子の他方の電極は第6の配線に電気的に接続され、

前記電流検出回路は前記第2の配線に電気的に接続されていることを特徴とする撮像装置。

【請求項7】

請求項6において、

前記第2のルックアップテーブルには、前記第7の配線から前記電荷蓄積部に供給する複数の異なる電位に対する、前記第2のトランジスタの前記電流検出回路および前記A/Dコンバータを介した出力値が格納されていることを特徴とする撮像装置。

【請求項8】

10

請求項6または7において、

前記プログラムは、前記第3のトランジスタおよび前記第4のトランジスタをオンし、前記第7の配線に複数の異なる電位を供給し、当該複数の異なる電位に対する前記第2のトランジスタの前記電流検出回路およびA/Dコンバータを介した出力を取得する動作を行うことを特徴とする撮像装置。

【請求項9】

請求項1乃至8のいずれか一項において、

前記画素回路上にシンチレータが形成されていることを特徴とする撮像装置。

【請求項10】

20

請求項1乃至9のいずれか一項に記載の撮像装置であって、

前記演算回路部は、

撮像前に前記プログラムを動作させて前記第2のルックアップテーブルの情報を取得し、

撮像時において、前記電流検出回路の出力値に対する前記電荷蓄積部の電位を前記第2のルックアップテーブルから読み出し、

当該電位に対する照度を前記第1のルックアップテーブルから読み出し、

当該照度に関する信号を前記記憶回路部に入力し、

当該記憶回路部から当該信号を出力することを特徴とする撮像装置の動作方法。

【発明の詳細な説明】

30

【技術分野】

【0001】

本発明は、物、方法、または、製造方法に関する。または、本発明は、プロセス、マシン、マニュファクチャ、または、組成物（コンポジション・オブ・マター）に関する。特に、本発明は、例えば、半導体装置、表示装置、発光装置、蓄電装置、撮像装置、それらの駆動方法、または、それらの製造方法に関する。特に、本発明の一態様は、シンチレータを有する撮像装置に関する。

【背景技術】

【0002】

医療現場では、患者の特定部位にX線を照射し、当該特定部位を透過したX線によってX線フィルムを感光し、現像することで当該特定部位の内部の様子を可視化する写真技術を用いた医療用画像診断装置が広く普及している。

40

【0003】

上記X線フィルムを用いた方法では、X線フィルムを保管するスペースの確保が必要なことや、その管理が煩雑であるため、画像の電子化が進められている。画像を電子化する方法の一つとして、イメージングプレートを用いる方法が知られている。イメージングプレートをX線フィルムと同様にX線で感光させ、当該イメージングプレートから発せられる光をスキャナで検出することにより、電子化された画像を得ることができる。

【0004】

イメージングプレートは、X線の照射によって光を発する特性（輝尽性）を有する材料（輝尽性蛍光体）が塗布された板であり、X線フィルムよりもX線吸収率の検出感度が高い

50

。また、X線照射の情報を消去することができ、繰り返して使用することができる。しかしながら、イメージングプレートで取得できる情報はアナログ情報であり、それを電子化するにはデジタル化処理をするという工程が残されていた。

#### 【0005】

そのため、近年では、デジタルデータを直接取得できるフラットパネルディテクタが注目されている（例えば、特許文献1、2）。フラットパネルディテクタは、直接方式と間接方式の二方式があり、直接方式はX線検出素子を用いてX線を電荷に直接変換する方式であり、間接方式はX線をシンチレータによって可視光に変換し、その光をフォトダイオードで電荷に変換する方式である。いずれの方式においても、フラットパネルディテクタは、マトリクス状に配置された複数の画素回路を有している。

10

#### 【先行技術文献】

##### 【特許文献】

##### 【0006】

【特許文献1】特開平2-164067号公報

【特許文献2】特開2002-151669号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

##### 【0007】

フラットパネルディテクタの画素回路を構成するトランジスタには半導体材料や絶縁材料が含まれており、エネルギーの強いX線等の放射線が当該半導体材料や当該絶縁材料に照射されると欠陥準位などが生成し、トランジスタの電気特性を変動させてしまう。

20

##### 【0008】

このような現象は、光電変換材料やシンチレータを透過してしまう微量の放射線によっても起こりうる。したがって、フラットパネルディテクタで得られるデータの信頼性が低下してしまう。

##### 【0009】

上記問題点を顧み、本発明の一態様では、画素回路の出力値を補正する撮像装置を提供することを目的の一つとする。または、画素回路が有するトランジスタの電気特性を読み取る動作を制御するためのプログラムを有する撮像装置を提供することを目的の一つとする。または、新規な撮像装置などを提供することを目的の一つとする。または、画素回路の出力値を補正する撮像装置の動作方法を提供することを目的の一つとする。または、画素回路が有するトランジスタの電気特性を読み取る撮像装置の動作方法を提供することを目的の一つとする。または、新規な撮像装置などの動作方法を提供することを目的の一つとする。

30

##### 【0010】

なお、これらの課題の記載は、他の課題の存在を妨げるものではない。なお、本発明の一態様は、これらの課題の全てを解決する必要はないものとする。なお、これら以外の課題は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の課題を抽出することが可能である。

#### 【課題を解決するための手段】

40

##### 【0011】

本発明の一態様は、画素回路に酸化物半導体を用いたトランジスタを有し、X線等の放射線を用いて画像を取得する撮像装置、および当該撮像装置の動作方法に関する。

##### 【0012】

本発明の一態様は、画素回路と、電流検出回路と、A/Dコンバータと、記憶回路部と、演算回路部と、を有し、画素回路は、トランジスタと、電荷蓄積部と、受光素子と、を有し、記憶回路部は単数または複数であり、複数の異なる照度において、受光素子が電荷蓄積部に蓄積する電位の情報が格納された第1のルックアップテーブルと、電荷蓄積部に供給される複数の異なる電位に対し、電荷蓄積部にゲートが電気的に接続されるトランジスタの電流検出回路およびA/Dコンバータを介した出力値の情報が格納された第2のルックアップテーブルと、を有する。

50

クアップテーブルと、演算回路部から出力される画像情報が格納される領域と、を有することを特徴とする撮像装置である。

【0013】

なお、本明細書等における「第1」、「第2」などの序数詞は、構成要素の混同を避けるために付すものであり、数的に限定するものではないことを付記する。

【0014】

上記記憶回路部には、第2のルックアップテーブルの情報を取得するプログラムが格納されてもよい。

【0015】

また、上記画素回路は、第1のトランジスタ、第2のトランジスタ、および第3のトランジスタを有し、第1のトランジスタのソースまたはドレインの一方は、受光素子の一方の電極と電気的に接続され、第1のトランジスタのソースまたはドレインの他方は、電荷蓄積部と電気的に接続され、第2のトランジスタのゲートは、電荷蓄積部と電気的に接続され、第2のトランジスタのソースまたはドレインの一方は、第3のトランジスタのソースまたはドレインの一方と電気的に接続され、第2のトランジスタのソースまたはドレインの他方は第1の配線に電気的に接続され、第3のトランジスタのソースまたはドレインの他方は第2の配線に電気的に接続され、第1のトランジスタのゲートは第3の配線に電気的に接続され、第3のトランジスタのゲートは第4の配線に電気的に接続され、受光素子の他方の電極は第5の配線に電気的に接続され、電流検出回路は第2の配線に電気的に接続されている構成とできる。

10

20

【0016】

また、上記画素回路が有するトランジスタは酸化物半導体を用いて形成されていることが好ましい。

【0017】

また、第2のルックアップテーブルには、第5の配線から受光素子および第1のトランジスタを介して電荷蓄積部に供給する複数の異なる電位に対する、第2のトランジスタの電流検出回路およびA/Dコンバータを介した出力値を格納することができる。

【0018】

また、上記プログラムは、第1のトランジスタおよび第3のトランジスタをオンし、第5の配線に複数の異なる電位を供給し、当該複数の異なる電位に対する第2のトランジスタの電流検出回路およびA/Dコンバータを介した出力を取得する動作を行うことができる。

30

【0019】

上記画素回路は、第1のトランジスタ、第2のトランジスタ、第3のトランジスタ、および第4のトランジスタを有し、第1のトランジスタのソースまたはドレインの一方は、受光素子の一方の電極と電気的に接続され、第1のトランジスタのソースまたはドレインの他方は、電荷蓄積部と電気的に接続され、第2のトランジスタのゲートは、電荷蓄積部と電気的に接続され、第2のトランジスタのソースまたはドレインの一方は、第3のトランジスタのソースまたはドレインの一方と電気的に接続され、第4のトランジスタのソースまたはドレインの一方は、電荷蓄積部と電気的に接続され、第2のトランジスタのソースまたはドレインの他方は第1の配線に電気的に接続され、第3のトランジスタのソースまたはドレインの他方は第2の配線に電気的に接続され、第4のトランジスタのソースまたはドレインの他方は、第7の配線と電気的に接続され、第1のトランジスタのゲートは第3の配線に電気的に接続され、第3のトランジスタのゲートは第4の配線に電気的に接続され、第4のトランジスタのゲートは第5の配線に電気的に接続され、受光素子の他方の電極は第6の配線に電気的に接続され、電流検出回路は第2の配線に電気的に接続されている構成としてもよい。

40

【0020】

上記画素回路が有するトランジスタは酸化物半導体を用いて形成されていることが好ましい。

50

**【 0 0 2 1 】**

また、第2のルックアップテーブルには、第7の配線から電荷蓄積部に供給する複数の異なる電位に対する、第2のトランジスタの電流検出回路およびA/Dコンバータを介した出力値を格納することができる。

**【 0 0 2 2 】**

また、上記プログラムは、第3のトランジスタおよび第4のトランジスタをオンし、第7の配線に複数の異なる電位を供給し、当該複数の異なる電位に対する第2のトランジスタの電流検出回路およびA/Dコンバータを介した出力を取得する動作を行うことができる。

**【 0 0 2 3 】**

また、当該撮像装置は、受光素子上にシンチレータが形成された構成とすることができる。

**【 0 0 2 4 】**

また、上記受光素子には、フォトダイオード、または、一対の電極間に半導体層を有する可変抵抗素子を用いることができる。

**【 0 0 2 5 】**

また、上記演算回路部は、撮像前にプログラムを動作させて第2のルックアップテーブルの情報を取得し、撮像時において、電流検出回路の出力値に対する電荷蓄積部の電位を第2のルックアップテーブルから読み出し、当該電位に対する照度を第1のルックアップテーブルから読み出し、当該照度に関する信号を記憶回路部に入力し、当該記憶回路部から当該信号を出力する動作を行うことができる。

**【発明の効果】****【 0 0 2 6 】**

本発明の一態様により、画素回路の出力値を補正する撮像装置を提供することができる。または、画素回路が有するトランジスタの電気特性を読み取る動作を制御するためのプログラムを有する撮像装置を提供することができる。または、新規な撮像装置などを提供することができる。または、画素回路の出力値を補正する撮像装置の動作方法を提供することができる。または、画素回路が有するトランジスタの電気特性を読み取る撮像装置の動作方法を提供することができる。または、新規な撮像装置などの動作方法を提供することができる。

**【 0 0 2 7 】**

なお、これらの効果の記載は、他の効果の存在を妨げるものではない。なお、本発明の一態様は、必ずしも、これらの効果の全てを有する必要はない。なお、これら以外の効果は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の効果を抽出することが可能である。

**【図面の簡単な説明】****【 0 0 2 8 】**

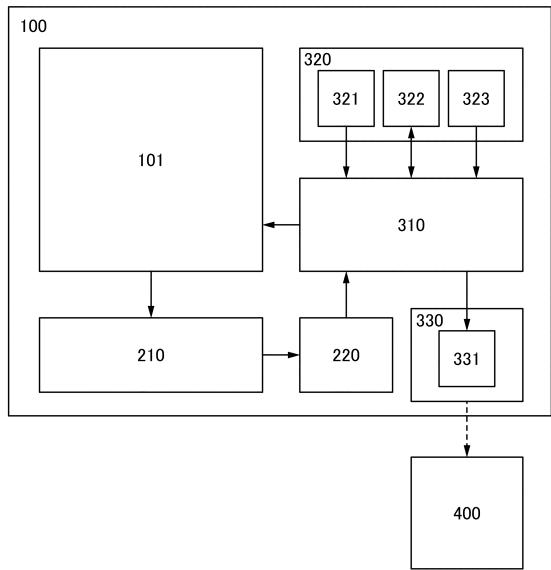

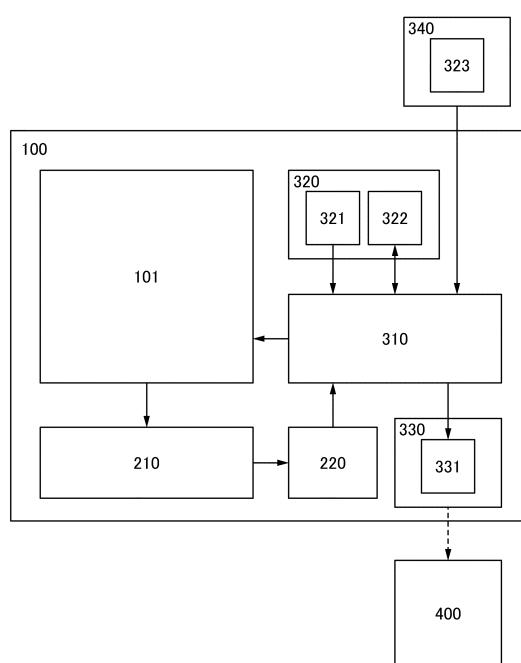

【図1】撮像装置を説明するブロック図。

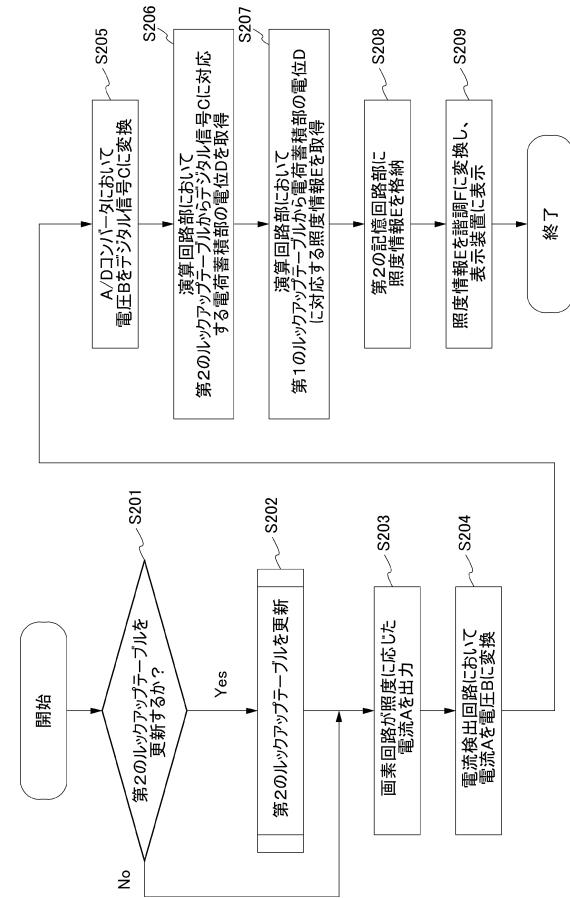

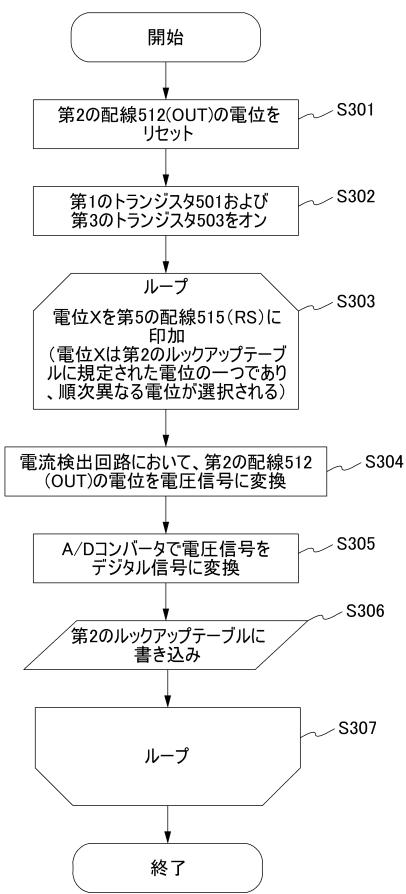

【図2】撮像装置の動作方法を説明するフローチャート。

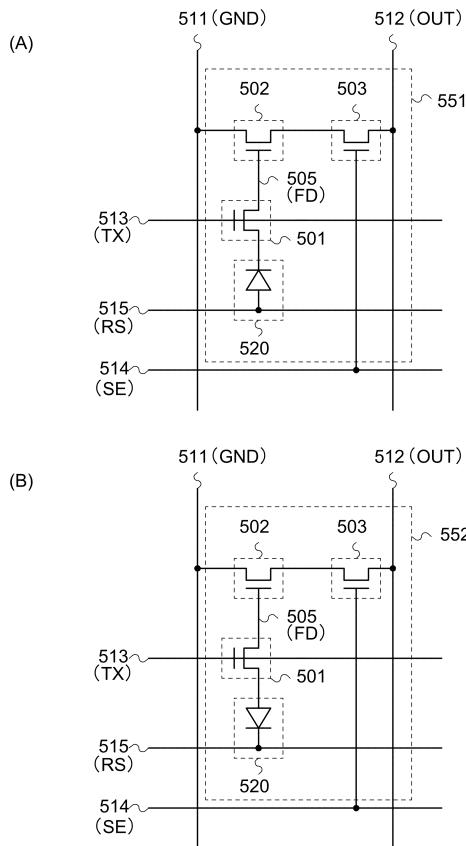

【図3】画素回路の構成を説明する図。

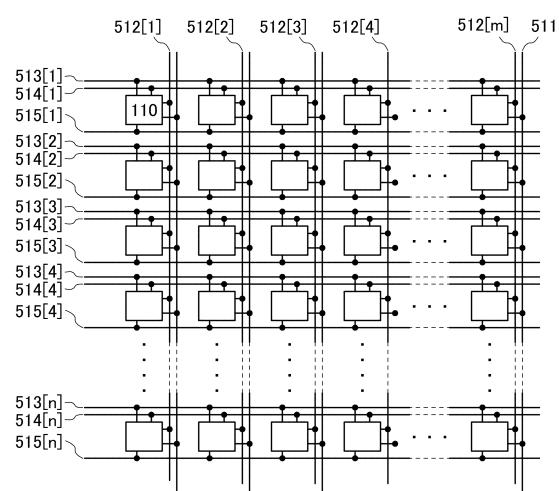

【図4】画素回路と配線の接続形態を説明する図。

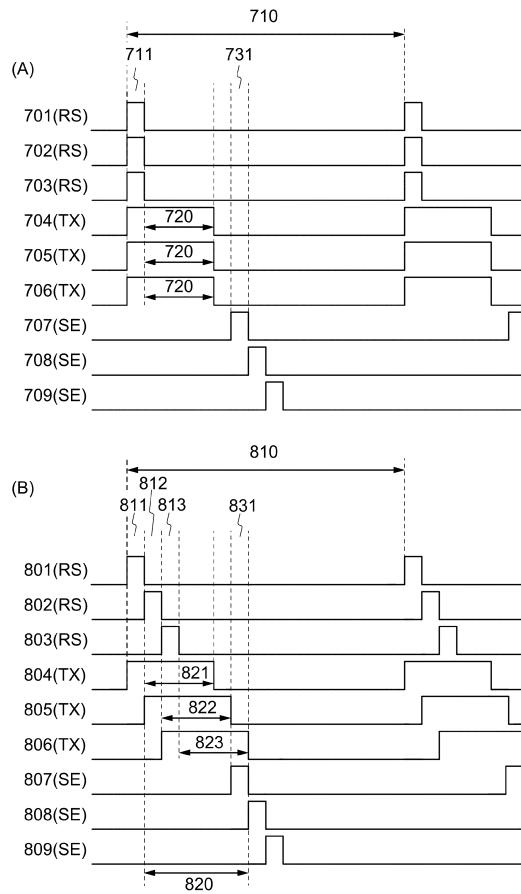

【図5】画素回路の動作を説明するタイミングチャート。

【図6】画素回路の構成を説明する図。

【図7】画素回路の構成を説明する図。

【図8】画素回路の構成を説明する図。

【図9】画素回路と配線の接続形態を説明する図。

【図10】電流検出回路およびその動作を説明する図。

【図11】撮像装置を説明するブロック図。

【図12】撮像装置を説明するブロック図。

【図13】撮像装置の動作方法を説明するフローチャート。

10

20

30

40

50

【図14】グローバルシャッタ方式とローリングシャッタ方式の動作を説明するタイミングチャート。

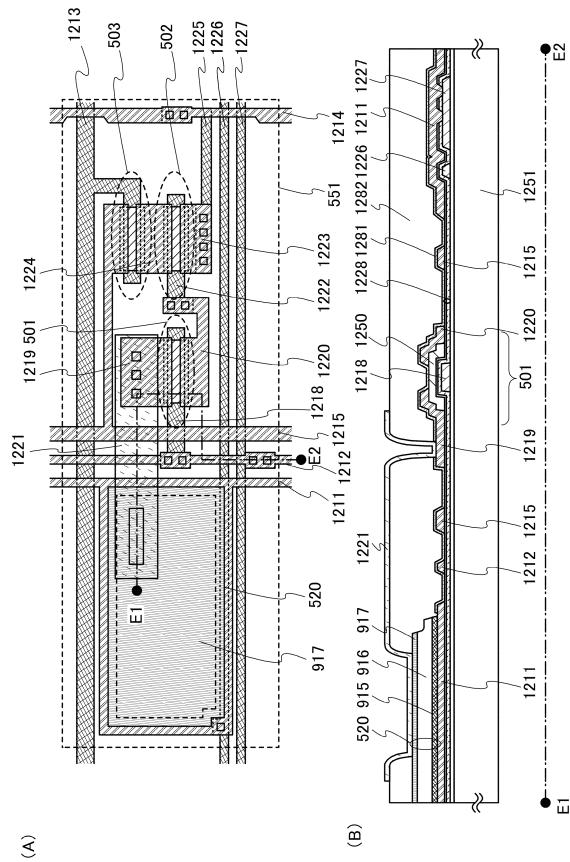

【図15】画素回路のレイアウトを説明する上面図および断面図。

【図16】画素回路のレイアウトを説明する上面図および断面図。

【図17】トランジスタを説明する断面図。

【図18】トランジスタを説明する断面図。

【図19】画素回路の構成を説明する図。

【図20】撮像システムの構成を説明する図。

【発明を実施するための形態】

【0029】

10

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、その形態および詳細を様々に変更し得ることは、当業者であれば容易に理解される。また、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、実施の形態を説明するための全図において、同一部分または同様な機能を有する部分には同一の符号を付し、その繰り返しの説明は省略することがある。

【0030】

20

なお、本明細書等において、XとYとが接続されている、と明示的に記載する場合は、XとYとが電気的に接続されている場合と、XとYとが機能的に接続されている場合と、XとYとが直接接続されている場合とを含むものとする。ここで、X、Yは、対象物（例えば、装置、素子、回路、配線、電極、端子、導電膜、層、など）であるとする。したがって、所定の接続関係、例えば、図または文章に示された接続関係に限定されず、図または文章に示された接続関係以外のものも含むものとする。

【0031】

30

XとYとが電気的に接続されている場合の一例としては、XとYとの電気的な接続を可能とする素子（例えば、スイッチ、トランジスタ、容量素子、インダクタ、抵抗素子、ダイオード、表示素子、発光素子、負荷など）が、XとYとの間に1個以上接続されることが可能である。なお、スイッチは、オンオフが制御される機能を有している。つまり、スイッチは、導通状態（オン状態）、または、非導通状態（オフ状態）になり、電流を流すか流さないかを制御する機能を有している。または、スイッチは、電流を流す経路を選択して切り替える機能を有している。

【0032】

40

XとYとが機能的に接続されている場合の一例としては、XとYとの機能的な接続を可能とする回路（例えば、論理回路（インバータ、NAND回路、NOR回路など）、信号変換回路（DA変換回路、AD変換回路、ガンマ補正回路など）、電位レベル変換回路（電源回路（昇圧回路、降圧回路など）、信号の電位レベルを変えるレベルシフタ回路など）、電圧源、電流源、切り替え回路、增幅回路（信号振幅または電流量などを大きく出来る回路、オペアンプ、差動增幅回路、ソースフォロワ回路、バッファ回路など）、信号生成回路、記憶回路、制御回路など）が、XとYとの間に1個以上接続されることが可能である。なお、一例として、XとYとの間に別の回路を挟んでいても、Xから出力された信号がYへ伝達される場合は、XとYとは機能的に接続されているものとする。

【0033】

なお、XとYとが接続されている、と明示的に記載する場合は、XとYとが電気的に接続されている場合（つまり、XとYとの間に別の素子または別の回路を挟んで接続されている場合）と、XとYとが機能的に接続されている場合（つまり、XとYとの間に別の回路を挟んで機能的に接続されている場合）と、XとYとが直接接続されている場合（つまり、XとYとの間に別の素子または別の回路を挟まずに接続されている場合）とを含むものとする。つまり、電気的に接続されている、と明示的に記載する場合は、単に、接続されている、とのみ明示的に記載されている場合と同じであるとする。

【0034】

50

なお、回路図上は独立している構成要素同士が電気的に接続しているように図示されている場合であっても、1つの構成要素が、複数の構成要素の機能を併せ持っている場合もある。例えば配線の一部が電極としても機能する場合は、一の導電膜が、配線の機能、および電極の機能の両方の構成要素の機能を併せ持っている。したがって、本明細書における電気的に接続とは、このような、一の導電膜が、複数の構成要素の機能を併せ持っている場合も、その範疇に含める。

#### 【0035】

なお、本明細書等において、様々な基板を用いて、トランジスタを形成することが出来る。基板の種類は、特定のものに限定されることはない。その基板の一例としては、半導体基板（例えば単結晶基板またはシリコン基板）、S O I 基板、ガラス基板、石英基板、プラスチック基板、金属基板、ステンレス・スチール基板、ステンレス・スチール・ホイルを有する基板、タングステン基板、タングステン・ホイルを有する基板、可撓性基板、貼り合わせフィルム、纖維状の材料を含む紙、または基材フィルムなどがある。ガラス基板の一例としては、バリウムホウケイ酸ガラス、アルミニノホウケイ酸ガラス、またはソーダライムガラスなどがある。可撓性基板の一例としては、ポリエチレンテレフタレート（P E T）、ポリエチレンナフタレート（P E N）、ポリエーテルサルファン（P E S）に代表されるプラスチック、またはアクリル等の可撓性を有する合成樹脂などがある。貼り合わせフィルムの一例としては、ポリプロピレン、ポリエステル、ポリフッ化ビニル、またはポリ塩化ビニルなどがある。基材フィルムの一例としては、ポリエステル、ポリアミド、ポリイミド、無機蒸着フィルム、または紙類などがある。特に、半導体基板、単結晶基板、またはS O I 基板などを用いてトランジスタを製造することによって、特性、サイズ、または形状などのばらつきが少なく、電流能力が高く、サイズの小さいトランジスタを製造することができる。このようなトランジスタによって回路を構成すると、回路の低消費電力化、または回路の高集積化を図ることができる。

10

20

#### 【0036】

なお、ある基板を用いてトランジスタを形成し、その後、別の基板にトランジスタを転置し、別の基板上にトランジスタを配置してもよい。トランジスタが転置される基板の一例としては、上述したトランジスタを形成することが可能な基板に加え、紙基板、セロファン基板、石材基板、木材基板、布基板（天然纖維（絹、綿、麻）、合成纖維（ナイロン、ポリウレタン、ポリエステル）若しくは再生纖維（アセテート、キュプラ、レーヨン、再生ポリエステル）などを含む）、皮革基板、またはゴム基板などがある。これらの基板を用いることにより、特性のよいトランジスタの形成、消費電力の小さいトランジスタの形成、壊れにくい装置の製造、耐熱性の付与、軽量化、または薄型化を図ることができる。

30

#### 【0037】

##### （実施の形態1）

本実施の形態では、本発明の一態様であるX線等の放射線を用いる撮像装置について、図面を参照して説明する。

#### 【0038】

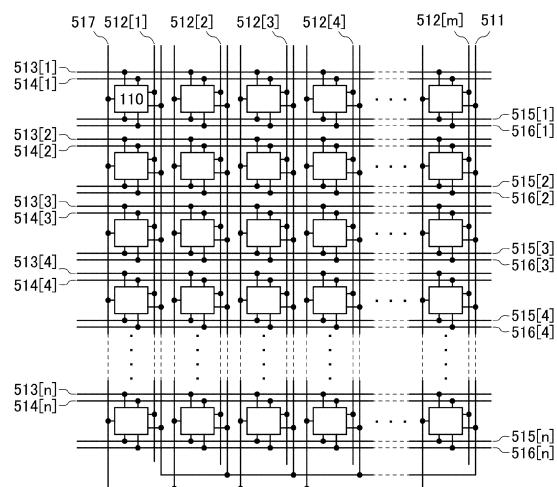

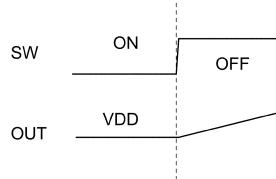

図1は、本発明の一態様であるX線等の放射線を用いる撮像装置100のブロック図の一例である。撮像装置100は、フラットパネルディテクタ101、電流検出回路210、A / D コンバータ220、演算回路部310、第1の記憶回路部320、および第2の記憶回路部330を含む。ここで、第1の記憶回路部320には、第1のルックアップテーブル321、第2のルックアップテーブル322、および第2のルックアップテーブルの情報を取得するためのプログラム323が格納されている。また、第2の記憶回路部330は、演算回路部310が出力する画像情報を格納する領域331を有している。また、図1においては、撮像装置100に表示装置400を含まない構成としているが、当該表示装置を含む構成とすることもできる。

40

#### 【0039】

ここで、第1のルックアップテーブル321には、フラットパネルディテクタ101が有する画素回路において、複数の異なる照度に対して受光素子が電荷蓄積部に蓄積する電位

50

の情報が格納されている。また、第2のルックアップテーブル322には、上記電荷蓄積部に供給される複数の異なる電位に対し、当該電荷蓄積部にゲート電極層が接続されるトランジスタの電流検出回路およびA/Dコンバータを介した出力値の情報が格納されている。

#### 【0040】

図1において、フラットパネルディテクタ101が有する画素回路は電流検出回路210に接続され、当該電流検出回路はA/Dコンバータ220に接続される。また、演算回路部310は、A/Dコンバータ220、第1の記憶回路部320、第2の記憶回路部330、およびフラットパネルディテクタ101と接続される。そして、第2の記憶回路部330は表示装置400と接続される。

10

#### 【0041】

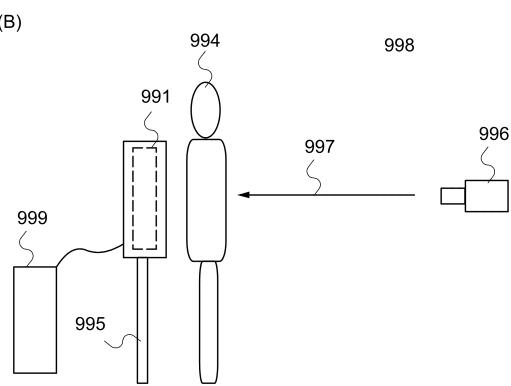

図20(A)において、フラットパネルディテクタ101が収納されたディテクタユニットの一例を示す。ディテクタユニット991には、取っ手992が設けられている。なお、ディテクタユニット991には、フラットパネルディテクタ101だけでなく、撮像装置100の一部、または、全部が収納されている場合もある。

#### 【0042】

図20(B)には、撮像システム998の全体構成図の一例を示す。ディテクタユニット991が、台995に取り付けられている。ディテクタユニット991には、表示装置やコンピュータ999が接続されている場合がある。X線源996から照射されたX線997は被写体994を透過し、ディテクタユニット991で検出される。

20

#### 【0043】

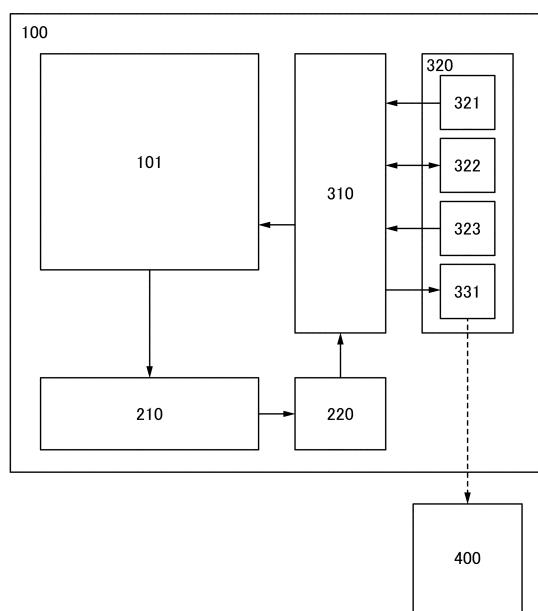

撮像装置100における撮像の手順を図2に示すフローチャートを用いて説明する。まず、第2のルックアップテーブルを更新するか否かの判断を行う(S201)。第2のルックアップテーブルを更新する場合は、後述する手順を用いて更新を行う(S202)。次に、フラットパネルディテクタ101が有する画素回路が照度に応じて電流Aを出力する(S203)。次に、電流検出回路210において、電流Aは電圧Bに変換される(S204)。次に、A/Dコンバータ220において、電圧Bはデジタル信号Cに変換される(S205)。次に、演算回路部310において、第2のルックアップテーブル322からデジタル信号Cに対応する電荷蓄積部の電位Dを取得する(S206)。次に、演算回路部310において、第1のルックアップテーブル321から電荷蓄積部の電位Dに対応する照度情報Eを取得する(S207)。次に、第2の記憶回路部330の領域331に照度情報Eを格納する(S208)。そして、照度情報Eを譜調Fに変換した画像が表示装置に表示される(S209)。

30

#### 【0044】

従来の撮像装置においては、画素回路の出力値(例えばデジタル信号C)に対する照度情報(例えば照度情報E)のルックアップテーブルを用いていたため、画素回路の出力を用うトランジスタの電気特性が変動すると当該ルックアップテーブルから読み取る照度情報が不正確となり、正確な画像が得られない問題があった。

#### 【0045】

本発明の一態様では、画素回路における照度に対する電荷蓄積部の電位からなる第1のルックアップテーブル321と電荷蓄積部の電位(ゲート電圧)に対するトランジスタの出力情報からなる第2のルックアップテーブル322の二つを用い、第2のルックアップテーブル322を撮像前に更新することを特徴とする。第2のルックアップテーブル322を更新することで、上記電流Aを出力するトランジスタの電気特性が経時変化をしたとしても正確な照度情報が得られるため、撮像装置から得られる画像情報の信頼性を高めることができる。特にX線などの放射線を用いるフラットパネルディテクタでは、画素回路に用いられるトランジスタのしきい値電圧がシフトするなど、電気特性が変化しやすい。したがって、本発明の一態様を適用することが特に好ましい。

40

#### 【0046】

なお、第2のルックアップテーブル322の更新間隔は、タイマーやカウンター等を用い

50

、所定の期間や撮影回数などで定めればよい。また、撮影前に毎回更新する設定としてもよい。

**【0047】**

次に、撮像装置100を構成する各要素の詳細について説明する。

**【0048】**

本発明の一態様におけるX線検出用のフラットパネルディテクタ101には、シンチレータを組み合すことができる。シンチレータは、X線やガンマ線などの放射線が照射されると、そのエネルギーを吸収して可視光や紫外光を発する物質、または当該物質を含む材料からなり、例えば、 $Gd_2O_2S : Tb$ 、 $Gd_2O_2S : Pr$ 、 $Gd_2O_2S : Eu$ 、 $BaFC1 : Eu$ 、 $NaI$ 、 $CsI$ 、 $CaF_2$ 、 $BaF_2$ 、 $CeF_3$ 、 $LiF$ 、 $LiI$ 、 $ZnO$ などの材料や、それらを樹脂やセラミクスに分散させたものが知られている。

10

**【0049】**

被写体を透過したX線等の放射線はシンチレータに入射され、可視光や紫外光などの光(蛍光)に変換される。そして、当該光を画素回路に設けられた受光素子で検知し、画像データを取得する。

**【0050】**

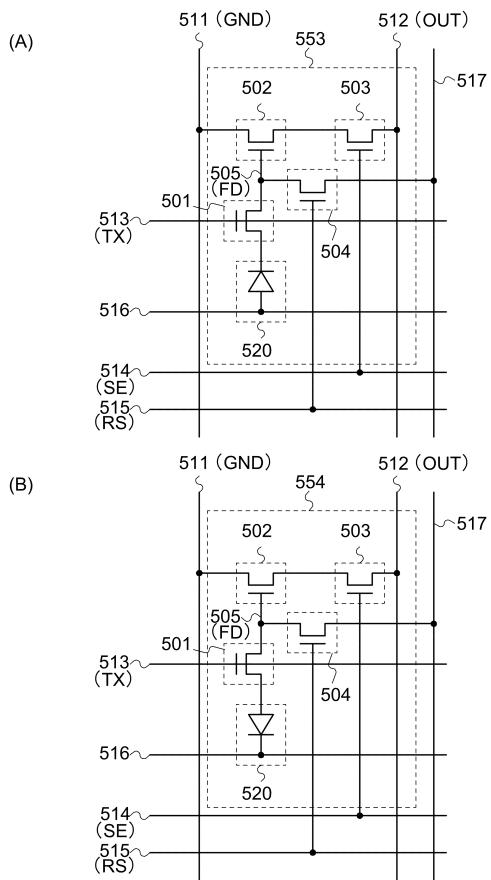

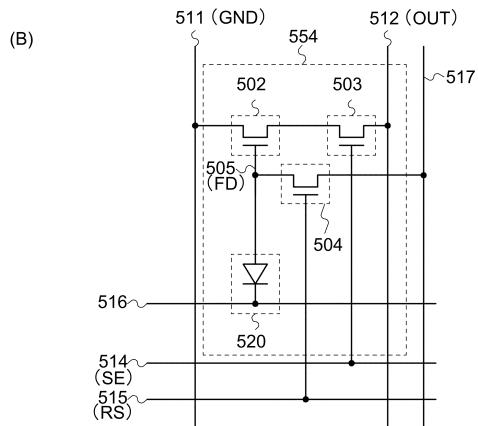

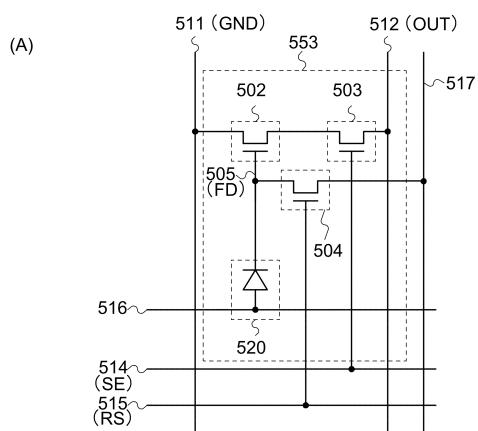

図3(A)、(B)は、フラットパネルディテクタ101における画素回路の一例を示す回路図である。

**【0051】**

図3(A)に示す回路551は、フォトダイオード520、第1のトランジスタ501、

20 第2のトランジスタ502、および第3のトランジスタ503を含んだ構成となっている。

**【0052】**

第1のトランジスタ501のソースまたはドレインの一方は、フォトダイオード520のカソードと電気的に接続され、第1のトランジスタ501のソースまたはドレインの他方、および第2のトランジスタ502のゲートは、配線505(FD)と電気的に接続され、第2のトランジスタ502のソースまたはドレインの一方は、第3のトランジスタ503のソースまたはドレインの一方と電気的に接続され、第2のトランジスタ502のソースまたはドレインの他方は第1の配線511(GND)に電気的に接続され、第3のトランジスタ503のソースまたはドレインの他方は第2の配線512(OUT)に電気的に接続され、第1のトランジスタ501のゲートは第3の配線513(TX)に電気的に接続され、第3のトランジスタ503のゲートは第4の配線514(SE)に電気的に接続され、フォトダイオード520のアノードは第5の配線515(RS)に電気的に接続されている。

30

**【0053】**

フォトダイオード520は受光素子であり、画素回路に入射した光に応じた電流を生成する動作を行う。第1のトランジスタ501は、フォトダイオード520による配線505(FD)への電荷蓄積を制御する。第2のトランジスタ502は、配線505(FD)の電位に応じた信号を出力する動作を行う。第3のトランジスタ503は、読み出し時に画素回路の選択を制御する。

40

**【0054】**

なお、配線505(FD)は、フォトダイオード520が受ける光の量に応じて変化する電荷を保持する、所謂電荷蓄積部である。実質的な電荷蓄積部は、配線505(FD)と電気的に接続される第1のトランジスタ501のソース領域またはドレイン領域近傍の空乏層容量、配線505(FD)の配線容量、配線505(FD)と電気的に接続される第2のトランジスタ502のゲート容量などである。また、配線505(FD)と第1の配線511(GND)との間に容量素子を設けてもよい。

**【0055】**

第1の配線511(GND)は、基準電位(例えばGND)を設定する信号線である。第2の配線512(OUT)は、回路551で得られた情報を出力するための信号線である

50

。第3の配線513(TX)は、第1のトランジスタ501を制御するための信号線である。第4の配線514(SE)は、第3のトランジスタ503を制御するための信号線である。第5の配線515(RS)は、配線505(FD)をリセットするための信号線である。なお、回路551における第5の配線515(RS)は、配線505(FD)への電荷蓄積を行うための信号線である。

#### 【0056】

また、画素回路は、図3(B)に示す構成であってもよい。図3(B)に示す回路552は、図3(A)に示す回路551と構成要素は同じであるが、フォトダイオード520のアノードが第1のトランジスタ501のソースまたはドレインの一方と電気的に接続され、フォトダイオード520のカソードが第5の配線515(RS)と電気的に接続される点で異なる。10

#### 【0057】

なお、図3(A)、(B)に示す各回路を画素回路110として用い、画素回路110をm行n列(m、nはともに1以上の整数)のマトリクス状に配置した場合の各配線との接続形態の一例は図4に示すようになる。

#### 【0058】

次に、図3(A)、(B)に示す各素子の構成について説明する。

#### 【0059】

フォトダイオード520には、シリコン半導体などでpn型やpin型の接合を形成した素子を用いることができる。シンチレータが可視光を発する場合は、i型の半導体層を非晶質シリコンで形成したpin型フォトダイオードを用いることが好ましい。非晶質シリコンは可視光の波長領域における感度が高く、微弱な可視光を検知しやすい。20

#### 【0060】

なお、i型の半導体とは、フェルミ準位がバンドギャップの中央に位置する所謂真性半導体の他、半導体に含まれるp型を付与する不純物、またはn型を付与する不純物がそれぞれ $1 \times 10^{20}$ atoms/cm<sup>3</sup>以下の濃度であり、暗伝導度に対して光伝導度が高い半導体を指す。

#### 【0061】

第1のトランジスタ501、第2のトランジスタ502、および第3のトランジスタ503は、非晶質シリコン、微結晶シリコン、多結晶シリコン、単結晶シリコンなどのシリコン半導体を用いて形成することも可能であるが、酸化物半導体を用いたトランジスタで形成することが好ましい。酸化物半導体でチャネル形成領域を形成したトランジスタは、極めてオフ電流が低い特性を示す特徴を有している。30

#### 【0062】

特に、配線505(FD)と接続されている第1のトランジスタ501のリーク電流が大きいと、配線505(FD)に蓄積された電荷が保持できる時間が十分でなくなる。したがって、当該トランジスタに酸化物半導体を用いたトランジスタを使用することで、フォトダイオードを介した不要な電荷の流出を防止することができる。

#### 【0063】

また、第2のトランジスタ502および第3のトランジスタ503においても、リーク電流が大きいと、第1の配線511(GND)または第2の配線512(OUT)に不必要的電荷の出力が起こるため、これらのトランジスタとして、酸化物半導体でチャネル形成領域を形成したトランジスタを用いることが好ましい。40

#### 【0064】

また、第2のトランジスタ502に極めてオフ電流の低い酸化物半導体を用いたトランジスタを用いることで、撮像のダイナミックレンジを拡大することができる。図3(A)に示す画素回路構成では、フォトダイオード520に入射される光の強度が大きいときに第2のトランジスタ502のゲート電位が小さくなる。また、図3(B)に示す画素回路構成では、フォトダイオード520に入射される光の強度が小さいときに第2のトランジスタ502のゲート電位が小さくなる。酸化物半導体を用いたトランジスタは極めてオフ電50

流が低いため、ゲート電位が極めて小さい場合においても当該ゲート電位に応じた電流を正確に出力することができる。したがって、検出することのできる照度のレンジ、すなわちダイナミックレンジを広げることができる。

#### 【0065】

また、図3(B)に示す画素回路構成においては、第2のトランジスタ502のゲート電位が比較的小さいとき、すなわち、シンチレータからフォトダイオードに照射される光の強度が小さい場合においても十分なダイナミックレンジを得られる。つまり、シンチレータが発する光の強度は小さくてもよいことになるため、被写体に照射するX線強度を小さくすることができ、生体に対する放射線の悪影響を低減させることができる。また、撮像装置の消費電力を低減させることができる。

10

#### 【0066】

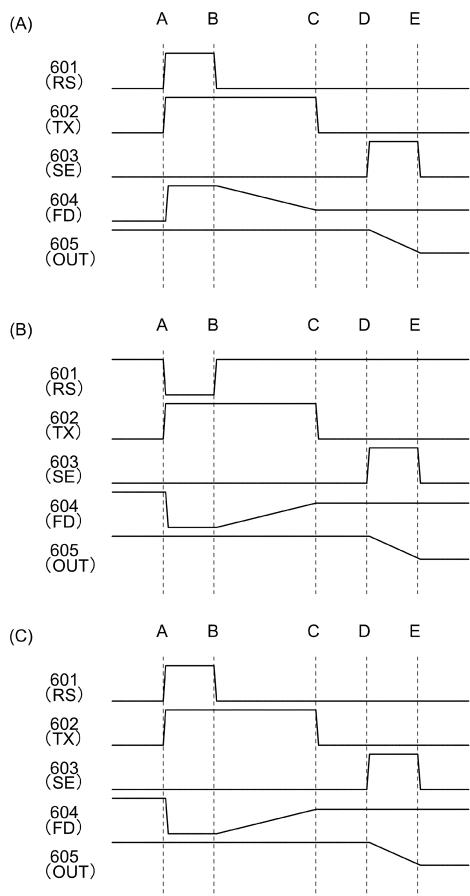

次に、図3(A)の回路551の動作の例について図5(A)に示すタイミングチャートを用いて説明する。

#### 【0067】

図5(A)では簡易に説明するため、各配線の電位は、二値変化する信号として与える。ただし、各電位はアナログ信号であるため、実際には状況に応じて二値に限らず種々の値を取り得る。なお、図に示す信号601は第5の配線515(RS)の電位、信号602は第3の配線513(TX)の電位、信号603は第4の配線514(SE)の電位、信号604は配線505(FD)の電位、信号605は第2の配線512(OUT)の電位に相当する。

20

#### 【0068】

時刻Aにおいて、第5の配線515(RS)の電位(信号601)を”High”、第3の配線513(TX)の電位(信号602)を”High”とすると、フォトダイオード520に順方向バイアスが印加され、配線505(FD)の電位(信号604)が”High”となる。すなわち、電荷蓄積部の電位は第5の配線515(RS)の電位に初期化され、リセット状態となる。以上がリセット動作の開始である。なお、第2の配線512(OUT)の電位(信号605)は、”High”にプリチャージしておく。

#### 【0069】

時刻Bにおいて、第5の配線515(RS)の電位(信号601)を”Low”、第3の配線513(TX)の電位(信号602)を”High”とするとリセット動作が終了し、蓄積動作が開始される。ここで、フォトダイオード520には逆方向バイアスが印加されるため、逆方向電流により、配線505(FD)の電位(信号604)が低下し始める。フォトダイオード520は、光が照射されると逆方向電流が増大するので、照射される光の量に応じて配線505(FD)の電位(信号604)の低下速度は変化する。すなわち、フォトダイオード520に照射する光の量に応じて、第2のトランジスタ502のソースとドレイン間のチャネル抵抗が変化する。

30

#### 【0070】

なお、ここでフォトダイオード520に照射される光とは、シンチレータによってX線等の放射線から変換された光を指す。

#### 【0071】

時刻Cにおいて、第3の配線513(TX)の電位(信号602)を”Low”とすると蓄積動作が終了し、配線505(FD)の電位(信号604)は一定となる。ここで、当該電位は、蓄積動作中にフォトダイオード520が生成した電荷量により決まる。すなわち、フォトダイオード520に照射されていた光の量に応じて変化する。また、第1のトランジスタ501は、酸化物半導体層でチャネル形成領域を形成したオフ電流が極めて低いトランジスタで構成されているため、後の選択動作(読み出し動作)を行うまで、配線505(FD)の電位を一定に保つことが可能である。

40

#### 【0072】

なお、第3の配線513(TX)の電位(信号602)を”Low”とする際に、第3の配線513(TX)と配線505(FD)との間ににおける寄生容量により、配線505(

50

F D ) の電位に変化が生じことがある。当該電位の変化量が大きい場合は、蓄積動作中にフォトダイオード 5 2 0 が生成した電荷量を正確に取得できることになる。当該電位の変化量を低減するには、第 1 のトランジスタ 5 0 1 のゲート - ソース（もしくはゲート - ドレイン）間容量を低減する、第 2 のトランジスタ 5 0 2 のゲート容量を増大する、配線 5 0 5 ( F D ) に保持容量を設ける、などの対策が有効である。なお、本実施の形態では、これらの対策により当該電位の変化を無視できるものとしている。

#### 【 0 0 7 3 】

時刻 D に、第 4 の配線 5 1 4 ( S E ) の電位（信号 6 0 3 ）を " H i g h " にすると、第 3 のトランジスタ 5 0 3 が導通して選択動作が開始され、第 1 の配線 5 1 1 ( G N D ) と第 2 の配線 5 1 2 ( O U T ) が、第 2 のトランジスタ 5 0 2 と第 3 のトランジスタ 5 0 3 とを介して導通する。そして、第 2 の配線 5 1 2 ( O U T ) の電位（信号 6 0 5 ）は、低下していく。なお、第 2 の配線 5 1 2 ( O U T ) のプリチャージは、時刻 D 以前に終了しておけばよい。ここで、第 2 の配線 5 1 2 ( O U T ) の電位（信号 6 0 5 ）が低下する速さは、第 2 のトランジスタ 5 0 2 のソースとドレイン間の電流に依存する。すなわち、蓄積動作中にフォトダイオード 5 2 0 に照射されている光の量に応じて変化する。10

#### 【 0 0 7 4 】

時刻 E において、第 4 の配線 5 1 4 ( S E ) の電位（信号 6 0 3 ）を " L o w " にすると、第 3 のトランジスタ 5 0 3 が遮断されて選択動作は終了し、第 2 の配線 5 1 2 ( O U T ) の電位（信号 6 0 5 ）は、一定値となる。ここで、一定値となる値は、フォトダイオード 5 2 0 に照射されていた光の量に応じて変化する。したがって、第 2 の配線 5 1 2 ( O U T ) の電位を取得することで、蓄積動作中にフォトダイオード 5 2 0 に照射されていた光の量を知ることができる。20

#### 【 0 0 7 5 】

より具体的には、フォトダイオード 5 2 0 に照射されている光が強いと、配線 5 0 5 ( F D ) の電位は低くなり、第 2 のトランジスタ 5 0 2 のゲート電圧は低くなるので、第 2 の配線 5 1 2 ( O U T ) の電位（信号 6 0 5 ）はゆっくりと低下する。したがって、第 2 の配線 5 1 2 ( O U T ) からは比較的高い電位を読み出すことができる。

#### 【 0 0 7 6 】

逆に、フォトダイオード 5 2 0 に照射されている光が弱いと、配線 5 0 5 ( F D ) の電位は高くなり、第 2 のトランジスタ 5 0 2 のゲート電圧は高くなるので、第 2 の配線 5 1 2 ( O U T ) の電位（信号 6 0 5 ）は速く低下する。したがって、第 2 の配線 5 1 2 ( O U T ) からは比較的低い電位を読み出すことができる。30

#### 【 0 0 7 7 】

次に、図 3 ( B ) の回路 5 5 2 の動作の例について図 5 ( B ) に示すタイミングチャートを用いて説明する。

#### 【 0 0 7 8 】

時刻 A において、第 5 の配線 5 1 5 ( R S ) の電位（信号 6 0 1 ）を " L o w " 、第 3 の配線 5 1 3 ( T X ) の電位（信号 6 0 2 ）を " H i g h " とすると、フォトダイオード 5 2 0 に順方向バイアスが印加され、配線 5 0 5 ( F D ) の電位（信号 6 0 4 ）が " L o w " となる。すなわち、電荷蓄積部の電位はリセット状態となる。以上がリセット動作の開始である。なお、第 2 の配線 5 1 2 ( O U T ) の電位（信号 6 0 5 ）は、 " H i g h " にプリチャージしておく。40

#### 【 0 0 7 9 】

時刻 B において、第 5 の配線 5 1 5 ( R S ) の電位（信号 6 0 1 ）を " H i g h " 、第 3 の配線 5 1 3 ( T X ) の電位（信号 6 0 2 ）を " H i g h " とするとリセット動作が終了し、蓄積動作が開始される。ここで、フォトダイオード 5 2 0 には逆方向バイアスが印加されるため、逆方向電流により、配線 5 0 5 ( F D ) の電位（信号 6 0 4 ）が増加し始める。フォトダイオード 5 2 0 は、光が照射されると逆方向電流が増大するので、照射される光の量に応じて配線 5 0 5 ( F D ) の電位（信号 6 0 4 ）の増加速度は変化する。すなわち、フォトダイオード 5 2 0 に照射する光の量に応じて、第 2 のトランジスタ 5 0 2 の50

ソースとドレイン間のチャネル抵抗が変化する。

【0080】

時刻C以降の動作は、図5(A)のタイミングチャートの説明を参照することができ、時刻Eにおいて、第2の配線512(OUT)の電位(信号605)を取得することで、蓄積動作中にフォトダイオード520に照射されていた光の量を知ることができる。

【0081】

また、画素回路は、図6(A)、(B)に示す構成であってもよい。

【0082】

図6(A)に示す回路553は、回路551の構成に第4のトランジスタ504が加えられた構成であり、当該トランジスタのゲートは第5の配線515(RS)と電気的に接続され、ソースまたはドレインの一方は配線505(FD)と電気的に接続され、ソースまたはドレインの他方は第7の配線517と電気的に接続され、フォトダイオード520のアノードが第6の配線516に電気的に接続される。ここで、第6の配線516はフォトダイオード520に常時逆バイアスを印加するための信号線(低電位線)である。また、第7の配線517は配線505(FD)を高電位にリセットするための信号線(高電位線)である。

10

【0083】

第4のトランジスタ504は、配線505(FD)をリセットするためのリセットトランジスタとして機能する。したがって、図3(A)に示す回路551とは異なり、フォトダイオード520を介したリセット動作は行われず、該フォトダイオードは常時逆バイアスが印加されている。配線505(FD)のリセットは、第5の配線515(RS)の電位を”High”に制御することで行うことができ、回路553は、図3(A)に示す回路551と同じく、図5(A)に示すタイミングチャートで動作することができる。

20

【0084】

また、図6(B)に示す回路554は、図3(B)に示す回路552の構成に第4のトランジスタ504が加えられた構成であり、当該トランジスタのゲートは第5の配線515(RS)と電気的に接続され、ソースまたはドレインの一方は配線505(FD)と電気的に接続され、ソースまたはドレインの他方は第7の配線517と電気的に接続され、フォトダイオード520のカソードが第6の配線516に電気的に接続される。ここで、第6の配線516はフォトダイオード520に常時逆バイアスを印加するための信号線(高電位線)である。また、第7の配線517は配線505(FD)を低電位にリセットするための信号線(低電位線)である。

30

【0085】

第4のトランジスタ504は、配線505(FD)をリセットするためのリセットトランジスタとして機能する。したがって、図3(B)に示す回路552とは異なり、フォトダイオード520を介したリセット動作は行われず、該フォトダイオードは常時逆バイアスが印加されている。配線505(FD)のリセットは、第5の配線515(RS)の電位を”High”に制御することで行うことができ、回路554は、図5(C)に示すタイミングチャートで動作することができる。

40

【0086】

なお、図6(A)、(B)では、第1のトランジスタ501が設けられている構成の例を示したが、本発明の実施形態の一態様は、これに限定されない。図19(A)、(B)に示すように、第1のトランジスタ501を設けない構成としてもよい。

【0087】

なお、第4のトランジスタ504は、非晶質シリコン、微結晶シリコン、多結晶シリコン、単結晶シリコンなどのシリコン半導体を用いて形成することも可能であるが、リーク電流が大きいと、電荷蓄積部で電荷が保持できる時間が十分でなくなってしまう。したがって、第1のトランジスタ501と同じく、オフ電流が極めて小さい特性を有する酸化物半導体で形成したトランジスタを用いることが好ましい。

【0088】

50

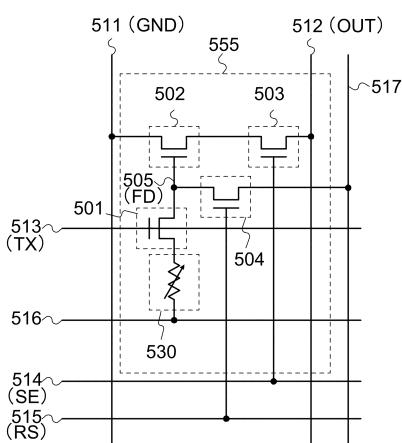

また、画素回路は、図7に示す構成であってもよい。図7に示す回路555は、図6(A)または図6(B)の構成における受光素子をフォトダイオードから可変抵抗素子530に置き換えた構成である。当該可変抵抗素子には、一対の電極と、その一対の電極間に設けられたi型の導電型を有する半導体層を用いることができる。

#### 【0089】

例えば、当該半導体層としてi型非晶質シリコン層を用いると、可視光が照射されることにより抵抗が変化するため、フォトダイオードを用いた場合と同様に配線505(FD)の電位を変化させることができ、蓄積動作中に可変抵抗素子530に照射されていた光の量を知ることができる。また、i型の導電型を有する半導体層として、バンドギャップが3eV以上の酸化物半導体層を用いてもよい。当該酸化物半導体層は、紫外光が照射されることにより抵抗が変化するため、配線505(FD)の電位を変化させることができ、蓄積動作中に可変抵抗素子530に照射されていた光の量を知ることができる。なお、可変抵抗素子530に照射される光の波長を選択するには、シンチレータの種類を変更すればよい。

10

#### 【0090】

図7に示す回路555は、第6の配線516の電位を”Low”、第7の配線517の電位を”High”とすれば、図5(A)のタイミングチャートに従って動作させることができる。また、第6の配線516の電位を”High”、第7の配線517の電位を”Low”とすることで、図5(C)のタイミングチャートに従って動作させることができる。

。

20

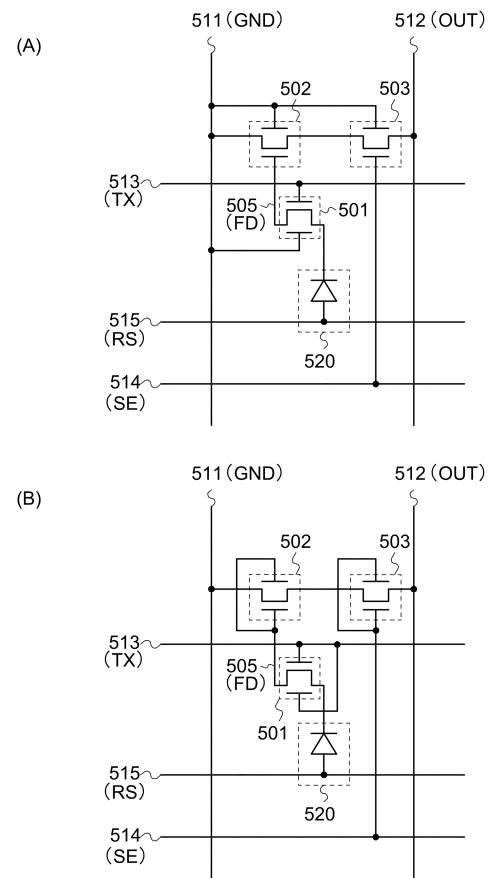

#### 【0091】

また、画素回路に用いるトランジスタは、図8(A)または図8(B)に示すように、第1のトランジスタ501、第2のトランジスタ502、および第3のトランジスタ503にバックゲートを設けた構成であってもよい。図8(A)はフロントゲートと同じ電位がバックゲートに印加される構成であり、オン電流を増加させることができる。また、図8(B)はバックゲートに定電位を印加する構成であり、しきい値電圧を制御することができる。なお、図8(B)においては、バックゲートが第1の配線511(GND)と電気的に接続される構成を例示したが、定電位が供給される別の配線と電気的に接続されてもよい。なお、図8(A)、(B)では回路551においてトランジスタにバックゲートを設けた例を示したが、回路552、回路553、回路554に示す回路の全てのトランジスタにバックゲートを設けてもよい。また、一つの画素回路に含まれるトランジスタに対し、フロントゲートと同じ電位がバックゲートに印加される構成、バックゲートに定電位を印加する構成、またはバックゲートを設けない構成を必要に応じて任意に組み合わせた回路構成としてもよい。

30

#### 【0092】

図9は、図6(A)、(B)、または図7に示す各回路を画素回路110として用い、画素回路110をm行n列(m、nはともに1以上の整数)のマトリクス状に配置した場合の各配線との接続形態の一例である。第7の配線517は全ての画素回路で共用することができる。

40

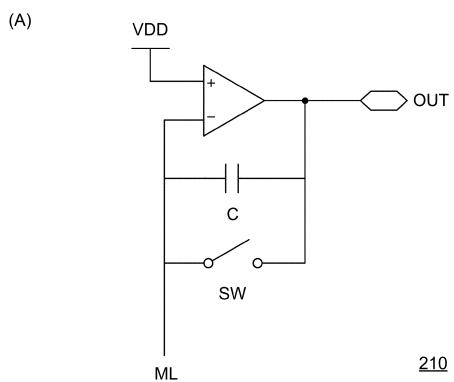

#### 【0093】

図1に示す電流検出回路210には、例えば図10(A)に示すような回路を用いることができる。第2の配線512(OUT)は図10(A)に示す配線MLに接続され、図10(B)に示すようなスイッチ(SW)をオン動作の後、オフ動作をさせることで出力端子(OUT)から照度に応じた電圧信号を得ることができる。また、電流検出回路210の出力端子(OUT)はA/Dコンバータ220(図1参照)の入力端子に接続され、当該電圧信号はデジタル信号に変換される。

#### 【0094】

演算回路部310は特に限定されず、本発明の一態様の動作が行える構成を有していればよい。

#### 【0095】

50

また、第1の記憶回路部320および第2の記憶回路部330も特に限定されず、揮発性メモリを有する回路、不揮発性メモリを有する回路のどちらであってもよい。例えば、書き換えが任意の間隔で行われる第2のルックアップテーブル322を記憶する第1の記憶回路部320には不揮発性メモリを有する回路を用い、画像情報(照度情報)の高速な書き込みおよび読み出しが必要とされる第2の記憶回路部330には揮発性メモリを有する回路を用いることができる。

#### 【0096】

なお、図1では第1の記憶回路部320および第2の記憶回路部330の二つの記憶回路部を有する構成を例示したが、図11に示すように撮像装置100が有する記憶回路部を第1の記憶回路部320のみとし、当該記憶回路部に第1のルックアップテーブル321、第2のルックアップテーブル322、第2のルックアップテーブルの情報を取得するためのプログラム323、および演算回路部310が出力する画像情報を格納する領域331を有する構成としてもよい。10

#### 【0097】

また、図12に示すように、第2のルックアップテーブルの情報を取得するためのプログラム323を撮像装置100の外部の記憶装置340等に格納してもよい。例えば、演算回路部310を制御するコンピュータ等に接続された記憶媒体などに当該プログラムが格納されていてもよい。

#### 【0098】

また、図示はしないが、第1のルックアップテーブル321、第2のルックアップテーブル322、第2のルックアップテーブルの情報を取得するためのプログラム323、および演算回路部310が出力する画像情報を格納する領域331のそれぞれに対して一つずつ記憶回路部を割り当ててもよい。このとき、第1のルックアップテーブル321に割り当てる記憶回路部は、リードオンリーメモリ(ROM)であってもよい。20

#### 【0099】

次に、画素回路に図3(A)の回路551を用いた場合の第2のルックアップテーブル322を更新する手順の一例について、図13に示すフロー・チャートを用いて説明する。第2のルックアップテーブル322の更新はプログラム323を演算回路部310で実行することに行われる。

#### 【0100】

まず、第2の配線512(OUT)の電位をリセットする(S301)。例えば、第2の配線512(OUT)を高電位にプリチャージすればよい。

#### 【0101】

次に、第2のルックアップテーブル322で規定されている電荷蓄積部に供給される複数の異なる電位を電位Xとして、電位Xを第5の配線515(RS)に印加するステップ(S303)と、電流検出回路で第2の配線512(OUT)の電位を電圧信号に変換するステップ(S304)と、A/Dコンバータで当該電圧信号をデジタル信号に変換するステップ(S305)と、第2のルックアップテーブル322に当該デジタル信号を書き込むステップ(S306)とを繰り返す。

#### 【0102】

なお、第2のルックアップテーブル322への書き込みは、全ての情報を取得した後に行つてもよい。第2のルックアップテーブル322に書き込まれた情報は、具体的には第2のトランジスタ502の電流-電圧特性に相当する。

#### 【0103】

上述した第2のルックアップテーブル322の更新方法は、画素回路に図3(B)の回路552を用いた場合にも適用できる。

#### 【0104】

また、画素回路に、図6(A)、(B)に示す回路553、回路554、図7に示す回路555を用いる場合は、図13に示す第2のステップ(S302)で第3のトランジスタ503および第4のトランジスタ504をオンとし、第3のステップ(S303)で電位4050

Xを第7の配線517に印加する方法を用いればよい。

【0105】

以上の本発明の一態様を用いることによって、画素回路が有するトランジスタの電気特性が変動しても、補正によって正確な照度情報を得ることができる撮像装置を提供することができる。

【0106】

なお、本明細書等においては、能動素子（トランジスタ、ダイオードなど）、受動素子（容量素子、抵抗素子など）などが有するすべての端子について、その接続先を特定しなくても、当業者であれば、本発明の一態様を構成することは可能な場合がある。つまり、接続先を特定しなくとも、本発明の一態様が明確であると言える。そして、接続先が特定された内容が、本明細書等に記載されている場合、接続先を特定しない本発明の一態様が、本明細書等に記載されていると判断することが可能な場合がある。特に、端子の接続先が複数のケース考えられる場合には、その端子の接続先を特定の箇所に限定する必要はない。したがって、能動素子（トランジスタ、ダイオードなど）、受動素子（容量素子、抵抗素子など）などが有する一部の端子についてのみ、その接続先を特定することによって、本発明の一態様を構成することが可能な場合がある。

10

【0107】

なお、本明細書等においては、ある回路について、少なくとも接続先を特定すれば、当業者であれば、発明を特定することが可能な場合がある。または、ある回路について、少なくとも機能を特定すれば、当業者であれば、発明を特定することが可能な場合がある。つまり、機能を特定すれば、本発明の一態様が明確であると言える。そして、機能が特定された本発明の一態様が、本明細書等に記載されていると判断することが可能な場合がある。したがって、ある回路について、機能を特定しなくても、接続先を特定すれば、本発明の一態様として開示されているものであり、本発明の一態様を構成することが可能である。または、ある回路について、接続先を特定しなくとも、機能を特定すれば、本発明の一態様として開示されているものであり、本発明の一態様を構成することが可能である。

20

【0108】

なお、本明細書等においては、ある一つの実施の形態において述べる図または文章において、その一部分を取り出して、本発明の一態様を構成することは可能である。したがって、ある部分を述べる図または文章が記載されている場合、その一部分の図または文章を取り出した内容も、本発明の一態様として開示されているものであり、本発明の一態様を構成することが可能であるものとする。そのため、例えば、能動素子（トランジスタ、ダイオードなど）、配線、受動素子（容量素子、抵抗素子など）、導電層、絶縁層、半導体層、有機材料、無機材料、部品、装置、動作方法、製造方法などが単数又は複数記載された図面または文章において、その一部分を取り出して、本発明の一態様を構成することが可能であるものとする。例えば、N個（Nは整数）の回路素子（トランジスタ、容量素子等）を有して構成される回路図から、M個（Mは整数で、M < N）の回路素子（トランジスタ、容量素子等）を抜き出して、本発明の一態様を構成することは可能である。別の例としては、N個（Nは整数）の層を有して構成される断面図から、M個（Mは整数で、M < N）の層を抜き出して、本発明の一態様を構成することは可能である。さらに別の例としては、N個（Nは整数）の要素を有して構成されるフローチャートから、M個（Mは整数で、M < N）の要素を抜き出して、本発明の一態様を構成することは可能である。

30

【0109】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

【0110】

（実施の形態2）

本実施の形態では、実施の形態1で説明した画素回路の駆動方法の一例について説明する。

【0111】

40

50

実施の形態 1 で説明したように、画素回路の動作は、リセット動作、蓄積動作、および選択動作の繰り返しである。X 線等の放射線を用いた撮像装置においては、生体への影響を考慮し、放射線の照射時間を極力短くすることが好ましい。放射線の照射時間の短縮し、短時間での撮像を実現するためには、全画素回路のリセット動作、蓄積動作、選択動作を速やかに実行することが必要である。

#### 【 0 1 1 2 】

そのため、撮像方法としては、図 14 ( A ) のタイミングチャートに示すようなグローバルシャッタ方式での駆動方法を用いることが好ましい。なお、図 14 ( A ) は、マトリクス状に複数の画素回路を有し、当該画素回路に図 3 ( A ) の回路 551 を有する撮像装置を例として、第 1 行目から最終行の回路 551 のうち、第 1 行目から第 3 行目までの動作を説明するものである。なお、下記の動作説明は、図 6 ( A ) の回路 553 、図 7 の回路 555 、および図 8 ( A ) 、( B ) に示す回路にも適用することができる。

10

#### 【 0 1 1 3 】

図 14 ( A ) において、信号 701 、信号 702 、信号 703 は、第 1 行目、第 2 行目、第 3 行目の各画素回路に接続された第 5 の配線 515 ( R S ) に入力される信号である。また、信号 704 、信号 705 、信号 706 は、第 1 行目、第 2 行目、第 3 行目の各画素回路に接続された第 3 の配線 513 ( T X ) に入力される信号である。また、信号 707 、信号 708 、信号 709 は、第 1 行目、第 2 行目、第 3 行目の各画素回路に接続された第 4 の配線 514 ( S E ) に入力される信号である。

#### 【 0 1 1 4 】

また、期間 710 は、1 回の撮像に要する期間である。また、期間 711 は、各行の画素回路がリセット動作を同時にしている期間であり、期間 720 は、各行の画素回路が蓄積動作を同時にしている期間である。なお、選択動作は各行の画素回路で順次行われる。一例として、期間 731 は、第 1 行目の画素回路が選択動作を行っている期間である。このように、グローバルシャッタ方式では、全画素回路で略同時にリセット動作が行われた後、全画素回路で略同時に蓄積動作が行われ、1 行毎に順次読み出し動作が行われる。

20

#### 【 0 1 1 5 】

つまり、グローバルシャッタ方式では、全ての画素回路において蓄積動作が略同時に行われているため、各行の画素回路における撮像の同時性が確保される。したがって、放射線照射と蓄積動作とを同期させることで、被写体へ放射線を照射する時間を短くすることができる。すなわち、期間 720 のみに放射線照射を行えばよい。

30

#### 【 0 1 1 6 】

一方、図 14 ( B ) は、ローリングシャッタ方式を用いた場合のタイミングチャートである。なお、期間 810 は 1 回の撮像に要する期間である。期間 811 、期間 812 、期間 813 はそれぞれ、第 1 行目、第 2 行目、第 3 行目のリセット期間であり、期間 821 、期間 822 、期間 823 はそれぞれ、第 1 行目、第 2 行目、第 3 行目の蓄積動作期間である。また、期間 831 は、1 行目の画素回路が選択動作を行っている期間ある。このように、ローリングシャッタ方式では、蓄積動作が全ての画素回路では同時に行われず、行毎に順次行われるため、各行の画素回路における撮像の同時性が確保されない。したがって、放射線照射と蓄積動作とを同期させたとしても、合計の放射線照射期間 820 がグローバルシャッタ方式よりも長くなってしまう。ただし、高速動作をすることなどによって、ローリングシャッタ方式でも放射線照射時間を短くすることができるため、本発明の一態様の撮像装置の駆動方式として、ローリングシャッタ方式を用いてもよい。

40

#### 【 0 1 1 7 】

グローバルシャッタ方式を実現するためには、蓄積動作が終了した後も、読み出しまでの間に各画素回路における配線 505 ( F D ) の電位を長時間保つ必要がある。配線 505 ( F D ) の電位の長時間の保持は、前述したように第 1 のトランジスタ 501 に極めてオフ電流の低い、チャネル形成領域を酸化物半導体で形成したトランジスタを用いることで実現できる。一方、第 1 のトランジスタ 501 にチャネル形成領域をシリコン半導体などで形成したトランジスタを適用した場合は、オフ電流が高いために配線 505 ( F D ) の

50

電位を長時間保持できず、グローバルシャッタ方式を用いることが困難となる。

**【0118】**

以上のように、画素回路にチャネル形成領域を酸化物半導体で形成したトランジスタを用いることでグローバルシャッタ方式を容易に実現することができ、被写体に照射する放射線量が少ない撮像装置を提供することができる。

**【0119】**

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することができる。

**【0120】**

(実施の形態3)

10

本実施の形態では、画素回路のレイアウトの一例について、図15および図16を用いて説明する。

**【0121】**

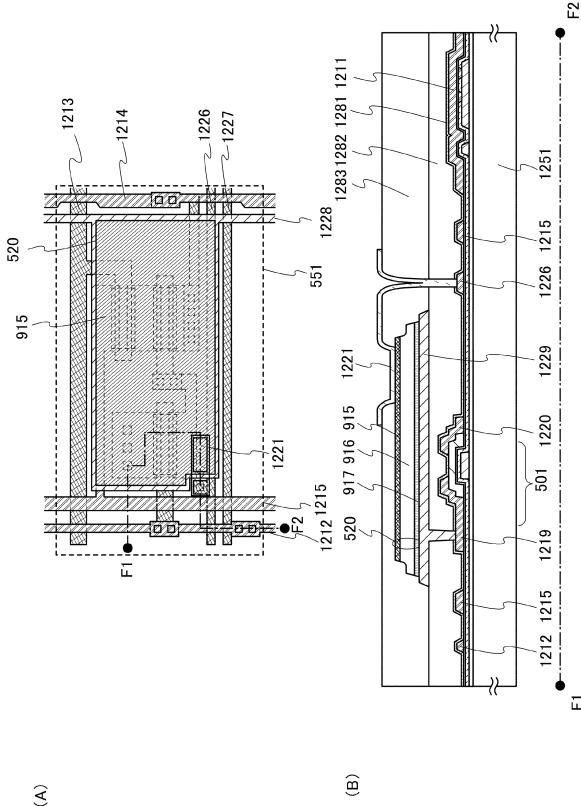

図15(A)は、図3(A)に示した回路551の上面図を示し、図15(B)は、図15(A)の一点鎖線E1-E2における断面図を示す。

**【0122】**

回路551は、第5の配線515(RS)として機能する導電膜1211と、第3の配線513(TX)として機能する導電膜1212と、第4の配線514(SE)として機能する導電膜1213と、第1の配線511(GND)として機能する導電膜1214と、第2の配線512(OUT)として機能する導電膜1215を有している。

20

**【0123】**

回路551が有するフォトダイオード520は、順に積層されたp型の半導体膜915、i型の半導体膜916、およびn型の半導体膜917を有している。導電膜1211は、フォトダイオード520のアノードとして機能するp型の半導体膜915に電気的に接続されている。

**【0124】**

回路551が有する導電膜1218は、第1のトランジスタ501のゲート電極として機能しており、さらに、導電膜1212に電気的に接続されている。導電膜1219は、第1のトランジスタ501のソース電極またはドレイン電極の一方として機能する。導電膜1220は、第1のトランジスタ501のソース電極またはドレイン電極の他方として機能する。導電膜1221は、n型の半導体膜917と、導電膜1219とに電気的に接続されている。導電膜1222は、第2のトランジスタ502のゲート電極として機能しており、さらに、導電膜1220に電気的に接続されている。

30

**【0125】**

回路551が有する導電膜1223は、第2のトランジスタ502のソース電極またはドレイン電極の一方として機能する。導電膜1224は、第2のトランジスタ502のソース電極またはドレイン電極の他方、および第3のトランジスタ503のソース電極またはドレイン電極の一方として機能する。導電膜1214は、第3のトランジスタ503のソース電極またはドレイン電極の他方として機能する。導電膜1213は、第3のトランジスタ503のゲート電極としても機能する。導電膜1225は、導電膜1223および導電膜1214に電気的に接続されている。

40

**【0126】**

なお、図15では、回路551が有する導電膜1226は、第5の配線515(RS)として機能する導電膜1211に電気的に接続されている。また、回路551が有する導電膜1227は、第3の配線513(TX)として機能する導電膜1212に電気的に接続されている。

**【0127】**

導電膜1213、導電膜1218、導電膜1222、導電膜1225、導電膜1226、導電膜1227は、絶縁表面上に形成された一つの導電膜を所望の形状に加工することで形成することができる。導電膜1213、導電膜1218、導電膜1222、導電膜12

50

25、導電膜1226、導電膜1227上にはゲート絶縁膜1228が形成されている。さらに、導電膜1211、導電膜1212、導電膜1214、導電膜1215、導電膜1219、導電膜1220、導電膜1223、導電膜1224は、ゲート絶縁膜1228上に形成された一つの導電膜を所望の形状に加工することで形成することができる。

【0128】

また、導電膜1211、導電膜1212、導電膜1214、導電膜1215、導電膜1219、導電膜1220、導電膜1223、導電膜1224の上には、絶縁膜1281および絶縁膜1282が形成されている。絶縁膜1281および絶縁膜1282の上に、導電膜1221が形成される。

【0129】

第1のトランジスタ501の半導体層1250には、酸化物半導体を用いることが好ましい。フォトダイオード520に光が照射されることにより生成された電荷を電荷蓄積部で長時間保持するためには、電荷蓄積部と電気的に接続される第1のトランジスタ501をオフ電流が極めて低いトランジスタで構成する必要がある。そのため、半導体層1250として酸化物半導体材料を用いることで回路551の性能を高めることができる。なお、電荷蓄積部とは、回路551における配線505を差し、図15では導電膜1220に相当する。なお、第2のトランジスタ502および第3のトランジスタ503も第1のトランジスタ501と同様の構成であってもよい。

【0130】

また、回路551は、図16(A)、(B)に示すように、トランジスタなどの素子とフォトダイオード520が重畳する構成としてもよい。このような構成とすることで、画素密度を高めることができ、撮像装置の解像度を高めることができる。また、フォトダイオード520の面積を増大させることができるために、撮像装置の感度を高めることもできる。なお、図16(A)は、回路551の上面図を示し、図16(B)は、図16(A)の一点鎖線F1-F2における断面図である。

【0131】

図16(A)、(B)に示す回路551において、第1のトランジスタ501のソース電極またはドレイン電極の一方として機能する導電膜1219とフォトダイオード520のカソードとして機能するn型の半導体膜917は、導電膜1229を介して電気的に接続されている。また、フォトダイオード520のアノードとして機能するp型の半導体膜915は、導電膜1221を介して第5の配線515(RS)と接する導電膜1226と電気的に接続されている。また、フォトダイオード520を保護する絶縁膜1283が形成されている。これらの点、およびトランジスタなどの素子とフォトダイオード520が重畳する構成以外は、図15(A)、(B)に示す回路551と同様の構成とすることができます。

【0132】

なお、p型の半導体膜915と導電膜1226との電気的な接続は、導電膜1221で直接接続する例を示したが、絶縁膜1281、絶縁膜1282、および絶縁膜1283に形成した開口部を通じて導電膜1226と電気的に接する他の導電膜を設け、該導電膜と導電膜1221が電気的に接する構成としてもよい。

【0133】

また、図16に示すようなトランジスタなどの素子とフォトダイオードなどの受光素子が重畳する構成は、図3(B)に示す回路552、図6(A)、(B)に示す回路553、554、図7に示す回路555、および図8(A)、(B)に示す回路においても適用することができる。

【0134】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

【0135】

(実施の形態4)

10

20

30

40

50

本実施の形態では、実施の形態 1 乃至 3 で説明した回路に用いることのできる、オフ電流の著しく小さいトランジスタおよび該トランジスタを構成する材料について説明する。

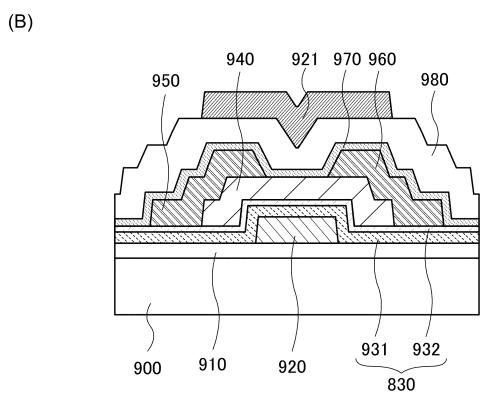

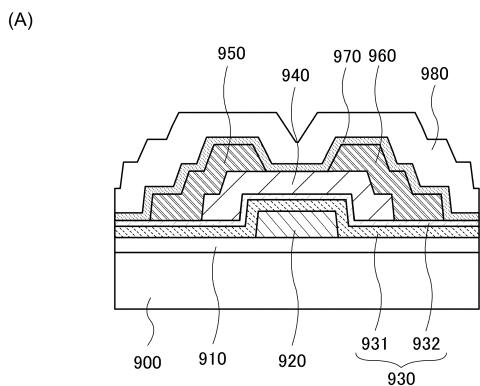

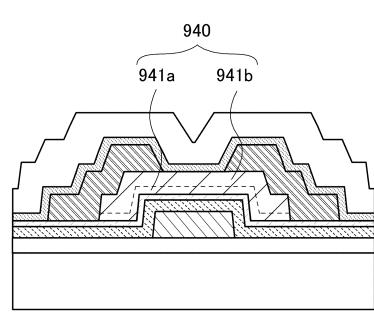

#### 【 0 1 3 6 】

図 17 ( A ) は、本発明の一態様である撮像装置に用いることができる一例のトランジスタの断面図である。当該トランジスタは、基板 900 上に形成された下地絶縁膜 910 、当該下地絶縁膜上に形成されたゲート電極層 920 、当該ゲート電極層上に第 1 の絶縁膜 931 、第 2 の絶縁膜 932 の順で形成されたゲート絶縁膜 930 、当該ゲート絶縁膜上に形成された酸化物半導体層 940 、当該酸化物半導体層の一部と接するソース電極層 950 およびドレイン電極層 960 を有する。また、ゲート絶縁膜 930 、酸化物半導体層 940 、およびソース電極層 950 およびドレイン電極層 960 上に絶縁層 970 が形成されていてもよい。また、当該絶縁層上に絶縁層 980 が形成されていてもよい。

10

#### 【 0 1 3 7 】

また、本発明の一態様のトランジスタは、図 17 ( B ) に示すように、絶縁層 970 または絶縁層 980 上にゲート電極層 920 および酸化物半導体層 940 と重なるように導電膜 921 を備えていてもよい。当該導電膜を第 2 のゲート電極層 ( バックゲート ) として用いることで、オン電流の増加や、しきい値電圧の制御を行うことができる。オン電流を増加させるには、例えば、ゲート電極層 920 と導電膜 921 を同電位とし、デュアルゲートトランジスタとして駆動させればよい。また、しきい値電圧の制御を行うには、ゲート電極層 920 とは異なる定電位を導電膜 921 に供給すればよい。

20

#### 【 0 1 3 8 】

本発明の一態様である撮像装置では、上述したように酸化物半導体を活性層に用いる。酸化物半導体層を用いたトランジスタは非晶質シリコンを用いたトランジスタよりも移動度が高いため、トランジスタを小さくすることが容易であり、画素を小さくすることができる。すなわち、撮像装置の解像度を高めることができる。

#### 【 0 1 3 9 】

ゲート絶縁膜 930 を構成する第 1 の絶縁膜 931 には、窒化珪素膜を用いることができる。当該窒化珪素膜の膜厚は 100 nm 乃至 400 nm であることが好ましい。また、ゲート絶縁膜 930 を構成する第 2 の絶縁膜 932 には、酸化珪素膜を用いることができる。当該酸化珪素膜の膜厚は 5 nm 乃至 20 nm であることが好ましい。ゲート絶縁膜 930 を上記材料および膜厚で形成することで、X 線等の放射線の照射に対して電気特性の変動の少ないトランジスタを形成することができる。

30

#### 【 0 1 4 0 】

なお、図 17 ( A ) 、 ( B ) ではチャネルエッチ型のボトムゲート構造を一例として示したが、チャネル保護型のボトムゲート構造、ノンセルフアライン型のトップゲート構造、またはセルフアライン型のトップゲート構造であってもよい。

#### 【 0 1 4 1 】

オフ電流の著しく小さいトランジスタを形成するには、半導体層に酸化物半導体などのシリコン半導体よりもバンドギャップの広く、真性キャリア密度がシリコンよりも低い半導体材料を用いることが好ましい。

#### 【 0 1 4 2 】

上記半導体材料の一例としては、酸化物半導体の他に、炭化珪素 ( SiC ) 、窒化ガリウム ( GaN ) などの化合物半導体などがあるが、酸化物半導体は、炭化珪素や窒化ガリウムと異なり、スパッタ法や湿式法により作製可能であり、量産性に優れるといった利点がある。また、酸化物半導体は室温でも成膜が可能なため、ガラス基板上への成膜、或いはシリコンを用いた集積回路上への成膜が可能である。また、基板の大型化にも対応が可能である。よって、上述したワイドギャップ半導体の中でも、特に酸化物半導体は量産性が高いというメリットを有する。また、トランジスタの性能 ( 例えば電界効果移動度 ) を向上させるために結晶性の酸化物半導体を得ようとする場合でも、250 から 800 の熱処理によって容易に結晶性の酸化物半導体を得ることができる。

40

#### 【 0 1 4 3 】

10

20

30

40

50

また、電子供与体（ドナー）となる不純物が低減され、なかつ酸素欠損が低減されることにより高純度化された酸化物半導体（purified OS）の導電型は、i型またはi型に限りなく近い。そのため、上記酸化物半導体を用いたトランジスタは、オフ電流が著しく低いという特性を有する。また、酸化物半導体のバンドギャップは、2 eV以上、好ましくは2.5 eV以上、より好ましくは3 eV以上である。水分または水素などの不純物濃度が十分に低減され、なかつ酸素欠損が低減されることにより高純度化された酸化物半導体膜を用いることにより、トランジスタのオフ電流を下げることができる。

#### 【0144】

酸化物半導体層において、水素、窒素、炭素、シリコン、および主成分以外の金属元素は不純物となる。例えば、水素および窒素は、ドナー準位の形成に寄与し、キャリア密度を増大させてしまう。また、シリコンは、酸化物半導体層中で不純物準位を形成する。当該不純物準位はトラップとなり、トランジスタの電気特性を劣化させることがある。酸化物半導体層中や、他の層との界面において不純物濃度を低減させることが好ましい。

10

#### 【0145】

なお、酸化物半導体層をチャネルとするトランジスタに安定した電気特性を付与するためには、酸化物半導体層中の不純物濃度を低減し、酸化物半導体層を真性または実質的に真性にすることが有効である。ここで、実質的に真性とは、酸化物半導体層のキャリア密度が、 $1 \times 10^{17} / \text{cm}^3$ 未満であること、好ましくは $1 \times 10^{15} / \text{cm}^3$ 未満であること、さらに好ましくは $1 \times 10^{13} / \text{cm}^3$ 未満であることを指す。

#### 【0146】

酸化物半導体層を真性または実質的に真性とすることには、SIMS (Secondary Ion Mass Spectrometry) 分析において、例えば、酸化物半導体層のある深さにおいて、または、酸化物半導体層のある領域において、シリコン濃度を $1 \times 10^{19} \text{ atoms/cm}^3$ 未満、好ましくは $5 \times 10^{18} \text{ atoms/cm}^3$ 未満、さらに好ましくは $1 \times 10^{18} \text{ atoms/cm}^3$ 未満とする部分を有することとする。また、水素濃度は、例えば、酸化物半導体層のある深さにおいて、または、酸化物半導体層のある領域において、 $2 \times 10^{20} \text{ atoms/cm}^3$ 以下、好ましくは $5 \times 10^{19} \text{ atoms/cm}^3$ 以下、より好ましくは $1 \times 10^{19} \text{ atoms/cm}^3$ 以下、さらに好ましくは $5 \times 10^{18} \text{ atoms/cm}^3$ 以下とする部分を有することとする。また、窒素濃度は、例えば、酸化物半導体層のある深さにおいて、または、酸化物半導体層のある領域において、 $5 \times 10^{19} \text{ atoms/cm}^3$ 未満、好ましくは $5 \times 10^{18} \text{ atoms/cm}^3$ 未満以下、より好ましくは $1 \times 10^{18} \text{ atoms/cm}^3$ 以下、さらに好ましくは $5 \times 10^{17} \text{ atoms/cm}^3$ 以下とする部分を有することとする。

20

#### 【0147】

また、酸化物半導体層が結晶を含む場合、シリコンや炭素が高濃度で含まれると、酸化物半導体層の結晶性を低下させことがある。酸化物半導体層の結晶性を低下させないためには、例えば、酸化物半導体層のある深さにおいて、または、酸化物半導体層のある領域において、シリコン濃度を $1 \times 10^{19} \text{ atoms/cm}^3$ 未満、好ましくは $5 \times 10^{18} \text{ atoms/cm}^3$ 未満、さらに好ましくは $1 \times 10^{18} \text{ atoms/cm}^3$ 未満とする部分を有することとする。また、例えば、酸化物半導体層のある深さにおいて、または、酸化物半導体層のある領域において、炭素濃度を $1 \times 10^{19} \text{ atoms/cm}^3$ 未満、好ましくは $5 \times 10^{18} \text{ atoms/cm}^3$ 未満、さらに好ましくは $1 \times 10^{18} \text{ atoms/cm}^3$ 未満とする部分を有することとする。

30

#### 【0148】

具体的に、高純度化された酸化物半導体膜をチャネル形成領域に用いたトランジスタのオフ電流が低いことは、いろいろな実験により証明できる。例えば、チャネル幅が $1 \times 10^6 \mu\text{m}$ でチャネル長が $10 \mu\text{m}$ の素子であっても、ソース電極とドレイン電極間の電圧（ドレイン電圧）が1 Vから10 Vの範囲において、オフ電流が、半導体パラメータアナライザの測定限界以下、すなわち $1 \times 10^{-13} \text{ A}$ 以下という特性を得ることができる。この場合、オフ電流をトランジスタのチャネル幅で規格化したオフ電流は、 $100 \text{ zA}/\mu$

40

50

$m$  以下であることが分かる。また、容量素子とトランジスタとを接続して、容量素子に流入または容量素子から流出する電荷を当該トランジスタで制御する回路を用いて、オフ電流の測定を行った。当該測定では、上記トランジスタに高純度化された酸化物半導体膜をチャネル形成領域に用い、容量素子の単位時間あたりの電荷量の推移から当該トランジスタのオフ電流を測定した。その結果、トランジスタのソース電極とドレイン電極間の電圧が 3 V の場合に、数十  $yA / \mu m$  という、さらに低いオフ電流が得られることが分かった。したがって、高純度化された酸化物半導体膜をチャネル形成領域に用いたトランジスタは、オフ電流が、結晶性を有するシリコンを用いたトランジスタに比べて著しく低い。

#### 【0149】

なお、酸化物半導体としては、少なくともインジウム ( $In$ ) あるいは亜鉛 ( $Zn$ ) を含むことが好ましい。特に  $In$  と  $Zn$  を含むことが好ましい。また、該酸化物半導体を用いたトランジスタの電気的特性のばらつきを減らすためのスタビライザーとして、それらに加えてガリウム ( $Ga$ ) を有することが好ましい。また、スタビライザーとしてスズ ( $Sn$ ) を有することが好ましい。また、スタビライザーとしてハフニウム ( $Hf$ ) を有することが好ましい。また、スタビライザーとしてアルミニウム ( $Al$ ) を有することが好ましい。

#### 【0150】

また、他のスタビライザーとして、ランタノイドである、ラントン ( $La$ )、セリウム ( $Ce$ )、プラセオジム ( $Pr$ )、ネオジム ( $Nd$ )、サマリウム ( $Sm$ )、ユウロピウム ( $Eu$ )、ガドリニウム ( $Gd$ )、テルビウム ( $Tb$ )、ジスプロシウム ( $Dy$ )、ホルミウム ( $Ho$ )、エルビウム ( $Er$ )、ツリウム ( $Tm$ )、イッテルビウム ( $Yb$ )、ルテチウム ( $Lu$ ) のいずれか一種または複数種を含んでいてもよい。

#### 【0151】

例えば、酸化物半導体として、酸化インジウム、酸化スズ、酸化亜鉛、 $In - Zn$  系酸化物、 $Sn - Zn$  系酸化物、 $Al - Zn$  系酸化物、 $Zn - Mg$  系酸化物、 $Sn - Mg$  系酸化物、 $In - Mg$  系酸化物、 $In - Ga$  系酸化物、 $In - Ga - Zn$  系酸化物 ( $IGZO$  とも表記する)、 $In - Al - Zn$  系酸化物、 $In - Sn - Zn$  系酸化物、 $Sn - Ga - Zn$  系酸化物、 $Al - Ga - Zn$  系酸化物、 $Sn - Al - Zn$  系酸化物、 $In - Hf - Zn$  系酸化物、 $In - La - Zn$  系酸化物、 $In - Ce - Zn$  系酸化物、 $In - Pr - Zn$  系酸化物、 $In - Nd - Zn$  系酸化物、 $In - Sm - Zn$  系酸化物、 $In - Eu - Zn$  系酸化物、 $In - Gd - Zn$  系酸化物、 $In - Tb - Zn$  系酸化物、 $In - Dy - Zn$  系酸化物、 $In - Ho - Zn$  系酸化物、 $In - Er - Zn$  系酸化物、 $In - Tm - Zn$  系酸化物、 $In - Yb - Zn$  系酸化物、 $In - Lu - Zn$  系酸化物、 $In - Sn - Ga - Zn$  系酸化物、 $In - Hf - Ga - Zn$  系酸化物、 $In - Al - Ga - Zn$  系酸化物、 $In - Sn - Al - Zn$  系酸化物、 $In - Sn - Hf - Zn$  系酸化物、 $In - Hf - Al - Zn$  系酸化物を用いることができる。また、上記酸化物半導体は、珪素を含んでいてもよい。

#### 【0152】

なお、例えば、 $In - Ga - Zn$  系酸化物とは、 $In$  と  $Ga$  と  $Zn$  を含む酸化物という意味であり、 $In$  と  $Ga$  と  $Zn$  の比率は問わない。また、 $In$  と  $Ga$  と  $Zn$  以外の金属元素を含んでいてもよい。 $In - Ga - Zn$  系酸化物は、無電界時の抵抗が十分に高くオフ電流を十分に小さくすることが可能であり、また、移動度も高いため、半導体装置に用いる半導体材料としては好適である。

#### 【0153】

例えば、 $In : Ga : Zn = 1 : 1 : 1 (= 1 / 3 : 1 / 3 : 1 / 3)$  あるいは  $In : Ga : Zn = 2 : 2 : 1 (= 2 / 5 : 2 / 5 : 1 / 5)$  の原子比の  $In - Ga - Zn$  系酸化物やその組成の近傍の酸化物を用いることができる。あるいは、 $In : Sn : Zn = 1 : 1 : 1 (= 1 / 3 : 1 / 3 : 1 / 3)$ 、 $In : Sn : Zn = 2 : 1 : 3 (= 1 / 3 : 1 / 6 : 1 / 2)$  あるいは  $In : Sn : Zn = 2 : 1 : 5 (= 1 / 4 : 1 / 8 : 5 / 8)$  の原子比の  $In - Sn - Zn$  系酸化物やその組成の近傍の酸化物を用いるとよい。

#### 【0154】

10

20

30

40

50

しかし、これらに限られず、必要とする電気的特性（移動度、しきい値電圧等）に応じて適切な組成のものを用いればよい。また、必要とする半導体特性を得るために、キャリア密度や不純物濃度、欠陥密度、金属元素と酸素の原子数比、原子間距離、密度等を適切なものとすることが好ましい。

#### 【0155】

なお、例えば、酸化物半導体膜は、In（インジウム）、Ga（ガリウム）、およびZn（亜鉛）を含むターゲットを用いたスパッタ法により形成することができる。In-Ga-Zn系酸化物半導体膜をスパッタ法で成膜する場合、好ましくは、原子数比がIn:Ga:Zn = 1:1:1、5:5:6、4:2:3、3:1:2、1:1:2、2:1:3、1:3:2、1:3:4、1:6:4または3:1:4で示されるIn-Ga-Zn系酸化物のターゲットを用いて酸化物半導体膜を成膜することで、結晶が形成されやすくなる。また、In、Ga、およびZnを含むターゲットの充填率は90%以上、好ましくは95%以上である。充填率の高いターゲットを用いることにより、成膜した酸化物半導体膜は緻密な膜となる。

#### 【0156】

なお、酸化物半導体としてIn-Zn系酸化物の材料を用いる場合、用いるターゲットの組成は、原子数比で、In:Zn = 50:1乃至1:2（モル数比に換算するとIn<sub>2</sub>O<sub>3</sub>:ZnO = 25:1乃至1:4）、好ましくはIn:Zn = 20:1乃至1:1（モル数比に換算するとIn<sub>2</sub>O<sub>3</sub>:ZnO = 10:1乃至1:2）、さらに好ましくはIn:Zn = 1.5:1乃至1.5:1（モル数比に換算するとIn<sub>2</sub>O<sub>3</sub>:ZnO = 3:4乃至1.5:2）とする。例えば、In-Zn系酸化物である酸化物半導体膜の形成に用いるターゲットは、原子数比がIn:Zn:O = X:Y:Zのとき、Z > 1.5X+Yとする。Znの比率を上記範囲に収めることで、移動度の向上を実現することができる。

#### 【0157】

また、酸化物半導体膜としてIn-Sn-Zn系酸化物半導体膜をスパッタ法で成膜する場合、好ましくは、原子数比がIn:Sn:Zn = 1:1:1、2:1:3、1:2:2、または20:45:35で示されるIn-Sn-Zn-Oターゲットを用いることができる。

#### 【0158】

以下では、酸化物半導体膜の構造について説明する。

#### 【0159】

なお、本明細書において、「平行」とは、二つの直線が-10°以上10°以下の角度で配置されている状態をいう。したがって、-5°以上5°以下の場合も含まれる。また、「垂直」とは、二つの直線が80°以上100°以下の角度で配置されている状態をいう。したがって、85°以上95°以下の場合も含まれる。

#### 【0160】

また、本明細書において、結晶が三方晶または菱面体晶である場合、六方晶系として表す。

#### 【0161】

酸化物半導体膜は、非単結晶酸化物半導体膜と単結晶酸化物半導体膜とに大別される。非単結晶酸化物半導体膜とは、CAAC-OS（C Axis Aligned Crystalline Oxide Semiconductor）膜、多結晶酸化物半導体膜、微結晶酸化物半導体膜、非晶質酸化物半導体膜などをいう。

#### 【0162】

まずは、CAAC-OS膜について説明する。

#### 【0163】

CAAC-OS膜は、複数の結晶部を有する酸化物半導体膜の一つであり、ほとんどの結晶部は、一边が100nm未満の立方体内に収まる大きさである。したがって、CAAC-OS膜に含まれる結晶部は、一边が10nm未満、5nm未満または3nm未満の立方

10

20

30

40

50

体内に収まる大きさの場合も含まれる。

**【0164】**

C AAC - OS 膜を透過型電子顕微鏡 (TEM : Transmission Electron Microscope) によって観察すると、明確な結晶部同士の境界、即ち結晶粒界（グレインバウンダリーともいう。）を確認することができない。そのため、C AAC - OS 膜は、結晶粒界に起因する電子移動度の低下が起こりにくいといえる。

**【0165】**

C AAC - OS 膜を、試料面と概略平行な方向から TEM によって観察（断面 TEM 観察）すると、結晶部において、金属原子が層状に配列していることを確認できる。金属原子の各層は、C AAC - OS 膜の膜を形成する面（被形成面ともいう。）または上面の凹凸を反映した形状であり、C AAC - OS 膜の被形成面または上面と平行に配列する。10

**【0166】**

一方、C AAC - OS 膜を、試料面と概略垂直な方向から TEM によって観察（平面 TEM 観察）すると、結晶部において、金属原子が三角形状または六角形状に配列していることを確認できる。しかしながら、異なる結晶部間で、金属原子の配列に規則性は見られない。

**【0167】**

断面 TEM 観察および平面 TEM 観察より、C AAC - OS 膜の結晶部は配向性を有していることがわかる。

**【0168】**

C AAC - OS 膜に対し、X 線回折 (XRD : X-Ray Diffraction) 装置を用いて構造解析を行うと、例えば InGaN<sub>0.4</sub> の結晶を有する C AAC - OS 膜の out-of-plane 法による解析では、回折角 ( $2\theta$ ) が  $31^\circ$  近傍にピークが現れる場合がある。このピークは、InGaN<sub>0.4</sub> の結晶の (009) 面に帰属されることから、C AAC - OS 膜の結晶が c 軸配向性を有し、c 軸が被形成面または上面に概略垂直な方向を向いていることが確認できる。20

**【0169】**

一方、C AAC - OS 膜に対し、c 軸に概略垂直な方向から X 線を入射させる in-plane 法による解析では、 $2\theta$  が  $56^\circ$  近傍にピークが現れる場合がある。このピークは、InGaN<sub>0.4</sub> の結晶の (110) 面に帰属される。InGaN<sub>0.4</sub> の単結晶酸化物半導体膜であれば、 $2\theta$  を  $56^\circ$  近傍に固定し、試料面の法線ベクトルを軸 (c 軸) として試料を回転させながら分析（スキャン）を行うと、(110) 面と等価な結晶面に帰属されるピークが 6 本観察される。これに対し、C AAC - OS 膜の場合は、 $2\theta$  を  $56^\circ$  近傍に固定して スキャンした場合でも、明瞭なピークが現れない。30

**【0170】**

以上のことから、C AAC - OS 膜では、異なる結晶部間では a 軸および b 軸の配向は不規則であるが、c 軸配向性を有し、かつ c 軸が被形成面または上面の法線ベクトルに平行な方向を向いていることがわかる。したがって、前述の断面 TEM 観察で確認された層状に配列した金属原子の各層は、結晶の ab 面に平行な面である。

**【0171】**

なお、結晶部は、C AAC - OS 膜を成膜した際、または加熱処理などの結晶化処理を行った際に形成される。上述したように、結晶の c 軸は、C AAC - OS 膜の被形成面または上面の法線ベクトルに平行な方向に配向する。したがって、例えば、C AAC - OS 膜の形状をエッチングなどによって変化させた場合、結晶の c 軸が C AAC - OS 膜の被形成面または上面の法線ベクトルと平行にならないこともある。40

**【0172】**

また、C AAC - OS 膜中の結晶化度が均一でなくてもよい。例えば、C AAC - OS 膜の結晶部が、C AAC - OS 膜の上面近傍からの結晶成長によって形成される場合、上面近傍の領域は、被形成面近傍の領域よりも結晶化度が高くなることがある。また、C AAC - OS 膜に不純物を添加する場合、不純物が添加された領域の結晶化度が変化し、部分50

的に結晶化度の異なる領域が形成されることもある。

#### 【0173】

なお、 $\text{InGaZnO}_4$  の結晶を有する CAAAC - OS 膜の out-of-plane 法による解析では、 $2\theta$  が  $31^\circ$  近傍のピークの他に、 $2\theta$  が  $36^\circ$  近傍にもピークが現れる場合がある。 $2\theta$  が  $36^\circ$  近傍のピークは、CAAAC - OS 膜中の一部に、c 軸配向性を有さない結晶が含まれることを示している。CAAAC - OS 膜は、 $2\theta$  が  $31^\circ$  近傍にピークを示し、 $2\theta$  が  $36^\circ$  近傍にピークを示さないことが好ましい。

#### 【0174】

CAAAC - OS 膜は、不純物濃度の低い酸化物半導体膜である。不純物は、水素、炭素、シリコン、遷移金属元素などの酸化物半導体膜の主成分以外の元素である。特に、シリコンなどの、酸化物半導体膜を構成する金属元素よりも酸素との結合力の強い元素は、酸化物半導体膜から酸素を奪うことで酸化物半導体膜の原子配列を乱し、結晶性を低下させる要因となる。また、鉄やニッケルなどの重金属、アルゴン、二酸化炭素などは、原子半径（または分子半径）が大きいため、酸化物半導体膜内部に含まれると、酸化物半導体膜の原子配列を乱し、結晶性を低下させる要因となる。なお、酸化物半導体膜に含まれる不純物は、キャリアトラップやキャリア発生源となる場合がある。

#### 【0175】

また、CAAAC - OS 膜は、欠陥準位密度の低い酸化物半導体膜である。例えば、酸化物半導体膜中の酸素欠損は、キャリアトラップとなることや、水素を捕獲することによってキャリア発生源となることがある。

#### 【0176】

不純物濃度が低く、欠陥準位密度が低い（酸素欠損の少ない）ことを、高純度真性または実質的に高純度真性と呼ぶ。高純度真性または実質的に高純度真性である酸化物半導体膜は、キャリア発生源が少ないため、キャリア密度を低くすることができます。したがって、当該酸化物半導体膜を用いたトランジスタは、しきい値電圧がマイナスとなる電気特性（ノーマリーオンともいう。）になることが多い。また、高純度真性または実質的に高純度真性である酸化物半導体膜は、キャリアトラップが少ない。そのため、当該酸化物半導体膜を用いたトランジスタは、電気特性の変動が小さく、信頼性の高いトランジスタとなる。なお、酸化物半導体膜のキャリアトラップに捕獲された電荷は、放出するまでに要する時間が長く、あたかも固定電荷のように振る舞うことがある。そのため、不純物濃度が高く、欠陥準位密度が高い酸化物半導体膜を用いたトランジスタは、電気特性が不安定となる場合がある。

#### 【0177】

また、CAAAC - OS 膜を用いたトランジスタは、可視光や紫外光の照射による電気特性の変動が小さい。

#### 【0178】

次に、微結晶酸化物半導体膜について説明する。

#### 【0179】

微結晶酸化物半導体膜は、TEM による観察像では、明確に結晶部を確認することができない場合がある。微結晶酸化物半導体膜に含まれる結晶部は、 $1\text{ nm}$  以上  $100\text{ nm}$  以下、または  $1\text{ nm}$  以上  $10\text{ nm}$  以下の大きさであることが多い。特に、 $1\text{ nm}$  以上  $10\text{ nm}$  以下、または  $1\text{ nm}$  以上  $3\text{ nm}$  以下の微結晶であるナノ結晶（nc : nanocrystalline）を有する酸化物半導体膜を、nc - OS (nanocrystalline Oxide Semiconductor) 膜と呼ぶ。また、nc - OS 膜は、例えば、TEM による観察像では、結晶粒界を明確に確認できない場合がある。

#### 【0180】

nc - OS 膜は、微小な領域（例えば、 $1\text{ nm}$  以上  $10\text{ nm}$  以下の領域、特に  $1\text{ nm}$  以上  $3\text{ nm}$  以下の領域）において原子配列に周期性を有する。また、nc - OS 膜は、異なる結晶部間で結晶方位に規則性が見られない。そのため、膜全体で配向性が見られない。したがって、nc - OS 膜は、分析方法によっては、非晶質酸化物半導体膜と区別が付かな

10

20

30

40

50

い場合がある。例えば、n c - O S 膜に対し、結晶部よりも大きい径の X 線を用いる X R D 装置を用いて構造解析を行うと、o u t - o f - p l a n e 法による解析では、結晶面を示すピークが検出されない。また、n c - O S 膜に対し、結晶部よりも大きいプローブ径（例えば 50 nm 以上）の電子線を用いる電子線回折（制限視野電子線回折ともいう。）を行うと、ハローパターンのような回折パターンが観測される。一方、n c - O S 膜に対し、結晶部の大きさと近いか結晶部より小さいプローブ径（例えば 1 nm 以上 30 nm 以下）の電子線を用いる電子線回折（ナノビーム電子線回折ともいう。）を行うと、スポットが観測される。また、n c - O S 膜に対しナノビーム電子線回折を行うと、円を描くように（リング状に）輝度の高い領域が観測される場合がある。また、n c - O S 膜に対しナノビーム電子線回折を行うと、リング状の領域内に複数のスポットが観測される場合がある。

10

#### 【 0 1 8 1 】

n c - O S 膜は、非晶質酸化物半導体膜よりも規則性の高い酸化物半導体膜である。そのため、n c - O S 膜は、非晶質酸化物半導体膜よりも欠陥準位密度が低くなる。ただし、n c - O S 膜は、異なる結晶部間で結晶方位に規則性が見られない。そのため、n c - O S 膜は、C A A C - O S 膜と比べて欠陥準位密度が高くなる。

#### 【 0 1 8 2 】

なお、酸化物半導体膜は、例えば、非晶質酸化物半導体膜、微結晶酸化物半導体膜、C A A C - O S 膜のうち、二種以上を有する積層膜であってもよい。

20

#### 【 0 1 8 3 】

C A A C - O S 膜は、例えば、多結晶である酸化物半導体スパッタ用ターゲットを用い、スパッタ法によって成膜する。当該スパッタ用ターゲットにイオンが衝突すると、スパッタ用ターゲットに含まれる結晶領域が a - b 面から劈開し、a - b 面に平行な面を有する平板状またはペレット状のスパッタ粒子として剥離することがある。この場合、当該平板状又はペレット状のスパッタリング粒子が、結晶状態を維持したまま基板に到達することで、C A A C - O S 膜を成膜することができる。

#### 【 0 1 8 4 】

また、C A A C - O S 膜を成膜するために、以下の条件を適用することが好ましい。

#### 【 0 1 8 5 】

成膜時の不純物混入を低減することで、不純物によって結晶状態が崩れることを抑制できる。例えば、成膜室内に存在する不純物（水素、水、二酸化炭素および窒素など）を低減すればよい。また、成膜ガス中の不純物を低減すればよい。具体的には、露点が - 80 以下、好ましくは - 100 以下である成膜ガスを用いる。

30

#### 【 0 1 8 6 】

また、成膜時の基板加熱温度を高めることで、基板到達後にスパッタ粒子のマイグレーションが起こる。具体的には、基板加熱温度を 100 以上 740 以下、好ましくは 200 以上 500 以下として成膜する。成膜時の基板加熱温度を高めることで、平板状又はペレット状のスパッタリング粒子が基板に到達した場合、基板上でマイグレーションが起こり、スパッタ粒子の平らな面が基板に付着する。

#### 【 0 1 8 7 】

40

また、成膜ガス中の酸素割合を高め、電力を最適化することで成膜時のプラズマダメージを軽減すると好ましい。成膜ガス中の酸素割合は、30 体積 % 以上、好ましくは 100 体積 % とする。

#### 【 0 1 8 8 】

スパッタ用ターゲットとしては、例えば、I n - G a - Z n - O 化合物ターゲットを用いることができる。I n - G a - Z n - O 化合物ターゲットは、I n O<sub>x</sub> 粉末、G a O<sub>y</sub> 粉末およびZ n O<sub>z</sub> 粉末を所定のモル数比で混合し、加圧処理後、1000 以上 1500 以下の温度で加熱処理をすることで多結晶体とする。なお、X、Y および Z は任意の正数である。また、当該多結晶体の粒径は、例えば 1 μm 以下など、小さいほど好ましい。ここで、粉末の種類、およびその混合するモル数比は、作製するスパッタ用ターゲットに

50

よって適宜変更すればよい。

**【0189】**

また、酸化物半導体膜は、複数の酸化物半導体膜が積層された構造でもよい。例えば、図18(A)に示すトランジスタのように、酸化物半導体層940を第1の酸化物半導体膜941aと第2の酸化物半導体膜941bの積層とすることができます。第1の酸化物半導体膜941aと第2の酸化物半導体膜941bに、異なる原子数比の金属酸化物を用いてもよい。例えば、一方の酸化物半導体膜に二種類の金属を含む酸化物、三種類の金属を含む酸化物、四種類の金属を含む酸化物のうち一つを用い、他方の酸化物半導体膜に一方の酸化物半導体膜と異なる二種類の金属を含む酸化物、三種類の金属を含む酸化物、四種類の金属を含む酸化物を用いてもよい。

10

**【0190】**

また、第1の酸化物半導体膜941aと第2の酸化物半導体膜941bの構成元素を同一とし、両者の原子数比を異ならせてよい。例えば、一方の酸化物半導体膜の原子数比をIn:Ga:Zn = 1:1:1、5:5:6、または3:1:2とし、他方の酸化物半導体膜の原子数比をIn:Ga:Zn = 1:3:2、1:3:4、1:3:6、1:6:4、または1:9:6である酸化物半導体膜で形成することができる。なお、各酸化物半導体膜の原子数比は、誤差として上記の原子数比のプラスマイナス20%の変動を含む。

**【0191】**

このとき、一方の酸化物半導体膜と他方の酸化物半導体膜のうち、ゲート電極に近い側(チャネル側)の酸化物半導体膜のInとGaの原子数比をIn > Gaとし、ゲート電極から遠い側(バックチャネル側)の酸化物半導体膜のInとGaの原子数比をIn < Gaとすることで、電界効果移動度の高いトランジスタを作製することができる。一方、チャネル側の酸化物半導体膜のInとGaの原子数比をIn < Gaとし、バックチャネル側の酸化物半導体膜のInとGaの原子数比をIn > Gaとすることで、トランジスタの経時変化や信頼性試験によるしきい値電圧の変動量を低減することができる。

20

**【0192】**

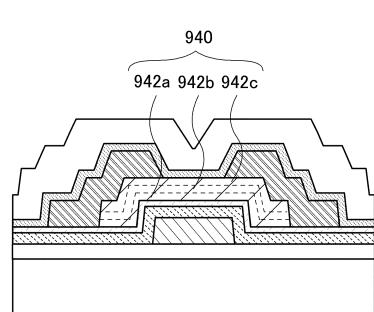

また、トランジスタの半導体膜を第1の酸化物半導体膜乃至第3の酸化物半導体膜からなる3層構造としてもよい。このとき、第1の酸化物半導体膜乃至第3の酸化物半導体膜の構成元素を同一とし、且つそれぞれの原子数比を異ならせてよい。半導体膜を3層構造とするトランジスタの構成について、図18(B)を用いて説明する。

30

**【0193】**

図18(B)に示すトランジスタは、第1の酸化物半導体膜942a、第2の酸化物半導体膜942b、および第3の酸化物半導体膜942cがゲート絶縁膜側から順に積層されている。

**【0194】**

第1の酸化物半導体膜942aおよび第3の酸化物半導体膜942cを構成する材料は、 $InM_{1-x}Zn_yO_z$ (x < 1, y > 0, M<sub>1</sub> = Ga, Hf等)で表記できる材料を用いる。また、第2の酸化物半導体膜942bを構成する材料は、 $InM_{2-x}Zn_yO_z$ (x < 1, y > 0, M<sub>2</sub> = Ga, Sn等)で表記できる材料を用いる。

**【0195】**

第1の酸化物半導体膜942aの伝導帯下端および第3の酸化物半導体膜942cの伝導帯下端に比べて第2の酸化物半導体膜942bの伝導帯下端が真空準位から最も深くなるような井戸型構造を構成するように、第1、第2、および第3の酸化物半導体膜の材料を適宜選択する。

40

**【0196】**

例えば、第1の酸化物半導体膜942aおよび第3の酸化物半導体膜942cを原子数比がIn:Ga:Zn = 1:3:2、1:3:4、1:3:6、1:6:4、または1:9:6である酸化物半導体膜で形成し、第2の酸化物半導体膜942bの原子数比がIn:Ga:Zn = 1:1:1、5:5:6、または3:1:2である酸化物半導体膜で形成することができる。

50

## 【0197】

第1の酸化物半導体膜942a乃至第3の酸化物半導体膜942cの構成元素は同一であるため、第2の酸化物半導体膜942bは、第1の酸化物半導体膜942aとの界面における欠陥準位(トラップ準位)が少ない。詳細には、当該欠陥準位(トラップ準位)は、ゲート絶縁膜と第1の酸化物半導体膜942aとの界面における欠陥準位よりも少ない。このため、上記のように酸化物半導体膜が積層されていることで、トランジスタの経時変化や信頼性試験によるしきい値電圧の変動量を低減することができる。

## 【0198】

また、第1の酸化物半導体膜942aの伝導帯下端および第3の酸化物半導体膜942cの伝導帯下端に比べて第2の酸化物半導体膜942bの伝導帯下端が真空準位から最も深くなるような井戸型構造を構成するように、第1、第2、および第3の酸化物半導体膜の材料を適宜選択することで、トランジスタの電界効果移動度を高めることができると共に、トランジスタの経時変化や信頼性試験によるしきい値電圧の変動量を低減することができる。

10

## 【0199】

また、第1の酸化物半導体膜942a乃至第3の酸化物半導体膜942cに、結晶性の異なる酸化物半導体を適用してもよい。すなわち、単結晶酸化物半導体、多結晶酸化物半導体、微結晶(ナノ結晶)酸化物半導体、非晶質酸化物半導体、およびCAC-O<sub>x</sub>膜を適宜組み合わせた構成としてもよい。

## 【0200】

20

また、少なくともチャネル形成領域となりうる第2の酸化物半導体膜942bはCAC-O<sub>x</sub>膜であることが好ましい。

## 【0201】

なお、酸素と結合し易い導電材料(例えば、ソース電極またはドレイン電極に用いられる金属)と酸化物半導体膜を接触させると、酸化物半導体膜中の酸素が、酸素と結合し易い導電材料側に拡散する現象が起こる。当該現象は、温度が高いほど顕著に起こりやすい。トランジスタの作製工程には、いくつかの加熱工程があることから、上記現象により、酸化物半導体層のソース電極またはドレイン電極と接触した近傍の領域に酸素欠損が発生し、当該領域はn型化する。したがって、n型化した当該領域はトランジスタのソースまたはドレインとして作用させることができる。

30

## 【0202】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

## 【符号の説明】

## 【0203】

100 撮像装置

101 フラットパネルディテクタ

110 画素回路

210 電流検出回路

220 A/Dコンバータ

40

310 演算回路部

320 第1の記憶回路部

321 第1のルックアップテーブル

322 第2のルックアップテーブル

323 プログラム

330 第2の記憶回路部

340 記憶装置

331 領域

400 表示装置

501 第1のトランジスタ

50

|       |             |    |

|-------|-------------|----|

| 5 0 2 | 第 2 のトランジスタ |    |

| 5 0 3 | 第 3 のトランジスタ |    |

| 5 0 4 | 第 4 のトランジスタ |    |

| 5 0 5 | 配線          |    |

| 5 1 1 | 第 1 の配線     |    |

| 5 1 2 | 第 2 の配線     |    |

| 5 1 3 | 第 3 の配線     |    |

| 5 1 4 | 第 4 の配線     |    |

| 5 1 5 | 第 5 の配線     |    |

| 5 1 6 | 第 6 の配線     | 10 |

| 5 1 7 | 第 7 の配線     |    |

| 5 2 0 | フォトダイオード    |    |

| 5 3 0 | 可変抵抗素子      |    |

| 5 5 1 | 回路          |    |

| 5 5 2 | 回路          |    |

| 5 5 3 | 回路          |    |

| 5 5 4 | 回路          |    |

| 5 5 5 | 回路          |    |

| 6 0 1 | 信号          |    |

| 6 0 2 | 信号          | 20 |

| 6 0 3 | 信号          |    |

| 6 0 4 | 信号          |    |

| 6 0 5 | 信号          |    |

| 7 0 1 | 信号          |    |

| 7 0 2 | 信号          |    |

| 7 0 3 | 信号          |    |

| 7 0 4 | 信号          |    |

| 7 0 5 | 信号          |    |

| 7 0 6 | 信号          |    |

| 7 0 7 | 信号          | 30 |

| 7 0 8 | 信号          |    |

| 7 0 9 | 信号          |    |

| 7 1 0 | 期間          |    |

| 7 1 1 | 期間          |    |

| 7 2 0 | 期間          |    |

| 7 3 1 | 期間          |    |

| 8 1 0 | 期間          |    |

| 8 1 1 | 期間          |    |

| 8 1 2 | 期間          |    |

| 8 1 3 | 期間          | 40 |

| 8 2 0 | 放射線照射期間     |    |

| 8 2 1 | 期間          |    |

| 8 2 2 | 期間          |    |

| 8 2 3 | 期間          |    |

| 8 3 1 | 期間          |    |

| 9 0 0 | 基板          |    |

| 9 1 0 | 下地絶縁膜       |    |

| 9 1 5 | 半導体膜        |    |

| 9 1 6 | 半導体膜        |    |

| 9 1 7 | 半導体膜        | 50 |

|         |            |    |

|---------|------------|----|

| 9 2 0   | ゲート電極層     |    |

| 9 2 1   | 導電膜        |    |

| 9 3 0   | ゲート絶縁膜     |    |

| 9 3 1   | 絶縁膜        |    |

| 9 3 2   | 絶縁膜        |    |

| 9 4 0   | 酸化物半導体層    |    |

| 9 4 1 a | 第1の酸化物半導体膜 |    |

| 9 4 1 b | 第2の酸化物半導体膜 |    |

| 9 4 2 a | 第1の酸化物半導体膜 | 10 |

| 9 4 2 b | 第2の酸化物半導体膜 |    |

| 9 4 2 c | 第3の酸化物半導体膜 |    |

| 9 5 0   | ソース電極層     |    |

| 9 6 0   | ドレイン電極層    |    |

| 9 7 0   | 絶縁層        |    |

| 9 8 0   | 絶縁層        |    |

| 9 9 1   | ディテクタユニット  |    |

| 9 9 2   | 取っ手        |    |

| 9 9 4   | 被写体        |    |

| 9 9 5   | 台          |    |

| 9 9 6   | X線源        | 20 |

| 9 9 7   | X線         |    |

| 9 9 8   | 撮像システム     |    |

| 9 9 9   | コンピュータ     |    |

| 1 2 1 1 | 導電膜        |    |

| 1 2 1 2 | 導電膜        |    |

| 1 2 1 3 | 導電膜        |    |

| 1 2 1 4 | 導電膜        |    |

| 1 2 1 5 | 導電膜        |    |

| 1 2 1 8 | 導電膜        |    |

| 1 2 1 9 | 導電膜        | 30 |

| 1 2 2 0 | 導電膜        |    |

| 1 2 2 1 | 導電膜        |    |

| 1 2 2 2 | 導電膜        |    |

| 1 2 2 3 | 導電膜        |    |

| 1 2 2 4 | 導電膜        |    |

| 1 2 2 5 | 導電膜        |    |

| 1 2 2 6 | 導電膜        |    |

| 1 2 2 7 | 導電膜        |    |

| 1 2 2 8 | ゲート絶縁膜     |    |

| 1 2 2 9 | 導電膜        | 40 |

| 1 2 5 0 | 半導体層       |    |

| 1 2 8 1 | 絶縁膜        |    |

| 1 2 8 2 | 絶縁膜        |    |

| 1 2 8 3 | 絶縁膜        |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

(B)

210

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

---

フロントページの続き

| (51)Int.Cl. |                 | F I                  |

|-------------|-----------------|----------------------|

| H 0 4 N     | 5/32 (2006.01)  | G 0 1 T 1/20 J       |

| H 0 4 N     | 5/374 (2011.01) | A 6 1 B 6/00 3 0 0 S |

| H 0 4 N     | 5/369 (2011.01) | H 0 4 N 5/32         |

|             |                 | H 0 4 N 5/374        |

|             |                 | H 0 4 N 5/369        |

(56)参考文献 特開2003-204052(JP,A)

特開平10-108075(JP,A)

特開2011-191292(JP,A)

特開平05-309087(JP,A)

特開2010-102877(JP,A)

特開2005-245507(JP,A)

特開2010-179155(JP,A)

## (58)調査した分野(Int.Cl., DB名)

|         |                       |

|---------|-----------------------|

| H 0 4 N | 5 / 2 2 5 - 5 / 3 7 8 |

| A 6 1 B | 6 / 0 0               |

| G 0 1 T | 1 / 2 0               |

| G 0 1 T | 7 / 0 0               |

| H 0 1 L | 2 7 / 1 4 6           |