US 20010006842A1

Jul. 5, 2001

# (19) United States (12) Patent Application Publication (10) Pub. No.: US 2001/0006842 A1 (43) **Pub. Date:** Hattori

## (54) MANUFACTURE OF FIELD EMISSION ELEMENT

(76) Inventor: Atsuo Hattori, Hamamatsu-shi (JP)

Correspondence Address: **OSTROLENK FABER GERB & SOFFEN 1180 AVENUE OF THE AMERICAS** NEW YORK, NY 100368403

- (21) Appl. No.: 09/764,958

- (22) Filed: Jan. 18, 2001

### **Related U.S. Application Data**

(62) Division of application No. 09/371,177, filed on Aug. 10, 1999.

#### (30)**Foreign Application Priority Data**

Aug. 10, 1998 (JP)...... 10-225878

### **Publication Classification**

| (51) | Int. Cl. <sup>7</sup> |  |

|------|-----------------------|--|

| (52) | U.S. Cl.              |  |

#### (57) ABSTRACT

In a field emission element manufacture method, a gate electrode having a gate hole and a getter film having a through hole communicating with the gate hole are formed on the surface of a substrate. A sacrificial film is formed over the substrate to form a mold which is used when an emitter electrode is formed, the sacrificial film covering the side walls of the gate hole and through hole and the partial surface of the substrate exposed via the holes. An emitter electrode is formed covering the surface of the mold, and thereafter the gate hole and emitter electrode are exposed to obtain a field emission element. The vacuum degree in a flat panel display can be raised and molecules are prevented from attaching to the surface of the emitter electrode.

-20b -20a

**FIG.12F**

FIG.131

FIG.16

# MANUFACTURE OF FIELD EMISSION ELEMENT

**[0001]** This application is based on Japanese patent application No. Hei 10-225878 filed on Aug. 10, 1998, the entire contents of which are incorporated herein by reference.

#### BACKGROUND OF THE INVENTION

[0002] a) Field of the Invention

**[0003]** The present invention relates to a field emission element and more particularly to a field emission element having a field emission cathode whose tip emits electrons and its manufacture method.

[0004] b) Description of the Related Art

**[0005]** A field emission element emits electrons from a sharp tip of an emitter (field emission cathode) by utilizing electric field concentration. For example, a flat panel display can be structured by using a field emitter array (FEA) having a number of emitters disposed on a substrate. Each emitter controls the luminance of a corresponding pixel of the display.

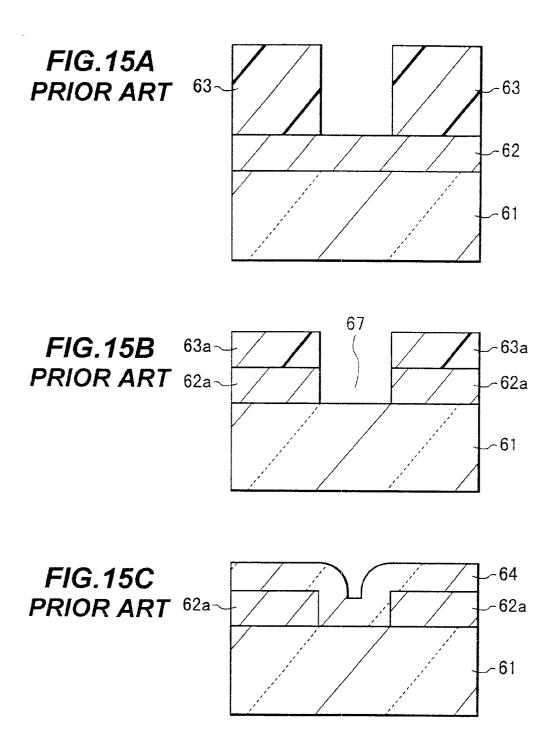

[0006] FIGS. 15A to 15F schematically illustrate a conventional method of manufacturing a field emission element.

[0007] As shown in FIG. 15A, a conductive gate electrode 62 is formed on a substrate 61. For example, the conductive gate electrode 62 is made of polysilicon doped with impurities. On the conductive gate electrode 62, a resist film 63 having a predetermined pattern is formed through photolithography.

[0008] Next, by using the resist pattern 63 as a mask, the gate electrode 62 is anisotropically etched to leave as shown in FIG. 15B a gate electrode 62a having a gate hole 67 having a circular flat shape (as viewed from the top). This etching thins the resist pattern 63 and a thin resist pattern 63*a* is left.

[0009] As shown in FIG. 15C, after the resist pattern 63a is removed, a sacrificial film 64 is isotropically deposited on the gate electrode 62a and on the exposed substrate 61.

[0010] Next, as shown in FIG. 15D, the sacrificial film 64 is anisotropically etched to leave a sacrificial film (side spacer) 64a on the side wall of the gate hole 67 of the gate electrode 62a.

[0011] Next, as shown in FIG. 15E, an insulating film 65 is formed on the whole upper surface of the substrate and a conductive emitter electrode 66 is formed on the insulating film 65.

[0012] Next, as shown in FIG. 15F, the whole of the substrate 61 and side spacer 64a and part of the insulating film 65 are etched to leave a peripheral portion of the insulating film 65a between the gate electrode 62a and emitter electrode 66.

**[0013]** As a positive potential is applied to the gate electrode to concentrate an electric field upon the tip of the emitter electrode (cathode) **66**, electrons can be emitted from the emitter electrode **66** toward an anode electrode (not shown).

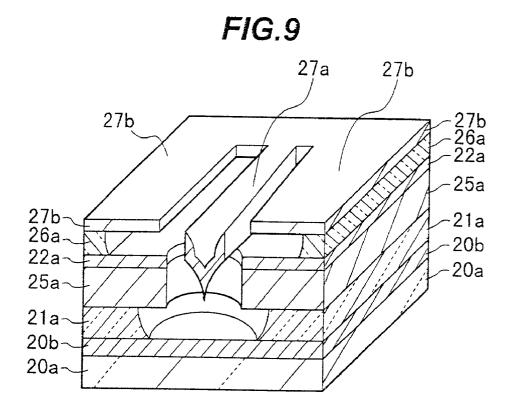

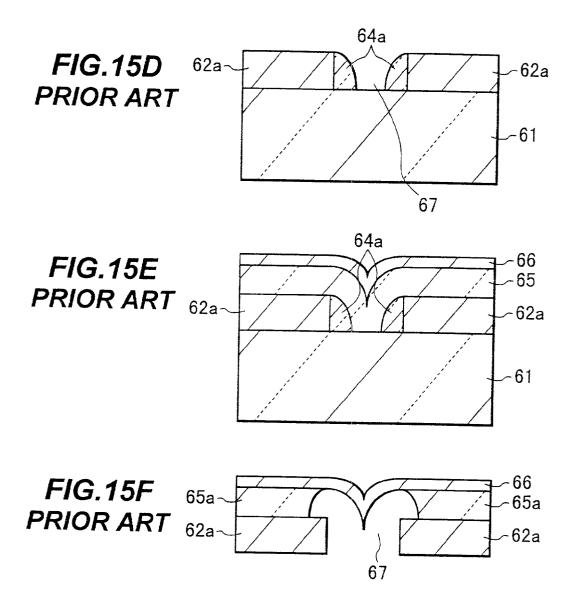

**[0014]** FIG. 16 is a cross sectional view of a flat panel display using such field emission elements.

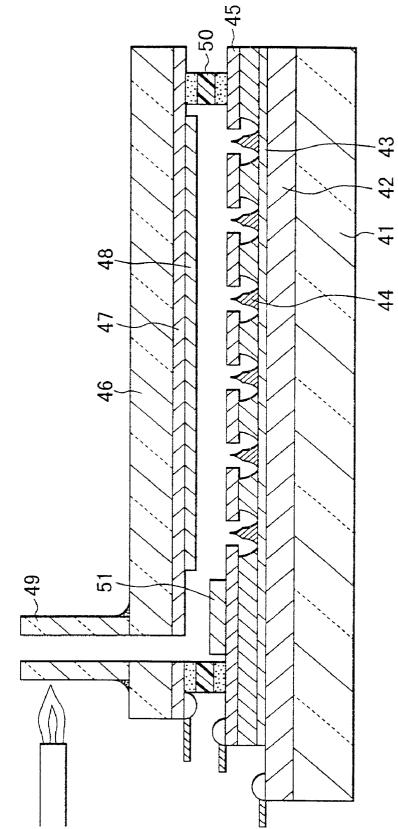

[0015] Each field emission element is manufactured by the above-described method, and has an emitter electrode 44 and a gate electrode 45. Formed on a support substrate 41 made of insulating material are a wiring layer 42 made of Al, Cu, or the like and a resistor layer 43 made of polysilicon or the like. On the resistor layer 43, a number of emitter electrodes 44 having a sharp tip are disposed to form a field emitter array (FEA). Each gate electrode 45 has a small opening (gate hole) near at the tip of each emitter electrode 44 and a voltage can be applied independently to each gate electrode although not specifically shown in FIG. 16. A plurality of emitter electrodes 44 can also be independently applied with a voltage.

[0016] Facing an electron source including the emitter electrode 44 and gate electrode 45, an opposing substrate is disposed including a transparent substrate 46 made of glass, quartz, or the like. The opposing substrate has a transparent electrode (anode electrode) 47 made of ITO or the like disposed under the transparent electrode 46 and a fluorescent member 48 disposed under the transparent electrode 47.

**[0017]** The electron source and opposing substrate are joined together via a spacer **50** made of a glass substrate and coated with adhesive, with the distance between the transparent electrode **47** and emitter electrode **44** being maintained about 0.1 to 5 mm. The adhesive may be low melting point glass.

[0018] Instead of the spacer 50 of a glass substrate, a spacer 50 made of adhesive such as epoxy resin with glass beads being dispersed therein may be used.

[0019] An air exhaust pipe 49 is coupled in advance to the opposing substrate. By using this air exhaust pipe 49, the inside of the flat display panel is evacuated to about  $1 \times 10^{-5}$  Torr to  $1 \times 10^{-9}$  Torr (about  $1 \times 10^{-5} \times 133.3$  Pa to  $1 \times 10^{-9} \times 133.3$  Pa), and then the air exhaust pipe 49 is sealed by using a burner or the like. Thereafter, the anode electrode (transparent electrode) 47, emitter electrode 44, gate electrode 45 are wired to complete the flat panel display.

**[0020]** The anode electrode (transparent electrode) **47** is always maintained at a positive potential. Pixels are selected two-dimensionally by emitter wiring lines and gate wiring lines. Field emission elements are selected disposed at each cross point of voltage applied emitter and gate wiring lines.

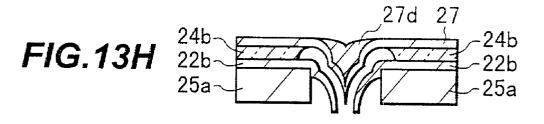

**[0021]** The emitter electrode is applied with a negative potential and the gate electrode is applied with a positive potential. Electrons are emitted from the emitter electrode toward the anode electrode. When electrons are bombarded with the fluorescent member **48**, fluorescence is radiated from the bombarded area (pixel).

[0022] In order to maintain the inside of the flat panel display at a high vacuum degree, a getter member 51 is provided at the corner in the flat panel display. For example, the getter member 51 is made of Ti, Ta, Zr, Al, Mg, or the like. After the air exhaust pipe 49 is sealed the getter member 51 is activated by heating it with a lamp or laser beam to adsorb ambient molecules therein. The initial vacuum degree in the flat panel display can therefore be improved.

**[0023]** Other molecules such as He passing through the transparent substrate **46** and support substrate **41** and entering the inside of the flat panel display or other molecules such as  $H_2O$ ,  $O_2$ , and  $N_2$  emitted in the flat panel display are

also adsorbed by the getter member **51**. As a result, the vacuum degree in the flat panel display is prevented from being lowered and the flat panel display is prolonged its lifetime.

[0024] The getter member 51 is disposed at the corner in the flat panel display so as not to obstruct electrons to be emitted from the emitter electrode 44 toward the transparent electrode 47. The getter member 51 is therefore placed at the position remote from the emitter electrodes 44. As the getter member 51 is placed remotely from the emitter electrodes 44, the function of the getter member 51 cannot be sufficiently demonstrated and the following disadvantages may occur.

- [0025] (1) Molecules described above are attached to the surface of the emitter electrode 44 in a high electric field, before they are adsorbed by the getter member 51. Radiation current (electron flow) from the emitter electrode 44 therefore reduces.

- [0026] (2) As molecules attach to or emit from the surface of the emitter electrode 44, a magnitude of the radiation current from the emitter electrode 44 fluctuates and becomes unstable.

- [0027] (3) As the emitter electrode 44 is bombarded with ions, the emitter electrode 44 is sputtered and the tip of the emitter electrode 44 deforms. As the tip of the emitter electrode 44 is rounded, an electric field is hard to be concentrated and the performance of the field emission element is degraded.

- [0028] (4) In order to maintain a high vacuum degree during the long span of one to ten years, a getter member 51 having a large area is required. As the large area getter member 51 is used, the flat panel display becomes large and the fluorescence radiation area (display area) becomes relatively small.

### SUMMARY OF THE INVENTION

**[0029]** It is an object of the present invention to provide a field emission element and a manufacture method thereof capable of improving the vacuum degree in the flat panel display and preventing molecules from being attached to the emitter surface.

**[0030]** According to one aspect of the present invention, there is provided a method of manufacturing a field emission element including a process of forming a lamination of a gate electrode and a getter film on a substrate.

**[0031]** In the field emission element, the gate electrode and getter film are laminated. The getter film in a flat panel display using such field emission elements is activated so that the vacuum degree near at the gate electrode can be raised. Since the gate electrode is generally positioned near at the tip of the emitter electrode, the vacuum degree near at the emitter electrode tip can also be raised.

# BRIEF DESCRIPTION OF THE DRAWINGS

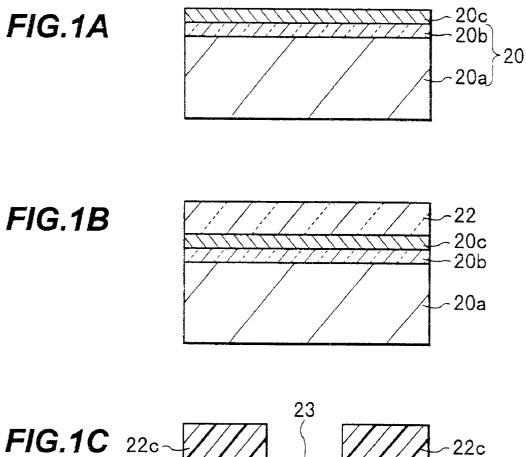

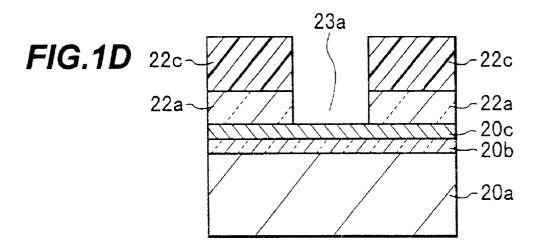

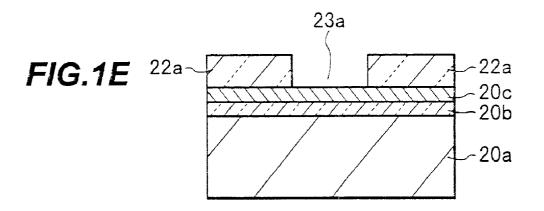

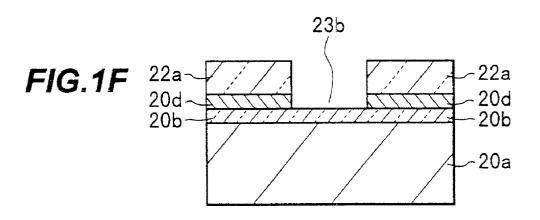

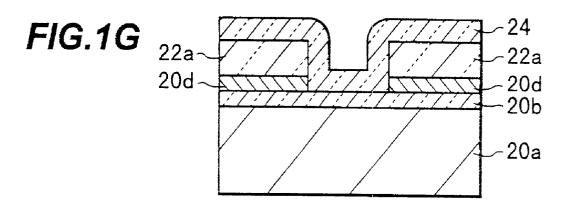

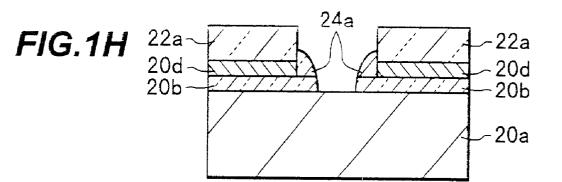

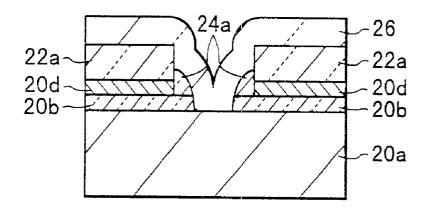

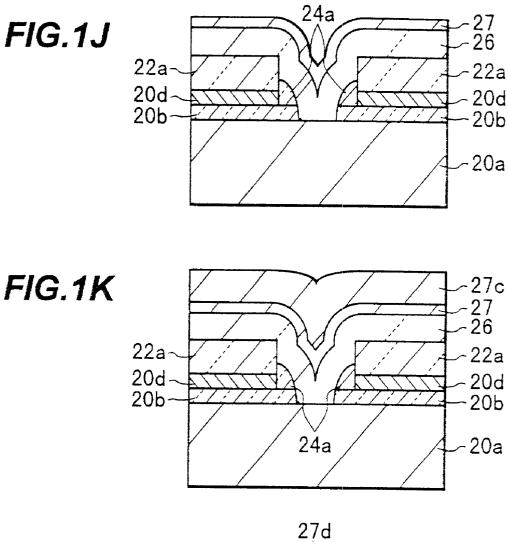

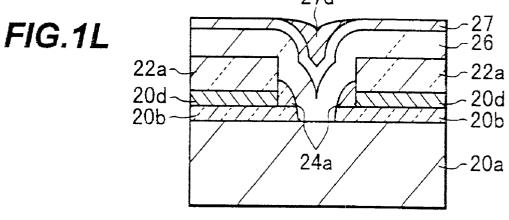

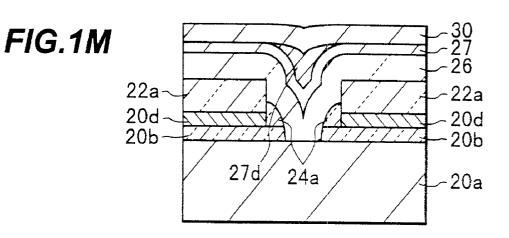

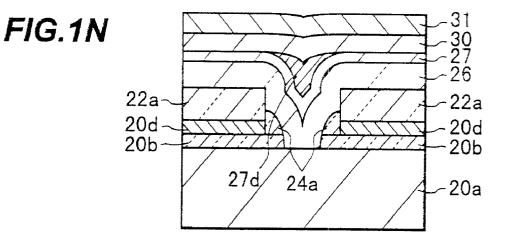

**[0032] FIGS. 1A** to 1O are schematic cross sectional views illustrating the manufacture steps of a field emission element (two-electrode element) according to a first embodiment of the invention.

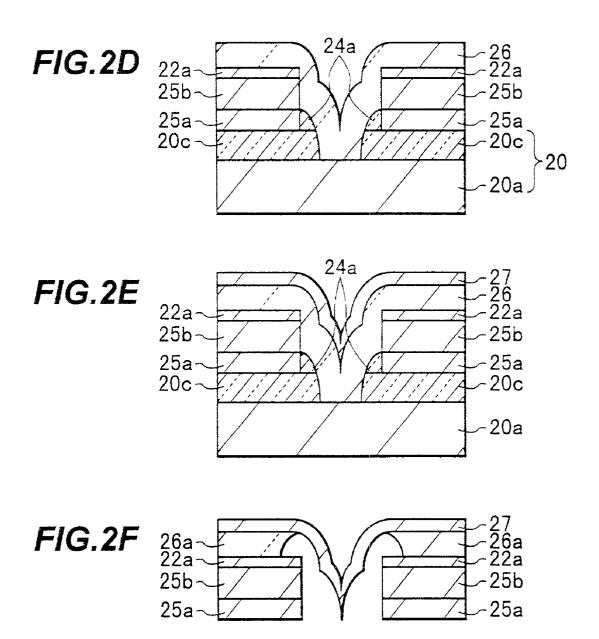

**[0033] FIGS. 2A** to 2F are schematic cross sectional views illustrating the manufacture steps of a field emission

element (two-electrode element) according to a modification of the first embodiment of the invention.

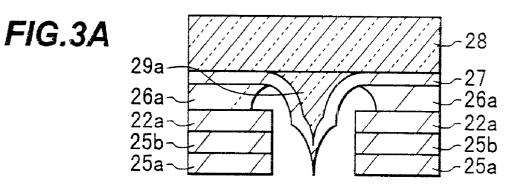

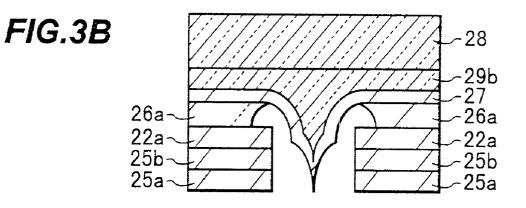

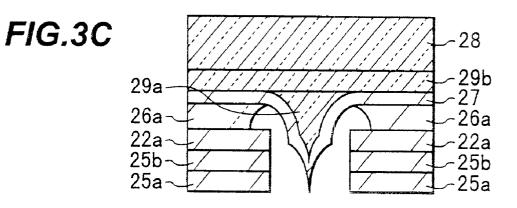

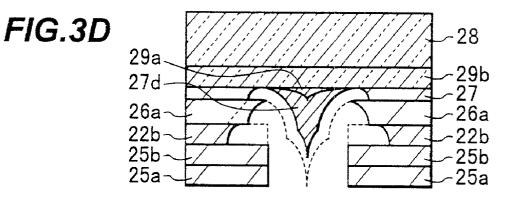

**[0034] FIGS. 3A** to **3D** are schematic cross sectional views illustrating the methods of reinforcing an emitter electrode by using a support substrate.

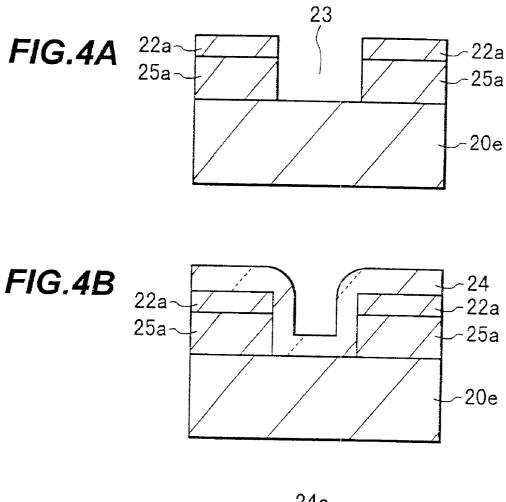

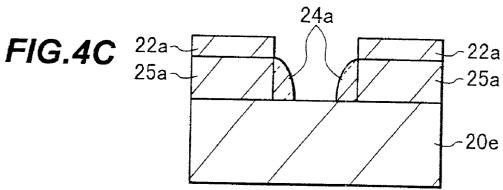

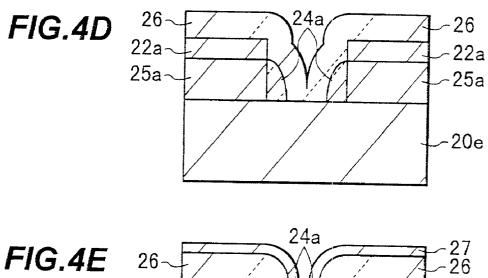

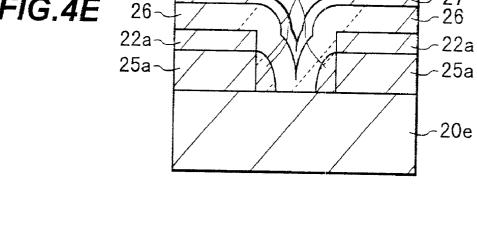

**[0035] FIGS. 4A** to **4**F are schematic cross sectional views illustrating the manufacture steps of a field emission element (two-electrode element) according to another modification of the first embodiment of the invention.

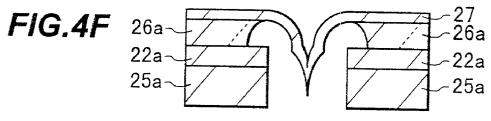

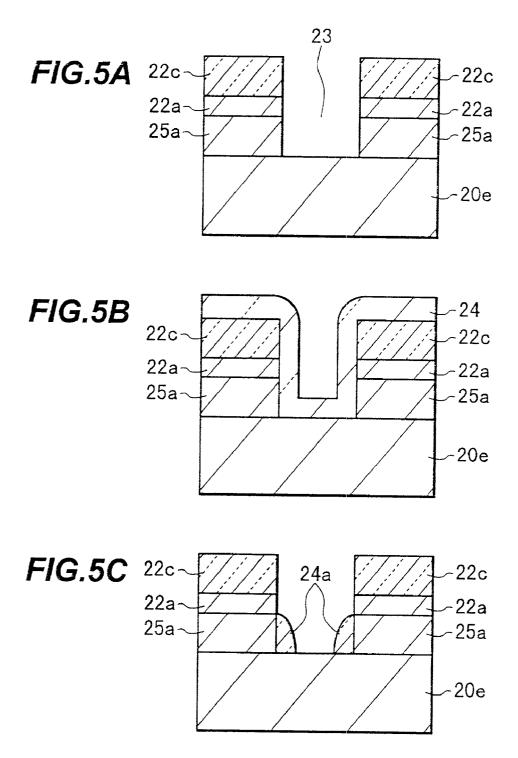

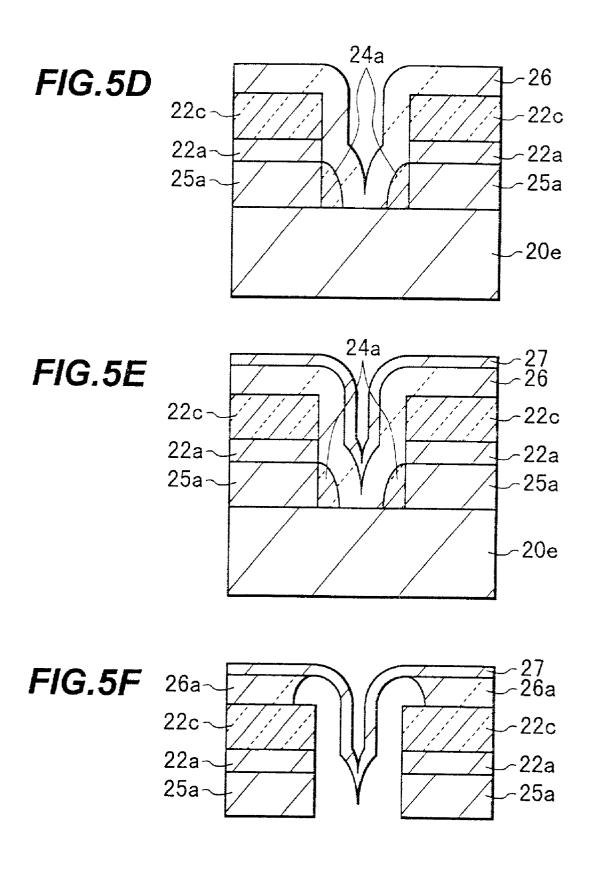

**[0036] FIGS. 5A** to **5**F are schematic cross sectional views illustrating the manufacture steps of a field emission element (two-electrode element) according to another modification of the first embodiment of the invention.

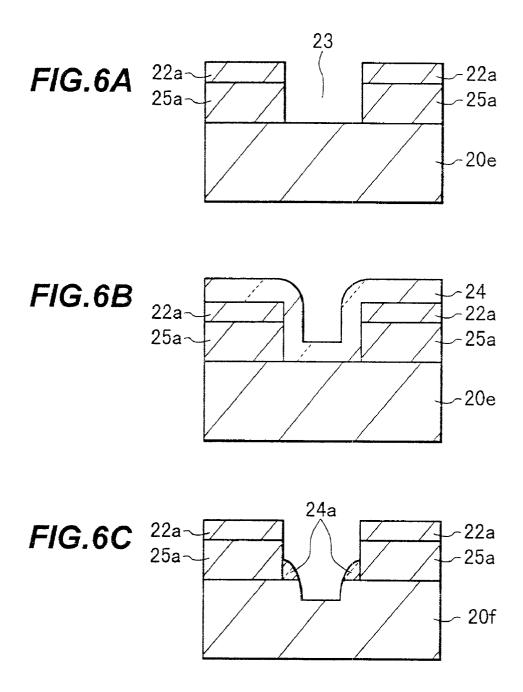

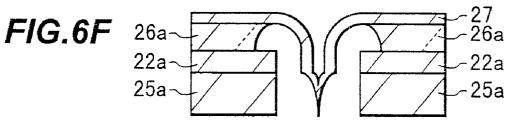

**[0037] FIGS. 6A** to 6F are schematic cross sectional views illustrating the manufacture steps of a field emission element (two-electrode element) according to another modification of the first embodiment of the invention.

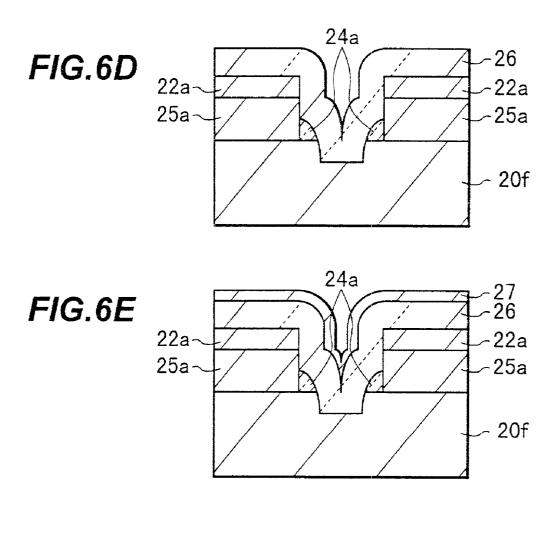

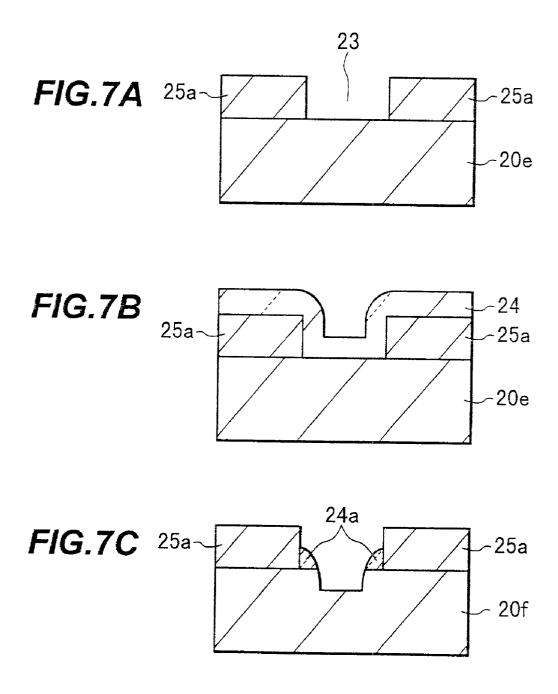

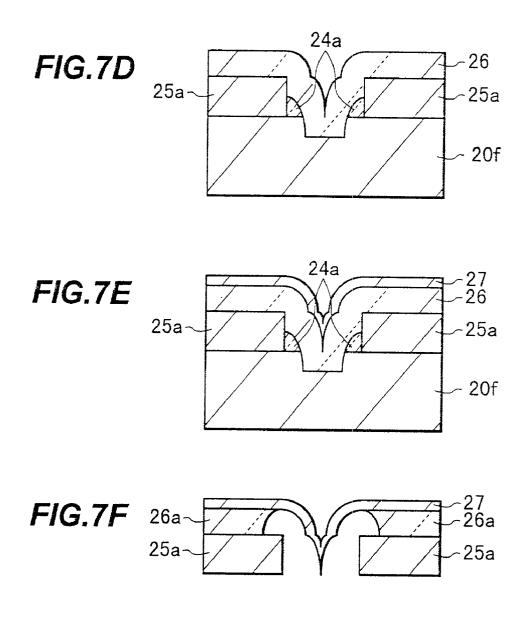

**[0038] FIGS. 7A** to 7F are schematic cross sectional views illustrating the manufacture steps of a field emission element (two-electrode element) according to another modification of the first embodiment of the invention.

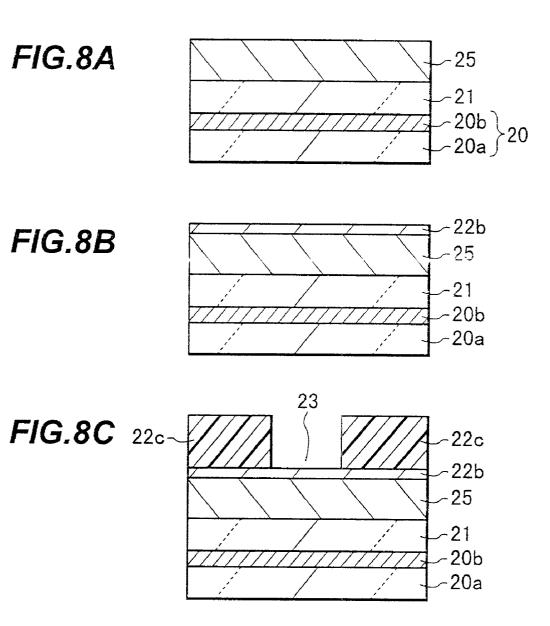

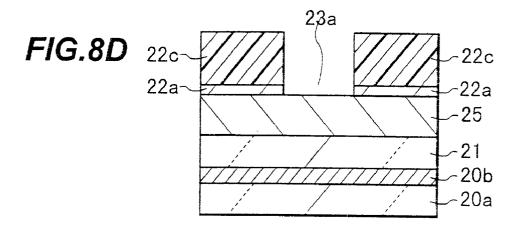

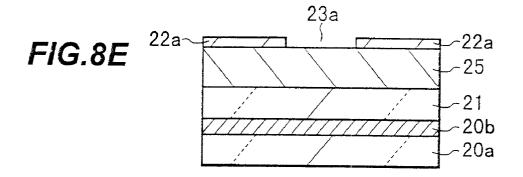

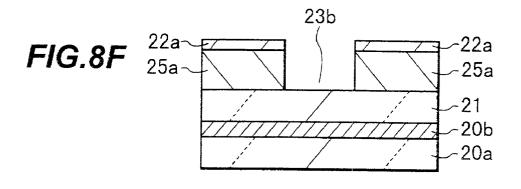

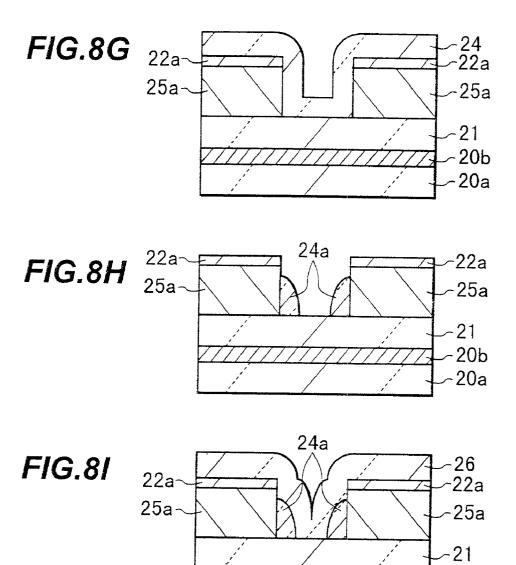

**[0039]** FIGS. 8A to 8L are schematic cross sectional views illustrating the manufacture steps of a field emission element (three-electrode element) according to a second embodiment of the invention.

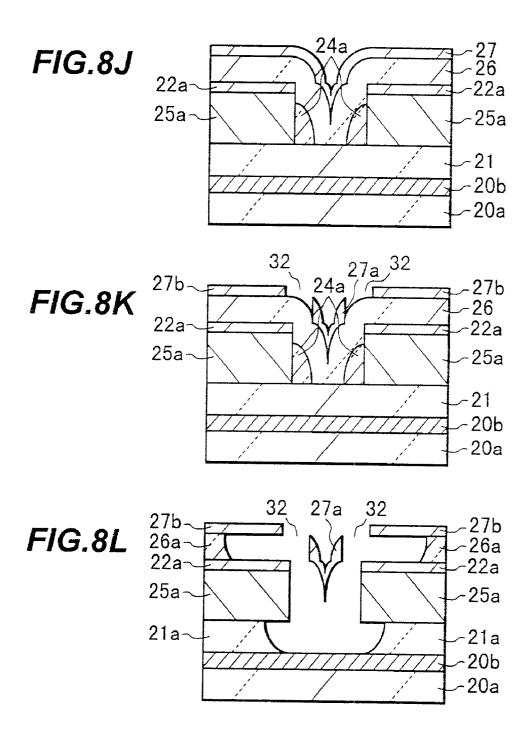

[0040] FIG. 9 is a schematic perspective view of the field emission element shown in FIG. 8L.

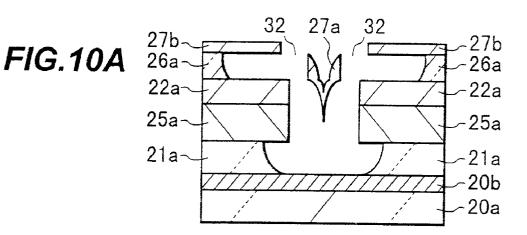

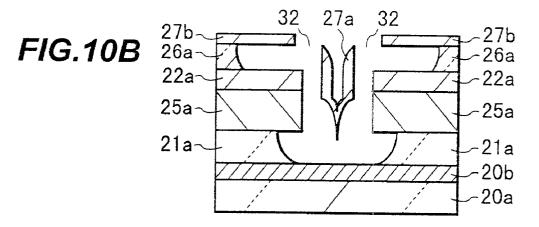

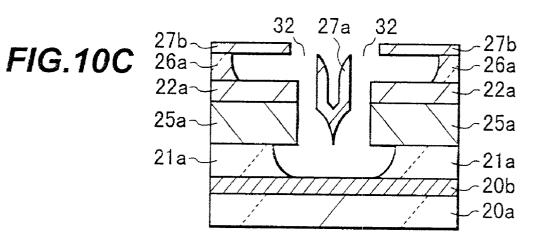

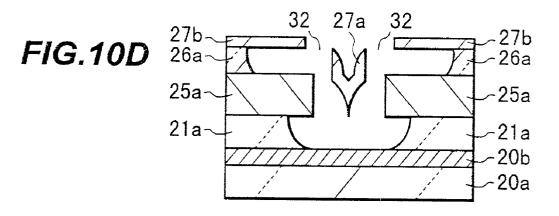

**[0041] FIGS. 10A** to **10D** are schematic cross sectional views illustrating the manufacture steps of a field emission element (three-electrode element) according to a modification of the second embodiment of the invention.

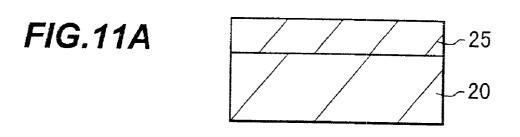

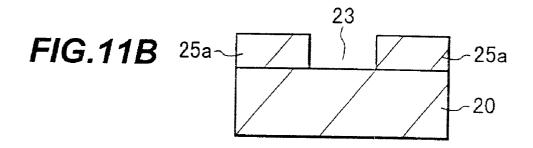

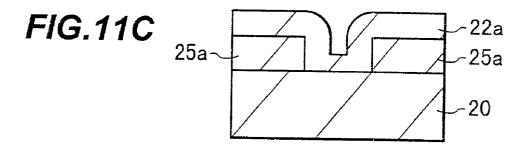

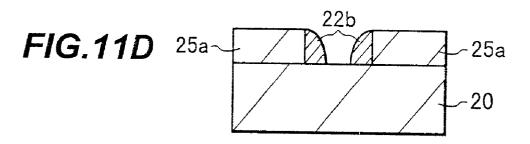

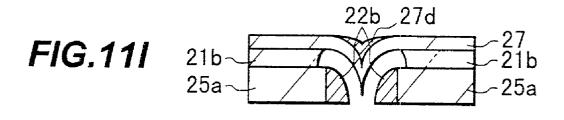

**[0042] FIGS. 11A** to **11I** are schematic cross sectional views illustrating the manufacture steps of a field emission element according to a third embodiment of the invention.

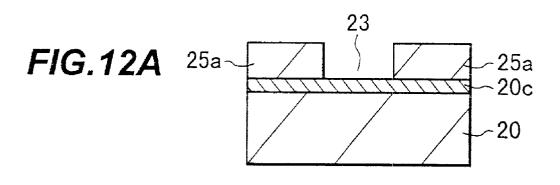

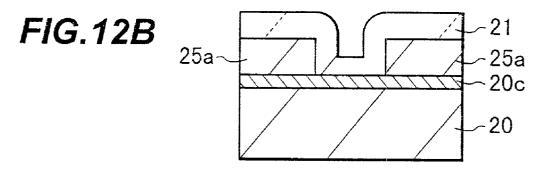

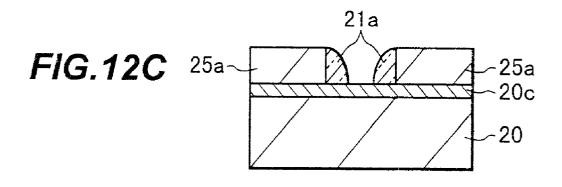

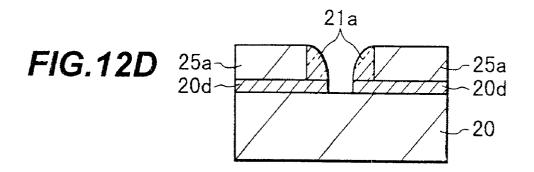

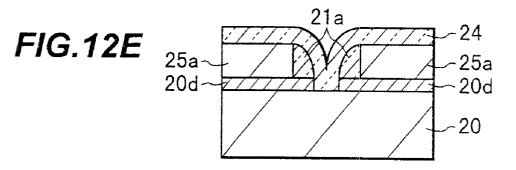

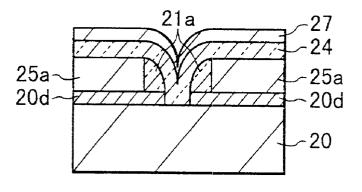

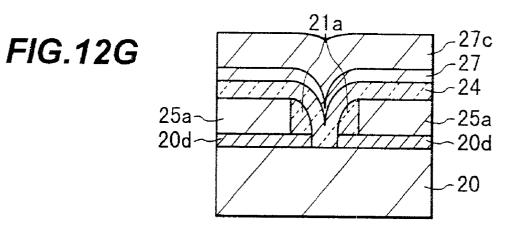

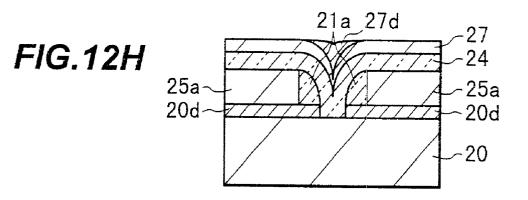

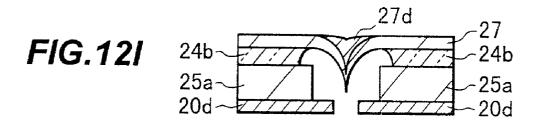

**[0043]** FIGS. 12A to 12I are schematic cross sectional views illustrating the manufacture steps of a field emission element according to a modification of the third embodiment of the invention.

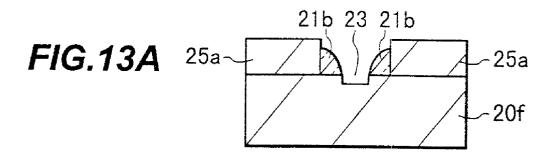

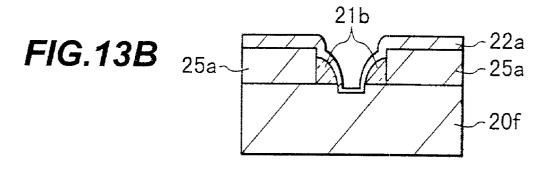

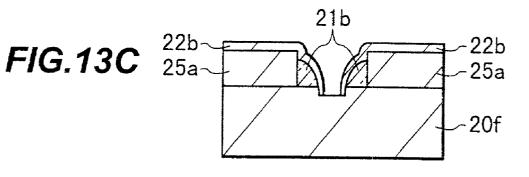

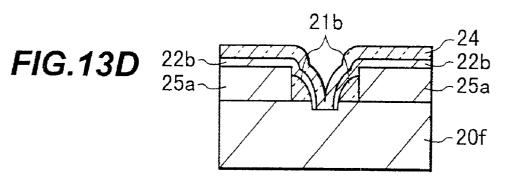

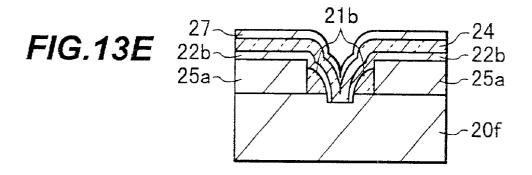

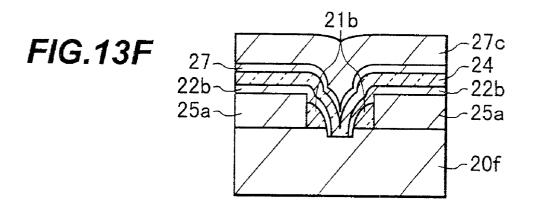

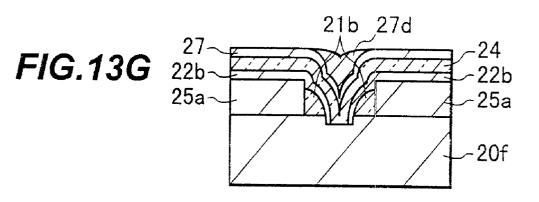

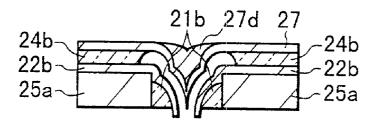

**[0044]** FIGS. 13A to 13I are schematic cross sectional views illustrating the manufacture steps of a field emission element according to another modification of the third embodiment of the invention.

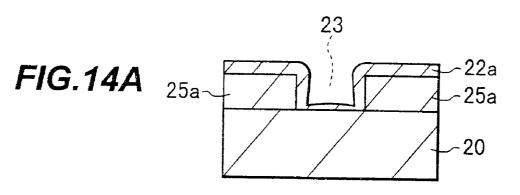

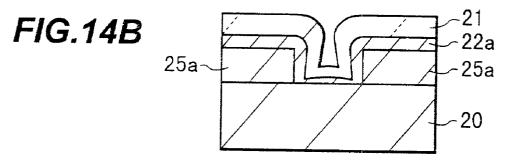

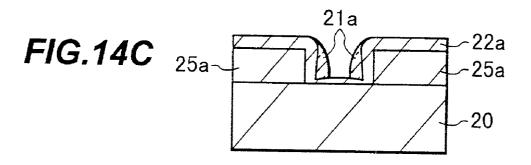

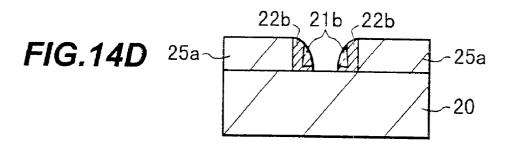

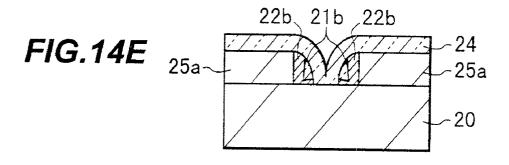

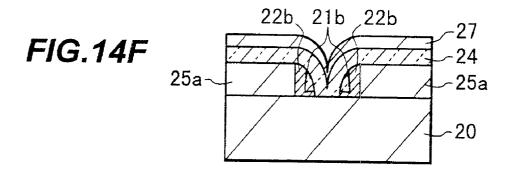

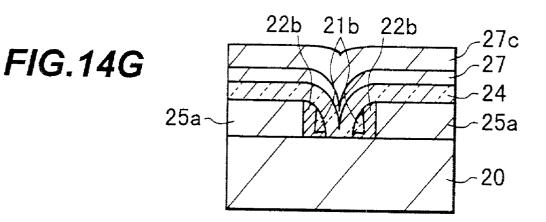

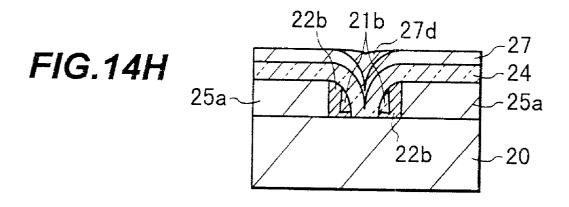

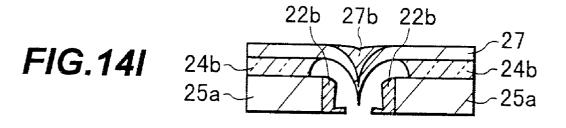

**[0045]** FIGS. 14A to 14I are schematic cross sectional views illustrating the manufacture steps of a field emission element according to another modification of the third embodiment of the invention.

**[0046] FIGS. 15A** to **15F** are schematic cross sectional views illustrating the conventional manufacture steps of a field emission element.

**[0047]** FIG. 16 is a schematic cross sectional view of a flat panel display using field emission elements.

### DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

**[0048]** FIGS. 1A to 1O are schematic cross sectional views illustrating the manufacture steps of a field emission element (two-electrode element) according to the first

embodiment of the invention. A two-electrode element has an emitter electrode and a gate electrode.

[0049] As shown in FIG. 1A, a substrate 20 is made of a starting substrate 20*a* and a first lamination film 20*b* formed thereon. By thermally oxidizing the starting substrate 20*a* made of Si, the first lamination film 20*b* made of SiO<sub>2</sub> can be formed 0.05  $\mu$ m thick.

**[0050]** For the thermal oxidation, for example, wet (water vapor) oxidation is performed in a vertical diffusion furnace at a hydrogen flow rate of 19 slm, an oxygen flow rate of 19 slm, and a temperature of 1000° C.

**[0051]** Next, a getter material layer **20***c* of Ti is deposited on the first lamination film **20***b* to a thickness of 0.05  $\mu$ m by sputtering. This sputtering is performed in a DC sputtering system using Ti as a target while Ar gas is introduced.

[0052] Next, as shown in FIG. 1B, a first sacrificial film (antireflection film) 22 of SiN<sub>x</sub> is deposited on the getter material layer 20c to a thickness of 0.12  $\mu$ m by reactive sputtering. The antireflection film 22 has an antireflection function for i-line ray at the surface of the getter material layer 20c. Sputtering for the antireflection film (SiN<sub>x</sub> film) 22 is performed in an RF sputtering system by using Si as a target while N<sub>2</sub>+Ar gas is introduced. SiN<sub>x</sub> may be used as the target while Ar gas is introduced. The SiN<sub>x</sub> film may be formed by plasma CVD.

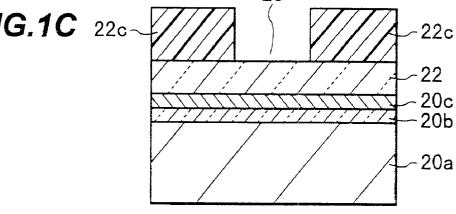

[0053] Next, as shown in FIG. 1C, a resist film 22c having a predetermined pattern is formed on the antireflection film 22 by photolithography, the resist film 22c having a hole 23. More specifically, a resist film is first coated on the whole surface of the antireflection film 22 and then the resist film 22c having a predetermined pattern is formed through selective exposure and development.

[0054] The antireflection film 22 can lower the intensity of reflection light during exposure because of light absorption of this film 22 itself and/or interference between reflected light from the surface of this film 22 and reflected light from the underlying layer. Since reflection light hardly exposes an undesired area, the resist film 22c having a predetermined pattern can be formed at a high resolution.

**[0055]** The hole 23 has a generally vertical side wall (inner wall) and has a circular plan shape (as viewed from the top) having a diameter of  $0.5 \,\mu\text{m}$ .

[0056] Next, as shown in FIG. 1D, by using the resist film 22c as a mask, the antireflection film 22 is anisotropically etched to leave an antireflection film 22a having a predetermined pattern with a hole 23a. This hole 23a has a generally vertical side wall (inner wall) and has a circular plan shape (as viewed from the top) having a diameter of 0.5  $\mu$ m. The antireflection film 22a has two parts (laterally separated regions) as viewed in section of FIG. 1D. Since the resist film 22c was formed at a high resolution, the antireflection film 22a having a predetermined pattern can be formed also at a high resolution.

[0057] For example, etching the antireflection film 22*a* is performed in a magnetron RIE system by using  $CHF_3$ +  $CO_2$ +Ar as etching gas under the conditions of a magnetic field of 5 G (Gauss), a reaction chamber pressure of 60 mTorr (about  $60 \times 10^{-3} \times 133.3$  Pa), a cooling He pressure of 8 Torr (about  $8 \times 133.3$  Pa) and an RF power of 500 W.

[0058] Next, as shown in FIG. 1E, the resist pattern 22c is removed to expose the upper surface of the antireflection film 22a.

[0059] Next, as shown in FIG. 1F, by using the antireflection film 22a as a mask, the getter material layer 20c is etched to form a getter film 20d having a predetermined pattern with a hole 23b. As will be later described, the hole 23b corresponds to a gate hole. By forming this hole 23b, a gate electrode made of the getter film 20d can be formed. Since the resist film 22c and antireflection film 22a were formed at a high resolution, the getter film 20d can be formed also at a high resolution.

**[0060]** For example, etching the getter material layer **20***c* is performed in a magnetron RIE system having a susceptor with a gas cooling mechanism, under the conditions of a  $Cl_2$  gas flow rate of 40 sccm, a pressure of 100 mTorr (about  $100 \times 10^{-3} \times 133.3$  Pa), an Rf power of 250 W, a magnetic field of 50 G (Gauss), and a cooling He pressure of 4 Torr (about  $4 \times 133.3$  Pa).

[0061] It is not limited only to that the getter material layer 20c is etched by using only the antireflection film 22a as a mask. The getter material layer 20c may be etched by using the antireflection film 22a and resist film 22c formed on the antireflection film 22a, without removing the resist film 22c. In this case, the resist film 22c is removed thereafter.

**[0062]** Next, as shown in **FIG. 1G, a** second sacrificial film (insulating film) **24** of SiO<sub>2</sub> is deposited over the whole upper surface of the substrate to a thickness of 0.15  $\mu$ m by atmospheric pressure CVD. For example, the atmospheric pressure CVD is performed by using O<sub>3</sub> and TEOS (tetra-etoxysilane, (C<sub>2</sub>H<sub>5</sub>O)<sub>4</sub>Si) as source gas at a substrate temperature of 400° C.

[0063] Next, as shown in FIG. 1H, the second sacrificial film 24 is anisotropically dry-etched (etched back) to leave a second sacrificial film 24a as a side spacer only on the side walls of the antireflection film 22a and getter film 20d. The "side wall" means a side wall of a hole formed by photoli-thography and etching, this definition being applied also in the following description. This etching exposes the upper area of the side wall of the antireflection film 22a is exposed and an etching process stops at the upper surface of the starting substrate 20a.

[0064] For example, this etching is performed in a magnetron RIE system by using  $CHF_3+CO_2+Ar$  as etching gas under the conditions of a reaction chamber pressure of 50 mTorr (about  $50\times10^{-3}\times133.3$  Pa), a  $CHF_3/CO_2/Ar$  flow rate of 60/10/30 (sccm), a substrate cooling He pressure of 8 Torr (about 8×133.3 Pa), a magnetic field of 30 G (Gauss), and an RF power of 700 W.

**[0065]** Next, as shown in **FIG. 1I**, a third sacrificial film (insulating film) **26** of SiO<sub>2</sub> is isotropically deposited over the whole upper surface of the substrate to a thickness of 0.15  $\mu$ m by atmospheric pressure CVD. The third sacrificial film **26** is deposited on the surfaces of the antireflection film **22***a*, side spacer **24***a*, first lamination film **20***b* and starting substrate **20***a*, inheriting (conformal to) the surface topology. The surface topology of the third sacrificial film **26** has curves of two stages. The first stage (upper) curve is dependent on the corner shape of the antireflection film **22***a* and the second stage (lower) curve is dependent on the surface **24***a*.

[0066] A cusp on the surface of the third sacrificial film 26 has an acute angle like a contact point between two circles or ellipses. This cusp is used as a mold for forming a two-stage shaped emitter electrode.

**[0067]** The "two-stage shaped emitter electrode" in this specification means an emitter electrode having a first circumferential surface continuous with the tip and a second circumferential surface continuous with the first circumferential surface, and a contour line of the first circumferential surface and the second circumferential surface, as viewed in vertical cross section of the emitter electrode, have different gradients at the boundary between the contour lines.

**[0068]** Next, as shown in **FIG. 1J**, an emitter electrode 27 of, for example,  $\text{TiN}_x$ , is deposited on the third sacrificial film 26 to a thickness of about 0.05  $\mu$ m by reactive sputtering. This reactive sputtering is performed in a DC sputtering system by using Ti as a target while gas of N<sub>2</sub>+Ar is introduced.

[0069] With this embodiment, a two-stage shaped emitter electrode 27 can be formed. It is easy to make the tip of the two-stage shaped emitter electrode have a smaller radius of curvature than that of the one-stage shaped emitter electrode shown in FIG. 15F. As the radius of curvature of the emitter electrode tip is made small, an electric field can be easily concentrated upon the emitter electrode tip and the performance of the field emission element can be improved.

**[0070]** Next, as shown in **FIG. 1K**, a blanket film (second emitter electrode) **27***c* of W (tungsten) is deposited on the emitter electrode (first emitter electrode) **27** to a thickness of 0.2  $\mu$ m by CVD. For example, this CVD is performed by using WF<sub>6</sub>+H<sub>2</sub>+N<sub>2</sub>+Ar gas as work gas at a pressure of 80 Torr (about 80×133.3 Pa) and a temperature of 450° C.

[0071] Next, as shown in FIG. 1L, the blanket film 27*c* of W (tungsten) is etched back 0.2  $\mu$ m thick by using an RIE etcher to leave a blanket film 27*d* only in a surface recess of the emitter electrode 27 to planarize the surface of the emitter electrode 27. For example, this RIE (reactive ion etching) is performed in a magnetron RIE system by using SF<sub>6</sub>+Ar+He as etching gas at a reaction chamber pressure of 280 mTorr (about 280×10<sup>-3</sup>×133.3 Pa).

[0072] Next, as shown in FIG. 1M, a resistor layer 30 of Si is deposited about 0.2  $\mu$ m thick by sputtering, covering the emitter electrode 27 and blanket film 27*d*. By serially connecting the resistor layer 30 to the emitter electrode 27, the emission current of the emitter electrode (field emission cathode) 27 can be stabilized sufficiently.

**[0073]** For example, sputtering for the resistor layer (Si) **30** is performed in a DC sputtering system by using Si as a target while Ar gas is introduced. Instead of Si, high resistance material such as  $SiN_x$ ,  $SiO_x$  and  $SiO_xN_y$  may be used as the material of the resistor layer **30**. In this case, instead of Ar gas, sputtering is performed by using N<sub>2</sub>+Ar gas, O<sub>2</sub>+Ar gas or N<sub>2</sub>+O<sub>2</sub>+Ar gas.

[0074] Next, as shown in FIG. 1N, an emitter wiring layer 31 of Al is deposited on the resistor layer 30 to a thickness of 0.3  $\mu$ m by sputtering. This sputtering is performed in a DC sputtering system by using Al as a target while Ar gas is introduced.

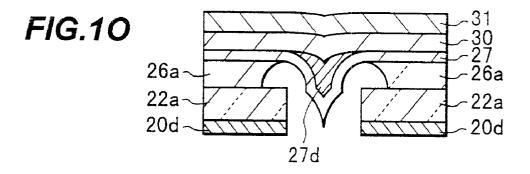

[0075] Lastly, as shown in FIG. 10, the whole of the starting substrate 20*a*, first lamination film 20*b* and side

spacer 24a and part of the third sacrificial film 26 are etched and removed from the bottom side, to leave a peripheral third sacrificial film 26a and expose the tip of the emitter electrode 27. The getter film 20d surrounds the tip of the emitter electrode 27.

[0076] For etching Si of the starting substrate 20a and the like, HF+HNO<sub>3</sub>+CH<sub>3</sub>COOH is used, and for etching SiO<sub>2</sub> of the third sacrificial film 26 and the like, HF+NH<sub>4</sub>F is used.

[0077] With the above processes, a field emission element (two-electrode element) having the two-stage shaped emitter electrode 27 is completed. Since the getter film (Ti film) 20d is a conductive film, it can function as the gate electrode. This field emission element has the emitter electrode 27 and gate electrode 20d.

[0078] The emitter electrode 27 is applied with a negative potential and an unrepresented anode electrode is applied with a positive potential. As a positive potential is applied to the gate electrode 20d, electrons can be emitted from the emitter electrode 27 toward the anode electrode.

[0079] After field emission elements are manufactured, a flat panel display such as shown in FIG. 16 is manufactured by the method similar to that described earlier. However, the getter member 51 shown in FIG. 16 is not necessary. After or before the inside of the flat display panel is evacuated and the air exhaust pipe is sealed, the getter film 20*d* (refer to FIG. 10) of field emission elements is activated by heating them with a lamp or laser beam or by other light application, so that ambient molecules can be adsorbed. In this manner, the vacuum degree in the flat panel display can be improved.

**[0080]** Other molecules such as He passing through the transparent substrate and support substrate and entering the inside of the flat display panel or other molecules such as  $H_2O$ ,  $O_2$ , and  $N_2$  emitted in the flat panel display are also adsorbed by the getter film **20***d*. As a result, the vacuum degree in the flat panel display is prevented from being lowered and the flat panel display is prolonged its lifetime.

**[0081]** The getter member **51** shown in **FIG. 16** is disposed at the corner in the flat panel display, remotely from the emitter electrodes, so that the function of the getter member cannot be sufficiently demonstrated.

[0082] According to the embodiment, the getter film 20d surrounds near the tip of the emitter electrode so that the following advantages can be obtained.

- [0083] (1) The getter film 20d adsorbs molecules near the emitter electrode 27 and prevents molecules from attaching the surface of the emitter electrode 27. Since the vacuum degree near at the emitter electrode 27 is improved, radiation current (electron flow) from the emitter electrode 27 can be prevented from being reduced.

- [0084] (2) Since the vacuum degree near the emitter electrode 27 can be improved, a magnitude of the radiation current of the emitter electrode 27 can be prevented from fluctuating.

- [0085] (3) Since the vacuum degree near the emitter electrode 27 can be improved, it is possible to prevent the emitter electrode 27 from being deformed through sputtering with ions.

- **[0086]** (4) Since the getter film **20***d* is formed in the field emission element, the size of the flat panel display can be made smaller than when the getter member is provided remotely from field emission elements.

- **[0087]** (5) The uniformity and reproductivity of characteristics of field emission elements in each flat display panel and between flat display panels can be improved. Flicker to be caused by luminance differences of a flat display panel can be reduced.

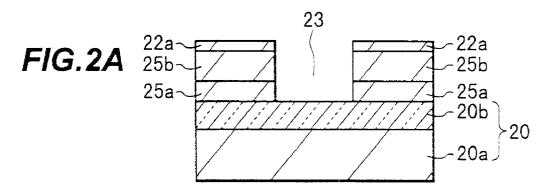

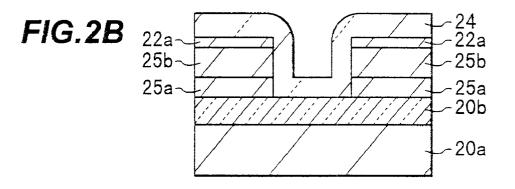

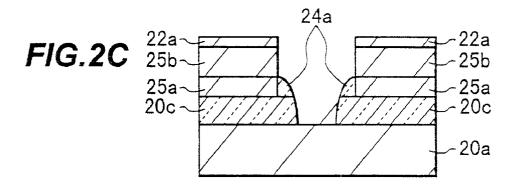

**[0088] FIGS. 2A** to 2F are schematic cross sectional views illustrating other manufacture steps of the field emission element (two-electrode element) according to the first embodiment of the invention.

[0089] As shown in FIG. 2A, similar to the first embodiment, by photolithography and etching, a first lamination film 20b of SiO<sub>2</sub> is formed on a starting substrate 20a of Si, and a first gate electrode 25a, a second gate electrode 25b and a getter film 22a respectively having a predetermined pattern are sequentially formed on the first lamination film 20b.

[0090] More specifically, on the surface of the starling substrate 20a of Si, the first lamination film 20b is formed through thermal oxidation. On the first lamination film 20b, a first gate electrode film is deposited by CVD to a thickness of 0.15  $\mu$ m, the first gate electrode film being made of polysilicon doped with P (phosphorous) or B (boron). On the first gate electrode film, a second gate electrode film of WSi. is deposited by CVD to a thickness of 0.15  $\mu$ m. On the second gate electrode film, a first sacrificial film (getter material layer) of Ti is deposited by sputtering to a thickness of 0.04  $\mu$ m. Thereafter, by photolithography and etching, the first and second gate electrode films and getter material layer are patterned. This patterning process forms a hole 23 through the getter material layer and first and second gate electrode films, the hole 23 reaching the surface of the first lamination film 20d. A hole formed through the first and second gate electrode films corresponds to the gate hole. Namely, this patterning process forms a two-layer structure gate electrode constituted of the first gate electrode 25a made of the first gate electrode film with a gate hole and the second gate electrode 25b made of the second gate electrode film with a gate hole. This patterning process also forms the getter film 22a shown in FIG. 2A.

**[0091]** Sputtering for the getter material layer (Ti layer) is performed in a DC sputtering system by using Ti as a target while Ar gas is introduced. Instead of Ti, the getter film **22***a* may be made of Ta or Zr (zirconium).

[0092] In the first embodiment (refer to FIG. 10), the getter film is formed as the gate electrode. In this modification of the first embodiment, the getter film 22a is formed over the gate electrodes 25a and 25b.

[0093] Next, as shown in FIG. 2B, a second sacrificial film (insulating film) 24 of  $SiO_2$  is isotropically deposited over the whole upper surface of the substrate to a thickness of 0.15  $\mu$ m by atmospheric pressure CVD.

[0094] Next, as shown in FIG. 2C, the second sacrificial film 24 is anisotropically dry-etched to leave a second sacrificial film 24a as a side spacer only on the side wall of the first gate electrode 25a. This etching process exposes the side walls of the getter film 22a and second gate electrode

**25***b* and a partial surface area of the first lamination film (etching stopper film) **20**. For example, this etching is performed in a magnetron RIE system by using CHF<sub>3</sub>+  $CO_2$ +Ar as etching gas under the conditions of a CHF<sub>3</sub>/ $CO_2$ /Ar flow ratio of 60/10/30 (sccm), a reaction chamber pressure of 50 mTorr (about  $50 \times 10^{-3} \times 133.3$  Pa), a substrate cooling He pressure of 8 Torr (about  $8 \times 133.3$  Pa), a magnetic field of 30 G. and an RF power of 700 W.

[0095] Next, as shown in FIG. 2D, a third sacrificial film (insulating film) 26 of SiO<sub>2</sub> is isotropically deposited over the whole upper surface of the substrate to a thickness of 0.15  $\mu$ m by atmospheric pressure CVD. The third sacrificial film 26 is deposited on the surfaces of the starting substrate 20*a*, first lamination film 20*c*, side spacer 24*a*, second gate electrode 25*b* and getter film 22*a*, being conformal to the surface topology. The surface topology of the third sacrificial film 26 has curves of two stages. This surface of the third sacrificial film 26 is used as a mold for forming a two-stage shaped emitter electrode.

[0096] Next, as shown in FIG. 2E, an emitter electrode 27 of, for example,  $\text{TiN}_{x}$ , is deposited on the third sacrificial film 26 to a thickness of about 0.05  $\mu$ m by reactive sputtering. This reactive sputtering is performed in a DC sputtering system by using Ti as a target while gas of N<sub>2</sub>+Ar is introduced.

[0097] Next, as shown in FIG. 2F, the whole of the starting substrate 20a, first lamination film 20c and side spacer 24a and part of the third sacrificial film 26 are etched and removed from the bottom side, to leave a peripheral third sacrificial film 26a and expose the tip of the emitter electrode 27.

**[0098]** For etching Si of the starting substrate 20a and the like, HF+HNO<sub>3</sub>+CH<sub>3</sub>COOH is used, and for etching SiO<sub>2</sub> of the third sacrificial film **26** and the like, HF+NH<sub>4</sub>F is used.

[0099] With the above processes, a field emission element (two-electrode element) having the two-stage shaped emitter electrode 27 is completed. Since the getter film (Ti film) 22a is a conductive film, it can function as the gate electrode together with the first and second gate electrodes 25a and 25b. This field emission element has the emitter electrode 27 and gate electrodes 25a, 25b and 22a. The getter film 22a is formed over the gate electrodes 25a and 25b and surrounds near the tip of the emitter electrode 27.

**[0100]** Similar to the first embodiment, after field emission elements are manufactured, a flat panel display such as shown in **FIG. 16** is manufactured. After or before the air exhaust pipe of the flat panel display is sealed, the getter film 22a of field emission elements is activated by heating them with a lamp or laser beam or by other light application, so that ambient molecules can be adsorbed.

[0101] For example, light may be applied to the gate electrodes 25a and 25b to heat them and heat the getter film 22a through heat conduction. If the getter film 22a made of a Ti film or the like is heated to  $400^{\circ}$  C. or higher, it can be activated. Light is preferably applied to the substrate along a direction perpendicular to the substrate surface. However, it may be applied obliquely. The getter film 22a may be activated by baking the substrate in a furnace.

**[0102]** FIGS. 3A to 3D are schematic cross sectional views illustrating four methods of reinforcing the emitter

electrode 27 by a support substrate 28. Since the emitter electrode 27 has a small thickness of about 0.2  $\mu$ m, it may preferably be reinforced with the support substrate 28.

**[0103]** FIG. 3A illustrates the first method. A recess of the emitter electrode 27 of the field emission element manufactured to the state shown in FIG. 2E is filled with a planarizing film 29a, e.g., an SOG (spin on glass) film. Thereafter, the planarizing film 29a is etched back through CMP (chemical-mechanical polishing) or RIE to planarize the surface of the emitter electrode 27. Instead of an SOG film, the planarizing film 29a may be formed by reflowing PSG (phosphosilicate glass) or BPSG (borophosphosilicate glass).

**[0104]** Next, a support substrate **28** is bonded to the emitter electrode by electrostatic bonding or with adhesive. The support substrate **28** is made of, for example, glass, quartz, or  $Al_xO_y$  (alumina or sapphire). Thereafter, similar to the process shown in **FIG. 2**F, the substrate **20***a* and the like are removed to expose the tip of the emitter electrode **27** as shown in **FIG. 3A**.

[0105] FIG. 3B illustrates the second method. In the state of the field emission element shown in FIG. 2E, adhesive 29b made of, e.g., low melting point glass or epoxy resin is flowed on the emitter electrode 27 to bond the emitter electrode 27 and a support substrate 28. The adhesive 29b also provides a function of planarizing the surface of the emitter electrode 27. Thereafter, similar to the process shown in FIG. 2F, the substrate 20a and the like are removed to expose the tip of the emitter electrode 27 as shown in FIG. 3B.

[0106] FIG. 3C illustrates the third method. After the field emission element shown in FIG. 2E is manufactured, a recess of the emitter electrode 27 is filled with a planarizing film 29a made of, for example, SOG. Thereafter, the planarizing film 29a is etched back to planarize the surface of the emitter electrode 27. Next, an adhesive layer 29b made of, for example, Al, is formed on the emitter electrode 27, and a support substrate 28 is bonded. Thereafter, similar to the process shown in FIG. 2F, the substrate 20a and the like are removed to expose the tip of the emitter electrode 27 as shown in FIG. 3C.

[0107] FIG. 3D illustrates the fourth method. Similar to the processes shown in FIGS. 1K and 1L, after the blanket film (second emitter electrode) 27c of W is formed on the emitter electrode (first emitter electrode) 27 to a thickness of 0.2  $\mu$ m by CVD, the blanket film 27c is etched back 0.2  $\mu$ m thick by using an RIE etcher to leave the blanket film 27d. Similar to the process shown in FIG. 3C, a recess of the blanket film 27d is filled with a planarizing film 29a such as SOG and thereafter the planarizing film 29a is etched back to planarize the surface of the blanket film 27d. Next, the emitter electrode 27, blanket film 27d and planarizing film 29a are bonded to a support substrate 28 with adhesive 29b. Thereafter, similar to the process shown in FIG. 2F, the substrate 20a and the like are removed while the getter film 22 is wet-etched, to leave a peripheral getter film 22b and expose the tip of the emitter electrode 27 as shown in FIG. **3D**.

[0108] Etching the getter film 22a of Ti is performed by using a mixture solution of sulfuric acid and hydrogen peroxide, while the mixture solution is heated to about  $120^{\circ}$

C. In place of the mixture solution of sulfuric acid and hydrogen peroxide, the etching may be performed by using hydrochloric acid, phosphoric acid or hydrofluoric acid.

**[0109]** FIGS. 4A to 4F are schematic cross sectional views illustrating the manufacture steps of a field emission element (two-electrode element) according to a modification of the first embodiment of the invention.

[0110] As shown in FIG. 4A, similar to the first embodiment, by photolithography and etching, a gate electrode 25aand a first sacrificial film (getter film) 22a having a predetermined pattern are formed on a starting substrate 20e. The gate electrode 25a has a gate hole 23.

**[0111]** More specifically, on the surface of the starting substrate **20***e* of Si, a gate electrode film of WSi<sub>x</sub> is deposited to a thickness of 0.3  $\mu$ m by sputtering, and on the gate electrode film a getter material layer of Ti is deposited to a thickness of 0.05  $\mu$ m by sputtering. Thereafter, by photoli-thography and etching, the gate electrode film and getter material layer are patterned. This patterning process forms the getter film **22***a* and gate electrode **25***a* shown in **FIG. 4A**. The getter film (Ti film) **22***a* is formed on the gate electrode (WSi<sub>x</sub> film) **25***a*.

**[0112]** For example, this etching process is performed in a magnetron RIE system by using  $Cl_2$  as etching gas under the conditions of a reaction chamber pressure of 100 mTorr (about  $100 \times 10^{-3} \times 133.3$  Pa), a  $Cl_2$  gas flow of 40 sccm, a substrate cooling He pressure of 4 Torr (about  $4 \times 133.3$  Pa), a magnetic field of 50 G, and an RF power of 250 W.

**[0113]** Sputtering for the gate electrode film (WSi<sub>x</sub> film) is performed in a DC sputtering system by using WSi<sub>x</sub> as a target while Ar gas is introduced. Sputtering for the getter material layer (Ti film) is performed in a DC sputtering system using Ti as a target while Ar gas is introduced.

**[0114]** Next, as shown in **FIG. 4B**, a second sacrificial film (insulating film) **24** of  $SiO_2$  is isotropically deposited over the whole upper surface of the substrate to a thickness of 0.15  $\mu$ m by atmospheric pressure CVD.

**[0115]** Next, as shown in **FIG. 4**C, the second sacrificial film **24** is anisotropically dry-etched to leave a second sacrificial film **24***a* as a side spacer only on the side wall of the gate electrode **25***a* and/or the side wall of the getter film **22***a*. This etching process exposes the side wall of the getter film **22***a* and a partial surface of the starting substrate **20***e*.

**[0116]** For example, this etching is performed in a magnetron RIE system by using  $CHF_3+CO_2+Ar$  as etching gas under the conditions of a reaction chamber pressure of 50 mTorr (about  $50 \times 10^{-3} \times 133.3$  Pa), a  $CHF_3/CO_2/Ar$  flow ratio of 60/10/30 (sccm), a substrate cooling He pressure of 8 Torr (about 8×133.3 Pa), a magnetic field of 30 G, and an RF power of 700 W.

**[0117]** Next, as shown in **FIG. 4D**, a third sacrificial film (insulating film) **26** of SiO<sub>2</sub> is isotropically deposited over the whole upper surface of the substrate to a thickness of 0.15  $\mu$ m by atmospheric pressure CVD. The third sacrificial film **26** is deposited on the surfaces of the starting substrate **20***e*, side spacer **24***a* and getter film **22***a*, being conformal to the surface topology. The surface topology of the third sacrificial film **26** has curves of two stages. This surface of the third sacrificial film **26** is used as a mold for forming a two-stage shaped emitter electrode.

**[0118]** Next, as shown in **FIG. 4**E, an emitter electrode **27** of, for example,  $\text{TiN}_x$ , is deposited on the third sacrificial film **26** to a thickness of about 0.05  $\mu$ m by reactive sputtering.

[0119] Lastly, as shown in FIG. 4F, the whole of the starting substrate 20e and side spacer 24a and part of the third sacrificial film 26 are etched and removed from the bottom side, to leave a peripheral third sacrificial film 26a and expose the tip of the emitter electrode 27.

**[0120]** With the above processes, a field emission element (two-electrode element) having the two-stage shaped emitter electrode 27 is completed. Since the getter film (Ti film) 22a is a conductive film formed on the gate electrode (WSi<sub>x</sub> film) 25a, it can function as the gate electrode together with the gate electrode 25a. This field emission element has the emitter electrode 27 and gate electrodes 25a and 22a. After or before field emission elements are hermetically accommodated in the flat panel display, the getter film 22a of field emission elements is activated by heating them or by light application.

**[0121]** FIGS. 5A to 5F are schematic cross sectional views illustrating the manufacture steps of a field emission element (two-electrode element) according to another modification of the first embodiment of the invention.

[0122] As shown in FIG. 5A, similar to the first embodiment, by photolithography and etching, a gate electrode 25a, a first sacrificial film (getter film) 22a and a second sacrificial film (insulating film) 22c respectively having a predetermined pattern are formed on a starting substrate 20e of Si.

[0123] More specifically, on the surface of the starting substrate 20e of Si, a gate electrode film of WSix is deposited to a thickness of 0.3  $\mu$ m by sputtering, and on the gate electrode film a getter material layer of Ti is deposited to a thickness of 0.04  $\mu$ m by sputtering, and on the getter material layer a second sacrificial film of SiN<sub>x</sub> is deposited to a thickness of 0.3  $\mu$ m by reactive sputtering. Thereafter, by photolithography and etching, the gate electrode film, getter material layer and second sacrificial film are patterned. This patterning process forms a hole 23 through the second sacrificial film to the surface of the starting substrate 20e. A hole formed through the gate electrode film corresponds to the gate hole. This patterning process therefore forms the gate electrode 25a having the gate hole, and also forms the getter film 22a and second sacrificial film 22cshown in FIG. 5A. The getter film 22a is formed between the gate electrode 25a and second sacrificial film 22c.

**[0124]** If the thickness of  $SiN_x$  is set to 0.3  $\mu$ m, the antireflection effect can be obtained. A resolution of photolithography and an etching precision are therefore improved.

**[0125]** Sputtering for the getter material layer (Ti film) is performed in a DC sputtering system by using Ti as a target while Ar gas is introduced. Reactive sputtering for the second sacrificial film (SiN<sub>x</sub> film) is performed in a DC sputtering system by using Si as a target while N<sub>2</sub>+Ar gas is introduced. The second sacrificial film (SiN<sub>x</sub> film) may be deposited by plasma CVD or low pressure CVD.

**[0126]** Next, as shown in **FIG. 5B**, a third sacrificial film (insulating film) **24** of SiO<sub>2</sub> is isotropically deposited over

the whole upper surface of the substrate to a thickness of 0.15  $\mu$ m by atmospheric pressure CVD.

[0127] Next, as shown in FIG. 5C, the third sacrificial film 24 is anisotropically dry-etched to leave a third sacrificial film 24*a* as a side spacer only on the side wall of the gate electrode 25a and/or the side wall of the getter film 22a. This etching process exposes the side wall of the getter film 22a and the side wall of the getter film 22a and the side wall of the getter film 22a and a partial surface of the starting substrate 20e.

**[0128]** For example, this etching is performed in a magnetron RIE system by using  $CHF_3+CO_2+Ar$  as etching gas under the conditions of a reaction chamber pressure of 50 mTorr (about  $50 \times 10^{-3} \times 133.3$  Pa), a  $CHF_3/CO_2/Ar$  flow ratio of 60/10/30 (sccm), a substrate cooling He pressure of 8 Torr (about 8×133.3 Pa), a magnetic field of 30 G, and an RF power of 700 W.

**[0129]** Next, as shown in **FIG. 5D**, **a** fourth sacrificial film (Insulating film) **26** of SiO<sub>2</sub> is isotropically deposited over the whole upper surface of the substrate to a thickness of 0.15  $\mu$ m by atmospheric pressure CVD. The fourth sacrificial film **26** is deposited on the surfaces of the starting substrate **20***e*, side spacer **24***a*, getter film **22***a*, and second sacrificial film **22***c*, being conformal to the surface topology. The surface topology of the third sacrificial film **26** has curves of two stages. This surface of the fourth sacrificial film **26** is used as a mold for forming a two-stage shaped emitter electrode.

**[0130]** Next, as shown in **FIG. 5**E, an emitter electrode **27** of, for example,  $TiN_x$ , is deposited on the fourth sacrificial film **26** to a thickness of about 0.05  $\mu$ m by reactive sputtering.

[0131] Lastly, as shown in FIG. 5F, the whole of the starting substrate 20e and side spacer 24a and part of the fourth sacrificial film 26 are etched and removed from the bottom side, to leave a peripheral fourth sacrificial film 26a and expose the tip of the emitter electrode 27.

**[0132]** With the above processes, a field emission element (two-electrode element) having the two-stage shaped emitter electrode 27 is completed. Since the getter film (Ti film) 22*a* is a conductive film formed on the gate electrode 25a, it can function as the gate electrode together with the gate electrode 25a. This field emission element has the emitter electrode 27 and gate electrodes 25a and 22a. After or before field emission elements are hermetically accommodated in the flat panel display, the getter film 22a of field emission elements is activated by heating them or by light application.

**[0133] FIGS. 6A** to **6**F are schematic cross sectional views illustrating the manufacture steps of a field emission element (two-electrode element) according to another modification of the first embodiment of the invention.

[0134] As shown in FIG. 6A, similar to the first embodiment, by photolithography and etching, a gate electrode 25aand a first sacrificial film (getter film) 22a respectively having a predetermined pattern are formed on a starting substrate 20e of Si.

**[0135]** More specifically, on the surface of the starting substrate **20***e* of Si, a gate electrode film is deposited by CVD to a thickness of  $0.15 \,\mu$ m, the gate electrode film being made of polysilicon doped with P (phosphorous) or B (boron). On the gate electrode film, a getter material layer of

Ti is deposited by sputtering to a thickness of 0.04  $\mu$ m. Thereafter, by photolithography and etching, the gate electrode film and getter material layer are patterned. This patterning process forms a hole 23 through the getter material layer, the hole 23 reaching the surface of the starting substrate 20e. A hole formed through the gate electrode film corresponds to the gate hole. Namely, this patterning process forms the gate electrode 25a having the gate hole and the getter film 22a shown in FIG. 6A.

**[0136]** Next, as shown in **FIG. 6B**, a second sacrificial film (insulating film) 24 of  $SiO_2$  is isotropically deposited over the whole upper surface of the substrate to a thickness of 0.15  $\mu$ m by atmospheric pressure CVD.

**[0137]** Next, as shown in **FIG. 6**C, the second sacrificial film **24** is anisotropically dry-etched to leave a second sacrificial film **24***a* as a side spacer only on the side wall of the gate electrode **25***a*. This etching process exposes the side walls of the getter film **22***a* and gate electrode **25***a*, and stops when the substrate **20***f* is trenched 0.1  $\mu$ m deep. This etching process forms the substrate **20***f* having a recess. For example, this etching is performed in a magnetron RIE system by using CHF<sub>3</sub>+CO<sub>2</sub>+Ar as etching gas under the conditions of a reaction chamber pressure of 50 mTorr (about 50×10<sup>-3</sup>×133.3 Pa), a CHF<sub>3</sub>/CO<sub>2</sub>/Ar flow ratio of 60/10/30 (sccm), a substrate cooling He pressure of 8 Torr (about 8×133.3 Pa), a magnetic field of 30 G, and an RF power of 700 W.

**[0138]** Next, as shown in **FIG. 6D**, a third sacrificial film (insulating film) **26** of SiO<sub>2</sub> is isotropically deposited over the whole upper surface of the substrate to a thickness of 0.15  $\mu$ m by atmospheric pressure CVD. The third sacrificial film **26** is deposited on the surfaces of the substrate **20***f*, side spacer **24***a*, gate electrode **25***a*, and getter film **22***a*, being conformal to the surface topology. The surface topology of the third sacrificial film **26** has curves of two stages. This surface of the third sacrificial film **26** is used as a mold for forming a two-stage shaped emitter electrode.

**[0139]** Next, as shown in **FIG. 6**E, an emitter electrode **27** of, for example,  $\text{TiN}_{xy}$ , is deposited on the third sacrificial film **26** to a thickness of about 0.05  $\mu$ m by reactive sputtering.

[0140] Lastly, as shown in FIG. 6F, the whole of the starting substrate 20f and side spacer 24a and part of the third sacrificial film 26 are etched and removed from the bottom side, to leave a peripheral third sacrificial film 26a and expose the tip of the emitter electrode 27.

[0141] This two-electrode element has the emitter electrode 27 positioned lower (as viewed in FIG. 6F) relative to the gate electrode 25a than the two-electrode element shown in FIG. 4F, because the recess is formed in the substrate 20f at the etching process shown in FIG. 6C.

[0142] With the above processes, a field emission element (two-electrode element) having the two-stage shaped emitter electrode 27 is completed. Since the getter film (Ti film) 22a is a conductive film, it can function as the gate electrode. This field emission element has the emitter electrode 27 and gate electrodes 25a and 22a and can be used with a flat display panel. After or before field emission elements are hermetically accommodated in the flat panel display, the getter film 22a of field emission elements is activated by heating them or by light application.

**[0143] FIGS. 7A** to 7F are schematic cross sectional views illustrating the manufacture steps of a field emission element (two-electrode element) according to another modification of the first embodiment of the invention.

**[0144]** As shown in **FIG. 7**A, similar to the first embodiment, by photolithography and etching, a gate electrode/ getter film 25a having a predetermined pattern is formed on a starting substrate 20e of Si.

**[0145]** More specifically, on the surface of the starting substrate **20***e* of Si, a gate electrode film/getter material layer is deposited by sputtering to a thickness of 0.3  $\mu$ m. Thereafter, by photolithography and etching, the gate electrode film/getter material layer is patterned. This patterning process forms a hole **23** through the gate electrode film/getter material layer, the hole **23** reaching the surface of the starting substrate **20***e*. The hole formed through the gate electrode film/getter material layer corresponds to the gate hole. Namely, this patterning process forms the gate electrode/getter film **25***a* having the gate hole shown in **FIG. 7A**.

**[0146]** Next, as shown in **FIG. 7B**, **a** second sacrificial film (insulating film) **24** of  $\text{SiO}_2$  is isotropically deposited over the whole upper surface of the substrate to a thickness of 0.15  $\mu$ m by atmospheric pressure CVD.

**[0147]** Next, as shown in **FIG. 7**C, the second sacrificial film **24** is anisotropically dry-etched to leave a second sacrificial film **24***a* as a side spacer only on the side wall of the gate electrode/getter film **25***a*. This etching process exposes the upper area of the side wall of the gate electrode/ getter film **25***a*, and stops when the substrate **20***f* is trenched 0.1  $\mu$ m deep. This etching process forms the substrate **20***f* having a recess. For example, this etching is performed in a magnetron RIE system by using CHF<sub>3</sub>+CO<sub>2</sub>+Ar as etching gas under the conditions of a reaction chamber pressure of 50 mTorr (about 50×10<sup>-3</sup>×133.3 Pa), a CHF<sub>3</sub>/CO<sub>2</sub>/Ar flow ratio of 60/10/30 (sccm), a substrate cooling He pressure of 8 Torr (about 8×133.3 Pa), a magnetic field of 30 G, and an RF power of 700 W.

**[0148]** Next, as shown in **FIG. 7D**, a third sacrificial film (insulating film) **26** of SiO<sub>2</sub> is isotropically deposited over the whole upper surface of the substrate to a thickness of 0.15  $\mu$ m by atmospheric pressure CVD. The third sacrificial film **26** is deposited on the surfaces of the substrate **20***f*, side spacer **24***a*, gate electrode/getter film **25***a*, being conformal to the surface topology. The surface topology of the third sacrificial film **26** has curves of two stages. This surface of the third sacrificial film **26** is used as a mold for forming a two-stage shaped emitter electrode.

**[0149]** Next, as shown in **FIG. 7**E, an emitter electrode **27** of, for example,  $\text{TiN}_{x}$ , is deposited on the third sacrificial film **26** to a thickness of about 0.05  $\mu$ m by reactive sputtering.

[0150] Lastly, as shown in FIG. 7F, the whole of the starting substrate 20f and side spacer 24a and part of the third sacrificial film 26 are etched and removed from the bottom side, to leave a peripheral third sacrificial film 26a and expose the tip of the emitter electrode 27.

**[0151]** With the above processes, a field emission element (two-electrode element) having the two-stage shaped emitter electrode **27** is completed. The gate electrode/getter film (Ti film) **25***a* functions as the gate electrode and getter film. This

field emission element has the emitter electrode 27 and gate electrode 25a and can be used with a flat display panel. After or before field emission elements are hermetically accommodated in the flat panel display, the getter film 25a of field emission elements is activated by heating them or by light application.

**[0152]** The manufacture steps of a field emission element (two-electrode element) having an emitter electrode and a gate electrode have been described above. In the following, the manufacture steps of a three-electrode element as an example of another field emission element will be described.

**[0153] FIGS. 8A** to **8**L are schematic cross sectional views illustrating the manufacture steps of a field emission element (three-electrode element) according to the second embodiment of the invention. A three-electrode element has an emitter electrode, a gate electrode and an anode electrode.

**[0154]** As shown in **FIG. 8A**, a substrate **20** is made of a starting substrate **20***a* and an anode electrode film **20***b* formed thereon. On the surface of the starting substrate **20***a* made of SiO<sub>2</sub> or the like, the anode electrode film **20***b* of WSi<sub>x</sub> is deposited to a thickness of 0.05  $\mu$ m by sputtering. Sputtering for the anode electrode film (WSi<sub>x</sub> film) **20***b* is performed in a DC sputtering system by using WSi<sub>x</sub> as a target while Ar gas is introduced.

**[0155]** Next, a first sacrificial film (insulating film) **21** of SiO<sub>2</sub> is deposited on the anode electrode film **20***b* by CVD, and on the first sacrificial film a gate electrode film of WSi<sub>x</sub> is deposited to a thickness of  $0.3 \,\mu$ m by sputtering similar to the above.

**[0156]** Next, as shown in **FIG. 8B**, a second sacrificial film (getter material layer) 22b of Ti is deposited on the gate electrode film 25 to a thickness of 0.04  $\mu$ m by sputtering. Sputtering for the getter material layer (Ti film) 22b is performed in a DOC sputtering system by using Ti as a target while Ar gas is introduced. In place of Ti, the getter material layer 22b may be formed by using Ta or Zr (zirconium).

[0157] Next as shown in FIG. 8C, a resist film 22*c* having a predetermined pattern with a hole 23 is formed on the getter material layer through photolithography.

**[0158]** Next, as shown in **FIG. 8**D, by using the resist film **22***c* as a mask, the getter material layer **22***b* is anisotropically etched to leave a getter film **22***a* having a predetermined pattern with a hole **23***a*. This hole **23***a* has a generally vertical side wall and has a circular plan shape (as viewed from the top) having a diameter of  $0.5 \ \mu m$ .

[0159] Next, as shown in FIG. 8E, the resist pattern 22*c* is removed to expose the upper surface of the getter film 22*a*.

**[0160]** Next, as shown in **FIG. 8**F, by using the getter film **22***a* as a mask, the gate electrode film **25** is anisotropically etched to form a gate electrode **25***a* having a predetermined pattern with a hole (gate hole) **23***b*.

[0161] When the gate electrode film 25 is etched, the resist film 22c and getter film 22a may be used as the mask, by leaving the resist film 23c on the getter film 22a. In this case, the resist film 22c is removed thereafter.

**[0162]** Next, as shown in **FIG. 8G**, **a** third sacrificial film (insulating film) **24** of SiO<sub>2</sub> is deposited over the whole upper surface of the substrate to a thickness of 0.15  $\mu$ m by

atmospheric pressure CVD. For example, the atmospheric pressure CVD is performed by using  $O_3$  and TEOS as source gas at a substrate temperature of 400° C.

[0163] Next, as shown in FIG. 8H, the third sacrificial film 24 is anisotropically dry-etched (etched back) to leave a third sacrificial film 24*a* as a side spacer only on the side wall of the gate electrode 25a and/or the side wall of the getter film 22a. This etching exposes the upper area of the side wall of the getter film 22a and a partial surface area of the first sacrificial film 21.

**[0164]** For example, this etching is performed in a magnetron RIE system by using  $CHF_3+CO_2+Ar$  as etching gas under the conditions of a reaction chamber pressure of 50 mTorr (about  $50\times10^{-3}\times133.3$  Pa), a substrate cooling He pressure of 8 Torr (about  $8\times133.3$  Pa), a magnetic field of 30 G, and an RF power of 700 W.

**[0165]** Next, as shown in **FIG. 8I**, **a** fourth sacrificial film (insulating film) **26** of SiO<sub>2</sub> is isotropically deposited over the whole upper surface of the substrate to a thickness of 0.15  $\mu$ m by atmospheric pressure CVD. The fourth sacrificial film **26** is deposited on the surfaces of the first sacrificial film **21**, side spacer **24***a* and getter film **22***a*, being conformal to the surface topology. The surface topology of the fourth sacrificial film **26** has curves of two stages. This surface of the fourth sacrificial film **26** has curves of a mold for forming a two-stage shaped emitter electrode.

**[0166]** Next, as shown in **FIG. 8J**, an emitter electrode **27** of, for example,  $TiN_x$ , is deposited on the fourth sacrificial film **26** to a thickness of about 0.05  $\mu$ m by reactive sputtering. This reactive sputtering is performed in a DC sputtering system by using Ti as a target while gas of N<sub>2</sub>+Ar is introduced.

**[0167]** Next, a resist film (not shown) having a predetermined pattern is formed on the emitter electrode **27** by photolithography. As shown in **FIG. 8**K, by using this resist film as an etching mask, slit openings **32** are formed by RIE through the emitter electrode **27***a* on both sides thereof in areas where the emitter electrode **27***a* is not used as the cathode. An emitter electrode **27***b* shown in **FIG. 8K** is an emitter electrode formed outside of the slit openings **32**. For example, RIE is performed in a magnetron RIE system by using Cl<sub>2</sub> as etching gas at a reaction chamber pressure of 125 mTorr (about  $125 \times 10^{-3} \times 133.3$  Pa).

[0168] Next, as shown in FIG. 8L, part of the fourth sacrificial film 26, the whole of the side spacer 24a, and part of the first sacrificial film 21 are isotropically wet etched and removed through the slit openings 32 to leave a peripheral fourth sacrificial film 26a and first sacrificial film 21a.

**[0169]** This etching exposes the emitter electrode 27a, gate electrode 25a and anode electrode film 20b. Since the getter film 22a electrically connects the gate electrode 25a, a resistance of the gate wiring line can be lowered.

**[0170]** FIG. 9 is a schematic perspective view partially in section of the three-electrode element shown in FIG. 8L. The emitter electrode 27a is continuous with the emitter electrode 27b and supported by the latter. The gate electrode 25a and getter film 22a have circular holes (gate holes) near at the tip of the emitter electrode 27a. The getter film 22a surrounds the tip of the emitter electrode 27a. The tip of the

emitter electrode 27a has a needle-like sharp edge near the gate hole of the gate electrode 25a.

[0171] The three-electrode element has the emitter electrode 27a as a cathode and an anode electrode film 20b as an anode. As a positive potential is applied to the gate electrode 25a, electrons can be emitted from the emitter electrode 27a toward the anode electrode film 20b.

[0172] Also in the case of the three-electrode element, by forming the getter film 22a near the tip of the emitter electrode 27a, the vacuum degree in the space near the emitter electrode 27a can be raised.

**[0173]** FIG. 10A is a schematic cross sectional view showing another example of the three-electrode element. This three-electrode element is fundamentally the same as the three-electrode element (shown in FIG. 8L), excepting that the gate electrode 25a is made of a WSi<sub>x</sub> film having a thickness of 0.3  $\mu$ m and the getter film 22a is made of a Ti film having a thickness of 0.2  $\mu$ m. The other structures are the same.

[0174] FIG. 10B is a schematic cross sectional view showing another example of the three-electrode element. This three-electrode element is fundamentally the same as the three-electrode element (shown in FIG. 8L), excepting that the gate electrode 25a is made of a WSi, film having a thickness of 0.3  $\mu$ m and the getter film 22*a* is made of a Ta film having a thickness of 0.15  $\mu$ m. Another different point is that in the etching process shown in FIG. 8H, an over-etch is performed to form a recess having a depth of  $0.1 \,\mu\text{m}$  in the first sacrificial film 21. The emitter electrode 27a can therefore be lowered relative to the gate electrode 25a as viewed in FIG. 8H. The other structures are the same. For example, this over-etch is performed in a magnetron RIE system by using CHF<sub>3</sub>+CO<sub>2</sub>+Ar as etching gas under the conditions of a reaction chamber pressure of 50 mTorr (about  $50 \times 10^{-3} \times 133.3$  Pa), a CHF<sub>3</sub>/CO<sub>2</sub>/Ar flow ratio of 60/10/30 (sccm), a substrate cooling He pressure of 8 Torr (about 8×133.3 Pa), a magnetic field of 30 G, and an RF power of 700 W.

**[0175]** FIG. 10C is a schematic cross sectional view showing another example of the three-electrode element. This three-electrode element is fundamentally the same as the three-electrode element (shown in FIG. 8L), excepting that the getter film 22*a* is made of a Ti film and that in the etching process shown in FIG. 8H, an over-etch is performed to form a recess having a depth of 0.1  $\mu$ m in the first sacrificial film 21. The other structures are the same. For example, this over-etch is performed in a magnetron RIE system by using CHF<sub>3</sub>+CO<sub>2</sub>+Ar as etching gas under the conditions of a reaction chamber pressure of 50 mTorr (about 50×10<sup>-3</sup>×133.3 Pa), a CHF<sub>3</sub>/CO<sub>2</sub>/Ar flow ratio of 60/10/30 (sccm), a substrate cooling He pressure of 8 Torr (about 8×133.3 Pa), a magnetic field of 30 G, and an RF power of 700 W.

**[0176] FIG. 10D** is a schematic cross sectional view showing another example of the three-electrode element. This three-electrode element is fundamentally the same as the three-electrode element (shown in **FIG. 8L**), excepting that the two layers of the gate electrode and getter film are made of one layer of a gate electrode/getter film **25***a* of Ti or the like and that in the etching process shown in **FIG. 8**H, an over-etch is performed to form a recess having a depth of

0.1  $\mu$ m in the first sacrificial film **21**. The other structures are the same. For example, this over-etch is performed in a magnetron RIE system by using CHF<sub>3</sub>+CO<sub>2</sub>+Ar as etching gas under the conditions of a reaction chamber pressure of 50 mTorr (about 50×10<sup>-3</sup>×133.3 Pa), a CHF<sub>3</sub>/CO<sub>2</sub>/Ar flow ratio of 60/10/30 (sccm), a substrate cooling He pressure of 8 Torr (about 8×133.3 Pa), a magnetic field of 30 G, and an RF power of 700 W.

**[0177]** In the first and second embodiments, the getter film in a field emission a element is formed under or on the gate electrode or by making the gate electrode of getter material. Since the getter film is formed surrounding the tip of the emitter electrode, molecules near the emitter electrode can be adsorbed and the vacuum degree can be raised.

**[0178]** By raising the vacuum degree near the emitter electrode, radiation current from the emitter electrode can be prevented from being lowered, a magnitude or the radiation current can be prevented from fluctuating, and the emitter electrode can be prevented from being deformed through sputtering.

**[0179]** Furthermore, the uniformity and reproductivity of characteristics of field emission elements in each flat display panel and between flat display panels can be improved and flicker to be caused by luminance differences of a flat display panel can be reduced.

**[0180]** Still further, since the getter film is provided in a field emission element, the size of a flat panel display can be made smaller than when the getter material is provided outside of field emission elements. It is not limited only to that the getter film is formed directly on the gate electrode, but an insulating film or other film may be formed between the gate electrode and getter film.

**[0181]** A side spacer made of Ti, Ta or Zr can be used as a getter film.

**[0182]** For the elements shown in **FIGS. 2F, 4F**, and **6**F, the gate electrode may be heated by light application to heat and activate the getter film through heat conduction. For the elements shown in **FIGS. 8L and 10D**, the emitter electrode may be heated by light application to heat and activate the getter film through heat conduction.

**[0183]** The material of the gate electrode and emitter electrode may be semiconductor such as polysilicon and amorphous silicon, silicide such as  $SWi_x$ ,  $TiSi_x$  and  $MoSi_x$ , metal such as Al, Cu, W, Mo and Ni, and conductive nitride such as  $TiN_x$ .

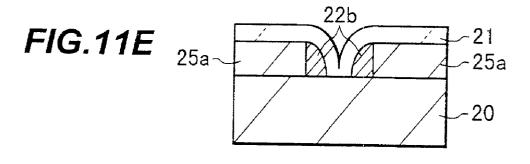

**[0184] FIGS. 11A** to **111** are schematic cross sectional views illustrating the manufacture steps of a field emission element according to the third embodiment of the invention.

**[0185]** As shown in **FIG. 11**A, on a substrate **20** of Si or the like, a gate electrode film **25** of 0.2  $\mu$ m in thickness is formed by CVD or the like. The gate electrode film **25** is, for example, a polysilicon film doped with phosphorous or boron. For example, a polysilicon film is formed by CVD by flowing SiH<sub>4</sub> gas diluted with He at a flow rate of 0.6 slm under the conditions of a chamber temperature of 625° C. and a pressure of about 225 mTorr (30 Pa). Next, in order to lower the resistance of the gate electrode film **25**, phosphorous is diffused into the polysilicon film in a vertical diffusion furnace under the conditions of POCl<sub>3</sub> at 50 mg/min, N<sub>2</sub> at 20 slm, O<sub>2</sub> at 0.1 slm, and a temperature of 850° C.

[0186] It is preferable to form a silicon oxide film or silicon nitride film between the Si substrate 20 and gate electrode film 25 as an etching stopper when the Si substrate 20 is etched.

**[0187]** Next, as shown in **FIG. 11B**, by using a resist pattern (not shown) as a mask, the gate electrode film **25** is etched to form a gate electrode **25***a* with a hole (gate hole) **23**. The hole (gate hole) is cylindrical and has a diameter of about 0.5  $\mu$ m and a depth of about 0.2  $\mu$ m. Thereafter, the resist pattern is removed.

**[0188]** Next, as shown in **FIG. 11C**, **a** getter material layer **22***a* of Ti is isotropically formed over the whole upper surface of the substrate by sputtering. The getter material layer **22***a* has a thickness of about 0.15  $\mu$ m. Sputtering is performed in a DC sputtering system by using Ti as a target while Ar gas is introduced. In order to improve the step coverage of the getter material layer **22***a*, it is preferable to form the getter material layer **22***a* by long throw sputtering, ionic beam sputtering, CVD, or plating. The getter material layer **22***a* also functions as a second gate electrode film.

**[0189]** Next, the getter material layer 22*a* is anisotropically etched (etched back). As shown in **FIG. 11D**, this etch-back process forms a getter film 22*b* only on the side wall of the gate electrode 25*a*. The getter film 22*b* also functions as a side spacer. The etch-back process is performed by anisotropic dry-etching. For example, it is performed in a magnetron RIE system by using Cl<sub>2</sub> as etching gas at a reaction chamber pressure of 125 mTorr (about  $125 \times 10^{-3} \times 133.3$  Pa).

**[0190]** Next, as shown in **FIG. 11E**, **a** first sacrificial film (insulating film) **21** of a silicon oxide film is deposited over the whole upper surface of the substrate by atmospheric pressure CVD. The first sacrificial film **21** has a thickness of about 0.1  $\mu$ m. For example, the atmospheric pressure CVD is performed by using O<sub>3</sub> and TEOS as source gas at a substrate temperature of 400° C.

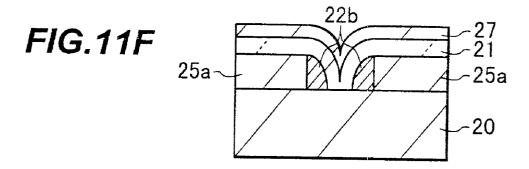

**[0191]** Next, as shown in **FIG. 11F, a** first emitter electrode 27 of  $\text{TiN}_{x}$  is deposited on the first sacrificial film 21 by reactive sputtering. The first emitter electrode 27 has a thickness of about 0.05  $\mu$ m. The reactive sputtering is performed in a DC sputtering system by using Ti as a target while N<sub>2</sub>+Ar gas is introduced.

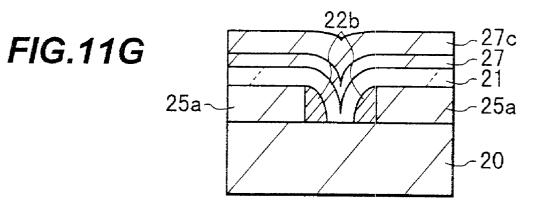

**[0192]** Next, as shown in **FIG. 11G, a** blanket film 27*c* of W (tungsten) is isotropically deposited on the first emitter electrode 27 by CVD. The blanket film 27*c* has a thickness of about 0.2  $\mu$ m and functions also as a second emitter electrode. For example, CVD is performed under the conditions of source gas of WF<sub>6</sub>+H<sub>2</sub>+N<sub>2</sub>+Ar, a pressure of 80 Torr (about 80×133.3 Pa) and a temperature of 450° C.

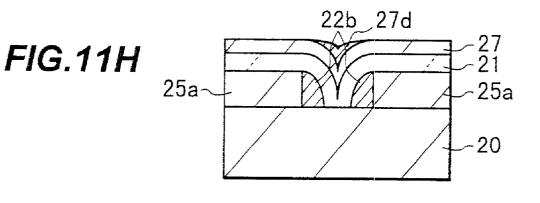

**[0193]** Next, as shown in **FIG. 11H**, the second emitter electrode 27*c* is anisotropically etched (etched back) about 0.2  $\mu$ m thick to leave a second emitter electrode 27*d* only in a recess of the first emitter electrode 27. A flat surface of the first emitter electrode 27 is exposed. This etch-back is performed by anisotropic dry-etching. For example, it is performed in a magnetron RIE system by using SF<sub>6</sub>+Ar+He as etching gas at a reaction chamber pressure of 280 mTorr (about 280×10<sup>-3</sup>×133.3 Pa).

[0194] Next, as shown in FIG. 111, the whole of the substrate 20 and part of the first sacrificial film 21 are etched

and removed to leave a peripheral first sacrificial film 21b and expose the tip of the first emitter electrode 27. The substrate 20 made of Si is etched by using HF+HNO<sub>3</sub>+ CH<sub>3</sub>COOH. The first sacrificial film 21 of a silicon oxide film is etched by HF+NH<sub>4</sub>F.

[0195] With the above processes, a field emission element of a two-electrode structure having the emitter electrodes 27 and 27d and gate electrode 25a is completed. Since the getter film 22b of Ti is a conductive film, it functions as a gate electrode together with the gate electrode 25a. This field emission element has the emitter electrodes 27 and 27d and gate electrodes 25a and 22b. The getter film 22b is formed on the side wall of the gate electrode 25a and surrounds the tip of the first emitter electrode 27.

[0196] By heating the getter film 22 by light application or the like, the getter film 22b can be activated. The getter film 22b adsorbs ambient molecules so that the vacuum degree in the flat panel display can be improved.

**[0197]** FIGS. 12A to 12I are schematic cross sectional views illustrating the manufacture steps of a field emission element according to a modification of the third embodiment of the invention.

**[0198]** As shown in **FIG. 12**A, on a substrate **20** of Si or the like, a getter material layer **20***c* is formed by sputtering. The getter material layer **20***c* has a thickness of  $0.1 \,\mu$ m, and functions also as a first gate electrode film. The sputtering is performed in a DC sputtering system by using Ti as a target while Ar gas is introduced. It is preferable to form a silicon oxide film or silicon nitride film between the substrate **20** and getter material layer **20***c* as an etching stopper layer.

**[0199]** Next, on the getter material layer **20***c*, a polysilicon layer doped with phosphorous or boron is formed about 0.2  $\mu$ m thick by sputtering. This polysilicon film corresponds to a gate electrode film. For example, the sputtering is performed in a DC sputtering system by using silicon doped with phosphorous or boron as a target while Ar gas is introduced.

**[0200]** Next, by using a resist pattern (not shown) as a mask, the polysilicon film doped with phosphorous or boron is etched to form a gate electrode 25a with a hole (gate hole) 23. The hole (gate hole) 23 is cylindrical and has a diameter of about 0.5  $\mu$ m and a depth of about 0.2  $\mu$ m. Thereafter, the resist pattern is removed.

**[0201]** Next, as shown in **FIG. 12B, a** first sacrificial film (insulating film) **21** of a silicon oxide film is deposited on the gate electrode **25***a* and getter film **20***c* to a thickness of 0.15  $\mu$ m by CVD. For example, this CVD is performed by using O<sub>3</sub> and TEOS as source gas at a substrate temperature of 400° C.

**[0202]** Next, as shown in **FIG. 12**C, the first sacrificial film **21** is anisotropically etched (etched back) to leave a first sacrificial film **21***a* only on the side wall of the gate electrode **25***a* as a side spacer. For example, this etch-back is performed in a magnetron RIE system by using CHF<sub>3</sub>+CO<sub>2</sub>+Ar as etching gas at a reaction chamber pressure of 50 mTorr (about  $50 \times 10^{-3} \times 133.3$  Pa).

[0203] Next, as shown in FIG. 12D, by using the gate electrode 25a and side spacer 21a as a mask, the getter material layer 20c is etched to form a getter film 20d under the gate electrode 25a and side spacer 21a. This etching is

**[0204]** Next, as shown in **FIG. 12E**, a second sacrificial film (insulating film) **24** is isotropically formed over the substrate to a thickness of about 0.1  $\mu$ m by atmospheric pressure CVD. This atmospheric pressure CVD is performed by using O<sub>3</sub> and TEOS as source gas at a substrate temperature of 400° C.

[0205] Next, as shown in FIG. 12F, a first emitter electrode 27 of  $\text{TiN}_{x}$  is deposited on the second sacrificial film 24 about 0.05  $\mu$ m thick by reactive sputtering. For example, this reactive sputtering is performed in a DC sputtering system by using Ti as a target while N<sub>2</sub>+Ar gas is introduced.

**[0206]** Next, as shown in **FIG. 12G, a** blanket film **27***c* of W (tungsten) is isotropically deposited on the first emitter electrode **27** about 0.2  $\mu$ m thick by CVD. For example, CVD is performed under the conditions of source gas of WF<sub>6</sub>+ H<sub>2</sub>+N<sub>2</sub>+Ar, a pressure of 80 Torr (about 80×133.3 Pa) and a temperature of 450° C. The blanket film **27***c* functions as a second emitter electrode.