(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7123996号**

**(P7123996)**

(45)発行日 令和4年8月23日(2022.8.23)

(24)登録日 令和4年8月15日(2022.8.15)

(51)国際特許分類

A 6 3 F 7/02 (2006.01)

F I

A 6 3 F

7/02

3 2 6 Z

請求項の数 1 (全66頁)

|          |                                  |          |                                             |

|----------|----------------------------------|----------|---------------------------------------------|

| (21)出願番号 | 特願2020-61261(P2020-61261)        | (73)特許権者 | 391010943<br>株式会社藤商事<br>大阪府大阪市中央区内本町一丁目1番4号 |

| (22)出願日  | 令和2年3月30日(2020.3.30)             |          |                                             |

| (65)公開番号 | 特開2021-159137(P2021-159137<br>A) | (74)代理人  | 110001645<br>特許業務法人谷藤特許事務所                  |

| (43)公開日  | 令和3年10月11日(2021.10.11)           | (72)発明者  | 成田 曜漢<br>大阪市中央区内本町一丁目1番4号 株式会社藤商事内          |

| 審査請求日    | 令和3年4月21日(2021.4.21)             | 審査官      | 阿部 知                                        |

最終頁に続く

(54)【発明の名称】 遊技機

**(57)【特許請求の範囲】****【請求項 1】**

複数の配線層と、それら複数の配線層を互いに導通させるための板厚方向の層間導通部とを有する基板を備え、

前記基板上に、C P U回路を内蔵したチップと、前記チップと接続されるR O Mと、前記チップ及び前記R O Mとは異なる所定電子部品とを配置した

遊技機において、

前記複数の配線層のうちの第1配線層に、前記チップが配置される第1配置領域と、前記R O Mが配置される第2配置領域とを設け、

前記チップは、所定情報を出力及び／又は入力可能な複数の第1端子を備え、

前記R O Mは、所定情報を入力及び／又は出力可能な複数の第2端子を備え、

前記所定電子部品は、所定情報を入力及び／又は出力可能な複数の第3端子を備え、

前記複数の第1端子の配列は、前記複数の第2端子の配列及び前記複数の第3端子の配列と夫々相違しており、

前記層間導通部のうち、前記第2配置領域内に配置される複数の所定層間導通部と前記複数の第1端子とを夫々接続する第1配線路群と、前記複数の所定層間導通部と前記複数の第2端子とを夫々接続する第2配線路群と、前記複数の所定層間導通部と前記複数の第3端子とを夫々接続する第3配線路群とを備え、

前記複数の所定層間導通部の配列を、前記複数の第3端子の配列と近似させ、

前記第2配線路群は、前記複数の所定層間導通部に対応する配列を前記第2配置領域内に

おいて前記第2端子に対応する配列に変換して当該第2端子に接続することを特徴とする遊技機。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、パチンコ機、スロットマシン等の遊技機に関するものである。

【背景技術】

【0002】

パチンコ機等の遊技機では、演出制御手段、払出制御手段、発射制御手段、それらの統括制御を行う主制御手段等の各種制御手段が、複数の基板に分散された形で搭載されている。各制御基板には、C P U回路を内蔵した複合チップ（L S I）、各種I C、R O M、コンデンサ、抵抗、コネクタ等の電子部品が搭載されるとともに、それらの電子部品を接続するための配線パターンが、例えば複数の配線層に跨がって形成されている（特許文献1）。

10

【先行技術文献】

【特許文献】

【0003】

【文献】特開2019-187989号公報

【発明の概要】

【発明が解決しようとする課題】

20

【0004】

近年の遊技機は、可動体や画像表示手段などの各種演出手段を多数搭載し、しかもそれらが大型化する傾向にあるため、限られたスペースに多数の部品を効率よく配置する必要がある。遊技機本体の後側等に配置される各種基板も例外ではなく、基板の大きさを最小化すべく、複雑な配線パターンを効率的に配置することが求められている。

本発明は上記事情に鑑みてなされたものであり、基板上の配線パターンをより効率的に配置することが可能な遊技機を提供することを目的とする。

【課題を解決するための手段】

【0005】

本発明は、複数の配線層と、それら複数の配線層を互いに導通させるための板厚方向の層間導通部とを有する基板を備え、前記基板上に、C P U回路を内蔵したチップと、前記チップと接続されるR O Mと、前記チップ及び前記R O Mとは異なる所定電子部品とを配置した遊技機において、前記複数の配線層のうちの第1配線層に、前記チップが配置される第1配置領域と、前記R O Mが配置される第2配置領域とを設け、前記チップは、所定情報を出力及び／又は入力可能な複数の第1端子を備え、前記R O Mは、所定情報を入力及び／又は出力可能な複数の第2端子を備え、前記所定電子部品は、所定情報を入力及び／又は出力可能な複数の第3端子を備え、前記複数の第1端子の配列は、前記複数の第2端子の配列及び前記複数の第3端子の配列と夫々相違しており、前記層間導通部のうち、前記第2配置領域内に配置される複数の所定層間導通部と前記複数の第1端子とを夫々接続する第1配線路群と、前記複数の所定層間導通部と前記複数の第2端子とを夫々接続する第2配線路群と、前記複数の所定層間導通部と前記複数の第3端子とを夫々接続する第3配線路群とを備え、前記複数の所定層間導通部の配列を、前記複数の第3端子の配列と近似させ、前記第2配線路群は、前記複数の所定層間導通部に対応する配列を前記第2配置領域内において前記第2端子に対応する配列に変換して当該第2端子に接続するものである。

30

【発明の効果】

【0006】

本発明によれば、基板上の配線パターンをより効率的に配置することが可能となる。

40

【図面の簡単な説明】

【0007】

50

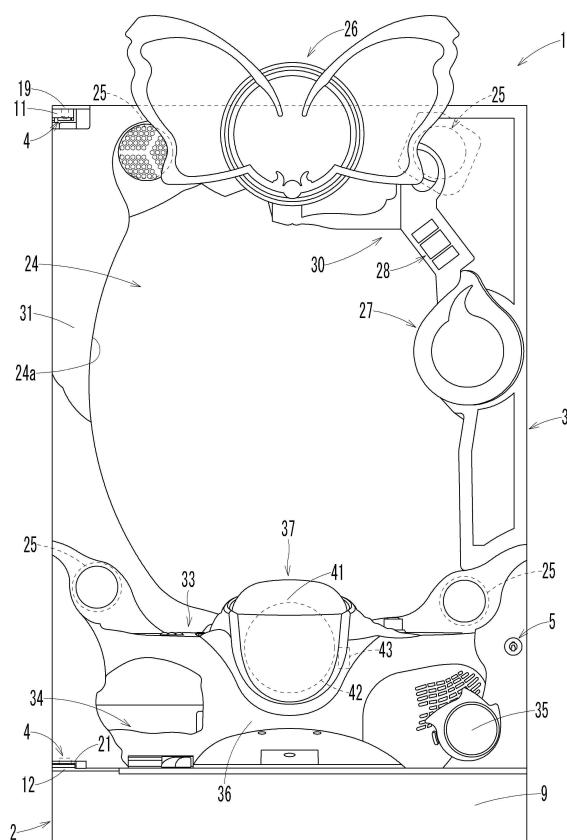

【図 1】本発明の一実施形態に係るパチンコ機の全体正面図である。

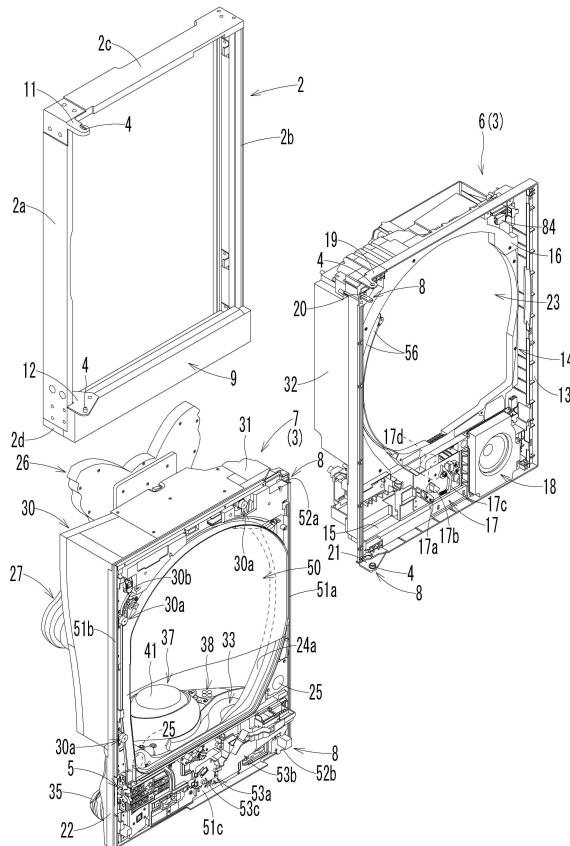

【図 2】同パチンコ機の分解斜視図である。

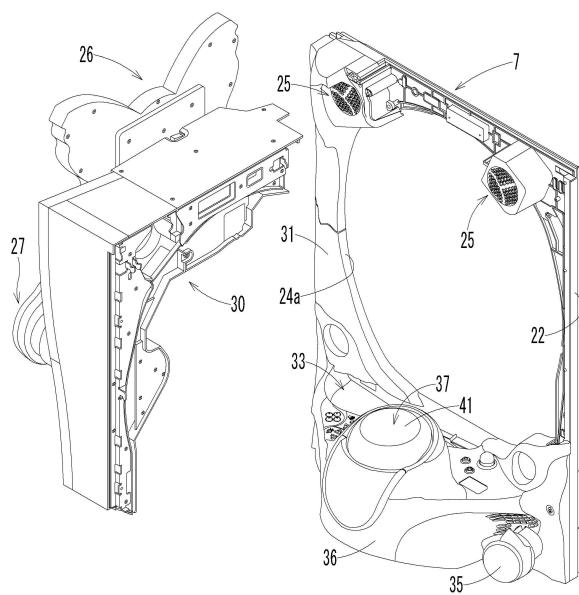

【図 3】同パチンコ機のガラス扉の分解斜視図である。

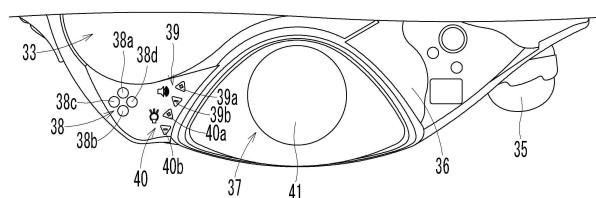

【図 4】同パチンコ機の操作演出手段、十字操作ボタン、音量調整ボタン、光量調整ボタン等を示す要部平面図である。

【図 5】同パチンコ機の遊技盤の正面図である。

【図 6】同パチンコ機の遊技情報表示手段の正面図である。

【図 7】同パチンコ機の背面図である。

【図 8】同パチンコ機の演出基板ケース及び演出制御部の分解斜視図である。

【図 9】同パチンコ機の演出基板ケース及び演出制御部の平面断面図である。

10

【図 10】同パチンコ機の全体回路構成を示すブロック図である。

【図 11】同パチンコ機の液晶制御基板に搭載される複合チップについて、関連する回路素子も含めて図示した回路ブロック図である。

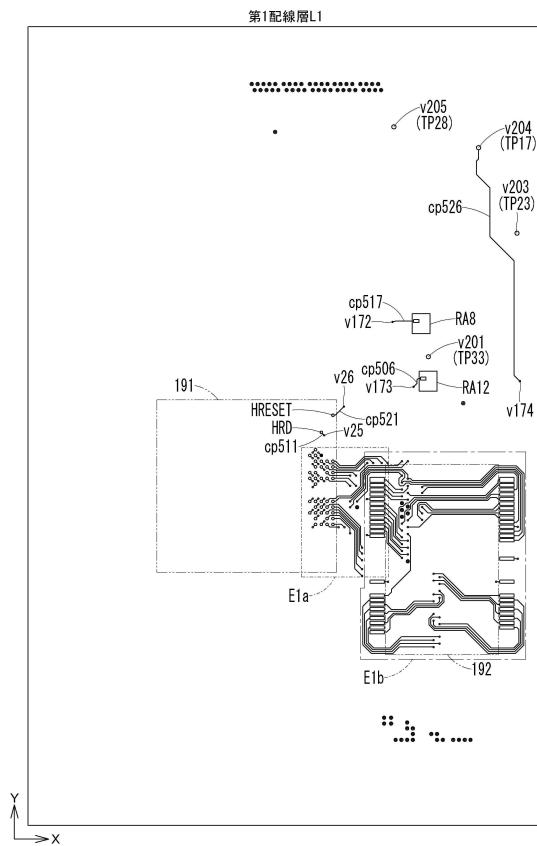

【図 12】同パチンコ機の液晶制御基板における第1配線層の配線パターンを示す図である。

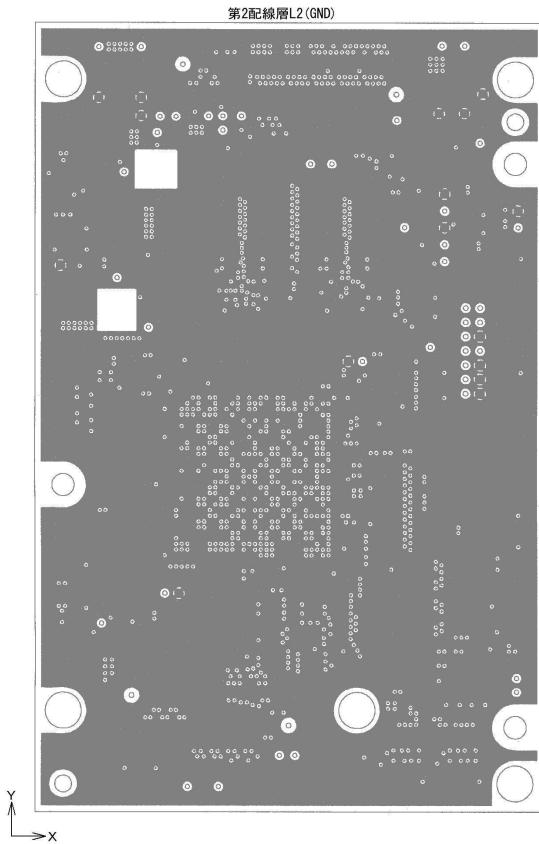

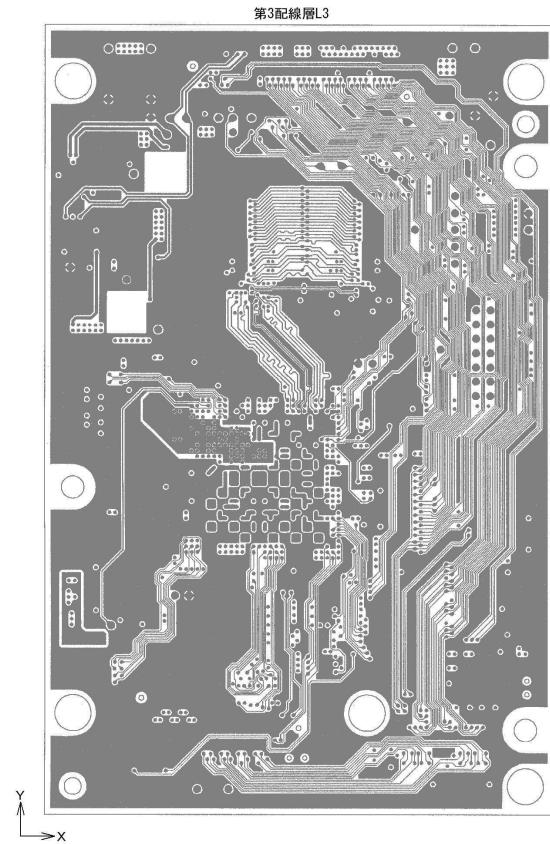

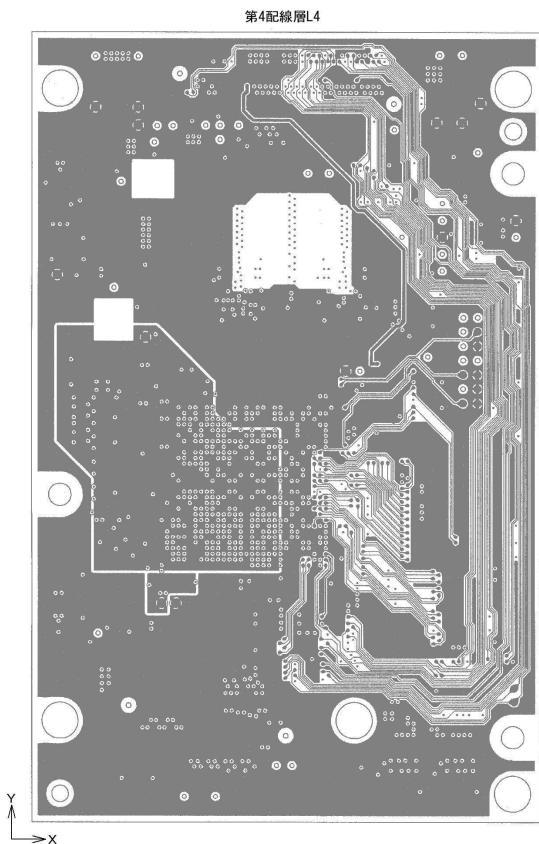

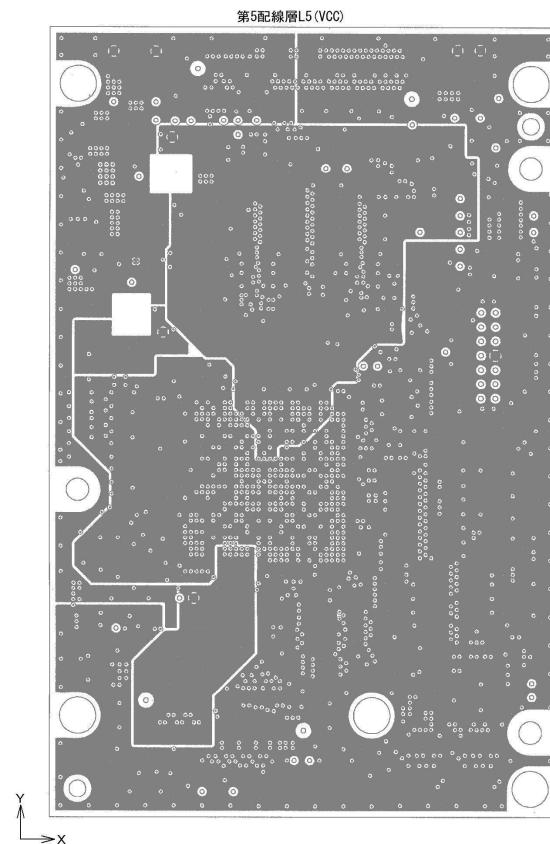

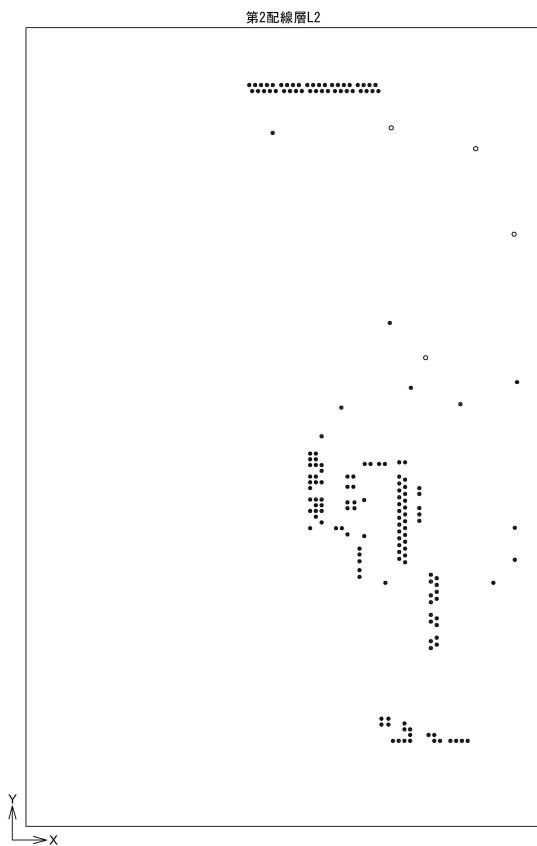

【図 13】同パチンコ機の液晶制御基板における第2配線層の配線パターンを示す図である。

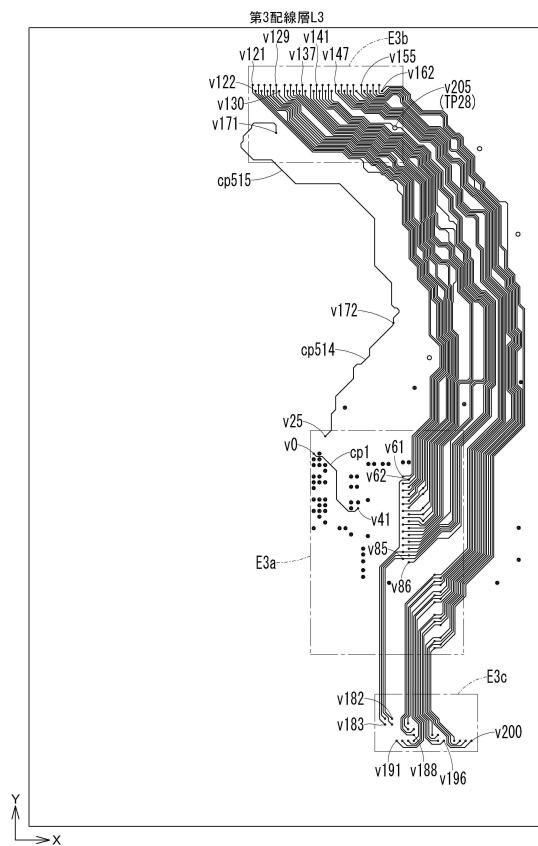

【図 14】同パチンコ機の液晶制御基板における第3配線層の配線パターンを示す図である。

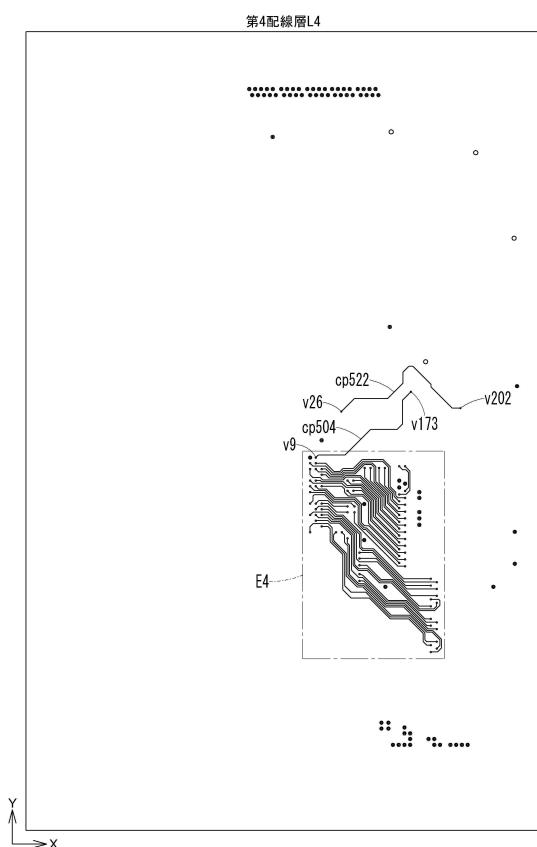

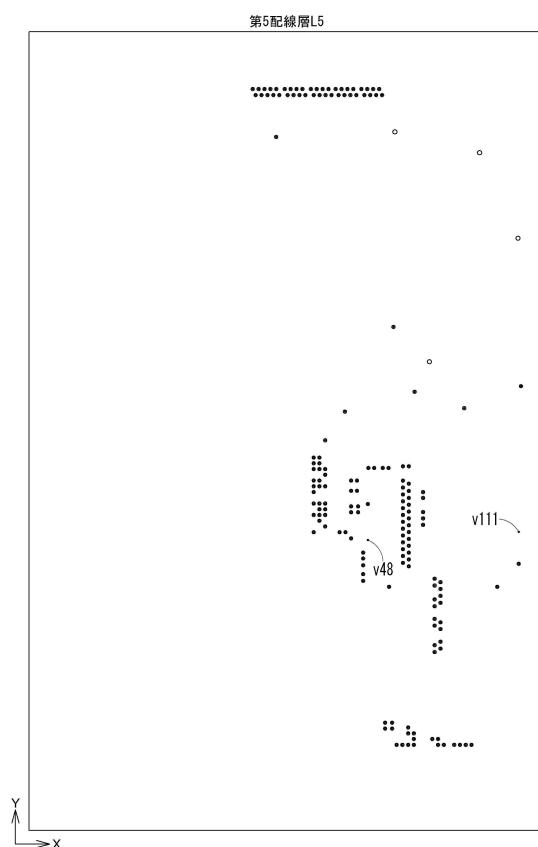

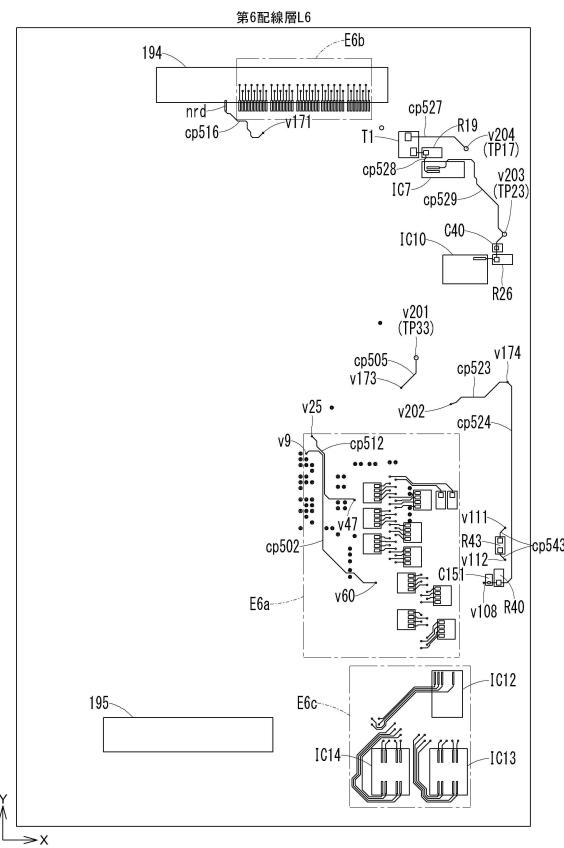

【図 15】同パチンコ機の液晶制御基板における第4配線層の配線パターンを示す図である。

20

【図 16】同パチンコ機の液晶制御基板における第5配線層の配線パターンを示す図である。

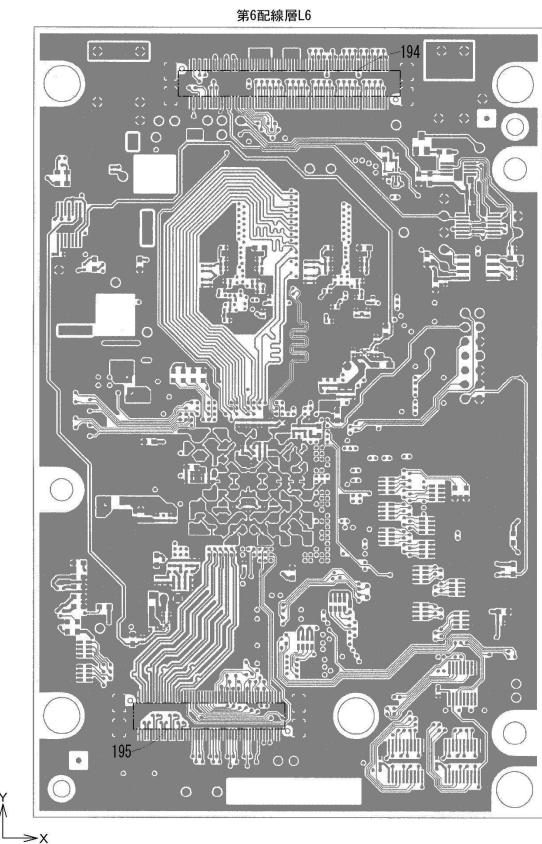

【図 17】同パチンコ機の液晶制御基板における第6配線層の配線パターンを示す図である。

【図 18】同パチンコ機の液晶制御基板に配置された複合チップの端子情報を示す図である。

【図 19】同パチンコ機の液晶制御基板に配置された制御ROMの端子情報を示す図である。

【図 20】同パチンコ機の液晶制御基板における第1配線層から配線路P1～P47のみを抽出した図である。

30

【図 21】同パチンコ機の液晶制御基板における第2配線層から配線路P1～P47のみを抽出した図である。

【図 22】同パチンコ機の液晶制御基板における第3配線層から配線路P1～P47のみを抽出した図である。

【図 23】同パチンコ機の液晶制御基板における第4配線層から配線路P1～P47のみを抽出した図である。

【図 24】同パチンコ機の液晶制御基板における第5配線層から配線路P1～P47のみを抽出した図である。

【図 25】同パチンコ機の液晶制御基板における第6配線層から配線路P1～P47のみを抽出した図である。

40

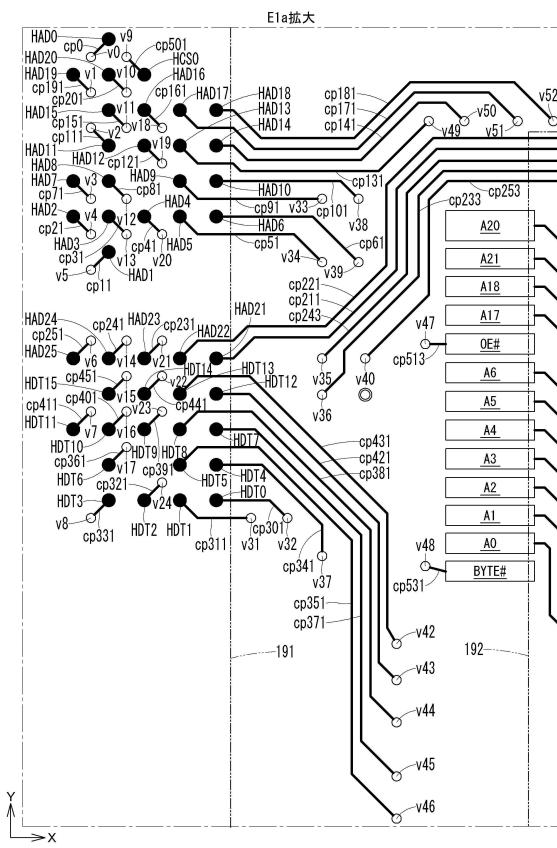

【図 26】図20における領域E1aの拡大図である。

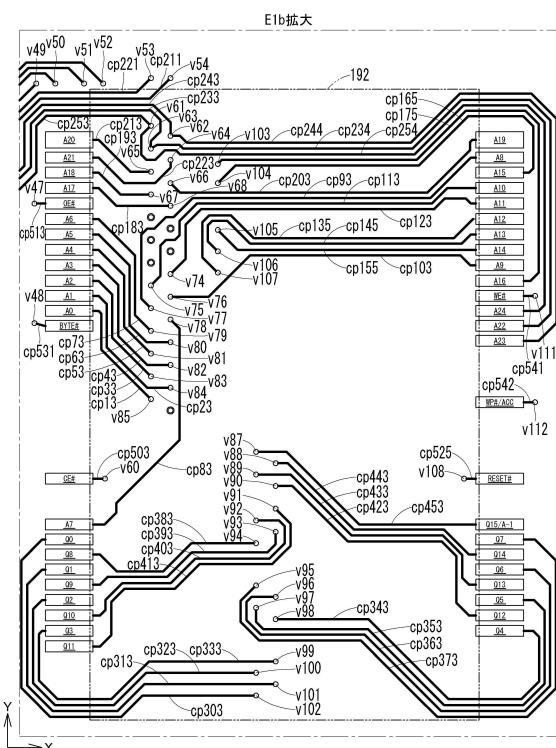

【図 27】図20における領域E1bの拡大図である。

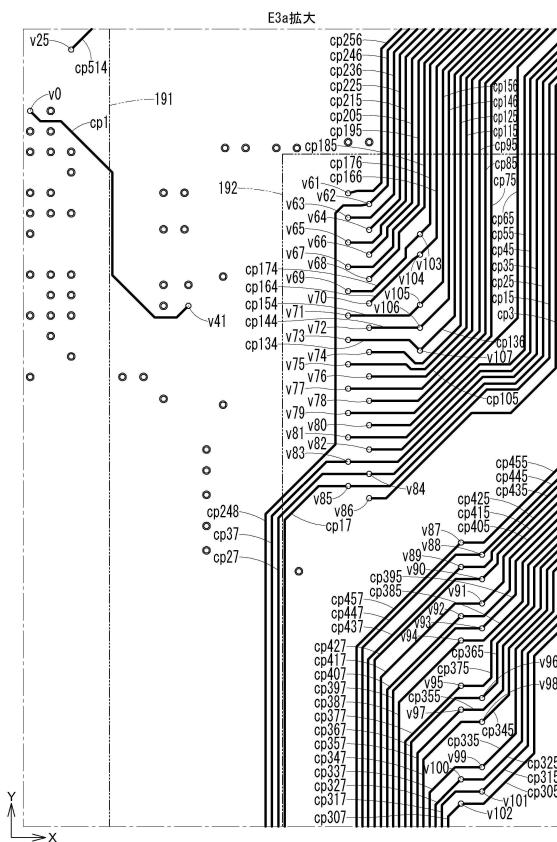

【図 28】図22における領域E3aの拡大図である。

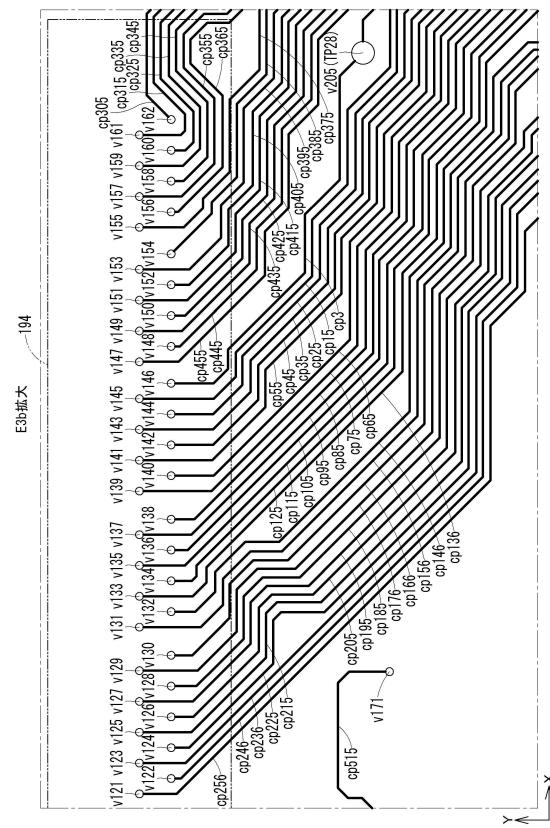

【図 29】図22における領域E3bの拡大図である。

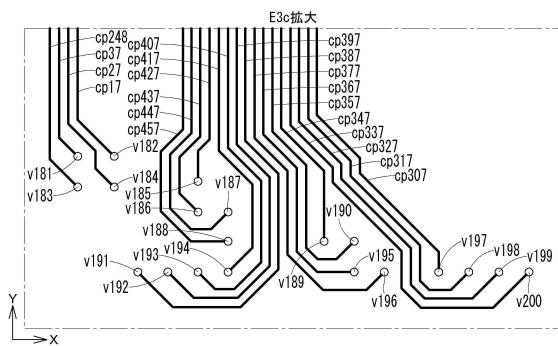

【図 30】図22における領域E3cの拡大図である。

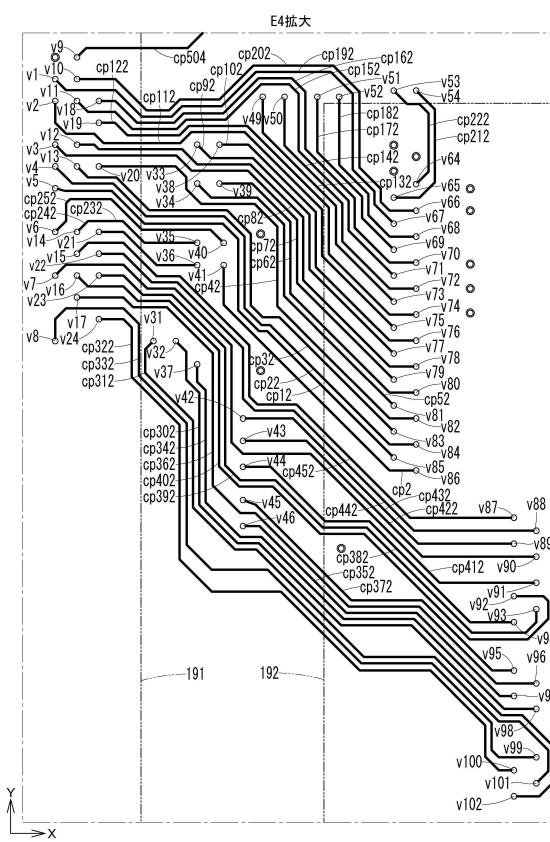

【図 31】図23における領域E4の拡大図である。

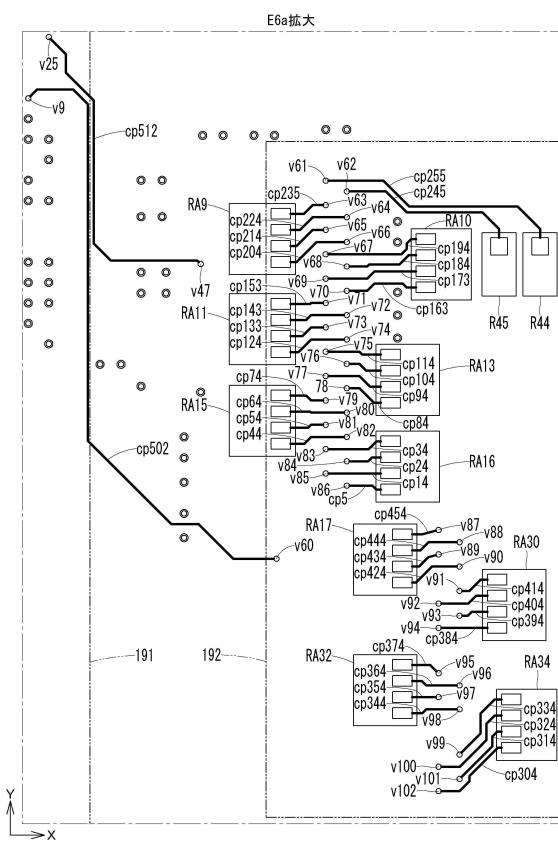

【図 32】図25における領域E6aの拡大図である。

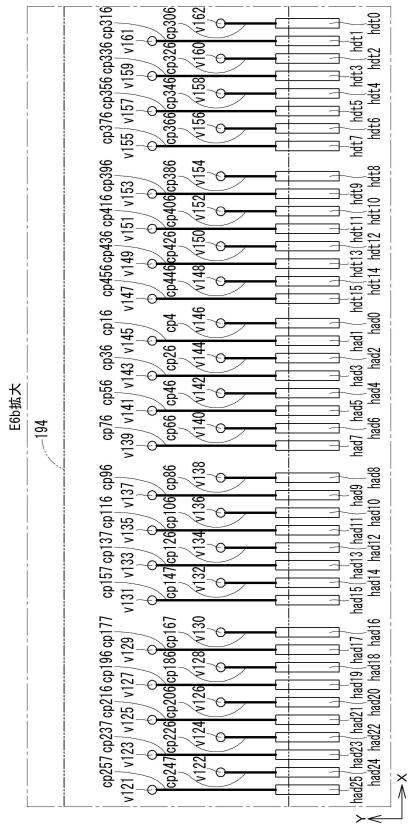

【図 33】図25における領域E6bの拡大図である。

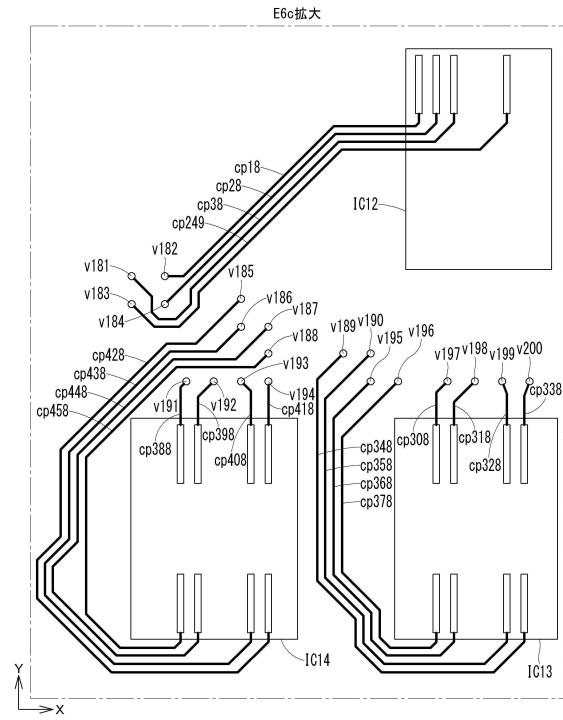

【図 34】図25における領域E6cの拡大図である。

50

【図35】本発明の一実施形態に係るパチンコ機の液晶制御基板における配線路P1～P8の配線経路を模式的に示す図である。

【図36】同パチンコ機の液晶制御基板における配線路P9～P17の配線経路を模式的に示す図である。

【図37】同パチンコ機の液晶制御基板における配線路P18～P26の配線経路を模式的に示す図である。

【図38】同パチンコ機の液晶制御基板における配線路P27～P34の配線経路を模式的に示す図である。

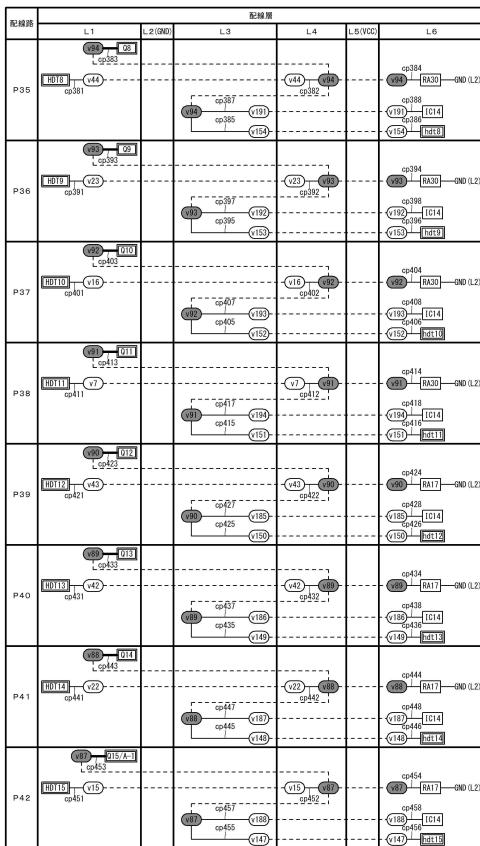

【図39】同パチンコ機の液晶制御基板における配線路P35～P42の配線経路を模式的に示す図である。

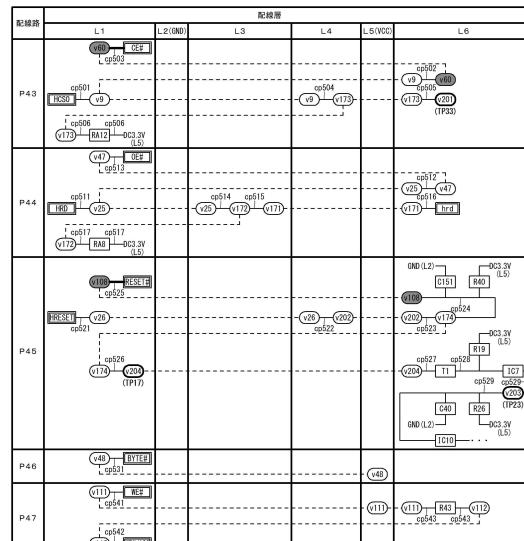

【図40】同パチンコ機の液晶制御基板における配線路P43～P47の配線経路を模式的に示す図である。

【図41】同パチンコ機の液晶制御基板におけるデコード回路の回路図である。

【図42】同パチンコ機の液晶制御基板におけるリセット回路の回路図である。

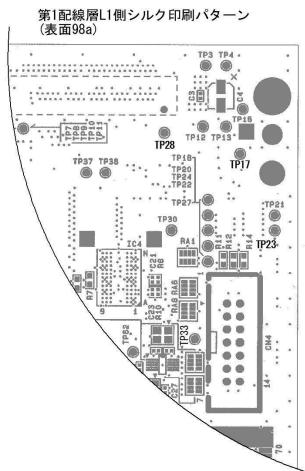

【図43】同パチンコ機の液晶制御基板における第1配線層側のシルク印刷パターンを示す図である。

#### 【発明を実施するための最良の形態】

##### 【0008】

以下、発明の実施形態を図面に基づいて詳述する。図1～図43は本発明をパチンコ機に採用した一実施形態を例示している。図1及び図2において、遊技機本体1は、外枠2と、この外枠2の前側に配置された前枠3とを備えている。前枠3は、左右方向一端側、例えば左端側に配置された上下方向の第1ヒンジ4を介して外枠2を開閉自在及び着脱自在に枢着されており、左右方向における第1ヒンジ4と反対側、例えば右端側に設けられた施錠手段5によって外枠2に対して閉状態で施錠可能となっている。

##### 【0009】

前枠3は、内枠6と、その内枠6の前側に配置された前扉7とを備えている。前扉7は、左右方向一端側、例えば左端側に配置された上下方向の第2ヒンジ8を介して内枠6を開閉自在及び着脱自在に枢着されており、施錠手段5によって内枠6に対して閉状態で施錠可能となっている。

##### 【0010】

外枠2は、図2に示すように左右一対の縦枠材2a, 2bと上下一対の横枠材2c, 2dとで矩形状に形成されている。外枠2の前側下部には、例えば合成樹脂製の前カバー部材9が、下横枠材2dの前縁に沿って左右の縦枠材2a, 2bの前側下部を連結するように装着されている。前カバー部材9は、左右の縦枠材2a, 2bよりも前側に突出しており、その上側に内枠6が配置されている。また外枠2には、第1ヒンジ4を構成する外枠上ヒンジ金具11が例えば左上部に、同じく外枠下ヒンジ金具12が左下部における前カバー部材9の上側に夫々配置されている。

##### 【0011】

内枠6は合成樹脂製で、前カバー部材9の上側で外枠2の前縁側に略当接可能な矩形状の枠部13と、この枠部13内の上部側に設けられた遊技盤装着部14と、枠部13内の下部側に設けられた下部装着部15とを例えば一体に備えている。遊技盤装着部14には、遊技盤16が例えば前側から着脱自在に装着され、下部装着部15には、その前側に発射手段17、下部スピーカ18等が配置されている。また内枠6には、第1ヒンジ4を構成する本体枠上ヒンジ金具19と第2ヒンジ8を構成する本体枠上ヒンジ金具20とが例えば左上部に、第1, 第2ヒンジ4, 8を構成する本体枠下ヒンジ金具21が例えば左下部に夫々配置されている。

##### 【0012】

前扉7は、内枠6の前面側に対応する矩形状に形成された樹脂製の扉ベース22を備えている。この扉ベース22には、遊技盤16に形成された遊技領域23の前側に対応してガラス窓24の窓孔24aが形成されると共に、例えば窓孔24aの周囲に複数（ここで

は4つ)の上部スピーカ25、枠第1可動体26、枠第2可動体27、送風手段28等の各種演出手段が配置されている。

【0013】

扉ベース22の上部前側には、窓孔24aの外周の少なくとも一部、例えば窓孔24aの上側と右側とに対応する正面視逆L字型の部分にサイドユニット30が装着され、その他の一部、例えば窓孔24aの左側には上装飾カバー31が装着されている。サイドユニット30内や上装飾カバー31内には、演出用の電飾を構成する多数のLEDが配置されている。サイドユニット30は、図2、図3等に示すように、前枠3を開いた状態で、特殊な工具を使用することなく、前枠3の裏側の固定ネジ30a、固定レバー30b等を操作することにより容易に着脱が可能となっている。通常、前枠3は複数の機種で共通に用いられ、機種毎に異なる遊技盤16をこの前枠3に装着することでその機種に特有の遊技性やデザインを実現しているが、本パチンコ機では、前枠3の前側の一部を、他の部品に比べて容易に着脱可能なサイドユニット30とし、このサイドユニット30に、遊技盤16と一体感のあるデザインや特有の機能を持たせることにより、前枠3の大部分を共通化しつつも、機種毎のデザインや機能の自由度を高めることを可能としている。

10

【0014】

本実施形態のサイドユニット30には、電飾用のLEDの他、枠第1可動体26、枠第2可動体27、送風手段28等が搭載されている。枠第1可動体26は、図外の駆動手段の駆動により略前後方向へのスライド移動が可能となっている。枠第2可動体27は、図外の駆動手段の駆動により略前後方向へのスライド移動が可能であると共に、遊技者による押し込み操作が可能となっている。送風手段28は、例えば遊技者が枠第2可動体27を操作するタイミングで、遊技者の手に向けて風を送ることが可能となっている。

20

【0015】

扉ベース22の下部前側には、内枠6の後側に配置された払出手段32から払い出された遊技球を貯留して発射手段17に供給する上皿33、その上皿33が満杯のときの余剰球等を貯留する下皿34、発射手段17を作動させるために操作する発射ハンドル35等が配置され、更に上皿33、下皿34等を前側から略覆う下装飾カバー36が装着されている。下装飾カバー36は、例えば前向きの膨出状に形成されており、例えばその上部側に、操作演出手段37、十字操作ボタン38、音量調整ボタン39、光量調整ボタン40等の各種操作手段が設けられている(図4)。

30

【0016】

操作演出手段37は、図柄変動中の予告演出、その他の演出に用いられるもので、遊技者が押下操作可能な上下動式の演出ボタン41、その演出ボタン41の内部に配置された枠第3可動体42等を備えている。枠第3可動体42は、例えば横軸廻りに回転可能な略球状の回転体により構成されており、回転駆動モータ43により正逆両方向に回転可能となっている。

【0017】

十字操作ボタン38は、図4に示すように上下左右の4つの操作ボタン38a~38dを備え、遊技者がメニュー項目を選択する場合など、上下左右へのカーソル移動等の操作が必要な場面で使用される。音量調整ボタン39は、遊技者による音量調整に用いられるもので、図4に示すように、遊技者がスピーカからの音量を上げたいときに操作するプラスボタン39aと、同じく音量を下げたいときに操作するマイナスボタン39bとを備えている。光量調整ボタン40は、遊技者による光量調整に用いられるもので、図4に示すように遊技者がLED電飾の光量を上げたいときに操作するプラスボタン40aと、同じく光量を下げたいときに操作するマイナスボタン40bとを備えている。なお、本実施形態では音量調整専用の音量調整ボタン39と光量調整専用の光量調整ボタン40とを設けたが、それらを設けることなく、十字操作ボタン38等の汎用操作手段を音量調整用、光量調整用にも使用するようにしてもよい。

40

【0018】

扉ベース22の背面側には、図2に示すように窓孔24aを後側から略塞ぐガラスユニ

50

ット 5 0 が着脱自在に装着されると共に、第 1 , 第 2 ヒンジ 4 , 8 側の縁部に沿って配置される上下方向のヒンジ端側補強板金 5 1 a と、開閉端側の縁部に沿って配置される上下方向の開閉端側補強板金 5 1 b と、窓孔 2 4 a の下側に配置される左右方向の下部補強板金 5 1 c とがねじ止め等により着脱自在に固定されている。また扉ベース 2 2 には、第 2 ヒンジ 8 を構成するガラス扉上ヒンジ金具 5 2 a が例えれば左上部に、同じくガラス扉下ヒンジ金具 5 2 b が例えれば左下部に夫々配置されている。

【 0 0 1 9 】

また、例えれば下部補強板金 5 1 c の背面側には、球送りユニット 5 3 a 、下皿案内ユニット 5 3 b 等が装着されている。球送りユニット 5 3 a は、上皿 3 3 内の遊技球を発射手段 1 7 に供給するためのもので、内枠 6 側に配置された発射手段 1 7 の前側に対応して配置されており、発射手段 1 7 の発射動作と同期して球送りソレノイド 5 3 c を作動させることにより、上皿 3 3 内の遊技球を 1 個ずつ発射手段 1 7 の発射レール 1 7 a 上に供給するようになっている。

10

【 0 0 2 0 】

なお発射手段 1 7 は、正面視で左上がりの傾斜状に配置された発射レール 1 7 a と、球送りユニット 5 3 a により発射レール 1 7 a 上に供給された遊技球を発射待機位置で支持する発射球ストップ 1 7 b と、発射レール 1 7 a 上の発射待機位置に対応して配置され且つ前後方向の駆動軸廻りに揺動可能な打撃槌 1 7 c と、打撃槌 1 7 c を揺動駆動するロータリソレノイド等の発射駆動手段 1 7 d とを備え、発射ハンドル 3 5 が回転操作されたときに、その操作量に応じた発射強度で発射駆動手段 1 7 d により打撃槌 1 7 c を打撃方向（時計方向）に連続的に駆動するようになっている。

20

【 0 0 2 1 】

下皿案内ユニット 5 3 b は、上皿 3 3 が満杯となったときの余剰球、及び発射手段 1 7 により発射されたにも拘わらず遊技領域 2 3 に達することなく戻ってきたファール球を下皿 3 4 に案内するためのもので、例えれば球送りユニット 5 3 a に隣接してその第 1 , 第 2 ヒンジ 4 , 8 側に配置されている。

【 0 0 2 2 】

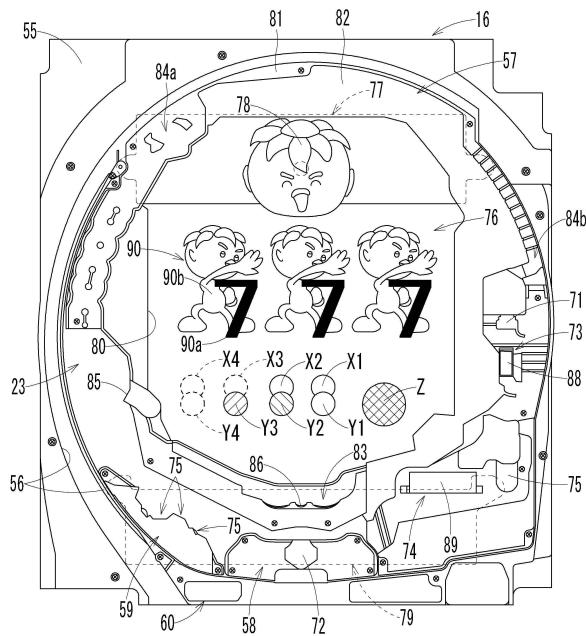

遊技盤 1 6 は、図 5 に示すようにベニヤ板、ポリカーボネート板等よりなるベース板 5 5 を備え、そのベース板 5 5 の前側に、発射手段 1 7 から発射された遊技球を案内するガイドレール 5 6 が環状に配置されると共に、そのガイドレール 5 6 の内側の遊技領域 2 3 に、中央表示枠ユニット 5 7 、始動入賞ユニット 5 8 、普通入賞ユニット 5 9 等のユニット部品の他、多数の遊技釘（図示省略）が配置され、また遊技領域 2 3 の外側の例えれば下部側には遊技情報表示手段 6 0 が配置されている。もちろん、遊技情報表示手段 6 0 は遊技領域 2 3 内に配置してもよい。

30

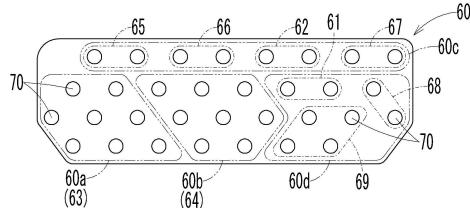

【 0 0 2 3 】

遊技情報表示手段 6 0 は、図 6 に示すように、例えば 8 個の L E D 7 0 で構成される L E D グループを 4 つ備えており、それら計 3 2 個の L E D 7 0 が普通図柄表示手段 6 1 、普通保留個数表示手段 6 2 、第 1 特別図柄表示手段 6 3 、第 2 特別図柄表示手段 6 4 、第 1 特別保留個数表示手段 6 5 、第 2 特別保留個数表示手段 6 6 、変動短縮報知手段 6 7 、右打ち報知手段 6 8 及びラウンド数報知手段 6 9 に所定個数ずつ割り当てられている。即ち、第 1 , 第 2 L E D グループ 6 0 a , 6 0 b に属する各 8 個の L E D 7 0 は夫々第 1 , 第 2 特別図柄表示手段 6 3 , 6 4 を構成し、第 3 L E D グループ 6 0 c に属する 8 個の L E D 7 0 は、2 個ずつに分けられて夫々第 1 特別保留個数表示手段 6 5 、第 2 特別保留個数表示手段 6 6 、普通保留個数表示手段 6 2 、変動短縮報知手段 6 7 を構成し、第 4 L E D グループ 6 0 d に属する 8 個の L E D 7 0 は、そのうちの 2 個が普通図柄表示手段 6 1 を、他の 2 個が右打ち報知手段 6 8 を、残りの 4 個がラウンド数報知手段 6 9 を夫々構成している。

40

【 0 0 2 4 】

遊技盤 1 6 の複数のユニット部品 5 7 ~ 5 9 上には、普通図柄始動手段 7 1 、第 1 特別図柄始動手段 7 2 、第 2 特別図柄始動手段 7 3 、大入賞手段 7 4 、複数の普通入賞手段 7

50

5等が設けられている。またベース板55の後側には、液晶表示ユニット(画像表示手段)76の他、盤第1可動体77、盤第2可動体78、盤第3可動体79等の可動体が配置されている。

【0025】

中央表示枠ユニット57は、液晶表示ユニット76及び可動体77～79の表示枠を構成するもので、後側の液晶表示ユニット76に対応する開口窓80が略中央に形成されており、ベース板55に形成された前後方向貫通状の装着孔(図示省略)に対して前側から着脱自在に装着されている。この中央表示枠ユニット57は、図5に示すように、ベース板55の前面に沿って装着孔の外側に配置され且つその前側を遊技球が通過可能な前面装着板81と、液晶表示ユニット76の前側における左右両側から上部側にわたる正面視略門形状に配置され且つ前面装着板81の内周側で前向きに突設された装飾枠82と、その装飾枠82の左右の下端部間に配置されるステージ83とを備えている。発射手段17により発射され、遊技領域23の上部側に進入した遊技球は、装飾枠82の頂部で左右に振り分けられ、中央表示枠ユニット57の左側の左流下経路84aと右側の右流下経路84bとの何れかを流下する。

【0026】

中央表示枠ユニット57には、左流下経路84a側と右流下経路84b側との少なくとも一方側、例えば左流下経路84a側に、遊技球が流入可能なワープ入口85が設けられている。左流下経路84aを流下中にワープ入口85に流入した遊技球は、ステージ83上で左右方向に自由に転動した後、遊技領域23の左右方向中央に対応して設けられた中央落下部86とそれ以外の部分との何れかから前側に落下する。

【0027】

盤第1可動体77及び盤第3可動体79は、何れも液晶表示ユニット76の前側に横長状に配置され、その左右両端側が開口窓80の外側で上下方向移動可能に支持されており、図外の昇降駆動手段により個別に昇降移動可能となっている。盤第2可動体78は、キャラクタ等の所定形状に形成された立体造形物で、盤第1可動体77の前側に配置されており、盤第1可動体77と一体的に昇降移動可能であると共に、図外の回転駆動手段の駆動により、盤第1可動体77に対して前後方向の中心軸廻りに回転動作可能となっている。

【0028】

始動入賞ユニット58は、図5に示すように中央表示枠ユニット57の下側にガイドレール56に沿って配置され、ベース板55に対して前側から着脱自在に装着されている。普通入賞ユニット59は、図5に示すように中央表示枠ユニット57の下側で始動入賞ユニット58の左側にガイドレール56に沿って配置され、ベース板55に対して前側から着脱自在に装着されている。

【0029】

普通図柄始動手段71は、普通図柄表示手段61による普通図柄の変動表示を開始させるためのもので、遊技球が通過可能な通過ゲート等により構成され、遊技球の通過を検出する遊技球検出スイッチ(図示省略)を備えている。この普通図柄始動手段71は、図5に示すように例えば中央表示枠ユニット57の右部における前面装着板81の前側に設けられており、右流下経路84bを流下する遊技球が通過可能となっている。

【0030】

普通図柄表示手段61は、普通図柄を変動表示するためのもので、図6に示すように遊技情報表示手段60における所定個数(ここでは2個)のLED70で構成されており、普通図柄始動手段71が遊技球を検出することに基づいて、普通図柄を構成するそれら2個のLED70が普通変動中発光パターンで発光した後、普通図柄始動手段71による遊技球検出時に取得された普通乱数情報に含まれる当り判定乱数值が予め定められた当り判定値と一致する場合には当り態様で、それ以外の場合にははずれ態様で変動を停止する。なお、普通図柄を構成する2個のLED70は、それらの発光態様(例えば点灯/消灯)の組み合わせにより一又は複数の当り態様と一又は複数のはずれ態様とを表示可能であり、また普通変動中発光パターンは、例えば特定の複数種類(ここでは2種類)の発光態様

を所定時間（例えば128ms）毎に切り替えるようになっている。

【0031】

また、普通図柄表示手段61の図柄変動中と普通利益状態中とを含む普通保留期間中に普通図柄始動手段71が遊技球を検出した場合には、それによって取得された普通乱数情報が予め定められた上限保留個数、例えば4個を限度として保留記憶され、普通保留期間が終了する毎に1個ずつ消化されて普通図柄の変動が行われる。普通乱数情報の記憶個数（普通保留個数）は、普通保留個数表示手段62等によって遊技者に報知される。普通保留個数表示手段62は、図6に示すように遊技情報表示手段60における所定個数（ここでは2個）のLED70で構成されており、それら2個のLED70の夫々の発光態様（例えば点灯／点滅／消灯）の組み合わせにより、0～4個の5種類の普通保留個数を表示可能となっている。

10

【0032】

第1特別図柄始動手段72は、第1特別図柄表示手段63による図柄変動を開始させるためのもので、開閉手段を有しない非開閉式入賞手段により構成され、入賞した遊技球を検出する遊技球検出スイッチ（図示省略）を備えている。この第1特別図柄始動手段72は、図5に示すように例えば始動入賞ユニット58に設けられ、ステージ83の中央落下部86に対応してその下側に上向き開口状に配置されており、左流下経路84a側のワープ入口85からステージ83を経て入賞するルートが存在すること等により、右流下経路84bを流下してきた遊技球よりも左流下経路84aを流下してきた遊技球の方が高い確率で入賞可能となっている。なお、この第1特別図柄始動手段72に遊技球が入賞すると、1入賞当たり所定個数の遊技球が賞球として払い出される。

20

【0033】

第2特別図柄始動手段73は、第2特別図柄表示手段64による図柄変動を開始させるためのもので、開閉部88の作動によって遊技球が入賞可能な開状態と入賞不可能（又は開状態よりも入賞困難）な閉状態とに変化可能な開閉式入賞手段により構成され、入賞した遊技球を検出する遊技球検出スイッチ（図示省略）と、開閉部88を開閉する電磁ソレノイド等の開閉駆動手段とを備えており、普通図柄表示手段61の変動後の停止図柄が当り態様となって普通利益状態が発生した場合に、開閉部88が所定時間閉状態から開状態に変化するようになっている。

30

【0034】

この第2特別図柄始動手段73は、図5に示すように例えば中央表示枠ユニット57の右部における前面装着板81上で且つ普通図柄始動手段71の下流側に配置されており、右流下経路84bを流下してきた遊技球が入賞可能となっている。なお、開閉部88は例えば下部側に設けられた左右方向の回転軸廻りに揺動可能であり、閉状態では前面装着板81と略面一となって遊技球が前側を通過可能となり、開状態では前面装着板81の前側で後ろ下がりの傾斜状となって遊技球を後向きに入賞させるようになっている。この第2特別図柄始動手段73に遊技球が入賞すると、1入賞当たり所定個数の遊技球が賞球として払い出される。

【0035】

第1特別図柄表示手段63は、図6に示すように遊技情報表示手段60における所定個数（ここでは8個）のLED70で構成されており、第1特別図柄始動手段72が遊技球を検出することを条件に、第1特別図柄を構成するそれら8個のLED70が特別変動中発光パターンで発光した後、第1特別図柄始動手段72による遊技球検出時に取得された第1特別乱数情報に含まれる大当たり判定乱数値が予め定められた大当たり判定値と一致する場合には第1大当たり態様で、それ以外の場合には第1はずれ態様で変動を停止するようになっている。第1特別図柄表示手段63の変動後の停止図柄が第1大当たり態様となった場合には第1特別利益状態が発生する。

40

【0036】

第2特別図柄表示手段64は、図6に示すように遊技情報表示手段60における所定個数（ここでは8個）のLED70で構成されており、第2特別図柄始動手段73が遊技球

50

を検出することを条件に、第2特別図柄を構成するそれら8個のLED70が特別変動中発光パターンで発光した後、第2特別図柄始動手段73による遊技球検出時に取得された第2特別乱数情報に含まれる大当たり判定乱数値が予め定められた大当たり判定値と一致する場合には第2大当たり態様で、それ以外の場合には第2はずれ態様で変動を停止するようになっている。第2特別図柄表示手段64の変動後の停止図柄が第2大当たり態様となった場合には第2特別利益状態が発生する。

#### 【0037】

第1、第2特別図柄表示手段63、64は、各8個のLED70の発光態様（例えば点灯／消灯）の組み合わせにより一又は複数の第1、第2大当たり態様と一又は複数の第1、第2はずれ態様とを表示可能であり、また特別変動中発光パターンは、特定の複数種類（ここでは2種類）の発光態様を所定時間（例えば128ms）毎に切り替えるようになっている。

10

#### 【0038】

また、第1特別図柄表示手段63の図柄変動中、第2特別図柄表示手段64の図柄変動中及び第1、第2特別利益状態中を含む特別保留期間中に第1、第2特別図柄始動手段72、73が遊技球を検出した場合には、それによって取得された第1、第2特別乱数情報が夫々予め定められた上限保留個数、例えば各4個を限度として保留記憶される。そして、特別保留期間が終了した時点で第2特別図柄側の保留記憶が1以上の場合にはその第2特別図柄の保留記憶を1個消化して第2特別図柄の変動を行い、第1特別図柄側の保留記憶のみが1以上の場合にはその第1特別図柄の保留記憶を1個消化して第1特別図柄の変動を行う。このように本実施形態では、第1特別図柄と第2特別図柄とが共に変動中になることはなく、また第1特別図柄側と第2特別図柄側との両方に保留記憶がある場合には、第2特別図柄の変動を優先的に行うようになっている。

20

#### 【0039】

なお、第1、第2特別乱数情報の記憶個数（第1、第2特別保留個数）は、第1、第2特別保留個数表示手段65、66、液晶表示ユニット76等によって遊技者に報知される。ここで、第1、第2特別保留個数表示手段65、66は、図6に示すように遊技情報表示手段60における所定個数（ここでは各2個）のLED70で構成され、それらの発光態様（例えば点灯／点滅／消灯）の組み合わせにより、0～4個の5種類の第1、第2特別保留個数を表示可能となっている。

30

#### 【0040】

大入賞手段74は、遊技球が入賞可能な開状態と入賞不可能な閉状態とに切り換え可能な開閉板89を備えた開閉式入賞手段で、図5に示すように例えば中央表示枠ユニット57に設けられ、入賞した遊技球を検出する遊技球検出スイッチ（図示省略）と、開閉板89を開閉する電磁ソレノイド等の開閉駆動手段とを備えており、第2特別図柄始動手段73の下流側で且つ第1特別図柄始動手段72の上流側に配置されていることにより、左流下経路84aを流下してきた遊技球よりも右流下経路84bを流下してきた遊技球の方が高い確率で入賞可能となっている。この大入賞手段74は、第1、第2特別図柄表示手段63、64の第1、第2特別図柄が変動後に第1、第2大当たり態様（特定態様）で停止した場合に発生する第1、第2特別利益状態において、開閉板89が一又は複数種類の開放パターンの何れかに従って前側に開放して、その上に落下してきた遊技球を内部へと入賞させるようになっている。この大入賞手段74に遊技球が入賞すると、1入賞当たり所定個数の遊技球が賞球として払い出される。

40

#### 【0041】

また液晶表示ユニット76には、第1、第2特別図柄表示手段63、64による第1、第2特別図柄の変動表示と並行して演出図柄90を変動表示可能である他、第1、第2特別保留個数を示す第1、第2保留画像X1～X4、Y1～Y4、変動中保留画像Z等の各種画像を表示可能となっている。

#### 【0042】

ここで演出図柄90は、数字図柄その他の複数個の図柄で構成される図柄列を複数（こ

50

こでは左右方向に3つ)備えており、またそれら各図柄列を構成する各図柄は、図5に示すように、1~8等の数字、その他で構成される図柄本体部90aと、この図柄本体部90aに付隨するキャラクタその他の装飾部90bとの結合で構成されている。なお演出図柄90は、拡大又は縮小、表示位置の変更、装飾部90bの消去等、表示態様を任意に変化させることが可能である。

#### 【0043】

演出図柄90は、例えば第1、第2特別図柄の変動開始と略同時に所定の変動パターンに従って図柄列毎に縦スクロール等による変動を開始すると共に、所定の有効ライン上の停止図柄が所定態様となるように例えば第1、第2特別図柄の変動停止と略同時に最終停止する。なお演出図柄90では、例えば有効ライン上の全ての停止図柄が同じ場合が大当たり演出態様、それ以外が外れ演出態様となっており、第1、第2特別図柄が第1、第2大当たり態様となる場合には演出図柄90は大当たり演出態様となり、第1、第2特別図柄が第1、第2外れ態様となる場合には演出図柄90は外れ演出態様となる。

10

#### 【0044】

また第1、第2保留画像X1~X4、Y1~Y4、変動中保留画像Zに関しては、第1、第2特別図柄始動手段72、73が遊技球を検出することに基づいて第1、第2特別保留個数が増加した場合に、第1、第2保留画像X1~、Y1~を液晶表示ユニット76上に1個追加表示し、また第1、第2特別図柄表示手段63、64による第1、第2特別図柄の新たな変動が開始することに基づいて第1、第2特別保留個数が減少した場合に、例えば変動中保留画像Zを消去し、第1、第2保留画像X1~、Y1~を待ち行列の前側(例えば画面右側)に向けて1個分ずつシフトすると共に、押し出された先頭の第1、第2保留画像X1、Y1を例えば所定位置まで移動させて新たな変動中保留画像Zに変化させるようになっている。

20

#### 【0045】

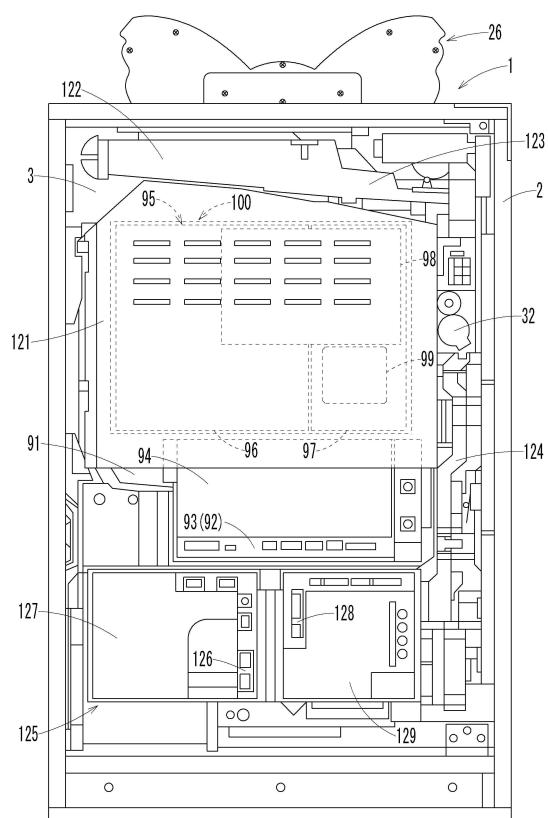

また遊技盤16の裏側には、図7に示すように、液晶表示ユニット76を遊技盤16の後側で支持するための裏ケース91が装着され、この裏ケース91の背面側に、主制御部92を構成する主制御基板93が格納された主基板ケース94、演出制御部95を構成する演出インターフェース基板96、液晶インターフェース基板97、液晶制御基板98及びROM基板99が格納された演出基板ケース100等が着脱自在に装着されている。

30

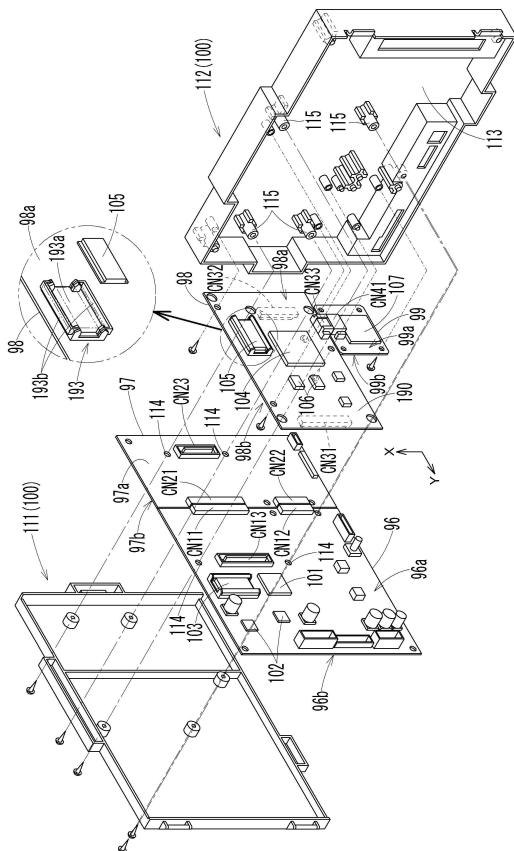

#### 【0046】

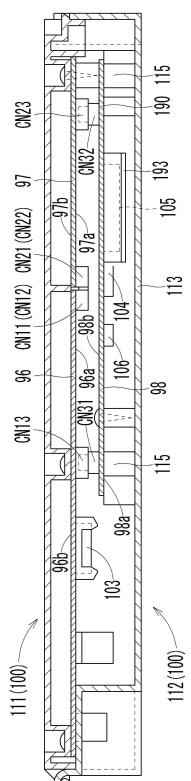

ここで、演出インターフェース基板96、液晶インターフェース基板97、液晶制御基板98及びROM基板99について、演出基板ケース100への格納状態の詳細について図8、図9を参照しつつ説明する。

#### 【0047】

演出インターフェース基板96と液晶インターフェース基板97とは、夫々の表面96a、97aが後側となる向きで、左右に互いに近接した状態で配置されている。そして、演出インターフェース基板96と液晶インターフェース基板97とは、演出インターフェース基板96における液晶インターフェース基板97側の縁部に沿って配置された演出IF第1、第2コネクタCN11、CN12と、液晶インターフェース基板97における演出インターフェース基板96側の縁部に沿って配置された液晶IF第1、第2コネクタCN21、CN22とを夫々左右方向に直結することによって互いに一体化されている。なお、演出インターフェース基板96では、その表裏両面に各種電子部品が配置されているが、音声プロセッサ101、デジタルアンプ102等の各種IC、液晶IF第1~第3コネクタCN21~CN23等の各種コネクタ、音声ROM103等は表面96a側に配置されている。また液晶インターフェース基板97についても、その表裏両面に各種電子部品が配置されているが、液晶IF第1~第3コネクタCN21~CN23等の各種コネクタについては表面97a側に配置されている。

40

#### 【0048】

また液晶制御基板98は、その表面98aが後向きとなり、裏面98bが演出インターフェース基板96及び液晶インターフェース基板97の表面96a、97aと対向するよ

50

うに、演出インターフェース基板 9 6 及び液晶インターフェース基板 9 7 の後側に配置されている。そして液晶制御基板 9 8 は、その裏面 9 8 b 側に設けられた液晶制御第 1 コネクタ C N 3 1 を演出インターフェース基板 9 6 側の演出 I F 第 3 コネクタ C N 1 3 に、同じく裏面 9 8 b 側に設けられた液晶制御第 2 コネクタ C N 3 2 を液晶インターフェース基板 9 7 側の液晶 I F 第 3 コネクタ C N 2 3 に夫々直結することにより、演出インターフェース基板 9 6 及び液晶インターフェース基板 9 7 と一体化されている。なお、液晶制御基板 9 8 では、その表裏両面に各種電子部品が配置されており、表面 9 8 a 側には複合チップ 1 0 4 、制御 R O M 1 0 5 、 D R A M 1 0 6 、液晶制御第 3 コネクタ C N 3 3 等が配置され、裏面 9 8 b 側には液晶制御第 1 、第 2 コネクタ C N 3 1 、 C N 3 2 等が配置されている。

10

#### 【 0 0 4 9 】

また R O M 基板 9 9 は、表面 9 9 a が後向きとなり、裏面 9 9 b が演出インターフェース基板 9 6 、液晶インターフェース基板 9 7 のうちの例えは液晶インターフェース基板 9 7 の表面 9 7 a と対向するように、液晶制御基板 9 8 に隣接して例えはその下側に配置されている。そして R O M 基板 9 9 は、その表面 9 9 a 側の上縁部に配置されている R O M 第 1 コネクタ C N 4 1 を、液晶制御基板 9 8 の下縁部に配置されている液晶制御第 3 コネクタ C N 3 3 に直結することにより液晶制御基板 9 8 と一体化されている。なお、 R O M 基板 9 9 では、その表裏両面に各種電子部品が配置されているが、 C G R O M 1 0 7 、 R O M 第 1 コネクタ C N 4 1 等については表面 9 9 a 側に配置されている。

20

#### 【 0 0 5 0 】

以上説明したように、基板 9 6 ~ 9 9 は、互いのコネクタ同士を直結することにより、演出インターフェース基板 9 6 及び液晶インターフェース基板 9 7 の表面 9 6 a 、 9 7 a と液晶制御基板 9 8 及び R O M 基板 9 9 の裏面 9 8 b 、 9 9 b とを、所定の隙間を空けて対向させた状態で接続され、一体化される。従って、それら基板 9 6 ~ 9 9 を互いに接続した状態では、液晶制御基板 9 8 の裏面 9 8 b 側は、演出インターフェース基板 9 6 及び液晶インターフェース基板 9 7 の陰になって目視することができない。

#### 【 0 0 5 1 】

演出基板ケース 1 0 0 は透明な合成樹脂製で、基板 9 6 ~ 9 9 の裏面側を覆うベース体 1 1 1 と、基板 9 6 ~ 9 9 の表面側を覆うカバーボディ 1 1 2 とで略箱形に形成されている。基板 9 6 ~ 9 9 を演出基板ケース 1 0 0 に格納する際には、まず液晶制御基板 9 8 と R O M 基板 9 9 とを、コネクタの直結により互いに連結した状態で、カバーボディ 1 1 2 の内側の所定位置にねじ止めにより固定する。このとき、液晶制御基板 9 8 、 R O M 基板 9 9 の表面 9 8 a 、 9 9 a が、カバーボディ 1 1 2 の背壁 1 1 3 の内面側に所定の隙間を挟んで対向する。

30

#### 【 0 0 5 2 】

次に、演出インターフェース基板 9 6 と液晶インターフェース基板 9 7 とを、コネクタの直結により互いに連結した状態で、液晶制御基板 9 8 及び R O M 基板 9 9 の背面側からカバーボディ 1 1 2 の内側の所定位置に嵌め込む。このとき、演出インターフェース基板 9 6 側の演出 I F 第 3 コネクタ C N 1 3 が液晶制御基板 9 8 側の液晶制御第 1 コネクタ C N 3 1 に、液晶インターフェース基板 9 7 側の液晶 I F 第 3 コネクタ C N 2 3 が液晶制御基板 9 8 側の液晶制御第 2 コネクタ C N 3 2 に夫々結合される。

40

#### 【 0 0 5 3 】

続いて、ベース体 1 1 1 を、演出インターフェース基板 9 6 及び液晶インターフェース基板 9 7 の裏面 9 6 b 、 9 7 b 側からカバーボディ 1 1 2 に嵌め合わせる。そして更に、ベース体 1 1 1 の外側から演出インターフェース基板 9 6 、液晶インターフェース基板 9 7 の通孔 1 1 4 を介してカバーボディ 1 1 2 側のねじ止め基部 1 1 5 に対してねじ止めすることにより、基板 9 6 ~ 9 9 は演出基板ケース 1 0 0 内の所定位置に固定される。基板 9 6 ~ 9 9 が格納された演出基板ケース 1 0 0 は、ベース体 1 1 1 を前側、カバーボディ 1 1 2 を後側に向けた状態で、裏ケース 9 1 の背面側に着脱自在に装着される。

#### 【 0 0 5 4 】

50

また前枠 3 の裏側には、図 7 に示すように、遊技盤 1 6 の裏側を開閉自在に覆う裏カバー 1 2 1 が着脱自在に装着されると共に、その上側に遊技球タンク 1 2 2 とタンクレール 1 2 3 とが、左右一側に払出手段 3 2 と払出通路 1 2 4 とが夫々装着されており、遊技球が大入賞手段 7 4 等の入賞口に入賞したとき、又は国外の自動球貸し機から球貸し指令があったときに、遊技球タンク 1 2 2 内の遊技球をタンクレール 1 2 3 経由で払出手段 3 2 により払い出し、その遊技球を払出通路 1 2 4 経由で上皿 3 3 に案内するようになっている。なお、裏カバー 1 2 1 は、演出基板ケース 1 0 0 の略全体と主基板ケース 9 4 の上部側の一部分とを後側から覆うように配置されている。

#### 【 0 0 5 5 】

また、前枠 3 の裏側下部には、基板装着台 1 2 5 が着脱自在に装着されており、この基板装着台 1 2 5 の背面側に、電源基板 1 2 6 が格納された電源基板ケース 1 2 7 、払出発射制御基板 1 2 8 が格納された払出発射基板ケース 1 2 9 が夫々着脱自在に装着されている。

10

#### 【 0 0 5 6 】

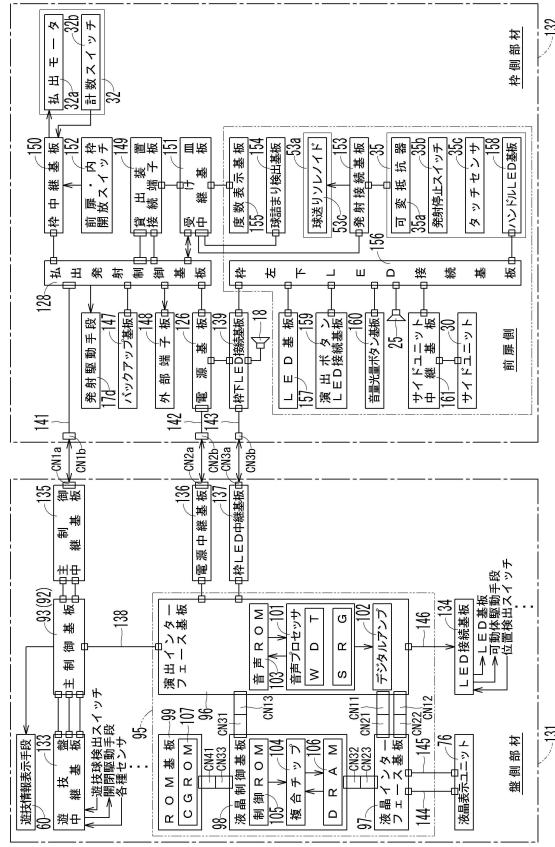

図 1 0 は本パチンコ機の全体回路構成を示すブロック図である。図 1 0 に示すように、本パチンコ機の全体回路構成は、遊技盤 1 6 側に搭載される盤側部材 1 3 1 と、前枠 3 側に搭載される枠側部材 1 3 2 とで構成されている。

#### 【 0 0 5 7 】

盤側部材 1 3 1 は、主制御部 9 2 を構成する主制御基板 9 3 、演出制御部 9 5 を構成する演出インターフェース基板 9 6 、液晶インターフェース基板 9 7 、液晶制御基板 9 8 及び ROM 基板 9 9 の他、遊技盤中継基板 1 3 3 、 LED 接続基板 1 3 4 、主制御中継基板 1 3 5 、電源中継基板 1 3 6 、枠 LED 中継基板 1 3 7 等で構成されている。

20

#### 【 0 0 5 8 】

主制御基板 9 3 は、遊技制御を統括的に行うもので、普通回路始動手段 7 1 や大入賞手段 7 4 等に設けられた遊技球検出スイッチ、大入賞手段 7 4 等に設けられた開閉駆動手段、遊技盤 1 6 の各部に配置された磁気、電波、振動等の各種センサ、遊技情報表示手段 6 0 等が、遊技盤中継基板 1 3 3 等の中継基板を介して、或いは中継基板を介すことなく直接的に接続されている。また主制御基板 9 3 は、演出制御ハーネス 1 3 8 を介して演出インターフェース基板 9 6 に接続されており、制御コマンド CMD とストローブ信号 STB とを送信可能となっている。

30

#### 【 0 0 5 9 】

主制御中継基板 1 3 5 、電源中継基板 1 3 6 及び枠 LED 中継基板 1 3 7 は、盤側部材 1 3 1 を枠側部材 1 3 2 に接続するためのもので、主制御基板 9 3 は主制御中継基板 1 3 5 を介して払出発射制御基板 1 2 8 に接続され、演出インターフェース基板 9 6 は電源中継基板 1 3 6 を介して電源基板 1 2 6 に、枠 LED 中継基板 1 3 7 を介して枠下 LED 接続基板 1 3 9 に夫々接続されている。遊技盤 1 6 側の主制御中継基板 1 3 5 、電源中継基板 1 3 6 、枠 LED 中継基板 1 3 7 には、盤側第 1 ~ 第 3 コネクタ CN 1 a ~ CN 3 a が夫々遊技盤 1 6 の後側に対応して配置され、また内枠 6 側の遊技盤装着部 1 4 ( 図 2 ) には、枠側第 1 ~ 第 3 コネクタ CN 1 b ~ CN 3 b が夫々盤側第 1 ~ 第 3 コネクタ CN 1 a ~ CN 3 a に対向するように配置されており、遊技盤 1 6 が内枠 6 の遊技盤装着部 1 4 に前側から装着されたとき、盤側第 1 ~ 第 3 コネクタ CN 1 a ~ CN 3 a が枠側第 1 ~ 第 3 コネクタ CN 1 b ~ CN 3 b に夫々結合されるようになっている。なお、枠側第 1 コネクタ CN 1 b は、払出発射制御基板 1 2 8 に接続される払出発射制御中継ハーネス 1 4 1 の一端側に設けられ、枠側第 2 コネクタ CN 2 b は、電源基板 1 2 6 に接続される演出制御電源ハーネス 1 4 2 の一端側に設けられ、枠側第 3 コネクタ CN 3 b は、枠下 LED 接続基板 1 3 9 に接続される枠下 LED 接続ハーネス 1 4 3 の一端側に設けられている。

40

#### 【 0 0 6 0 】

また、演出制御部 9 5 を構成する演出インターフェース基板 9 6 、液晶インターフェース基板 9 7 、液晶制御基板 9 8 及び ROM 基板 9 9 は、既に説明したようにハーネスを介すことなくコネクタ同士を直結することによって互いに一体化されている。

50

## 【0061】

液晶インターフェース基板97には、バックライトハーネス144、液晶表示ユニットハーネス145を介して液晶表示ユニット76が接続されている。また演出インターフェース基板96には、LED接続ハーネス146を介してLED接続基板134が接続されている。LED接続基板134には、遊技盤16側の各種LED基板の他、可動体77~79の駆動制御に使用するモータ、ソレノイド等の可動体駆動手段、位置検出スイッチ等が接続されている。

## 【0062】

枠側部材132は、電源基板126、派出発射制御基板128を中心に構成されている。電源基板126は、AC24Vを受けて各種の直流電圧を出力するもので、派出発射制御基板128にDC5V, DC12V, DC35Vを、枠下LED接続基板139にDC12Vを夫々出力する他、電源中継基板136を介して演出インターフェース基板96にDC5V, DC12V, DC35Vを出力するようになっている。派出発射制御基板128にはバックアップ基板147が接続されており、派出発射制御基板128から主制御基板93に対しては、電源基板126から受けたDC5V, DC12V, DC35Vの他、バックアップ電源、電源異常信号等が、主制御中継基板135を介して出力される。

10

## 【0063】

また派出発射制御基板128には、発射手段17を構成する発射駆動手段17d、外部のホストコンピュータ等に各種情報を出力するための外部端子板148、外部の遊技球貸出装置を接続するための貸出装置接続端子板149の他、枠中継基板150、受け皿中継基板151等が接続されている。

20

## 【0064】

枠中継基板150は、内枠6側に配置された派出モータ32a、派出計数スイッチ32b、前扉・内枠開放スイッチ152等と派出発射制御基板128との接続を中継するものである。また受け皿中継基板151は、前扉7側の発射接続基板153、球詰まり検出基板154、度数表示基板155等と派出発射制御基板128との接続を中継するものである。発射接続基板153には、発射ハンドル35を構成する可変抵抗器35a、発射停止スイッチ35b、タッチセンサ35cの他、球送りユニット53aに設けられた球送りソレノイド53c等が接続されている。

## 【0065】

30

また、枠下LED接続基板139には、内枠6側の下部スピーカ18の他、前扉7側の枠左下LED接続基板156が接続されている。枠左下LED接続基板156には、前扉7側の電飾を構成するLED基板157、発射ハンドル35に配置されたハンドルLED基板158、演出ボタン41やその内部のLED基板等が接続される演出ボタンLED接続基板159、音量/光量調整ボタン39, 40等が接続される音量光量ボタン基板160、上部スピーカ25、サイドユニット30に接続されるサイドユニット中継基板161等が接続されている。

## 【0066】

続いて、演出制御部95を構成する演出インターフェース基板96、液晶インターフェース基板97、液晶制御基板98及びROM基板99の回路構成について、図10, 図11を参照しつつ詳細に説明する。

40

## 【0067】

図10に示すように、演出インターフェース基板96は、各種入出力バッファの他、液晶制御基板98の複合チップ104に搭載されているCPU回路171(図11)から受けける指示に基づいて音声信号を再生する音声プロセッサ101、再生される音声信号の元データである圧縮音声データ等を記憶する音声ROM103、音声プロセッサ101から出力される音声信号を受けるデジタルアンプ102等を備えている。音声プロセッサ101は、内部回路の異常動作時に内部回路の設定値を自動的にデフォルト値にリセットするWDT回路と、音声制御レジスタSRGとを内蔵しており、音声制御レジスタSRGが、複合チップ104のCPU回路171から受ける動作パラメータに基づいて音声ROM1

50

03にアクセスし、必要な音声信号を再生してデジタルアンプ102に出力するようになつている。

#### 【0068】

演出インターフェース基板96に搭載されている各種入出力バッファには、主制御基板93から制御コマンドCMDとストローブ信号STBとを受けて液晶制御基板98の複合チップ104に転送するための入力バッファ、枠LED中継基板137を経由して演出ボタン41等のスイッチ信号を受けて液晶制御基板98の複合チップ104に転送するための入力バッファ、液晶制御基板98から受けたシリアル信号を枠LED中継基板137を経由してLED基板等のドライバICに転送するための出力バッファ、LED接続基板134を経由して可動体の位置検出スイッチ等のスイッチ信号を受けて液晶制御基板98の複合チップ104に転送するための入力バッファ、液晶制御基板98から受けたシリアル信号をLED接続基板134を経由してLED基板等のドライバICに転送するための出力バッファ等がある。

#### 【0069】

また液晶制御基板98には、CPU回路171を内蔵する複合チップ(チップ)104と、CPU回路171の制御プログラムを記憶する制御ROM(チップと接続されるROM)105と、大量のデータを高速にアクセス可能なDRAM(Dynamic Random Access Memory)106とが搭載されており、その液晶制御基板98に接続されているROM基板99には、演出制御に必要な大量のCGデータを記憶するGROM107が搭載されている。

#### 【0070】

制御ROM105は、チップセレクト信号CS0で選択されるアドレス空間CS0に位置付けされている。またDRAM106は、チップセレクト信号CS5で選択されるアドレス空間CS5に位置付けされている。

#### 【0071】

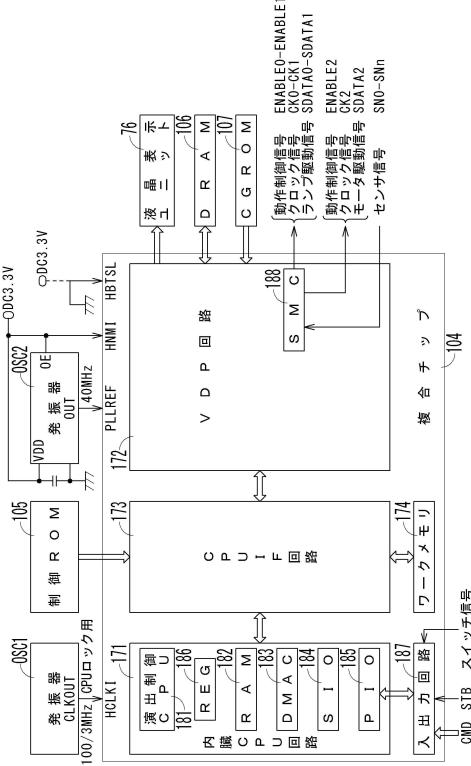

図11は、液晶制御基板98に搭載される複合チップ104について、関連する回路素子も含めて図示した回路ブロック図である。図示の通り、複合チップ104には、所定時間毎にディスプレイリストDLを発行するCPU回路171と、発行されたディスプレイリストDLに基づいて画像データを生成し、液晶表示ユニット76を駆動するVDP回路172とが内蔵されている。そして、CPU回路171とVDP回路172とは、互いの送受信データを中継するCPUIF回路173を介して接続されている。

#### 【0072】

CPU回路171は、複合チップ104のHCLK端子で受けた発振器OSC1からの発振出力(例えば100/3MHz)を周波数倍(例えば8倍)して、266.7MHz程度のCPU動作クロックとしている。ここで、発振器OSC1は、スペクトラムス拡散波を出力するよう構成されることで、電波障害/電磁妨害を防止するEMI(Electromagnetic Interference)対策を図っている。

#### 【0073】

一方、VDP回路172は、複合チップ104のPLLREF端子で受けた発振器OSC2からの発振出力(例えば40MHz)を、必要に応じて周波数倍した上で、VDP回路172のシステムクロック、表示装置用の表示クロック(ドットクロックなど)、及び外付けのDRAM106のDDRクロックとして使用している。即ち、発振器OSC2の出力は、VDP回路172全体のリファレンスクロックとして機能している。

#### 【0074】

そこで、このリファレンスクロックの重要性を考慮して、発振器OSC2をVDP回路172と同じ電源電圧3.3Vで動作させると共に、出力イネーブル端子OEがHレベル(=3.3V)であることを条件に、リファレンスクロックを発振出力し、電源電圧3.3Vが所定レベル以下に低下した場合には、マスク不能の割込み(NMI)が生じるよう構成されている。

#### 【0075】

10

20

30

40

50

また複合チップ 104 には H B T S L 端子が設けられており、この H B T S L 端子の論理レベルに基づいて、電源投入 (C P U リセット) 後に実行されるブートプログラム (初期設定プログラム) を記憶する R O M を特定している。図示の通り、本実施形態では H B T S L = L に設定されており、C P U 回路 171 のアドレス空間 C S 0 のゼロ番地が制御 R O M 105 に割り当てられている。

#### 【 0 0 7 6 】

C P U I F 回路 173 には、制御プログラムや必要な制御データを不揮発的に記憶する制御 R O M 105 と、2 M バイト程度の記憶容量を有するワークメモリ (R A M) 174 とが接続されており、各々 C P U 回路 171、V D P 回路 172 からアクセス可能となっている。

10

#### 【 0 0 7 7 】

なお、制御 R O M 105 は、チップセレクト信号 C S 0 で選択されるアドレス空間 C S 0 に位置付けられ、ワークメモリ 174 は、チップセレクト信号 C S 6 で選択されるアドレス空間 C S 6 に位置付けられている。このワークメモリ 174 には、液晶表示ユニット 76 の一フレームを特定する一連の指示コマンドが記載されたディスプレイリスト D L を一次的に記憶する D L バッファ B U F が確保されている。

#### 【 0 0 7 8 】

C P U 回路 171 は、汎用のワンチップマイコンと同等の性能を有する回路であり、制御 R O M 105 の制御プログラムに基づいて画像演出を統括的に制御する演出制御 C P U 181 と、16 k バイト程度の記憶容量を有して C P U の作業領域として使用される内蔵 R A M 182 と、演出制御 C P U 181 を経由しないでデータ転送を実現するための D M A C (Direct Memory Access Controller) 183 と、複数の入力ポート S i 及び出力ポート S o を有するシリアル入出力ポート (S I O) 184 と、複数の入力ポート P i 及び出力ポート P o を有するパラレル入出力ポート (P I O) 185 と、それら各部の動作を制御するべく設定値が設定される制御レジスタ (R E G) 186 等を備えている。

20

#### 【 0 0 7 9 】

パラレル入出力ポート 185 は、入出力回路 187 等を介して外部機器 (演出インターフェース基板 96) に接続されており、演出制御 C P U 181 は、入出力回路 187 を経て、演出ボタン 41 等のスイッチ信号、制御コマンド C M D、割込み信号 S T B 等を受信するようになっている。

30

#### 【 0 0 8 0 】

また本実施形態では、発光演出と可動体演出のために、V D P 回路 172 の S M C 部 (Serial Management Controller) 188 を使用している。S M C 部 188 は、L E D コントローラとモータコントローラとを内蔵し、クロック同期方式でシリアル信号を出力可能となっている。また、モータコントローラは、所定の制御レジスタへの設定値に基づいて、任意のタイミングでラッチパルスを出力可能であり、またクロック同期方式でシリアル信号を入力可能となっている。そこで本実施形態では、クロック信号に同期してモータ駆動信号や L E D 駆動信号を S M C 部 187 から出力させる一方、適宜のタイミングで、ラッチパルスを動作制御信号 E N A B L E として出力するようになっている。また、可動体駆動手段を構成するモータ群 M 1 ~ M n からの原点センサ信号 S N 0 ~ S N n をクロック同期方式でシリアル入力するようになっている。

40

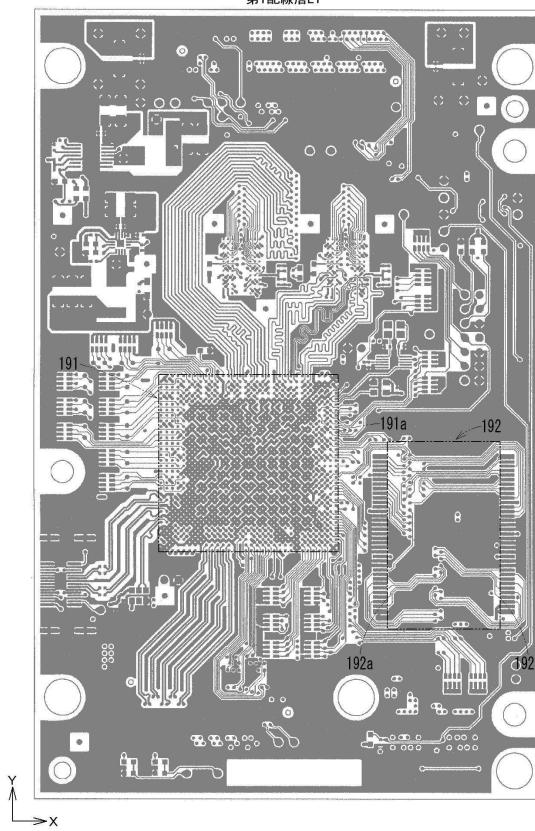

#### 【 0 0 8 1 】

続いて、演出制御部 95 を構成する液晶制御基板 98 について、配線パターン等の詳細を説明する。液晶制御基板 98 は、基板本体 190 (図 8 参照) に複数の配線層、具体的には表面 (第 1 面) 98 a 側の第 1 配線層 L 1 と、裏面 (第 2 面) 98 b 側の第 6 配線層 L 6 と、それらの間に配置される第 2 ~ 第 5 配線層 L 2 ~ L 5 とよりなる計 6 層の第 1 ~ 第 6 配線層 L 1 ~ L 6 (図 12 ~ 図 17) を備えている。なお、第 2 配線層 L 2 (図 13) はグランドに接続されるベタ配線層、第 5 配線層 L 5 (図 16) は電源に接続されるベタ配線層となっている。また、液晶制御基板 98 の基板本体 190 には多数のビア (層間導通部) が板厚方向に設けられており、複数の配線層 L 1 ~ L 6 はそれらのビア (層間導

50

通部)を介して互いに導通されている。本実施形態で使用されるビアは、スルーホールにメッキを施したスルーホール型のビアで、基板本体190の表面(第1面)98aから裏面(第2面)98bまで貫通している。

#### 【0082】

なお以下の説明では、各配線層L1～L6の面内での方向や向きについては、図12～図17に座標系で示すように、同図における左右方向をX方向、同じく上下方向をY方向とし、右向き/左向きを夫々+X/-X方向(側)、上向き/下向きを夫々+Y/-Y方向(側)とする。また、斜め方向についても斜め+X-Y方向、斜め-X-Y方向のように表現する。なお図7、図8等より明らかのように、液晶制御基板98を遊技機本体1に装着した状態では、液晶制御基板98の+X方向が上向き、同じく+Y方向が遊技機本体1に向かって右向き(背面視で左向き)となる。

10

#### 【0083】

図12に示すように、表面98a側の第1配線層L1には、複合チップ(第1電子部品)104が配置される複合チップ配置領域(第1配置領域)191と、制御ROM(第2電子部品、特定電子部品)105が配置される制御ROM配置領域(第2配置領域)192とが設けられている。複合チップ配置領域191は、複合チップ104の形状に対応する略正方形で、液晶制御基板98の表面98aにおける中央部付近に配置されている。複合チップ配置領域191内には、複合チップ104の各端子に対応するドット状の端子接続部が略等間隔でマトリックス状に配置されている。なお複合チップ104は、32行32列(但し四隅の4個は欠落)で配列される計1020個の端子を底面側に備えており、それら各端子を夫々対応する端子接続部に接続させた状態で複合チップ配置領域191に装着されている。

20

#### 【0084】

制御ROM配置領域192は、制御ROM105を装着するROMソケット193(図8参照)の形状に対応してY方向に長い略長方形で、その長辺の長さが複合チップ配置領域191の一辺の長さと同程度となっている。制御ROM配置領域192は、複合チップ配置領域191に対して+X側の近傍に配置されており、制御ROM配置領域192の-X側、+X側の長辺である第1、第2縁部192a、192bのうちの第1縁部192aが、複合チップ配置領域191における+X側の第1縁部191aに対して、-Y方向にずれた状態で所定距離をあいて対向している。

30

#### 【0085】

制御ROM配置領域192には、その両長辺、即ち第1、第2縁部192a、192bに沿って夫々複数個(ここでは各35個)の端子接続部(ROM端子接続部)が配列されている。また制御ROM配置領域192には、制御ROM105を着脱可能に支持するROMソケット193が固定されており、そのROMソケット193に制御ROM105が着脱自在に装着されている(図8)。制御ROM105には、その両端部に沿って夫々複数(ここでは各35個)の端子が配列されており、それら各端子が、ROMソケット193を介して制御ROM配置領域192の各端子接続部に接続されている。

#### 【0086】

なおROMソケット193は、図8に示すように、制御ROM配置領域192に対応する略長方形の底壁193aと、その底壁193a上に装着された制御ROM105の両縁部を係脱可能に保持する一対のROM保持部193bとを備えており、底壁193aが制御ROM配置領域192の略全体を覆う状態で液晶制御基板98の表面98aに固定されている。従って、第1配線層L1における制御ROM配置領域192内の配線パターン(ビア等)については、ROMソケット193から制御ROM105を取り外した状態でもROMソケット193の底壁(遮蔽壁)193aによって遮蔽され、外部から視認することはできない。これにより、複合チップ104と制御ROM105とを接続する配線パターンを不正改造するなどのゴト行為に対する予防性を高めることが可能となる。また、制御ROM配置領域192内に配線パターンを引くことで、それ以外の領域に配線スペースを確保することが可能となる。

40

50

## 【0087】

また図17に示すように、裏面98b側の第6配線層L6には、液晶制御第1コネクタCN31が配置される第1コネクタ配置領域194と、液晶制御第2コネクタCN32が配置される第2コネクタ配置領域195とが設けられている。第1コネクタ配置領域194は、X方向に長い略長方形で、液晶制御基板98の裏面98bにおける+Y側の縁部近傍に配置されている。第1コネクタ配置領域194内には、液晶制御第1コネクタCN31の各端子に対応する端子接続部が、一対の長辺に沿って夫々複数（ここでは各70個）配列されている。また第2コネクタ配置領域195は、X方向に長い略長方形で、液晶制御基板98の裏面98bにおける-Y側の縁部近傍に配置されている。第2コネクタ配置領域195内には、液晶制御第2コネクタCN32の各端子に対応する端子接続部が、一対の長辺に沿って夫々複数（ここでは各50個）配列されている。

10

## 【0088】

複合チップ104の全ての端子のうち、制御ROM105に接続される端子については、複合チップ配置領域191における制御ROM105側の第1縁部191aの近傍に集中的に配置されている。図18は、複合チップ104の全ての端子のうち、第1縁部191a近傍の一部の端子についてその種類（端子情報）を示している。なお、図18における各端子の配列は、図12における複合チップ配置領域191内の端子接続部の配列と一致させている。

20

## 【0089】

図18において、HAD0～HAD25がアドレス情報を出力するためのアドレス出力端子、HDT0～HDT15がデータ情報を入出力するためのデータ入出力端子、HCS0がチップセレクト信号を出力するためのチップセレクト出力端子、HRDがリードストローブ信号を出力するためのリードストローブ出力端子、RESETがシステムリセット信号を入力するためのシステムリセット端子である。なお以下の説明では、複合チップ配置領域191内の端子接続部に、対応する複合チップ104の端子の符号HAD0～HAD25、HDT0～HDT15等をそのまま用いるものとする。例えば、端子接続部HRDは、リードストローブ出力端子HRDに対応する端子接続部を示している。

20

## 【0090】

また図19は、制御ROM105の各端子についてその種類（端子情報）を示している。図19に示す各端子のうち、A0～A24はアドレス情報を入力するためのアドレス入力端子、Q0～Q15はデータ情報を入出力するためのデータ入出力端子で、夫々複合チップ104のアドレス出力端子、データ入出力端子と接続される。CE#はチップセレクト信号を入力するためのチップセレクト入力端子で、複合チップ104のチップセレクト出力端子と接続される。WE#は書き込み可能入力端子で、電源と接続して常にHレベルとすることにより、OE#端子の値（H/L）に応じてモードを切り替えることが可能となっている。なお、OE#は出力可能入力端子で、複合チップ104のリードストローブ出力端子と接続される。

30

## 【0091】

RESET#はリセット端子で、複合チップ104のシステムリセット入力端子HRESETと共に電源電圧監視用集積回路（リセットIC）と接続される。WP#/ACCは書き込み禁止/プログラムインプット端子で、グランド（Lレベル）又は電源（Hレベル）に接続することで、書き込みの禁止/許容、プログラムの実行禁止/許容を切り替えることが可能となっている。本実施形態では、WP#/ACC端子は電源に接続され、Hレベルに設定されている。BYTE#は8/16bitモード選択端子で、グランド（Lレベル）又は電源（Hレベル）に接続することで、8bit通信モードと16bit通信モードとの何れかを選択することが可能となっている。

40

## 【0092】

なお以下の説明では、制御ROM配置領域192に対応する端子接続部についても、対応する制御ROM105の端子の符号A0～A24、Q0～Q15、CE#等をそのまま用いるものとする。例えば、端子接続部RESET#は、リセット端子RESET#に対

50

応する端子接続部を示している。

【0093】

以下、液晶制御基板98上に設けられた多数の配線路のうち、複合チップ104と制御ROM105とを接続している配線路を含む複数種類の配線路P1～P47に着目し、その詳細について図面を参照しつつ説明する。なお、図20～図25は、図12～図17に示す第1～第6配線層L1～L6の各配線パターンから夫々配線路P1～P47を構成する部分のみを抽出して示したもので、図26～図34はその部分拡大図である。また、図35～図40は、配線路P1～P47の配線経路を模式的に示したものである。なお、図35～図40において、グレーで表示したビア（例えば図35の配線路P1におけるビアv86）は、制御ROM配置領域192内に配置されているビア（特定層間導通部）を示し、太線で表示した配線路（例えば図35の配線路P2における配線路cp13）は、制御ROM105側の端子接続部に対して制御ROM配置領域192の内側から接続されている配線路を示している。

【0094】

まず初めに、複合チップ104のアドレス出力端子HAD0～HAD25に接続される配線路P1～P26について説明する。本実施形態では、アドレス出力端子HAD0～HAD25のうち、HAD1～HAD25については、制御ROM105側のアドレス入力端子A0～A24に夫々接続されるとともに、液晶制御第1コネクタCN31にも接続されている。一方、アドレス出力端子HAD0については、液晶制御第1コネクタCN31には接続されているが、制御ROM105側の端子とは接続されていない。

【0095】

なお、複合チップ104のアドレス出力端子HAD1～HAD25の配列（図18）と、それに対応する制御ROM105のアドレス入力端子A0～A24の配列（図19）とを比較すると、両者は明らかに相違している。即ち、複合チップ104のアドレス出力端子HAD1～HAD25は、図18に示すように6行に分けて配列されており、行毎に列数は異なるが並び順は一定しているのに対し、制御ROM105のアドレス入力端子A0～A24は、図19に示すように2列に分けて配列されており、各列における並び順に一定の規則性はない。しかも、複合チップ104と制御ROM105の配置位置や配線パターンの数の多さが関係してくることで、配線パターンの引き回しが非常に複雑なものとなる。そのため、複合チップ104と制御ROM105とを接続する配線パターンの引き回しを最適化することは非常に重要であり、それによって配線パターンの線長を短くすることができ、ノイズ低減や基板全体のスリム化を図ることにつながる。また、これらは複合チップ104と制御ROM105との間の関係だけでなく、複合チップ104と各種コネクタ等の電子部品との関係性においても同様のことが言える。特に、HAD1～HAD25やHDT1～HDT25などの複合チップ104や制御ROM105、各種コネクタなどの複数の電子部品と接続される配線パターンについては、上述の課題が大きい分、最適化することによる効果も大きいものとなる。

【0096】

配線路P1～P26のうち、配線路P1（図35）では、図26に示すように、第1配線層L1の複合チップ配置領域191に設けられた端子接続部HAD0が、配線路cp0により、斜め-X-Y方向の近傍に配置されたビアv0に接続されている。ビアv0は、その周囲に配置されている4つの端子接続部（端子接続部HAD0を含む）の略中央に配置されている。このビアv0は、図28に示すように、第3配線層L3に設けられた配線路cp1によりビアv41と接続されている。このビアv41は、複合チップ配置領域191と制御ROM配置領域192との間に配置されている。そしてビアv41は、図31に示すように、第4配線層L4に設けられた配線路cp2により、制御ROM配置領域192内に配置されるビアv86と接続されている。このように、第1配線層L1で端子接続部HAD0から引き出された配線路は、2つの配線層L3, L4を経て制御ROM配置領域192内のビアv86に接続されている。

【0097】

10

20

30

40

50

端子接続部 H A D 0 からビア v 8 6 に達した配線路は、このビア v 8 6 で 2 つに分岐している。第 1 の分岐路は、図 2 8 , 図 2 9 に示すように、第 3 配線層 L 3 に設けられた配線路 c p 3 により、ビア v 8 6 からテストポイント T P 2 8 を構成するビア v 2 0 5 を経て第 1 コネクタ配置領域 1 9 4 内のビア v 1 4 6 に接続され、更に図 3 3 に示すように、第 6 配線層 L 6 に設けられた配線路 c p 4 により、端子接続部 h a d 0 に対して第 1 コネクタ配置領域 1 9 4 の内側から接続されている。また第 2 の分岐路は、図 3 2 に示すように、第 6 配線層 L 6 に設けられた配線路 c p 5 により、ビア v 8 6 から終端抵抗 R A 1 6 に接続されている。この終端抵抗 R A 1 6 は、他端側が所定のビアを介して第 2 配線層 L 2 のベタ配線層 ( G N D ) に接続されている ( 配線図では省略 ) 。

#### 【 0 0 9 8 】

配線路 P 2 ( 図 3 5 ) では、図 2 6 に示すように、第 1 配線層 L 1 の複合チップ配置領域 1 9 1 に設けられた端子接続部 H A D 1 が、配線路 c p 1 1 により、斜め - X - Y 方向の近傍に配置されたビア v 5 に接続されている。ビア v 5 は、その周囲に配置されている 4 つの端子接続部 ( 端子接続部 H A D 1 を含む ) の略中央に配置されている。このビア v 5 は、図 3 1 に示すように、第 4 配線層 L 4 に設けられた配線路 c p 1 2 により、制御 R O M 配置領域 1 9 2 内に配置されるビア v 8 5 に接続されている。このように、端子接続部 H A D 1 から引き出された配線路は、端子接続部 H A D 0 から引き出された配線路とは異なり、第 3 配線層 L 3 は経由せず、第 4 配線層 L 4 を経て制御 R O M 配置領域 1 9 2 内のビア v 8 5 に接続されている。

#### 【 0 0 9 9 】

端子接続部 H A D 1 からビア v 8 5 に達した配線路は、このビア v 8 5 で 4 つに分岐している。第 1 の分岐路は、図 2 7 に示すように、第 1 配線層 L 1 に設けられた配線路 c p 1 3 により、ビア v 8 5 から制御 R O M 1 0 5 の端子接続部 A 0 に対して制御 R O M 配置領域 1 9 2 の内側から接続されている。また第 2 の分岐路は、図 3 2 に示すように、第 6 配線層 L 6 に設けられた配線路 c p 1 4 により、ビア v 8 5 から終端抵抗 R A 1 6 に接続されている。

#### 【 0 1 0 0 】

また第 3 の分岐路は、図 2 8 , 図 2 9 に示すように、第 3 配線層 L 3 に設けられた配線路 c p 1 5 により、ビア v 8 5 から第 1 コネクタ配置領域 1 9 4 内のビア v 1 4 5 に接続され、更に図 3 3 に示すように、第 6 配線層 L 6 に設けられた配線路 c p 1 6 により、端子接続部 h a d 1 に対して第 1 コネクタ配置領域 1 9 4 の内側から接続されている。また第 4 の分岐路は、図 2 8 , 図 3 0 に示すように、第 3 配線層 L 3 に設けられた配線路 c p 1 7 により、ビア v 8 5 からビア v 1 8 2 に接続され、更に図 3 4 に示すように、第 6 配線層 L 6 に設けられた配線路 c p 1 8 により、デコード回路を構成するデコーダ I C 1 2 に接続されている。

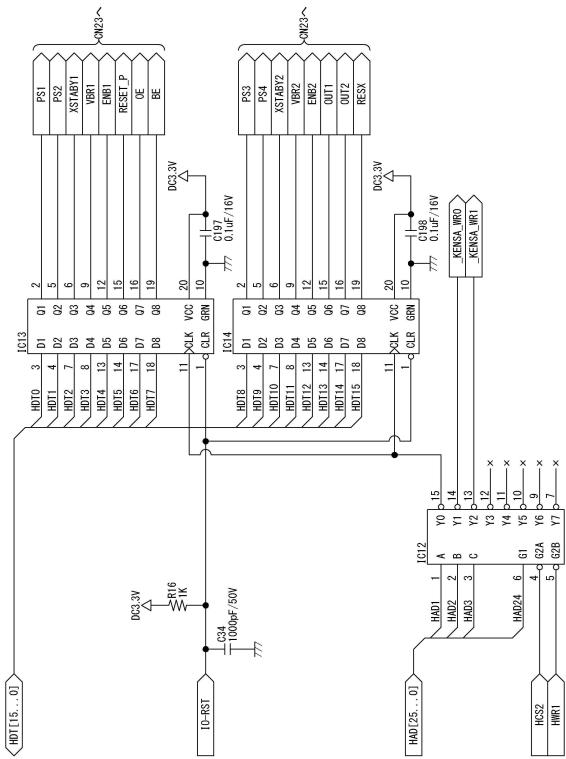

#### 【 0 1 0 1 】

なお、図 3 4 等の配線図では省略しているが、デコーダ I C 1 2 ~ I C 1 4 を含むデコード回路は図 4 1 に示すように構成されている。図 4 1 に示すように、デコーダ I C 1 3 , I C 1 4 は、液晶 I F 第 3 コネクタ C N 2 3 等を介して液晶表示ユニット 7 6 等に接続されており、電源投入時に、複合チップ 1 0 4 のデータ入出力端子 H D T 0 ~ H D T 1 5 からデータ情報が入力される。そしてデコーダ I C 1 3 , I C 1 4 は、デコーダ I C 1 2 から入力される C P U と同期したクロックに基づいて、液晶表示ユニット 7 6 等にデータ情報を出力するため、固定のデータ情報を C P U が毎回送信する必要がない。これにより、C P U から所定時間毎に同一のデータ情報を出力する必要がなく、C P U はデータ情報の内容を変更する場合にのみ新たなデータ情報を送信するようすればよいため、制御プログラムを簡素化することが可能となる。

#### 【 0 1 0 2 】

配線路 P 3 ( 図 3 5 ) では、図 2 6 に示すように、第 1 配線層 L 1 の複合チップ配置領域 1 9 1 に設けられた端子接続部 H A D 2 が、配線路 c p 2 1 により、斜め + X - Y 方向の近傍に配置されたビア v 4 に接続されている。ビア v 4 は、その周囲に配置されている

10

20

30

40

50

4つの端子接続部（端子接続部 HAD 2 を含む）の略中央に配置されている。このビア v 4 は、図 3 1 に示すように、第 4 配線層 L 4 に設けられた配線路 c p 2 2 により、制御 ROM 配置領域 192 内に配置されるビア v 8 4 に接続されている。

#### 【0103】

端子接続部 HAD 2 からビア v 8 4 に達した配線路は、このビア v 8 4 で 4 つに分岐している。第 1 の分岐路は、図 2 7 に示すように、第 1 配線層 L 1 に設けられた配線路 c p 2 3 により、ビア v 8 4 から制御 ROM 105 の端子接続部 A 1 に対して制御 ROM 配置領域 192 の内側から接続されている。また第 2 の分岐路は、図 3 2 に示すように、第 6 配線層 L 6 に設けられた配線路 c p 2 4 により、ビア v 8 4 から終端抵抗 RA16 に接続されている。

10

#### 【0104】

また第 3 の分岐路は、図 2 8 , 図 2 9 に示すように、第 3 配線層 L 3 に設けられた配線路 c p 2 5 により、ビア v 8 4 から第 1 コネクタ配置領域 194 内のビア v 144 に接続され、更に図 3 3 に示すように、第 6 配線層 L 6 に設けられた配線路 c p 2 6 により、端子接続部 had 2 に対して第 1 コネクタ配置領域 194 の内側から接続されている。また第 4 の分岐路は、図 2 8 , 図 3 0 に示すように、第 3 配線層 L 3 に設けられた配線路 c p 2 7 により、ビア v 8 4 からビア v 184 に接続され、更に図 3 4 に示すように、第 6 配線層 L 6 に設けられた配線路 c p 2 8 により、デコード回路を構成するデコーダ I C 12 に接続されている。

#### 【0105】

配線路 P 4 (図 3 5) では、図 2 6 に示すように、第 1 配線層 L 1 の複合チップ配置領域 191 に設けられた端子接続部 HAD 3 が、配線路 c p 3 1 により、斜め + X - Y 方向の近傍に配置されたビア v 13 に接続されている。ビア v 13 は、その周囲に配置されている 4 つの端子接続部（端子接続部 HAD 3 を含む）の略中央に配置されている。このビア v 13 は、図 3 1 に示すように、第 4 配線層 L 4 に設けられた配線路 c p 3 2 により、制御 ROM 配置領域 192 内に配置されるビア v 8 3 に接続されている。

20

#### 【0106】

端子接続部 HAD 3 からビア v 8 3 に達した配線路は、このビア v 8 3 で 4 つに分岐している。第 1 の分岐路は、図 2 7 に示すように、第 1 配線層 L 1 に設けられた配線路 c p 3 3 により、ビア v 8 3 から制御 ROM 105 の端子接続部 A 2 に対して制御 ROM 配置領域 192 の内側から接続されている。また第 2 の分岐路は、図 3 2 に示すように、第 6 配線層 L 6 に設けられた配線路 c p 3 4 により、ビア v 8 3 から終端抵抗 RA16 に接続されている。

30

#### 【0107】

また第 3 の分岐路は、図 2 8 , 図 2 9 に示すように、第 3 配線層 L 3 に設けられた配線路 c p 3 5 により、ビア v 8 3 から第 1 コネクタ配置領域 194 内のビア v 143 に接続され、更に図 3 3 に示すように、第 6 配線層 L 6 に設けられた配線路 c p 3 6 により、端子接続部 had 3 に対して第 1 コネクタ配置領域 194 の内側から接続されている。また第 4 の分岐路は、図 2 8 , 図 3 0 に示すように、第 3 配線層 L 3 に設けられた配線路 c p 3 7 により、ビア v 8 3 からビア v 181 に接続され、更に図 3 4 に示すように、第 6 配線層 L 6 に設けられた配線路 c p 3 8 により、デコード回路を構成するデコーダ I C 12 に接続されている。

40

#### 【0108】

配線路 P 5 (図 3 5) では、図 2 6 に示すように、第 1 配線層 L 1 の複合チップ配置領域 191 に設けられた端子接続部 HAD 4 が、配線路 c p 4 1 により、斜め + X - Y 方向の近傍に配置されたビア v 20 に接続されている。ビア v 20 は、その周囲に配置されている 4 つの端子接続部（端子接続部 HAD 4 を含む）の略中央に配置されている。このビア v 20 は、図 3 1 に示すように、第 4 配線層 L 4 に設けられた配線路 c p 4 2 により、制御 ROM 配置領域 192 内に配置されるビア v 8 2 に接続されている。

#### 【0109】

50

端子接続部 H A D 4 からビア v 8 2 に達した配線路は、このビア v 8 2 で 3 つに分岐している。第 1 の分岐路は、図 2 7 に示すように、第 1 配線層 L 1 に設けられた配線路 c p 4 3 により、ビア v 8 2 から制御 R O M 1 0 5 の端子接続部 A 3 に対して制御 R O M 配置領域 1 9 2 の内側から接続されている。また第 2 の分岐路は、図 3 2 に示すように、第 6 配線層 L 6 に設けられた配線路 c p 4 4 により、ビア v 8 2 から終端抵抗 R A 1 5 に接続されている。この終端抵抗 R A 1 5 は、他端側が所定のビアを介して第 2 配線層 L 2 のベタ配線層 ( G N D ) に接続されている（配線図では省略）。

#### 【 0 1 1 0 】

また第 3 の分岐路は、図 2 8 , 図 2 9 に示すように、第 3 配線層 L 3 に設けられた配線路 c p 4 5 により、ビア v 8 2 から第 1 コネクタ配置領域 1 9 4 内のビア v 1 4 2 に接続され、更に図 3 3 に示すように、第 6 配線層 L 6 に設けられた配線路 c p 4 6 により、端子接続部 h a d 4 に対して第 1 コネクタ配置領域 1 9 4 の内側から接続されている。

#### 【 0 1 1 1 】

配線路 P 6 ( 図 3 5 ) では、図 2 6 に示すように、第 1 配線層 L 1 の複合チップ配置領域 1 9 1 に設けられた端子接続部 H A D 5 が、配線路 c p 5 1 により、複合チップ配置領域 1 9 1 の外側、具体的には複合チップ配置領域 1 9 1 と制御 R O M 配置領域 1 9 2 との間に配置されたビア v 3 4 に接続されている。なお、端子接続部 H A D 5 は、複合チップ配置領域 1 9 1 の外周側から 2 列目に配置されている。ビア v 3 4 は、図 3 1 に示すように、第 4 配線層 L 4 に設けられた配線路 c p 5 2 により、制御 R O M 配置領域 1 9 2 内に配置されるビア v 8 1 に接続されている。

#### 【 0 1 1 2 】

端子接続部 H A D 5 からビア v 8 1 に達した配線路は、このビア v 8 1 で 3 つに分岐している。第 1 の分岐路は、図 2 7 に示すように、第 1 配線層 L 1 に設けられた配線路 c p 5 3 により、ビア v 8 1 から制御 R O M 1 0 5 の端子接続部 A 4 に対して制御 R O M 配置領域 1 9 2 の内側から接続されている。また第 2 の分岐路は、図 3 2 に示すように、第 6 配線層 L 6 に設けられた配線路 c p 5 4 により、ビア v 8 1 から終端抵抗 R A 1 5 に接続されている。

#### 【 0 1 1 3 】

また第 3 の分岐路は、図 2 8 , 図 2 9 に示すように、第 3 配線層 L 3 に設けられた配線路 c p 5 5 により、ビア v 8 1 から第 1 コネクタ配置領域 1 9 4 内のビア v 1 4 1 に接続され、更に図 3 3 に示すように、第 6 配線層 L 6 に設けられた配線路 c p 5 6 により、端子接続部 h a d 5 に対して第 1 コネクタ配置領域 1 9 4 の内側から接続されている。

#### 【 0 1 1 4 】

配線路 P 7 ( 図 3 5 ) では、図 2 6 に示すように、第 1 配線層 L 1 の複合チップ配置領域 1 9 1 に設けられた端子接続部 H A D 6 が、配線路 c p 6 1 により、複合チップ配置領域 1 9 1 の外側、具体的には複合チップ配置領域 1 9 1 と制御 R O M 配置領域 1 9 2 との間に配置されたビア v 3 9 に接続されている。なお、端子接続部 H A D 6 は、複合チップ配置領域 1 9 1 の最も外周側に配置されている。ビア v 3 9 は、図 3 1 に示すように、第 4 配線層 L 4 に設けられた配線路 c p 6 2 により、制御 R O M 配置領域 1 9 2 内に配置されるビア v 8 0 に接続されている。

#### 【 0 1 1 5 】

端子接続部 H A D 6 からビア v 8 0 に達した配線路は、このビア v 8 0 で 3 つに分岐している。第 1 の分岐路は、図 2 7 に示すように、第 1 配線層 L 1 に設けられた配線路 c p 6 3 により、ビア v 8 0 から制御 R O M 1 0 5 の端子接続部 A 5 に対して制御 R O M 配置領域 1 9 2 の内側から接続されている。また第 2 の分岐路は、図 3 2 に示すように、第 6 配線層 L 6 に設けられた配線路 c p 6 4 により、ビア v 8 0 から終端抵抗 R A 1 5 に接続されている。

#### 【 0 1 1 6 】

また第 3 の分岐路は、図 2 8 , 図 2 9 に示すように、第 3 配線層 L 3 に設けられた配線路 c p 6 5 により、ビア v 8 0 から第 1 コネクタ配置領域 1 9 4 内のビア v 1 4 0 に接続

10

20

30

40

50

され、更に図33に示すように、第6配線層L6に設けられた配線路c p 6 6により、端子接続部h a d 6に対して第1コネクタ配置領域194の内側から接続されている。

#### 【0117】

配線路P8(図35)では、図26に示すように、第1配線層L1の複合チップ配置領域191に設けられた端子接続部H A D 7が、配線路c p 7 1により、斜め+X-Y方向の近傍に配置されたビアv 3に接続されている。ビアv 3は、その周囲に配置されている4つの端子接続部(端子接続部H A D 7を含む)の略中央に配置されている。このビアv 3は、図31に示すように、第4配線層L4に設けられた配線路c p 7 2により、制御ROM配置領域192内に配置されるビアv 7 9に接続されている。

#### 【0118】

端子接続部H A D 7からビアv 7 9に達した配線路は、このビアv 7 9で3つに分岐している。第1の分岐路は、図27に示すように、第1配線層L1に設けられた配線路c p 7 3により、ビアv 7 9から制御ROM105の端子接続部A 6に対して制御ROM配置領域192の内側から接続されている。また第2の分岐路は、図32に示すように、第6配線層L6に設けられた配線路c p 7 4により、ビアv 7 9から終端抵抗RA15に接続されている。

#### 【0119】

また第3の分岐路は、図28、図29に示すように、第3配線層L3に設けられた配線路c p 7 5により、ビアv 7 9から第1コネクタ配置領域194内のビアv 1 3 9に接続され、更に図33に示すように、第6配線層L6に設けられた配線路c p 7 6により、端子接続部h a d 7に対して第1コネクタ配置領域194の内側から接続されている。

#### 【0120】

配線路P9(図36)では、図26に示すように、第1配線層L1の複合チップ配置領域191に設けられた端子接続部H A D 8が、配線路c p 8 1により、斜め+X-Y方向の近傍に配置されたビアv 1 2に接続されている。ビアv 1 2は、その周囲に配置されている4つの端子接続部(端子接続部H A D 8を含む)の略中央に配置されている。このビアv 1 2は、図31に示すように、第4配線層L4に設けられた配線路c p 8 2により、制御ROM配置領域192内に配置されるビアv 7 8に接続されている。

#### 【0121】

端子接続部H A D 8からビアv 7 8に達した配線路は、このビアv 7 8で3つに分岐している。第1の分岐路は、図27に示すように、第1配線層L1に設けられた配線路c p 8 3により、ビアv 7 8から制御ROM105の端子接続部A 7に対して制御ROM配置領域192の内側から接続されている。また第2の分岐路は、図32に示すように、第6配線層L6に設けられた配線路c p 8 4により、ビアv 7 8から終端抵抗RA13に接続されている。この終端抵抗RA13は、他端側が所定のビアを介して第2配線層L2のベタ配線層(GND)に接続されている(配線図では省略)。

#### 【0122】

また第3の分岐路は、図28、図29に示すように、第3配線層L3に設けられた配線路c p 8 5により、ビアv 7 8から第1コネクタ配置領域194内のビアv 1 3 8に接続され、更に図33に示すように、第6配線層L6に設けられた配線路c p 8 6により、端子接続部h a d 8に対して第1コネクタ配置領域194の内側から接続されている。

#### 【0123】

配線路P10(図36)では、図26に示すように、第1配線層L1の複合チップ配置領域191に設けられた端子接続部H A D 9が、配線路c p 9 1により、複合チップ配置領域191の外側、具体的には複合チップ配置領域191と制御ROM配置領域192との間に配置されたビアv 3 3に接続されている。なお、端子接続部H A D 9は、複合チップ配置領域191の外周側から2列目に配置されている。ビアv 3 3は、図31に示すように、第4配線層L4に設けられた配線路c p 9 2により、制御ROM配置領域192内に配置されるビアv 7 7に接続されている。

#### 【0124】

10

20

30

40

50

端子接続部 HAD 9 からビア v 77 に達した配線路は、このビア v 77 で 3 つに分岐している。第 1 の分岐路は、図 27 に示すように、第 1 配線層 L 1 に設けられた配線路 c p 93 により、ビア v 77 から制御 ROM 105 の端子接続部 A 8 に対して制御 ROM 配置領域 192 の内側から接続されている。また第 2 の分岐路は、図 32 に示すように、第 6 配線層 L 6 に設けられた配線路 c p 94 により、ビア v 77 から終端抵抗 RA 13 に接続されている。

#### 【0125】

また第 3 の分岐路は、図 28, 図 29 に示すように、第 3 配線層 L 3 に設けられた配線路 c p 95 により、ビア v 77 から第 1 コネクタ配置領域 194 内のビア v 137 に接続され、更に図 33 に示すように、第 6 配線層 L 6 に設けられた配線路 c p 96 により、端子接続部 had 9 に対して第 1 コネクタ配置領域 194 の内側から接続されている。

10

#### 【0126】

配線路 P 11 (図 36) では、図 26 に示すように、第 1 配線層 L 1 の複合チップ配置領域 191 に設けられた端子接続部 HAD 10 が、配線路 c p 101 により、複合チップ配置領域 191 の外側、具体的には複合チップ配置領域 191 と制御 ROM 配置領域 192 との間に配置されたビア v 38 に接続されている。なお、端子接続部 HAD 10 は、複合チップ配置領域 191 の最も外周側に配置されている。ビア v 38 は、図 31 に示すように、第 4 配線層 L 4 に設けられた配線路 c p 102 により、制御 ROM 配置領域 192 内に配置されるビア v 76 に接続されている。

20

#### 【0127】

端子接続部 HAD 10 からビア v 76 に達した配線路は、このビア v 76 で 3 つに分岐している。第 1 の分岐路は、図 27 に示すように、第 1 配線層 L 1 に設けられた配線路 c p 103 により、ビア v 76 から制御 ROM 105 の端子接続部 A 9 に対して制御 ROM 配置領域 192 の内側から接続されている。また第 2 の分岐路は、図 32 に示すように、第 6 配線層 L 6 に設けられた配線路 c p 104 により、ビア v 76 から終端抵抗 RA 13 に接続されている。

#### 【0128】

また第 3 の分岐路は、図 28, 図 29 に示すように、第 3 配線層 L 3 に設けられた配線路 c p 105 により、ビア v 76 から第 1 コネクタ配置領域 194 内のビア v 136 に接続され、更に図 33 に示すように、第 6 配線層 L 6 に設けられた配線路 c p 106 により、端子接続部 had 10 に対して第 1 コネクタ配置領域 194 の内側から接続されている。

30

#### 【0129】

配線路 P 12 (図 36) では、図 26 に示すように、第 1 配線層 L 1 の複合チップ配置領域 191 に設けられた端子接続部 HAD 11 が、配線路 c p 111 により、斜め - X + Y 方向の近傍に配置されたビア v 2 に接続されている。ビア v 2 は、その周囲に配置されている 4 つの端子接続部 (端子接続部 HAD 11 を含む) の略中央に配置されている。このビア v 2 は、図 31 に示すように、第 4 配線層 L 4 に設けられた配線路 c p 112 により、制御 ROM 配置領域 192 内に配置されるビア v 75 に接続されている。

#### 【0130】

端子接続部 HAD 11 からビア v 75 に達した配線路は、このビア v 75 で 3 つに分岐している。第 1 の分岐路は、図 27 に示すように、第 1 配線層 L 1 に設けられた配線路 c p 113 により、ビア v 75 から制御 ROM 105 の端子接続部 A 10 に対して制御 ROM 配置領域 192 の内側から接続されている。また第 2 の分岐路は、図 32 に示すように、第 6 配線層 L 6 に設けられた配線路 c p 114 により、ビア v 75 から終端抵抗 RA 13 に接続されている。

40

#### 【0131】

また第 3 の分岐路は、図 28, 図 29 に示すように、第 3 配線層 L 3 に設けられた配線路 c p 115 により、ビア v 75 から第 1 コネクタ配置領域 194 内のビア v 135 に接続され、更に図 33 に示すように、第 6 配線層 L 6 に設けられた配線路 c p 116 により、端子接続部 had 11 に対して第 1 コネクタ配置領域 194 の内側から接続されている。

50

## 【0132】

配線路 P 13 (図 36) では、図 26 に示すように、第 1 配線層 L 1 の複合チップ配置領域 191 に設けられた端子接続部 HAD12 が、配線路 c p 121 により、斜め + X - Y 方向の近傍に配置されたビア v 19 に接続されている。ビア v 19 は、その周囲に配置されている 4 つの端子接続部 (端子接続部 HAD12 を含む) の略中央に配置されている。このビア v 19 は、図 31 に示すように、第 4 配線層 L 4 に設けられた配線路 c p 122 により、制御 ROM 配置領域 192 内に配置されるビア v 74 に接続されている。

## 【0133】

端子接続部 HAD12 からビア v 74 に達した配線路は、このビア v 74 で 3 つに分岐している。第 1 の分岐路は、図 27 に示すように、第 1 配線層 L 1 に設けられた配線路 c p 123 により、ビア v 74 から制御 ROM105 の端子接続部 A11 に対して制御 ROM 配置領域 192 の内側から接続されている。また第 2 の分岐路は、図 32 に示すように、第 6 配線層 L 6 に設けられた配線路 c p 124 により、ビア v 74 から終端抵抗 RA11 に接続されている。この終端抵抗 RA11 は、他端側が所定のビアを介して第 2 配線層 L 2 のベタ配線層 (GND) に接続されている (配線図では省略)。

10

## 【0134】

また第 3 の分岐路は、図 28, 図 29 に示すように、第 3 配線層 L 3 に設けられた配線路 c p 125 により、ビア v 74 から第 1 コネクタ配置領域 194 内のビア v 134 に接続され、更に図 33 に示すように、第 6 配線層 L 6 に設けられた配線路 c p 126 により、端子接続部 h ad12 に対して第 1 コネクタ配置領域 194 の内側から接続されている。

20

## 【0135】

配線路 P 14 (図 36) では、図 26 に示すように、第 1 配線層 L 1 の複合チップ配置領域 191 に設けられた端子接続部 HAD13 が、配線路 c p 131 により、複合チップ配置領域 191 の外側、具体的には制御 ROM 配置領域 192 の + Y 側に配置されたビア v 49 に接続されている。なお、端子接続部 HAD13 は、複合チップ配置領域 191 の外周側から 2 列目に配置されている。ビア v 49 は、図 31 に示すように、第 4 配線層 L 4 に設けられた配線路 c p 132 により、制御 ROM 配置領域 192 内に配置されるビア v 73 に接続されている。

## 【0136】

端子接続部 HAD13 からビア v 73 に達した配線路は、このビア v 73 で 2 つに分岐している。第 1 の分岐路は、図 32 に示すように、第 6 配線層 L 6 に設けられた配線路 c p 133 により、ビア v 73 から終端抵抗 RA11 に接続されている。

30

## 【0137】

また第 2 の分岐路は、図 28 に示すように、第 3 配線層 L 3 に設けられた配線路 c p 134 により、ビア v 73 から、制御 ROM 配置領域 192 内に配置されるビア v 107 に接続されており、ここで更に 2 つに分岐している。その 1 つ目の第 2a の分岐路は、図 27 に示すように、第 1 配線層 L 1 に設けられた配線路 c p 135 により、ビア v 107 から制御 ROM105 の端子接続部 A12 に対して制御 ROM 配置領域 192 の内側から接続されている。また 2 つ目の第 2b の分岐路は、図 28, 図 29 に示すように、第 3 配線層 L 3 に設けられた配線路 c p 136 により、ビア v 107 から第 1 コネクタ配置領域 194 内のビア v 133 に接続され、更に図 33 に示すように、第 6 配線層 L 6 に設けられた配線路 c p 137 により、端子接続部 h ad13 に対して第 1 コネクタ配置領域 194 の内側から接続されている。

40

## 【0138】

配線路 P 15 (図 36) では、図 26 に示すように、第 1 配線層 L 1 の複合チップ配置領域 191 に設けられた端子接続部 HAD14 が、配線路 c p 141 により、複合チップ配置領域 191 の外側、具体的には制御 ROM 配置領域 192 の + Y 側に配置されたビア v 50 に接続されている。なお、端子接続部 HAD14 は、複合チップ配置領域 191 の最も外周側に配置されている。ビア v 50 は、図 31 に示すように、第 4 配線層 L 4 に設けられた配線路 c p 142 により、制御 ROM 配置領域 192 内に配置されるビア v 72

50

に接続されている。

【 0 1 3 9 】

端子接続部 H A D 1 4 からビア v 7 2 に達した配線路は、このビア v 7 2 で 2 つに分岐している。第 1 の分岐路は、図 3 2 に示すように、第 6 配線層 L 6 に設けられた配線路 c p 1 4 3 により、ビア v 7 2 から終端抵抗 R A 1 1 に接続されている。

【 0 1 4 0 】

また第 2 の分岐路は、図 2 8 に示すように、第 3 配線層 L 3 に設けられた配線路 c p 1 4 4 により、ビア v 7 2 から、制御 R O M 配置領域 1 9 2 内に配置されるビア v 1 0 6 に接続されており、ここで更に 2 つに分岐している。その 1 つ目の第 2 a の分岐路は、図 2 7 に示すように、第 1 配線層 L 1 に設けられた配線路 c p 1 4 5 により、ビア v 1 0 6 から制御 R O M 1 0 5 の端子接続部 A 1 3 に対して制御 R O M 配置領域 1 9 2 の内側から接続されている。また 2 つ目の第 2 b の分岐路は、図 2 8 , 図 2 9 に示すように、第 3 配線層 L 3 に設けられた配線路 c p 1 4 6 により、ビア v 1 0 6 から第 1 コネクタ配置領域 1 9 4 内のビア v 1 3 2 に接続され、更に図 3 3 に示すように、第 6 配線層 L 6 に設けられた配線路 c p 1 4 7 により、端子接続部 h a d 1 4 に対して第 1 コネクタ配置領域 1 9 4 の内側から接続されている。

10

【 0 1 4 1 】

配線路 P 1 6 ( 図 3 6 ) では、図 2 6 に示すように、第 1 配線層 L 1 の複合チップ配置領域 1 9 1 に設けられた端子接続部 H A D 1 5 が、配線路 c p 1 5 1 により、斜め + X - Y 方向の近傍に配置されたビア v 1 1 に接続されている。ビア v 1 1 は、その周囲に配置されている 4 つの端子接続部 ( 端子接続部 H A D 1 5 を含む ) の略中央に配置されている。このビア v 1 1 は、図 3 1 に示すように、第 4 配線層 L 4 に設けられた配線路 c p 1 5 2 により、制御 R O M 配置領域 1 9 2 内に配置されるビア v 7 1 に接続されている。

20

【 0 1 4 2 】

端子接続部 H A D 1 5 からビア v 7 1 に達した配線路は、このビア v 7 1 で 2 つに分岐している。第 1 の分岐路は、図 3 2 に示すように、第 6 配線層 L 6 に設けられた配線路 c p 1 5 3 により、ビア v 7 1 から終端抵抗 R A 1 1 に接続されている。

【 0 1 4 3 】

また第 2 の分岐路は、図 2 8 に示すように、第 3 配線層 L 3 に設けられた配線路 c p 1 5 4 により、ビア v 7 1 から、制御 R O M 配置領域 1 9 2 内に配置されるビア v 1 0 5 に接続されており、ここで更に 2 つに分岐している。その 1 つ目の第 2 a の分岐路は、図 2 7 に示すように、第 1 配線層 L 1 に設けられた配線路 c p 1 5 5 により、ビア v 1 0 5 から制御 R O M 1 0 5 の端子接続部 A 1 4 に対して制御 R O M 配置領域 1 9 2 の内側から接続されている。また 2 つ目の第 2 b の分岐路は、図 2 8 , 図 2 9 に示すように、第 3 配線層 L 3 に設けられた配線路 c p 1 5 6 により、ビア v 1 0 5 から第 1 コネクタ配置領域 1 9 4 内のビア v 1 3 1 に接続され、更に図 3 3 に示すように、第 6 配線層 L 6 に設けられた配線路 c p 1 5 7 により、端子接続部 h a d 1 5 に対して第 1 コネクタ配置領域 1 9 4 の内側から接続されている。

30

【 0 1 4 4 】

配線路 P 1 7 ( 図 3 6 ) では、図 2 6 に示すように、第 1 配線層 L 1 の複合チップ配置領域 1 9 1 に設けられた端子接続部 H A D 1 6 が、配線路 c p 1 6 1 により、斜め + X - Y 方向の近傍に配置されたビア v 1 8 に接続されている。ビア v 1 8 は、その周囲に配置されている 4 つの端子接続部 ( 端子接続部 H A D 1 6 を含む ) の略中央に配置されている。このビア v 1 8 は、図 3 1 に示すように、第 4 配線層 L 4 に設けられた配線路 c p 1 6 2 により、制御 R O M 配置領域 1 9 2 内に配置されるビア v 7 0 に接続されている。

40

【 0 1 4 5 】

端子接続部 H A D 1 6 からビア v 7 0 に達した配線路は、このビア v 7 0 で 2 つに分岐している。第 1 の分岐路は、図 3 2 に示すように、第 6 配線層 L 6 に設けられた配線路 c p 1 6 3 により、ビア v 7 0 から終端抵抗 R A 1 0 に接続されている。この終端抵抗 R A 1 0 は、他端側が所定のビアを介して第 2 配線層 L 2 のベタ配線層 ( G N D ) に接続され

50

ている（配線図では省略）。

【0146】

また第2の分岐路は、図28に示すように、第3配線層L3に設けられた配線路c p 1 6 4により、ビアv 7 0から、制御ROM配置領域192内に配置されるビアv 1 0 4に接続されており、ここで更に2つに分岐している。その1つ目の第2aの分岐路は、図27に示すように、第1配線層L1に設けられた配線路c p 1 6 5により、ビアv 1 0 4から制御ROM105の端子接続部A 1 5に対して制御ROM配置領域192の外側から接続されている。また2つ目の第2bの分岐路は、図28、図29に示すように、第3配線層L3に設けられた配線路c p 1 6 6により、ビアv 1 0 4から第1コネクタ配置領域194内のビアv 1 3 0に接続され、更に図33に示すように、第6配線層L6に設けられた配線路c p 1 6 7により、端子接続部h a d 1 6に対して第1コネクタ配置領域194の内側から接続されている。

【0147】

配線路P18（図37）では、図26に示すように、第1配線層L1の複合チップ配置領域191に設けられた端子接続部H A D 1 7が、配線路c p 1 7 1により、複合チップ配置領域191の外側、具体的には制御ROM配置領域192の+Y側に配置されたビアv 5 1に接続されている。なお、端子接続部H A D 1 7は、複合チップ配置領域191の外周側から2列目に配置されている。ビアv 5 1は、図31に示すように、第4配線層L4に設けられた配線路c p 1 7 2により、制御ROM配置領域192内に配置されるビアv 6 9に接続されている。

【0148】

端子接続部H A D 1 7からビアv 6 9に達した配線路は、このビアv 6 9で2つに分岐している。第1の分岐路は、図32に示すように、第6配線層L6に設けられた配線路c p 1 7 3により、ビアv 6 9から終端抵抗R A 1 0に接続されている。

【0149】

また第2の分岐路は、図28に示すように、第3配線層L3に設けられた配線路c p 1 7 4により、ビアv 6 9から、制御ROM配置領域192内に配置されるビアv 1 0 3に接続されており、ここで更に2つに分岐している。その1つ目の第2aの分岐路は、図27に示すように、第1配線層L1に設けられた配線路c p 1 7 5により、ビアv 1 0 3から制御ROM105の端子接続部A 1 6に対して制御ROM配置領域192の外側から接続されている。また2つ目の第2bの分岐路は、図28、図29に示すように、第3配線層L3に設けられた配線路c p 1 7 6により、ビアv 1 0 3から第1コネクタ配置領域194内のビアv 1 2 9に接続され、更に図33に示すように、第6配線層L6に設けられた配線路c p 1 7 7により、端子接続部h a d 1 7に対して第1コネクタ配置領域194の内側から接続されている。

【0150】

配線路P19（図37）では、図26に示すように、第1配線層L1の複合チップ配置領域191に設けられた端子接続部H A D 1 8が、配線路c p 1 8 1により、複合チップ配置領域191の外側、具体的には制御ROM配置領域192の+Y側に配置されたビアv 5 2に接続されている。なお、端子接続部H A D 1 8は、複合チップ配置領域191の最も外周側に配置されている。ビアv 5 2は、図31に示すように、第4配線層L4に設けられた配線路c p 1 8 2により、制御ROM配置領域192内に配置されるビアv 6 8に接続されている。

【0151】

端子接続部H A D 1 8からビアv 6 8に達した配線路は、このビアv 6 8で3つに分岐している。第1の分岐路は、図27に示すように、第1配線層L1に設けられた配線路c p 1 8 3により、ビアv 6 8から制御ROM105の端子接続部A 1 7に対して制御ROM配置領域192の内側から接続されている。また第2の分岐路は、図32に示すように、第6配線層L6に設けられた配線路c p 1 8 4により、ビアv 6 8から終端抵抗R A 1 0に接続されている。

10

20

30

40

50

## 【0152】

また第3の分岐路は、図28、図29に示すように、第3配線層L3に設けられた配線路c p 185により、ビアv 68から第1コネクタ配置領域194内のビアv 128に接続され、更に図33に示すように、第6配線層L6に設けられた配線路c p 186により、端子接続部h a d 18に対して第1コネクタ配置領域194の内側から接続されている。

## 【0153】

配線路P20(図37)では、図26に示すように、第1配線層L1の複合チップ配置領域191に設けられた端子接続部H A D 19が、配線路c p 191により、斜め+X-Y方向の近傍に配置されたビアv 1に接続されている。ビアv 1は、その周囲に配置されている4つの端子接続部(端子接続部H A D 19を含む)の略中央に配置されている。このビアv 1は、図31に示すように、第4配線層L4に設けられた配線路c p 192により、制御ROM配置領域192内に配置されるビアv 67に接続されている。

10

## 【0154】

端子接続部H A D 19からビアv 67に達した配線路は、このビアv 67で3つに分岐している。第1の分岐路は、図27に示すように、第1配線層L1に設けられた配線路c p 193により、ビアv 67から制御ROM105の端子接続部A 18に対して制御ROM配置領域192の内側から接続されている。また第2の分岐路は、図32に示すように、第6配線層L6に設けられた配線路c p 194により、ビアv 67から終端抵抗RA10に接続されている。

20

## 【0155】

また第3の分岐路は、図28、図29に示すように、第3配線層L3に設けられた配線路c p 195により、ビアv 67から第1コネクタ配置領域194内のビアv 127に接続され、更に図33に示すように、第6配線層L6に設けられた配線路c p 196により、端子接続部h a d 19に対して第1コネクタ配置領域194の内側から接続されている。

## 【0156】

配線路P21(図37)では、図26に示すように、第1配線層L1の複合チップ配置領域191に設けられた端子接続部H A D 20が、配線路c p 201により、斜め+X-Y方向の近傍に配置されたビアv 10に接続されている。ビアv 10は、その周囲に配置されている4つの端子接続部(端子接続部H A D 20を含む)の略中央に配置されている。このビアv 10は、図31に示すように、第4配線層L4に設けられた配線路c p 202により、制御ROM配置領域192内に配置されるビアv 66に接続されている。

30

## 【0157】

端子接続部H A D 20からビアv 66に達した配線路は、このビアv 66で3つに分岐している。第1の分岐路は、図27に示すように、第1配線層L1に設けられた配線路c p 203により、ビアv 66から制御ROM105の端子接続部A 19に対して制御ROM配置領域192の内側から接続されている。また第2の分岐路は、図32に示すように、第6配線層L6に設けられた配線路c p 204により、ビアv 66から終端抵抗RA9に接続されている。この終端抵抗RA9は、他端側が所定のビアを介して第2配線層L2のベタ配線層(GND)に接続されている(配線図では省略)。

40

## 【0158】

また第3の分岐路は、図28、図29に示すように、第3配線層L3に設けられた配線路c p 205により、ビアv 66から第1コネクタ配置領域194内のビアv 126に接続され、更に図33に示すように、第6配線層L6に設けられた配線路c p 206により、端子接続部h a d 20に対して第1コネクタ配置領域194の内側から接続されている。

## 【0159】

配線路P22(図37)では、図26、図27に示すように、第1配線層L1の複合チップ配置領域191に設けられた端子接続部H A D 21が、配線路c p 211により、複合チップ配置領域191の外側、具体的には制御ROM配置領域192の+Y側に配置されたビアv 54に接続されている。なお、端子接続部H A D 21は、複合チップ配置領域191の最も外周側に配置されている。ビアv 54は、図31に示すように、第4配線層

50

L 4 に設けられた配線路 c p 2 1 2 により、制御 R O M 配置領域 1 9 2 内に配置されるビア v 6 5 に接続されている。

【 0 1 6 0 】

端子接続部 H A D 2 1 からビア v 6 5 に達した配線路は、このビア v 6 5 で 3 つに分岐している。第 1 の分岐路は、図 2 7 に示すように、第 1 配線層 L 1 に設けられた配線路 c p 2 1 3 により、ビア v 6 5 から制御 R O M 1 0 5 の端子接続部 A 2 0 に対して制御 R O M 配置領域 1 9 2 の内側から接続されている。また第 2 の分岐路は、図 3 2 に示すように、第 6 配線層 L 6 に設けられた配線路 c p 2 1 4 により、ビア v 6 5 から終端抵抗 R A 9 に接続されている。

【 0 1 6 1 】

また第 3 の分岐路は、図 2 8 , 図 2 9 に示すように、第 3 配線層 L 3 に設けられた配線路 c p 2 1 5 により、ビア v 6 5 から第 1 コネクタ配置領域 1 9 4 内のビア v 1 2 5 に接続され、更に図 3 3 に示すように、第 6 配線層 L 6 に設けられた配線路 c p 2 1 6 により、端子接続部 h a d 2 1 に対して第 1 コネクタ配置領域 1 9 4 の内側から接続されている。

【 0 1 6 2 】

配線路 P 2 3 ( 図 3 7 ) では、図 2 6 , 図 2 7 に示すように、第 1 配線層 L 1 の複合チップ配置領域 1 9 1 に設けられた端子接続部 H A D 2 2 が、配線路 c p 2 2 1 により、複合チップ配置領域 1 9 1 の外側、具体的には制御 R O M 配置領域 1 9 2 の + Y 側に配置されたビア v 5 3 に接続されている。なお、端子接続部 H A D 2 2 は、複合チップ配置領域 1 9 1 の外周側から 2 列目に配置されている。ビア v 5 3 は、図 3 1 に示すように、第 4 配線層 L 4 に設けられた配線路 c p 2 2 2 により、制御 R O M 配置領域 1 9 2 内に配置されるビア v 6 4 に接続されている。

【 0 1 6 3 】

端子接続部 H A D 2 2 からビア v 6 4 に達した配線路は、このビア v 6 4 で 3 つに分岐している。第 1 の分岐路は、図 2 7 に示すように、第 1 配線層 L 1 に設けられた配線路 c p 2 2 3 により、ビア v 6 4 から制御 R O M 1 0 5 の端子接続部 A 2 1 に対して制御 R O M 配置領域 1 9 2 の内側から接続されている。また第 2 の分岐路は、図 3 2 に示すように、第 6 配線層 L 6 に設けられた配線路 c p 2 2 4 により、ビア v 6 4 から終端抵抗 R A 9 に接続されている。

【 0 1 6 4 】

また第 3 の分岐路は、図 2 8 , 図 2 9 に示すように、第 3 配線層 L 3 に設けられた配線路 c p 2 2 5 により、ビア v 6 4 から第 1 コネクタ配置領域 1 9 4 内のビア v 1 2 4 に接続され、更に図 3 3 に示すように、第 6 配線層 L 6 に設けられた配線路 c p 2 2 6 により、端子接続部 h a d 2 2 に対して第 1 コネクタ配置領域 1 9 4 の内側から接続されている。

【 0 1 6 5 】

配線路 P 2 4 ( 図 3 7 ) では、図 2 6 に示すように、第 1 配線層 L 1 の複合チップ配置領域 1 9 1 に設けられた端子接続部 H A D 2 3 が、配線路 c p 2 3 1 により、斜め + X + Y 方向の近傍に配置されたビア v 2 1 に接続されている。ビア v 2 1 は、その周囲に配置されている 4 つの端子接続部 ( 端子接続部 H A D 2 3 を含む ) の略中央に配置されている。このビア v 2 1 は、図 3 1 に示すように、第 4 配線層 L 4 に設けられた配線路 c p 2 3 2 により、複合チップ配置領域 1 9 1 の外側、具体的には複合チップ配置領域 1 9 1 と制御 R O M 配置領域 1 9 2 との間に配置されたビア v 3 6 に接続され、更に図 2 6 , 図 2 7 に示すように、第 1 配線層 L 1 に設けられた配線路 c p 2 3 3 により、制御 R O M 配置領域 1 9 2 内に配置されるビア v 6 3 に接続されている。

【 0 1 6 6 】

端子接続部 H A D 2 3 からビア v 6 3 に達した配線路は、このビア v 6 3 で 3 つに分岐している。第 1 の分岐路は、図 2 7 に示すように、第 1 配線層 L 1 に設けられた配線路 c p 2 3 4 により、ビア v 6 3 から制御 R O M 1 0 5 の端子接続部 A 2 2 に対して制御 R O M 配置領域 1 9 2 の外側から接続されている。また第 2 の分岐路は、図 3 2 に示すように、第 6 配線層 L 6 に設けられた配線路 c p 2 3 5 により、ビア v 6 3 から終端抵抗 R A 9

10

20

30

40

50

に接続されている。

【 0 1 6 7 】

また第3の分岐路は、図28、図29に示すように、第3配線層L3に設けられた配線路c p 2 3 6により、ビアv 6 3から第1コネクタ配置領域1 9 4内のビアv 1 2 3に接続され、更に図33に示すように、第6配線層L6に設けられた配線路c p 2 3 7により、端子接続部h a d 2 3に対して第1コネクタ配置領域1 9 4の内側から接続されている。

【 0 1 6 8 】

配線路P 2 5(図37)では、図26に示すように、第1配線層L1の複合チップ配置領域1 9 1に設けられた端子接続部H A D 2 4が、配線路c p 2 4 1により、斜め+X+Y方向の近傍に配置されたビアv 1 4に接続されている。ビアv 1 4は、その周囲に配置されている4つの端子接続部(端子接続部H A D 2 4を含む)の略中央に配置されている。このビアv 1 4は、図31に示すように、第4配線層L4に設けられた配線路c p 2 4 2により、複合チップ配置領域1 9 1の外側、具体的には複合チップ配置領域1 9 1と制御ROM配置領域1 9 2との間に配置されたビアv 3 5に接続され、更に図26、図27に示すように、第1配線層L1に設けられた配線路c p 2 4 3により、制御ROM配置領域1 9 2内に配置されるビアv 6 2に接続されている。

【 0 1 6 9 】

端子接続部H A D 2 4からビアv 6 2に達した配線路は、このビアv 6 2で4つに分岐している。第1の分岐路は、図27に示すように、第1配線層L1に設けられた配線路c p 2 4 4により、ビアv 6 2から制御ROM1 0 5の端子接続部A 2 3に対して制御ROM配置領域1 9 2の外側から接続されている。また第2の分岐路は、図32に示すように、第6配線層L6に設けられた配線路c p 2 4 5により、ビアv 6 2から終端抵抗R 4 5に接続されている。この終端抵抗R 4 5は、他端側が所定のビアを介して第2配線層L2のベタ配線層(G N D)に接続されている(配線図では省略)。

【 0 1 7 0 】

また第3の分岐路は、図28、図29に示すように、第3配線層L3に設けられた配線路c p 2 4 6により、ビアv 6 2から第1コネクタ配置領域1 9 4内のビアv 1 2 2に接続され、更に図33に示すように、第6配線層L6に設けられた配線路c p 2 4 7により、端子接続部h a d 2 4に対して第1コネクタ配置領域1 9 4の内側から接続されている。また第4の分岐路は、図28、図30に示すように、第3配線層L3に設けられた配線路c p 2 4 8により、ビアv 6 2からビアv 1 8 3に接続され、更に図34に示すように、第6配線層L6に設けられた配線路c p 2 4 9により、デコード回路を構成するデコーダI C 1 2に接続されている。

【 0 1 7 1 】

配線路P 2 6(図37)では、図26に示すように、第1配線層L1の複合チップ配置領域1 9 1に設けられた端子接続部H A D 2 5が、配線路c p 2 5 1により、斜め+X+Y方向の近傍に配置されたビアv 6に接続されている。ビアv 6は、その周囲に配置されている4つの端子接続部(端子接続部H A D 2 5を含む)の略中央に配置されている。このビアv 6は、図31に示すように、第4配線層L4に設けられた配線路c p 2 5 2により、複合チップ配置領域1 9 1の外側、具体的には複合チップ配置領域1 9 1と制御ROM配置領域1 9 2との間に配置されたビアv 4 0に接続され、更に図26、図27に示すように、第1配線層L1に設けられた配線路c p 2 5 3により、制御ROM配置領域1 9 2内に配置されるビアv 6 1に接続されている。

【 0 1 7 2 】

端子接続部H A D 2 5からビアv 6 1に達した配線路は、このビアv 6 1で3つに分岐している。第1の分岐路は、図27に示すように、第1配線層L1に設けられた配線路c p 2 5 4により、ビアv 6 1から制御ROM1 0 5の端子接続部A 2 4に対して制御ROM配置領域1 9 2の外側から接続されている。また第2の分岐路は、図32に示すように、第6配線層L6に設けられた配線路c p 2 5 5により、ビアv 6 1から終端抵抗R 4 4に接続されている。この終端抵抗R 4 4は、他端側が所定のビアを介して第2配線層L2

10

20

30

40

50

のベタ配線層 ( G N D ) に接続されている ( 配線図では省略 ) 。

【 0 1 7 3 】

また第 3 の分岐路は、図 2 8 , 図 2 9 に示すように、第 3 配線層 L 3 に設けられた配線路 c p 2 5 6 により、ビア v 6 1 から第 1 コネクタ配置領域 1 9 4 内のビア v 1 2 1 に接続され、更に図 3 3 に示すように、第 6 配線層 L 6 に設けられた配線路 c p 2 5 7 により、端子接続部 h a d 2 5 に対して第 1 コネクタ配置領域 1 9 4 の内側から接続されている。

【 0 1 7 4 】

続いて、複合チップ 1 0 4 のデータ入出力端子 H D T 0 ~ H D T 1 5 に接続される配線路 P 2 7 ~ P 4 2 について説明する。データ入出力端子 H D T 0 ~ H D T 1 5 は、制御 R O M 1 0 5 側のデータ入出力端子 Q 0 ~ Q 1 5 に夫々接続されるとともに、液晶制御第 1 コネクタ C N 3 1 にも接続されている。

10

【 0 1 7 5 】

なお、複合チップ 1 0 4 のデータ入出力端子 H D T 0 ~ H D T 1 5 の配列 ( 図 1 8 ) と、それに対応する制御 R O M 1 0 5 のデータ入出力端子 Q 0 ~ Q 1 5 の配列 ( 図 1 9 ) とを比較すると、両者は明らかに相違している。即ち、複合チップ 1 0 4 のデータ入出力端子 H D T 0 ~ H D T 1 5 は、図 1 8 に示すように 4 行に分けて配列されており、行毎に列数は異なるが並び順は一定しているのに対し、制御 R O M 1 0 5 のデータ入出力端子 Q 0 ~ Q 1 5 は、図 1 9 に示すように 2 列に分けて配列されており、各列における並び順に一定の規則性はない。しかも、複合チップ 1 0 4 と制御 R O M 1 0 5 の配置位置や配線パターンの数の多さが関係してくることで、配線パターンの引き回しが非常に複雑なものとなる。そのため、複合チップ 1 0 4 と制御 R O M 1 0 5 とを接続する配線パターンの引き回しを最適化することは非常に重要であり、それによって配線パターンの線長を短くすることができ、ノイズ低減や基板全体のスリム化を図ることにつながる。また、これらは複合チップ 1 0 4 と制御 R O M 1 0 5 との間の関係だけでなく、複合チップ 1 0 4 と各種コネクタ等の電子部品との関係性においても同様のことが言える。特に、 H A D 1 ~ H A D 2 5 や H D T 1 ~ H D T 2 5 などの複合チップ 1 0 4 や制御 R O M 1 0 5 、各種コネクタなどの複数の電子部品と接続される配線パターンについては、上述の課題が大きい分、最適化することによる効果も大きいものとなる。

20

【 0 1 7 6 】

配線路 P 2 7 ~ P 4 2 のうち、配線路 P 2 7 ( 図 3 8 ) では、図 2 6 に示すように、第 1 配線層 L 1 の複合チップ配置領域 1 9 1 に設けられた端子接続部 H D T 0 が、配線路 c p 3 0 1 により、複合チップ配置領域 1 9 1 の外側、具体的には複合チップ配置領域 1 9 1 と制御 R O M 配置領域 1 9 2 との間に配置されたビア v 3 2 に接続されている。なお、端子接続部 H D T 0 は、複合チップ配置領域 1 9 1 の最も外周側に配置されている。ビア v 3 2 は、図 3 1 に示すように、第 4 配線層 L 4 に設けられた配線路 c p 3 0 2 により、制御 R O M 配置領域 1 9 2 内に配置されるビア v 1 0 2 に接続されている。

30

【 0 1 7 7 】

端子接続部 H D T 0 からビア v 1 0 2 に達した配線路は、このビア v 1 0 2 で 4 つに分岐している。第 1 の分岐路は、図 2 7 に示すように、第 1 配線層 L 1 に設けられた配線路 c p 3 0 3 により、ビア v 1 0 2 から制御 R O M 1 0 5 の端子接続部 Q 0 に対して制御 R O M 配置領域 1 9 2 の外側から接続されている。また第 2 の分岐路は、図 3 2 に示すように、第 6 配線層 L 6 に設けられた配線路 c p 3 0 4 により、ビア v 1 0 2 から終端抵抗 R A 3 4 に接続されている。この終端抵抗 R A 3 4 は、他端側が所定のビアを介して第 2 配線層 L 2 のベタ配線層 ( G N D ) に接続されている ( 配線図では省略 ) 。

40

【 0 1 7 8 】

また第 3 の分岐路は、図 2 8 , 図 2 9 に示すように、第 3 配線層 L 3 に設けられた配線路 c p 3 0 5 により、ビア v 1 0 2 から第 1 コネクタ配置領域 1 9 4 内のビア v 1 6 2 に接続され、更に図 3 3 に示すように、第 6 配線層 L 6 に設けられた配線路 c p 3 0 6 により、端子接続部 h d t 0 に対して第 1 コネクタ配置領域 1 9 4 の内側から接続されている。また第 4 の分岐路は、図 2 8 , 図 3 0 に示すように、第 3 配線層 L 3 に設けられた配線

50

路 c p 3 0 7 により、ビア v 1 0 2 からビア v 1 9 7 に接続され、更に図 3 4 に示すように、第 6 配線層 L 6 に設けられた配線路 c p 3 0 8 により、デコード回路を構成するデコーダ I C 1 3 に接続されている。

【 0 1 7 9 】

配線路 P 2 8 ( 図 3 8 ) では、図 2 6 に示すように、第 1 配線層 L 1 の複合チップ配置領域 1 9 1 に設けられた端子接続部 H D T 1 が、配線路 c p 3 1 1 により、複合チップ配置領域 1 9 1 の外側、具体的には複合チップ配置領域 1 9 1 と制御 R O M 配置領域 1 9 2 との間に配置されたビア v 3 1 に接続されている。なお、端子接続部 H D T 1 は、複合チップ配置領域 1 9 1 の外周側から 2 列目に配置されている。ビア v 3 1 は、図 3 1 に示すように、第 4 配線層 L 4 に設けられた配線路 c p 3 1 2 により、制御 R O M 配置領域 1 9 2 内に配置されるビア v 1 0 1 に接続されている。10

【 0 1 8 0 】

端子接続部 H D T 1 からビア v 1 0 1 に達した配線路は、このビア v 1 0 1 で 4 つに分岐している。第 1 の分岐路は、図 2 7 に示すように、第 1 配線層 L 1 に設けられた配線路 c p 3 1 3 により、ビア v 1 0 1 から制御 R O M 1 0 5 の端子接続部 Q 1 に対して制御 R O M 配置領域 1 9 2 の外側から接続されている。また第 2 の分岐路は、図 3 2 に示すように、第 6 配線層 L 6 に設けられた配線路 c p 3 1 4 により、ビア v 1 0 1 から終端抵抗 R A 3 4 に接続されている。

【 0 1 8 1 】

また第 3 の分岐路は、図 2 8 , 図 2 9 に示すように、第 3 配線層 L 3 に設けられた配線路 c p 3 1 5 により、ビア v 1 0 1 から第 1 コネクタ配置領域 1 9 4 内のビア v 1 6 1 に接続され、更に図 3 3 に示すように、第 6 配線層 L 6 に設けられた配線路 c p 3 1 6 により、端子接続部 h d t 1 に対して第 1 コネクタ配置領域 1 9 4 の内側から接続されている。また第 4 の分岐路は、図 2 8 , 図 3 0 に示すように、第 3 配線層 L 3 に設けられた配線路 c p 3 1 7 により、ビア v 1 0 1 からビア v 1 9 8 に接続され、更に図 3 4 に示すように、第 6 配線層 L 6 に設けられた配線路 c p 3 1 8 により、デコード回路を構成するデコーダ I C 1 3 に接続されている。20

【 0 1 8 2 】

配線路 P 2 9 ( 図 3 8 ) では、図 2 6 に示すように、第 1 配線層 L 1 の複合チップ配置領域 1 9 1 に設けられた端子接続部 H D T 2 が、配線路 c p 3 2 1 により、斜め + X + Y 方向の近傍に配置されたビア v 2 4 に接続されている。ビア v 2 4 は、その周囲に配置されている 4 つの端子接続部 ( 端子接続部 H D T 2 を含む ) の略中央に配置されている。このビア v 2 4 は、図 3 1 に示すように、第 4 配線層 L 4 に設けられた配線路 c p 3 2 2 により、制御 R O M 配置領域 1 9 2 内に配置されるビア v 1 0 0 に接続されている。30

【 0 1 8 3 】

端子接続部 H D T 2 からビア v 1 0 0 に達した配線路は、このビア v 1 0 0 で 4 つに分岐している。第 1 の分岐路は、図 2 7 に示すように、第 1 配線層 L 1 に設けられた配線路 c p 3 2 3 により、ビア v 1 0 0 から制御 R O M 1 0 5 の端子接続部 Q 2 に対して制御 R O M 配置領域 1 9 2 の外側から接続されている。また第 2 の分岐路は、図 3 2 に示すように、第 6 配線層 L 6 に設けられた配線路 c p 3 2 4 により、ビア v 1 0 0 から終端抵抗 R A 3 4 に接続されている。40

【 0 1 8 4 】

また第 3 の分岐路は、図 2 8 , 図 2 9 に示すように、第 3 配線層 L 3 に設けられた配線路 c p 3 2 5 により、ビア v 1 0 0 から第 1 コネクタ配置領域 1 9 4 内のビア v 1 6 0 に接続され、更に図 3 3 に示すように、第 6 配線層 L 6 に設けられた配線路 c p 3 2 6 により、端子接続部 h d t 2 に対して第 1 コネクタ配置領域 1 9 4 の内側から接続されている。また第 4 の分岐路は、図 2 8 , 図 3 0 に示すように、第 3 配線層 L 3 に設けられた配線路 c p 3 2 7 により、ビア v 1 0 0 からビア v 1 9 9 に接続され、更に図 3 4 に示すように、第 6 配線層 L 6 に設けられた配線路 c p 3 2 8 により、デコード回路を構成するデコーダ I C 1 3 に接続されている。50

## 【0185】

配線路 P 3 0 (図 3 8) では、図 2 6 に示すように、第 1 配線層 L 1 の複合チップ配置領域 1 9 1 に設けられた端子接続部 H D T 3 が、配線路 c p 3 3 1 により、斜め - X - Y 方向の近傍に配置されたビア v 8 に接続されている。ビア v 8 は、その周囲に配置されている 4 つの端子接続部 (端子接続部 H D T 3 を含む) の略中央に配置されている。このビア v 8 は、図 3 1 に示すように、第 4 配線層 L 4 に設けられた配線路 c p 3 3 2 により、制御 R O M 配置領域 1 9 2 内に配置されるビア v 9 9 に接続されている。

## 【0186】

端子接続部 H D T 3 からビア v 9 9 に達した配線路は、このビア v 9 9 で 4 つに分岐している。第 1 の分岐路は、図 2 7 に示すように、第 1 配線層 L 1 に設けられた配線路 c p 3 3 3 により、ビア v 9 9 から制御 R O M 1 0 5 の端子接続部 Q 3 に対して制御 R O M 配置領域 1 9 2 の外側から接続されている。また第 2 の分岐路は、図 3 2 に示すように、第 6 配線層 L 6 に設けられた配線路 c p 3 3 4 により、ビア v 9 9 から終端抵抗 R A 3 4 に接続されている。

10

## 【0187】

また第 3 の分岐路は、図 2 8 , 図 2 9 に示すように、第 3 配線層 L 3 に設けられた配線路 c p 3 3 5 により、ビア v 9 9 から第 1 コネクタ配置領域 1 9 4 内のビア v 1 5 9 に接続され、更に図 3 3 に示すように、第 6 配線層 L 6 に設けられた配線路 c p 3 3 6 により、端子接続部 h d t 3 に対して第 1 コネクタ配置領域 1 9 4 の内側から接続されている。また第 4 の分岐路は、図 2 8 , 図 3 0 に示すように、第 3 配線層 L 3 に設けられた配線路 c p 3 3 7 により、ビア v 9 9 からビア v 2 0 0 に接続され、更に図 3 4 に示すように、第 6 配線層 L 6 に設けられた配線路 c p 3 3 8 により、デコード回路を構成するデコーダ I C 1 3 に接続されている。

20

## 【0188】

配線路 P 3 1 (図 3 8) では、図 2 6 に示すように、第 1 配線層 L 1 の複合チップ配置領域 1 9 1 に設けられた端子接続部 H D T 4 が、配線路 c p 3 4 1 により、複合チップ配置領域 1 9 1 の外側、具体的には複合チップ配置領域 1 9 1 と制御 R O M 配置領域 1 9 2 との間に配置されたビア v 3 7 に接続されている。なお、端子接続部 H D T 4 は、複合チップ配置領域 1 9 1 の最も外周側に配置されている。ビア v 3 7 は、図 3 1 に示すように、第 4 配線層 L 4 に設けられた配線路 c p 3 4 2 により、制御 R O M 配置領域 1 9 2 内に配置されるビア v 9 8 に接続されている。

30

## 【0189】

端子接続部 H D T 4 からビア v 9 8 に達した配線路は、このビア v 9 8 で 4 つに分岐している。第 1 の分岐路は、図 2 7 に示すように、第 1 配線層 L 1 に設けられた配線路 c p 3 4 3 により、ビア v 9 8 から制御 R O M 1 0 5 の端子接続部 Q 4 に対して制御 R O M 配置領域 1 9 2 の外側から接続されている。また第 2 の分岐路は、図 3 2 に示すように、第 6 配線層 L 6 に設けられた配線路 c p 3 4 4 により、ビア v 9 8 から終端抵抗 R A 3 2 に接続されている。この終端抵抗 R A 3 2 は、他端側が所定のビアを介して第 2 配線層 L 2 のベタ配線層 (G N D) に接続されている (配線図では省略)。

40

## 【0190】

また第 3 の分岐路は、図 2 8 , 図 2 9 に示すように、第 3 配線層 L 3 に設けられた配線路 c p 3 4 5 により、ビア v 9 8 から第 1 コネクタ配置領域 1 9 4 内のビア v 1 5 8 に接続され、更に図 3 3 に示すように、第 6 配線層 L 6 に設けられた配線路 c p 3 4 6 により、端子接続部 h d t 4 に対して第 1 コネクタ配置領域 1 9 4 の内側から接続されている。また第 4 の分岐路は、図 2 8 , 図 3 0 に示すように、第 3 配線層 L 3 に設けられた配線路 c p 3 4 7 により、ビア v 9 8 からビア v 1 8 9 に接続され、更に図 3 4 に示すように、第 6 配線層 L 6 に設けられた配線路 c p 3 4 8 により、デコード回路を構成するデコーダ I C 1 3 に接続されている。

## 【0191】

配線路 P 3 2 (図 3 8) では、図 2 6 に示すように、第 1 配線層 L 1 の複合チップ配置

50

領域 191 に設けられた端子接続部 HDT5 が、配線路 c p 351 により、複合チップ配置領域 191 の外側、具体的には複合チップ配置領域 191 と制御 ROM 配置領域 192 との間に配置されたビア v 46 に接続されている。なお、端子接続部 HDT5 は、複合チップ配置領域 191 の外周側から 2 列目に配置されている。ビア v 46 は、図 31 に示すように、第 4 配線層 L4 に設けられた配線路 c p 352 により、制御 ROM 配置領域 192 内に配置されるビア v 97 に接続されている。

#### 【0192】

端子接続部 HDT5 からビア v 97 に達した配線路は、このビア v 97 で 4 つに分岐している。第 1 の分岐路は、図 27 に示すように、第 1 配線層 L1 に設けられた配線路 c p 353 により、ビア v 97 から制御 ROM 105 の端子接続部 Q5 に対して制御 ROM 配置領域 192 の外側から接続されている。また第 2 の分岐路は、図 32 に示すように、第 6 配線層 L6 に設けられた配線路 c p 354 により、ビア v 97 から終端抵抗 RA32 に接続されている。

10

#### 【0193】

また第 3 の分岐路は、図 28, 図 29 に示すように、第 3 配線層 L3 に設けられた配線路 c p 355 により、ビア v 97 から第 1 コネクタ配置領域 194 内のビア v 157 に接続され、更に図 33 に示すように、第 6 配線層 L6 に設けられた配線路 c p 356 により、端子接続部 hdt5 に対して第 1 コネクタ配置領域 194 の内側から接続されている。また第 4 の分岐路は、図 28, 図 30 に示すように、第 3 配線層 L3 に設けられた配線路 c p 357 により、ビア v 97 からビア v 190 に接続され、更に図 34 に示すように、第 6 配線層 L6 に設けられた配線路 c p 358 により、デコード回路を構成するデコーダ IC13 に接続されている。

20

#### 【0194】

配線路 P33 (図 38) では、図 26 に示すように、第 1 配線層 L1 の複合チップ配置領域 191 に設けられた端子接続部 HDT6 が、配線路 c p 361 により、斜め +X+Y 方向の近傍に配置されたビア v 17 に接続されている。ビア v 17 は、その周囲に配置されている 4 つの端子接続部 (端子接続部 HDT6 を含む) の略中央に配置されている。このビア v 17 は、図 31 に示すように、第 4 配線層 L4 に設けられた配線路 c p 362 により、制御 ROM 配置領域 192 内に配置されるビア v 96 に接続されている。

30

#### 【0195】

端子接続部 HDT6 からビア v 96 に達した配線路は、このビア v 96 で 4 つに分岐している。第 1 の分岐路は、図 27 に示すように、第 1 配線層 L1 に設けられた配線路 c p 363 により、ビア v 96 から制御 ROM 105 の端子接続部 Q6 に対して制御 ROM 配置領域 192 の外側から接続されている。また第 2 の分岐路は、図 32 に示すように、第 6 配線層 L6 に設けられた配線路 c p 364 により、ビア v 96 から終端抵抗 RA32 に接続されている。

#### 【0196】

また第 3 の分岐路は、図 28, 図 29 に示すように、第 3 配線層 L3 に設けられた配線路 c p 365 により、ビア v 96 から第 1 コネクタ配置領域 194 内のビア v 156 に接続され、更に図 33 に示すように、第 6 配線層 L6 に設けられた配線路 c p 366 により、端子接続部 hdt6 に対して第 1 コネクタ配置領域 194 の内側から接続されている。また第 4 の分岐路は、図 28, 図 30 に示すように、第 3 配線層 L3 に設けられた配線路 c p 367 により、ビア v 96 からビア v 195 に接続され、更に図 34 に示すように、第 6 配線層 L6 に設けられた配線路 c p 368 により、デコード回路を構成するデコーダ IC13 に接続されている。

40

#### 【0197】

配線路 P34 (図 38) では、図 26 に示すように、第 1 配線層 L1 の複合チップ配置領域 191 に設けられた端子接続部 HDT7 が、配線路 c p 371 により、複合チップ配置領域 191 の外側、具体的には複合チップ配置領域 191 と制御 ROM 配置領域 192 との間に配置されたビア v 45 に接続されている。なお、端子接続部 HDT7 は、複合チ

50

ツップ配置領域 191 の最も外周側に配置されている。ビア v45 は、図 31 に示すように、第4配線層 L4 に設けられた配線路 c p372 により、制御 ROM 配置領域 192 内に配置されるビア v95 に接続されている。

#### 【0198】

端子接続部 HDT7 からビア v95 に達した配線路は、このビア v95 で4つに分岐している。第1の分岐路は、図 27 に示すように、第1配線層 L1 に設けられた配線路 c p373 により、ビア v95 から制御 ROM 105 の端子接続部 Q7 に対して制御 ROM 配置領域 192 の外側から接続されている。また第2の分岐路は、図 32 に示すように、第6配線層 L6 に設けられた配線路 c p374 により、ビア v95 から終端抵抗 RA32 に接続されている。

10

#### 【0199】

また第3の分岐路は、図 28, 図 29 に示すように、第3配線層 L3 に設けられた配線路 c p375 により、ビア v95 から第1コネクタ配置領域 194 内のビア v155 に接続され、更に図 33 に示すように、第6配線層 L6 に設けられた配線路 c p376 により、端子接続部 hdt7 に対して第1コネクタ配置領域 194 の内側から接続されている。また第4の分岐路は、図 28, 図 30 に示すように、第3配線層 L3 に設けられた配線路 c p377 により、ビア v95 からビア v196 に接続され、更に図 34 に示すように、第6配線層 L6 に設けられた配線路 c p378 により、デコード回路を構成するデコーダ I C13 に接続されている。

#### 【0200】

配線路 P35 (図 39) では、図 26 に示すように、第1配線層 L1 の複合チップ配置領域 191 に設けられた端子接続部 HDT8 が、配線路 c p381 により、複合チップ配置領域 191 の外側、具体的には複合チップ配置領域 191 と制御 ROM 配置領域 192 との間に配置されたビア v44 に接続されている。なお、端子接続部 HDT8 は、複合チップ配置領域 191 の外周側から2列目に配置されている。ビア v44 は、図 31 に示すように、第4配線層 L4 に設けられた配線路 c p382 により、制御 ROM 配置領域 192 内に配置されるビア v94 に接続されている。

20

#### 【0201】

端子接続部 HDT8 からビア v94 に達した配線路は、このビア v94 で4つに分岐している。第1の分岐路は、図 27 に示すように、第1配線層 L1 に設けられた配線路 c p383 により、ビア v94 から制御 ROM 105 の端子接続部 Q8 に対して制御 ROM 配置領域 192 の内側から接続されている。また第2の分岐路は、図 32 に示すように、第6配線層 L6 に設けられた配線路 c p384 により、ビア v94 から終端抵抗 RA30 に接続されている。この終端抵抗 RA30 は、他端側が所定のビアを介して第2配線層 L2 のベタ配線層 (GND) に接続されている (配線図では省略)。

30

#### 【0202】

また第3の分岐路は、図 28, 図 29 に示すように、第3配線層 L3 に設けられた配線路 c p385 により、ビア v94 から第1コネクタ配置領域 194 内のビア v154 に接続され、更に図 33 に示すように、第6配線層 L6 に設けられた配線路 c p386 により、端子接続部 hdt8 に対して第1コネクタ配置領域 194 の内側から接続されている。また第4の分岐路は、図 28, 図 30 に示すように、第3配線層 L3 に設けられた配線路 c p387 により、ビア v94 からビア v191 に接続され、更に図 34 に示すように、第6配線層 L6 に設けられた配線路 c p388 により、デコード回路を構成するデコーダ I C14 に接続されている。

40

#### 【0203】

配線路 P36 (図 39) では、図 26 に示すように、第1配線層 L1 の複合チップ配置領域 191 に設けられた端子接続部 HDT9 が、配線路 c p391 により、斜め + X + Y 方向の近傍に配置されたビア v23 に接続されている。ビア v23 は、その周囲に配置されている4つの端子接続部 (端子接続部 HDT9 を含む) の略中央に配置されている。このビア v23 は、図 31 に示すように、第4配線層 L4 に設けられた配線路 c p392 に

50

より、制御 ROM 配置領域 192 内に配置されるビア v93 に接続されている。

【0204】

端子接続部 HDT9 からビア v93 に達した配線路は、このビア v93 で 4 つに分岐している。第 1 の分岐路は、図 27 に示すように、第 1 配線層 L1 に設けられた配線路 c p 393 により、ビア v93 から制御 ROM105 の端子接続部 Q9 に対して制御 ROM 配置領域 192 の内側から接続されている。また第 2 の分岐路は、図 32 に示すように、第 6 配線層 L6 に設けられた配線路 c p 394 により、ビア v93 から終端抵抗 RA30 に接続されている。

【0205】

また第 3 の分岐路は、図 28, 図 29 に示すように、第 3 配線層 L3 に設けられた配線路 c p 395 により、ビア v93 から第 1 コネクタ配置領域 194 内のビア v153 に接続され、更に図 33 に示すように、第 6 配線層 L6 に設けられた配線路 c p 396 により、端子接続部 hdt9 に対して第 1 コネクタ配置領域 194 の内側から接続されている。また第 4 の分岐路は、図 28, 図 30 に示すように、第 3 配線層 L3 に設けられた配線路 c p 397 により、ビア v93 からビア v192 に接続され、更に図 34 に示すように、第 6 配線層 L6 に設けられた配線路 c p 398 により、デコード回路を構成するデコーダ I C14 に接続されている。

10

【0206】

配線路 P37 (図 39) では、図 26 に示すように、第 1 配線層 L1 の複合チップ配置領域 191 に設けられた端子接続部 HDT10 が、配線路 c p 401 により、斜め + X + Y 方向の近傍に配置されたビア v16 に接続されている。ビア v16 は、その周囲に配置されている 4 つの端子接続部 (端子接続部 HDT10 を含む) の略中央に配置されている。このビア v16 は、図 31 に示すように、第 4 配線層 L4 に設けられた配線路 c p 402 により、制御 ROM 配置領域 192 内に配置されるビア v92 に接続されている。

20

【0207】

端子接続部 HDT10 からビア v92 に達した配線路は、このビア v92 で 4 つに分岐している。第 1 の分岐路は、図 27 に示すように、第 1 配線層 L1 に設けられた配線路 c p 403 により、ビア v92 から制御 ROM105 の端子接続部 Q10 に対して制御 ROM 配置領域 192 の内側から接続されている。また第 2 の分岐路は、図 32 に示すように、第 6 配線層 L6 に設けられた配線路 c p 404 により、ビア v92 から終端抵抗 RA30 に接続されている。

30

【0208】

また第 3 の分岐路は、図 28, 図 29 に示すように、第 3 配線層 L3 に設けられた配線路 c p 405 により、ビア v92 から第 1 コネクタ配置領域 194 内のビア v152 に接続され、更に図 33 に示すように、第 6 配線層 L6 に設けられた配線路 c p 406 により、端子接続部 hdt10 に対して第 1 コネクタ配置領域 194 の内側から接続されている。また第 4 の分岐路は、図 28, 図 30 に示すように、第 3 配線層 L3 に設けられた配線路 c p 407 により、ビア v92 からビア v193 に接続され、更に図 34 に示すように、第 6 配線層 L6 に設けられた配線路 c p 408 により、デコード回路を構成するデコーダ I C14 に接続されている。

40

【0209】

配線路 P38 (図 39) では、図 26 に示すように、第 1 配線層 L1 の複合チップ配置領域 191 に設けられた端子接続部 HDT11 が、配線路 c p 411 により、斜め + X + Y 方向の近傍に配置されたビア v7 に接続されている。ビア v7 は、その周囲に配置されている 4 つの端子接続部 (端子接続部 HDT11 を含む) の略中央に配置されている。このビア v7 は、図 31 に示すように、第 4 配線層 L4 に設けられた配線路 c p 412 により、制御 ROM 配置領域 192 内に配置されるビア v91 に接続されている。

【0210】

端子接続部 HDT11 からビア v91 に達した配線路は、このビア v91 で 4 つに分岐している。第 1 の分岐路は、図 27 に示すように、第 1 配線層 L1 に設けられた配線路 c

50

p 4 1 3 により、ビア v 9 1 から制御 R O M 1 0 5 の端子接続部 Q 1 1 に対して制御 R O M 配置領域 1 9 2 の内側から接続されている。また第 2 の分岐路は、図 3 2 に示すように、第 6 配線層 L 6 に設けられた配線路 c p 4 1 4 により、ビア v 9 1 から終端抵抗 R A 3 0 に接続されている。

#### 【 0 2 1 1 】

また第 3 の分岐路は、図 2 8 , 図 2 9 に示すように、第 3 配線層 L 3 に設けられた配線路 c p 4 1 5 により、ビア v 9 1 から第 1 コネクタ配置領域 1 9 4 内のビア v 1 5 1 に接続され、更に図 3 3 に示すように、第 6 配線層 L 6 に設けられた配線路 c p 4 1 6 により、端子接続部 h d t 1 1 に対して第 1 コネクタ配置領域 1 9 4 の内側から接続されている。また第 4 の分岐路は、図 2 8 , 図 3 0 に示すように、第 3 配線層 L 3 に設けられた配線路 c p 4 1 7 により、ビア v 9 1 からビア v 1 9 4 に接続され、更に図 3 4 に示すように、第 6 配線層 L 6 に設けられた配線路 c p 4 1 8 により、デコード回路を構成するデコーダ I C 1 4 に接続されている。

#### 【 0 2 1 2 】

配線路 P 3 9 ( 図 3 9 ) では、図 2 6 に示すように、第 1 配線層 L 1 の複合チップ配置領域 1 9 1 に設けられた端子接続部 H D T 1 2 が、配線路 c p 4 2 1 により、複合チップ配置領域 1 9 1 の外側、具体的には複合チップ配置領域 1 9 1 と制御 R O M 配置領域 1 9 2 との間に配置されたビア v 4 3 に接続されている。なお、端子接続部 H D T 1 2 は、複合チップ配置領域 1 9 1 の最も外周側に配置されている。ビア v 4 3 は、図 3 1 に示すように、第 4 配線層 L 4 に設けられた配線路 c p 4 2 2 により、制御 R O M 配置領域 1 9 2 内に配置されるビア v 9 0 に接続されている。

#### 【 0 2 1 3 】

端子接続部 H D T 1 2 からビア v 9 0 に達した配線路は、このビア v 9 0 で 4 つに分岐している。第 1 の分岐路は、図 2 7 に示すように、第 1 配線層 L 1 に設けられた配線路 c p 4 2 3 により、ビア v 9 0 から制御 R O M 1 0 5 の端子接続部 Q 1 2 に対して制御 R O M 配置領域 1 9 2 の内側から接続されている。また第 2 の分岐路は、図 3 2 に示すように、第 6 配線層 L 6 に設けられた配線路 c p 4 2 4 により、ビア v 9 0 から終端抵抗 R A 1 7 に接続されている。この終端抵抗 R A 1 7 は、他端側が所定のビアを介して第 2 配線層 L 2 のベタ配線層 ( G N D ) に接続されている ( 配線図では省略 ) 。

#### 【 0 2 1 4 】

また第 3 の分岐路は、図 2 8 , 図 2 9 に示すように、第 3 配線層 L 3 に設けられた配線路 c p 4 2 5 により、ビア v 9 0 から第 1 コネクタ配置領域 1 9 4 内のビア v 1 5 0 に接続され、更に図 3 3 に示すように、第 6 配線層 L 6 に設けられた配線路 c p 4 2 6 により、端子接続部 h d t 1 2 に対して第 1 コネクタ配置領域 1 9 4 の内側から接続されている。また第 4 の分岐路は、図 2 8 , 図 3 0 に示すように、第 3 配線層 L 3 に設けられた配線路 c p 4 2 7 により、ビア v 9 0 からビア v 1 8 5 に接続され、更に図 3 4 に示すように、第 6 配線層 L 6 に設けられた配線路 c p 4 2 8 により、デコード回路を構成するデコーダ I C 1 4 に接続されている。

#### 【 0 2 1 5 】

配線路 P 4 0 ( 図 3 9 ) では、図 2 6 に示すように、第 1 配線層 L 1 の複合チップ配置領域 1 9 1 に設けられた端子接続部 H D T 1 3 が、配線路 c p 4 3 1 により、複合チップ配置領域 1 9 1 の外側、具体的には複合チップ配置領域 1 9 1 と制御 R O M 配置領域 1 9 2 との間に配置されたビア v 4 2 に接続されている。なお、端子接続部 H D T 1 3 は、複合チップ配置領域 1 9 1 の外周側から 2 列目に配置されている。ビア v 4 2 は、図 3 1 に示すように、第 4 配線層 L 4 に設けられた配線路 c p 4 3 2 により、制御 R O M 配置領域 1 9 2 内に配置されるビア v 8 9 に接続されている。

#### 【 0 2 1 6 】

端子接続部 H D T 1 3 からビア v 8 9 に達した配線路は、このビア v 8 9 で 4 つに分岐している。第 1 の分岐路は、図 2 7 に示すように、第 1 配線層 L 1 に設けられた配線路 c p 4 3 3 により、ビア v 8 9 から制御 R O M 1 0 5 の端子接続部 Q 1 3 に対して制御 R O

10

20

30

40

50

M配置領域192の内側から接続されている。また第2の分岐路は、図32に示すように、第6配線層L6に設けられた配線路c p 4 3 4により、ビアv 8 9から終端抵抗R A 1 7に接続されている。

#### 【0217】

また第3の分岐路は、図28、図29に示すように、第3配線層L3に設けられた配線路c p 4 3 5により、ビアv 8 9から第1コネクタ配置領域194内のビアv 1 4 9に接続され、更に図33に示すように、第6配線層L6に設けられた配線路c p 4 3 6により、端子接続部h d t 1 3に対して第1コネクタ配置領域194の内側から接続されている。また第4の分岐路は、図28、図30に示すように、第3配線層L3に設けられた配線路c p 4 3 7により、ビアv 8 9からビアv 1 8 6に接続され、更に図34に示すように、第6配線層L6に設けられた配線路c p 4 3 8により、デコード回路を構成するデコーダI C 1 4に接続されている。

10

#### 【0218】

配線路P 4 1(図39)では、図26に示すように、第1配線層L1の複合チップ配置領域191に設けられた端子接続部H D T 1 4が、配線路c p 4 4 1により、斜め+X+Y方向の近傍に配置されたビアv 2 2に接続されている。ビアv 2 2は、その周囲に配置されている4つの端子接続部(端子接続部H D T 1 4を含む)の略中央に配置されている。このビアv 2 2は、図31に示すように、第4配線層L4に設けられた配線路c p 4 4 2により、制御R O M配置領域192内に配置されるビアv 8 8に接続されている。

20

#### 【0219】

端子接続部H D T 1 4からビアv 8 8に達した配線路は、このビアv 8 8で4つに分岐している。第1の分岐路は、図27に示すように、第1配線層L1に設けられた配線路c p 4 4 3により、ビアv 8 8から制御R O M 1 0 5の端子接続部Q 1 4に対して制御R O M配置領域192の内側から接続されている。また第2の分岐路は、図32に示すように、第6配線層L6に設けられた配線路c p 4 4 4により、ビアv 8 8から終端抵抗R A 1 7に接続されている。

#### 【0220】

また第3の分岐路は、図28、図29に示すように、第3配線層L3に設けられた配線路c p 4 4 5により、ビアv 8 8から第1コネクタ配置領域194内のビアv 1 4 8に接続され、更に図33に示すように、第6配線層L6に設けられた配線路c p 4 4 6により、端子接続部h d t 1 4に対して第1コネクタ配置領域194の内側から接続されている。また第4の分岐路は、図28、図30に示すように、第3配線層L3に設けられた配線路c p 4 4 7により、ビアv 8 8からビアv 1 8 7に接続され、更に図34に示すように、第6配線層L6に設けられた配線路c p 4 4 8により、デコード回路を構成するデコーダI C 1 4に接続されている。

30

#### 【0221】

配線路P 4 2(図39)では、図26に示すように、第1配線層L1の複合チップ配置領域191に設けられた端子接続部H D T 1 5が、配線路c p 4 5 1により、斜め+X+Y方向の近傍に配置されたビアv 1 5に接続されている。ビアv 1 5は、その周囲に配置されている4つの端子接続部(端子接続部H D T 1 5を含む)の略中央に配置されている。このビアv 1 5は、図31に示すように、第4配線層L4に設けられた配線路c p 4 5 2により、制御R O M配置領域192内に配置されるビアv 8 7に接続されている。

40

#### 【0222】

端子接続部H D T 1 5からビアv 8 7に達した配線路は、このビアv 8 7で4つに分岐している。第1の分岐路は、図27に示すように、第1配線層L1に設けられた配線路c p 4 5 3により、ビアv 8 7から制御R O M 1 0 5の端子接続部Q 1 5 / A - 1に対して制御R O M配置領域192の内側から接続されている。また第2の分岐路は、図32に示すように、第6配線層L6に設けられた配線路c p 4 5 4により、ビアv 8 7から終端抵抗R A 1 7に接続されている。

#### 【0223】

50

また第3の分岐路は、図28、図29に示すように、第3配線層L3に設けられた配線路c p 4 5 5により、ビアv 8 7から第1コネクタ配置領域1 9 4内のビアv 1 4 7に接続され、更に図33に示すように、第6配線層L6に設けられた配線路c p 4 5 6により、端子接続部h d t 1 5に対して第1コネクタ配置領域1 9 4の内側から接続されている。また第4の分岐路は、図28、図30に示すように、第3配線層L3に設けられた配線路c p 4 5 7により、ビアv 8 7からビアv 1 8 8に接続され、更に図34に示すように、第6配線層L6に設けられた配線路c p 4 5 8によりデコーダI C 1 4に接続されている。

#### 【0224】

続いて、複合チップ1 0 4のチップセレクト出力端子H C S 0、リードストローブ出力端子H R D、システムリセット端子H R E S E Tに夫々接続される配線路P 4 3～P 4 5について説明する。

#### 【0225】

配線路P 4 3(図40)では、図26に示すように、第1配線層L1の複合チップ配置領域1 9 1に設けられた端子接続部H C S 0が、配線路c p 5 0 1により、斜め-X+Y方向の近傍に配置されたビアv 9に接続され、ここで2つに分岐している。なおビアv 9は、その周囲に配置されている4つの端子接続部(端子接続部H C S 0を含む)の略中央に配置されている。ビアv 9における第1の分岐路は、図25に示すように、第6配線層L6に設けられた配線路c p 5 0 2により、制御R O M配置領域1 9 2内に配置されるビアv 6 0に接続され、更に図27に示すように、第1配線層L1に設けられた配線路c p 5 0 3により、端子接続部C E #に対して制御R O M配置領域1 9 2の内側から接続されている。

#### 【0226】

またビアv 9における第2の分岐路は、図23に示すように、第4配線層L4に設けられた配線路c p 5 0 4によってビアv 1 7 3に接続され、ここで更に2つに分岐している。このビアv 1 7 3における第2aの分岐路は、図25に示すように、第6配線層L6に設けられた配線路c p 5 0 5によってビアv 2 0 1に接続されている。このビアv 2 0 1はテストポイントT P 3 3を構成している。またビアv 1 7 3における第2bの分岐路は、図20に示すように、第1配線層L1に設けられた配線路c p 5 0 6により、抵抗R A 1 2を経てD C 3 . 3 V(第5配線層L5)に接続されている。

#### 【0227】

配線路P 4 4(図40)では、図20に示すように、第1配線層L1の複合チップ配置領域1 9 1に設けられた端子接続部H R Dが、配線路c p 5 1 1により、斜め+X-Y方向の近傍に配置されたビアv 2 5に接続され、ここで2つに分岐している。なおビアv 2 5は、その周囲に配置されている4つの端子接続部(端子接続部H R Dを含む)の略中央に配置されている。ビアv 2 5における第1の分岐路は、図25に示すように、第6配線層L6に設けられた配線路c p 5 1 2により、複合チップ配置領域1 9 1の外側、具体的には複合チップ配置領域1 9 1と制御R O M配置領域1 9 2との間に配置されたビアv 4 7に接続され、更に図27に示すように、第1配線層L1に設けられた配線路c p 5 1 3により、端子接続部O E #に対して制御R O M配置領域1 9 2の外側から接続されている。

#### 【0228】

またビアv 2 5における第2の分岐路は、図22に示すように、第3配線層L3に設けられた配線路c p 5 1 4によってビアv 1 7 2に接続され、ここで更に2つに分岐している。このビアv 1 7 2における第2aの分岐路は、図22に示すように、第3配線層L3に設けられた配線路c p 5 1 5により、第1コネクタ配置領域1 9 4の外側近傍に配置されたビアv 1 7 1に接続され、更に図25に示すように、第6配線層L6に設けられた配線路c p 5 1 6により、端子接続部h r dに対して第1コネクタ配置領域1 9 4の外側から接続されている。またビアv 1 7 2における第2bの分岐路は、図20に示すように、第1配線層L1に設けられた配線路c p 5 1 7により、抵抗R A 8を経てD C 3 . 3 V(第5配線層L5)に接続されている。

10

20

30

40

50

## 【0229】

配線路 P 4 5 (図 4 0) では、図 2 0 に示すように、第 1 配線層 L 1 の複合チップ配置領域 1 9 1 に設けられた端子接続部 H R E S E T が、配線路 c p 5 2 1 により、複合チップ配置領域 1 9 1 の外側 (+ X 側) に配置されたビア v 2 6 に接続されている。なお、端子接続部 H R E S E T は、複合チップ配置領域 1 9 1 の最も外周側に配置されている。ビア v 2 6 は、図 2 3 に示すように、第 4 配線層 L 4 に設けられた配線路 c p 5 2 2 によってビア v 2 0 2 に接続され、更に図 2 5 に示すように、第 6 配線層 L 6 に設けられた配線路 c p 5 2 3 によってビア v 1 7 4 に接続され、ここで 2 つに分岐している。

## 【0230】

ビア v 1 7 4 における第 1 の分岐路は、図 2 5 に示すように、第 6 配線層 L 6 に設けられた配線路 c p 5 2 4 により、制御 R O M 配置領域 1 9 2 の外側 (+ X 側) 近傍に配置されたビア v 1 0 8 に接続され、更に図 2 7 に示すように、第 1 配線層 L 1 に設けられた配線路 c p 5 2 5 により、端子接続部 R E S E T # に対して制御 R O M 配置領域 1 9 2 の内側から接続されている。なお図 2 5 に示すように、第 6 配線層 L 6 の配線路 c p 5 2 4 は、抵抗 R 4 0 を介して D C 3 . 3 V (第 5 配線層 L 5 ) に接続され、またコンデンサ C 1 5 1 を介してグランド (第 2 配線層 L 2 ) に接続されている。

10

## 【0231】

またビア v 1 7 4 における第 2 の分岐路は、図 2 0 に示すように、第 1 配線層 L 1 に設けられた配線路 c p 5 2 6 によってビア v 2 0 4 に接続されている。なお、このビア v 2 0 4 はテストポイント T P 1 7 を構成している。そしてビア v 2 0 4 は、第 6 配線層 L 6 側のリセット回路に接続されている。即ち図 2 5 に示すように、ビア v 2 0 4 は、第 6 配線層 L 6 に設けられた配線路 c p 5 2 7 によって抵抗内蔵トランジスタ T 1 に接続され、更に配線路 c p 5 2 8 によって論理集積回路 I C 7 に接続され、更に配線路 c p 5 2 9 により、テストポイント T P 2 3 を構成するビア v 2 0 3 を経て W D T 内蔵リセット集積回路 (リセット I C ) I C 1 0 に接続されている。なお、配線路 c p 5 2 8 は、抵抗 R 1 9 を介して D C 3 . 3 V (第 5 配線層 L 5 ) に接続され、配線路 c p 5 2 9 は、コンデンサ C 4 0 を介してグランド (第 2 配線層 L 2 ) に、また抵抗 R 2 6 を介して D C 3 . 3 V (第 5 配線層 L 5 ) に夫々接続されている。

20

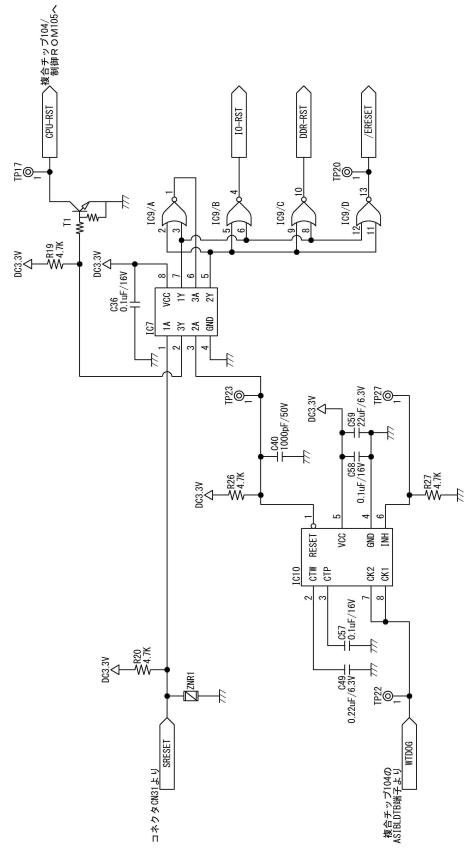

## 【0232】

なお、この第 6 配線層 L 6 側のリセット回路は図 4 2 に示すように構成されている。論理集積回路 I C 7 には、液晶制御第 1 コネクタ C N 3 1 を介してシステムリセット信号が、また W D T 内蔵リセット集積回路 (リセット I C ) I C 1 0 からリセット信号が夫々入力可能となっており、それらの何れかのリセット信号が入力されたとき、ノイズ対策用の抵抗内蔵トランジスタ T 1 を介して複合チップ 1 0 4 及び制御 R O M 1 0 5 にリセット信号が送信されるようになっている。なお、W D T 内蔵リセット集積回路 (リセット I C ) I C 1 0 には、W D T リセット用として例えば複合チップ 1 0 4 の L E D 用データ出力端子 A S I B L D T B が接続されている。

30

## 【0233】