(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-258921

(P2006-258921A)

(43) 公開日 平成18年9月28日(2006.9.28)

| (51) Int.CI.                | F 1                  | テーマコード (参考) |

|-----------------------------|----------------------|-------------|

| <b>G09G 3/22 (2006.01)</b>  | G09G 3/22 G 2H093    |             |

| <b>G02F 1/133 (2006.01)</b> | G02F 1/133 550 5C080 |             |

| <b>G09G 3/20 (2006.01)</b>  | G09G 3/20 612F       |             |

|                             | G09G 3/20 621A       |             |

|                             | G09G 3/20 622C       |             |

審査請求 未請求 請求項の数 3 O L (全 18 頁) 最終頁に続く

|           |                            |          |                                                  |

|-----------|----------------------------|----------|--------------------------------------------------|

| (21) 出願番号 | 特願2005-73142 (P2005-73142) | (71) 出願人 | 502356528<br>株式会社 日立ディスプレイズ<br>千葉県茂原市早野3300番地    |

| (22) 出願日  | 平成17年3月15日 (2005.3.15)     | (74) 代理人 | 100093506<br>弁理士 小野寺 洋二                          |

|           |                            | (72) 発明者 | 尾崎 俊文<br>千葉県茂原市早野3300番地<br>株式会社日立ディスプレイズ内        |

|           |                            | (72) 発明者 | 塚原 正久<br>神奈川県横浜市戸塚区吉田町292番地<br>株式会社日立アドバンストデジタル内 |

|           |                            |          |                                                  |

最終頁に続く

(54) 【発明の名称】表示装置

(57) 【要約】 (修正有)

【課題】MIM型電子放出素子を用いた表示装置において、行配線の電圧降下による画素の輝度むらを防止する。

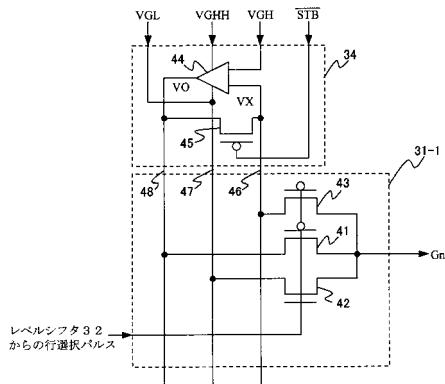

【解決手段】反転信号S TBが立ち上ると、pMOS帰還スイッチ45がオフするとともに、レベルシフタ32からの行選択バルスが出力され、nMOS非選択スイッチ42がオフし、pMOS選択スイッチ41とpMOS検出用スイッチ43がオンし、出力回路ユニット31-1の出力電圧Gnが非選択電圧VGLから選択電圧VGHへと上昇する。この時、pMOS検出用スイッチ43には電流は流れないから、出力回路ユニット31-1の出力電圧Gnは入力電圧VXに等しくなる。すなわち、出力回路ユニット31-1の出力電圧Gnは常に行選択電圧VGHに等しくなる。

【選択図】図4

図4 スキャンドライバ出力回路と補正選択電圧発生回路

**【特許請求の範囲】****【請求項 1】**

複数の行配線と複数の列配線とそれらの各交点に配置された複数の電子放出素子を有する背面板と、アノード電圧が与えられる前面板とを有する表示パネルと、前記行配線の選択を行う走査回路と、前記列配線に変調電圧を与える変調回路とを備えた表示装置において、

前記走査回路は走査回路出力点と電源線間に設けられた非選択電圧をオンオフする非選択スイッチと、走査回路出力点と補正選択電圧発生回路出力配線間に設けられた補正選択電圧をオンオフする選択スイッチと、走査回路出力点と補正選択電圧発生回路入力配線間に設けられた選択行の出力電圧を検出する検出用スイッチを各行毎に備え、

第1の入力を補正選択電圧発生回路入力配線と接続し、第2の入を行選択電圧と接続し、出力を補正選択電圧発生回路出力配線と接続した差動增幅器からなる補正選択電圧発生回路を複数の行配線毎に備えることを特徴とする表示装置。

**【請求項 2】**

前記補正選択電圧発生回路は、前記差動增幅器の入力と出力との間に帰還スイッチを備えることを特徴とする請求項1に記載の表示装置。

**【請求項 3】**

前記帰還スイッチのオフ時刻を前記選択スイッチと前記検出用スイッチのオン時刻より遅らせたことを特徴とする請求項2に記載の表示装置。

10

20

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、走査線(行配線)における電圧降下を補正する表示装置、特に、MIM型電子放出素子を用いた表示装置に関する。

**【背景技術】****【0002】**

これまで、冷陰極電子放出素子として、例えば、金属／絶縁層／金属型電子放出素子(以下「MIM型電子放出素子」という。)が知られている。このMIM型電子放出素子は、絶縁層を挟む上下の電極に電圧を印加することで、電極の表面から電子を放出させるものである。

**【0003】**

このMIM型電子放出素子では、下部電極から放出される電子の95%程度が電子放出されず上部電極に流れるため、上部電極に接続された行配線に電圧降下が生じ、輝度むらが生じる。これを防ぐため、下部電極に接続された列配線の電圧を補正する方式が検討されている。

**【0004】**

しかし、MIM型電子放出素子では列配線の寄生容量が大きいため、補正による列配線電圧振幅増加により列配線を駆動する変調回路を構成するデータドライバの消費電力が増加するという問題が生じていた。

**【0005】**

下記特許文献1には、走査回路出力電圧を帰還させて走査回路出力回路への入力電圧を補正する行選択電圧補正回路を有するものが記載されている。

**【特許文献1】特開2004-86130号公報****【発明の開示】****【発明が解決しようとする課題】****【0006】**

上記特許文献1に示される図17の補正回路では、演算增幅器205を用いた抵抗帰還がかけられている。この結果、出力端子207の電圧は参照電圧Refと等しくならず行配線に流れる電流と走査回路の出力オン抵抗とにより生じる電圧降下が補正しきれない。

30

40

50

## 【0007】

また、上記特許文献1に示される図26の補正回路では、各行配線出力毎に演算増幅器503を用いたボルテージフォロワーを設け、出力501が一定になるようにFET502のゲートを演算増幅器503により駆動している。しかし、FET502のドレインソース間電圧が一定となるように動作するため、行配線に流れる電流によりゲートソース間電圧が変化してオン抵抗が大きく変化し、行配線電圧変化の時定数が変化する。さらに、多出力の行を共通の演算増幅器で補正する場合についての考慮がなされていない。

## 【課題を解決するための手段】

## 【0008】

請求項1における差動増幅器の入力インピーダンスは高いため、補正選択電圧発生回路10

入力配線と検出用スイッチには定常電流は流れないから、差動増幅器の第1の入力電圧は走査回路出力点電圧と等しくなる。この結果、行配線に流れ込む電流と補正選択電圧発生回路出力配線と選択スイッチの抵抗により生じる電圧降下量によらず、走査回路出力点電圧が差動増幅器の第2の入力に印加された行選択電圧と等しくなる様に差動増幅器出力電圧が補正される。したがって、行配線に流れ込む電流と走査回路の出力オン抵抗とにより生じる電圧降下を高精度で補正できる。また、行配線に流れ込む電流により選択スイッチのソース電圧が変化するため、ゲートソース間電圧の変化を小さくすることができ、オン抵抗と時定数変化を小さくできる。

## 【0009】

請求項2における帰還スイッチは、選択スイッチと検出用スイッチがオフしている非選択期間にオンしているので、選択行が切り替わる際に、帰還路が切断され差動増幅器出力が不安定になるのを防ぐことができる。

## 【0010】

請求項3において、帰還スイッチのオフ時刻を選択行の選択スイッチと検出用スイッチのオン時刻より遅らせることで、走査回路の出力電圧が非選択電圧から選択電圧へと上昇する際生じる初期の急激な電位変動時に、差動増幅器の出力電圧に対する入力電圧の変化が遅れることがないため、オーバーシュートを低減できる。

## 【発明の効果】

## 【0011】

請求項1に記載の表示装置によると、補正誤差が少なく発光時間の信号依存性の少ない30

高画質特性とを実現できる。

## 【0012】

請求項2に記載の表示装置によると、差動増幅器出力を安定化させ、画像異常の発生を防げる。

## 【0013】

請求項3に記載の表示装置によると、行配線に出力される選択電圧のオーバーシュートを低減し発光量の高精度制御ができる。

## 【発明を実施するための最良の形態】

## 【0014】

以下、図面を用いて、本発明の実施例を説明する。

## 【実施例1】

## 【0015】

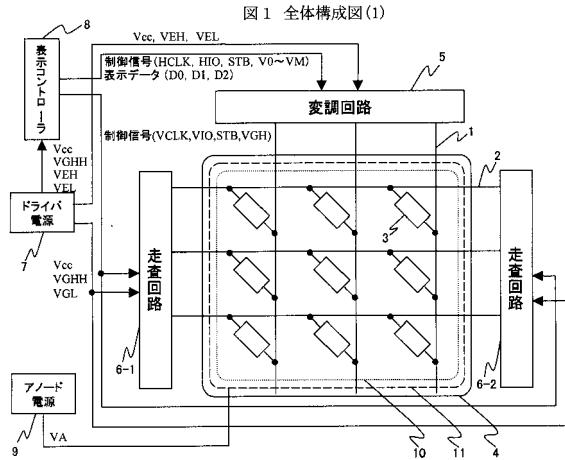

図1は、本実施例の全体回路構成(1)を示すブロック図である。表示パネル4は、列配線1、行配線2、MIM型電子放出素子3を備える背面板と、この背面板の対向面に蛍光膜10と蛍光膜10を覆う様に形成されたメタルバック11を備える前面板と、パネル内を真空にするためにパネル周辺に設けられた側壁(図示せず)とからなる。

## 【0016】

蛍光膜10は、MIM型電子放出素子3の各列毎に塗分けられた赤、緑、青の3原色からなる。5は列配線に変調信号を出力する変調回路、6-1、6-2は表示パネル4の両側に配置され行選択を行う走査回路である。

## 【0017】

ドライバ電源7は、走査回路6-1と6-2に高電源電圧VGHH、非選択電圧VGL、論理回路用電圧Vccを、変調回路5に最大発光電圧VEL、非発光電圧VEH、論理回路用電圧Vccを、表示コントローラ8に最大発光電圧VEL、非発光電圧VEH、高電源電圧VGHH、論理回路用電圧Vccを供給する。

## 【0018】

表示コントローラ8は、走査回路6-1と6-2に制御信号として垂直クロックVCLK、スタートパルスVIO、出力切り替え信号STBを、変調回路5に制御信号として水平クロックHCLK、スタートパルスHI0、出力切り替え信号STB、変調回路用参照電圧V0~VMと、赤、緑、青に対応する3出力nビットの表示データD0、D1、D2を出力する。10

## 【0019】

これらの制御信号と、変調回路用参照電圧V0~VM以外の信号は全て論理回路用電圧Vccの振幅を持つ。また、アノード電源9はメタルバック11に蛍光体を発光させるためのアノード電圧VAを供給する。

## 【0020】

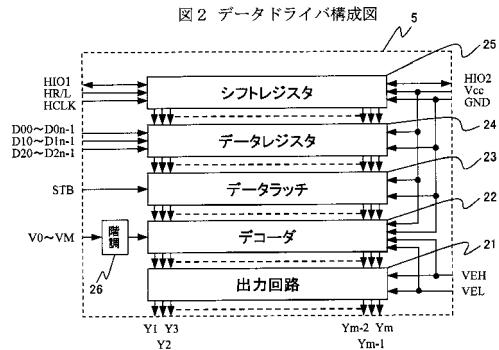

図1の変調回路5は、図2に示すデータドライバの直列接続からなる。

## 【0021】

図2において、25は表示データを取り込むためのラッチ信号を生成するシフトレジスタ、24は表示コントローラから同時に入力される赤、緑、青に対応するD00~D0n-1、D10~D1n-1、D20~D2n-1の3出力nビットの表示データを順次取り込むデータレジスタ、23はデータレジスタ24からの表示データを出力切り替え信号STBに同期して取り込むデータラッチ、26は表示コントローラ8の出力する変調回路用参照電圧V0~VMから抵抗分割により2のn乗個の階調電圧を発生させる階調電圧生成部、22はデータラッチ23の出力するnビット表示データに応じ2のn乗個の階調電圧から電圧を選択するデコーダ、21はデコーダ22の出力電圧を出力電圧Y1~Ymとして表示パネル4の列配線1の各々に出力するためのボルテージフォロワーからなる出力回路である。20

## 【0022】

また、HR/Lはシフトレジスタ25のシフト方向を決めるための信号で、論理回路用電圧Vcc又は接地電圧GNDに固定されている。なお、変調回路用参照電圧V0~VMは非発光電圧VEHから最大発光電圧VELの間をM等分した電圧であり、階調電圧生成部26を構成する抵抗の分割抵抗値は全て等しく、階調と出力電圧の関係は線形となっている。30

## 【0023】

ここで、1水平走査期間が開始されると、スタートパルスHI0が第1のデータドライバのHI01(又はHI02)信号として入力され、シフトレジスタ25内を水平クロックHCLKに同期してシフトし、ラッチ信号が出力されると、3出力同時にnビットの表示データが順次データレジスタ24に取り込まれる。

## 【0024】

第1のデータドライバのデータレジスタ24への表示データの取り込みが終了すると、HI02(又はHI01)の電圧が論理回路用電圧Vccとなり、第2のデータドライバのHI01(又はHI02)に入力され、第2のデータドライバへの表示データ取り込みが開始される。40

## 【0025】

この様にして、全表示データのデータレジスタ24への取り込みが終了すると、1水平走査期間の直前に、出力切り替え信号STBの立ち上がりに同期して、全表示データがデータレジスタ24からデータラッチ23に取り込まれる。取り込まれた表示データはそれぞれデコーダ22により階調電圧に変換され、階調電圧は出力回路21により各列配線に出力される。50

## 【0026】

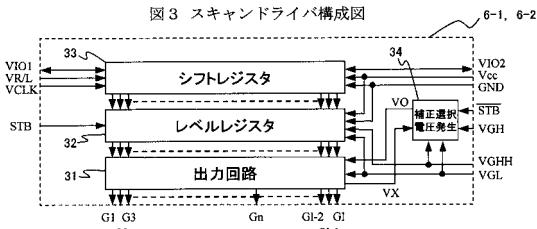

次に、図1の走査回路6-1、6-2は、図3に示すスキャンドライバの直列接続からなる。

## 【0027】

図3において、33は1水平走査期間毎に選択行を順次切り替えるための選択信号を生成するシフトレジスタ、32はシフトレジスタ33の出力を論理回路用電圧Vcc-GNDのレベルから高電源電圧VGHH-非選択電圧VGLのレベルに変換するレベルシフタ、31はレベルシフトされたシフトレジスタ33の出力に応じ選択電圧VGH又は非選択電圧VGLを出力電圧G1~G1として、表示パネル4の行配線2の各々に出力するためのCMOS反転回路からなる出力回路、34は出力回路31に入力する補正選択電圧VOを発生させる補正選択電圧発生回路である。VR/Lはシフトレジスタのシフト方向を決めるための信号で、論理回路用電圧Vcc又は接地電圧GNDに固定されている。10

## 【0028】

ここで、1垂直走査期間が開始されると、スタートパルスVIOが第1のスキャンドライバのVIO1(又はVIO2)信号として入力され、1水平走査期間毎にシフトレジスタ33内を垂直クロックVCLKに同期してシフトし、選択信号が順次出力される。

## 【0029】

次に、出力された選択信号と出力切り替え信号STBの反転信号との論理積がレベルシフタ32により高電源電圧VGHH-非選択電圧VGLのレベルにレベルシフトされ、補正選択電圧発生回路34により生成された補正された選択電圧VOが出力回路31に入力され、表示パネル4の選択行配線に選択電圧VGHとして出力される。他方、表示パネル4の非選択行配線には非選択電圧VGLが出力される。20

## 【0030】

第1のスキャンドライバ内のシフトが終了するとVIO2(又はVIO1)の電圧が論理回路用電圧Vccとなり第2のスキャンドライバのVIO1(又はVIO2)に入力され、第2のスキャンドライバ内のシフトが開始される。

## 【0031】

この様にして全行が順次選択される。各スキャンドライバの補正選択電圧発生回路34は、VIO1(又はVIO2)が入力されると動作可能となり、VIO2(又はVIO1)が次のスキャンドライバに入力されると動作停止する。30

## 【0032】

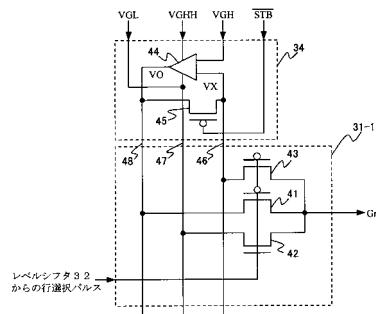

図4は、図3に示すスキャンドライバ内の出力回路31と補正選択電圧発生回路34の詳細を示す。31-1は各行毎に設けられた出力回路のユニットを示す。

## 【0033】

図3において、41は補正選択電圧発生回路34の発生する補正選択電圧VOをオンオフするpMOS選択スイッチ、42は非選択電圧VGLをオンオフするnMOS非選択スイッチ、43は選択行の出力回路の出力電圧Gnを補正選択電圧発生回路34への入力電圧VXとして伝えるpMOS検出用スイッチである。

## 【0034】

また、44は出力回路ユニット31-1からの入力電圧VXが行配線に電流が流れず補正を行わない時の行選択電圧VGHに等しくなる様に補正選択電圧VOを出力する差動増幅器、45は出力切り替え信号STBの反転信号によりオンオフするpMOS帰還スイッチ、46は各出力回路のユニット31-1内のPMOS検出用スイッチ43と補正選択電圧発生回路34内の差動増幅器44の入力を接続する補正選択電圧発生回路入力配線、47は各出力回路のユニット31-1内のnMOS非選択スイッチ42に非選択電圧VGLを供給する電源線、48は各出力回路のユニット31-1内のPMOS選択スイッチ41と補正選択電圧発生回路34内の差動増幅器44の出力を接続する補正選択電圧発生回路出力配線である。40

## 【0035】

ここで、出力切り替え信号STBが立下がり、その反転信号が立ち上がると、pMOS

10

20

30

40

50

帰還スイッチ 4 5 がオフするとともに、レベルシフタ 3 2 から選択行に低電圧の行選択バルスが出力され、選択行の n MOS 非選択スイッチ 4 2 がオフし、p MOS 選択スイッチ 4 1 と p MOS 検出用スイッチ 4 3 がオンし、出力回路の出力電圧 G n が非選択電圧 V G L から選択電圧 V G H へと上昇する。

## 【0036】

定常状態では差動増幅器 4 4 が、出力回路ユニット 3 1 - 1 からの入力電圧 V X が行配線に電流が流れず補正を行わない時の行選択電圧 V G H に等しくなる様に補正選択電圧 V O を出力する。

## 【0037】

この時、p MOS 検出用スイッチ 4 3 には電流は流れないから、出力回路ユニット 3 1 - 1 の出力電圧 G n は入力電圧 V X に等しくなる。すなわち、出力回路ユニット 3 1 - 1 の出力電圧 G n は常に行選択電圧 V G H に等しくなる。

## 【0038】

ついで、出力切り替え信号 S T B が立ち上がり、その反転信号が立下がると、p MOS 帰還スイッチ 4 5 がオンするとともに、選択行の行選択バルスが高電圧となり、選択行の p MOS 選択スイッチ 4 1 と p MOS 検出用スイッチ 4 3 がオフし、n MOS 非選択スイッチ 4 2 がオンし、出力回路ユニット 3 1 - 1 の出力電圧 G n が選択電圧 V G H から非選択電圧 V G L へと低下する。

## 【0039】

この時、p MOS 帰還スイッチ 4 5 は、p MOS 選択スイッチ 4 1 と p MOS 検出用スイッチ 4 3 がオフしている非選択期間にオンする。この結果、選択行が切り替わる際に帰還路が切斷され差動増幅器 4 4 の出力が不安定になるのを防ぐことができる。

## 【0040】

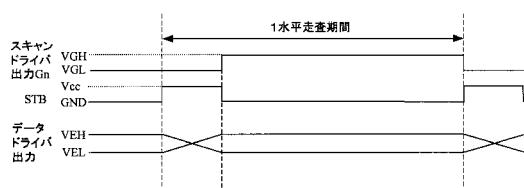

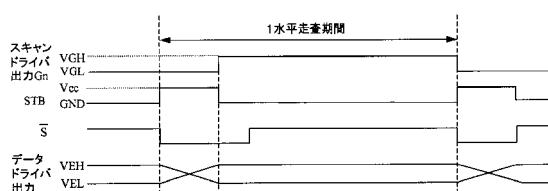

図 5 に 1 水平走査期間内のデータドライバとスキャンドライバ出力タイミングを示す。

## 【0041】

図 5において、出力切り替え信号 S T B の立ち上がりに同期してデータドライバの出力が切り替わる。列配線の抵抗と容量及びデータドライバの出力インピーダンスにより決まるデータドライバ出力遅延時間経過後、出力切り替え信号 S T B の立ち下がりに同期して選択行スキャンドライバの出力が非選択電圧 V G L から選択電圧 V G H に変化する。

## 【0042】

1 水平走査期間の終了時点で、選択行スキャンドライバの出力が選択電圧 V G H から非選択電圧 V G L に変化するとともにデータドライバの出力が切り替わる。行配線に電流が流れる場合には、電圧降下を防ぐために行配線抵抗は低く設定され、行配線時定数は列配線時定数に比し小さい。

## 【0043】

本実施例のタイミングでは、発光時間は、配線時定数の小さな行配線に信号を出力するスキャンドライバの出力時間により決定される。この結果、配線遅延により生じる輝度の不均一性を小さくできる。

## 【0044】

本発明では、表示データによらず選択時のスキャンドライバ出力点での電圧降下がそれぞれゼロとなり、スキャンドライバ出力点電圧が常に一定の選択電圧 V G H となる様に左右スキャンドライバ出力回路へ入力される選択電圧を補正している。

## 【0045】

図 6 はこの時の行配線電圧降下とデータドライバ出力電圧補正值を説明する図である。

## 【0046】

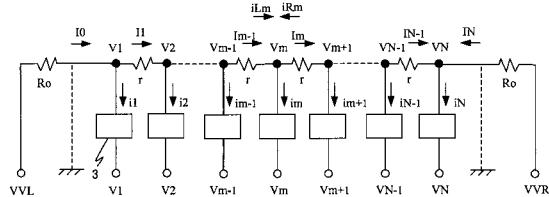

図 6において、3 は MIM 型電子放出素子、r は一画素当たりの走査線抵抗、R o はスキャンドライバ出力回路オン抵抗、i m は第 m 番目の画素のタイオード電流、i R m は第 m 番目の画素のタイオード電流中右から流れ込む成分、i L m は第 m 番目の画素のタイオード電流中左から流れ込む成分、V m は第 m 番目の画素に生じる行配線電圧降下、I m は第 m 番目の画素から第 m + 1 番目の画素に流れる電流、V VL は左端スキャンドライバ出

10

20

30

40

50

力回路へ入力される選択電圧補正值、 $VVR$  は右端スキャンドライバ出力回路へ入力される補正選択電圧である。

## 【0047】

$MIM$  型電子放出素子 3 の各画素に流れるタイオード電流  $i_m$  を所定値とするために、第  $m$  番目の画素に出力されるデータドライバ出力には第  $m$  番目の画素に生じる行配線電圧降下  $V_m$  だけ補正された電圧が出力され、スキャンドライバ出力点での電圧降下がゼロとなる様に左右のスキャンドライバ出力回路には、それぞれ補正值  $VVL$ 、 $VVR$  だけ補正された電圧が入力される。

## 【0048】

第  $m$  番目の画素に生じる行配線電圧降下  $V_m$  は以下の様に求められる。スキャンドライバ出力回路にそれぞれ補正值  $VVL$ 、 $VVR$  を入力することによりスキャンドライバ出力点での電圧降下量はゼロとなり、左右スキャンドライバ出力点が仮想接地点となる。

## 【0049】

第  $m$  番目の画素のダイオード電流  $i_m$  は両側の走査回路から流れ込む  $i_Lm$  と  $i_Rm$  の 2 成分からなる。ダイオード電流が第  $m$  番目の画素だけに流れる場合に第  $m$  番目の画素に生じる電圧降下を  $v_m$  とすると、両端の接地点への電圧降下が等しいことから、次式(1) が成り立つ。

## 【数1】

式(1)

$$vm = -(m-1)r iLm = -(N-m)r iRm \quad \dots\dots\dots (1)$$

10

20

## 【0050】

$iRm = im - iLm$  であることを考慮して  $iLm$  を求めると次式(2) となる。

## 【数2】

式(2)

$$iLm = \frac{N-m}{N-1} im \quad \dots\dots\dots (2)$$

30

## 【0051】

また、 $iRm$  を求めると次式(3) となる。

## 【数3】

式(3)

$$iRm = \frac{m-1}{N-1} im \quad \dots\dots\dots (3)$$

40

## 【0052】

重ね合わせの定理により、次式(4) に示す様に、接地点から右端の第  $N$  番目の画素に向かって流れる電流  $IN$  は、第  $m$  番目の画素のダイオード電流  $im$  中右から流れ込む成分  $iRm$  の和となる。

## 【数4】

式(4)

$$IN = \sum_{j=1}^N iRj = \sum_{j=1}^N \frac{j-1}{N-1} ij \quad \dots\dots\dots (4)$$

## 【0053】

50

電流は保存されるから第  $m - 1$  番目の画素から第  $m$  番目の画素に流れる電流  $I_{m-1}$  は第  $m$  番目の画素から第  $m + 1$  番目の画素に流れる電流  $I_m$  に第  $m$  番目の画素のダイオード電流  $i_m$  を加算して求められる。この関係は任意の  $m$  について成り立ち、 $I_N$  の向きが他とは逆であることを考慮して次式(5)が成り立つ。

【数5】

式(5)

$$I_{m-1} = I_m + i_m$$

$$I_{m-1} = -IN + \sum_{j=m}^N i_j \quad \dots\dots\dots (5)$$

10

【0054】

さらに、第  $m - 1$  番目の画素に生じる電圧降下  $V_{m-1}$  は、電流  $I_{m-1}$  に 1 画素当たりの抵抗値  $r$  をかけた隣接画素間の電圧降下を  $V_m$  に加えて求められる。この関係は任意の  $m$  について成り立ち、第  $N$  番目の画素での電圧降下  $V_N$  が常にゼロであることを考慮すると、次式(6)が成り立つ。

【数6】

式(6)

$$V_{m-1} = V_m + rI_{m-1}$$

$$V_{m-1} = r \sum_{j=m}^N I_{j-1} \quad \dots\dots\dots (6)$$

20

【0055】

以上から、式(4)に示す  $IN$  を初期値として式(5), (6)を逐次計算することで第  $m$  番目の画素に生じる電圧降下を計算できる。所定のダイオード電流を流すにはデータドライバ出力電圧をこの値だけ補正すればよい。

30

【0056】

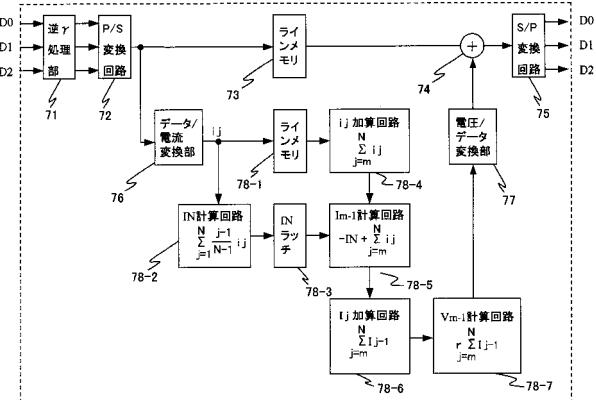

図7に電圧降下補正回路(1)の詳細を示す。電圧降下補正回路(1)は、図1の表示コントローラ8内に設けられ、変調回路5に3出力  $n$  ビットの表示データ  $D_0$ 、 $D_1$ 、 $D_2$  を出力する。表示コントローラ8の他の部分は、表示装置外部から映像信号を受取り、電圧降下補正回路(1)に赤、緑、青に対応する3出力  $n$  ビットの表示データ  $D_0$ 、 $D_1$ 、 $D_2$  を、変調回路5と走査回路6-1、6-2に制御信号を出力する。

【0057】

図7において、71は逆ガンマ処理部、72は赤、緑、青に対応する表示データ  $D_0$ 、 $D_1$ 、 $D_2$  を表示パネル4上の配列に合わせ変換するパラレル/シリアル(P/S)変換回路、73はシリアルデータに変換された表示データを保持するラインメモリ、74は補正データを表示データに加算するための加算回路、75は補正された表示データを赤、緑、青に対応する表示データ  $D_0$ 、 $D_1$ 、 $D_2$  に変換するシリアル/パラレル(S/P)変換回路である。

40

【0058】

また、76は表示データをダイオード電流に変換する変換テーブルよりなるデータ電流変換回路、78-1～78-7は補正電圧を算出するための補正電圧算出手段、77は補正電圧を補正データに変換するための電圧データ変換回路である。

【0059】

また、78-1は各画素のダイオード電流値  $i_j$  を保持するラインメモリ、78-2は

50

各画素のダイオード電流値  $i_j$  と係数とを乗算して順次加算し、式(4)に示す接地点から右端の第N番目の画素に向かって流れる電流  $I_N$  を計算する  $I_N$  計算回路、78-3は計算された電流  $I_N$  を保持する電流  $I_N$  ラッチ回路、78-4はラインメモリ78-1中の各画素のダイオード電流  $i_j$  をN番目から順次加算する電流  $i_j$  加算回路、78-5は電流  $i_j$  加算回路78-4の加算値から電流  $I_N$  ラッチ回路78-3に保持された電流  $I_N$  を減算し、式(5)に示す第m-1番目の画素から第m番目の画素に流れる電流  $I_{m-1}$  を求める電流  $I_{m-1}$  計算回路、78-6は電流  $I_j$  をN番目から順次加算する電流  $I_j$  加算回路、78-7は電流  $I_j$  加算回路78-6の加算値に1画素当たりの走査線抵抗  $r$  を乗じた値を加算して、式(6)に示す第m-1番目の画素に生じる電圧降下  $V_{m-1}$  を求める  $V_{m-1}$  計算回路である。

10

## 【0060】

図7に示す電圧降下補正回路(1)に入力された赤、緑、青に対応する3出力nビットの表示データ  $D_0$ 、 $D_1$ 、 $D_2$ は、逆ガンマ処理部71で表示パネル4の駆動電圧と発光特性の関係に基づいて逆ガンマ補正がなされた後、パラレル／シリアル変換回路72で表示パネル4上の配列に合わせたシリアルデータに変換され、ラインメモリ73に書き込まれる。

## 【0061】

これと並列に、変換されたシリアルデータはデータ電流変換部76に入力され、ダイオード電流  $i_j$  に変換された後、78-1～78-7からなる補正電圧算出手段に入力され補正電圧が計算される。なお、ダイオード電流  $i_j$  はラインメモリ78-1に順次保持される。

20

## 【0062】

他方、 $I_N$  計算回路78-2では、順次ダイオード電流  $i_j$  と係数との乗算と前画素までの加算値との加算がなされ、式(4)に示す接地点から右端の第N番目の画素に向かって流れる電流  $I_N$  が計算され、N番目の画素の積和が終了した時点の値が電流  $I_N$  ラッチ78-3に保持される。

20

## 【0063】

次の水平期間になると、ラインメモリ73よりN番目の画素から順次表示データが読み出されるのに同期して、補正のための電圧降下が読み出されて、補正のための電圧降下が加算される。第m-1番目の画素に生じる電圧降下  $V_{m-1}$  は以下の様に計算される。

30

## 【0064】

ラインメモリ78-1からm番目のダイオード電流  $i_m$  が読み出され、電流  $i_j$  加算回路78-4内に保持されたN番目の画素から第m-1番目の画素のダイオード電流の和に加算される。

## 【0065】

この加算値から、電流  $I_{m-1}$  計算回路78-5で電流  $I_N$  ラッチ回路78-3に保持された電流  $I_N$  が減算され、式(5)に示す第m-1番目の画素から第m番目の画素に流れる電流  $I_{m-1}$  が計算される。

## 【0066】

電流  $I_{m-1}$  は、電流  $I_j$  加算回路78-6内に保持された第N-1番目の画素から右端のN番目の画素に流れる電流  $-I_{N-1}$  から、第m番目の画素から第m+1番目の画素に流れる電流  $I_m$  までの電流の和に加算される。

40

## 【0067】

この加算値は、 $V_{m-1}$  計算回路78-7で1画素当たりの走査線抵抗  $r$  を乗じられ、式(6)に示す第m-1番目の画素に生じる電圧降下  $V_{m-1}$  が求められる。

## 【0068】

この電圧降下  $V_{m-1}$  は、電圧データ変換回路77で補正データに変換され、加算回路74でラインメモリ73に保持された表示データに加算される。その後、補正された表示データはシリアル／パラレル変換回路75で赤、緑、青に対応する表示データ  $D_0$ 、 $D_1$ 、 $D_2$  に変換される。

50

## 【0069】

本実施例では、スキャンドライバの出力回路31の出力電圧Gnが、pMOS検出用スイッチ43と補正選択電圧発生回路34への入力配線46により差動増幅器44の入力に伝えられ、差動増幅器44で補正を行わない時の行選択電圧VGHと比較され、差動増幅器44の出力が補正され出力配線48を介してpMOS選択スイッチ41に出力される。

## 【0070】

差動増幅器44の入力インピーダンスは高いため入力配線46と検出用スイッチ43には定常電流は流れないのであるから、差動増幅器44の第1の入力電圧は走査回路出力点電圧と等しくなる。

## 【0071】

この結果、行配線に流れ込む電流と、出力配線48とpMOS選択スイッチ41との抵抗により生じる電圧降下量によらず、走査回路の出力点電圧が補正を行わない時の行選択電圧VGHと等しくなる様に、差動増幅器44の出力電圧が補正される。したがって、行配線に流れ込む電流と走査回路の出力オン抵抗とにより生じる電圧降下を高精度で補正できる。

## 【0072】

さらに、pMOS選択スイッチ41のソース電圧が、差動増幅器44の出力により補正されるためゲートソース間電圧の変化を小さくすることができ、オン抵抗変化を小さくできる。

## 【0073】

他方、pMOS帰還スイッチ45は、pMOS選択スイッチ41とpMOS検出用スイッチ43がオフしている非選択期間にオンする。この結果、選択行が切り替わる際に帰還路が切断され差動増幅器44の出力が不安定になるのを防ぐことができる。

## 【実施例2】

## 【0074】

以上説明した実施例1では、出力回路の出力電圧Gnが非選択電圧VGLから選択電圧VGHへと上昇する際にオーバーシュートが生じ、発光量の高精度制御が困難になるという場合がある。

## 【0075】

このオーバーシュートは、pMOS選択スイッチ41のオン抵抗と行配線2の配線容量による遅延、pMOS検出用スイッチ43と差動増幅器44の入力配線46の配線容量による遅延により、差動増幅器44の出力電圧変化に対し入力電圧変化が遅れることにより生じる。

## 【0076】

本実施例では、pMOS帰還スイッチ45のオフ時刻を選択行のpMOS選択スイッチ41とpMOS検出用スイッチ43のオン時刻より遅らせる。

## 【0077】

図8に1水平走査期間内のデータドライバとスキャンドライバの出力タイミングを示す。信号Sの反転信号以外は図5と同様である。信号Sの反転信号は、出力切り替え信号STBの反転信号の代わりにpMOS帰還スイッチ45のゲートに入力されるpMOS帰還スイッチ制御信号である。

## 【0078】

この動作を、図3, 4を用いて説明する。出力切り替え信号STBが立下がると、レベルシフタ32から選択行に行選択バルスが出力され、選択行のnMOS非選択スイッチ42がオフし、pMOS選択スイッチ41とpMOS検出用スイッチ43がオンし、出力回路の出力電圧Gnが非選択電圧VGLから選択電圧VGHへと上昇する。

## 【0079】

この時、図8に示す信号Sの反転信号は低電圧であり、pMOS帰還スイッチ45がオンしているため、差動増幅器44の出力電圧と入力電圧変化は等しく遅延は生じない。その後、出力回路の出力電圧Gnが選択電圧VGH近傍まで立ち上がった後、信号Sの反転

10

20

30

40

50

信号が立ち上ると p M O S 帰還スイッチ 4 5 がオフする。

【 0 0 8 0 】

この時刻以降、差動増幅器 4 4 の出力電圧変化に対し入力電圧変化が遅れるが、差動増幅器 4 4 の出力電圧の変化が小さいためオーバーシュートが生じることはない。

【 0 0 8 1 】

本実施例では、p M O S 帰還スイッチ 4 5 のオフ時刻を選択行の p M O S 選択スイッチ 4 1 と p M O S 検出用スイッチ 4 3 のオン時刻より遅らせることで、走査回路の出力電圧が非選択電圧から選択電圧へと上昇する際に生じる初期の急激な電位変動時に、差動増幅器 4 4 の出力電圧に対する入力電圧変化の遅れが生じることがないため、オーバーシュートを低減できる。

10

【 実施例 3 】

【 0 0 8 2 】

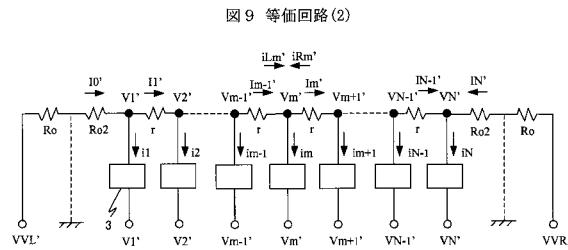

本実施例では、実施例 2 でスキャンドライバの出力点から両端の画素までの抵抗を考慮してデータドライバ出力電圧を補正した。図 9 は、この時の行配線電圧降下と補正の様子を説明する図である。

【 0 0 8 3 】

図 9において、符号 3、 $r$ 、 $R_o$ 、 $i_m$  は、図 6 と同様であり、符号  $i_{Rm'}$ 、 $i_{Lm'}$ 、 $V_{m'}$ 、 $I_{m'}$ 、 $V_{VL'}$ 、 $V_{VR'}$  は、図 6 の  $i_{Rm}$ 、 $i_{Lm}$ 、 $V_m$ 、 $I_m$ 、 $V_{VL}$ 、 $V_{VR}$  と同様である。また、 $R_o 2$  は、スキャンドライバ出力点から両端画素までの抵抗である。

20

【 0 0 8 4 】

第  $m$  番目の画素に生じる行配線電圧降下  $V_{m'}$  は以下の様に求められる。スキャンドライバ出力回路にそれぞれ補正值  $V_{VL'}$ 、 $V_{VR'}$  を入力することによりスキャンドライバ出力点の電圧降下量はゼロとなり、スキャンドライバ出力点が仮想接地点となる。

【 0 0 8 5 】

第  $m$  番目の画素のダイオード電流  $i_m$  は両端の走査回路から流れ込む  $i_{Lm'}$  と  $i_{Rm'}$  の 2 成分からなる。ダイオード電流が第  $m$  番目の画素だけに流れる場合に第  $m$  番目の画素に生じる電圧降下を  $v_{m'}$  とすると、両端の接地点への電圧降下が等しいことから、次式(7)が成り立つ。

30

【 数 7 】

$$\text{式(7)} \\ V_{m'} = -(m-1)r + R_o 2 \quad i_{Lm'} = -(N-m)r + R_o 2 \quad i_{Rm'} \quad \dots \dots \dots (7)$$

【 0 0 8 6 】

$i_{Rm'} = i_m - i_{Lm'}$  であることを考慮して  $i_{Lm'}$  を求めると次式(8)となる。

【 数 8 】

$$\text{式(8)} \\ i_{Lm'} = \frac{(N-m)r + R_o 2}{(N-1)r + 2R_o 2} i_m \quad \dots \dots \dots (8)$$

40

【 0 0 8 7 】

また、 $i_{Rm'}$  を求めると次式(9)となる。

【数9】

$$\text{式(9)} \\ iRm' = \frac{(m-1)r + Ro2}{(N-1)r + 2Ro2} im \quad \dots\dots\dots (9)$$

【0088】

重ね合わせの定理により、次式（10）に示す様に接地点から右端の第N番目の画素に向かって流れる電流  $I_{N'}$  は、第m番目の画素のダイオード電流  $i_m$  中右端から流れこむ成分  $iRm'$  の和となる。

10

【数10】

$$\text{式(10)} \\ IN' = \sum_{j=1}^N iRj' = \sum_{j=1}^N \frac{(j-1)r + Ro2}{(N-1)r + 2Ro2} ij \quad \dots\dots\dots (10)$$

【0089】

この  $I_{N'}$  にスキャンドライバ出力点から両端画素までの抵抗  $Ro2$  をかけると、第N番目の画素での電圧降下  $V_{N'}$  が次式（11）により求められる。

20

【数11】

$$\text{式(11)} \\ VN' = -Ro2 \times IN' \quad \dots\dots\dots (11)$$

【0090】

また、電流は保存されるから第  $m-1$  番目の画素から第m番目の画素に流れる電流  $I_{m-1'}$  は、第m番目の画素から第  $m+1$  番目の画素に流れる電流  $I_{m'}$  に第m番目の画素のダイオード電流  $i_m$  を加算して求められる。

30

【0091】

この関係は任意の  $m$  について成り立ち、 $I_{N'}$  の向きが他とは逆であることを考慮して次式（12）が成り立つ。

【数12】

$$\text{式(12)} \\ Im-1' = Im' + im \\ Im-1' = -IN' + \sum_{j=m}^N ij \quad \dots\dots\dots (12)$$

40

【0092】

さらに、第  $m-1$  番目の画素に生じる電圧降下  $V_{m-1'}$  は、 $V_{m'}$  から電流  $I_{m-1'}$  に1画素当たりの抵抗値  $r$  をかけた隣接画素間の電圧降下を加えて求められる。

【0093】

この関係は任意の  $m$  について成り立ち、第N番目の画素での電圧降下が  $V_{N'}$  であることを考慮すると、次式（13）が成り立つ。

【数13】

式(13)

$$V_{m-1}' = V_m' + r I_{m-1}'$$

$$V_{m-1}' = VN' + r \sum_{j=m}^N I_{j-1}' \quad \dots\dots\dots (13)$$

【0094】

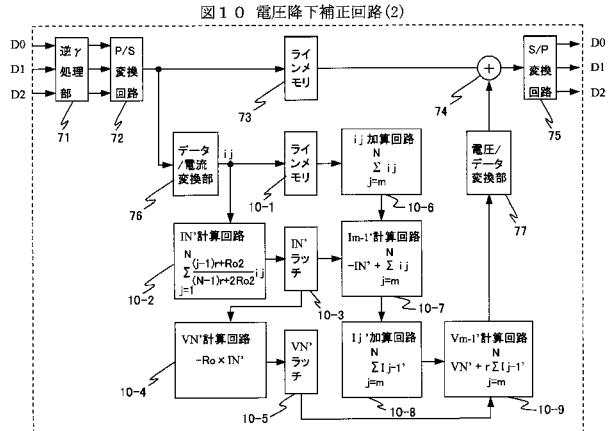

以上から、式(10)(11)に示す $I_N'$ ,  $V_N'$ を初期値として式(12), (13)を逐次計算することで第m番目の画素に生じる電圧降下 $V_{m-1}'$ を計算できる。所定のダイオード電流を流すにはデータドライバ出力電圧をこの値だけ補正すればよい。

【0095】

図10に電圧降下補正回路(2)の詳細を示す。電圧降下補正回路(2)は、図1の表示コントローラ8内に設けられ、変調回路5に3出力nビットの表示データD0、D1、D2を出力する。

【0096】

表示コントローラ8の他の部分は、表示装置外部から映像信号を受取り、電圧降下補正回路(2)に赤、緑、青に対応する3出力nビットの表示データD0、D1、D2を、変調回路5と走査回路6-1, 6-2に制御信号を出力する。

【0097】

図10において、符号71、72、73、74、75、76、77は、図7と同様であり、10-1~10-9は、補正電圧を算出するための補正電圧算出手段である。

【0098】

また、10-1、10-3、10-6、10-7、10-8はそれぞれ図7の78-1、78-3、78-4、78-5、78-6と同様であり、10-2と10-4は、各画素のダイオード電流値 $i_j$ と係数とを乗算して順次加算し、式(10)に示す接地点から右端の第N番目の画素に向かって流れる電流 $I_N'$ を計算する $I_N'$ 計算回路と、この電流 $I_N'$ と係数とを乗算し、式(11)に示す第N番目の画素での電圧降下 $V_N'$ を求める電圧降下 $V_N'$ 計算回路、10-5は計算された電圧降下 $V_N'$ を保持する電圧降下 $V_N$ ラッチ回路、10-9はラッチ回路10-5に保持された電圧降下 $V_N'$ に、電流 $i_j$ 加算回路10-8の加算値に1画素当たりの走査線抵抗 $r$ を乗じた値を加えて、式(13)に示す第m-1番目の画素に生じる電圧降下 $V_{m-1}'$ を求める $V_{m-1}'$ 計算回路である。

【0099】

図10における電圧降下補正回路(2)では、図7と同様の表示データの補正が行われる。入力された赤、緑、青に対応する3出力nビットの表示データD0、D1、D2は、逆ガンマ処理部71で表示パネル4の駆動電圧と発光特性の関係に基づいて逆ガンマ補正がなされた後、パラレル/シリアル変換回路72で表示パネル4上の配列に合わせたシリアルデータに変換され、ラインメモリ73に書き込まれる。

【0100】

これと並列に、変換されたシリアルデータは、データ電流変換部76に入力され、ダイオード電流 $i_j$ に変換された後、10-1~10-9からなる補正電圧算出手段に入力され式(13)により計算された電圧降下 $V_{m-1}'$ が、電圧データ変換回路77で補正データに変換され、加算回路74でラインメモリ73に保持された表示データに加算される。

【0101】

その後、補正された表示データはシリアル/パラレル変換回路75で赤、緑、青に対応する表示データD0、D1、D2に変換される。

【0102】

本実施例では、スキャンドライバ出力点から両端の画素までの抵抗R<sub>o2</sub>を考慮してデ

10

20

30

40

50

ータドライバの出力電圧を補正することでより高精度の補正ができる。

【実施例4】

【0103】

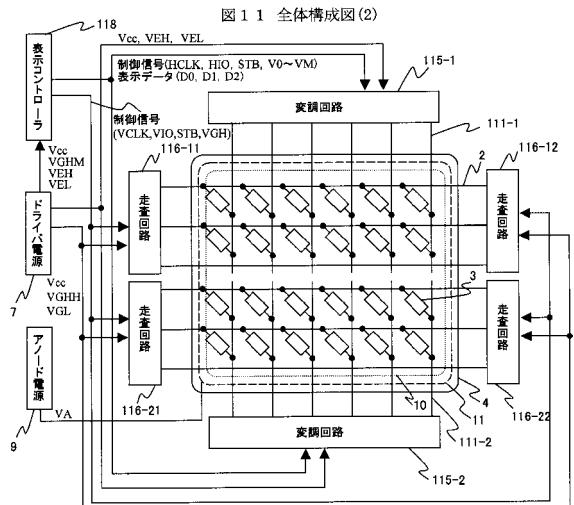

図11は、本発明に係る他の全体構成図(2)であって、画面を上下ブロックに分割し上下ブロックに画像を同時表示するものである。

【0104】

図11において、符号2、4、7、9、10、11は、図1と同様であり、111-1と111-2は、表示パネル4の中央で分割された列配線、115-1、115-2は、それぞれ上下の列配線に変調信号を出力する変調回路、116-11、116-12は、表示パネル4の両側に配置され画面上部の行選択を行う走査回路、116-21、116-22は、表示パネル4の両側に配置され画面下部の行選択を行う走査回路である。 10

【0105】

また、ドライバ電源7は、走査回路116-11、116-12、116-21、116-22に、高電源電圧VGHM、非選択電圧VGL、論理回路用電圧Vccを、変調回路115-1、115-2と表示コントローラ118に、最大発光電圧VEL、非発光電圧VEH、高電源電圧VGHM、論理回路用電圧Vccを供給する。

【0106】

また、表示コントローラ118は、走査回路116-11、116-12、116-21、116-22に、垂直クロックVCLK、スタートパルスVIO、出力切り替え信号STBを、変調回路115-1、115-2に、水平クロックHCLK、スタートパルスHIO、出力切り替え信号STB、赤、緑、青に対応する3出力nビットの表示データD0、D1、D2、参照電圧V0～VMを出力する。 20

【0107】

これらの制御信号中、参照電圧V0～VM以外の信号は全て論理回路用電圧Vccの振幅を持つ。なお、赤、緑、青に対応する3出力nビットの表示データD0、D1、D2は変調回路115-1、115-2で異なるものが入力される。

【0108】

図11の変調回路115-1、115-2及び走査回路116-11、116-12、116-21、116-22の構成と動作は実施例1と同様である。

【0109】

表示コントローラ118内には図7又は図10に示す電圧降下補正回路が2個設けられ、それぞれ変調回路115-1、115-2に同時に3出力nビットの表示データD0、D1、D2を出力する。表示コントローラ118の他の部分にはフレームメモリが設けられ、表示装置外部から映像信号を取り、電圧降下補正回路に上下ブロックに対応する赤、緑、青に対応する3出力nビットの表示データD0、D1、D2を、変調回路115-1、115-2と走査回路116-1、116-2に制御信号を出力する。 30

【0110】

本実施例では、画面を上下ブロックに分割し上下ブロックに画像を同時表示した。この結果、1行の表示時間を従来に比べ2倍にできるため、輝度を同一とすると行配線に流れ電流を1/2とでき、補正する電圧降下量を1/2とできる。

【0111】

さらに、列配線を分割しているので、変調回路115-1、115-2の駆動容量が1/2となり、変調回路115-1と115-2で消費される電力を1/2とできる。

【0112】

実施例1から実施例4では補正選択電圧発生回路34はスキャンドライバ毎に設けたが、独立して動作する走査回路毎に設けてもよい。すなわち、図1に示す様に表示パネル4の両側に走査回路6-1、6-2を配置する場合には、走査回路6-1、6-2毎に補正選択電圧発生回路を設けてもよい。

【0113】

また、図11に示す様に画面を上下ブロックに分割し上下ブロックに画像を同時表示す 50

る場合には、走査回路 116-11、116-12、116-21、116-22 毎に補正選択電圧発生回路を設けてよい。

#### 【0114】

スキャンドライバ出力点から両端の画素までの抵抗  $R_o$  2 が配線配置のために各行で異なる場合がある。この時には、実施例 3 で各行毎に異なる  $R_o$  2 を用い係数を計算する。これによりスキャンドライバ出力点から両端の画素までの抵抗  $R_o$  2 のばらつきにより発生する画質劣化を防ぐ事ができる。

#### 【図面の簡単な説明】

#### 【0115】

【図 1】本発明に係る全体構成図(1)。

10

【図 2】図 1 に示す変調回路におけるデータドライバの構成図。

【図 3】図 1 に示す走査回路におけるスキャンドライバの構成図。

【図 4】図 3 に示す補正電圧発生回路 34 と出力回路 31 の詳細図。

【図 5】図 2、図 3 に示すデータドライバとスキャンドライバの駆動タイミング図(1)

。

【図 6】図 1 に示す行配線の等価回路図(1)。

20

【図 7】図 1 に示す表示コントローラ内に設けられた電圧降下補正回路図(1)。

【図 8】図 2、図 3 に示す他のデータドライバとスキャンドライバの駆動タイミング図(2)。

【図 9】図 1 に示す行配線の他の等価回路図(2)。

20

【図 10】図 1 に示す表示コントローラ内に設けられた他の電圧降下補正回路図(2)。

【図 11】本発明に係る他の全体構成図(2)。

#### 【符号の説明】

#### 【0116】

1...列配線、2...行配線、3...MIM型電子放出素子、4...表示パネル、5...変調回路、6-1、6-2...走査回路、7...ドライバ電源、8...表示コントローラ、9...アノード電源。

21...出力回路、22...デコーダ、23...データラッチ、24...データレジスタ、25...シフトレジスタ、26...階調電圧生成部。

31...出力回路、32...レベルレジスタ、33...シフトレジスタ、34...補正選択電圧発生回路、31-1...出力回路ユニット。

41...pMOS選択スイッチ、42...nMOS非選択スイッチ、43...pMOS検出用スイッチ、44...差動増幅器、45...pMOS帰還スイッチ、46...補正選択電圧発生回路入力配線、47...電源線、48...補正選択電圧発生回路出力配線。

71...逆処理部、72...P/S変換回路、73...ラインメモリ、74...加算回路、75...S/P変換回路、76...データ/電流変換部、77...電圧/データ変換部、78-1～78-7...補正電圧算出手段(78-1...ラインメモリ、78-2...電流IN計算回路、78-3...電流INラッチ回路、78-4...電流ij加算回路、78-5...電流Im-1計算回路、78-6...電流Ij加算回路、78-7...電圧降下Vm-1計算回路)。

10-1～10-9...補正電圧算出手段(10-1...ラインメモリ、10-2...IN'計算回路、10-3...電流IN'ラッチ回路、10-4...VN'計算回路、10-5...VN'ラッチ回路、10-6...電流ij加算回路、10-7...電流Im-1'計算回路、10-8...電流Ij'加算回路、10-9...Vm-1'計算回路)。

111-1、111-2...列配線、115-1、115-2...変調回路、116-11、116-12、116-21、116-22...走査回路、118...表示コントローラ。

40

【図1】

【図2】

【図5】

図5 駆動タイミング(1)

【図6】

図6 等価回路(1)

【図3】

【図4】

図4 スキャンドライバ出力回路と補正選択電圧発生回路

【図7】

図7 電圧降下補正回路(1)

【図8】

図8 駆動タイミング(2)

【図9】

【図10】

【図11】

---

フロントページの続き

(51)Int.Cl.

F I

テーマコード(参考)

G 09 G 3/20 6 4 1 P

G 09 G 3/20 6 4 2 A

(72)発明者 御園生 俊樹

千葉県茂原市早野3300番地 株式会社日立ディスプレイズ内

F ターム(参考) 2H093 NA16 NA43 NA53 NA64 NC10 NC13 NC22 NC25 NC26 NC38

NC65 ND05 ND58

5C080 AA08 BB05 DD05 DD09 DD26 EE28 EE29 FF12 JJ02 JJ03

JJ04