**(19) 대한민국특허청(KR)**

**(12) 등록특허공보(B1)**

(51) Int. Cl.

H01L 29/78 (2006.01)

(45) 공고일자 2006년12월01일

(11) 등록번호 10-0652381

(24) 등록일자 2006년11월24일

|           |                 |           |                 |

|-----------|-----------------|-----------|-----------------|

| (21) 출원번호 | 10-2004-0086555 | (65) 공개번호 | 10-2006-0037561 |

| (22) 출원일자 | 2004년10월28일     | (43) 공개일자 | 2006년05월03일     |

| 심사청구일자    | 2004년10월28일     |           |                 |

(73) 특허권자 삼성전자주식회사

경기도 수원시 영통구 매탄동 416

(72) 발명자 리명

경기도 용인시 기흥읍 농서리 산24 남자기숙사 상록수 601호

김성민

인천 부평구 부개3동 삼부아파트 108-2204

(74) 대리인 리엔목특허법인

이해영

(56) 선행기술조사문현

06140636 \* 1020040086555 – 662113 \*

06140636

\* 심사관에 의하여 인용된 문현

심사관 : 박근용

전체 청구항 수 : 총 16 항

**(54) 다수의 나노 와이어 채널을 구비한 멀티 브릿지 채널 전계효과 트랜지스터 및 그 제조방법**

**(57) 요약**

다수의 나노 와이어 채널을 구비한 MBCFET 및 그것의 제조방법을 개시한다. 본 발명의 일 실시예에 따른 MBCFET은 다수의 나노 와이어 채널을 구비하는 전계 효과 트랜지스터로서, 상기한 전계 효과 트랜지스터를 구성하는 액티브 패턴은 반도체 기판의 상면으로부터 이격되어서 형성되어 있으며, 서로 이격되어 있는 1쌍의 소오스/드레인 패턴과 상기한 1쌍의 소오스/드레인 패턴 사이에 서로 이격되어 개재되어 되어, 수평 방향으로 평행하게 어레이되어 있는 1쌍의 와이어 채널 패턴을 포함한다. 그리고, 상기한 1쌍의 채널 패턴을 둘러싸도록 그것의 외면에는 게이트 절연막이 형성되어 있고, 게이트 전극은 게이트 절연막을 둘러싸도록 상기한 1쌍의 소오스/드레인 패턴 사이에 형성되어 있다.

대표도

도 12a

**특허청구의 범위**

## 청구항 1.

반도체 기판;

상기 반도체 기판의 상면으로부터 이격되어서 형성되어 있는 제1 액티브 패턴으로서, 서로 이격되어 있는 1쌍의 소오스/드레인 패턴과 상기 1쌍의 소오스/드레인 패턴 사이에 서로 이격되어 개재되어 있되, 수평 방향으로 평행하게 어레이되어 있는 1쌍의 와이어 채널 패턴을 포함하는 상기 제1 액티브 패턴;

상기 제1 액티브 패턴을 지지하도록 상기 반도체 기판과 상기 소오스/드레인 패턴 사이에 개재되어 있는 액티브 지지용 패턴;

상기 1쌍의 채널 패턴을 둘러싸도록 상기 채널 패턴의 외면에 형성되어 있는 게이트 절연막; 및

상기 게이트 절연막을 둘러싸도록 상기 1쌍의 소오스/드레인 패턴 사이에 형성되어 있는 게이트 전극을 포함하는 멀티 브릿지 채널 전계 효과 트랜지스터.

## 청구항 2.

삭제

## 청구항 3.

제1항에 있어서,

상기 와이어 채널 패턴의 단면은 완전 공핍형이 되도록 폭과 두께가 작은 것을 특징으로 하는 멀티 브릿지 채널 전계 효과 트랜지스터.

## 청구항 4.

제3항에 있어서,

상기 와이어 채널 패턴의 단면의 폭과 두께는 모두 10-20nm인 것을 특징으로 하는 멀티 브릿지 채널 전계 효과 트랜지스터.

## 청구항 5.

제1항에 있어서,

상기 와이어 채널 패턴의 단면은 타원형인 것을 특징으로 하는 멀티 브릿지 채널 전계 효과 트랜지스터.

## 청구항 6.

제1항에 있어서,

상기 모스 트랜지스터는 상기 제1 액티브 패턴과 동일한 형상을 가지되, 상기 제1 액티브 패턴의 상부에 소정의 거리로 이격되어서 적층되어 있는 제2 액티브 패턴을 더 포함하는 것을 특징으로 하는 멀티 브릿지 채널 전계 효과 트랜지스터.

## 청구항 7.

반도체 기판 상에 n개의 희생층과 n개의 예비-액티브층이 교대로 적층되어 있는 액티브 형성용 스택을 형성하는 단계;

상기 액티브 형성용 스택 상에 액티브 영역을 정의하는 마스크 패턴을 형성하는 단계;

상기 마스크 패턴을 식각 마스크로 사용하여 상기 액티브 형성용 스택층을 식각하여 액티브 형성용 스택 패턴을 형성하는 단계로서, n개의 희생층 패턴과 소오스/드레인 패턴 및 상기 소오스/드레인 패턴 사이에 개재되어 있는 예비-채널 패턴을 포함하는 n개의 예비-액티브 패턴을 포함하는 상기 액티브 형성용 스택 패턴을 형성하는 단계;

상기 예비-채널 패턴 하부의 상기 희생층 패턴은 제거되고 상기 소오스/드레인 패턴 하부의 상기 희생층 패턴은 잔류하도록 상기 희생층 패턴을 식각하여 n개의 액티브 지지용 패턴을 형성하는 단계;

상기 액티브 지지용 패턴, 상기 예비-액티브 패턴 및 상기 마스크 패턴을 둘러싸되, 상기 마스크 패턴의 상면을 노출시키는 제1 버퍼층을 형성하는 단계;

상기 마스크 패턴 및 상기 제1 버퍼층을 패터닝함으로써 상기 예비-액티브 패턴의 상기 소오스/드레인 패턴의 상면을 노출시키는 더미 게이트 패턴을 형성하는 단계;

상기 더미 게이트 패턴을 둘러싸되 상기 더미 게이트 패턴의 상면을 노출시키는 제2 버퍼층을 형성하는 단계;

상기 더미 게이트 패턴에 잔류하는 상기 마스크 패턴을 제거함으로써 상기 예비-채널 패턴의 상면을 노출시키는 홀을 형성하는 단계;

상기 홀을 통하여 상기 예비-채널 패턴을 식각함으로써 1쌍의 와이어 채널 패턴을 형성하는 단계;

상기 제2 버퍼층 및 잔류하는 상기 제1 버퍼층을 제거하는 단계;

상기 와이어 채널 패턴을 둘러싸도록 상기 와이어 채널 패턴의 외면에 게이트 절연막을 형성하는 단계; 및

상기 게이트 절연막 상에 게이트 전극을 형성하는 단계를 포함하는 것을 특징으로 하는 멀티 브릿지 채널 전계 효과 트랜지스터의 제조방법.

## 청구항 8.

제7항에 있어서,

상기 n은 1 또는 2인 것을 특징으로 하는 멀티 브릿지 채널 전계 효과 트랜지스터의 제조방법.

## 청구항 9.

제7항에 있어서,

상기 희생층은 단결정 실리콘 저매듭으로 형성하고, 상기 예비-액티브 층은 단결정 실리콘으로 형성하는 것을 특징으로 하는 멀티 브릿지 채널 전계 효과 트랜지스터의 제조방법.

## 청구항 10.

제7항에 있어서, 상기 예비-액티브 층은 15-25nm의 두께로 형성하는 것을 특징으로 하는 멀티 브릿지 채널 전계 효과 트랜지스터의 제조방법.

## 청구항 11.

제7항에 있어서,

상기 액티브 형성용 스택 패턴을 형성하는 단계 이후에 상기 마스크 패턴을 트리밍하는 단계를 더 포함하는 것을 특징으로 하는 멀티 브릿지 채널 전계 효과 트랜지스터의 제조방법.

## 청구항 12.

제7항에 있어서,

상기 액티브 형성용 스택 패턴을 형성하는 단계에서는 상기 마스크 패턴을 식각하여 상기 반도체 기판을 식각함으로써 상기 반도체 기판에 트렌치를 형성하는 공정을 동시에 수행하고,

상기 제1 버퍼층을 형성하는 단계에서는 상기 트렌치를 매립하는 소자 격리용 절연막을 형성하는 공정을 동시에 수행하는 것을 특징으로 하는 멀티 브릿지 채널 전계 효과 트랜지스터의 제조방법.

## 청구항 13.

제7항에 있어서,

상기 홀을 형성하는 단계 이후에 상기 홀에 의해 노출된 잔류하는 상기 제1 버퍼층 및 상기 제2 버퍼층의 측벽 상에 측벽 스페이서를 형성하는 단계를 더 포함하고,

상기 1쌍의 와이어 채널 패턴을 형성하는 단계에서는 상기 측벽 스페이서를 식각 마스크로 사용하는 것을 특징으로 하는 멀티 브릿지 채널 전계 효과 트랜지스터의 제조방법.

## 청구항 14.

제13항에 있어서,

상기 제1 버퍼층 및 상기 제2 버퍼층은 실리콘 산화물로 형성하고, 상기 측벽 스페이서는 실리콘 질화물로 형성하는 단계를 더 포함하는 것을 특징으로 하는 멀티 브릿지 채널 전계 효과 트랜지스터의 제조방법.

## 청구항 15.

제13항에 있어서,

상기 제2 버퍼층 및 잔류하는 상기 제1 버퍼층을 제거하는 단계 이전에 상기 측벽 스페이서를 제거하는 단계를 더 포함하는 것을 특징으로 하는 멀티 브릿지 채널 전계 효과 트랜지스터의 제조방법.

## 청구항 16.

제7항에 있어서,

상기 게이트 절연막을 형성하는 단계 이전에 상기 와이어 채널 패턴을 트리밍하는 단계를 더 포함하는 것을 특징으로 하는 멀티 브릿지 채널 전계 효과 트랜지스터의 제조방법.

## 청구항 17.

제7항에 있어서,

상기 게이트 절연막을 형성하는 단계 이전에 상기 와이어 채널 패턴의 모서리가 둑글게 되도록 상기 와이어 채널 패턴을 열산화하는 단계를 더 포함하는 것을 특징으로 하는 멀티 브릿지 채널 전계 효과 트랜지스터의 제조방법.

명세서

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 반도체 소자 및 그 제조방법에 관한 것으로, 보다 구체적으로는 다수의 나노 와이어 채널을 구비한 전계 효과 트랜지스터(Field Effect Transistor, FET) 및 그것의 제조방법에 관한 것이다.

반도체 소자의 응용 분야가 확대됨에 따라서 고집적 및/또는 고속 반도체 소자에 대한 요구도 증가하고 있다. 집적도의 증가로 인하여 디자인 룰이 계속 작아지고 있는데, 특히 전계 효과 트랜지스터의 채널 길이와 폭도 작아지고 있다. 채널 길이가 작아지면 단채널 효과(short channel effect)가 발생하는 문제점이 있으며, 채널 폭이 줄어들면 협채널 효과(narrow width effect)가 발생하는 문제점이 있다. 단채널 효과란 채널 영역에 미치는 소오스/드레인 영역에서의 전위의 영향이 현저해지는 현상을 말하며, 협채널 효과란 채널의 폭이 감소하여 문턱 전압이 증가하는 현상을 말한다. 이러한 단채널 효과 및 협채널 효과의 발생을 방지하기 위하여 여러 가지 형태의 모스 전계 효과 트랜지스터 구조가 제안되었다.

예를 들어, 새로운 형태의 MOSFET 중의 하나는 체밍 후(chenming Hu) 등에 의한 미합중국 특허 제6,413,802 호,"FinFET transistor structures having a double gate channel extending vertically from a substrate and methods of amsufacture"에 개시되어 있는 것과 같은 핀 구조(fin structure)의 모스 트랜지스터이다. 그리고, 새로운 형태의 모스트랜지스터 중에서 다른 하나는 쇠라사키(shirasaki)에 의한 미합중국 특허 제4,996,574호, "MIS transistor structure for increasing conductance between source and drain regions"에 개시되어 있는 것과 같은 DELTA 구조(fully DEpleted Lean-channel TrAnsistor structure)의 모스 트랜지스터이다. 그리고, 새로운 형태의 모스 트랜지스터 중에서 또 다른 하나는 김(Kim) 등에 의한 미합중국 특허 제6,605,847호, "Semiconductor device having gate all around type transistor and method of forming the same"에 개시되어 있는 것과 같은 게이트 올 어라운드 구조(Gate All Around structure, GAA 구조)의 모스 트랜지스터이다.

하지만, 상기한 새로운 구조의 모스 트랜지스터들은 각각 장점과 단점을 가지고 있는데, 본 특허 출원의 양수인과 동일인에 의하여 양수된 미합중국특허출원 공개번호 제20040063286호, "Field effect transistors having multiple stacked channels"에 각각의 트랜지스터의 장점과 단점이 기술되어 있다. 그리고, 상기 공개특허에는 각 트랜지스터가 가지고 있는 단점을 해결하기 위하여 새로운 구조의 모스 트랜지스터를 제시하고 있다. 즉, 상기 공개 특허에서는 서로 이격되어 있는 다수의 채널이 수직으로 적층되어 있는 멀티 브릿지 채널(Multi Bridge Channel structure, MBC)을 구비하는 모스 트랜지스터가 개시되어 있다. MBC를 구비하는 모스 트랜지스터는 소오스/드레인 영역이 차지하는 면적을 줄일 수가 있기 때문에 고집적화에 유리하며, 채널의 위치에 관계없이 균일한 소오스/드레인 접합 커패시턴스를 유지할 수 있기 때문에 고속 및 고신뢰성 소자의 제조에 유리한 장점이 있다. 상기 특허 출원은, 그 전부가 본 명세서에 개시되어 있는 것처럼, 참조에 의하여 본 명세서에 완전히 결합한다.

하지만 전술한 새로운 구조의 모스 트랜지스터들, 즉, 핀 구조, DELTA 구조, GAA 구조 및 MBC 구조의 채널을 구비하는 모스 트랜지스터들은 모두가 고속 동작을 하는데 일정한 한계를 보이고 있다. 예를 들어, MBC를 구비하는 모스 트랜지스터의 경우에, 게이트 전극에 의하여 둘러싸여 있는 채널의 단면 모양이, 수평 방향으로 길이가 상대적으로 긴 직사각형이

나 판 모양이다. 이 경우에 수평 방향보다는 수직 방향으로 게이트 전극에 이르는 거리가 가깝기 때문에, 게이트 전극에 의하여 수평 방향보다 수직 방향으로 더 큰 전계가 채널층에 가해진다. 게이트 전극에 의하여 채널에 가해지는 전압이 방향에 따라 차이가 생기면 채널층을 통하여 흐르는 캐리어 예컨대 전자가 완전한 직진 운동을 하지 못하고, 위쪽 또는 아래쪽으로 치우친다. 그 결과, 캐리어가 채널층을 구성하는 입자와 충돌할 가능성도 그 만큼 증가한다. 캐리어가 결정 입자와 충돌하여 스캐터링이 많이 발생하면, 채널층을 통하여 소오스/드레인 영역을 흐르는 전자의 속도가 저하된다. 그러므로, 종래 기술에 따른 MBC 구조의 채널을 구비하는 모스 트랜지스터를 포함하는 반도체 소자는 고속 동작에 일정한 한계가 있을 수가 있다. 이러한 문제는 전술한 다른 구조의 채널을 구비한 모스 트랜지스터의 경우에도 동일하게 발생한다.

그리고, 종래 기술에 따른 MBC 구조의 채널을 구비하는 모스 트랜지스터는 서로 이격되어 있는 채널의 개수를 증가시키는데 일정한 한계가 있다. 왜냐하면, 채널의 개수를 증가시키기 위해서는 채널층의 총수를 증가시켜야 하는데, 채널층의 총수를 증가시키는 것은 건식 식각 공정에서 달성할 수 있는 식각 깊이의 한계로 인하여 일정한 제한을 받을 수 밖에 없다. 이와 같이 채널의 개수가 제한되는 것은 MBC 구조의 채널을 구비하는 모스 트랜지스터의 성능 및 신뢰도를 향상시키는데 일정한 한계로 작용할 수가 있다.

### 발명이 이루고자 하는 기술적 과제

본 발명이 이루고자 하는 기술적 과제는 단채널 효과 및 협채널 효과가 발생하는 것을 방지할 수 있는 멀티 브릿지 채널 전계 효과 트랜지스터 및 그것의 제조방법을 제공하는데 있다.

본 발명이 이루고자 하는 다른 기술적 과제는 고속 동작이 가능한 멀티 브릿지 채널 전계 효과 트랜지스터 및 그것의 제조방법을 제공하는데 있다.

본 발명이 이루고자 하는 또 다른 기술적 과제는 종래의 멀티 브릿지 채널 트랜지스터, GAA 트랜지스터 및 DELTA 구조의 트랜지스터의 장점을 모두 가지는 새로운 유형의 멀티 브릿지 채널 전계 효과 트랜지스터 및 그것의 제조방법을 제공하는데 있다.

### 발명의 구성

상기한 기술적 과제를 달성하기 위한 본 발명의 일 실시예에 따른 멀티 브릿지 채널 트랜지스터는 반도체 기판, 제1 액티브 패턴, 게이트 절연막 및 게이트 전극을 포함한다. 상기 제1 액티브 패턴은 상기 반도체 기판의 상면으로부터 이격되어 서 형성되어 있으며, 서로 이격되어 있는 1쌍의 소오스/드레인 패턴과 상기 1쌍의 소오스/드레인 패턴 사이에 서로 이격되어 개재되어 있되, 수평 방향으로 평행하게 어레이되어 있는 1쌍의 와이어 채널 패턴을 포함한다. 그리고, 상기 게이트 절연막은 상기 1쌍의 채널 패턴을 둘러싸도록 상기 채널 패턴의 외면에 형성되어 있다. 그리고, 상기 게이트 전극은 상기 게이트 절연막을 둘러싸도록 상기 1쌍의 소오스/드레인 패턴 사이에 형성되어 있다.

상기한 실시예의 일 측면에 의하면, 상기 모스 트랜지스터는 상기 제1 액티브 패턴을 지지하도록 상기 반도체 기판과 상기 소오스/드레인 패턴 사이에 개재되어 있는 액티브 지지용 패턴을 더 포함할 수 있다.

상기 실시예의 다른 측면에 의하면, 상기 와이어 채널 패턴의 단면은 완전 공핍형이 되도록 폭과 두께가 작는데, 상기 폭과 두께는 모두 약 10-20nm일 수 있다.

상기한 실시예의 또 다른 측면에 의하면, 상기 와이어 채널 패턴의 단면은 타원형일 수 있다.

상기한 실시예의 또 다른 측면에 의하면, 상기 모스 트랜지스터는 상기 제1 액티브 패턴과 동일한 형상을 가지되, 상기 제1 액티브 패턴의 상부에 소정의 거리로 이격되어서 적층되어 있는 제2 액티브 패턴을 더 포함할 수도 있다.

상기한 기술적 과제를 달성하기 위한 본 발명의 일 실시예에 따른 멀티 브릿지 채널 전계 효과 트랜지스터의 제조방법은 먼저, 반도체 기판 상에 n개의 희생층과 n개의 예비-액티브층이 교대로 적층되어 있는 액티브 형성용 스택을 형성하고, 상기 액티브 형성용 스택 상에 액티브 영역을 정의하는 마스크 패턴을 형성한다. 그리고, 상기 마스크 패턴을 식각 마스크로 사용하여 상기 액티브 형성용 스택층을 식각하여 액티브 형성용 스택 패턴을 형성하는데, 상기 액티브 형성용 스택 패턴은 n개의 희생층 패턴과 소오스/드레인 패턴 및 상기 소오스/드레인 패턴 사이에 개재되어 있는 예비-채널 패턴을 포함하는 n개의 예비-액티브 패턴을 포함하도록 식각 공정을 진행한다. 그리고, 상기 예비-채널 패턴 하부의 상기 희생층 패턴은 제거되고 상기 소오스/드레인 패턴 하부의 상기 희생층 패턴은 잔류하도록 상기 희생층 패턴을 식각하여 n개의 액티브 지지용 패턴을 형성한 다음, 상기 액티브 지지용 패턴, 상기 예비-액티브 패턴 및 상기 마스크 패턴을 둘러싸되, 상기 마스크 패

턴의 상면을 노출시키는 제1 베피층을 형성한다. 그리고, 상기 마스크 패턴 및 상기 제1 베피층을 패터닝함으로써 상기 예비-액티브 패턴의 상기 소오스/드레인 패턴의 상면을 노출시키는 더미 게이트 패턴을 형성하고, 상기 더미 게이트 패턴을 둘러싸여 상기 더미 게이트 패턴의 상면을 노출시키는 제2 베피층을 형성한 뒤에, 상기 더미 게이트 패턴에 잔류하는 상기 마스크 패턴을 제거함으로써 상기 예비-채널 패턴의 상면을 노출시키는 홀을 형성한다. 그리고, 상기 홀을 통하여 상기 예비-채널 패턴을 식각함으로써 1쌍의 와이어 채널 패턴을 형성한 다음, 상기 제2 베피층 및 잔류하는 상기 제1 베피층을 제거한다. 그리고, 상기 와이어 채널 패턴을 둘러싸도록 상기 와이어 채널 패턴의 외면에 게이트 절연막을 형성하고, 상기 게이트 절연막 상에 게이트 전극을 형성한다.

상기한 실시예의 일 측면에 의하면, 상기 n은 1 또는 2일 수 있다. 그리고, 상기 희생층은 단결정 실리콘 저매듭으로 형성하고, 상기 예비-액티브 층은 단결정 실리콘으로 형성할 수 있다. 또한, 상기 예비-액티브 층은 15-25nm의 두께로 형성할 수 있다.

상기한 실시예의 다른 측면에 의하면, 상기 액티브 형성용 스택 패턴을 형성한 이후에 상기 마스크 패턴을 트리밍하는 공정을 더 실시할 수도 있다.

상기한 실시예의 또 다른 측면에 의하면, 상기 액티브 형성용 스택 패턴을 형성할 때, 상기 마스크 패턴을 식각하여 상기 반도체 기판을 식각함으로써 상기 반도체 기판에 트렌치를 형성하는 공정을 동시에 수행하고, 상기 제1 베피층을 형성할 때, 상기 트렌치를 매립하는 소자 격리용 절연막을 형성하는 공정을 동시에 수행할 수 있다.

상기한 실시예의 또 다른 측면에 의하면, 상기 홀을 형성한 이후에 상기 홀에 의해 노출된 잔류하는 상기 제1 베피층 및 상기 제2 베피층의 측벽 상에 측벽 스페이서를 형성하는 공정을 더 수행하고, 상기 1쌍의 와이어 채널 패턴을 형성할 때 상기 측벽 스페이서를 식각 마스크로 사용할 수 있다. 이 경우, 상기 제1 베피층 및 상기 제2 베피층은 실리콘 산화물로 형성하고, 상기 측벽 스페이서는 실리콘 질화물로 형성할 수 있다. 또한, 상기 제2 베피층 및 잔류하는 상기 제1 베피층을 제거하기 이전에 상기 측벽 스페이서를 제거하는 공정을 더 실시할 수도 있다.

상기한 실시예의 또 다른 측면에 의하면, 상기 게이트 절연막을 형성하기 이전에 상기 와이어 채널 패턴을 트리밍하는 공정을 더 수행할 수도 있다. 또한, 상기 게이트 절연막을 형성하는 공정 이전에 상기 와이어 채널 패턴의 모서리가 둥글게 되도록 상기 와이어 채널 패턴을 열산화하는 공정을 더 수행할 수도 있다.

기타 실시예들의 구체적인 사항들은 상세한 설명 및 도면들에 포함되어 있다.

이하, 첨부된 도면들을 참조하여 본 발명의 바람직한 실시예들을 상세하게 설명하기로 한다. 그러나, 본 발명은 여기서 설명되어지는 실시예들에 한정되지 않고 다른 형태로 구체화될 수 있다. 오히려 여기서 소개되는 실시예들은 본 발명의 기술적 사상이 절저하고 완전하게 개시될 수 있도록 그리고 당업자에게 본 발명의 사상이 충분히 전달될 수 있도록 하기 위하여 예시적으로 제공되어지는 것들이다. 도면에 있어서, 층의 두께 및/또는 영역들의 크기 등은 명확성을 기하기 위하여 과장되어진 것이다. 명세서 전체에 걸쳐서 동일한 참조 번호는 동일한 구성요소를 나타낸다.

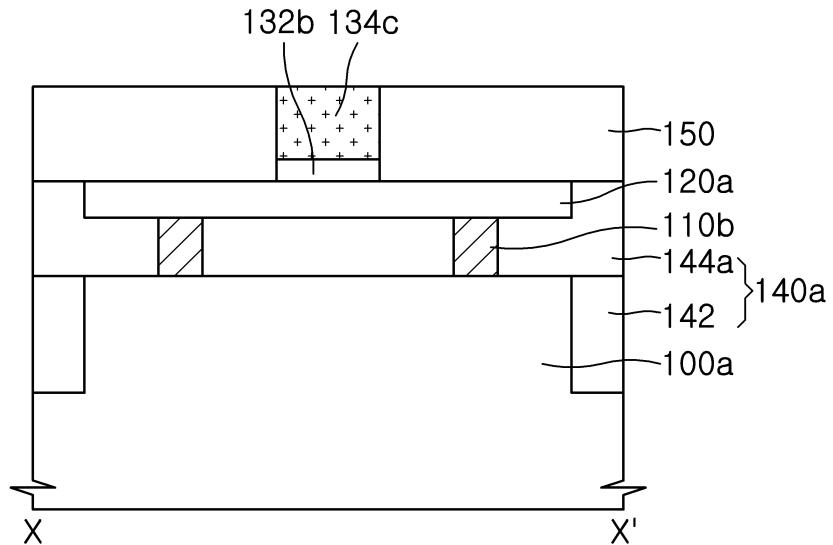

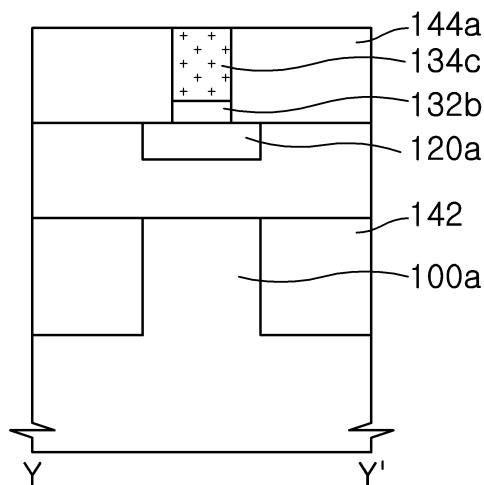

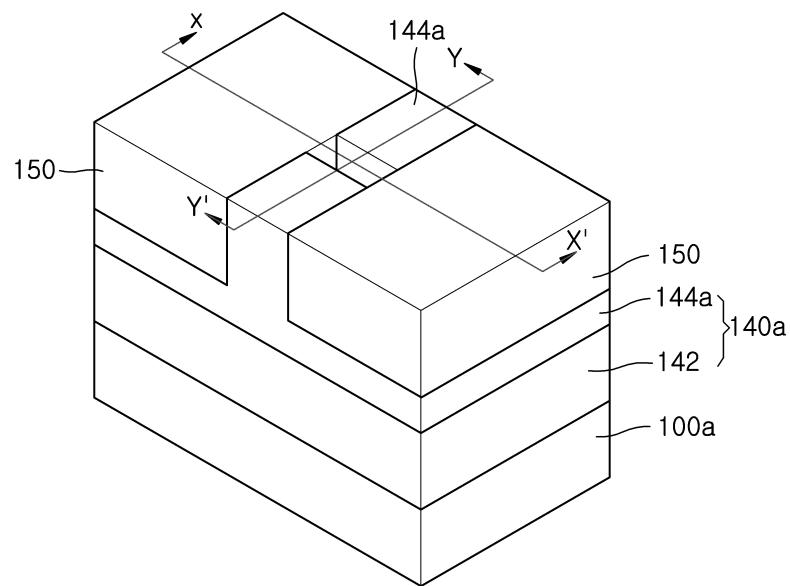

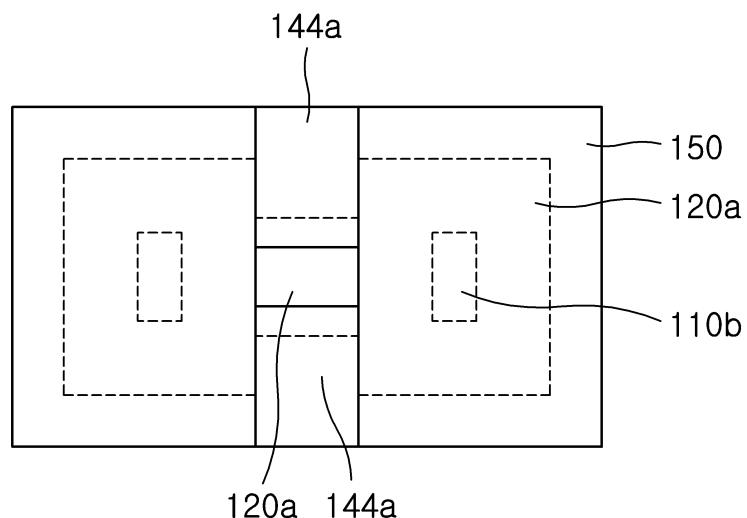

도 1 내지 도 12d에는 본 발명의 바람직한 일 실시예에 따른 다수의 나노 와이어 브릿지 채널을 구비한 전계 효과 트랜지스터 및 그것의 제조방법을 설명하기 위한 도면이 도시되어 있다. 상기 도면 중에서, 도 1, 도 2a, 도 3a, …, 도 12a는 사시도이고, 도 2b, 도 3b, …, 도 12b는 각각 도 2a, 도 3a, …, 도 12a에 대한 평면도이고, 도 2c, 도 3c, …, 도 12c는 각각 도 2a, 도 3a, …, 도 12a의 XX'라인을 따라 취한 단면도이고 그리고, 도 2d, 도 3d, …, 도 12d는 각각 도 2a, 도 3a, …, 도 12a의 YY'라인을 따라 취한 단면도이다.

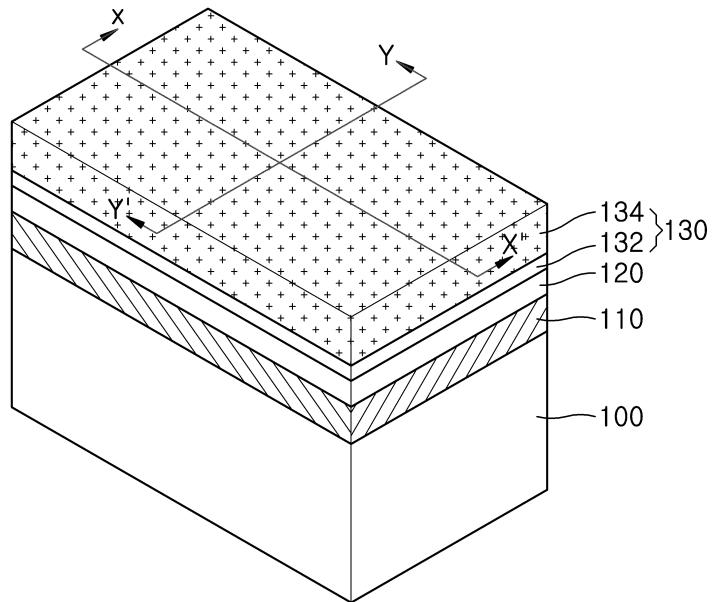

도 1은 본 발명의 일 실시예에 따른 다수의 나노 와이어 브릿지 채널을 구비한 모스 트랜지스터를 제조하기 위해 반도체 기판 상에 액티브 형성용 스택층과 마스크층을 형성한 단계를 나타내는 사시도이다.

도 1을 참조하면, 반도체 기판(100)의 표면 상에 먼저 희생층(110) 및 예비-액티브층(120)으로 구성된 액티브 형성용 스택층(110, 120)을 형성한다. 본 실시예에서 상기 반도체 기판(100)은 단결정 실리콘 기판인 것이 바람직하지만, 실리콘 저매듭층이나 실리콘-온-인슐레이터(SOI) 기판 또는 실리콘저매듭-온-인슐레이터(SGOI) 등일 수도 있다.

그리고, 액티브 형성용 스택층(110, 120)은 희생층(110)과 예비-액티브층(120)이 반복되어 적층되도록 형성한다. 예컨대, 액티브 형성용 스택층(110, 120)은 도시된 바와 같이 희생층(110)과 예비-액티브층(120)의 단층 구조일 수 있다. 또는, 액티브 형성용 스택층(110, 120)의 상부에 제2 희생층과 제2 예비-액티브층이 순차적으로 더 적층되어 있거나, 제2 예비-액티브층의 상부에 제3 희생층과 제3 예비-액티브층이 더 적층되어 있을 수도 있다. 반도체 기판(100)이 실리콘 기

관일 경우에, 희생층(110)은 실리콘에 대하여 식각 선택비가 큰 물질로 형성하는데, 예컨대, 실리콘 저매늄으로 약 20-50nm의 두께로 형성한다. 그리고, 예비-액티브층(120)은 희생층(110)에 대하여 식각 선택비가 큰 물질로 형성하는데, 예컨대 실리콘으로 약 20nm 또는 그 이하의 두께로 형성한다. 실리콘 저매늄 희생층(110)과 실리콘 예비-액티브층(120)은 두께 조정성이 뛰어난 에피택셜 성장법으로 형성할 수가 있다.

계속해서 도 1을 참조하면, 실리콘 에피택시층으로 형성된 예비-액티브층(120)의 전면에 식각 마스크 역할을 할 수 있는 마스크층(130)을 형성한다. 마스크층(130)은 통상적인 STI 형성 공정에서 사용하는 마스크층과 마찬가지로 활성 영역을 정의하기 위한 것이다. 예를 들어, 마스크층(130)은 패드 산화막(132)과 실리콘 질화막으로 형성된 하드 마스크막(134)의 복합막일 수 있다.

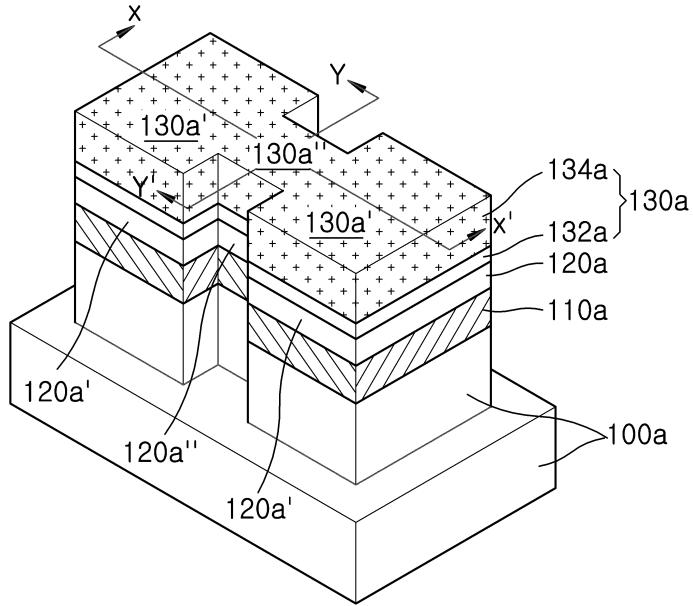

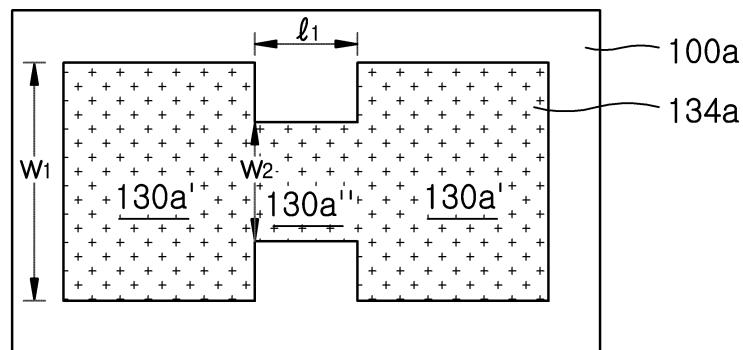

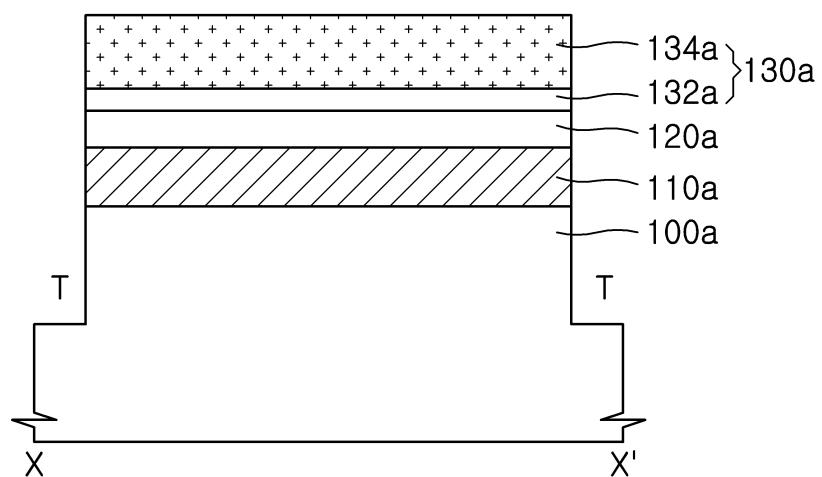

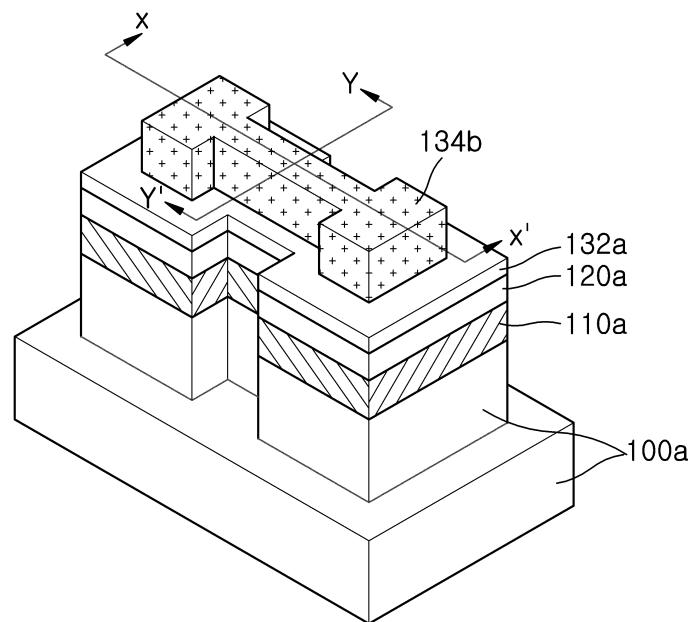

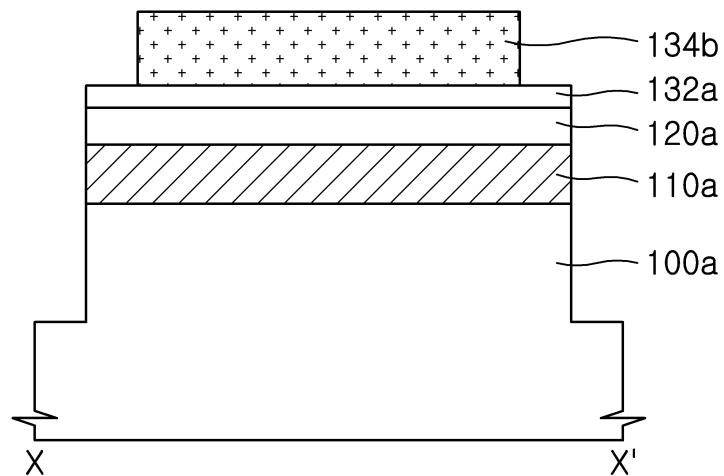

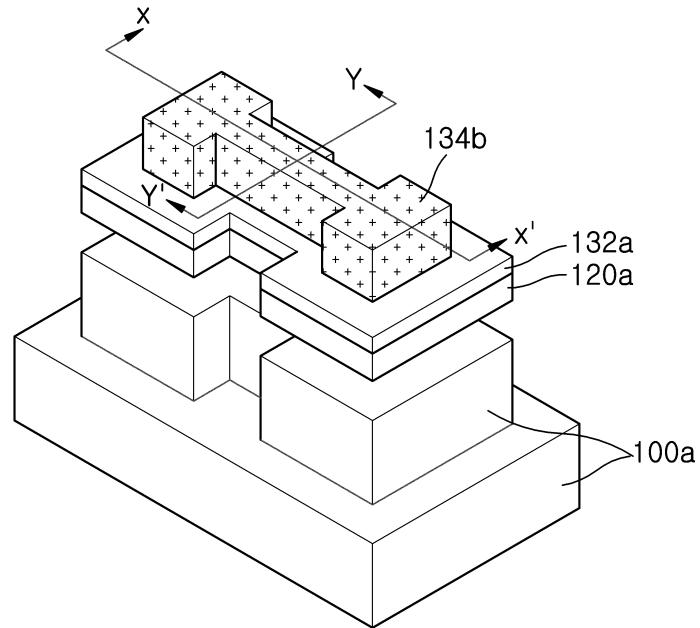

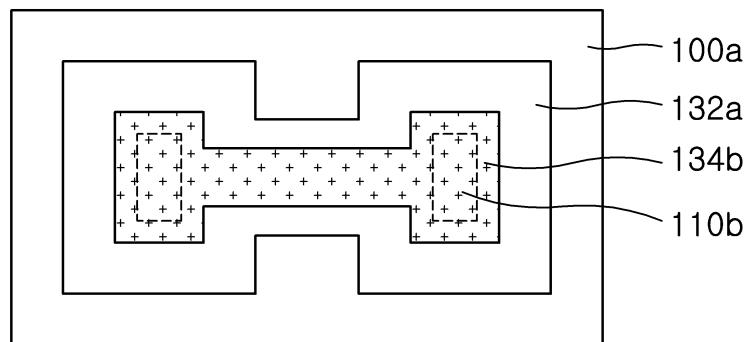

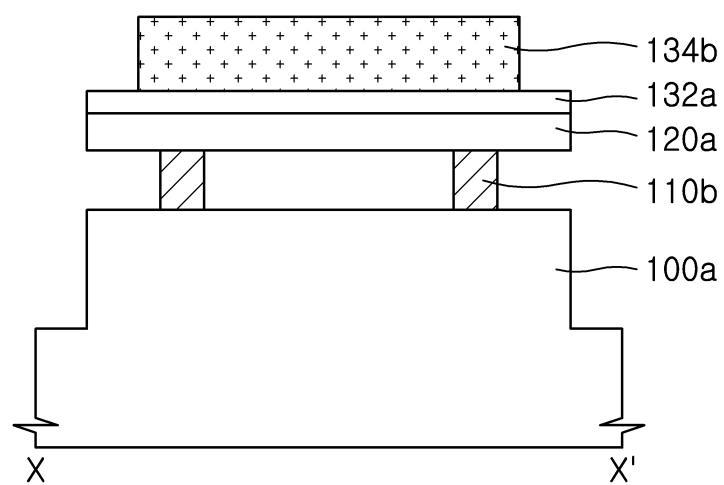

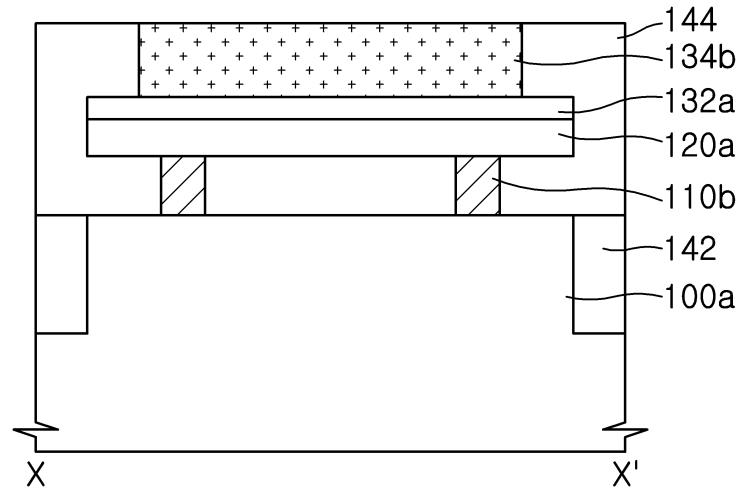

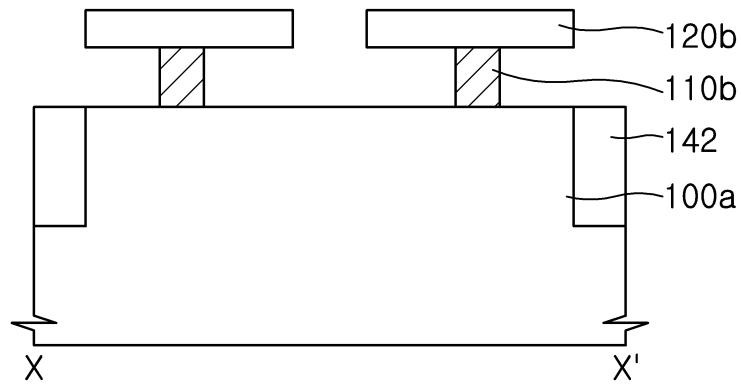

도 2a는 본 실시예에 따라 활성 영역을 정의하고 트렌치를 형성한 단계를 나타내는 사시도이다. 그리고, 도 2b는 도 2a에 대한 평면도이고, 도 2c는 도 2a의 XX'라인을 따라 취한 단면도이고, 도 2d는 도 2a의 YY'라인을 따라 취한 단면도이다.

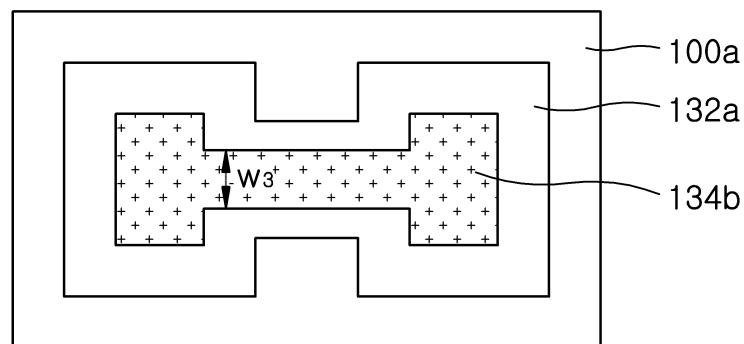

도 2a 내지 도 2d를 참조하면, 통상적인 포토리소그라피 공정을 사용하여 활성 영역을 한정하는 마스크 패턴(130a)을 형성한다. 본 실시예에서, 마스크 패턴(130a)은 패드 산화막 패턴(132a)과 하드 마스크 패턴(134a)을 포함할 수 있다. 그리고, 마스크 패턴(130a)을 식각 마스크로 사용하여 액티브 형성용 스택층(110, 120) 및 반도체 기판(100)을 순차적으로 이방성 식각함으로써, 액티브 형성용 스택 패턴(110a, 120a)을 형성하고 반도체 기판(100a)에는 STI형성을 위한 트렌치(T)를 형성한다. 액티브 형성용 스택 패턴(110a, 120a)은 희생 패턴(110a) 및 예비-액티브 패턴(120a)을 포함할 수 있다.

여기에서 마스크 패턴(130a)은 활성 영역을 한정하는데, 상기 마스크 패턴(130a)은 소오스/드레인 영역(120a')에 상응하는 영역(130a')의 사이에 위치하는 채널 영역(120a'')에 상응하는 영역(130a'')의 폭이 상대적으로 좁은 H와 같은 모양을 가지도록 한다. 즉, 마스크 패턴(130a)의 형성 단계에서는 채널 영역(120a'')에 상응하는 영역(130a'')의 폭( $w_2$ )이 소오스/드레인 영역(120a')에 상응하는 영역(130a')의 폭( $w_1$ )보다 작도록 마스크 패턴(130a)을 형성한다. 그리고, 채널 영역(120a'')에 상응하는 영역(130a'')의 길이는 디자인 룰을 고려하여 적절한 길이가 되도록 하는데, 최종 타겟으로 하는 채널의 길이와 같거나 이보다 약간 큰 것이 바람직하다.

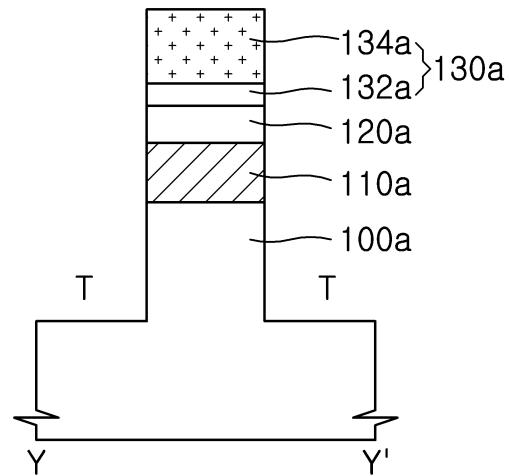

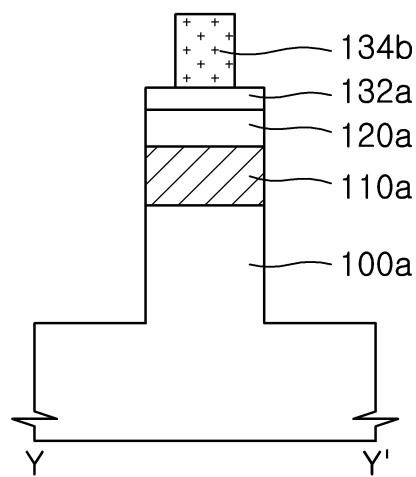

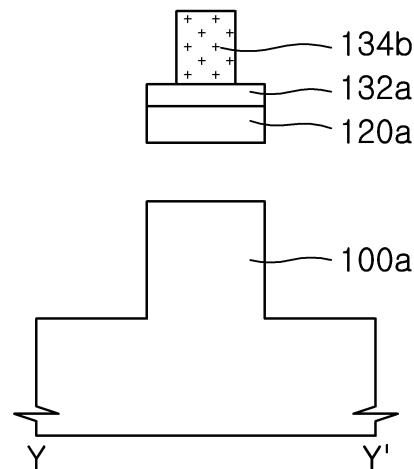

도 3a 내지 도 3d는 본 실시예에 따라 하드 마스크 패턴(134a)을 트리밍(trimming)하는 단계를 나타내는 사시도이다. 그리고, 도 3b는 도 3a에 대한 평면도이고, 도 3c는 도 3a의 XX'라인을 따라 취한 단면도이고, 도 3d는 도 2a의 YY'라인을 따라 취한 단면도이다.

도 3a 내지 도 3d를 참조하면, 화학적 건식 식각이나 습식 식각과 같은 등방성 식각 공정을 사용하여 하드 마스크 패턴(134a)을 트리밍하여 크기가 축소된 제2 하드 마스크 패턴(134b)을 형성한다. 하드 마스크 패턴(134a)이 실리콘 질화막으로 이루어진 경우에 인산 등을 포함하는 식각 매체를 사용하여 트리밍 공정을 수행할 수 있다. 상기 트리밍 공정은, 제2 하드 마스크 패턴(134b)의 채널 영역(120a'')에 상응하는 영역(134b'')의 폭( $w_3$ )을 줄이는 것을 일차적인 목적으로 하는 공정이다. 따라서, 이전 단계인 마스크 패턴(130a)의 형성 단계에서 채널 영역(120a'')에 상응하는 영역(134a'')의 폭( $w_2$ )을 100nm 이하가 되도록 충분히 작게 패터닝할 수 있는 경우에는, 하드 마스크 패턴(134a)의 트리밍 단계는 생략이 가능하다.

또한, 상기한 실시예의 일측면에 의하면, 하드 마스크 패턴(134a)을 트리밍하는 공정은, 마스크 패턴(130a)을 형성한 이후이고 상기 마스크 패턴(130a)을 식각 마스크로 사용하여 그 하부의 막 즉, 채널층(120), 희생층(110) 및 반도체 기판(100)을 이방성 건식 식각하는 단계 이전에 실시할 수도 있다. 이 방법에 의하면, 도면에 도시되어 있는 실시예에 비하여, 채널 영역(120a'')의 폭이 좁은 예비-액티브 패턴(120a)을 형성하는 것이 가능하다.

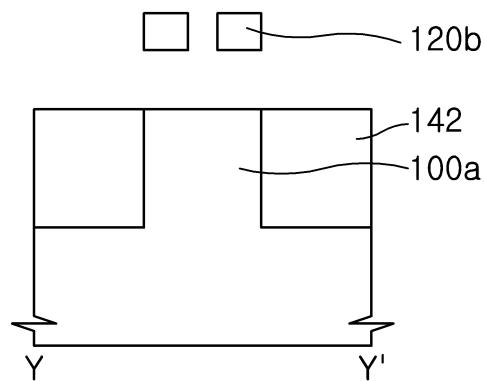

도 4a는 본 실시예에 따라 희생 패턴(110a)을 선택적으로 식각하는 단계를 나타내는 사시도이다. 그리고, 도 4b는 도 4a에 대한 평면도이고, 도 4c는 도 4a의 XX'라인을 따라 취한 단면도이고, 도 4d는 도 4a의 YY'라인을 따라 취한 단면도이다.

도 4a 내지 도 4d를 참조하면, 등방성 식각 공정을 사용하여 희생 패턴(110a)을 선택적으로 식각함으로써, 한 쌍의 액티브 지지 패턴(110b)을 형성한다. 한 쌍의 액티브 지지 패턴(110b)은 소오스/드레인 영역을 지지하는 역할을 하도록 그 하부에만 형성된다. 그러므로, 희생 패턴(110a)을 식각할 경우에, 채널 영역에 상응하는 희생 패턴(110a)의 영역은 완전히 식

각이 되도록 한다. 임의적 공정이지만, 한 쌍의 액티브 지지 패턴(110b)이 형성될 수 있도록 소오스/드레인 영역에 상응하는 영역을 마스크하는 포토 레지스트 패턴을 마스크 패턴(130a)의 상부에 더 형성한 후에, 희생 패턴(110a)을 선택적으로 식각하는 공정을 실시할 수도 있다.

희생 패턴(110a)은 습식 식각법 또는 화학적 건식 식각법을 사용하여 식각할 수 있다. 이 때, 반도체 기판(100a)과 예비 액티브 패턴(120a)에 대한 희생 패턴(110a)의 식각 선택비가 30 이상이 되는 조건으로 식각을 실시하는 것이 바람직하다. 예컨대, 반도체 기판(100a), 예비 액티브 패턴(120a) 및 희생 패턴(110a)이 각각 실리콘, 에피택시얼 실리콘 및 에피택시얼 실리콘 저매듭으로 형성된 경우에, 과산화수소( $H_2O_2$ ), 불화수소(HF) 및 초산( $CH_3COOH$ )을 포함하는 혼합액, 수산화암모늄( $NH_4OH$ ), 과산화수소( $H_2O_2$ ) 및 탈이온수( $H_2O$ )를 포함하는 혼합 용액 또는 과초산을 포함하는 식각액 등을 사용할 수 있다.

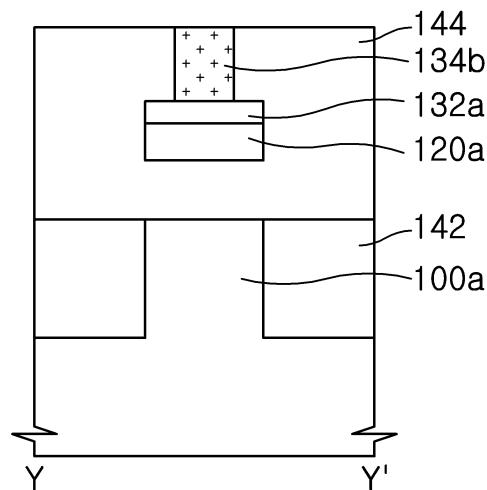

도 5a는 본 실시예에 따라 트렌치 매립용 절연막 및 제1 베퍼층을 형성하는 단계를 나타내는 사시도이다. 그리고, 도 5b는 도 5a에 대한 평면도이고, 도 5c는 도 5a의 XX'라인을 따라 취한 단면도이고, 도 5d는 도 5a의 YY'라인을 따라 취한 단면도이다.

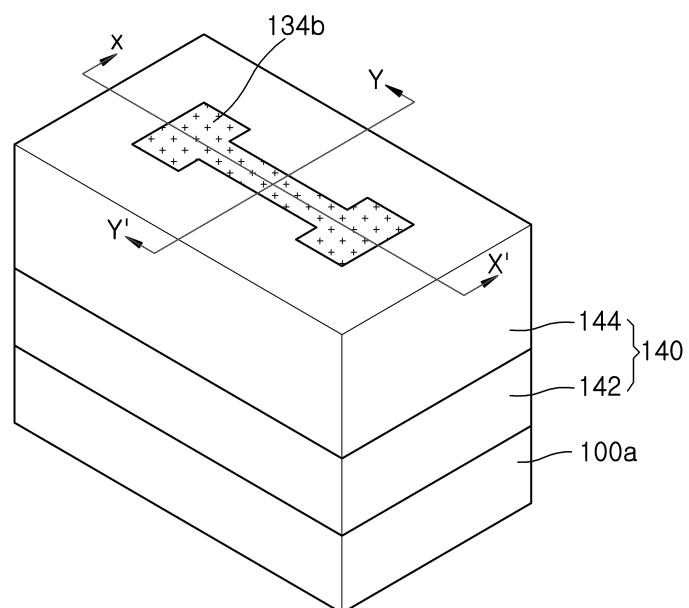

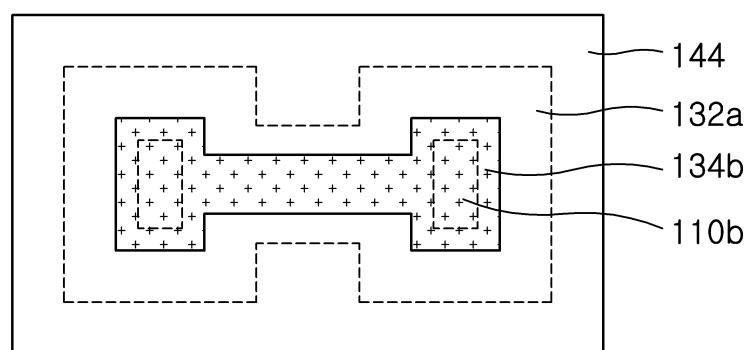

도 5a 내지 도 5d를 참조하면, 갭 충전(gap-fill) 특성이 우수한 HDP 산화막을 상기 결과물 상에 두껍게 증착한 다음, 축소된 하드 마스크 패턴(134b)의 상면이 노출될 때까지 평탄화 공정을 실시한다. 그 결과, 반도체 기판(100a)에 형성된 트렌치(T)를 매립하는 트렌치 매립용 절연막(142)이 형성됨과 동시에, 액티브 지지 패턴(110b), 예비-액티브 패턴(120a), 패드 산화막 패턴(132a) 및 축소된 하드 마스크 패턴(134b)을 둘러싸는 제1 베퍼층(144)이 형성된다.

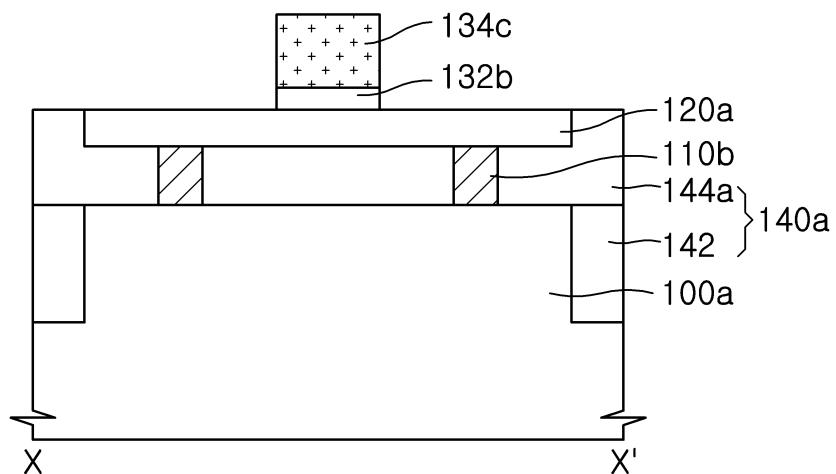

도 6a는 본 실시예에 따라 더미 게이트 패턴을 형성하는 단계를 나타내는 사시도이다. 그리고, 도 6b는 도 6a에 대한 평면도이고, 도 6c는 도 6a의 XX'라인을 따라 취한 단면도이고, 도 6d는 도 6a의 YY'라인을 따라 취한 단면도이다.

도 6a 내지 도 6d를 참조하면, 통상적인 포토 리스그라피 공정을 사용하여 상기 결과물, 보다 구체적으로는 제1 베퍼층(144), 마스크 패턴(132a, 134b)을 식각함으로써 게이트 라인이 형성될 방향으로 연장된 더미 게이트 패턴(132b, 134c 및 144a)을 형성한다. 그 결과, 더미 게이트 패턴(132b, 134c 및 144a)의 양 옆으로는 예비-액티브 패턴(120a)의 일부가 노출된다. 상기 노출된 예비-액티브 패턴(120a)은 소오스/드레인 영역으로서 역할을 할 액티브 패턴의 일 부분이다.

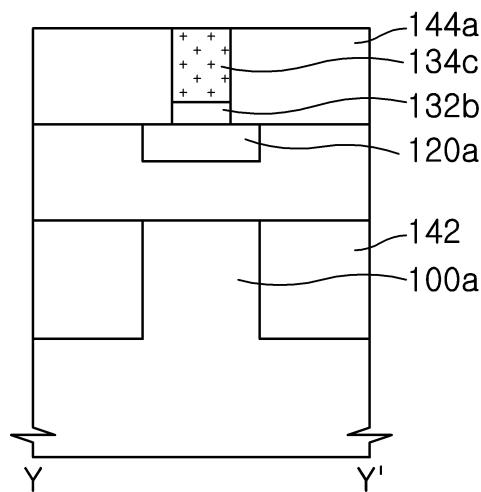

도 7a는 본 실시예에 따라 제2 베퍼층(150)을 형성하는 단계를 나타내는 사시도이다. 그리고, 도 7b는 도 7a에 대한 평면도이고, 도 7c는 도 7a의 XX'라인을 따라 취한 단면도이고, 도 7d는 도 7a의 YY'라인을 따라 취한 단면도이다.

도 7a 내지 도 7d를 참조하면, 중온 산화막(Middle temperature oxide, MTO)과 같은 절연 물질을 상기 결과물 상에 두껍게 증착한 다음, 마스크 패턴(134c)의 상면이 노출될 때까지 평탄화한다. 그 결과, 더미 게이트 패턴(132b, 134c 및 144a)을 둘러싸는 제2 베퍼층(150)이 형성된다.

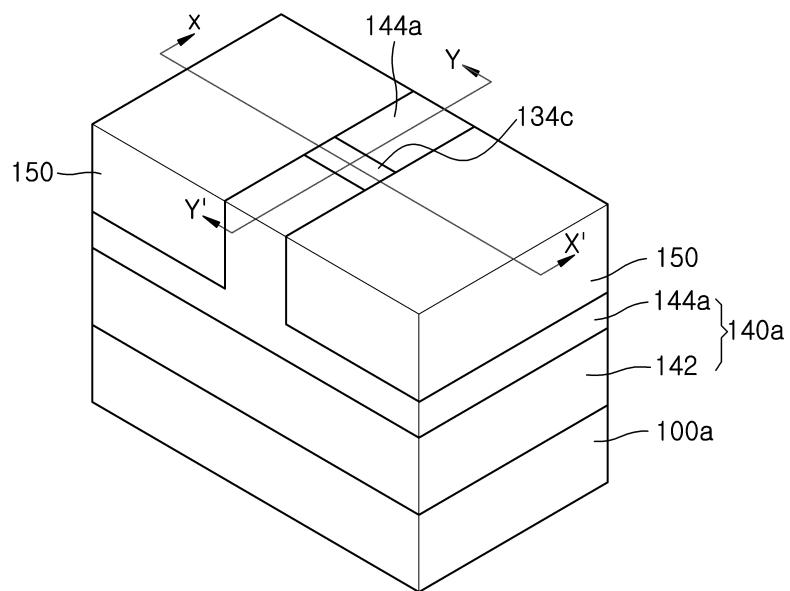

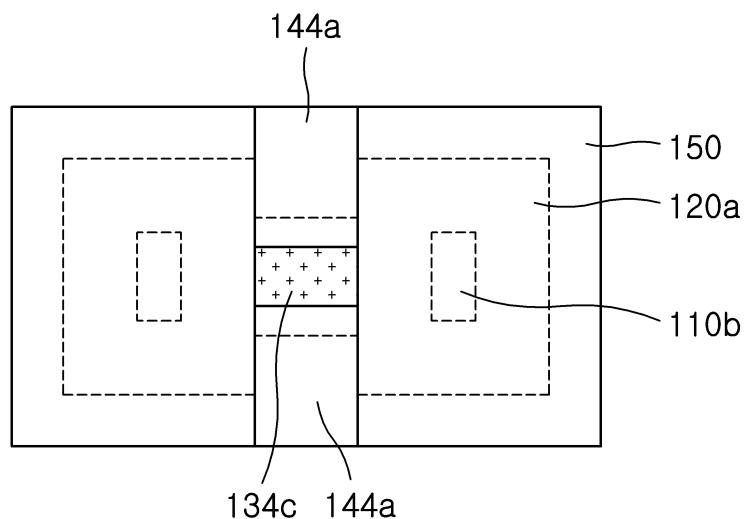

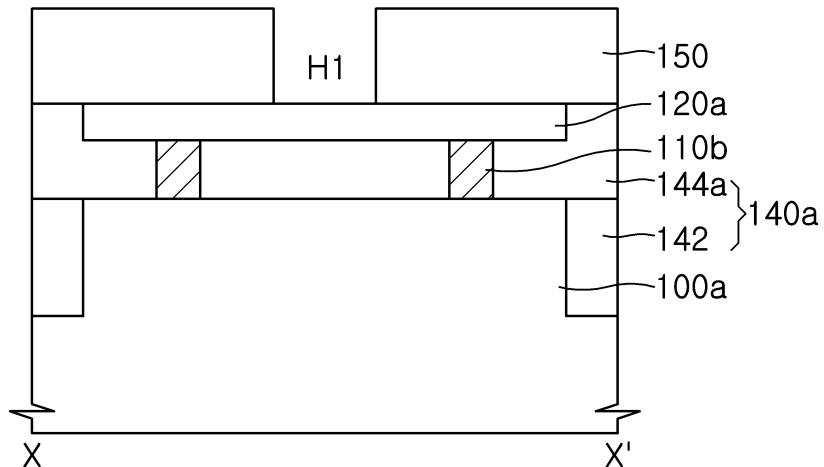

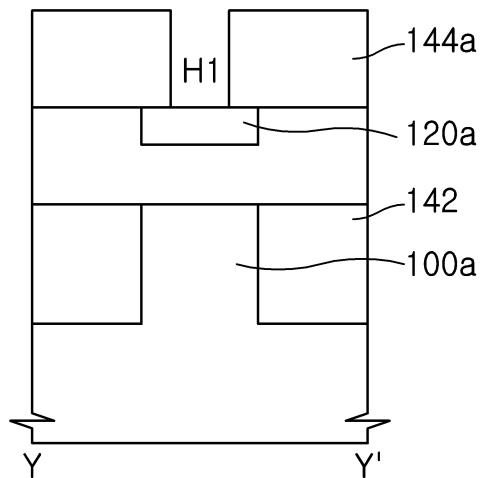

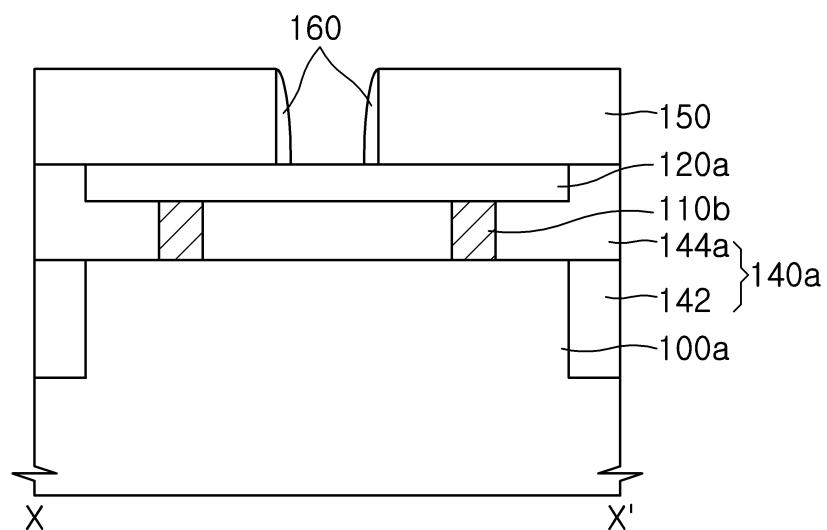

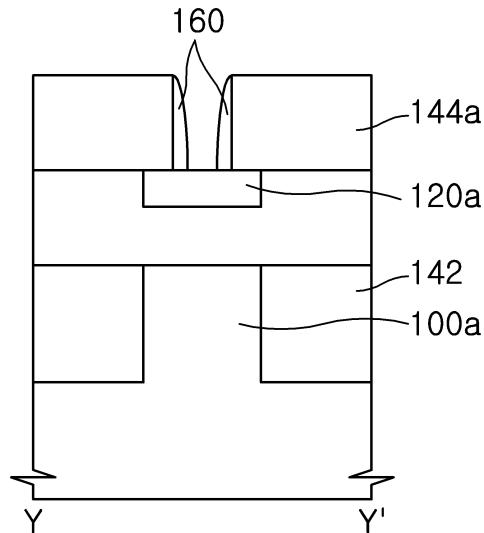

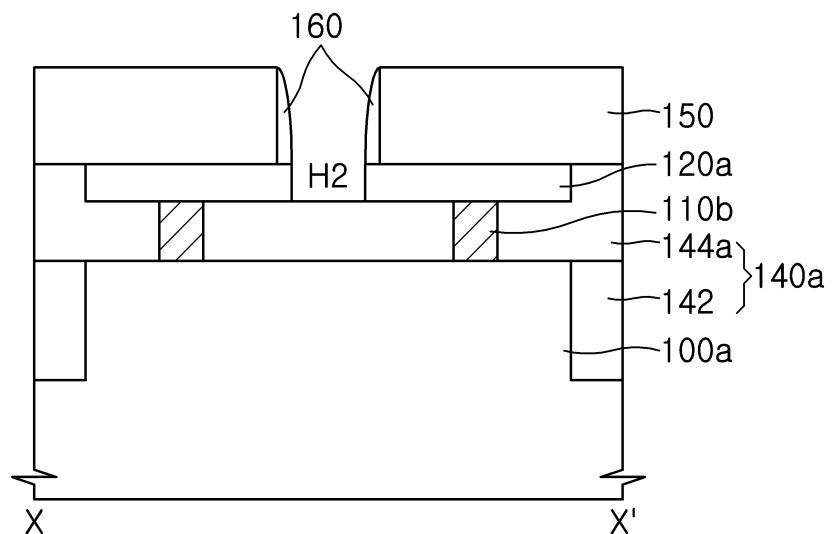

도 8a는 본 실시예에 따라 마스크 패턴(134c, 132b)을 제거하는 단계를 나타내는 사시도이다. 그리고, 도 8b는 도 8a에 대한 평면도이고, 도 8c는 도 8a의 XX'라인을 따라 취한 단면도이고, 도 8d는 도 8a의 YY'라인을 따라 취한 단면도이다.

도 8a 내지 도 8d를 참조하면, 더미 게이트 패턴(132b, 134c 및 144a)을 형성하는 하드 마스크 패턴(134c) 및 패드 산화막 패턴(132b)을 순차적으로 제거하여 제1 베퍼 패턴(144a) 및 제2 베퍼층(150)으로 둘러싸인 제1 홀(hole, H1)을 형성한다. 제1 홀(H1)을 통해서는 예비-액티브 패턴(120a)의 상면이 노출된다. 이 경우, 제1 홀(H1)을 형성하기 위하여 인산 스트립 등의 공정을 이용하여 노출된 실리콘 질화막의 하드 마스크 패턴(134c)을 먼저 제거한 다음, 연속적으로 노출된 패드 산화막 패턴(132b)을 제거하는 것이 바람직하다.

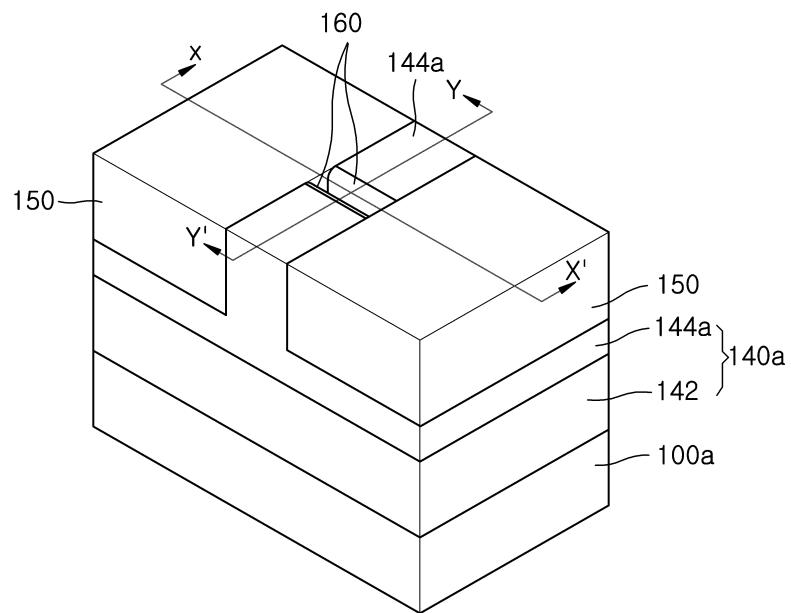

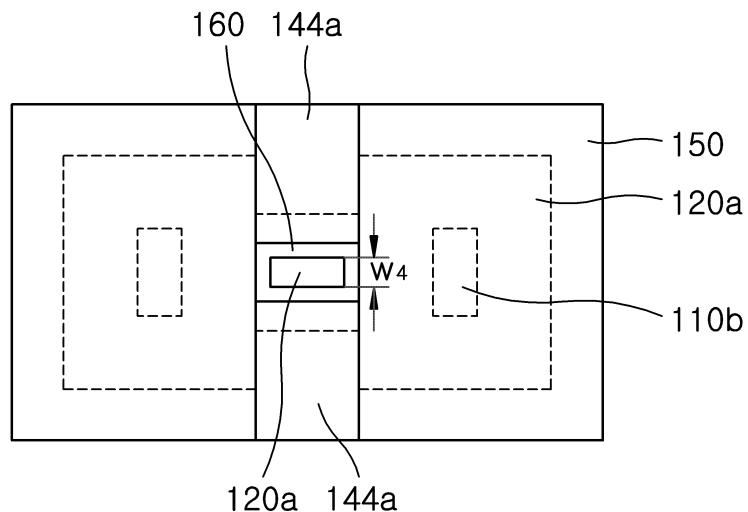

도 9a는 본 실시예에 따라 측벽 스페이서를 형성하는 단계를 나타내는 사시도이다. 그리고, 도 9b는 도 9a에 대한 평면도이고, 도 9c는 도 9a의 XX'라인을 따라 취한 단면도이고, 도 9d는 도 9a의 YY'라인을 따라 취한 단면도이다.

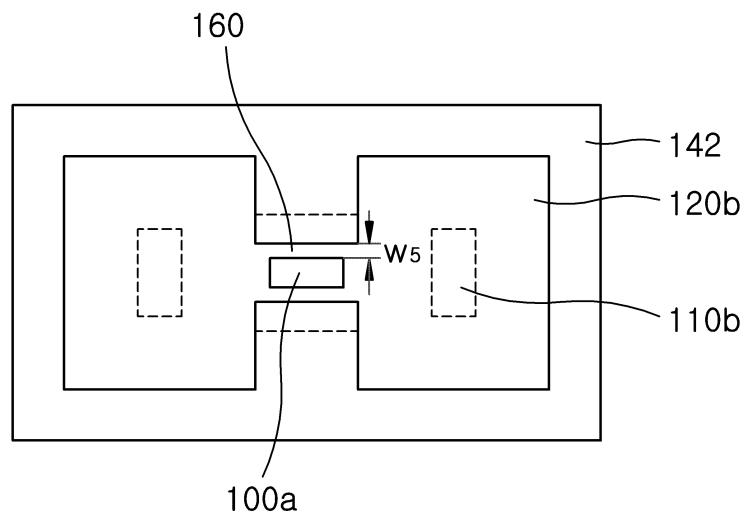

도 9a 내지 도 9d를 참조하면, 통상의 스페이서 형성 공정을 사용하여 제1 홀(H1)에 노출된 제1 베퍼 패턴(144a) 및 제2 베퍼층(150)의 측벽에 스페이서(160)를 형성한다. 스페이서(160)는 제1 홀(H1)의 폭( $w_4$ )을 줄임으로써 채널의 폭(도 11b의  $w_5$  참조)을 확보하기 위한 것이다. 그러므로, 이전 단계인 하드 마스크 패턴(134a)의 트리밍 단계에서 채널의 폭을 적절하게 확보한 경우에는 본 단계는 생략이 가능하다. 그러나, 하드 마스크 패턴(134a)의 트리밍 공정을 실시하지 않은

경우, 하드 마스크 패턴(134a)의 트리밍 공정에 의하여 채널의 폭이 적절하게 확보되지 않은 경우 또는 하드 마스크 패턴(134a)의 트리밍 공정을 실시한 이후에, 예비-액티브 패턴(120a)을 형성한 경우 등과 같이 필요하다고 생각하는 경우에는 스페이서(160) 형성 공정을 실시할 수 있다. 본 실시예에서 스페이서(160)는 실리콘 질화물로 형성하는 것이 바람직하다.

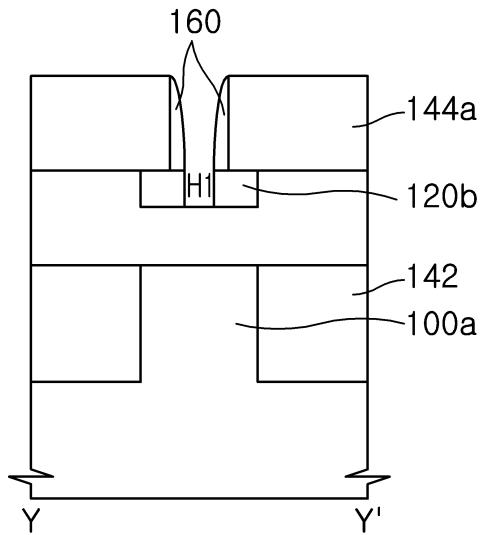

도 10a는 본 실시예에 따라 액티브 패턴을 형성하는 단계를 나타내는 사시도이다. 그리고, 도 10b는 도 10a에 대한 평면도이고, 도 10c는 도 10a의 XX'라인을 따라 취한 단면도이고, 도 10d는 도 10a의 YY'라인을 따라 취한 단면도이다.

도 10a 내지 도 10d를 참조하면, 스페이서(160), 제1 베퍼 패턴(144a) 및 제2 베퍼층(150)을 마스크로 사용하여 노출된 예비 액티브 패턴(120a)을 식각하여 제2 홀(H2)을 형성한다. 제2 홀(H2)을 통해서는 그 하부를 채우고 있는 제1 베퍼 패턴(144a)이 노출되는데, 상기 제2 홀(H2)에 의하여 액티브 패턴(120b)의 채널 영역(120b'')이 듀얼 타입으로 형성된다. 즉, 예비 액티브 패턴(120a)의 경우에는 채널 영역(120a'')이 단일의 판(plate) 형상이었지만, 액티브 패턴(120b)의 경우에는 채널 영역(120b'')이 상기 단일의 판 형상 채널 영역(120a'')이 2개로 나뉘어져서 2개의 와이어 형상이 된다.

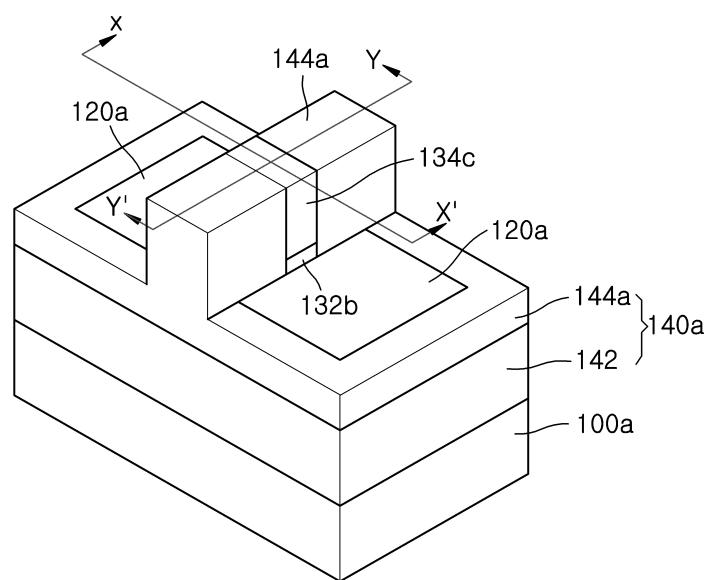

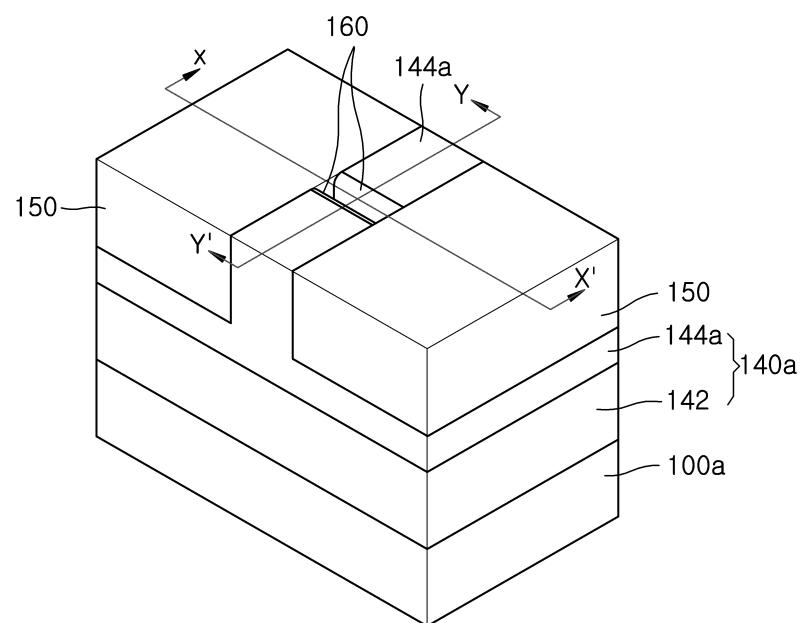

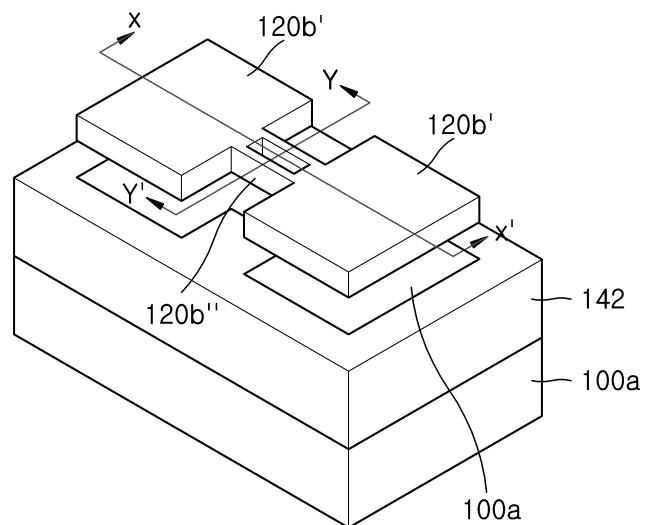

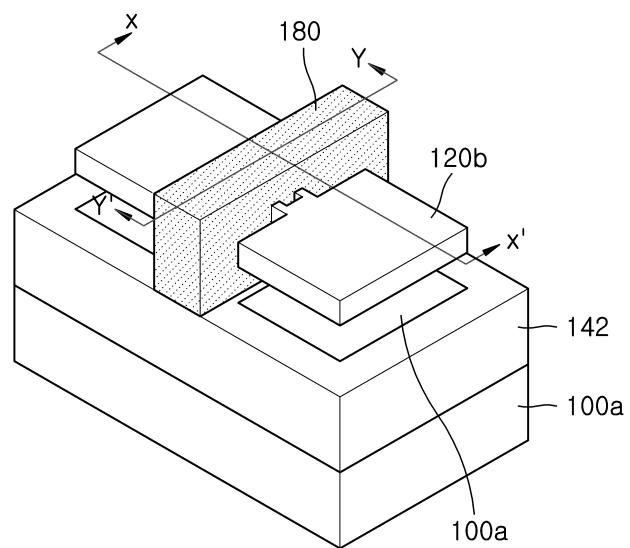

도 11a는 본 실시예에 따라 제1 베퍼 패턴(144a) 및 제2 베퍼층(150)을 제거하는 단계를 나타내는 사시도이다. 그리고, 도 11b는 도 11a에 대한 평면도이고, 도 11c는 도 11a의 XX'라인을 따라 취한 단면도이고, 도 11d는 도 11a의 YY'라인을 따라 취한 단면도이다.

도 11a 내지 도 11d를 참조하면, 먼저 실리콘질화막으로 형성된 스페이서(160)를 먼저 제거한다. 그리고, 통상적인 식각 공정을 사용하여 제1 베퍼 패턴(144a) 및 제2 베퍼층(150)을 제거한다. 이 경우, 공정 조건을 적절히 조절함으로써 제1 베퍼 패턴(144a) 하부의 트렌치 매립용 절연막(142)이 노출되는 레벨까지만 실리콘 산화막을 식각하는 것이 바람직하다. 그 결과, 도시된 바와 같이 채널 영역(120b'')이 공중에 떠 있는 형상이 된다.

계속해서, 임의적인 공정이지만, 액티브 패턴(120b)에 대한 트리밍 공정을 수행할 수 있다. 상기 트리밍 공정은 액티브 패턴(120b)의 채널 영역(120b'')의 크기를 줄여서 크기가 아주 작은 와이어 형상의 채널을 형성하기 위한 목적으로 수행한다. 예를 들어, 도 1에서 예비 액티브층(120)의 두께를 약 20nm로 형성한 경우에, 상기 트리밍 공정의 결과 채널 영역(120b'')의 두께 및/또는 폭을 10 내지 15nm 정도로 줄이는 것이 가능하다.

계속해서, 임의적인 공정이지만, 액티브 패턴(120b)이 그 상부에 형성되어 있는 반도체 기판(100a)을 1차로 어닐링한다. 1차 어닐링 공정은 채널 영역(120b)을 구성하는 각 채널 패턴의 단면의 모서리 부분을 둥글게 만들기 위한 것이다. 그러나, 채널 영역(120b'') 즉 와이어 형상의 채널 패턴의 단면이 사각형인 경우보다 타원형과 같이 둥근 형상인 경우에는, 게이트 전극에 의하여 전 방향으로 균일한 전압이 채널 패턴에 가해질 수 있을 뿐만 아니라 소자의 신뢰성 및 후속 공정과의 적합성 측면에서도 유리하기 때문에, 상기 1차 어닐링 공정은 수행하는 것이 보다 바람직하다.

1차 어닐링 공정은 채널 패턴(120b'')의 단면이 원형이 될 수 있는 적절한 온도에서 실시하는 것이 바람직하다. 예컨대, 수소 분위기에서 어닐링을 실시하는 경우에는 약 600 내지 1200°C의 온도에서 수행하는 것이 바람직하며, 아르곤 분위기에서 어닐링을 실시하는 경우에는 약 900 내지 1200°C의 온도에서 수행하는 것이 바람직하다. 1차 어닐링 공정에 의하여, 채널 패턴(120b'')의 단면의 크기가 약간 감소할 수 있는데, 그 감소 크기는 거의 무시할 수 있는 정도로 아주 작다.

상기한 공정의 결과물을 보여주는 도 11a에는 본 발명의 바람직한 실시예에 따른 멀티 브릿지 채널 전계 효과 트랜지스터의 액티브 패턴에 대한 사시도가 도시되어 있다.

도 11a를 참조하면, 액티브 패턴(120b)은 1쌍의 소오스/드레인 패턴(120b')과 서로 평행하게 어레이되어 있는 1쌍의 채널 패턴(120b'')을 포함한다. 채널 패턴(120b'')은 소오스/드레인 패턴(120b') 사이에 개재되어 있으며, 나노 와이어 형상인 것이 바람직하다. 여기서, "나노 와이어"란 그 크기, 즉 채널 패턴(120b'')의 수직 방향으로의 단면의 폭과 높이가 20nm 보다 작은 와이어 모양의 패턴을 지칭한다. 그리고, 소오스/드레인 패턴(120b')은 상기 채널 패턴(120b'')과 같은 두께를 가지는데, 그 전체가 소오스/드레인 영역으로서의 역할을 한다.

채널 패턴(120b'')의 길이는 디자인 룰 등을 고려하여 적절한 크기로 설정된다. 그리고, 채널 패턴(120b'')의 단면 모양 및/또는 크기는 전계 효과 트랜지스터의 전기적 특성 특히 전류 특성을 향상시킬 수 있도록 적절한 모양과 크기를 가지는 것이 바람직하다.

본 발명에 따르면, 채널 패턴(120b") 단면은 소위 등방성 채널이 형성될 수 있는 모양인 것이 바람직하다. 등방성 채널이 형성될 수 있는 채널 패턴(120b")의 단면의 모양은 예컨대 원형, 타원형 또는 가로 및 세로의 크기 차이가 작은 사각형 등이다. 이러한 채널 패턴의 모양은 게이트 전위가 사방에서 고르게 가해지기 때문에 캐리어의 스캐터링 효과를 감소시킬 수가 있기 때문에 나노 와이어 채널을 통하여 많은 전류가 흐르게 할 수 있다.

그리고, 채널 패턴(120b")의 단면은 게이트 전극에 소정의 전압이 인가된 경우에 채널 전체가 완전히 공핍될 수 있는 크기를 가지는 것이 바람직하다. 완전 공핍형이 될 수 있는 채널 패턴(120b")의 크기는 게이트 전압의 크기, 게이트 절연막의 특성과 두께 그리고 채널의 도핑 레벨에 따라 달라질 수 있다. 예컨대, 현재 평면 트랜지스터에서와 같이 반전층(inversion layer)의 두께가 약 10nm 정도가 되는 조건이라면, 채널 패턴(120b")의 크기는 약 10 내지 30nm 사이가 바람직하며, 약 20nm 이하가 되는 것이 보다 바람직하다.

그리고, 본 실시예에서는 단결정 실리콘으로 형성된 액티브 패턴(120b)은 단층의 구조물이다. 그러나, 이와 같은 단층 구조물은 예시적인 것으로서, 전술한 바와 같이 공정의 초기 단계에서 희생층(도 1의 참조 부호 110)과 예비-액티브층(도 1의 참조 부호 120)의 스택을 증가시킴으로써 액티브 패턴(120b)의 층 수도 증가시킬 수가 있다.

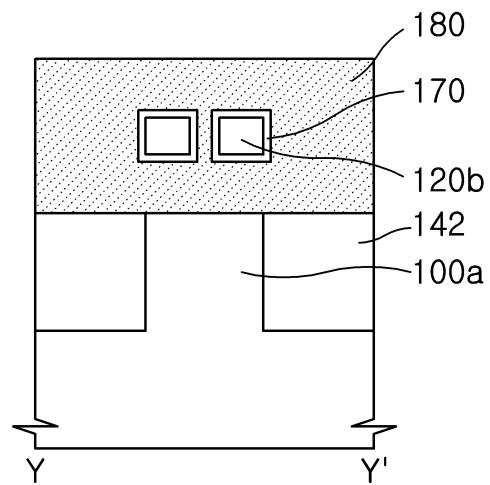

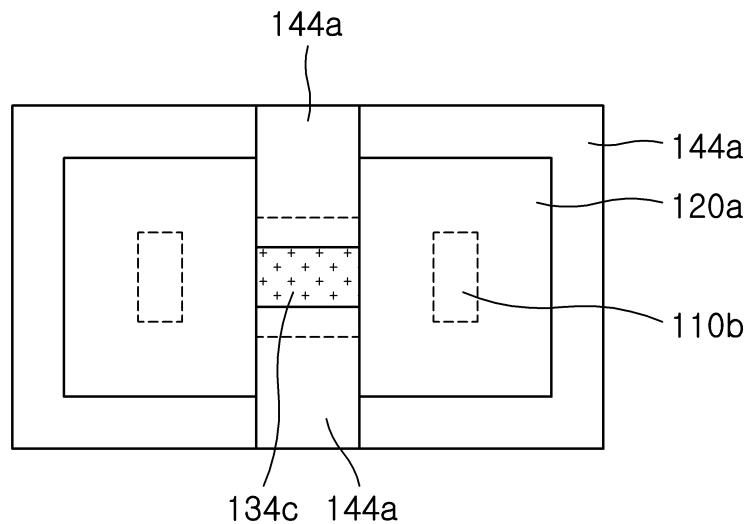

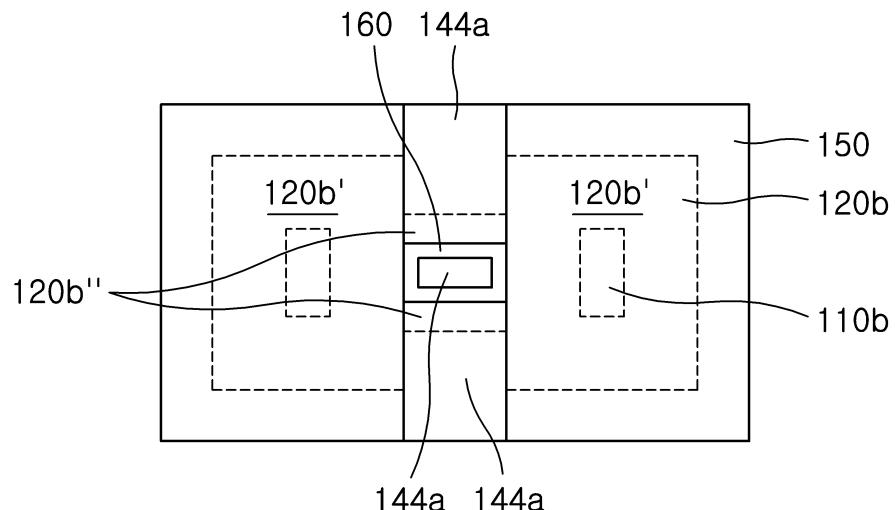

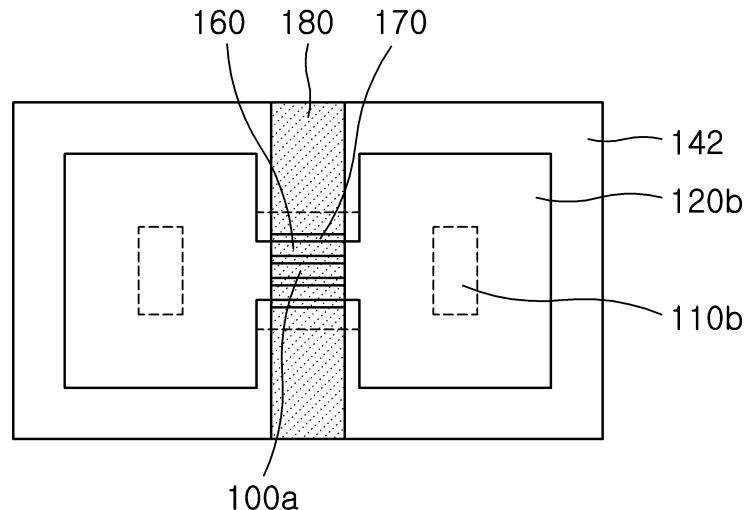

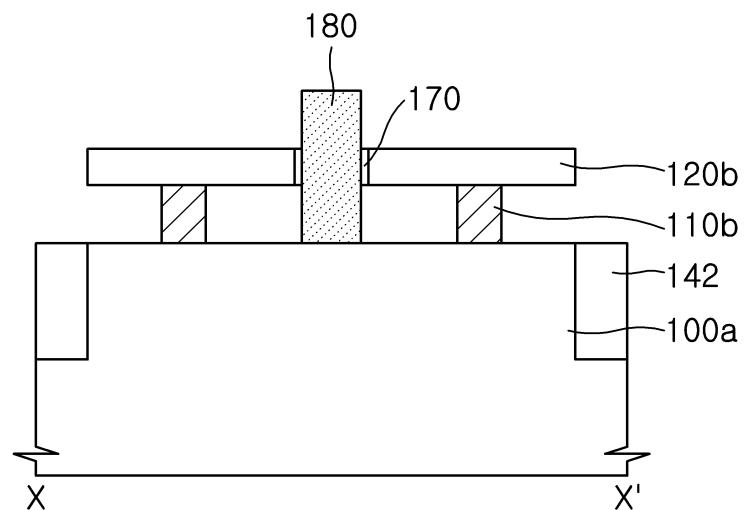

도 12a는 본 실시예에 따라 게이트 절연막 및 게이트 전극을 형성하는 단계를 보여주는 사시도가 도시되어 있다. 그리고, 도 12b는 도 12a에 대한 평면도이고, 도 12c는 도 12a의 XX'라인을 따라 취한 단면도이고, 도 12d는 도 12a의 YY'라인을 따라 취한 단면도이다.

도 12a 내지 도 12d를 참조하면, 게이트 절연막(170)을 형성하기 위하여, 상기 결과물을 산소 또는 오존 분위기에서 2차로 어닐링한다. 산소 등의 분위기에서 어닐링하면, 표면에 노출된 실리콘의 소모되면서 그 표면에 실리콘 산화막(170)이 형성된다. 2차 어닐링 공정의 온도 및 어닐링 시간은 형성하고자 하는 게이트 절연막(170)의 두께에 따라서 달라질 수 있다. 예컨대, 게이트 절연막(170)이 약 50 내지 100Å의 두께가 되도록 2차 어닐링 공정을 수행할 수 있다. 상기 2차 어닐링 공정의 결과, 액티브 패턴(120b)의 소오스/드레인 영역(120b')의 표면에도 실리콘 산화막(도시하지 않음)이 부수적으로 형성될 수 있다.

계속해서, 소오스/드레인 영역(120b') 사이의 게이트 절연막(170) 상에 즉, 채널 패턴(120b")을 둘러싸는 게이트 절연막(170) 상에 게이트 전극(180)을 형성한다. 게이트 전극(180)은 폴리 실리콘막의 단일막이나 또는 폴리 실리콘막 및 금속막 또는 금속 실리사이드막의 복합막으로 형성할 수 있다.

이후, 통상적인 반도체 제조 공정을 수행함으로써 전체 반도체 소자를 완성한다.

### 발명의 효과

본 발명에 따른 모스 트랜지스터는 와이어 구조의 채널을 게이트 전극이 완전히 둘러싸고 있다. 따라서, 채널 영역에 대한 게이트의 지배력이 현저해지기 때문에 단채널 효과가 발생하는 것을 방지할 수가 있다. 아울러, 인버전 영역이 적어도 와이어 채널의 외면에 따라서 형성된다. 그 결과, 채널이 폭이 증가하기 때문에 협채널 효과가 발생하는 것을 방지할 수 있다.

그리고, 본 발명에 따른 모스 트랜지스터는 와이어 구조의 채널이 완전 공핍형이 될 뿐만 아니라 등방성 채널 구조이다. 따라서, 본 발명에 의하면, 캐리어의 직진성을 향상시켜서 스캐터링 현상을 방지할 수 있기 때문에 트랜지스터의 고속 동작이 가능하며, 많은 전류를 반도체 소자에 적합하다.

또한, 본 발명에 의하면 와이어 구조의 채널 개수를 증가시키는 것이 용이하고 종래의 반도체 제조 공정을 적용하기 때문에 제조가 용이하다. 뿐만 아니라, 소오스/드레인 영역이 벌크 기판과 이격되어 있어서 누설 전류 방지에 효과적이기 때문에 고속으로 동작하면서 아울러 신뢰성 있는 모스 트랜지스터를 제조하는 것이 가능하다.

이상, 첨부된 도면 및 실시예에서는 본 발명의 전형적인 바람직한 실시예가 개시되어 있으며, 비록 특정한 용어를 사용하여 기술하였지만 이것들은 단지 일반적이고 묘사적인 의미로 사용된 것이지 청구항에 의하여 정해지는 본 발명의 사상을 제한하기 위하여 사용된 것은 아니다.

### 도면의 간단한 설명

도 1 내지 도 12d는 본 발명의 바람직한 일 실시예에 따른 다수의 나노 와이어 브릿지 채널을 구비한 전계 효과 트랜지스터의 제조방법을 공정 순서에 따라 도시한 도면으로서,

도 1, 도 2a, 도 3a, …, 도 12a는 사시도이고,

도 2b, 도 3b, …, 도 12b는 각각 도 2a, 도 3a, …, 도 12a에 대한 평면도이고,

도 2c, 도 3c, …, 도 12c는 각각 도 2a, 도 3a, …, 도 12a의 XX'라인을 따라 취한 단면도이고,

도 2d, 도 3d, …, 도 12d는 각각 도 2a, 도 3a, …, 도 12a의 YY'라인을 따라 취한 단면도이다.

### 도면

도면1

도면2a

도면2b

도면2c

도면2d

도면3a

도면3b

도면3c

도면3d

도면4a

도면4b

도면4c

도면4d

도면5a

도면5b

도면5c

도면5d

도면6a

도면6b

도면6c

도면6d

도면7a

도면7b

도면7c

도면7d

도면8a

도면8b

도면8c

도면8d

도면9a

### 도면9b

### 도면9c

도면9d

도면10a

도면10b

도면10c

도면10d

도면11a

도면11b

도면11c

도면11d

도면12a

도면12b

도면12c

도면12d