【公報種別】特許法第17条の2の規定による補正の掲載

【部門区分】第7部門第2区分

【発行日】令和1年10月31日(2019.10.31)

【公開番号】特開2017-157816(P2017-157816A)

【公開日】平成29年9月7日(2017.9.7)

【年通号数】公開・登録公報2017-034

【出願番号】特願2016-193919(P2016-193919)

【国際特許分類】

|        |        |           |

|--------|--------|-----------|

| H 01 L | 27/146 | (2006.01) |

| H 01 L | 31/10  | (2006.01) |

| H 01 L | 27/14  | (2006.01) |

| H 04 N | 5/369  | (2011.01) |

| H 04 N | 5/374  | (2011.01) |

【F I】

|        |       |       |

|--------|-------|-------|

| H 01 L | 27/14 | E     |

| H 01 L | 31/10 | H     |

| H 01 L | 27/14 | D     |

| H 04 N | 5/335 | 6 9 0 |

| H 04 N | 5/335 | 7 4 0 |

| H 01 L | 27/14 | A     |

【手続補正書】

【提出日】令和1年9月18日(2019.9.18)

【手続補正1】

【補正対象書類名】明細書

【補正対象項目名】0002

【補正方法】変更

【補正の内容】

【0002】

光電変換層に有機半導体材料を用いる撮像素子は、特定の色（波長帯）を光電変換することが可能である。そして、このような特徴を有するが故に、固体撮像装置における撮像素子として用いる場合、オンチップ・カラーフィルタ(OCCF)と撮像素子との組合せから副画素が成り、副画素が2次元配列されている、従来の固体撮像装置では不可能な、副画素を積層した構造（積層型撮像素子）を得ることが可能である（例えば、特開2011-138927参照）。また、デモザイク処理を必要としないことから、偽色が発生しないといった利点がある。尚、以下の説明において、半導体基板の上あるいは上方に設けられた光電変換部を備えた撮像素子を、便宜上、『第1タイプの撮像素子』と呼び、第1タイプの撮像素子を構成する光電変換部を、便宜上、『第1タイプの光電変換部』と呼び、半導体基板内に設けられた撮像素子を、便宜上、『第2タイプの撮像素子』と呼び、第2タイプの撮像素子を構成する光電変換部を、便宜上、『第2タイプの光電変換部』と呼ぶ場合がある。

【手続補正2】

【補正対象書類名】明細書

【補正対象項目名】0013

【補正方法】変更

【補正の内容】

【0013】

本開示の撮像素子、本開示の積層型撮像素子を構成する本開示の撮像素子、本開示の第1の態様～第2の態様に係る固体撮像装置を構成する本開示の撮像素子（これらの撮像素

子を総称して、以下、『本開示の撮像素子等』と呼ぶ場合がある)にあっては、第1電極と離間して配置され、且つ、絶縁層を介して光電変換層と対向して配置された電荷蓄積用電極が備えられているので、光電変換部に光が照射され、光電変換部において光電変換されるとき、光電変換層に電荷を蓄えることができる。それ故、露光開始時、電荷蓄積部を完全空乏化し、電荷を消去することが可能となる。その結果、KTCノイズが大きくなり、ランダムノイズが悪化し、撮像画質の低下をもたらすといった現象の発生を抑制することができる。本開示の固体撮像装置の駆動方法にあっては、各撮像素子は、第2電極側から入射した光が第1電極には入射しない構造を有し、全ての撮像素子において、一齊に、光電変換層に電荷を蓄積しながら、第1電極における電荷を系外に排出するので、全撮像素子において同時に第1電極のリセットを確実に行うことができる。そして、その後、全ての撮像素子において、一齊に、光電変換層に蓄積された電荷を第1電極に転送し、転送完了後、順次、各撮像素子において第1電極に転送された電荷を読み出す。それ故、所謂グローバルシャッター機能を容易に実現することができる。尚、本明細書に記載された効果はあくまで例示であって限定されるものでは無く、また、付加的な効果があつてもよい。

### 【手続補正3】

【補正対象書類名】明細書

【補正対象項目名】0029

【補正方法】変更

【補正の内容】

【0029】

本開示の積層型撮像素子は、少なくとも本開示の撮像素子(光電変換素子)を1つ有するが、具体的には、例えば、

[A] 第1タイプの青色用光電変換部、第1タイプの緑色用光電変換部及び第1タイプの赤色用光電変換部が、垂直方向に積層され、

第1タイプの青色用撮像素子、第1タイプの緑色用撮像素子及び第1タイプの赤色用撮像素子の制御部のそれぞれが、半導体基板に設けられた構成、構造

[B] 第1タイプの青色用光電変換部及び第1タイプの緑色用光電変換部が、垂直方向に積層され、

これらの2層の第1タイプの光電変換部の下方に、第2タイプの赤色用光電変換部が配置され、

第1タイプの青色用撮像素子、第1タイプの緑色用撮像素子及び第2タイプの赤色用撮像素子の制御部のそれぞれが、半導体基板に設けられた構成、構造

[C] 第1タイプの緑色用光電変換部の下方に、第2タイプの青色用光電変換部及び第2タイプの赤色用光電変換部が配置され、

第1タイプの緑色用撮像素子、第2タイプの青色用撮像素子及び第2タイプの赤色用撮像素子の制御部のそれぞれが、半導体基板に設けられた構成、構造

[D] 第1タイプの青色用光電変換部の下方に、第2タイプの緑色用光電変換部及び第2タイプの赤色用光電変換部が配置され、

第1タイプの青色用撮像素子、第2タイプの緑色用撮像素子及び第2タイプの赤色用撮像素子の制御部のそれぞれが、半導体基板に設けられた構成、構造を挙げることができる。尚、これらの撮像素子の光電変換部の垂直方向における配置順は、光入射方向から青色用光電変換部、緑色用光電変換部、赤色用光電変換部の順、あるいは、光入射方向から緑色用光電変換部、青色用光電変換部、赤色用光電変換部の順であることが好ましい。これは、より短い波長の光がより入射表面側において効率良く吸収されるからである。赤色は3色の中では最も長い波長であるので、光入射面から見て赤色用光電変換部を最下層に位置させることが好ましい。これらの撮像素子の積層構造によって、1つの画素が構成される。また、第1タイプの赤外線用光電変換部を備えていてもよい。ここで、第1タイプの赤外線用光電変換部の光電変換層は、例えば、有機系材料から構成され、第1タイプの撮像素子の積層構造の最下層であって、第2タイプの撮像素子よりも

上に配置することが好ましい。あるいは又、第1タイプの光電変換部の下方に、第2タイプの赤外線用光電変換部を備えていてもよい。

#### 【手続補正4】

【補正対象書類名】明細書

【補正対象項目名】0035

【補正方法】変更

【補正の内容】

【0035】

あるいは又、光電変換層を、下層半導体層と、上層光電変換層の積層構造とすることができます。このように下層半導体層を設けることで、電荷蓄積時の再結合を防止することができ、光電変換層に蓄積した電荷の第1電極への転送効率を増加させることができるし、暗電流の生成を抑制することができる。上層光電変換層を構成する材料は、上記の光電変換層を構成する各種材料から、適宜、選択すればよい。一方、下層半導体層を構成する材料として、バンドギャップエネルギーの値が大きく（例えば、3.0 eV以上のバンドギャップエネルギーの値）、しかも、光電変換層を構成する材料よりも高い移動度を有する材料を用いることが好ましい。具体的には、IGZO等の酸化物半導体材料；遷移金属ダイカルコゲナイト；シリコンカーバイド；ダイヤモンド；グラフェン；カーボンナノチューブ；縮合多環炭化水素化合物や縮合複素環化合物等の有機半導体材料を挙げることができる。あるいは又、下層半導体層を構成する材料として、蓄積すべき電荷が正孔である場合、光電変換層を構成する材料のイオン化ポテンシャルよりも小さなイオン化ポテンシャルを有する材料を挙げができるし、蓄積すべき電荷が電子である場合、光電変換層を構成する材料の電子親和力よりも大きな電子親和力を有する材料を挙げができる。あるいは又、下層半導体層を構成する材料における不純物濃度は  $1 \times 10^{18} \text{ cm}^{-3}$  以下であることが好ましい。下層半導体層は、単層構成であってもよいし、多層構成であってもよい。また、電荷蓄積用電極の上方に位置する下層半導体層を構成する材料と、第1電極の上方に位置する下層半導体層を構成する材料とを、異ならせてよい。

#### 【手続補正5】

【補正対象書類名】明細書

【補正対象項目名】0041

【補正方法】変更

【補正の内容】

【0041】

積層型撮像素子を構成する場合、第1電極、電荷蓄積用電極、転送制御用電極、電荷排出電極及び第2電極は透明導電材料から成る構成とすることができます。尚、第1電極、電荷蓄積用電極、転送制御用電極及び電荷排出電極を総称して、『第1電極等』と呼ぶ場合がある。あるいは又、本開示の撮像素子等が、例えばペイヤ配列のように平面に配される場合には、第2電極は透明導電材料から成り、第1電極は金属材料から成る構成とすることができます、この場合、具体的には、光入射側に位置する第2電極は透明導電材料から成り、第1電極等は、例えば、Al-Nd（アルミニウム及びネオジウムの合金）又はASC（アルミニウム、サマリウム及び銅の合金）から成る構成とすることができます。尚、透明導電材料から成る電極を『透明電極』と呼ぶ場合がある。ここで、透明導電材料のバンドギャップエネルギーは、2.5 eV以上、好ましくは3.1 eV以上であることが望ましい。透明電極を構成する透明導電材料として、導電性のある金属酸化物を挙げることができ、具体的には、酸化インジウム、インジウム-錫酸化物(ITO, Indium Tin Oxide, SnドープのIn<sub>2</sub>O<sub>3</sub>、結晶性ITO及びアモルファスITOを含む)、酸化亜鉛にドーパントとしてインジウムを添加したインジウム-亜鉛酸化物(IZO, Indium Zinc Oxide)、酸化ガリウムにドーパントとしてインジウムを添加したインジウム-ガリウム酸化物(IGO)、酸化亜鉛にドーパントとしてインジウムとガリウムを添加したインジウム-ガリウム-亜鉛酸化物(IGZO, In-Ga-ZnO<sub>4</sub>)、酸化亜鉛にドーパントとしてインジウムと錫を添加したインジウム-錫-亜鉛酸化物(ITZO)、IFO(Fド-

プの  $In_2O_3$  )、酸化錫 (  $SnO_2$  )、ATO ( Sb ドープの  $SnO_2$  )、FTO ( F ドープの  $SnO_2$  )、酸化亜鉛 ( 他元素をドープした  $ZnO$  を含む )、酸化亜鉛にドーパントとしてアルミニウムを添加したアルミニウム - 亜鉛酸化物 ( AZO )、酸化亜鉛にドーパントとしてガリウムを添加したガリウム - 亜鉛酸化物 ( GZO )、酸化チタン (  $TiO_2$  )、酸化チタンにドーパントとしてニオブを添加したニオブ - チタン酸化物 ( TNO )、酸化アンチモン、スピネル型酸化物、 $YbFe_2O_4$  構造を有する酸化物を例示することができる。あるいは又、ガリウム酸化物、チタン酸化物、ニオブ酸化物、ニッケル酸化物等を母層とする透明電極を挙げることができる。透明電極の厚さとして、 $2 \times 10^{-8} m$  乃至  $2 \times 10^{-7} m$ 、好ましくは  $3 \times 10^{-8} m$  乃至  $1 \times 10^{-7} m$  を挙げることができる。第 1 電極が透明性を要求される場合、製造プロセスの簡素化といった観点から、電荷排出電極も透明導電材料から構成することが好ましい。

## 【手続補正 6】

【補正対象書類名】明細書

【補正対象項目名】0044

【補正方法】変更

【補正の内容】

## 【0044】

絶縁層を構成する材料として、酸化ケイ素系材料；窒化ケイ素 ( $SiNy$ )；酸化アルミニウム ( $Al_2O_3$ ) 等の金属酸化物高誘電絶縁材料に例示される無機系絶縁材料だけでなく、ポリメチルメタクリレート (PMMA)；ポリビニルフェノール (PVP)；ポリビニルアルコール (PVA)；ポリイミド；ポリカーボネート (PC)；ポリエチレンテレフタレート (PET)；ポリスチレン；N-2(アミノエチル)3-アミノプロピルトリメトキシシラン (AEAPTMS)、3-メルカプトプロピルトリメトキシシラン (MPTMS)、オクタデシルトリクロロシラン (OTS) 等のシラノール誘導体 (シランカップリング剤)；ノボラック型フェノール樹脂；フッ素系樹脂；オクタデカンチオール、ドデシルイソシアネイト等の一端に制御電極と結合可能な官能基を有する直鎖炭化水素類にて例示される有機系絶縁材料 (有機ポリマー) を挙げることができるし、これらの組み合わせを用いることもできる。尚、酸化ケイ素系材料として、酸化シリコン ( $SiO_x$ )、BPSG、PSG、BSG、ASSG、PbSG、酸化窒化シリコン ( $SiON$ )、SOG (スピンオングラス)、低誘電率材料 (例えば、ポリアリールエーテル、シクロパーカルオロカーボンポリマー及びベンゾシクロブテン、環状フッ素樹脂、ポリテトラフルオロエチレン、フッ化アリールエーテル、フッ化ポリイミド、アモルファスカーボン、有機SOG) を例示することができる。各種層間絶縁層や絶縁膜を構成する材料も、これらの材料から適宜選択すればよい。

## 【手続補正 7】

【補正対象書類名】明細書

【補正対象項目名】0079

【補正方法】変更

【補正の内容】

## 【0079】

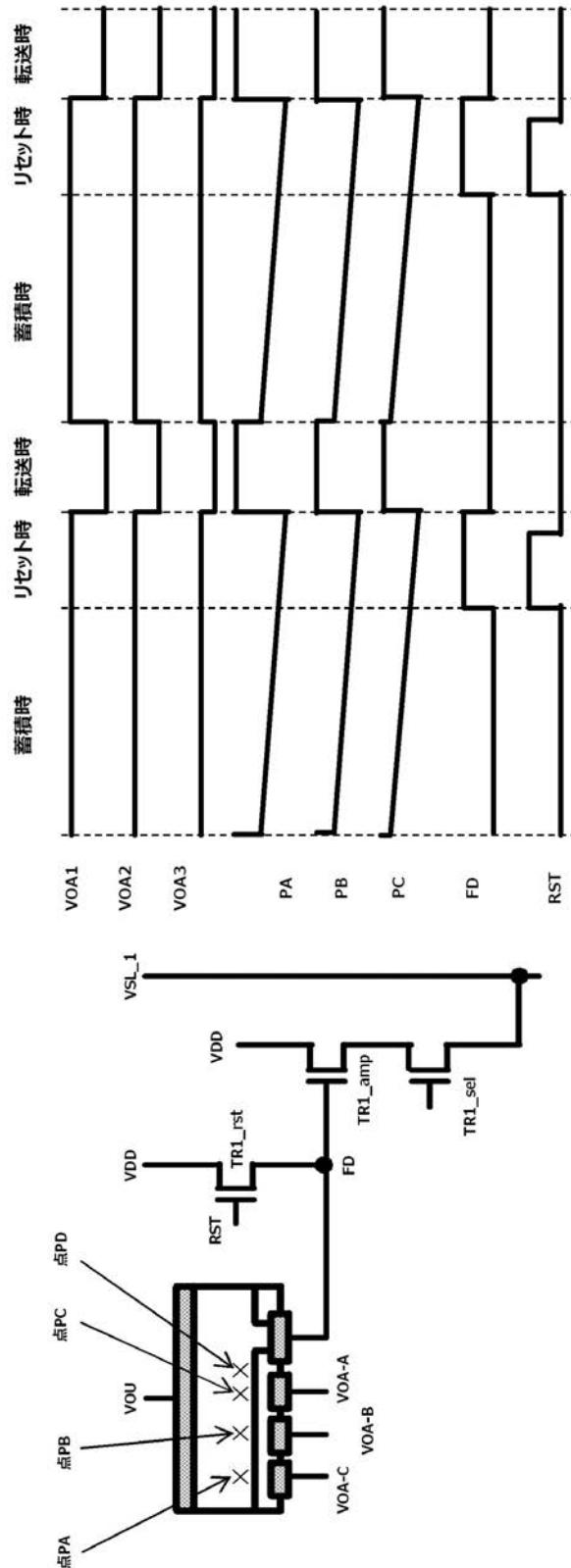

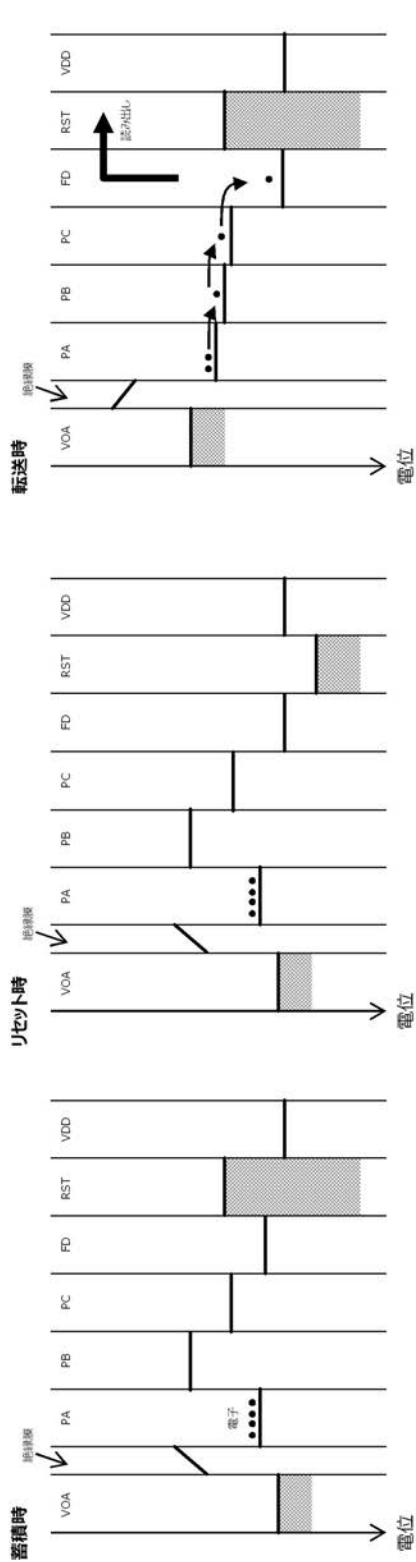

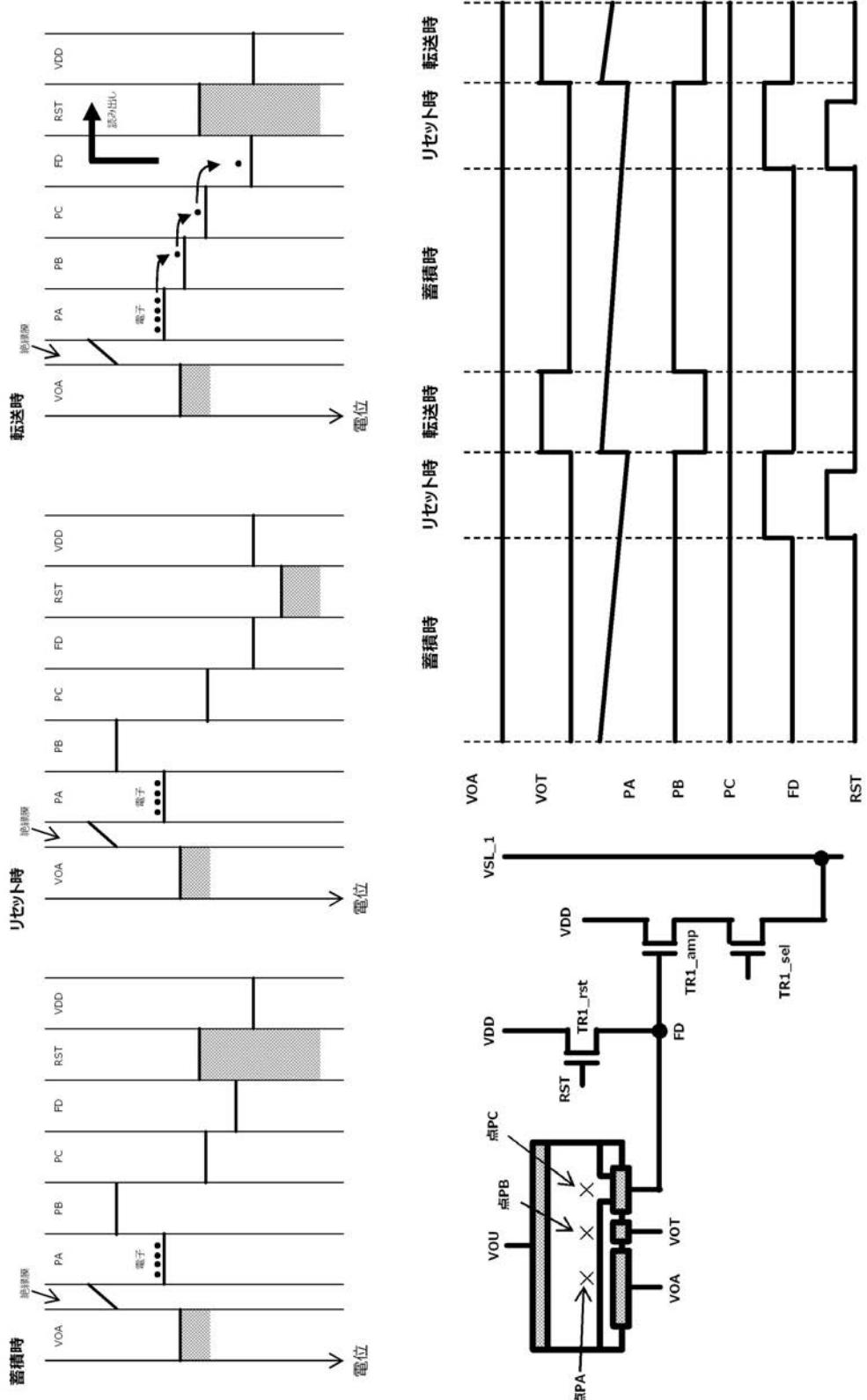

以下、図 5 を参照して、実施例 1 の撮像素子 ( 第 1 撮像素子 ) の動作を説明する。ここで、第 1 電極 11 の電位を第 2 電極の電位よりも高くした。即ち、例えば、第 1 電極 11 を正の電位とし、第 2 電極を負の電位とし、光電変換層 15 において光電変換によって生成した電子が浮遊拡散層に読み出される。他の実施例においても同様とする。尚、第 1 電極 11 を負の電位とし、第 2 電極を正の電位とし、光電変換層 15 において光電変換に基づき生成した正孔が浮遊拡散層に読み出される形態にあっては、以下の述べる電位の高低を逆にすればよい。

## 【手続補正 8】

【補正対象書類名】明細書

【補正対象項目名】0086

【補正方法】変更

【補正の内容】

【0086】

以上のとおり、実施例1にあっては、第1電極と離間して配置され、且つ、絶縁層を介して光電変換層と対向して配置された電荷蓄積用電極が備えられているので、光電変換部に光が照射され、光電変換部において光電変換されるとき、光電変換層と絶縁層と電荷蓄積用電極とによって一種のキャパシタが形成され、光電変換層に電荷を蓄えることができる。それ故、露光開始時、電荷蓄積部を完全空乏化し、電荷を消去することが可能となる。その結果、KTCノイズが大きくなり、ランダムノイズが悪化し、撮像画質の低下をもたらすといった現象の発生を抑制することができる。また、全画素を一斉にリセットすることができるので、所謂グローバルシャッター機能を実現することができる。

【手続補正9】

【補正対象書類名】明細書

【補正対象項目名】0088

【補正方法】変更

【補正の内容】

【0088】

駆動制御回路116は、垂直同期信号、水平同期信号及びマスター・クロックに基づいて、垂直駆動回路112、カラム信号処理回路113及び水平駆動回路114の動作の基準となるクロック信号や制御信号を生成する。そして、生成されたクロック信号や制御信号は、垂直駆動回路112、カラム信号処理回路113及び水平駆動回路114に入力される。

【手続補正10】

【補正対象書類名】明細書

【補正対象項目名】0142

【補正方法】変更

【補正の内容】

【0142】

本開示の撮像素子、積層型撮像素子から構成された固体撮像装置201を電子機器(カメラ)200に用いた例を、図48に概念図として示す。電子機器200は、固体撮像装置201、光学レンズ210、シャッタ装置211、駆動回路212、及び、信号処理回路213を有する。光学レンズ210は、被写体からの像光(入射光)を固体撮像装置201の撮像面上に結像させる。これにより固体撮像装置201内に、一定期間、信号電荷が蓄積される。シャッタ装置211は、固体撮像装置201への光照射期間及び遮光期間を制御する。駆動回路212は、固体撮像装置201の転送動作等及びシャッタ装置211のシャッタ動作を制御する駆動信号を供給する。駆動回路212から供給される駆動信号(タイミング信号)により、固体撮像装置201の信号転送を行う。信号処理回路213は、各種の信号処理を行う。信号処理が行われた映像信号は、メモリ等の記憶媒体に記憶され、あるいは、モニタに出力される。このような電子機器200では、固体撮像装置201における画素サイズの微細化及び転送効率の向上を達成することができるので、画素特性の向上が図られた電子機器200を得ることができる。固体撮像装置201を適用できる電子機器200としては、カメラに限られるものではなく、デジタルスチルカメラ、携帯電話機等のモバイル機器向けカメラモジュール等の撮像装置に適用可能である。

【手続補正11】

【補正対象書類名】明細書

【補正対象項目名】0143

【補正方法】変更

【補正の内容】

【0143】

尚、本開示は、以下のような構成を取ることもできる。

## [ A 0 1 ] 《撮像素子》

第1電極、光電変換層及び第2電極が積層されて成る光電変換部を備えており、

光電変換部は、更に、第1電極と離間して配置され、且つ、絶縁層を介して光電変換層と対向して配置された電荷蓄積用電極を備えている撮像素子。

## [ A 0 2 ] 半導体基板を更に備えており、

光電変換部は、半導体基板の上方に配置されている [ A 0 1 ] に記載の撮像素子。

[ A 0 3 ] 第1電極は、絶縁層に設けられた開口部内を延在し、光電変換層と接続されている [ A 0 1 ] 又は [ A 0 2 ] に記載の撮像素子。

[ A 0 4 ] 光電変換層は、絶縁層に設けられた開口部内を延在し、第1電極と接続されている [ A 0 1 ] 又は [ A 0 2 ] に記載の撮像素子。

## [ A 0 5 ] 第1電極の頂面の縁部は絶縁層で覆われており、

開口部の底面には第1電極が露出しており、

第1電極の頂面と接する絶縁層の面を第1面、電荷蓄積用電極と対向する光電変換層の部分と接する絶縁層の面を第2面としたとき、開口部の側面は、第1面から第2面に向かって広がる傾斜を有する [ A 0 4 ] に記載の撮像素子。

[ A 0 6 ] 第1面から第2面に向かって広がる傾斜を有する開口部の側面は、電荷蓄積用電極側に位置する [ A 0 5 ] に記載の撮像素子。

## [ A 0 7 ] 《第1電極及び電荷蓄積用電極の電位の制御》

半導体基板に設けられ、駆動回路を有する制御部を更に備えており、

第1電極及び電荷蓄積用電極は、駆動回路に接続されており、

電荷蓄積期間において、駆動回路から、第1電極に電位  $V_{11}$  が印加され、電荷蓄積用電極に電位  $V_{12}$  が印加され、光電変換層に電荷が蓄積され、

電荷転送期間において、駆動回路から、第1電極に電位  $V_{21}$  が印加され、電荷蓄積用電極に電位  $V_{22}$  が印加され、光電変換層に蓄積された電荷が第1電極を経由して制御部に読み出される [ A 0 1 ] 乃至 [ A 0 6 ] のいずれか1項に記載の撮像素子。

但し、第1電極の電位が第2電極より高い場合、

$$V_{12} > V_{11}, \text{ 且つ, } V_{22} < V_{21}$$

であり、第1電極の電位が第2電極より低い場合、

$$V_{12} < V_{11}, \text{ 且つ, } V_{22} > V_{21}$$

である。

## [ A 0 8 ] 《転送制御用電極》

第1電極と電荷蓄積用電極との間に、第1電極及び電荷蓄積用電極と離間して配置され、且つ、絶縁層を介して光電変換層と対向して配置された転送制御用電極を更に備えている [ A 0 1 ] 乃至 [ A 0 6 ] のいずれか1項に記載の撮像素子。

## [ A 0 9 ] 《第1電極、電荷蓄積用電極及び転送制御用電極の電位の制御》

半導体基板に設けられ、駆動回路を有する制御部を更に備えており、

第1電極、電荷蓄積用電極及び転送制御用電極は、駆動回路に接続されており、

電荷蓄積期間において、駆動回路から、第1電極に電位  $V_{11}$  が印加され、電荷蓄積用電極に電位  $V_{12}$  が印加され、転送制御用電極に電位  $V_{13}$  が印加され、光電変換層に電荷が蓄積され、

電荷転送期間において、駆動回路から、第1電極に電位  $V_{21}$  が印加され、電荷蓄積用電極に電位  $V_{22}$  が印加され、転送制御用電極に電位  $V_{23}$  が印加され、光電変換層に蓄積された電荷が第1電極を介して制御部に読み出される [ A 0 8 ] に記載の撮像素子。

但し、第1電極の電位が第2電極より高い場合、

$$V_{12} > V_{13}, \text{ 且つ, } V_{22} < V_{23} < V_{21}$$

であり、第1電極の電位が第2電極より低い場合、

$$V_{12} < V_{13}, \text{ 且つ, } V_{22} > V_{23} > V_{21}$$

である。

## [ A 1 0 ] 《電荷排出電極》

光電変換層に接続され、第1電極及び電荷蓄積用電極と離間して配置された電荷排出電

極を更に備えている [A 01] 乃至 [A 09] のいずれか 1 項に記載の撮像素子。

[A 11] 電荷排出電極は、第 1 電極及び電荷蓄積用電極を取り囲むように配置されている [A 10] に記載の撮像素子。

[A 12] 光電変換層は、絶縁層に設けられた第 2 開口部内を延在し、電荷排出電極と接続されており、

電荷排出電極の頂面の縁部は絶縁層で覆われており、

第 2 開口部の底面には電荷排出電極が露出しており、

電荷排出電極の頂面と接する絶縁層の面を第 3 面、電荷蓄積用電極と対向する光電変換層の部分と接する絶縁層の面を第 2 面としたとき、第 2 開口部の側面は、第 3 面から第 2 面に向かって広がる傾斜を有する [A 10] 又は [A 11] に記載の撮像素子。

[A 13] 《第 1 電極、電荷蓄積用電極及び電荷排出電極の電位の制御》

半導体基板に設けられ、駆動回路を有する制御部を更に備えており、

第 1 電極、電荷蓄積用電極及び電荷排出電極は、駆動回路に接続されており、

電荷蓄積期間において、駆動回路から、第 1 電極に電位  $V_{11}$  が印加され、電荷蓄積用電極に電位  $V_{12}$  が印加され、電荷排出電極に電位  $V_{14}$  が印加され、光電変換層に電荷が蓄積され、

電荷転送期間において、駆動回路から、第 1 電極に電位  $V_{21}$  が印加され、電荷蓄積用電極に電位  $V_{22}$  が印加され、電荷排出電極に電位  $V_{24}$  が印加され、光電変換層に蓄積された電荷が第 1 電極を介して制御部に読み出される [A 10] 乃至 [A 12] のいずれか 1 項に記載の撮像素子。

但し、第 1 電極の電位が第 2 電極より高い場合、

$V_{14} > V_{11}$ 、且つ、 $V_{24} < V_{21}$

であり、第 1 電極の電位が第 2 電極より低い場合、

$V_{14} < V_{11}$ 、且つ、 $V_{24} > V_{21}$

である。

[A 14] 《電荷蓄積用電極セグメント》

電荷蓄積用電極は、複数の電荷蓄積用電極セグメントから構成されている [A 01] 乃至 [A 13] のいずれか 1 項に記載の撮像素子。

[A 15] 第 1 電極の電位が第 2 電極より高い場合、電荷転送期間において、第 1 電極に最も近い所に位置する電荷蓄積用電極セグメントに印加される電位は、第 1 電極に最も遠い所に位置する電荷蓄積用電極セグメントに印加される電位よりも高く、

第 1 電極の電位が第 2 電極より低い場合、電荷転送期間において、第 1 電極に最も近い所に位置する電荷蓄積用電極セグメントに印加される電位は、第 1 電極に最も遠い所に位置する電荷蓄積用電極セグメントに印加される電位よりも低い [A 14] に記載の撮像素子。

[B 01] 半導体基板には、制御部を構成する少なくとも浮遊拡散層及び増幅トランジスタが設けられており、

第 1 電極は、浮遊拡散層及び増幅トランジスタのゲート部に接続されている [A 01] 乃至 [A 15] のいずれか 1 項に記載の撮像素子。

[B 02] 半導体基板には、更に、制御部を構成するリセット・トランジスタ及び選択トランジスタが設けられており、

浮遊拡散層は、リセット・トランジスタの一方のソース / ドレイン領域に接続されており、

増幅トランジスタの一方のソース / ドレイン領域は、選択トランジスタの一方のソース / ドレイン領域に接続されており、選択トランジスタの他方のソース / ドレイン領域は信号線に接続されている [B 01] に記載の撮像素子。

[B 03] 電荷蓄積用電極の大きさは第 1 電極よりも大きい [A 01] 乃至 [B 02] のいずれか 1 項に記載の撮像素子。

[B 04] 第 2 電極側から光が入射し、第 2 電極よりの光入射側には遮光層が形成されている [A 01] 乃至 [B 03] のいずれか 1 項に記載の撮像素子。

[B05] 第2電極側から光が入射し、第1電極には光が入射しない[A01]乃至[B03]のいずれか1項に記載の撮像素子。

[B06] 第2電極よりの光入射側であって、第1電極の上方には遮光層が形成されている[B05]に記載の撮像素子。

[B07] 電荷蓄積用電極及び第2電極の上方にはオンチップ・マイクロ・レンズが設けられており、

オンチップ・マイクロ・レンズに入射する光は、電荷蓄積用電極に集光される[B05]に記載の撮像素子。

[C01] 《積層型撮像素子》

[A01]乃至[B07]のいずれか1項に記載の撮像素子を少なくとも1つ有する積層型撮像素子。

[D01] 《固体撮像装置・・・第1の態様》

[A01]乃至[B04]のいずれか1項に記載の撮像素子を、複数、備えた固体撮像装置。

[D02] 《固体撮像装置・・・第2の態様》

[C01]に記載の積層型撮像素子を、複数、備えた固体撮像装置。

[E01] 《固体撮像装置の駆動方法》

第1電極、光電変換層及び第2電極が積層されて成る光電変換部を備えており、

光電変換部は、更に、第1電極と離間して配置され、且つ、絶縁層を介して光電変換層と対向して配置された電荷蓄積用電極を備えており、

第2電極側から光が入射し、第1電極には光が入射しない構造を有する撮像素子を、複数、備えた固体撮像装置の駆動方法であって、

全ての撮像素子において、一斉に、光電変換層に電荷を蓄積しながら、第1電極における電荷を系外に排出し、その後、

全ての撮像素子において、一斉に、光電変換層に蓄積された電荷を第1電極に転送し、転送完了後、順次、各撮像素子において第1電極に転送された電荷を読み出す、各工程を繰り返す固体撮像装置の駆動方法。

【手続補正12】

【補正対象書類名】明細書

【補正対象項目名】0144

【補正方法】変更

【補正の内容】

【0144】

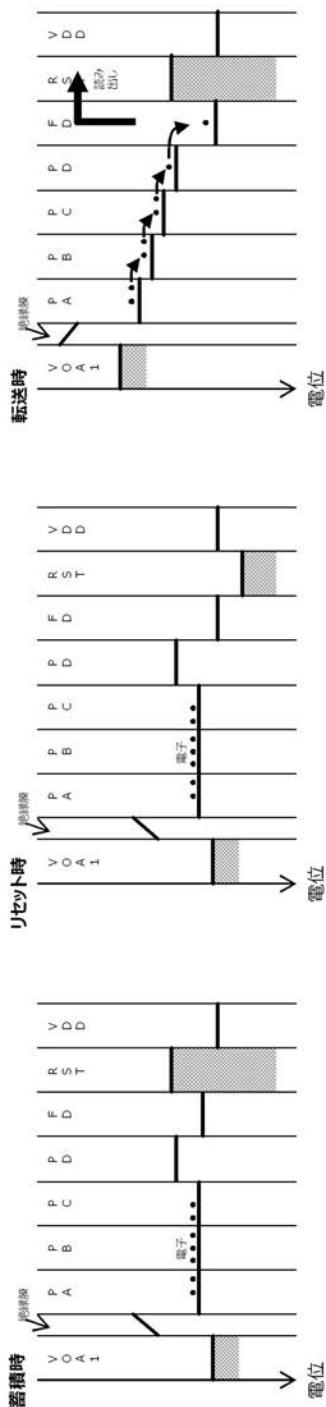

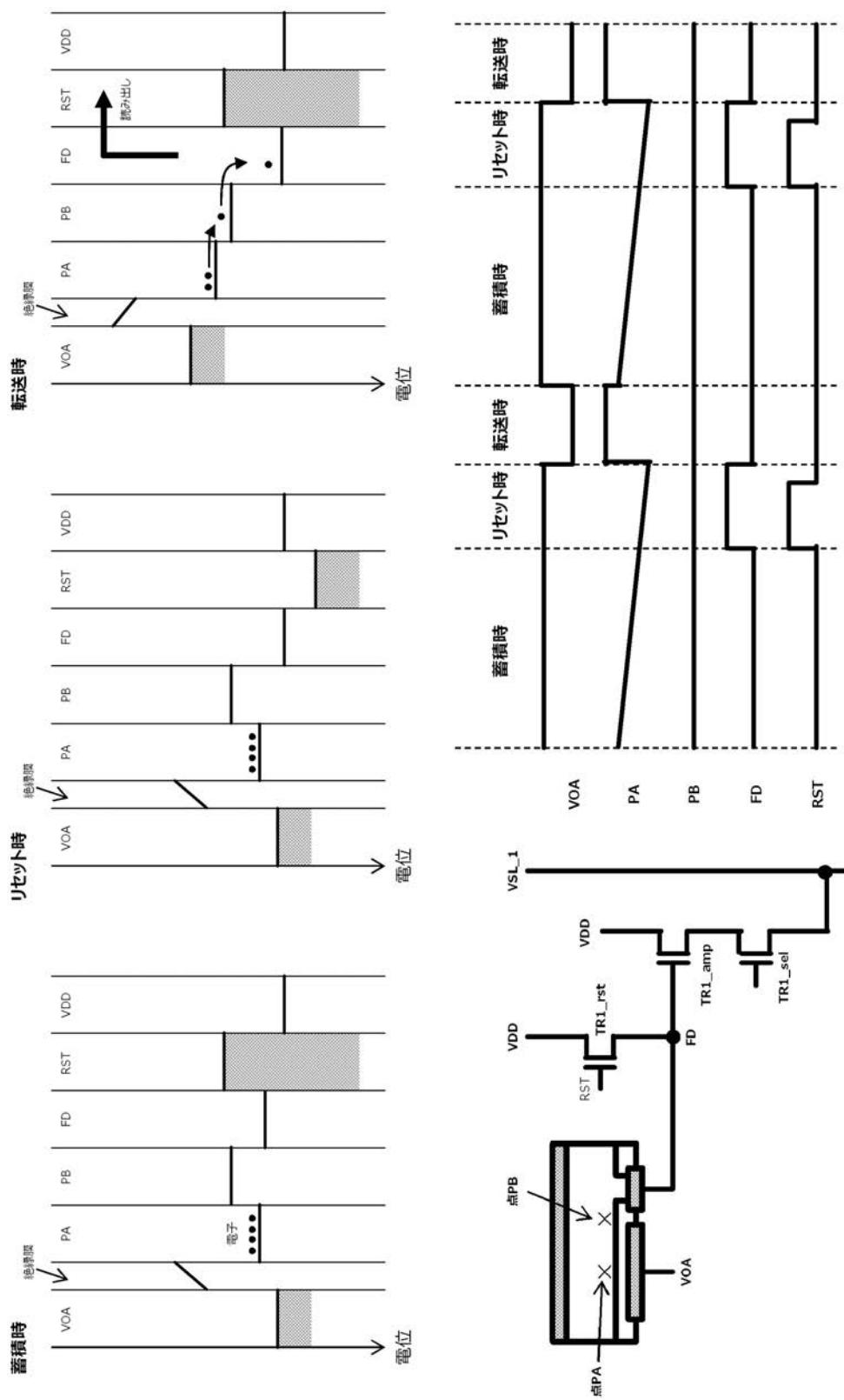

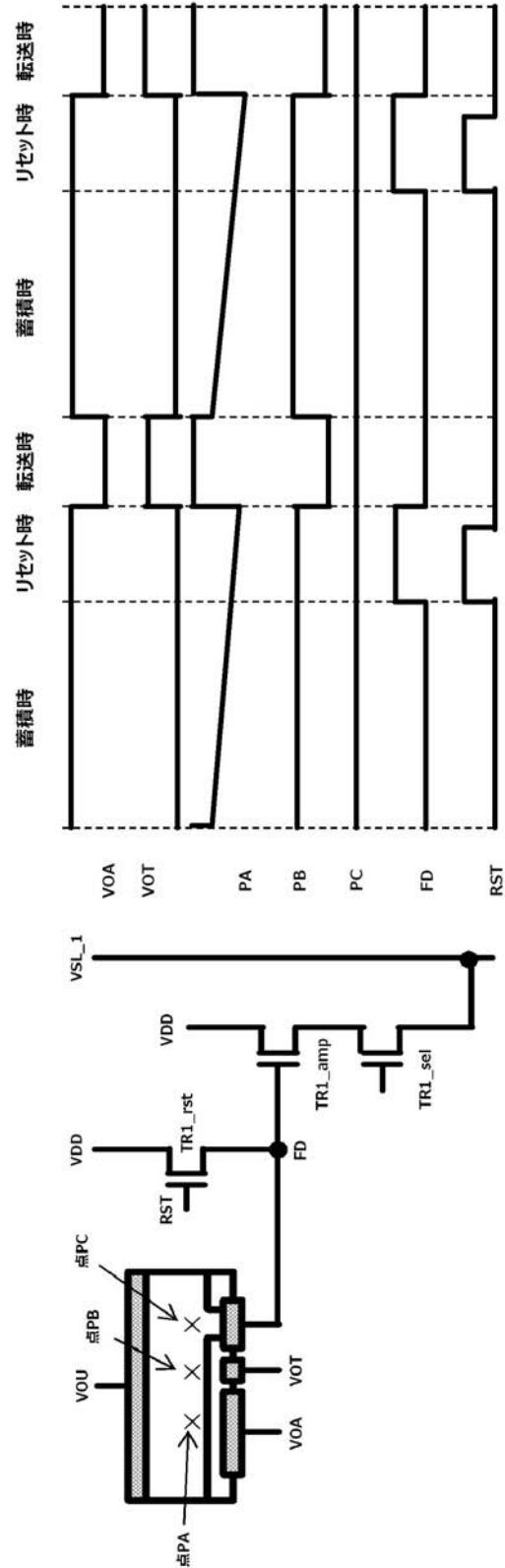

11・・・第1電極、12・・・電荷蓄積用電極、12A, 12B, 12C・・・電荷蓄積用電極セグメント、13, 13A, 13B・・・転送制御用電極(電荷転送電極)、14・・・電荷排出電極、15・・・光電変換層、16・・・第2電極、41・・・第2撮像素子を構成するn型半導体領域、43・・・第3撮像素子を構成するn型半導体領域、42, 44, 73・・・p<sup>+</sup>層、F D<sub>1</sub>, F D<sub>2</sub>, F D<sub>3</sub>, 45C, 46C・・・浮遊拡散層、T R 1<sub>amp</sub>・・・増幅トランジスタ、T R 1<sub>rst</sub>・・・リセット・トランジスタ、T R 1<sub>sel</sub>・・・選択トランジスタ、51・・・リセット・トランジスタT R 1<sub>rst</sub>のゲート部、51A・・・リセット・トランジスタT R 1<sub>rst</sub>のチャネル形成領域、51B, 51C・・・リセット・トランジスタT R 1<sub>rst</sub>のソース/ドレイン領域、52・・・増幅トランジスタT R 1<sub>amp</sub>のゲート部、52A・・・増幅トランジスタT R 1<sub>amp</sub>チャネル形成領域、52B, 52C・・・増幅トランジスタT R 1<sub>amp</sub>のソース/ドレイン領域、53・・・選択トランジスタT R 1<sub>sel</sub>のゲート部、53A・・・選択トランジスタT R 1<sub>sel</sub>のチャネル形成領域、53B, 53C・・・選択トランジスタT R 1<sub>sel</sub>のソース/ドレイン領域、T R 2<sub>trs</sub>・・・転送トランジスタ、45・・・転送トランジスタのゲート部、T R 2<sub>rst</sub>・・・リセット・トランジスタ、T R 2<sub>amp</sub>・・・増幅トランジスタ、T R 2<sub>sel</sub>・・・選択トランジスタ、T R 3<sub>trs</sub>・・・転送トランジスタ、46・・・転送トランジスタのゲート部、T R 3<sub>rst</sub>・・・リセット・トランジスタ、T R 3<sub>amp</sub>・・・増幅トランジ

ジスタ、 $T\ R\ 3_{sel}$  . . . 選択トランジスタ、 $V_{DD}$  . . . 電源、 $R\ S\ T_1$  ,  $R\ S\ T_2$  ,  $R\ S\ T_3$  . . . リセット線、 $S\ E\ L_1$  ,  $S\ E\ L_2$  ,  $S\ E\ L_3$  . . . 選択線、 $1\ 1\ 7$  ,  $V\ S\ L_1$  ,  $V\ S\ L_2$  ,  $V\ S\ L_3$  . . . 信号線、 $T\ G_2$  ,  $T\ G_3$  . . . 転送ゲート線、 $V_{OA}$  ,  $V_{OT}$  ,  $V_{OU}$  . . . 配線、 $6\ 1$  . . . コンタクトホール部、 $6\ 2$  . . . 配線層、 $6\ 3$  ,  $6\ 4$  ,  $6\ 8\ A$  . . . パット部、 $6\ 5$  ,  $6\ 8\ B$  . . . 接続孔、 $6\ 6$  ,  $6\ 7$  ,  $6\ 9$  . . . 接続部、 $7\ 0$  . . . 半導体基板、 $7\ 0\ A$  . . . 半導体基板の第1面(おもて面)、 $7\ 0\ B$  . . . 半導体基板の第2面(裏面)、 $7\ 1$  . . . 素子分離領域、 $7\ 2$  . . . 酸化膜、 $7\ 4$  . . .  $HfO_2$ 膜、 $7\ 5$  . . . 絶縁膜、 $7\ 6$  . . . 層間絶縁層、 $7\ 7$  ,  $7\ 8$  ,  $8\ 1$  . . . 層間絶縁層、 $8\ 2$  . . . 絶縁層、 $8\ 2\ a$  . . . 絶縁層の第1面、 $8\ 2\ b$  . . . 絶縁層の第2面、 $8\ 2\ c$  . . . 絶縁層の第3面、 $8\ 3$  . . . 保護層、 $8\ 4$  ,  $8\ 4\ A$  ,  $8\ 4\ B$  ,  $8\ 4\ C$  . . . 開口部、 $8\ 5$  ,  $8\ 5\ A$  . . . 第2開口部、 $9\ 0$  . . . オンチップ・マイクロ・レンズ、 $9\ 1$  . . . 層間絶縁層 $8\ 1$ より下方に位置する各種の撮像素子構成要素、 $9\ 2$  . . . 遮光層、 $1\ 0\ 0$  . . . 固体撮像装置、 $1\ 0\ 1$  . . . 積層型撮像素子、 $1\ 1\ 1$  . . . 撮像領域、 $1\ 1\ 2$  . . . 垂直駆動回路、 $1\ 1\ 3$  . . . カラム信号処理回路、 $1\ 1\ 4$  . . . 水平駆動回路、 $1\ 1\ 5$  . . . 出力回路、 $1\ 1\ 6$  . . . 駆動制御回路、 $1\ 1\ 8$  . . . 水平信号線、 $2\ 0\ 0$  . . . 電子機器(カメラ)、 $2\ 0\ 1$  . . . 固体撮像装置、 $2\ 1\ 0$  . . . 光学レンズ、 $2\ 1\ 1$  . . . シャッタ装置、 $2\ 1\ 2$  . . . 駆動回路、 $2\ 1\ 3$  . . . 信号処理回路

【手続補正13】

【補正対象書類名】図面

【補正対象項目名】図5

【補正方法】変更

【補正の内容】

【図5】

図5

【手続補正14】

【補正対象書類名】図面

【補正対象項目名】図20

【補正方法】変更

【補正の内容】

【図20】

図20

【手続補正15】

【補正対象書類名】図面

【補正対象項目名】図21

【補正方法】変更

【補正の内容】

【図 2 1】

図 2 1

【手続補正 1 6】

【補正対象書類名】図面

【補正対象項目名】図 3 2

【補正方法】変更

【補正の内容】

【図32】

図32