# (19) 대한민국특허청(KR) (12) 등록특허공보(B1)

| (51) Int. CI. <sup>6</sup> |                                | (45) 공고일자    | 1999년04월 15일  |

|----------------------------|--------------------------------|--------------|---------------|

| G11B 20/02                 |                                | (11) 등록번호    | 특0184337      |

|                            |                                | (24) 등록일자    | 1998년 12월 18일 |

| (21) 출원번호                  | 특1995−022848                   | (65) 공개번호    | 특1996-005555  |

| (22) 출원일자                  | 1995년07월28일                    | (43) 공개일자    | 1996년02월23일   |

| (30) 우선권주장                 | 94-196106 1994년07월28일          | 일본(뫄)        |               |

|                            | 94-197260 1994년07월29일          | 일본(뫄)        |               |

|                            |                                |              |               |

| (73) 특허권자                  | 니홍 빅타 가부시기가이샤                  | 슈즈이 다께오      |               |

|                            | 일본국 가나가와껭 요꼬하마                 | 시 가나가와구 모리야쪼 | 3-12          |

| (72) 발명자                   | 젠노 요오이찌                        |              |               |

|                            | 일본국 도오교오도 오오다구 우노기 3-12-12-206 |              |               |

|                            | 히구라시 세이지                       |              |               |

|                            | 일본국 도오교오도 후쮸우시                 | 후쮸우쪼 3-14-8  |               |

| (74) 대리인                   | 최재철, 김기종, 권동용                  |              |               |

| 실사관 : 서흥선                  |                                |              |               |

#### <u>심사관 : 서호선</u>

#### (54) 위상비교회로 및 피엘엘 회로

#### 요약

본 발명은 다중레벨신호에 따라 검출신호를 발생시키는 제1장치를 포함하는 위상비교회로에 관한 것이다. 검출신호는 다중레벨신호가 소정의 레벨인지 여부를 나타낸다. 제1수단에 접속된 제2장치는 제1장치에 의해 발생한 검출신호와 클럭신호에 따라 제1제어신호를 발생시킨다. 제1제어신호는 검출신호의 펄스의 리딩 에지와 검출신호의 펄스의 리딩 에지를 즉시 추종하는 클럭신호의 스트로브 포인트간의 시간 간격을 나타낸다. 제1장치에 접속된 제3장치는 제1장치에 의해 발생한 검출신호와 클럭신호에 따라 제2제어신호를 발생시킨다. 제2제어신호는 클럭신호의 스트로브 포인트와 검출신호의 펄스의 트레일링 에지간의 시간 간격을 나타낸다. 제2장치 및 제3장치에 접속된 제4장치는 제2장치에 의해 발생한 제1제어신호와 제3장치에 의해 발생한 제2제어신호에 따라 위상에러신호를 발생시킨다. 위상에러신호는 제1장치에 의해 발생한 검출신호의 위상과 클럭신호의 위상간의 차이를 나타낸다.

### 出丑至

## 명세서

[발명의 명칭]

위상비교회로 및 피엘엘(PLL)회로

[도면의 간단한 설명]

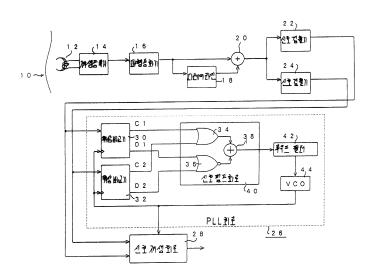

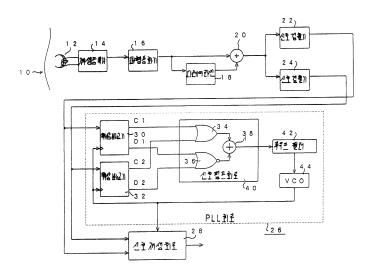

제1도는 본 발명의 제1실시예의 PLL회로와 위상비교기를 포함하는 정보재생 장치의 블록도.

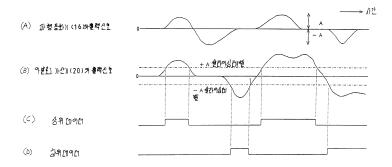

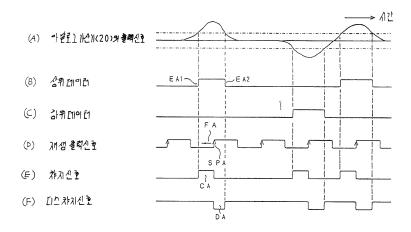

제2도는 제1도의 장치의 신호의 타임 도메인도.

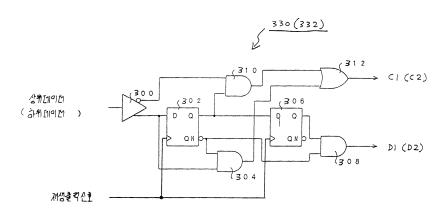

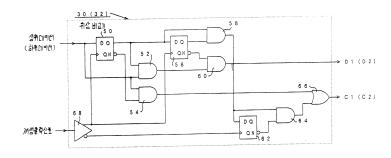

제3도는 제1도의 장치의 위상비교기의 블록도.

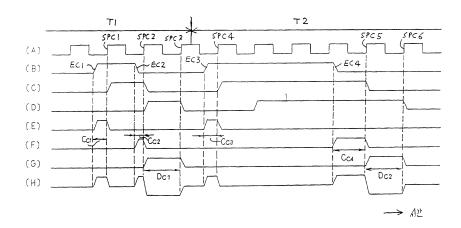

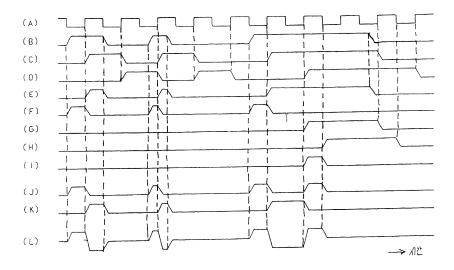

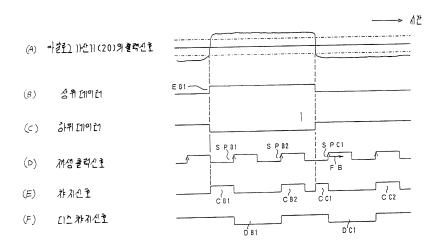

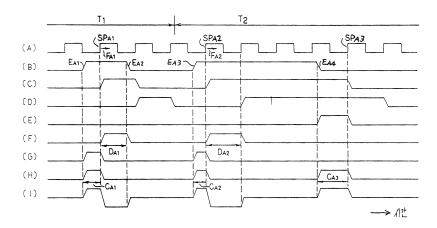

제4도는 제3도의 위상비교기의 신호의 타임 도메인도.

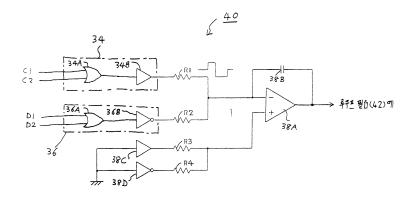

제5도는 제1도의 장치의 차지펌프의 도면.

제6도는 제1도의 장치의 신호의 타임 도메인도.

제7도는 제1도의 장치의 신호의 타임 도메인도.

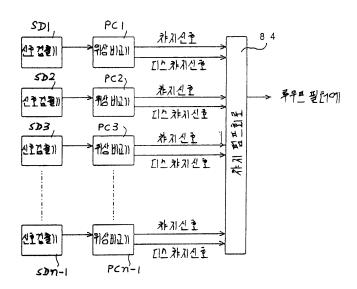

제8도는 본 발명의 제2실시예의 정보재생장치의 부분의 블록도.

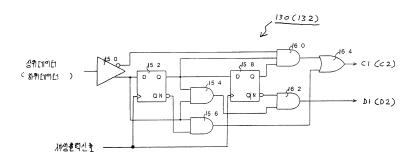

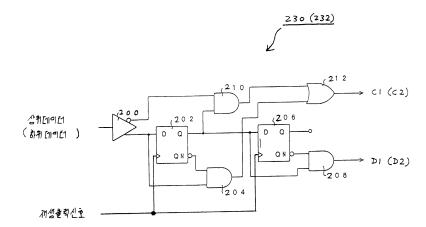

제9도는 본 발명의 제6실시예의 위상비교기의 블록도.

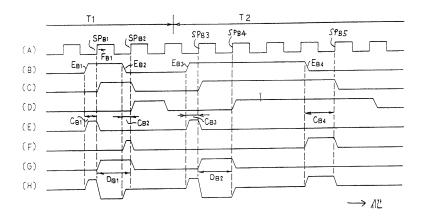

제10도는 제9도의 위상비교기의 신호의 타임 도메인도.

제11도는 본 발명의 제7실시예의 위상비교기의 블록도.

제12도는 제11도의 위상비교기의 신호의 타임 도메인도.

제13도는 본 발명의 제8실시예의 위상비교기의 블록도.

제14도는 제12도의 위상비교기의 신호의 타임 도메인도.

\* 도면의 주요부분에 대한 부호의 설명

16 : 파형등화기 18 : 디레이 라인

22, 24, SD1, SD2, SD3, . . SDn-1: 신호검출기

28 : 신호재생회로

30, 32, PC1, PC2, PC3, . . PCn-1: 위상비교기

40, 84 : 차지펌프회로 42: 루우프필터

44 : VCO

[발명의 상세한 설명]

본 발명은 위상비교회로 및 PLL(위상동기루우프)회로에 관한 것이다.

VTR(비디오 테이프 레코더), 디스크 플레이어 및 통신기기와 같은 전자기기는 재생되거나 수신된 정보신호로부터 클럭신호를 발생시키는 장치를 구비한다. 발생된 클럭신호는 정보신호의 데이터 검출과 관련된타이밍 제어에 이용된다. 이러한 클럭신호 발생장치에서 PLL(위상동기루우프)회로를 이용하는 것이 공지되어 있다.

파티셜 리스판스 클래스 4(Partial Response Class 4)에 따르는 PCM-VTR의 재생측은 재생정보신호로부터 내부기호 방해성분을 제거하는 파형등화기를 포함한다. 파형등화기는 재생된 정보신호를 내부기호 방해가 없는 3레벨 정보신호로 처리한다. 파형등화기는 서로 병렬인 부분응답 검출기 및 클럭신호 발생기에 의해 추종된다. 부분응답 검출기는 3레벨 정보신호 2레벨 정보신호(이진정보신호 또는 디지털 정보신호)로 변환시킨다. 클럭신호 발생회로는 3레벨 정보신호로부터 클럭신호를 회복하거나 발생시킨다. 부분응답 검출기 및 클럭신호 발생회로를 추종하는 D-플립플롭은 발생된 클럭신호에 의해 결정된 시간에 2레벨 정보신호를 샘플하여 유지시킨다. 샘플링 및 유지처리에 의해 2레벨 정보신호로부터 원데이터(정보)가 추출되거나 유지된다.

위에서 언급한 PCM-VTR의 재생측에는 파형등화기와 D-플립플롭 사이에 두 개의 상이한 신호전송통로가 있다. 신호전송통로의 하나는 부분응답 검출기를 포함하는 반면, 나머지 신호전송통로는 클럭신호 발생회로를 포함한다. 신호전송 통로가 서로 다르기 때문에 신호전송통로의 출력단에 나타나는 신호위상간에 차이가 있다. 이러한 위상차를 보상하기 위해 신호지연장치가 신호전송통로중 하나에 위치해 있다.

재생처리중, 재생속도의 변동에 의해 재생된 정보신호에 관한 데이터비(데이터전송비)가 변화하게 된다. 위해서 언급한 PCM-VTR의 재생측에서 재생된 정보신호에 관한 데이터비가 변할 때, 위상차의 적절한 보상 을 유지하기가 어렵다.

본 발명의 목적은 향상된 PLL 회로를 제공하는 것이다.

본 발명의 또 다른 목적은 PLL 장치에 이용할 수 있는 향상된 위상비교회로를 제공하는 것이다.

본 발명의 제1특징은, 다중레벨신호에 따라 다중레벨신호가 소정의 레벨인지 여부를 나타내는 검출신호를 발생시키는 제1수단을 구비하고; 제1수단에 접속되어서 제1수단에 의해 발생된 검출신호와 클럭신호에 따 라 제1제어신호를 발생하는 제2수단을 구비하고, 상기 제1제어신호는 검출신호의 펄스의 리딩 에지 (leading edag)와 검출신호의 펄스의 리딩 에지를 즉시 추종하는 클럭신호의 스토로브 포인트(strobe point)간의 시간 간격을 나타내며; 또한, 제1수단에 접속되어서 제1수단에 의해 발생된 검출신호와 클럭 신호에 응답하여 제2제어신호를 발생시키는 제3수단을 구비하고, 상기 제2제어신호는 클럭신호의 스트로 브 포인트와 검출신호의 펄스의 트레일링 에지간의 시간 간격을 나타내며; 또한, 제2수단과 제3수단에 접 속되어서 제2수단에 의해 발생한 제1제어신호와 제3수단에 의해 발생한 제2제어신호에 응답하여 위상에러 신호를 발생시키는 제4수단을 구비하고, 상기 위상에러신호는 제1수단에 의해 발생한 검출신호의 위상과 클럭신호의 위상간의 차를 나타내며; 를 구비하는 위상비교 회로를 제공한다.

본 발명의 제2특징은, 다중레벨신호가 소정의 레벨에 있는지 여부를 나타내는 검출신호를 다중레벨신호에 따라 발생시키는 제1수단을 구비하고; 제1수단에 접속되어서 제1수단에 의해 발생한 검출신호와 클럭신호 에 따라 제1제어신호를 발생하는 제2수단을 구비하고, 상기 제1수단은 검출신호의 펄스의 리딩 에지와 검 출신호의 펄스의 리딩 에지를 즉시 추종하는 클럭신호의 제1스트로브 포인트간의 시간 간격을 나타내며; 또한, 클럭신호에 따라 제2제어신호를 발생시키는 제3수단을 구비하고, 상기 제2제어신호는 클럭신호의 제1스트로브 포인트와 클럭신호의 제1스트로브 포인트를 즉시 추종하는 클럭신호의 제2스트로브 포인트간 의 시간 간격을 나타내며; 또한, 클럭신호에 응답하여 제3제어신호를 발생시키는 제4수단을 구비하고, 상 기 제3제어신호는 클럭신호의 주기의 반에 해당하고, 클럭신호의 제2스트로브 포인트로부터 시작하는 시 간 간격을 나타내며; 제2수단, 제3수단 및 제4수단에 접속되어서 제2수단에 의해 발생한 제1제어신호, 제 3수단에 의해 발생한 제2제어신호 및 제4수단에 의해 발생한 제3제어신호에 응답하여 위상에러신호를 발 생시키는 제5수단을 구비하고, 상기 위상에러신호는 제1수단에 의해 발생한 검출신호의 위상과 클럭신호 의 위상간의 차를 나타내며;를 구비하는 위상비교회로를 제공한다.

본 발명의 제3특징은, 다중레벨신호에 따라 다중레벨신호가 소정의 레벨인지 여부를 나타내는 검출신호를 발생시키는 제1수단을 구비하고; 제1수단에 접속되어서 제1수단에 의해 발생한 검출신호의 클럭신호에 따라 제1제어신호를 발생시키는 제2수단을 구비하고, 상기 제1제어신호는 검출신호의 펄스의 리딩 에지와 검출신호의 펄스의 리딩 에지를 추종하는 클럭신호의 제1스트로브 포인트간의 시간점을 나타내며; 또한, 제1수단에 접속되어서 검출신호의 펄스의 트레일링 에지가 클럭신호의 제1스트로브 포인트를 즉시 추종하는 클럭신호의 제2스트로브 포인트를 선행하는 경우, 제1수단에 의해 발생한 검출신호와 클럭신호에 따라제2제어신호를 발생하고, 클럭신호의 제2스트로브 포인트가 검출신호의 펄스의 트레일링 에지를 선행하는 경우, 제1수단에 의해 발생한 검출신호와 클럭신호에 따라제2제어신호를 발생하고, 클럭신호의 제2스트로브 포인트가 검출신호의 펄스의 트레일링 에지를 선행하는 경우, 제1수단에 의해 발생한 검출신호와 클럭신호에 따라 제3제어신호와 제4제어신호를 발생시키는 제3수단을 구비하고, 상기 제2제어신호는 클럭신호의 제1스트로브 포인트와 검축신호의 펄스의 트레일링 에지간의 시간 간격을 나타내며, 제3제어신호는 클럭신호의 제2스트로브 포인트와 클럭신호의 제2스트로브 포인트간의 시간 간격을 나타내고, 제4제어신호는 클럭신호의 제2스트로브 포인트로부터 시작하는 클럭신호의 주기의 반에 해당하는 시간 간격을 나타내며; 또한, 제2수단에 의해 발생한 제1제어신호 및 제3수단에 의해 발생한 제2제어신호 또는 제2수단에 의해 발생한 제1제어신호 및 제3수단에 의해 발생한 제2제어신호는 제1수단에 의해 발생한 검출신호의 위상과 클럭신호의 위상간의 차를 나타내며; 를 구비하는 위상비교회로를 제공한다.

본 발명의 제4특징은, a)다중레벨신호에 응답하여 다중레벨신호가 상기한 소정의 레벨에 있는지 여부를 나타내는 검출신호를 발생시키는 다수의 신호검출기와, b)신호검출기를 추종하고 신호검출기에 의해 발생한 검출신호를 처리하는 다수의 위상비교부를 구비함에 있어서, 각각의 위상비교부는, b1)관련된 검출신호에 따라 제1제어신호를 발생시키는 제1수단을 구비하고, 상기 제1제어신호는 검출신호의 펄스의 리딩에지와 검출신호의 펄스의 리딩에지를 즉시 추종하는 클럭신호의 스트로브 포인트간의 시간 간격을 나타내며; b2)관련된 검출신호에 따라 제2제어신호를 발생시키는 제2수단을 구비하고, 상기 제2제어신호는 클럭신호의 스트로브 포인트와 검출신호의 펄스의 트레일링 에지간의 시간 간격을 나타내며; b3)제1및 제2수단에 접속되어서 제1수단에 의해 발생한 제1제어신호와 제2수단에 의해 발생한 제2제어신호에 응답하여위상에러신호를 발생하는 제3수단을 구비하고, 상기 위상에러신호는 제1수단에 의해 발생한 검출신호의위상과 클럭신호의위상간의 차를 나타내며; 를 구비하는 위상비교회로를 제공한다.

본 발명의 제5특징은, 제1특징을 토대로 하고, 제4수단이 차지펌프회로를 구비하는 위상비교회로를 제공한다.

본 발명의 제6특징은, 클럭신호를 발생시키는 제1수단을 구비하고; 제1수단에 접속되어서 입력신호와 제1수단에 의해 발생된 클럭신호에 응답하여 제1제어신호를 발생시키는 제2수단을 구비하고, 상기 제1제어신호는 입력신호의 펄스의 리딩 에지와 입력신호의 펄스의 리딩 에지를 즉시 추종하는 클럭신호의 스트로브 포인트간의 시간 간격을 나타내며; 또한, 제1수단에 접속되어서 제1수단에 의해 발생된 클럭신호와 입력신호에 따라 제2제어신호를 발생시키는 제3수단을 구비하고, 상기 제2제어신호는 클럭신호의 스트로브 포인트와 입력신호의 펄스의 트레일링 에지간의 시간 간격을 나타내며; 또한, 제2수단과 제3수단에 접속되어서 제2수단에 의해 발생한 제1제어신호와 제3수단에 의해 발생한 제2제어신호에 따라 위상에러신호를 발생시키는 제4수단을 구비하고, 상기 위상에러신호는 제1수단에 의해 발생한 클럭신호의 위상과 입력신호의 위상간의 차이를 나타내며; 또한, 제4수단에 의해 발생된 위상에러신호에 따라 클럭신호의 위상을 제어하는 제5수단; 을 구비하는 PLL 회로를 제공한다.

본 발명의 제7특징은, 다중레벨신호에 따라 이 다중레벨신호가 소정의 레벨인지 여부를 나타내는 검출신호를 발생시키는 제1수단을 구비하고; 제1수단에 접속되어서 제1수단에 의해 발생한 검출신호와 클럭신호에 따라 제1제어신호를 발생시키는 제2수단을 구비하고, 상기 제1제어신호는 검출신호의 펄스의 리딩 에지와 검출신호의 펄스의 리딩 에지와 검출신호의 펄스의 리딩 에지와 검출신호의 펄스의 리딩 에지와 검출신호의 펄스의 리딩 에지가 금럭신호의 제1스트로브 포인트간의 시간 간격을 나타내며; 또한, 제1수단에 접속되어서 검출신호의 펄스의 트레일링 에지가 클럭신호의 제1스트로브 포인트를 즉시 추종하는 클럭신호의 제2스트로브 포인트를 선행하는 경우, 제1수단에 의해 발생한 검출신호와 클럭신호에 따라 제2제어신호를 발생시키고, 클럭신호의 제2스트로브 포인트가 검출신호의 펄스의 트레일링 에지를 선행하는 경우, 제1수단에 의해 발생한 검출신호와 클럭신호에 따라 제3제어신호 및 제4제어신호를 발생시키는 제3수단을 구비하고, 상기 제2제어신호는 클럭신호의 제1스트로브 포인트와 검출신호의 펄스의 트레일링 에지간의 시간 간격을 나타내며, 제3제어신호는 금럭신호의 퍼스의 트레일링 에지와 감출신호의 펄스의 트레일링 에지와 감출신호의 펄스의 트레일링 에지와 감출신호의 펄스의 트레일링 에지를 즉시 추종하는 클럭신호의 제3스트로브 포인트간의 시간 간격을 나타내며; 또한, 제2수단과 제3수단에 접속되어서 제2수단에 의해 발생한 제1제어신호와,(1)제3수단에 의해 발생한 제2제어신호의 결합에 따라 위상에러신호를 발생시키는 제4수단을 구비하고, 상기 위상에러신호는 제1수단에 의해 발생한 검출신호의 위상과클럭신호의 위상간의 차이를 나타내며; 를 구비하는 위상비교회로를 제공한다.

본 발명의 제8특징은, 다중레벨신호에 따라 다중레벨신호가 소정의 레벨인지 여부를 나타내는 검출신호를 발생시키는 제1수단을 구비하고; 제1수단에 접속되어서 제1수단에 의해 발생한 검출신호와 클럭신호에 따라 제1제어신호를 발생시키는 제2수단을 구비하고, 상기 제1제어신호는 검출신호의 펄스의 리딩 에지와 검출신호의 펄스의 리딩 에지를 즉시 추종하는 클럭신호의 제1스트로브 포인트간의 시간 간격을 나타내며; 또한, 제1수단에 접속되어서 제1수단에 의해 발생한 검출신호와 클럭신호에 따라 제2제어신호 를 발생시키는 제3수단을 구비하고, 상기 제2제어신호는 검출신호의 펄스의 트레일링 에지와 검출신호의 펄스의 트레일링 에지를 즉시 추종하는 클럭신호의 제2스트로브 포인트간의 시간 간격을 나타내며; 또한, 클럭신호에 따라 제3제어신호를 발생시키는 제4수단을 구비하고, 상기 제3제어신호는 클럭신호의 주기와 같은 시간 간격을 나타내며; 또한, 제2수단, 제3수단 및 제4수단에 접속되어서 제2수단에 의해 발생한 제 1제어신호, 제3수단에 의해 발생한 제2제어신호 및 제4수단에 의해 발생한 제3제어신호에 따라 위상에러 신호를 발생시키는 제5수단을 구비하고, 상기 위상에러신호는 제1수단에 의해 발생한 검출신호의 위상과 클럭신호의 위상간의 차를 나타내며;를 구비하는 위상비교회로를 제공한다.

본 발명의 제9특징은, 제2특징을 토대로 하고, 제1수단이 다중레벨신호에 따라 상이한 검출신호를 발생시키는 다수의 신호검출기를 포함하되, 상기 검출신호는 다중레벨신호가 상이한 소정의 레벨인지 여부를 나타내고, 제2수단은 신호검출기에 의해 발생한 검출신호에 응답하는 위상비교회로를 제공한다.

본 발명의 제10특징은, 제3특징을 토대로 하고, 제1수단이 다중레벨신호에 따라 상이한 검출신호를 발생 시키는 다수의 신호검출기를 포함하되, 상기 검출신호는 다중레벨신호가 상이한 소정의 레벨인지 여부를 나타내고, 제2수단은 신호검출기에 의해 발생한 검출신호에 응답하는 위상비교회로를 제공한다.

본 발명의 제11특징은, 제7특징을 토대로 하고, 제1수단이 다중레벨신호에 따라 상이한 검출신호를 발생 시키는 다수의 신호검출기를 포함하되, 상기 검출신호는 다중레벨신호가 상이한 소정의 레벨인지 여부를 나타내고, 제2수단 및 제3수단은 신호검출기에 의해 발생한 검출신호에 응답하는 위상비교회로를 제공한 다.

본 발명의 제12특징은, 제8특징을 토대로 하고, 제1수단이 다중레벨신호에 따라 상이한 검출신호를 발생 시키는 다수의 신호검출기를 포함하되, 상기 검출신호는 다중레벨신호가 상이한 소정의 레벨인지 여부를 나타내고, 제2수단 및 제3수단은 신호검출기에 의해 발생한 검출신호에 응답하는 위상비교회로를 제공한 다

본 발명의 제13특징은, 제2특징을 토대로 하고, 제5수단이 차지펌프회로를 포함하는 위상비교회로를 제공 한다.

본 발명의 제14특징은, 제3특징을 토대로 하고, 제4수단이 차지펌프회로를 포함하는 위상비교회로를 제공 한다.

본 발명의 제15특징은, 제7특징을 토대로 하고, 제4수단이 차지펌프회로를 포함하는 위상비교회로를 제공한다.

본 발명의 제16특징은, 제8특징을 토대로 하고, 제5수단이 차지펌프회로를 포함하는 위상비교회로를 제공하다.

본 발명의 제17특징은, 제2특징에 따라 위상비교회로를 포함하는 PLL 회로를 제공한다.

본 발명의 제18특징은, 제3특징에 따라 위상비교회로를 포함하는 PLL 회로를 제공한다.

본 발명의 제19특징은, 제7특징에 따라 위상비교회로를 포함하는 PLL 회로를 제공한다.

본 발명의 제20특징은, 제8특징에 따라 위상비교회로를 포함하는 PLL 회로를 제공한다.

#### [제1실시예]

제1도는 본 발명의 제1실시예의 장치를 도시한다. 제1도를 참조하면, 파티셜 리스판스 검출 클래스(PR4)를 이용한 경우의 정보신호가 재생헤드(12)에 의해 자기테이프(10)로부터 판독될 수 있다. 재생헤드(12)는 재생증폭기(14)와 파형등화기(16)에 의해 순서대로 추종된다. 파형등화기(16)의 출력측은 디레이 라인(디레이장치)(18)의 입력단에 접속되어 있다. 또한, 파형등화기(16)의 출력측은 아날로그 가산기(20)의 제1입력단자에 접속되어 있다. 아날로그 가산기(20)의 출력단은 디레이 라인(18)에 안내되어 있다. 아날로그 가산기(20)의 출력단자(120)의 출력단자는 PLL 회로(26)와 신호재생회로(28)에 의해 추종되는 신호검출기(22및 24)의입력단자에 접속되어 있다.

PLL 회로(26)는 위상비교기(30 및 32), 차지펌프회로(40), 루우프 필터(42)및 VCO(전압제어발진기)(44)를 포함함다. 차지펌프회로(40)는 OR 게이트(34), NOR 게이트(36)및 적분기(아날로그 가산기)(38)를 지닌다. 위상비교기(30 및 32)의 제1입력단자는 신호검출기(22및 24)의 출력단자에 접속되어 있다. 위상비교기(30 및 32)의 제2입력단자는 VCO(44)의 출력 단자에 공통으로 접속되어 있다. 위상비교기(30)는 OR 게이트(34)의 제1입력단자에 접속된 차지신호(C1)에 대한 제1입력단자를 지닌다. 또한, 위상비교기(30)는 NOR 게이트(36)의 제1입력단자에 접속된 디스차지신호(D1)에 대한 출력단자를 지닌다. 위상비교기(32)는 OR 게이트(34)의 제2입력단자에 접속된 디스차지신호(C2)에 대한 출력단자를 지닌다. 또한, 위상비교기(32)는 NOR 게이트(36)의 제2입력단자에 접속된 차지신호(C2)에 대한 출력단자를 지닌다. 또한, 위상비교기(32)는 NOR 게이트(36)의 제2입력단자에 접속된 디스차지신호(D2)에 대한 출력단자를 지닌다. OR 게이트(34)의 출력단자는 적분기(38)의 제1입력단자에 안내된다. NOR 게이트(36)의 출력단자는 적분기(38)의 제2입력단자에 안내된다. NOR 게이트(36)의 출력단자는 적분기(38)의 제2입력단자에 안내된다. VCO(44)의 입력단자에 접속되어 있다. 루우프필터(42)의 합력단자는 VCO(44)의 제어단자에 안내된다. VCO(44)의 출력단자는 신호재생회로(28)의 클럭입력단자에 접속되어 있다. 후에 알 수 있듯이, VCO(44)는 재생클럭신호를 출력시킨다.

재생증폭기(14)는 파형등화기(16)와 디레이 라인(18)을 경유해 전송된 재생된 정보신호를 아날로그 가산기(20)에 출력시킨다. 디레이 라인(18)은 클럭주기(클럭신호의 주기) T에 해당하는 시간까지 파형등화기(16)의 출력신호를 지연시키는 역할을 한다. 아날로그 가산기(20)는 파형등화기(16)와 디레이 라인(18)의 출력신호를 합하거나 가산한다. 가산된 신호, 즉 아날로그 가산기(20)의 출력신호는 정보전송 시간점마다 3개의 상이한 레벨중 하나를 한다. 따라서, 아날로그 가산기(20)의 출력신호가 3개의 상이한 레벨 사이에서 변경될 수 있다.

파형등화기(16)가 제2도의 부분(A)에 도시된 것과 같은 파형을 지닌다고 하자. 이 경우에, 아날로그 가산기(20)의 출력신호는 제2도의 부분(B)에 도시되어 있듯이 3레벨신호를 구성한다. 특히, 아날로그 가산기(20)의 출력신호는 레벨 +A, 0 -A 사이에서 변할 수 있다. 기록측(도시하지 않음)은 자기테이프(10)에 기

록된 정보신호의 예비코딩을 실행한다. 예비코딩은 아날로그 가산기(20)의 출력신호의 +A 및 -A가 이진디지털신호의 H의 논리값에 해당하는 반면, 0 레벨은 이진디지털신호의 L 논리값에 해당하게 되어 있다. 논리값 H 와 L은 1, 0의 논리상태와 같다는 것을 알 수 있다.

신호검출기(22및 24)는 아날로그 가산기(20)의 출력신호를 수신한다. 신호검출기(22)는 아날로그 가산기(20)의 출력신호의 레벨 +A를 감지하는 역할을 한다. 신호검출기(24)는 아날로그 가산기(20)의 출력신호의 레벨 -A를 감지하는 역할을 한다. 특히, 신호검출기(22)는 아날로그 가산기(20)의 출력신호를 레벨 +A(제2도의 부분(B))에 해당하는 소정의 슬라이딩 레벨과 비교하는 비교기를 포함한다. 신호검출기(22)의 비교기는 제2도의 부분(C)의 파형의 상위데이터를 출력시킨다. 신호검출기(24)는 아날로그 가산기(20)의 출력신호를 -A레벨(제2도의 부분(D))에 해당하는 소정의 슬라이딩 레벨과 비교하는 비교기를 포함한다. 신호검출기(24)의 비교기는 제2도의 부분(D)에 도시된 것과 같은 파형을 하는 하위데이터를 출력시킨다.

PLL 회로(26)의 위상비교기(30 및 32)는 서로 유사하다. 위상비교기(30 및 32)는 신호검출기(22및 24)로 부터 상위데이터 및 하위데이터를 수신한다.

제3도에 도시되어 있듯이, 위상비교기(30)(또는 위상비교기(32))는 D-플립플롭(50,56 및 62), AND 게이트 (52,54,58,60 및 64), OR 게이트(66) 및 버퍼(68)를 포함한다. 신호검출기(22)로부터 출력된 상위데이터 (또는 신호검출기(24)로부터 출력된 하위데이터)가 D-플립플롭(50)의 D 입력단자와 AND 게이트(52및 54) 의 제1입력단자에 적용된다. D-플립플롭(50)의 비반전출력단자(Q)가 AND 게이트(52)의 제2입력단자, D-플 립플롭(56)의 D 입력단자 및 AND 게이트(58)의 제1입력단자에 접속되어 있다. D-플립플롭(50)의 반전출력 단자(QN)는 AND 게이트(54)의 제2입력단자에 접속되어 있다. AND 게이트(52)의 출력단자는 AND 게이트 (60)의 제1입력단자에 접속되어 있다. AND 게이트(54)의 출력단자는 OR 게이트(66)의 제1입력단자에 안내 되어 있다. D-플립플롭(56)의 비반전출력단자(Q)가 AND 게이트(58)의 제2입력단자에 접속되어 있다. D-플 립플롭(56)의 반전출력단자(QN)가 AND 게이트(60)의 제2입력단자에 접속되어 있다. AND 게이트(60)는 디 스차지신호(D1)(또는 D2)를 출력시킨다. AND 게이트(58)의 출력단자는 D-플립플롭(62)의 입력단자와 AND 게이트(64)의 제1입력단자에 접속되어 있다. D-플립플롭(52)의 반전출력단자(QN)가 AND 게이트(64)의 제2 입력단자에 접속되어 있다. AND 게이트(64)의 출력단자는 OR 게이트(66)의 제2입력단자에 안내되어 있다. OR 게이트(66)는 차지신호(C1)(또는 C2)를 출력시킨다. 버퍼(68)의 입력단자는 VCO(44)에서 재생된 클럭 신호를 수신한다. 버퍼(68)의 비반전출력단자는 D-플립플롭(50 및 56)의 클럭입력단자에 접속되어 있다. 재생된 클럭신호가 버퍼(68)를 경유하여 D-플립플롭(50 및 56)에 전달된다. 버퍼(68)의 반전출력단자가 D-플립플롭(62)의 클럭입력단자에 접속되어 있다. 재생되 클럭신호의 반전이 버퍼(68)로부터 D-플립플롭 (62)에 공급된다.

위상비교기(30 및 32)는 작동이 유사하다. 따라서, 위상비교기(30)의 작동만을 설명한 것이다. 버퍼(68)에 가해진 재싱된 클럭신호가 제4도의 부분(A)에 도시된 것과 파형을 한다. 신호검출기(22)로부터 D-플립플롭(50)및 AND 게이트(52및 54)에 공급된 상위데이터가 제4도의 부분(B)에 도시된 것과 같은 파형을 한다. 상위데이터가 재생된 클럭신호의 매 스트로브 포인트마다(즉, 재생된 클럭신호에서 상승 또는 양 진행 모서리의 발생의 매 순간마다)D-플립플롭(50)에 의해 래치된다. 따라서, 비반전출력단자(Q)에서 나타나는 D-플립플롭(50)의 출력신호는 제4도의 부분(C)에 도시된 것과 같은 파형을 한다. D-플립플롭(50)(제4도의 부분(C))의 Q 출력신호가 재생클럭신호의 스트로브 포인트마다(즉, 재생클럭신호의 상승 또는 양진행 모서리의 발생 순간마다)D-플립플롭(56)에 의해 래치되어 비반전출력단자(Q)에 나타나는 D-플립플롭(56)의 출력신호가 제4도의 부분(D)의 파형을 한다.

AND 게이트(52)는 상위데이터(제4도의 부분(B))와 D-플립플롭(50)의 Q 출력신호(제4도의 부분(C))간의 AND 연산을 실행하여 제4도의 부분(E)에 도시된 것과 같은 파형을 하는 신호를 발생하여 출력시킨다. 반전출력단자(QN)에서 나타나는 D-플립플롭(50)의 출력신호가 AND 게이트(54)에 적용된다. AND 게이트(54)는 상위데이터(제4도의 부분(B))와 D-플립플롭(50)의 QN 출력신호간의 AND 연산을 실행하여 제4도의 부분(F)에 도시된 것과 같은 파형을 하는 신호를 발생하여 출력시킨다. AND 게이트(58) D-플립플롭(50)(제4도의 부분(C))의 Q출력신호와 D-플립플롭(56)의 Q 출력신호(제4도의 부분(D))간의 AND 연산을 실행함으로써 제4도의 부분(G)에 도시된 것과 같은 파형을 하는 신호를 발생하여 출력시킨다. 반전출력단자(QN)에 나타나는 D-플립플롭(56)의 출력신호가 AND 게이트(60)에 적용된다. AND 게이트(60)는 D-플립플롭(56)의 QN 출력신호와 AND 게이트(52)의 출력신호(제4도의 부분(E))간의 AND 연산을 실행하여 제4도의 부분(K)에 도시된 것과 같은 파형을 하는 신호를 발생하여 출력시킨다. AND 게이트(60)의 출력신호(제4도의 부분(K))는 디스차지 신호(D1)를 구성한다.

AND 게이트(58)의 출력신호는 재생된 클럭신호의 반전의 매 스트로브 포인트마다(즉, 재생크럭신호의 하강 또는 부로 향하는 에지의 발생의 매 순간마다) D-플립플롭(62)에 의해 래치된다. 따라서, 비반전출력단자(Q)에 나타나는 D-플립플롭(62)의 출력신호가 제4도의 부분(H)에 도시된 것과 같은 파형을 한다. 한편, 반전출력단자(QN)에 나타나는 D-플립플롭(62)의 출력신호가 Q 출력신호의 반전과 일치한다. AND 게이트(64)는 D-플립플롭(62)의 QN 출력과 AND 게이트(58)의 출력신호(제4도의 부분(G))간의 AND 연산을 실행함으로써 제4도의 부분(I)에 도시된 파형을 하는 신호를 발생하여 출력시킨다. OR 게이트(66)는 AND 게이트(54)의 출력신호(제4도의 부분(I))간의 OR 연산을 실행함으로써 제4도의 부분(J)에 도시된 파형을 하는 신호를 발생하여 출력시킨다. OR 게이트(66)의 출력신호(제4도의 부분(J)에 도시된 파형을 하는 신호를 발생하여 출력시킨다. OR 게이트(66)의 출력신호(제4도의 부분(J)에 도시된 파형을 하는 신호를 발생하여 출력시킨다. OR 게이트(66)의 출력신호(제4도의 부분(J))는 차지신호(C1)를 구성한다.

위상비교기(32)는 신호검출기(24)로부터 하위데이터를 수신한다. 위상비교기(32)는 위상비교기(30)에 의해 상위데이터를 처리하는 방식으로 재생된 클럭신호에 따라 하위데이터를 처리함으로써 위상비교기(32)는 하위데이터에 응답하여 차지신호(C2)와 디스차지신호(D2)를 발생하여 출력시킨다.

차지펌프회로(40)를 상세히 설명할 것이다. 제5도에 도시되어 있듯이, 차지펌프회로(40)의 0R 게이트(34)는 0R 소자(34A) 및 버퍼(34B)를 포함한다. 0R 소자(34A)의 제1및 제2입력단자는 위상비교기(30 및 32)로부터 차지신호(C1및 C2)를 수신한다. 0R 소자(34A)의 출력단자는 버퍼(34B)의 입력단자에 안내되어 있다. 버퍼(34B)의 출력단자는 저항(R1)을 경유하여 차지펌프회로(40)의 연상증폭기(38A)의 반전입력단자에 접속되어 있다. 차지펌프회로(40)의 NOR 게이트(36)는 0R 소자(36A)와 인버터(36B)를 포함한다. 0R 소자(36A)의 제1및 제2단자는 위상비교기(30 및 32)로부터 디스차지신호(D1및 D2)를 수신한다. 0R 소자

(36A)의 출력단자는 인버터(36B)의 입력단자에 안내되어 있다. 인버터(36B)의 출력단자는 저항(R2)을 경유하여 연산증폭기(38A)의 반전입력단자에 접속되어 있다.

제5도에 도시되어 있듯이, 차지펌프회로(40)는 버퍼(348)와 인버터(36B)와 같은 버퍼(38C)와 인버터(38 B)를 포함한다. 버퍼(38C)와 인버터(38B)의 입력단자는 접지되어 있다. 버퍼(38C)의 출력단자는 저항(R 1)에 해당하는 저항(R3)을 경유하여 연산증폭기(38A)의 비반전입력단자에 접속되어 있다. 인버터(38D)의 출력단자는 저항(R2)에 해당하는 저항(R4)를 경유하여 연산증폭기(38A)의 비반전입력단자에 접속되어 있다.

캐패시터(38B)가 연산증폭기(38A)의 출력단자와 연산증폭기(38A)의 반전입력단자 사이에 접속되어 있다. 따라서, 연산증폭기(38A)와 캐패시턴스(38B)는 차지펌프회로(40)의 적분기(38)에 해당하는 적분기를 구성 한다. 연산증폭기(38A)의 출력단자, 즉 적분기(38)의 출력단자가 루우프 필터(42)의 입력단자에 접속되어 있다(제1도).

차지신호(C1및 C2)는 OR 소자(34A), 버퍼(34B) 및 저항(R1)을 경유하여 연산증폭기(38A)에 전달된다. 디스차지신호(D1및 D2)는 OR 소자(36A), 인버터(36B) 및 저항(R2)을 경유하여 연산증폭기(38A)에 전달된다. 차지신호(C1및 C2)와 디스차지신호(D1및 D2)의 반전이 저항(R1및 R2) 사이의 접점에서 아날로그 가산처리에 의해 합성차지/디스차지신호로 결합된 다음, 합성차지/디스차지신호가 연산증폭기(38A)의 반전입력단자에 도달한다. 연산증폭기(38A)의 출력신호의 전압(즉, 적분기(38)의 전압)이 차지신호(C1또는 C2)의 모든 유효펄스에 따라 증가한다. 연산증폭기(38A)의 출력신호의 전압(즉, 적분기(38)의 전압)은 디스차지신호(D1또는 D2)의 모든 유효펄스에 따라 감소한다. 차지신호 및 디스차지신호가 제4도의 부분(J) 및 (K)에 도시된 것퍼럼 변하는 경우, 연산증폭기(38A)에 적용된 합성차지/디스차지신호가 제4도의 부분(L)에 도시된 것과 같은 파형을 한다. 연산증폭기(38A)는 합성차지/디스차지신호에 따라 캐패시터(38B)를 차지하고디스차지하는 과정을 실행한다. 연산증폭기(38A)의 출력신호(즉, 적분기(38)의 출력신호)는 루우프 필터(42)에 공급된 차지펌프회로(40)의 출력 신호를 구성한다(제1도).

제1도를 다시 참조하면, 신호재생회로(28)는 신호검출기(22및 24)로부터 상위데이터와 하위데이터를 수신한다. 신호재생회로(28)는 PLL 회로(26)의 VCO(44)로부터 재생된 클럭신호를 수신한다. 신호재생회로(28)는 상위데이터와 하위데이터간의 OR 연산을 실행하는 OR 게이트를 포함한다. 또한, 신호재생회로(28)는 재생된 클럭신호에 따라 OR 게이트의 출력신호를 래칭함으로써 OR 게이트의 출력신호를 원 2레벨 디지털신호로 변환하는 장치(예를 들어, D-플립플롭)를 포함한다.

제1도의 장치의 전체 작동을 아래에 설명할 것이다. 파티셜 리스판스 검출 클래스 4(PR4)에 따르는 정보신호가 재생해드(12)에 의해 자기테이프(10)로부터 판독된다. 판독된 정보신호(재생된 정보신호)가 재생해드(12)로부터 재생증폭기(14)에 출력되어 재생증폭기(14)에 의해 증폭된다. 증폭된 정보신호가 재생증폭기(14)로부터 파형등화기(16)에 가해진다. 증폭된 정보신호가 파형등화기(16)에 의해 처리된다. 특히, 파형등화기(16)는 증폭된 정보신호에서 내부기호 방해성분을 제거한다. 파형등화기(16)로부터 출력된 정보신호가 지연되지 않은 정보신호로 아날로그 가산기(20)에 직접 적용된다. 파형등화기(16)로부터 출력된 정보신호가 지연되지 않은 정보신호로 아날로그 가산기(20)에 직접 적용된다. 자연된 정보신호가 지연된 정보신호가 지연된 정보신호가 이번로그 가산기(20)에 디레이 라인(18)으로부터 적용된다. 지연되지 않은 정보신호와 지연된 정보신호가 아날로그 가산기(20)에 의해 가산된다. 가산된 정보신호가 아날로그 가산기(20)로부터 신호검출기(22및 24)에 공급된다. 전에 설명했듯이, 가산된 정보신호가 신호검출기(22및 24)에 의해 상위데이터와 하위데이터로 변환된다. 상위데이터와 하위데이터가 신호검출기(22및 24)에서 PLL 회로(26)의 위상비교기(30 및 32)에 적용된다. 위상비교기(30)는 상위데이터의 위상과 하위데이터의 위상을 비교함으로써 상위데이터와 재생된 클럭신호에 따라 차지신호(C1)와 디스차지신호(D1)를 발생하여 출력시킨다. 위상비교기(32)는 하위데이터의 위상과 재생된 클럭신호를 비교함으로써 하위데이터와 재생된 클럭신호에 따라 차지신호(C2)와 디스차지신호(D2)를 발생하여 출력시킨다.

모든 유효펄스의 기간이 재생된 클럭신호의 하나의 스토로브 포인트만을 포함하도록 상위데이터와 하위데이터의 유효펄스가 매우 짧은 경우가 고려되었다. 이 상태에서 아날로그 가산기(20)의 출력신호가 제6도의 부분(A)에 도시된 것과 같은 파형을 한다. 또한, 신호검출기(22)로부터 출력된 상위데이터가 제6도의 부분(B)에 도시된 것과 같은 파형을 하는 반면, 신호검출기(24)로부터 출력된 하위데이터가 제6도의 부분(C)에 도시된 것과 같은 파형을 한다. 재생된 클럭신호가 제6도의 부분(D)에 도시된 것과 같은 파형을 한다. 재생된 클럭신호가 제6도의 부분(D)에 도시된 것과 같은 파형을 한다. 이 상태에서, OR 게이트(34)에 의해 제공된 차지신호(C1및 C2)의 결합은 제6도의 부분(E)에 도시된 것과 같은 파형을 한다. 한편, NOR 게이트(36)에 의해 제공된 디스차지신호(D1및 D2)의 결합의 반전은 제6도의 부분(F)에 도시된 것과 같은 파형을 한다.

제6도의 상태에서, 차지신호(C1및 C2)의 결합의 제1유효펄스(CA)의 리딩 에지(제6도의 부분(E))는 상위데이터의 제1상승모서리(EA1)(제6도의 부분(B))에 의해 야기된다. 제1유효차지펄스(CA)의 트레일링 에지(제6도의 부분(E))는 상위데이터의 제1상승모서리(EA1)(제6도의 부분(B))의 발생 순간을 즉시 추종하는 재생된 클럭신호의 스트로브 포인트(SPA)(제6도의 부분(D))에 의해 야기된다. 이와 유사하게, 차지신호(C1및C2)의 결합의 제2유효펄스 또는 후의 펄스의 리딩 에지와 트레일링에지(제6도의 부분(E))가 상위데이터(또는 하위데이터)의 상승모서의 및 재생된 클럭신호의 스트로브 포인트에 의해 결정된다.

제6도의 상태에서, 디스차지신호(D1및 D2)의 결합반전의 제1유효펄스(DA)의 리딩 에지(제6도의 부분(F))는 재생클럭신호의 스트로브 포인트(SPA)(제6도의 부분(D))에 의해 야기된다. 제1유효디스차지펄스(DA)의트레일링 에지(제6도의 부분(F))는 재생된 클럭신호의 스트로브 포인트(SPA)(제6도의 부분(D))를 즉시 추종하는 상위데이터의 제1하강모서리(EA2)(제6도의 부분(B))에 의해 야기된다. 이와 유사하게, 디스차지신호(D1및 D2)의 결합반전의 제2유효펄스 또는 후의 유효펄스의 리딩에지와 트레일링 에지(제6도의 부분(F))가 재생된 클럭신호의 스트로브 포인트 및 상위데이터(또는 하위데이터)의 하강모서리에 의해 결정된다.

차지신호(C1및 C2)의 결합은 OR 게이트(34)로부터 적분기(38)에 공급된다. 디스차지신호(D1및 D2)의 결합의 반전이 NOR 게이트(36)로부터 적분기(38)에 공급된다. 위상에러 또는 주파수에러가 재생정보신호(상위데이터 및 하위데이터)와 재생된 클럭신호 사이에서 발생하는 경우, 차지신호(C1및 C2)의 결합의 모든 유

호펄스(에 의해 점유된 타임 도메인 영역)의 기간과 디스차지신호(D1및 D2)의 결합의 반전의 모든 유효펄스(에 의해 점유된 타임 도메인 영역)의 기간 사이에 차이가 있다. 적분기(38)는 이러한 차이를 검출하고, 검출된 차이를 나타내는 신호를 출력시킨다. 이러한 차이를 나타내는 시호가 적분기(38)로부터 루우프 필터(42)를 경유하여 VCO(44)에 대한 제어신호로 VCO(44)에 공급된다. VCO(44)는 재생된 정보신호와 재생된 클럭신호간의 위에서 언급한 위상에러를 널(nu11)하기 위해 제어신호에 따라 재생된 클럭 신호의 위상 또는 주파수를 조절한다.

제6도의 상태에서, 차지신호(C1및 C2)의 결합의 유호펄스(CA)와 디스치지신호(D1및 D2)의 걸합의 반전의 유효펄스(DA)는 유효펄스(CA 및 DA)간의 기간(펄스폭)의 차를 나타내는 신호가 적분기(38)로부터 출력되도록 적분기(38)에 의해 가산된다. 차이를 나타내는 신호가 적분기(38)부터 루우프 필터(42)를 경유하여 VCO(44)에 대한 제어신호로 VCO(44)에 공급된다. VCO(44)는 재생된 정보신호와 재생된 클럭신호를 널 (nu11)하기 위해 제어신호에 따라 재생클럭신호의 위상 또는 주파수를 조절한다. 제6도의 상태에서, VCO(44)에 의한 재생클럭신호의 위상조절은 제6도의 부분(D)에 도시 되어 있듯이 방향(FA)으로 스트로브 포인트의 타이밍을 이동시킨다. 따라서, 재생된 클럭신호가 재생된 정보신호와 양호한 동기화된 관계 또는 양호한 타이밍 관계로 유지된다.

모든 유효펄스의 기간이 재생된 클럭신호의 두 개 이상의 스트로브 포인트를 포함하도록 상위데이터와 하 위데이터의 유효펄스가 긴 경우가 고려되었다. 이 상태에서 이날로그 가산기(20)의 출력신호가 제7도의 부분(A)에 도시된 것과 같은 파형을 한다. 또한, 신호검출기(22)로부터 출력된 상위데이터가 제7도의 부 분(B)에 도시된 것과 같은 파형을 하는 반면, 신호검출기(24)로부터 출력된 하위데이터가 제7도의 부분 (C)에 도시된 것과 같은 파형을 한다. 재생된 클럭신호가 제7도의 부분(D)에 도시된 것과 같은 파형을 한 다고 하면, OR 게이트(34)에 의해 제공되는 차지신호(C1및 C2)의 결합이 제7도의 부분(E)에 도시된 것과 같은 파형을 한다. 한편, NOR 게이트(36)에 의해 제공된 디스차지신호(D1및 D2)의 결합의 반전은 제7도의 부분(F)에 도시된 것과 같은 파형을 한다.

제7도의 상태에서, 차지신호(C1및 C2)의 결합의 제1유효펄스(CB1)의 리딩 에지(제7도의 부분(E))는 상위 데이터의 제1상승모서리(EB1)(제7도의 부분(B))에 의해 야기된다. 제1유효차지펄스(CB1)의 트레일링 에지 (제7도의 부분(E))는 상위데이터의 제1상승모서리(EB1)(제7도의 부분(B))의 발생 순간을 즉시 추종하는 재생클럭신호의 스트로브 포인트(SPB1)(제7도의 부분(D))에 의해 야기된다. 한편, 디스차지신호(D1및 D 2)의 결합의 반전의 제1유효펄스(DB1)의 리딩 에지(제7도의 부분(F))는 재생된 클럭신호의 스트로브 포인트(SPB1)(제7도의 부분(D))에 의해 야기된다.

제1유효디스차지펄스(DB1)의 트레일링 에지(제7도의 부분(F))가 재생 클럭신호의 다음 스트로브 포인트 (SPB2)(제7도의 부분(D))에 의해 야기된다. 차지신호(C1및 C2)의 결합의 제2유효펄스(CB2)의 리딩 에지(제7도의 부분(E))는 제1유효디스차지펄스(DB1)의 트레일링 에지(제7도의 부분(F))와 일치한다. 제2유효 차지펄스(CB2)의 기간(제7도의 부분(E))은 재생된 클럭신호의 주기(제7도의 부분(D))의 반에 해당한다. 이와 유사하게, 제3및 이후 유효펄스(CC1및 CC2)가 차지신호(C1및 C2)의 결합(제7도의 부분(E))으로 발생하는 반면, 제2유효펄스(DC1)가 디스차지펄스(D1및 D2)의 결합(제7도의 부분(F))의 반전으로 발생된다.

자지신호(C1및 C2)의 결합은 OR 게이트(34)로부터 적분기(38)에 공급된다. 디스차지신호(D1및 D2)의 결합의 반전이 NOR 게이트(36)로부터 적분기(38)에 공급된다. 제7도의 상태에서, 적분기(38)는 유효차지펄스(CB1및 CB2)의 기간의 합(제7도의 부분(E))에서 유효디스차지펄스(DB1)의 기간(제7도의 부분(F))을 감산하는 역할을 한다. 유효디스차지펄스(DB1)의 기간은 재생된 클럭신호의 기간과 같고, 유효차지펄스(CB2)의 기간은 재생클럭신호의 기간의 반이기 때문에 유효디스차지펄스(DB1)의 기간의 반이 적분기(38)에 의해 감산중 유효차지펄스(CB2)의 기간까지 취소된다. 따라서, 적분기(38)는 유효차지펄스(CB1)의 기간과유효디스차지펄스(DB1)의 기간의 반 사이의 차이를 검출한다. 위상에러 또는 주파수에러가 재생된 정보신호(상위데이터 및 하위데이터)가 재생된 클럭신호 사이에서 발생하는 경우, 유효차지펄스(CB1)의 기간과유효디스차지펄스(DB1)의 기간의 반 사이에 차이가 존재한다. 적분기(38)는 이러한 차이를 검출하고,검출된 차이를 나타내는 신호를 출력시킨다. 이러한 차이를 나타내는 신호가 적분기(38)로부터 루우프 필터(42)를 경유하여 VCO(44)에 대한 제어신호로 VCO(44)에 공급된다. VCO(44)는 재생정보신호와 재생클럭신호 사이의 위에서 언급한 위상 에러를 널(nu11)하기 위해 제어신호에 따라 재생된 클럭신호의 위상 또는 주파수를 조절한다.

제7도의 최종 단계중, 유효차지펄스(DC1)의 기간과 유효차지펄스(CC1및 CC2)의 기간의 합 사이의 차이를 나타내는 신호가 적분기(38)로부터 출력되도록 유효차지펄스(CC1및 CC2)와 유효디스차지펄스(DC1)가 적분기(38)에 의해 가산된다. 차이를 나타내는 신호가 적분기(38)로부터 루우프 필터(42)를 경유하여 VCO(44)에 대한 제어신호로 VCO(44)에 공급된다. VCO(44)는 재생된 정보신호와 재생된 클럭시호간의 위에서 업급한 위상에러를 널(nu11)하기 위해 제어시호에 따라 재생된 클럭신호의 위상 또는 주파수를 조절한다.

제7도의 상태에서, VCO(44)에 의한 재생클럭신호의 위상조절이 제7도의 부분(D)에 도시된 방향(FB)으로 스트로브 포이트의 타이밍을 이동시킨다. 따라서, 재생된 클럭신호가 재생된 정보신호와 양호한 동기화된 관계 또는 양호한 타이밍 관계로 유지된다.

### [제2실시예]

제8도는 아래에서 지적한 설계변경을 제외하고 제1도의 실시예와 유사한 본 발명의 제2실시예의 부분을 도시한다.

제8도의 실시예는 파티셜 리스판스 검출 클래스 4(PR4)에 따르지 않는 n 레벨 정보신호를 처리한다. 여기서. n 은 3과 다른 소정의 자연수이다.

제8도의 실시예는 제1도의 신호검출기(22및 24)에 해당하는 신호검출기(SD1, SD2, SD3, . . . 및 SDn-1)를 포함한다. 신호검출기(SD1, SD2, SD3, . . . 및 SDn-1)는 아날로그 가산기(20)를 추종한다(제1도). 신호검출기(SD1, SD2, SD3, . . . 및 SDn-1)는 아날로그 가산기(20)의 출력신호의 상이한 레벨을 감지한다. 제8도의 실시예는 제1도의 위상비교기(30 및 32)에 해당하는 위상비교기(PC1, PC2, PC3, . . . 및 PCn-1)를 포함한다. 위상비교기(PC1, PC2, PC3, . . . 및 PCn-1)는 신호검출기(SD1, SD2, SD3, . . . 및 SDn-1)를 추종한다. 각각의 위상비교기(PC1, PC2, PC3, . . . 및 PCn-1)는 관련 위상비교기의 출력 신호에 따라 차지신호와 디스차지신호를 차지펌프회로(84)에 출력시킨다. 차지펌프회로(84)는 제1도의 차지펌프회로(40)에 해당한다. 위상비교기(PC1, PC2, PC3, . . . 및 PCn-1)로부터 출력된 차지신호와 디스차지신호가 차지 펌프회로(84)에 의해 가산된다. 차지펌프회로(84)의 결과출력신호가 루우프필터(42)에 공급된다(제1도).

#### [제3실시예]

본 발명의 제3실시예는 아래에서 지적한 설계변경 외에 제1도의 실시예와 유사하다.

제3실시예는 PR(1)또는 PR(1, -1)에 해당하는 정보신호를 처리하고, 여기서 PR 은 파티셜 리스판스이다. 신호검출기(22및 24)중 하나(제1도)및 위상비교기(30 및 32) 중 하나(제1도)가 제1실시예(제3실시예)로부터 생략되었다.

#### [제4실시예]

본발명의 제4실시예는 제4실시예가 디스크장치 또는 디지털전송장치로 설치되었다는 점을 제외하고 제1도의 실시예와 유사하다.

#### [제5실시예]

본 발명의 제5실시예는 후에 설명한 부가적인 배열을 제외하고 제1도의 실시예와 유사하다.

제5실시예는 제5도의 차지펌프회로(40)에 부가된 주파수검출회로를 포함한다. 주파수 검출회로는 재생된 클럭신호의 주파수를 감지하고, 재생된 클럭신호의 주파수를 소정의 주파수범위와 비교한다. 재생된 클럭신호의 주파수가 소정의 주파수범위의 상한 보다 높을 때, 주파수검출신호가 디스차지 입력측을 고레벨에 설정한다. 재생된 클럭신호의 주파수가 소정의 주파수범위의 하한 보다 낮을 때, 주파수검출회로는 차지입력측을 고레벨에 설정한다.

제5실시예에서 주파수 검출회로는 PLL 회로에 관계하는 록-인 레인지를 넓게 록-인 타임을 짧게 한다.

#### [제6실시예]

제6실시예는 후에 설명한 설계변경을 제외하고 제1도의 실시예와 유사하다 제6실시예는 제1도의 위상비교기(30 및 32)대신 위상비교기(130 및 132)를 포함한다.

위상비교기(130 및 132)는 서로 유사하다. 위상비교기(130 및 132)는 신호검출기(22및 24)로부터 상위데이터와 하위데이터를 수신한다(제1도).

제9도에 도시되어 있듯이, 위상비교기(130)(또는 위상비교기(132))는 버퍼(150), D-플립를롭(152및 158), AND 게이트(154, 156, 160 및 162)및 OR 게이트(164)를 포함한다. 버퍼(150)의 입력단자는 신호검출기(22)로부터 상위데이터(또는 신호검출기(24)로부터 하워데이터)를 수신한다. 비교기(130)의 비반전출력단지는 D-플림플롭의 D 입력단자 및 AND 게이트(154 및 156)의 제1입력단자에 접속되어 있다. 버퍼(150)의 반전출력단자는 AND 게이트(160)의 제1입력단자에 접속되어 있다.

D-플립플롭(152)의 비반전출력단자(Q)는 AND 게이트(154 및 160)의 제2입력단자와 D-플립플롭(158)의 D입력단자에 접속되어 있다. D-플립플롭(152)의 반전출력단자(QN)가 AND 게이트(156)의 제2입력단자에 접속되어 있다. AND 게이트(154)의 출력단자는 AND 게이트(162)의 제1입력단자에 안내되어 있다. AND 게이트(156)의 출력단자는 OR 게이트(164)의 제1입력 단자에 안내되어 있다. D-플립플롭(158)의 비반전출력단자(Q)가 AND 게이트(160)의 제3입력단자에 접속되어 있다. D-플립플롭(158)의 반전 출력단자(QN)가 AND 게이트(162)의 제2입력단자에 접속되어 있다.

AND 게이트(162)는 디지차지신호(D1또는 D2)를 차지펌프회로(40)의 NOR 게이트(36)(제1도)에 출력시킨다. AND 게이트(160)의 출력단자는 OR 게이트(164)의 제2입력단자에 안내되어 있다. OR 게이트(164)는 차지신호(C1또는 C2)를 차지펌프회로(40)의 OR 게이트(34)(제1도)에 출력시킨다. D-플립플롭(152및 158)의 클럭입력단자 VCO(44)(제1도)로부터 재생클럭신호를 수신한다.

위상비교기(130 및 132)는 작동이 유사하다. 따라서, 위상비교기(130)의 작동만을 설명할 것이다. D-플립플롭(152및 158)에 가해진 재생된 클럭신호는 제10도의 부분(A)에 도시된 것과 같은 파형을 한다. 신호검출기(22)(제1도)로부터 퍼버(150)에 공급된 상위데이터는 제10도의 부분(B))에 도시된 것과 같은 파형을 한다. 상위데이터는 버퍼(150)를 통과한 다음 D-플립플롭(152)에 도달한다. 상위데이터는 재생된 클럭신호의 매 스트로보 포인트 마다(즉, 재생된 클럭신호의 상승 또는 양 진행 모서리의 발생의 매 순간 마다) D-플립플롭(152)에 의해 래치된다. 따라서, 비반전추력단자(Q)에 나타나는 D-플립플롭(152)의 출력신호가 제10도의 부분(C)에 도시된 것과 같은 파형을 한다. D-플립플롭(152)의 Q 출력신호(제10도의 부분(C))가 재생클럭신호의 매 스트로브 포인트(즉, 재생클럭신호의 상승 또는 양 진행 모서리의 발생의 매 순간마다)D-플립플롭(158)에 의해 래치된다. 따라서, 비반전출력단저(Q)에 나타나는 D-플립플롭(158)의 출력신호가 제10도의 부분(D)에 도시된 것과 같은 파형을 한다.

상위데이터(제10도의 부분(B))가 버퍼(150)를 통과한 후 AND 게이트(154 및 156)에 도달한다. D-플립플롭(152)(제10도의 부분(C))의 Q 출력신호가 AND 게이트(154)에 가해진다. AND 게이트(154)는 상위데이터(제10도의 부분(B))와 D-플립플롭(152)의 Q 출력신호(제10도의 부분(C))간의 AND 연산을 실행한다. AND 게이트(154)의 출력신호는 AND 게이트(162)에 가해진다. 반전출력단자(QN)에 나타나는 D-플립플롭(158)의 출력신호가 AND 게이트(162)에 가해진다. AND 게이트(162)는 AND 게이트(154)의 출력신호와 D-플립플롭(158)의 QN 출력신호간의 AND 연산을 실행함으로써 제10도의 부분(F)에 도시된 것과 같은 파형을 하는 신호를 발생하여 출력시킨다. AND 게이트(162)의 출력신호는 디스차지신호(D1)를 구성한다.

반전출력단자(QN)에 나타나는 D-플립플롭(152)의 출력신호가 AND 게이트(156)에 가해진다. AND 게이트

(156)는 상위데이터(제10도의 부분(B))와 D-플립플롭(152)의 QN 출력신호간의 AND 연산을 실행함으로써 제10도의 부분(G)에 도시된 것과 같은 파형을 하는 신호를 발생하여 출력시킨다. AND 게이트(156)의 출력신호는 OB 게이트(164)에 가해진다.

버퍼(150)는 상위데이터의 반전을 AND 게이트(160)에 출력시킨다. D-플립플롭(152및 158)의 Q 출력신호는 AND 게이트(160)에 공급된다. AND 게이트(160)는 D-플립플롭(152및 158)의 상위데이터와 Q 출력신호의 반전간의 AND 연산을 실행함으로써 제10도의 부분(E)에 도시된 것과 같은 파형을 하는 신호를 발생하여 출력시킨다. AND 게이트(164)의 출력신호가 OR 게이트(164)에 가해진다. OR 게이트(164)는 AND 게이트(156)(제10도의 부분(G))의 출력신호와 AND 게이트(160)(제10도의 부분(E))의 출력신호간의 OR 연산을 실행함으로써 제10도의 부분(H)에 도시된 것과 같은 파형을 하는 신호를 발생하여 출력시킨다. OR 게이트(164)의 출력신호는 차지신호(C1)를 구성한다.

위상비교기(132)는 신호검출기(24)(제1도)로부터 하위데이터를 수신한다. 위상비교기(132)는 위상비교기(130)에 의한 상위데이터를 처리하는 방식으로 재생된 클럭신호에 따라 하위데이터를 처리함으로써 위상비교기(132)는 하위데이터에 따라 차지신호(C2) 및 디스차지신호(D2)를 발생하여 출력시킨다. 디스차지신호와 차지신호가 제10도의 부분(F) 및 (H)에 도시된 것처럼 변하는 경우, 연산증폭기(38A)(제5도)에 가해진 합성차지/디스차지신호가 제10도의 부분(I)에 도시된 것과 같은 파형을 한다.

매 유효펄스의 기간이 재생된 클럭신호의 하나의 스트로브 포인트만을 포함하도록 상위데이터와 하위데이터의 유효펄스가 매우 짧은 상태가 고려되었다. 이러한 상태의 예는 제10도 기간(T1)동안 발생한다. 제10도의 기간(T1)동안, 차지신호(C1)의 유효펄스(CA1)의 리딩 에지(제10도의 부분(H))가 상위데이터의 제1상 승모서리(EA1)(제10도의 부분(B))에 의해 야기된다. 유효차지펄스(CA1)의 트레일링 에지(제10도의 부분(H))가 상위데이터(제10도의 부분(B))의 제1상승모서리(EA1)의 발생 순간을 즉시 추종하는 재생된 클럭신호의 스트로브 포인트(SPA1)에 의해 야기된다. 한편, 디스차지신호(D1)(제10도의 부분(F))의 유효펄스(DA1)의 리딩 에지가 재생클럭신호(제10도의 부분(A))의 스트로브 포인트(SPA1)에 의해 야기된다. 유효디스차지펄스(DA1)(제10도의 부분(F))의 트레일링 에지는 재생클럭신호(제10도의 부분(A))의 스트로브 포인트(SPA1)에 의해 야기된다. 무인트(SPA1)를 즉시 추종하는 상위데이터(제10도의 부분(B))의 제1하강모서리(EA2)에 의해 야기된다.

이와 유사하게, 차지신호(C2)와 디스차지신호(D2)의 유효펄스가 하위 데이터와 재생된 클럭신호에 따라 발생된다.

위상비교기(130 및 132)는 차지신호(C1및 C2)를 차지펌프회로(40)의 OR 게이트(34)(제1도)에 출력시킨다. 차지신호(C1및 C2)의 결합은 OR 게이트(34)에 의해 제공된다. 위상비교기(130 및 132)는 디스차지신호(D1 및 D2)를 차지펌프회로(40)의 NOR 게이트(36)(제1도)에 출력시킨다. 디스차지신호(D1및 D2)의 결합의 반 전은 NOR 게이트(36)에 의해 제공된다.

차지신호(C1및 C2)의 결합은 NOR 게이트(34)로부터 차지펌프회로(40)의 적분기(38)(제1도)에 공급된다. 디스차지신호(D1및 D2)의 결합의 반전은 NOR 게이트(36)로부터 적분기(38)에 공급된다. 위상에러 또는 주파수에러가 재생된 정보신호(상위데이터와 하위데이터)와 재생된 클럭신호 간에서 발생하는 경우, 차지신호(C1및 C2)의 결합의 매 유효펄스(에 의해 점유된 타임 도메인 영역)의 기간과 디스차지신호(D1및 D2)의 결합의 반전의 매 유효펄스(에 의해 점유된 타임 도메인 영역)의 기간 사이에 차이가 존재한다. 적분기(38)는 이러한 차이를 검출하고, 검출된 차이를 나타내는 신호를 출력시킨다. 차이를 나타내는 신호가 적분기(38)에서 루우프 필터(42)(제1도)를 경유하여 VCO(44)에 대한 제어신호로 VCO(44)에 공급된다. VCO(44)는 재생된 정보신호와 재생된 클럭신호간의 위에서 언급한 위상에러를 널(null)하기 위해 제어신호에 따라 재생된 클럭신호의 위상 또는 주파수를 조절한다.

제10도의 기간(T1)동안, 유효차지펄스(CA1)(제10도의 부분(H))와 유효디스차지펄스(DA1)(제10도의 부분(F))의 반전은 유효펄스(CA1및 DA1)간의 기간(펄스폭)의 차이를 나타내는 신호가 적분기(38)로부터 출력되도록 적분기(38)에 의해 가산된다. 차이를 나타내는 신호가 적분기(38)로부터 루우프 필터(42)를 경유하여 VCO(44)에 대한 제어신호로 VCO(44)에 공급된다. VCO(44)는 재생된 정보신호와 재생된 클럭신호간의위에서 언급한 위상에러를 널(null)하기 위해 제어신호에 따라 재생된 클럭신호의 위상 또는 주파수를 조절한다. 제10도의 기간(T1)동안, VCO(44)에 의한 재생된 클럭신호의 위상조절은 제10도의 부분(A)에 도시된 것처럼 방향(FA1)으로 스트로브 포인트의 타이밍을 이동시킨다. 따라서, 재생된 클럭신호는 재생된 정보신호와 양호한 동기화된 관계 또는 양호한 타이밍 관계로 유지된다.

상위데이터와 하위데이터는 유효펄스마다의 기간이 재생된 클럭신호의 두 개 이상의 스트로브 포인트를 포함하도록 매우 긴 경우가 고려되었다. 이러한 상태의 예는 제10도의 기간(DT2)동안 발생한다. 제10도의 기간(T2)동안, 차지신호(C1)(제10도의 부분(H))의 유효펄스(CA2)의 리딩 에지가 상위데이터(제10도의 부분(B))의 상승모서리(EA3)에 의해 야기된다. 유효차지펄스(CA2)(제10도의 부분(H))의 트레일링 에지는 상위데이터(제10도의 부분(B))의 상승모서리(EA3)의 발생 순간을 즉시 추종하는 재생 클럭신호(제10도의 부분(A))의 스트로브 포인트(SPA2)에 의해 야기된다. 한편, 디스차지신호(D1)(제10도의 부분(F))의 유효펄스(DA2)의 리딩 에지가 재생된 클럭신호(제10도의 부분(A))의 스트로브 포인트(SPA2)에 의해 야기된다. 유효디스차지펄스(DA2)(제10도의 부분(F))의 트레일링 에지는 재생클럭신호(제10도의 부분(A))의 다음 스트로브 포인트에 의해 야기된다. 차지신호(C1)(제10도의 부분(H))의 다음 유표펄스(CA3)의 리딩 에지가 상위데이터(제10도의 부분(B))의 하강모서리(EA4)에 의해 야기된다. 유효차지펄스(CA3)의 트레일링 에지는 상위데이터(제10도의 부분(B))의 하강모서리(EA4)에 일해 순간을 즉시 추종하는 재생된 클럭신호(제10도의 부분(A))의 스트로브 포인트(SPA3)에 의해 야기된다.

이와 유사하게, 차지신호(C2)와 디스차지신호(D2)의 유효펄스가 하위데이터와 재생클럭신호에 따라 발생한다.

위상비교기(130 및 132)는 차지신호(C1및 C2)를 차지펌프회로(40)의 OR 게이트(34)에 출력시킨다. 차지신호(C1및 C2)의 결합은 OR 게이트(34)에 의해 제공된다. 위상비교기(130 및 132)는 디스차지신호(D1및 D 2)를 차지펌프회로(40)의 NOR 게이트(36)에 출력시킨다. 디스차지신호(D1및 D2)의 결합의 반전은 NOR 게이트(36)에 의해 제공된다.

차지신호(C1및 C2)의 결합은 OR 게이트(34)로부터 차지펌프회로(40)의 적분기(38)에 공급된다. 디스차지신호(D1및 D2)의 결합의 반전은 NOR 게이트(36)로부터 적분기(38)에 공급된다. 제10도의 기간(T2)동안, 적분기(38)는 유효차지펄스(CA2및 CA3)(제10도의 부분(H))의 기간합으로부터 유효디스차지펄스(DA2)(제10도의 부분(F))의 기간을 감산하는 역할을 한다. 재생된 정보신호(상위데이터와 하위데이터)와 재생된 클럭신호 사이에서 위상에러 또는 주파수에러가 발생하는 경우, 유효디스차지펄스(DA2)의 기간과 유효차지펄스(CA2및 CA3)의 합간에 차이가 존재한다. 적분기(38)는 이러한 차이를 검출하고, 검출된 차이를 나타내는 신호를 출력시킨다. 차이를 나타내는 신호가 적분기(38)로부터 루우프 필터(42)를 경유하여 VCO(44)에 대한 제어신호로 VCO(44)에 공급된다. VCO(44)는 재생된 정보신호와 재생된 클럭신호간의 위에서 언급한 위상에러를 널(null)하기 위해 제어신호에 따라 재생된 클럭신호의 위상 또는 주파수를 조절한다. 제10도의 기간(T2)동안, VCO(44)에 의한 재생된 클럭신호의 위상조절은 제10도의 부분(A)에 도시되어 있듯이 방향(FA2)으로 스트로브 포인트의 타이밍을 이동시킨다. 따라서, 재생된 클럭신호가 재생된 정보신호와 양호한 동기화된 관계 및 양호한 타이밍 관계로 유지된다.

#### [제7실시예]

본 발명의 제7실시예는 아래에서 설명한 설계변경을 제외하고 제1도의 실시예와 유사하다. 제7실시예는 제1도의 비상비교기(30 및 32)대신 위상비교기(230 및 232)를 포함한다.

위상비교기(230 및 232)는 서로 유사하다. 위상비교기(230 및 232)는 신호검출기(22및 24)(제1도)로부터 상위 데이터와 하위데이터를 수신한다.

제11도에 도시되어 있듯이, 위상비교기(230)(또는 위상비교기(232))는 버퍼(200), D-플립플롭(202및 206), AND 게이트(204, 208 및 210)및 OR 게이트(212)를 구비한다. 버퍼(200)의 입력단자는 신호검출기(22)로부터 상위데이터(또는 신호검출기(24)로부터 하위데이터)를 수신한다. 버퍼(200)의 비반전출력단자는 D-플립플롭(202)의 D 입력단자와 AND 게이트(204)의 제1입력단자에 접속되어 있다. 버퍼(200)의 반전입력단자는 AND 게이트(210)의 제1입력단자에 접속되어 있다. D-플립플롭(202)의 비반전출력단자(Q)가 AND 게이트(210)의 제2입력단자, D-플립플롭(206)의 D 입력단자 및 AND 게이트(208)의 제1입력단자에 접속되어 있다. D-플립플롭(202)의 반전출력단자(QN)가 AND 게이트(204)의 제2입력단자에 접속되어 있다. AND 게이트(204)의 출력단자는 OR 게이트(212)의 제1입력단자에 안내되어 있다. AND 게이트(210)의 출력단자는 OR 게이트(212)의 제2입력단자에 안내되어 있다. OR 게이트(212)는 차지펌프회로(40)의 OR 게이트(34)(제1도)에 차지신호(C1또는 C2)를 출력시킨다. D-플립플롭(206)의 반전출력단자(QN)가 AND 게이트(208)의 제2입력단자에 접속되어 있다. AND 게이트(208)의 제2입력단자에 접속되어 있다. OP 플립플롭(206)의 발전출력단자(QN)가 AND 게이트(208)의 제2입력단자에 접속되어 있다. AND 게이트(208)는 디스차지신호(D1또는 D2)를 차지펌프회로(40)의 NOR 게이트(36)(제1도)에 출력시킨다. D-플립플롭(202및 206)의 클럭입력신호 VCO(44)(제1도)에서 재생신호를 수신한다.

위상비교기(230 및 232)는 작동이 유사하다. 따라서, 위생비교기(230)의 작동만을 설명할 것이다. D-플립 플롭(202및 206)에 가해진 재생된 클럭신호는 제12도의 부분(A)에 도시된 것과 같은 파형을 한다. 신호검출기(22)(제1도)로부터 버퍼(200)에 공급된 상위데이터는 제12도의 부분(B))에 도시된 것과 같은 파형을한다. 상위데이터는 버퍼(200)를 통과한 다음 D-플립플롭(202)에 도달한다. 상위데이터는 재생된 클럭신호의 매 스트로브 포인트 마다(즉, 재생된 클럭신호의 상승 또는 양 진행 모서리의 발생의 매 순간 마다)D-플립플롭(202)에 의해 래치된다. 따라서, 비반전출력단자(Q)에 나타나는 D-플립플롭(202)의 출력신호가 제12도의 부분(C)에 도시된 것과 같은 파형을 한다. D-플립플롭(202)의 Q 출력신호(제12도의 부분(C))가 재생클럭신호의 매 스트로브 포인트(즉, 재생클럭신호의 상승 또는 양 진행 모서리의 발생의 매순간 마다) D-플립플롭(206)에 의해 래치된다. 따라서, 비반전출력단자(Q)에 나타나는 D-플립플롭(206)을 출력신호가 제12도의 부분(D)에 도시된 것과 같은 파형을 한다.

상위데이터(제12도의 부분(B))가 버퍼(200)를 통과한 후 AND 게이트(204)에 도달한다. 반전출력단자(QN)에 나타나는 D-플립플롭(202)의 출력신호가 AND 게이트(204)에 가해진다. AND 게이트(204)는 상위데이터 (제12도의 부분(B))와 D-플립플롭(202)의 QN 출력신호간의 AND 연산을 실행함으로서 제12도의 부분(E)에 도시된 것과 같은 파형을 하는 신호를 발생하여 출력시킨다. 버퍼(200)는 상위데이터의 반전을 AND 게이트(210)에 출력시킨다. D-플립플롭(202)(제12도의 부분(C))의 Q 출력신호는 AND 게이트(210)에 가해진다. AND 게이트(210)는 상위데이터의 반전과 D-플립플롭(202)(제12도의 부분(C))의 Q 출력신호간의 AND 연산을 실행함으로써 제12도의 부분(E)에 도시된 것과 같은 파형을 하는 신호를 발생하여 출력시킨다. AND 게이트(204)(제12도의 부분(F))의 출력신호간 OR 게이트(212)에 가해진다. OR 게이트(212)는 AND 게이트(204)(제12도의 부분(E))의 출력신호와 AND 게이트(210)(제12도의 부분(F))의 출력신호간의 OR 연산을 실행한다. OR 게이트(212)의 Q 출력신호는 차지신호(C1)를 구성한다. D-플립플롭(202)(제12도의 부분(C))의 Q 출력신호가 AND 게이트(208)에 가해진다. AND 게이트(208)는 D-플립플롭(202)(제12도의 부분(C))의 Q 출력신호와 D-플립플롭(206)의 QN 출력신호간 AND 연산을 실행함으로써 제12도의 부분(G)에 도시된 파형을 하는 신호를 발생하여 출력시킨다. AND 게이트(208)의 출력신호는 디스차지신호(D1)를 구성한다.

위상비교기(232)는 신호검출기(24)(제1도)로부터 하위데이터를 수신한다. 위상비교기(232)는 위상비교기(230)에 의한 상위데이터를 처리하는 방식으로 재생된 클럭신호에 따라 하위데이터를 처리함으로써 위상비교기(232)는 하위데이터에 따라 차지신호(C2) 및 디스차지신호(D2)를 발생하여 출력시킨다. 디스차지신호와 차지신호가 제12도의 부분(E), (F) 및 (G)에 도시된 것처럼 변하는 경우, 연산증폭기(38A)(제5도)에 가해진 합성차지/디스차지신호가 제12도의 부분(H)에 도시된 것과 같은 파형을 한다.

매 유효펄스의 기간이 재생된 클럭신호의 하나의 스트로브 포인트만을 포함하도록 상위데이터와 하위데이터의 유효펄스가 매우 짧은 상태가 고려되었다. 이러한 상태의 예는 제12도 기간(T1)동안 발생한다. 제12도의 기간(T1)동안, 차지신호(C1)의 유효펄스(CB1)의 리딩 에지(제12도의 부분(E))가 상위데이터의 제1상 승모서리(EB1)(제12도의 부분(E))에 의해 야기된다. 유효차지펄스(CB1)의 트레일링 에지(제12도의 부분(E))가 상위데이터(제12도의 부분(B))의 제1상승모서리(EB1)의 발생 순간을 즉시 추종하는 재생된 클럭신호의 스트로브 포인트(SPB1)(제12도의 부분(A))에 의해 야기된다. 한편, 디스차지신호(D1)(제12도의 부분(G))의 유효펄스(DB1)의 리딩 에지가 재생클럭신호(제12도의 부분(A))의 스트로브 포인트(SPB1)에 의해 야기된다. 유효디스차지펄스(DB1)(제12도의 부분(G))의 트레일링 에지는 재생클럭신호(제12도의 부분(A))의 다음 스트로브 포인트(SPB2)에 의해 야기된다. 차지신호(C1)(제12도의 부분(F))의 다음 유효펄스

(CB2)의 이딩 에지가 상위데이터(제12도의 부분(B))의 제1하강모서리(EB2)의 발생 순간을 즉시 추종하는 재생클럭신호(제12도의 부분(A))의 스트로브 포인트(SPB1)에 의해 야기된다. 유효차지펄스(CB2)(제12도의 부분(F))의 트레일링 에지는 재생된 클럭신호(제12도의 부분(A))의 스트로브 포인트(SPB2)에 의해 야기된다.

이와 유사하게, 차지신호(C2)와 디스차지신호(D2)의 유효펄스가 하위데이터와 재생된 클럭신호에 따라 발생되다

위상비교기(230 및 232)는 차지신호(C1및 C2)를 차지펌프회로(40)의 OR 게이트(34)(제1도)에 출력시킨다. 차지신호(C1및 C2)의 결합은 OR 게이트(34)에 의해 제공된다. 위상비교기(230 및 232)는 디스차지신호(D1 및 D2)를 차지펌프회로(40)의 NOR 게이트(36)(제1도)에 출력시킨다. 디스차지신호(D1및 D2)의 결합의 반전은 NOR 게이트(36)에 의해 제공된다.

차지신호(C1및 C2)의 결합은 OR 게이트(34)로부터 차지펌프회로(40)의 적분기(38)에 공급된다. 디스차지신호(D1및 D2)의 결합의 반전은 NOR 게이트(36)로부터 적분기(38)에 공급된다. 제12도의 기간(T1)동안, 적빈기(38)는 유효차지펄스(CD1및 CD2)(제12도의 부분(E) 및 (F))의 기간의 합에서 유효디스차지펄스(DB1)(제12도의 부분(G))의 기간을 감산하는 역할을 한다. 위상에러 또는 주파수에러가 재생된 정보신호(상위데이터와 하위데이터)와 재생된 클럭신호간에서 발생하는 경우, 유효디스차지펄스(DB1)의 기간과 유효차지펄스(CB1및 CB2)의 기간의 합 사이에 차이가 존재한다. 적분기(38)는 이러한 차이를 검출하고, 검출된 차이를 나타내는 신호를 출력시킨다. 차이를 나타내는 신호가 적분기(38)에서 루우프 필터(42)(제1도)를 경유하여 VCO(44)에 대한 제어신호로 VCO(44)에 공급된다. VCO(44)는 재생된 정보신호와 재생된 클럭신호간의 위에서 언급한 위상에러를 널(null)하기 위해 제어신호에 따라 재생된 클럭신호의 위상 또는주파수를 조절한다. 제12도의 기간(T1)동안, VCO(44)에 의한 재생된 클럭신호의 위상조절은 제12도의 부분(A)에 도시된 것처럼 방향(FB1)으로 스트로브 포인트의 타이밍을 이동시킨다. 따라서, 재생된 클럭신호는 재생된 정보신호와 양호한 동기화된 관계 또는 양호한 타이밍 관계로 유지된다.

상위데이터와 하위데이터는 유효펄스마다의 기간이 재생된 클럭신호의 두 개 이상의 스트로브 포인트를 포함하도록 매우 긴 경우가 고려되었다. 이러한 상태의 예는 제12도의 기간(T2)동안 발생한다. 제12도의 기간(T2)동안, 차지신호(C1)(제12도의 부분(E))의 유효펄스(CB3)의 리딩 에지가 상위데이터(제12도의 부분(B))의 상승모서리(EB3)에 의해 야기된다. 유효차지펄스(CB3)(제12도의 부분(E))의 트레일링 에지는 상위데이터(제12도의 부분(B))의 상승모서리(EB3)의 발생 순간을 즉시 추종하는 재생 클럭신호(제12도의 부분(A))의 스트로브 포인트(SPB3)에 의해 야기된다. 한편, 디스차지신호(D1)(제12도의 부분(G))의 유효펄스(DB2)의 리딩 에지가 재생된 클럭신호(제12도의 부분(A))의 스트로브 포인트(SPB3)에 의해 야기된다. 유효디스차지펄스(DA1)(제12도의 부분(G))의 트레일링 에지는 재생클럭신호(제12도의 부분(A))의 다음 스트로브 포인트(SPB4)에 의해 야기된다. 차지신호(C1)(제12도의 부분(F))의 다음 유효펄스(SB4)의 리딩 에지는 재생클럭신호(제12도의 부분(A))의 스트로브 포인트(SPB4)를 추종하는 상위데이터(제12도의 부분(B))의 하강모서리(EB4)에 의해 야기된다. 유효차지펄스(CB4)(제12도의 부분(F))의 트레일링 에지는 상위데이터(제12도의 부분(B))의 하강모서리(EB4)의 발생 순간을 즉시 추종하는 재생된 클럭신호(제12도의 부분(A))의 스트로브 포안트(SPB5)에 의해 야기된다.

이와 유사하게, 차지신호(C2)와 디스차지신호(D2)의 유효펄스가 하위데이터와 재생클럭신호에 따라 발생한다.

위상비교기(230 및 232)는 차지신호(C1및 C2)를 차지펌프회로(40)의 OR 게이트(34)(제1도)에 출력시킨다. 차지신호(C1및 C2)의 결합은 OR 게이트(34)에 의해 제공된다. 위상비교기(230 및 232)는 디스차지신호(D1 및 D2)를 차지펌프회로(40)의 NOR 게이트(36)(제1도)에 출력시킨다. 디스차지신호(D1및 D2)의 결합의 반전은 NOR 게이트(36)에 의해 제공된다.

차지신호(C1및 C2)의 결합은 OR 게이트(34)로부터 차지펌프회로(40)의 적분기(38)에 공급된다. 디스차지신호(D1및 D2)의 결합의 반전은 NOR 게이트(36)로부터 적분기(38)에 공급된다. 제12도의 기간(T2)동안, 적분기(38)는 유효차지펄스(CB3및 CB4)(제12도의 부분(E) 및 (F))의 기간의 합으로부터 유효디스차지펄스(DB2)(제12도의 부분(G))의 기간을 감산하는 역할을 한다. 재생된 정보신호(상위데이터와 하위데이터)와 재생된 클럭신호 사이에서 위상에러 또는 주파수에러가 발생하는 경우, 유효디스차지펄스(DB2)의 기간과 유효차지펄스(CB3및 CB4)의 기간의 합 사이에 차이가 존재한다. 적분기(38)는 이러한 차이를 검출하고, 검출된 차이를 나타내는 신호를 출력시킨다. 차이를 나타내는 신호가 적분기(38)로부터 루우프 필터(42)를 경유하여 VCO(44)에 대한 제어신호를 VCO(44)에 공급된다. VCO(44)는 재생된 정보신호와 재생된 클럭신호간의 위에서 언급한 위상에러를 널(null)하기 위해 제어신호에 따라 재생된 클럭신호의 위상 또는 주파수를 조절한다. 제12도의 기간(T2)동안, VCO(44)에 의한 재생된 클럭신호의 위상조절은 위에서 언급한 차이를 감소시키는 방향으로 스트로브 포인트의 타이밍을 이동시킨다. 따라서, 재생된 클럭신호가 재생된 정보신호와 양호한 동기화된 관계 및 양호한 타이밍 관계로 유지된다.

### [제8실시예]

본 발명의 제8실시예는 아래에서 설명한 설계변경을 제외하고 제1도의 실시예와 유사하다. 제8실시예는 제1도의 위상비교기(30 및 32)대신 위상비교기(330 및 332)를 포함한다.

위상비교기(330 및 332)는 서로 유사하다. 위상비교기(330 및 332)는 신호검출기(22및 24)(제1도)로부터 상위데이터와 하위데이터를 수신한다.

제13도에 도시되어 있듯이, 위상비교기(230)(또는 위상비교기(332))는 버퍼(300), D-플립플롭(302및 306), AND 게이트(304, 308 및 310) 및 OR 게이트(312)를 구비한다. 버퍼(300)의 입력단자는 신호검출기(22)로부터 상위데이터(또는 신호검출기(24)로부터 하위데이터)를 수신한다. 버퍼(300)의 비반전출력단자는 D-플립플롭(302)의 D 입력단자와 AND 게이트(304)의 제1입력단자에 접속되어 있다. 버퍼(300)의 반전입력 단자는 AND 게이트(310)의 제1입력단자에 접속되어 있다. D-플립플롭(302)의 비반전출력단자(Q)가 AND 게이트(310)의 제2입력단자, D-플립플롭(306)의 D 입력단자에 접속되어 있다. D-플립플롭(302)의 반전출력단자(QN)가 AND 게이트(304)의 제2입력단자 및 AND 게이트(308)의 제1입력단자에 접속되어 있다.

AND 게이트(304)의 출력단자는 OR 게이트(312)의 제1입력단자에 안내되어 있다. AND 게이트(310)의 출력 단자는 OR 게이트(312)의 제2입력단자에 안내되어 있다. OR 게이트(312)는 차지펌프회로(40)의 OR 게이트 (34)(제1도)에 차지신호(C1또는 C2)를 출력시킨다. D-플립플롭(306)의 비반전출력단자(Q)가 AND 게이트 (308)의 제2입력단자에 접속되어 있다. AND 게이트(308)는 디스차지신호(D1또는 D2)를 차지펌프회로(40) 의 NOR 게이트(36)(제1도)에 출력시킨다. D-플립플롭(302및 306)의 클럭입력단자는 VCO(44)(제1도)에서 재생클럭 신호를 수신한다.

위상비교기(330 및 332)는 작동이 유사하다. 따라서, 위생비교기(330)의 작동만을 설명할 것이다. D-플립 플롭(302및 306)에 가해진 재생된 클럭신호는 제14도의 부분(A)에 도시된 것과 같은 파형을 한다. 신호검출기(22)(제1도)로부터 버퍼(300)에 공급된 상위데이터는 제12도의 부분(B))에 도시된 것과 같은 파형을 한다. 상위데이터는 버퍼(300)를 통과한 다음 D-플립플롭(302)에 도달한다. 상위데이터는 재생된 클럭신호의 매 스트로브 포인트 마다(즉, 재생된 클럭신호의 상승 또는 양 진행 모서리의 발생의 매 순간 마다) D-플립플롭(302)에 의해 래치된다. 따라서, 비반전출력단자(Q)에 나타나는 D-플립플롭(302)의 출력신호가 제14도의 부분(C)에 도시된 것과 같은 파형을 한다. D-플립플롭(302)의 Q 출력신호(제14도의 부분(C))가 재생클럭신호의 매 스트로브 포인트(즉, 재생클럭신호의 상승 또는 양 진행 모서리의 발생의 매 순간 마다) D-플립플롭(306)에 의해 래치된다. 따라서, 비반전출력단자(Q)에 나타나는 D-플립플롭(306)을 출력신호가 제14도의 부분(D)에 도시된 것과 같은 파형을 한다.

상위데이터(제14도의 부분(B))가 버퍼(300)를 통과한 후 AND 게이트(304)에 도달한다. 반전출력단자(QN)에 나타나는 D-플립플롭(302)의 출력신호가 AND 게이트(304)에 가해진다. AND 게이트(304)는 상위데이터 (제14도의 부분(B))와 D-플립플롭(302)의 QN 출력신호간의 AND 연산을 실행함으로서 제14도의 부분(E)에 도시된 것과 같은 파형을 하는 신호를 발생하여 출력시킨다. 버퍼(300)는 AND 게이트(310)에 상위데이터의 반전을 출력시킨다. D-플립플롭(302)(제14도의 부분(C))의 Q 출력신호는 AND 게이트(310)에 가해진다. AND 게이트(310)는 상위데이터의 반전과 D-플립플롭(302)의 Q 출력신호(제14도의 부분(C))간의 AND 연산을 실행함으로써 제12도의 부분(E)에 도시된 것과 같은 파형을 하는 신호를 발생하여 출력시킨다. AND 게이트(304)(제14도의 부분(E))의 출력신호가 OR 게이트(312)에 가해진다. AND 게이트(304)(제14도의 부분(E))의 출력신호가 OR 게이트(312)에 가해진다. OR 게이트(312)는 AND 게이트(304)(제14도의 부분(E))의 출력신호와 AND 게이트(310)(제14도의 부분(F))의 출력신호가 OR 게이트(310)(제14도의 부분(E))의 출력신호는 차지신호(C1)를 구성한다. D-플립플롭(302)(제14도의 부분(C))의 Q 출력신호가 AND 게이트(30\*0에 가해진다. AND 게이트(30\*0는 D-플립플롭(302)의 QN 출력신호와 D-플립플롭(306)(제14도의 부분(D))의 Q 출력신호라의 AND 연산을 실행함으로써 제14도의 부분(G)에 도시된 것과 같은 파형을 하는 신호를 발생하여 출력시킨다. AND 게이트(30\*0)의 출력신호는 디스차지신호(D1)를 구성한다.

위상비교기(332)는 신호검출기(24)(제1도)로부터 하위데이터를 수신한다. 위상비교기(332)는 위상비교기(330)에 의한 상위데이터를 처리하는 방식으로 재생된 클럭신호에 따라 하위데이터를 처리함으로써 위상비교기(332)는 하위데이터에 따라 차지신호(C2) 및 디스차지신호(D2)를 발생하여 출력시킨다. 디스차지신호와 차지신호가 제14도의 부분(E),(F) 및 (G)에 도시된 것처럼 변하는 경우, 연산증폭기(38A)(제5도)에 가해진 합성차지/디스차지신호가 제14도의 부분(H)에 도시된 것과 같은 파형을 한다.

매 유효펄스의 기간이 재생된 클럭신호의 하나의 스트로브 포인트만을 포함하도록 상위데이터와 하위데이터의 유효펄스가 매우 짧은 상태가 고려되었다. 이러한 상태의 예는 제14도 기간(T1)동안 발생한 제14도의 기간(T1)동안, 차지신호(C1)의 유효펄스(CC1)의 리팅 에지(제12도의 부분(E))가 상위데이터의 제1상승모서리(EC1)(제14도의 부분(E))에 의해 야기된다. 유효차지펄스(CC1)의 트레일링 에지(제14도의 부분(E))가 상위데이터(제14도의 부분(B))의 제1상승모서리(EC1)의 발생 순간을 즉시 추종하는 재생된 클럭신호의 스트로브 포인트(SPC1)(제12도의 부분(A))에 의해 야기된다. 차지신호(C1)(제14도의 부분(F))의 다음 유효펄스(CC2)의 리팅 에지는 재생클럭신호(제14도의 부분(A))의 스트로브 포인트(SPC1)를 추종하는 상위데이터의 제1하강모서리(EC2)(제14도의 부분(B))에 의해 야기된다. 유효차지펄스(CC2)의 트레일링 에지는 상위데이터(제14도의 부분(B))의 하강모서리(EC2)의 발생 순간을 즉시 추종하는 재생클럭신호(제14도의 부분(A))의 스트로브 포인트(SPC2)에 의해 야기된다. 한편, 디스차지신호(D1)(제14도의 부분(G))의 유효펄스(DC1)의 리팅 에지가 재생클럭신호(제14도의 부분(A))의 스트로브 포인트(SPC1)에 의해 야기된다. 유효디스차지펄스(DC1)(제14도의 부분(G))의 트레일링 에지는 재생클럭신호(제14도의 부분(A))의 다음 스트로브 포인트(SPC2)에 의해 야기된다.

이와 유사하게, 차지신호(C2)와 디스차지신호(D2)의 유효펄스가 하위데이터와 재생된 클럭신호에 따라 발생된다.

위상비교기(330 및 332)는 차지신호(C1및 C2)를 차지펌프회로(40)의 OR 게이트(34)(제1도)에 출력시킨다. 차지신호(C1및 C2)의 결합은 OR 게이트(34)에 의해 제공된다. 위상비교기(330 및 332)는 디스차지신호(D1 및 D2)를 차지펌프회로(40)의 NOR 게이트(36)(제1도)에 출력시킨다. 디스차지신호(D1및 D2)의 결합의 반전이 NOR 게이트(36)에 의해 제공된다.

차지신호(C1및 C2)의 결합은 OR 게이트(34)로부터 차지펌프회로(40)의 적분기(38)에 공급된다. 디스차지신호(D1및 D2)의 결합의 반전은 NOR 게이트(36)로부터 적분기(38)에 공급된다. 제14도의 기간(T1)동안, 적분기(38)는 유효차지펄스(CC1및 CC2)(제14도의 부분(E) 및 (F))의 기간의 합에서 유효디스차지펄스(DC1)(제14도의 부분(G))의 기간을 감산하는 역할을 한다. 위상에러 또는 주파수에러가 재생된 정보신호(상위데이터와 하위데이터)와 재생된 클럭신호간에서 발생하는 경우, 유효디스차지펄스(DC1)의 기간과 유효차지펄스(CC1및 CC2)의 기간의 합 사이에 차이가 존재한다. 적분기(38)는 이러한 차이를 검출하고, 검출된 차이를 나타내는 신호를 출력시킨다. 신호를 나타내는 신호가 적분기(38)에서 루우프 필터(42)(제1도)를 경유하여 VCO(44)에 대한 제어신호로 VCO(44)에 공급된다. VCO(44)는 재생된 정보신호와 재생된 클럭신호간의 위에서 언급한 위상에러를 널(null)하기 위해 제어신호에 따라 재생된 클럭신호의 위상 또는 주파수를 조절한다. 제14도의 기간(T1)동안, VCO(44)에 의한 재생된 클럭신호의 위상조절은 위에서 언급한 차이를 감소시키는 방향으로 스트로브 포인트의 타이밍을 이동시킨다. 따라서, 재생된 클럭신호는 재생된 정보신호와 양호한 동기화된 관계 또는 양호한 타이밍 관계로 유지된다.

상위데이터와 하위데이터는 유효펄스마다의 기간이 재생된 클럭신호의 두 개 이상의 스트로브 포인트를 포함하도록 매우 긴 경우가 고려되었다. 이러한 상태의 예는 제12도의 기간(T2)동안 발생한다. 제14도의 기간(T2)동안, 차지신호(C1)(제14도의 부분(E))의 유효펄스(CC3)의 리딩 에지가 상위데이터(제14도의 부분(B))의 상승모서리(EC3)에 의해 야기된다. 유효차지펄스(CC3)(제14도의 부분(E))의 트레일링 에지는 상위데이터(제14도의 부분(B))의 상승모서리(EC3)의 발생 순간을 즉시 추종하는 재생 클럭신호(제14도의 부분(A))의 스트로브 포인트(SPC4)에 의해 야기된다. 차지신호(C1)(제14도의 부분(F))의 다음 유효펄스(CC4)의 리딩 에지가 스트로브 포인트(SPC4)를 추종하는 상위데이터(제14도의 부분(B))의 하강모서리(EC4)에 의해 야기된다. 유효차지펄스(CC4)(제14도의 부분(F))의 트레일링 에지는 상위데이터(제14도의부분(B))의 하강모서리(EC4)의 발생 순간을 즉시 추종하는 상위데이터(제14도의부분(B))의 스트로브 포인트(SPC5)에 의해 야기된다. 한편, 디스차지신호(D1)(제14도의부분(G))의 유효펄스(DC2)의 리딩 에지가 재생된 클럭신호(제14도의부분(A))의 스트로브 포인트(SPB5)에 의해 야기된다. 유효디스차지펄스(DC2)(제14도의부분(G))의 트레일링 에지는 재생클럭신호(제14도의부분(A))의 다음 스트로브 포인트(SPB6)에 의해 야기된다.

이와 유사하게, 차지신호(C2)와 디스차지신호(D2)의 유효펄스가 하위데이터와 재생클럭신호에 따라 발생한다.

위상비교기(330 및 332)는 차지신호(C1및 C2)를 차지펌프회로(40)의 OR 게이트(34)(제1도)에 출력시킨다. 차지신호(C1및 C2)의 결합은 OR 게이트(34)에 의해 제공된다. 위상비교기(330 및 332)는 디스차지신호(D1 및 D2)를 차지펌프회로(40)의 NOR 게이트(36)(제1도)에 출력시킨다. 디스차지신호(D1및 D2)의 결합의 반전은 NOR 게이트(36)에 의해 제공된다.

차지신호(C1및 C2)의 결합은 OR 게이트(34)로부터 차지펌프회로(40)의 적분기(38)에 공급된다. 디스차지신호(D1및 D2)의 결합의 반전은 NOR 게이트(36)로부터 적분기(38)에 공급된다. 제14도의 기간(T2)동안, 적분기(38)는 유효차지펄스(CC3및 CC4)(제14도의 부분(E) 및 (F))의 기간의 합으로부터 유효디스차지펄스(DC2)(제14도의 부분(G))의 기간을 감산하는 역할을 한다. 재생된 정보신호(상위데이터와 하위데이터)와 재생된 클럭신호 사이에서 위상에러 또는 주파수에러가 발생하는 경우, 유효디스차지펄스(DC2)의 기간과 유효차지펄스(CC3및 CC4)의 기간의 합 사이에 차이가 존재한다. 적분기(38)는 이러한 차이를 검출하고, 검출된 차이를 나타내는 신호를 출력시킨다. 차이를 나타내는 신호가 적분기(38)로부터 루우프 필터(42)를 경유하여 VCO(44)에 대한 제어신호 VCO(44)에 공급된다. VCO(44)는 재생된 정보신호와 재생된 클럭신호 위에서 언급한 위상에러를 널(null)하기 위해 제어신호에 따라 재생 클럭신호의 위상 또는 주파수를 조절한다. 제14도의 기간(T2)동안, VCO(44)에 의한 재생된 클럭신호의 위상조절은 위에서 언급한 차이를 감소시키는 방향으로 스트로브 포인트의 타이밍을 이동시킨다. 따라서, 재생된 클럭신호가 재생된 정보신호와 양호한 동기화된 관계 및 양호한 타이밍 관계로 유지된다.

#### (57) 청구의 범위

#### 청구항 1

다중레벨신호에 따라 다중레벨신호가 소정의 레벨인지 여부를 나타내는 검출신호를 발생시키는 제1수단을 구비하고; 제1수단에 접속되어서 제1수단에 의해 발생된 검출신호와 클럭신호에 따라 제1제어신호를 발생하는 제2수단을 구비하고, 상기 제1제어신호는 검출신호의 펄스의 리딩 에지(leading edge)와 검출신호의 펄스의 리딩 에지(leading edge)와 검출신호의 펄스의 리딩 에지를 즉시 추종하는 클럭신호의 스트로브 포인트(strobe point)간의 시간 간격을 나타내며; 또한, 제1수단에 접속되어서 제1수단에 의해 발생된 검출신호와 클럭신호에 응답하여 제2제어신호를 발생시키는 제3수단을 구비하고, 상기 제2제어 신호는 클럭신호의 스트로브 포인트와 검출신호의 펄스의 트레일링 에지간의 시간 간격을 나타내며; 또한, 제2수단과 제3수단에 접속되어서 제2수단에 의해 발생한 제1제어신호와 제3수단에 의해 발생한 제2제어신호에 응답하여 위상에러신호를 발생시키는 제4수단을 구비하고, 상기 위상에러신호는 제1수단에 의해 발생한 검출신호의 위상과 클럭신호의 위상간의 차를 나타내는 것을 특징으로 하는 위상비교회로.

### 청구항 2

다중벨신호가 소정의 레벨에 있는지 여부를 나타내는 검출신호를 다중레벨신호에 따라 발생시키는 제1수단을 구비하고; 제1수단에 접속되어서 제1수단에 의해 발생한 검출신호와 클럭신호에 따라 제1제어신호를 발생하는 제2수단을 구비하고, 상기 제1수단은 검출신호의 펼스의 리딩 에지와 검출신호의 펼스의 리딩에지를 즉시 추종하는 클럭신호의 제1스트로브 포인트간의 시간 간격을 나타내며; 또한, 클럭신호에 따라제2제어신호를 발생시키는 제3수단을 구비하고, 상기 제2제어신호는 클럭신호의 제1스트로브 포인트와 클럭신호의 제1스트로브 포인트와 클럭신호의 제1스트로브 포인트를 즉시 추종하는 클럭신호의 제2스트로브 포인트간의 시간 간격을 나타내며; 또한, 클럭신호에 응답하여 제3제어신호를 발생시키는 제4수단을 구비하고, 상기 제3제어신호는 클럭신호의 주기의 반에 해당하고, 클럭신호의 제2스트로브 포인트로부터 시작하는 시간 간격을 나타내며; 제2수단, 제3수단 및 제4수단에 접속되어서 제2수단에 의해 발생한 제1제어신호, 제3수단에 의해발생한 제2제어신호 및 제4수단에 의해발생한 제3제어신호에 응답하여 위상에러신호를 발생시키는 제5수단을 구비하고, 상기 위상에러신호는 제1수단에 의해발생한 검출신호의 위상과 클럭신호의 위상간의 차를 나타내는 것을 특징으로 하는 위상비교회로.

### 청구항 3

다중레벨신호에 따라 다중레벨신호가 소정의 레벨인지 여부를 나타내는 검출신호를 발생시키는 제1수단을 구비하고; 제1수단에 접속되어서 제1수단에 의해 발생한 검출신호의 클럭신호에 따라 제1제어신호를 발생시키는 제2수단을 구비하고, 상기 제1제어 신호는 검출신호의 펄스의 리딩 에지와 검출신호의 펄스의 리딩 에지와 검출신호의 펄스의 리딩 에지를 즉시 추종하는 클럭신호의 제1스트로브 포인트간의 시간점을 나타내며; 또한, 제1수단에 접속되어서 감출신호의 펄스의 트레일링 에지가 클럭신호의 제1스트로브 포인트를 즉시 추종하는 클럭신호의 제2스트로브 포인트를 선행하는 경우, 제1수단에 의해 발생한 검출신호와 클럭신호에 따라 제2제어신호를 발생하고, 클럭신호의 제2스트로브 포인트가 검출신호의 펄스의 트레일링 에지를 선행하는 경우, 제1수단

에 의해 발생한 검출신호와 클럭신호에 따라 제3제어신호와 제4제어신호를 발생시키는 제3수단을 구비하고, 상기 제2제어신호는 클럭신호의 제1스트로브 포인트와 검출신호의 펄스의 트레일링 에지간의 시간 간격을 나타내며, 제3제어신호는 클럭신호와 제1스트로브 포인트와 클럭신호의 제2스트로브 포인트라의 제2스트로브 포인트라의 제2스트로브 포인트라이 제3제어신호는 클럭신호의 제2스트로브 포인트로부터 시작하는 클럭신호의 주기의 반에 해당하는 시간 간격을 나타내며; 또한, 제2수단에 의해 발생한 제1제어신호 및 제3수단에 의해 발생한 제2제어신호 또는 제2수단에 의해 발생한 제1제어신호 및 제3수단에 의해 발생한 제3 및 제4제어신호에 따라 위상에러신호를 발생시키는 제4수단을 구비하고, 상기 위상에러신호는 제1수단에 의해 발생한 검출신호의 위상과 클럭신호의 위상간의 차를 나타내는 것을 특징으로 하는 위상비교회로.

#### 청구항 4

a) 다중레벨신호에 응답하여 다중레벨신호가 상기한 소정의 레벨에 있는지 여부를 나타내는 검출신호를 발생시키는 다수의 신호검출기와, b) 신호검출기를 추종하고 신호검출기에 의해 발생한 검출신호를 처리 하는 다수의 위상비교기를 구비함에 있어서, 각각의 위상비교기는, b1) 관련된 검출신호에 따라 제1제어 신호를 발생시키는 제1수단을 구비하고, 상기 제1제어신호는 검출신호의 펄스의 리딩 에지와 검출신호의 펄스의 리딩 에지를 즉시 추종하는 클럭신호의 스트로브 포인트간의 시간 간격을 나타내며; b2)관력된 검 출신호에 따라 제2제어신호를 발생시키는 제2수단을 구비하고, 상기 제2제어신호는 클럭신호의 스트로브 포인트와 검출신호의 펄스의 트레일링 에지간의 시간 간격을 나타내며; b3) 제1 및 제2수단에 접속되어서 제1수단에 의해 발생한 제1제어신호와 제2수단에 의해 발생한 제2제어신호에 응답하여 위상에러신호를 발 생하는 제3수단을 구비하고, 상기 위상에러신호는 제1수단에 의해 발생한 검출신호의 위상과 클럭신호의 위상간의 차를 나타내는 것을 특징으로 하는 위상비교회로.

#### 청구항 5

제1항에 있어서, 제4수단이 차지펌프회로를 구비하는 것을 특징으로 하는 위상비교회로.

#### 청구항 6

클럭신호를 발생시키는 제1수단을 구비하고; 제1수단에 접속되어서 입력신호와 제1수단에 의해 발생된 클럭신호에 응답하여 제1제어신호를 발생시키는 제2수단을 구비하고, 상기 제1제어신호는 입력신호의 펄스의 리딩 에지와 입력신호의 펄스의 리딩 에지를 즉시 추종하는 클럭신호의 스트로브 포인트간의 시간 간격을 나타내며; 또한, 제1수단에 접속되어서 제1수단에 의해 발생된 클럭신호와 입력신호에 따라 제2제어신호를 발생시킨 제3수단을 구비하고, 상기 제2제어신호는 클럭신호의 스트로브 포인트와 입력신호의 펄스의 트레일링 에지간의 시간 간격을 나타내며; 또한, 제2수단과 제3수단에 접속되어서 제2수단에 의해 발생한 제1제어신호와 제3수단에 의해 발생한 제2제어신호에 따라 위상에러신호를 발생시키는 제4수단을 구비하고, 상기 위상에러신호는 제1수단에 의해 발생한 클럭신호의 위상과 입력신호의 위상간의 차이를나타내며; 또한, 제4수단에 의해 발생된 위상에러신호에 따라 클럭신호의 위상을 제어하는 제5수단을 구비하는 것을 특징으로 하는 PLL 회로.

#### 청구항 7

다중레벨신호에 따라 이 다중레벨신호가 소정의 레벨인지 여부를 나타내는 검출신호를 발생시키는 제1수 단을 구비하고; 제1수단에 접속되어서 제1수단에 의해 발생한 검출신호와 클럭신호에 따라 제1제어신호를 발생시키는 제2수단을 구비하고, 상기 제1제어신호는 검출신호의 펄스의 리딩 에지와 검출신호의 펄스의 리딩 에지를 즉시 추종하는 클럭신호의 제1스트로브 포인트간의 시간 간격을 나타내며; 또한, 제1수단에 접속되어서 검출신호의 펄스의 트레일링 에지가 클럭신호의 제1스트로브 포인트를 즉시 추종하는 클럭신 호의 제2스트로브 포인트를 선행하는 경우, 제1수단에 의해 발생한 검출신호와 클럭신호에 따라 제2제어 신호를 발생시키고, 클럭신호의 제2스트로브 포인트가 검출신호의 펄스의 트레일링 에지를 선행하는 경우. 제1수단에 의해 발생한 검출신호와 클럭신호에 따라 제3제어신호 및 제4제어신호를 발생시키는 제3 수단을 구비하고, 상기 제2제어신호는 클럭신호의 제1스트로브 포인트와 검출신호의 펄스의 트레일링 에 지간의 시간 간격을 나타내며, 제3제어신호는 클럭신호의 제1스트로브 포인트와 클럭신호의 제2스트로브 포인트간의 시간 간격을 나타내고, 제4제어신호는 검출신호의 펄스의 트레일링 에지와 검출신호의 펄스의 트레일링 에지를 즉시 추종하는 클럭신호의 제3스트로브 포인트간의 시간 간격을 나타내며; 또한, 제2수 단과 제3수단에 접속되어서 제2수단에 의해 발생한 제1제어신호와, (1) 제3수단에 의해 발생한 제2제어신 호와, (2) 제3수단에 의해 발생한 제3제어신호와 제4제어신호의 결합에 따라 위상에러신호를 발생시키는 제4수단을 구비하고, 상기 위상에러신호는 제1수단에 의해 발생한 검출신호의 위상과 클럭신호의 위상간 의 차이를 나타내는 것을 특징으로 하는 위상비교회로.

#### 청구항 8

다중레벨신호에 따라 다중레벨신호가 소정의 레벨인지 여부를 나타내는 검출신호를 발생시키는 제1수단을 구비하고; 제1수단에 접속되어서 제1수단에 의해 발생한 검출신호와 클럭신호에 따라 제1제어신호를 발생시키는 제2수단을 구비하고, 상기 제1제어신호는 검출신호의 펄스의 리딩 에지와 검출신호의 펄스의 리딩에지를 즉시 추종하는 클럭신호의 제1스트로브 포인트간의 시간 간격을 나타내며; 또한, 제1수단에 접속되어서 제1수단에 의해 발생한 검출신호와 클럭신호에 따라 제2제어신호를 발생시키는 제3수단을 구비하고, 상기 제2제어신호는 검출신호의 펄스의 트레일링에지와 검출신호의 펄스의 트레일링에지를 즉시 추정하는 클럭신호의 제2스트로브 포인트간의 시간 간격을 나타내며; 또한, 클럭신호에 따라 제3제어신호를 발생시키는 제4수단을 구비하고, 상기 제3제어신호는 클럭신호의 주기와 같은 시간 간격을 나타내며; 또한, 제2수단, 제3수단 및 제4수단에 접속되어서 제2수단에 의해 발생한 제1제어신호, 제3수단에 의해 발생한 제2제어신호 및 제4수단에 의해 발생한 제3제어 신호에 따라 위상에러신호를 발생시키는 제5수단을 구비하고, 상기 위상에러신호는 제1수단에 의해 발생한 검출신호의 위상과 클럭신호의 위상간의 차를 나타내는 것을 특징으로 하는 위상비교회로.

### 청구항 9

제2항에 있어서, 제1수단이 다중레벨신호에 따라 상이한 검출신호를 발생시키는 다수의 신호검출기를 포함하되, 상기 검출신호는 다중레벨신호가 상이한 소정의 레벨인지 여부를 나타내고, 제2수단은 신호검출기에 의해 발생한 검출 신호에 응답하는 것을 특징으로 하는 위상비교회로.

#### 청구항 10

제3항에 있어서, 제1수단이 다중레벨신호에 따라 상이한 검출신호를 발생시키는 다수의 신호검출기를 포함하되, 상기 검출신호는 다중레벨신호가 상이한 소정의 레벨인지 여부를 나타내고, 제2수단은 신호검출기에 의해 발생한 검출신호에 응답하는 것을 특징으로 하는 위상비교회로.

#### 청구항 11

제7항에 있어서, 제1수단이 다중레벨신호에 따라 상이한 검출신호를 발생시키는 다수의 신호검출기를 포함하되, 상기 검출신호는 다중레벨신호가 상이한 소정의 레벨인지 여부를 나타내고, 제2수단 및 제3수단은 신호검출기에 의해 발생한 검출신호에 응답하는 것을 특징으로 하는 위상비교회로.

#### 청구항 12

제8항에 있어서, 제1수단이 다중레벨신호에 따라 상이한 검출신호를 발생시키는 다수의 신호검출기를 포함하되, 상기 검출신호는 다중레벨신호가 상이한 소정의 레벨인지 여부를 나타내고, 제2수단 및 제3수단은 신호검출기에 의해 발생한 검출신호에 응답하는 것을 특징으로 하는 위상비교회로.

#### 청구항 13

제2항에 있어서, 제5수단이 차지펌프회로를 포함하는 것을 특징으로 하는 위상비교회로.

#### 청구항 14

제3항에 있어서, 제4수단이 차지펌프회로를 포함하는 것을 특징으로 하는 위상비교회로.

#### 청구항 15

제7항에 있어서, 제4수단이 차지펌프회로를 포함하는 것을 특징으로 하는 위상비교회로.

### 청구항 16

제8항에 있어서, 제5수단이 차지펌프회로를 포함하는 것을 특징으로 하는 위상비교회로.

### 청구항 17

제2항에 있어서, 위상비교회로는 PLL 회로를 포함하는 것을 특징으로 하는 위상비교회로.

#### 청구항 18

제3항에 있어서, 위상비교회로는 PLL 회로를 포함하는 것을 특징으로 하는 위상비교회로.

### 청구항 19

제7항에 있어서, 위상비교회로는 PLL 회로를 포함하는 것을 특징으로 하는 위상비교회로.

#### 청구항 20

제8항에 있어서, 위상비교회로는 PLL 회로를 포함하는 것을 특징으로 하는 위상비교회로.

### 도면

## 도면3

## 도면4

## 도면7

## 도면10

## 도면13