(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6889855号

(P6889855)

(45) 発行日 令和3年6月18日(2021.6.18)

(24) 登録日 令和3年5月26日(2021.5.26)

|                   |           |

|-------------------|-----------|

| (51) Int.Cl.      | F 1       |

| <b>H05K 3/42</b>  | (2006.01) |

| <b>H01L 23/32</b> | (2006.01) |

| <b>H05K 1/03</b>  | (2006.01) |

| <b>H05K 3/38</b>  | (2006.01) |

| <b>H05K 1/11</b>  | (2006.01) |

| HO5K              | 3/42      |

| HO1L              | 23/32     |

| HO5K              | 1/03      |

| HO5K              | 3/38      |

| HO5K              | 1/11      |

| HO5K              | 3/42      |

| HO1L              | 23/32     |

| HO5K              | 1/03      |

| HO5K              | 3/38      |

| HO5K              | 1/11      |

請求項の数 13 (全 19 頁) 最終頁に続く

(21) 出願番号 特願2017-70285 (P2017-70285)

(22) 出願日 平成29年3月31日 (2017.3.31)

(65) 公開番号 特開2018-174190 (P2018-174190A)

(43) 公開日 平成30年11月8日 (2018.11.8)

審査請求日 令和2年1月30日 (2020.1.30)

(73) 特許権者 000002897

大日本印刷株式会社

東京都新宿区市谷加賀町一丁目1番1号

(74) 代理人 100091982

弁理士 永井 浩之

(74) 代理人 100091487

弁理士 中村 行孝

(74) 代理人 100082991

弁理士 佐藤 泰和

(74) 代理人 100105153

弁理士 朝倉 悟

(74) 代理人 100127465

弁理士 堀田 幸裕

(74) 代理人 100120385

弁理士 鈴木 健之

最終頁に続く

(54) 【発明の名称】貫通電極基板およびその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

第1表面と、前記第1表面の反対側の第2表面とを有し、前記第1表面から前記第2表面まで貫通する貫通孔が設けられた透明基板と、

前記貫通孔の側壁上に位置する第1密着層と、

前記第1表面上および前記第2表面上の少なくとも一方に少なくとも部分的に位置する第2密着層と、

前記第1密着層上に位置する貫通電極と、

前記第2密着層上に位置する導電層と、を備え、

前記第1密着層および前記第2密着層は、15nm以上200nm以下の厚みを有する、貫通電極基板。

10

## 【請求項 2】

前記第1密着層を介した前記透明基板と前記貫通電極との密着性は、前記透明基板と前記貫通電極との直接的な密着性より高く、

前記第2密着層を介した前記透明基板と前記導電層との密着性は、前記透明基板と前記導電層との直接的な密着性より高い、請求項1に記載の貫通電極基板。

## 【請求項 3】

前記第1密着層および前記第2密着層は、有機物を含有する、請求項1または2に記載の貫通電極基板。

## 【請求項 4】

20

前記貫通孔は、前記第1表面に沿った面方向の寸法に対する前記第1表面に交差する厚み方向の寸法の比であるアスペクト比が、3以上3以下である、請求項1乃至3のいずれか一項に記載の貫通電極基板。

**【請求項5】**

前記導電層は、前記第1表面に沿った面方向に間隔を空けて位置する複数の配線部を有し、

前記第2密着層は、前記導電層の前記複数の配線部のそれぞれに対応するように前記第1表面上および前記第2表面上の少なくとも一方に部分的に位置する、請求項1乃至4のいずれか一項に記載の貫通電極基板。

**【請求項6】**

前記導電層は、前記貫通孔の周縁部上において前記貫通電極に連続するパッド部を更に有し、

前記貫通電極と前記パッド部との境界部において、前記パッド部に覆われた前記第2密着層は、前記第1密着層に連続している、請求項5に記載の貫通電極基板。

**【請求項7】**

前記第1密着層と前記貫通電極との間および前記第2密着層と前記導電層との間に触媒が存在する、請求項1乃至6のいずれか一項に記載の貫通電極基板。

**【請求項8】**

前記導電層は、前記第2密着層上に位置する第1導電層と、前記第1導電層上に位置する第2導電層と、を有する、請求項1乃至7のいずれか一項に記載の貫通電極基板。

10

**【請求項9】**

前記貫通電極は、前記第1密着層上に位置し、前記第1導電層と同一の成分を含有する第3導電層と、前記第3導電層上に位置し、前記第2導電層と同一の成分を含有する第4導電層と、を有する、請求項8に記載の貫通電極基板。

**【請求項10】**

前記第1導電層と前記第2導電層とは、同一の成分を含有する、請求項8または9に記載の貫通電極基板。

20

**【請求項11】**

前記透明基板は、ガラスを含有する、請求項1乃至10のいずれか一項に記載の貫通電極基板。

30

**【請求項12】**

第1表面と、前記第1表面の反対側の第2表面とを有する透明基板を準備する工程と、前記透明基板に、前記第1表面から前記第2表面まで貫通する貫通孔を形成する工程と、

前記貫通孔の側壁上に第1密着層を形成する工程と、

前記第1表面上および前記第2表面上の少なくとも一方に、少なくとも部分的に第2密着層を形成する工程と、

前記第1密着層上に貫通電極を形成する工程と、

前記第2密着層上に導電層を形成する工程と、を備え、

前記第1密着層および前記第2密着層は、15nm以上200nm以下の厚みを有するように形成する、貫通電極基板の製造方法。

40

**【請求項13】**

前記貫通電極を形成する工程は、前記第1密着層上に触媒を付着させる工程と、前記触媒が付着された前記第1密着層上に無電解めっきを行う工程と、を有し、

前記導電層を形成する工程は、前記第2密着層上に触媒を付着させる工程と、前記触媒が付着された前記第2密着層上に無電解めっきを行う工程と、を有する、請求項12に記載の貫通電極基板の製造方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

50

本開示は、貫通電極基板およびその製造方法に関する。

【背景技術】

【0002】

従来から、貫通孔が設けられた透明基板と、貫通孔の内部に位置する貫通電極とを備えた貫通電極基板に関して、種々の技術が提案されている。例えば、特許文献1には、透明基板と貫通電極との密着性を高めるために、貫通孔の側壁に密着層を介して貫通電極を形成したインターポーラが開示されている。

【先行技術文献】

【特許文献】

【0003】

10

【特許文献1】特開2017-5081号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、特許文献1に記載の技術では、透明基板と貫通電極との密着性を高めることはできても、透明基板と、透明基板の表面上に位置する配線との密着性を高めることはできなかった。このため、特許文献1には、透明基板からの貫通電極と配線との剥離を同時に抑制することが困難であるといった問題があった。

【0005】

20

本開示は、以上の点を考慮してなされたものであり、透明基板からの貫通電極と配線との剥離を同時に抑制することができる貫通電極基板およびその製造方法を提供することを目的とする。

【課題を解決するための手段】

【0006】

上記の課題を解決するために、本開示の一態様では、

第1表面と、前記第1表面の反対側の第2表面とを有し、前記第1表面から前記第2表面まで貫通する貫通孔が設けられた透明基板と、

前記貫通孔の側壁上に位置する第1密着層と、

前記第1表面上および前記第2表面上の少なくとも一方に少なくとも部分的に位置する第2密着層と、

30

前記第1密着層上に位置する貫通電極と、

前記第2密着層上に位置する導電層と、を備える、貫通電極基板が提供される。

【0007】

前記第1密着層を介した前記透明基板と前記貫通電極との密着性は、前記透明基板と前記貫通電極との直接的な密着性より高く、

前記第2密着層を介した前記透明基板と前記導電層との密着性は、前記透明基板と前記導電層との直接的な密着性より高くてよい。

【0008】

前記第1密着層および前記第2密着層は、有機物を含有してもよい。

【0009】

40

前記第1密着層および前記第2密着層は、15nm以上200nm以下の厚みを有してもよい。

【0010】

前記貫通孔は、前記第1表面に沿った面方向の寸法に対する前記第1表面に交差する厚み方向の寸法の比であるアスペクト比が、3以上33以下であってもよい。

【0011】

前記導電層は、前記第1表面に沿った面方向に間隔を空けて位置する複数の配線部を有し、

前記第2密着層は、前記導電層の前記複数の配線部のそれぞれに対応するように前記第1表面上および前記第2表面上の少なくとも一方に部分的に位置してもよい。

50

## 【0012】

前記導電層は、前記貫通孔の周縁部上において前記貫通電極に連続するパッド部を更に有し、

前記貫通電極と前記パッド部との境界部において、前記パッド部に覆われた前記第2密着層は、前記第1密着層に連続していてもよい。

## 【0013】

前記第1密着層と前記貫通電極との間および前記第2密着層と前記導電層との間に触媒が存在してもよい。

## 【0014】

前記導電層は、前記第2密着層上に位置する第1導電層と、前記第1導電層上に位置する第2導電層と、を有してもよい。 10

## 【0015】

前記貫通電極は、前記第1密着層上に位置し、前記第1導電層と同一の成分を含有する第3導電層と、前記第3導電層上に位置し、前記第2導電層と同一の成分を含有する第4導電層と、を有してもよい。

## 【0016】

前記第1導電層と前記第2導電層とは、同一の成分を含有してもよい。

## 【0017】

前記透明基板は、ガラスを含有してもよい。

## 【0018】

本開示の他の一態様では、

第1表面と、前記第1表面の反対側の第2表面とを有する透明基板を準備する工程と、前記透明基板に、前記第1表面から前記第2表面まで貫通する貫通孔を形成する工程と、

前記貫通孔の側壁上に第1密着層を形成する工程と、

前記第1表面上および前記第2表面上の少なくとも一方に、少なくとも部分的に第2密着層を形成する工程と、

前記第1密着層上に貫通電極を形成する工程と、

前記第2密着層上に導電層を形成する工程と、を備える、貫通電極基板の製造方法が提供される。 30

## 【0019】

前記貫通電極を形成する工程は、前記第1密着層上に触媒を付着させる工程と、前記触媒が付着された前記第1密着層上に無電解めっきを行う工程と、を有し、

前記導電層を形成する工程は、前記第2密着層上に触媒を付着させる工程と、前記触媒が付着された前記第2密着層上に無電解めっきを行う工程と、を有してもよい。

## 【発明の効果】

## 【0020】

本開示によれば、透明基板からの貫通電極と配線との剥離を同時に抑制することができる。

## 【図面の簡単な説明】

## 【0021】

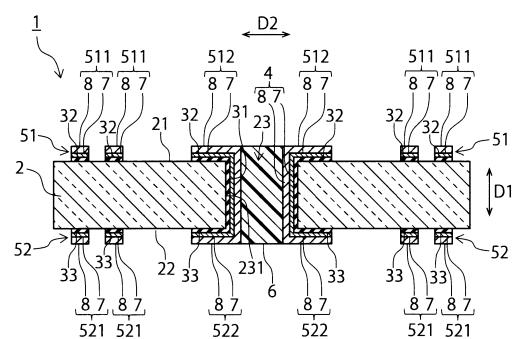

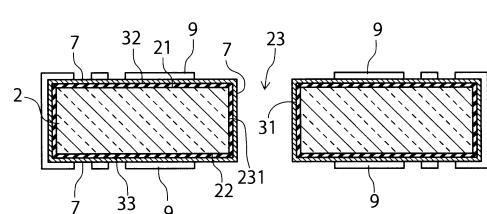

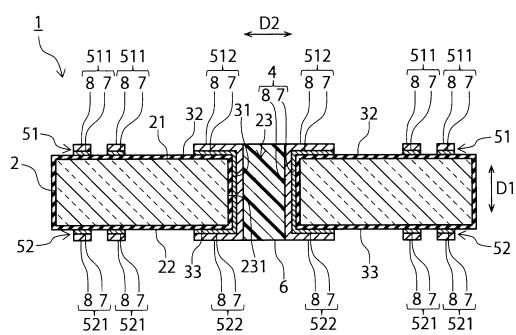

【図1】本実施形態による貫通電極基板を示す断面図である。

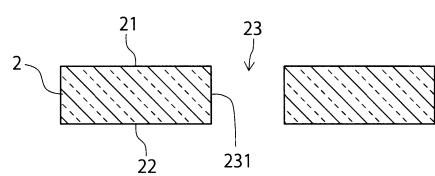

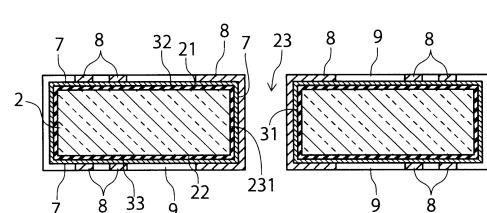

【図2】本実施形態による貫通電極基板の製造方法を示す断面図である。

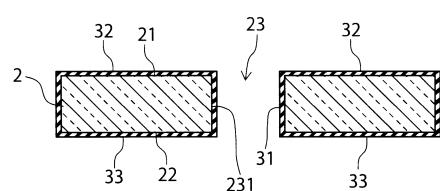

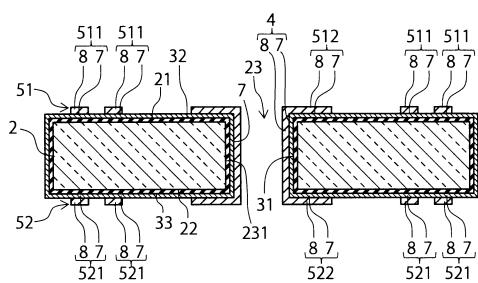

【図3】図2に続く本実施形態による貫通電極基板の製造方法を示す断面図である。

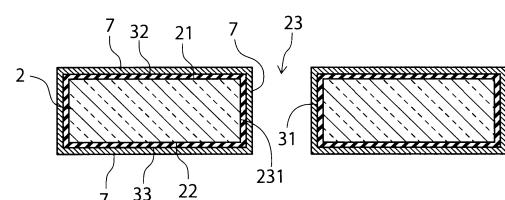

【図4】図3に続く本実施形態による貫通電極基板の製造方法を示す断面図である。

【図5】図4に続く本実施形態による貫通電極基板の製造方法を示す断面図である。

【図6】図5に続く本実施形態による貫通電極基板の製造方法を示す断面図である。

【図7】図6に続く本実施形態による貫通電極基板の製造方法を示す断面図である。

【図8】図7に続く本実施形態による貫通電極基板の製造方法を示す断面図である。

【図9】図8に続く本実施形態による貫通電極基板の製造方法を示す断面図である。 40

50

【図10】図10(a)は、本実施形態による貫通電極基板において、透明基板上へのシード層の形成状態を模式的に示す平面図であり、図10(b)は、第1の比較例による貫通電極基板において、透明基板上へのシード層の形成状態を模式的に示す平面図であり、図10(c)は、第2の比較例による貫通電極基板において、透明基板上へのシード層の形成状態を模式的に示す平面図である。

【図11】図11(a)は、本実施形態の第1の変形例による貫通電極基板として、貫通孔の一変形例を示す断面図であり、図11(b)は、図11(a)と異なる貫通孔の変形例を示す断面図であり、図11(c)は、図11(a)および図11(b)と異なる貫通孔の変形例を示す断面図である。

【図12】本実施形態の第2の変形例による貫通電極基板を示す断面図である。 10

【図13】本実施形態の第3の変形例による貫通電極基板を示す断面図である。

【図14】本実施形態による貫通電極基板を適用できる製品の例を示す図である。

【発明を実施するための形態】

【0022】

以下、本開示の実施形態に係る貫通電極基板の構成について、図面を参照しながら詳細に説明する。なお、以下に示す実施形態は本開示の実施形態の一例であって、本開示はこれらの実施形態に限定して解釈されるものではない。また、本明細書において、「基板」、「基材」、「シート」や「フィルム」など用語は、呼称の違いのみに基づいて、互いに区別されるものではない。例えば、「基板」や「基材」は、シートやフィルムと呼ばれ得るような部材も含む概念である。また、本実施形態で参照する図面において、同一部分または同様な機能を有する部分には同一の符号または類似の符号を付し、その繰り返しの説明は省略する場合がある。また、図面の寸法比率は説明の都合上実際の比率とは異なる場合や、構成の一部が図面から省略される場合がある。 20

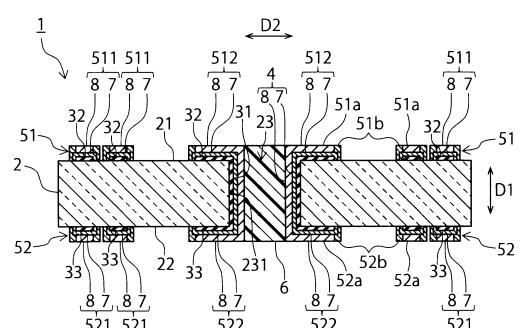

【0023】

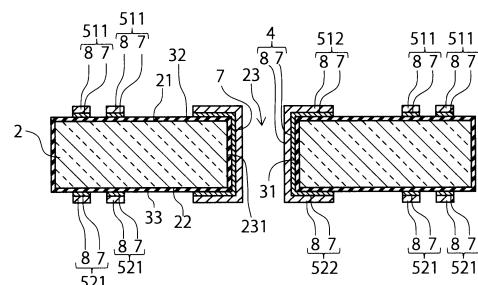

先ず、図1を参照しながら、本開示の貫通電極基板の一例について説明する。図1は、本実施形態による貫通電極基板1を示す断面図である。本実施形態の貫通電極基板1は、例えば、光学用途のインターポーザ基板に用いることができる。

【0024】

図1に示すように、本実施形態の貫通電極基板1は、透明基板2と、第1密着層の一例である側壁密着層31と、第2密着層の一例である第1面密着層32および第2面密着層33と、貫通電極4と、導電層の一例である第1面導電層51および第2面導電層52と、有機層6と、を備える。 30

【0025】

(透明基板2)

透明基板2は、可視光に対する透過性を有する基板であり、例えば、石英ガラス、無アルカリガラス、ソーダライムガラス、パイレックス(登録商標)ガラス、合成石英板等の可撓性のない透明なリジッド材が挙げられる。この種の透明基板2は、透明性が要求される貫通電極基板1に好適に用いることができる。特に無アルカリガラスは信頼性とコストの点で好ましい。

【0026】

透明基板2は、第1表面21と、第1表面21の反対側の第2表面22とを有する。図1の例において、第1表面21と第2表面22とは互いに平行である。透明基板2の内部に貫通電極4を位置させるため、透明基板2には、第1表面21から第2表面22まで透明基板2を貫通する貫通孔23が設けられている。 40

【0027】

貫通孔23は、第1表面21に直交すなわち交差する透明基板2の厚み方向D1に垂直な断面において円形状を有する。また、図示はしないが、貫通孔23は、第1表面21に沿った第1表面21の面方向D2に間隔を空けて複数設けられている。

【0028】

また、図1の例において、貫通孔23の内径は、第1表面21から第2表面22に至る

10

20

30

40

50

まで殆ど変化しない。すなわち、図1の貫通孔23は、厚み方向D1に沿ってストレートな円筒形状の側壁231を有している。後述の図10(a)~図10(c)に示すように、貫通孔23の内径は、第1表面21および第2表面22の一方から他方に向かって変化してもよい。

【0029】

貫通孔23は、面方向D2の寸法すなわち内径に対する厚みTの比T/であるアスペクト比が、3以上33以下であることが望ましい。一例として、貫通孔23の内径は、15μm以上100μm以下であり、貫通孔23の厚みTは、300μm以上500μm以下である。貫通孔23のアスペクト比T/を3以上とすることで、貫通孔23の内径を抑制できるので、貫通電極4の配線密度を高めることができる。貫通孔23のアスペクト比T/を33以下とすることで、貫通孔23の内部に貫通電極4を形成するため十分な内径を確保することができる。

【0030】

(側壁密着層31)

側壁密着層31は、貫通孔23の側壁231上に位置し、透明基板2および貫通電極4の双方への密着性および絶縁性を有する層である。

【0031】

側壁密着層31を介した透明基板2と貫通電極4との密着性は、側壁密着層31が無い場合の透明基板2と貫通電極4との直接的な密着性より高い。このような密着性の大小関係は、側壁密着層31を介して側壁231上に形成した貫通電極4を剥離することを模擬した剥離試験と、側壁231上に直接形成した貫通電極4を剥離することを模擬した剥離試験とを実施し、双方の剥離試験における剥離力を比較することで確認することができる。剥離試験としては、JIS H 8504に規定されているめっきの密着性試験方法のうち、テープ試験を用いることができる。テープ試験は、めっき皮膜に粘着力のあるテープを貼り付けて急速に引き剥がす試験である。テープを引き剥がすとき、めっき皮膜の密着性が悪いほど、テープ粘着面に付着するめっき皮膜の量、すなわちめっき皮膜の剥離量が多くなる。めっき皮膜の剥離量が多いほど、めっき皮膜の剥離に要する剥離力は小さい。テープ試験によれば、透明基板上に密着層を介して形成されためっき皮膜にテープを貼り付けて引き剥がした場合のめっき皮膜の剥離量と、透明基板上に直接形成されためっき皮膜にテープを貼り付けて引き剥がした場合のめっき皮膜の剥離量とを比較することで、密着層の有無に応じた剥離力を比較することができる。

【0032】

なお、密着層の大小関係は、実施例において説明する「JIS K5600 塗料一般試験方法」に規定されているクロスカット試験法によって確認することもできる。

【0033】

側壁密着層31は、有機物を含有する。有機物を含有することで、側壁密着層31は、透明基板2および貫通電極4との間で高い密着性を発揮することができる。

【0034】

側壁密着層31に含有される有機物は、側壁密着層31上に無電解めっき法で貫通電極4のシード層を形成する場合における金属析出性と薬液耐性との双方を有することが望ましい。このような有機物としては、例えば、エポキシ樹脂、アクリル樹脂、ポリイミド樹脂、ウレタン樹脂などの高分子樹脂を好適に用いることができる。なお、高分子樹脂は、無機酸化膜や有機单分子膜と比較して、側壁231上に均一に側壁密着層31が形成されているか否かを判断し易いので、生産性の向上に寄与することもできる。

【0035】

側壁密着層31の厚みは、15nm以上200nm以下であることが望ましい。側壁密着層31の厚みを15nm以上とすることで、側壁密着層31上に無電解めっき法で貫通電極4のシード層を形成する場合に、側壁密着層31に十分な量の触媒を吸着させることができるので、貫通電極4のシード層の析出性を向上させることができる。側壁密着層31の厚みを200nm以下とすることで、無電解めっきの後工程として実施される各種の

10

20

30

40

50

加熱工程において側壁密着層31から発生するガスの総量を抑制することができるので、ガスの圧力による貫通電極4の変形およびこれにともなう電気的特性の悪化を抑制することができる。

【0036】

側壁密着層31は、例えば、ディップコート、スプレーコート、およびスピンドルコートなどのウェットプロセスを用いて形成してもよい。

【0037】

(第1面密着層32)

第1面密着層32は、第1表面21上に位置し、透明基板2および第1面導電層51の双方への密着性および絶縁性を有する層である。

10

【0038】

第1面密着層32を介した透明基板2と第1面導電層51との密着性は、第1面密着層32が無い場合の透明基板2と第1面導電層51との直接的な密着性より高い。このような密着性の大小関係は、第1面密着層32を介して第1表面21上に形成した第1面導電層51を剥離することを模擬した剥離試験と、第1表面21上に直接形成した第1面導電層51を剥離することを模擬した剥離試験とを実施し、双方の剥離試験における第1面導電層51の剥離力を比較することで確認することができる。剥離試験としては、JIS H 8504に規定されているめっきの密着性試験方法のうち、テープ試験、または、「JIS K 5600 塗料一般試験方法」に規定されているクロスカット試験法を用いることができる。

20

【0039】

側壁密着層31と同様に、第1面密着層32は、有機物を含有する。有機物を含有することで、第1面密着層32は、透明基板2および第1面導電層51との間で高い密着性を発揮することができる。

【0040】

側壁密着層31と同様に、第1面密着層32に含有される有機物は、第1面密着層32上に無電解めっき法で第1面導電層51のシード層を形成する場合における金属析出性と薬液耐性との双方を有することが望ましい。このような有機物としては、例えば、エポキシ樹脂、アクリル樹脂、ポリイミド樹脂、ウレタン樹脂などの高分子樹脂を好適に用いることができる。なお、高分子樹脂は、無機酸化膜や有機単分子膜と比較して第1表面21上に均一に第1面密着層32が形成されているか否かを判断し易いので、生産性の向上に寄与することもできる。

30

【0041】

側壁密着層31と同様に、第1面密着層32の厚みは、15nm以上200nm以下であることが望ましい。第1面密着層32の厚みを15nm以上とすることで、第1面密着層32上に無電解めっき法で第1面導電層51のシード層を形成する場合に、第1面密着層32に十分な量の触媒を吸着させることができるので、第1面導電層51のシード層の析出性を向上させることができる。第1面密着層32の厚みを200nm以下とすることで、無電解めっき後の加熱工程において第1面密着層32から発生するガスの総量を抑制することができるので、ガスの圧力による第1面導電層51の膨張およびこれにともなう電気的特性の悪化を抑制することができる。

40

【0042】

第1面密着層32は、後述する第1面導電層51の複数の第1面配線部511および第1面パッド部512に対応するように、面方向D2に間隔を空けて部分的に第1表面21上に位置している。したがって、複数の第1面配線部511間には第1面密着層32が存在しない。このような構成によれば、後述する複数の第1面配線部511間におけるマイグレーションを抑制することができる。

【0043】

第1面密着層32は、例えば、ディップコート、スプレーコート、およびスピンドルコートなどのウェットプロセスによって側壁密着層31と同一材料で同時に形成してもよい。

50

## 【0044】

(第2面密着層33)

第2面密着層33は、第2表面22上に位置し、透明基板2および第2面導電層52の双方への密着性および絶縁性を有する層である。

## 【0045】

第2面密着層33を介した透明基板2と第2面導電層52との密着性は、第2面密着層33が無い場合の透明基板2と第2面導電層52との直接的な密着性より高い。このような密着性の大小関係は、第2面密着層33を介して第2表面22上に形成した第2面導電層52を剥離することを模擬した剥離試験と、第2表面22上に直接形成した第2面導電層52を剥離することを模擬した剥離試験とを実施し、双方の剥離試験における第2面導電層52の剥離力を比較することで確認することができる。剥離試験としては、JIS H 8504に規定されているめっきの密着性試験方法のうち、テープ試験、または、「JIS K 5600 塗料一般試験方法」に規定されているクロスカット試験法を用いることができる。

10

## 【0046】

側壁密着層31と同様に、第2面密着層33は、有機物を含有する。有機物を含有することで、第2面密着層33は、透明基板2および第2面導電層52との間で高い密着性を発揮することができる。

## 【0047】

側壁密着層31と同様に、第2面密着層33に含有される有機物は、第2面密着層33上に無電解めっき法で第2面導電層52のシード層を形成する場合における金属析出性と薬液耐性との双方を有することが望ましい。このような有機物としては、例えば、エポキシ樹脂、アクリル樹脂、ポリイミド樹脂、ウレタン樹脂などの高分子樹脂を好適に用いることができる。なお、高分子樹脂は、無機酸化膜や有機単分子膜と比較して第2表面22上に均一に第2面密着層33が形成されているか否かを判断し易いので、生産性の向上に寄与することもできる。

20

## 【0048】

側壁密着層31と同様に、第2面密着層33の厚みは、15nm以上200nm以下であることが望ましい。第2面密着層33の厚みを15nm以上とすることで、第2面密着層33上に無電解めっき法で第2面導電層52のシード層を形成する場合に、第2面密着層33に十分な量の触媒を吸着させることができるので、第2面導電層52のシード層の析出性を向上させることができる。第2面密着層33の厚みを200nm以下とすることで、無電解めっき後の加熱工程において第2面密着層33から発生するガスの総量を抑制することができるので、ガスの圧力による第2面導電層52の膨張およびこれにともなう電気的特性の悪化を抑制することができる。

30

## 【0049】

第2面密着層33は、後述する第2面導電層52の複数の第2面配線部521および第2面パッド部522に対応するように、面方向D2に間隔を空けて部分的に第2表面22上に位置している。したがって、複数の第2面配線部521間には第2面密着層33が存在しない。このような構成によれば、後述する複数の第2面配線部521間におけるマイグレーションを抑制することができる。

40

## 【0050】

第2面密着層33は、例えば、ディップコート、スプレーコート、およびスピンドルコートなどのウェットプロセスによって側壁密着層31および第1面密着層32と同一材料で同時に形成してもよい。

## 【0051】

(貫通電極4)

貫通電極4は、貫通孔23の内部において側壁密着層31上に位置し、且つ導電性を有する部材である。図1の例において、貫通電極4の厚みは、貫通孔23の幅すなわち内径よりも小さく、このため、貫通孔23の内部には、貫通電極4が存在しない空間がある。

50

すなわち、貫通電極 4 は、いわゆるコンフォーマルピアである。なお、図 1 の例において、貫通孔 2 3 の内部の空間は、貫通電極 4 の内側に位置する有機層 6 で埋められている。

【0052】

図 1 に示すように、貫通電極 4 は、第 3 導電層の一例として、側壁密着層 3 1 上に位置するシード層 7 と、第 4 導電層の一例として、シード層 7 上に位置するめっき層 8 とを有する。

【0053】

シード層 7 は、電解めっき法によってめっき層 8 を形成する電解めっき工程の際に、めっき液中の金属イオンを析出させてめっき層 8 を成長させるための土台となる、導電性を有する層である。

10

【0054】

シード層 7 の材料としては、銅などの導電性を有する材料を用いることができる。シード層 7 の材料は、めっき層 8 の材料と同一であってもよく、異なっていてもよい。例えば、シード層 7 は、チタンと銅を順に積層した積層膜や、クロムなどであってもよい。シード層 7 は、例えば、無電解めっき法で形成することができる。

【0055】

めっき層 8 は、電解めっき法によって形成される、導電性を有する層である。めっき層 8 は、例えば、銅を含有する。めっき層 8 は、銅と、銅以外の金属、例えば、金、銀、白金、ロジウム、スズ、アルミニウム、ニッケル、クロムとの合金を含有していてもよく、または、銅と銅以外の金属とを積層したものであってもよい。

20

【0056】

また、シード層 7 およびめっき層 8 は、タングステン、チタン、タンタルその他の高融点化合物を主成分として含有していてもよい。

【0057】

(第 1 面導電層 5 1)

第 1 面導電層 5 1 は、第 1 面密着層 3 2 上に位置し、且つ導電性を有する層である。第 1 面導電層 5 1 は、複数の第 1 面配線部 5 1 1 と、第 1 面パッド部 5 1 2 とを有する。

【0058】

第 1 面パッド部 5 1 2 は、貫通電極 4 と電気的に接続されており、より具体的には、貫通孔 2 3 の第 1 表面 2 1 側の周縁部上において、貫通電極 4 の第 1 表面 2 1 側の端部に連続している。第 1 面パッド部 5 1 2 は、平面視した場合に貫通孔 2 3 と同心の円環形状を呈していてもよい。貫通電極 4 と同様に、第 1 面パッド部 5 1 2 は、第 1 導電層の一例として、第 1 面密着層 3 2 上に位置するシード層 7 と、第 2 導電層の一例として、シード層 7 上に位置するめっき層 8 とを有する。第 1 面パッド部 5 1 2 のシード層 7 およびめっき層 8 は、貫通電極 4 のシード層 7 およびめっき層 8 と共に、すなわち同一成分を含有する。なお、貫通電極 4 と第 1 面パッド部 5 1 2 との境界部において、第 1 面パッド部 5 1 2 に覆われた第 1 面密着層 3 2 は、側壁密着層 3 1 に連続している。第 1 面密着層 3 2 が側壁密着層 3 1 に連続していることで、透明基板 2 の内で比較的にめっき不良が起こり易い角部上に位置する第 1 面パッド部 5 1 2 についても、透明基板 2 への密着性を可及的に向上させることができる。

30

【0059】

複数の第 1 面配線部 5 1 1 は、面方向 D 2 に間隔を空けて第 1 面密着層 3 2 上に位置する。各第 1 面配線部 5 1 1 の少なくとも 1 つは、貫通電極 4 と電気的に接続されていてもよい。貫通電極 4 と同様に、各第 1 面配線部 5 1 1 は、第 1 導電層の一例として、第 1 面密着層 3 2 上に位置するシード層 7 と、第 2 導電層の一例として、シード層 7 上に位置するめっき層 8 とを有する。第 1 面配線部 5 1 1 のシード層 7 およびめっき層 8 は、貫通電極 4 のシード層 7 およびめっき層 8 と共に、すなわち同一成分を含有する。

【0060】

なお、各第 1 面配線部 5 1 1 に覆われた第 1 面密着層 3 2 は、各第 1 面配線部 5 1 1 のそれぞれに対応するように面方向 D 2 に間隔を空けて第 1 表面 2 1 上に位置する。図 1 の

40

50

例において、隣り合う第1面配線部511同士の間には第1面密着層32が存在しない。これにより、隣り合う第1面配線部511同士の間で、第1面密着層32の表面を伝った金属の移動によるマイグレーションが生じることを抑制することができる。

【0061】

(第2面導電層52)

第2面導電層52は、第2面密着層33上に位置し、且つ導電性を有する層である。第2面導電層52は、複数の第2面配線部521と、第2面パッド部522とを有する。

【0062】

第2面パッド部522は、貫通電極4と電気的に接続されており、より具体的には、貫通孔23の第2表面22側の周縁部上において、貫通電極4の第2表面22側の端部に連続している。第2面パッド部522は、平面視した場合に貫通孔23と同心の円環形状を呈していてもよい。貫通電極4と同様に、第2面パッド部522は、第1導電層の一例として、第2面密着層33上に位置するシード層7と、第2導電層の一例として、シード層7上に位置するめっき層8とを有する。第2面パッド部522のシード層7およびめっき層8は、貫通電極4のシード層7およびめっき層8と共に、すなわち同一成分を含有する。なお、貫通電極4と第2面パッド部522との境界部において、第2面パッド部522に覆われた第2面密着層33は、側壁密着層31に連続している。第2面密着層33が側壁密着層31に連続していることで、透明基板2の中で比較的にめっき不良が起こり易い角部上に位置する第2面パッド部522についても、透明基板2への密着性を可及的に向上させることができる。

10

20

【0063】

複数の第2面配線部521は、面方向D2に間隔を空けて第2面密着層33上に位置する。各第2面配線部521の少なくとも1つは、貫通電極4と電気的に接続されていてよい。貫通電極4と同様に、各第2面配線部521は、第1導電層の一例として、第2面密着層33上に位置するシード層7と、第2導電層の一例として、シード層7上に位置するめっき層8とを有する。第2面配線部521のシード層7およびめっき層8は、貫通電極4のシード層7およびめっき層8と共に、すなわち同一成分を含有する。

【0064】

なお、各第2面配線部521に覆われた第2面密着層33は、各第2面配線部521のそれぞれに対応するように面方向D2に間隔を空けて第2表面22上に位置する。図1の例において、隣り合う第2面配線部521同士の間には第2面密着層33が存在しない。これにより、第2面配線部521同士の間で、第2面密着層33の表面を伝った金属の移動によるマイグレーションが生じることを抑制することができる。

30

【0065】

(有機層6)

有機層6は、貫通孔23の内部に位置する、絶縁性を有する層である。有機層6の有機材料としては、ポリイミドやエポキシ樹脂などを用いることができる。

【0066】

(貫通電極基板1の製造方法)

以下、貫通電極基板1の製造方法の一例について、図1乃至図9を参照して説明する。

40

【0067】

(貫通孔形成工程)

図2は、本実施形態による貫通電極基板1の製造方法を示す断面図である。まず、透明基板2を準備する。透明基板2を準備した後、図2に示すように、第1表面21から第2表面22まで透明基板2を貫通する貫通孔23を透明基板2に形成する。貫通孔23の形成方法としては、例えば、レーザ照射を用いることができる。レーザとしては、エキシマレーザ、Nd:YAGレーザ、フェムト秒レーザ等を用いることができる。Nd:YAGレーザを採用する場合、波長が1064nmの基本波、波長が532nmの第2高調波、波長が355nmの第3高調波等を用いることができる。

【0068】

50

また、レーザ照射とウェットエッティングを適宜組み合わせることもできる。具体的には、まず、レーザ照射によって透明基板2のうち貫通孔23が形成されるべき領域に変質層を形成する。続いて、透明基板2をフッ化水素などに浸漬して、変質層をエッティングする。これによって、透明基板2に貫通孔23を形成することができる。

【0069】

レーザ照射以外にも、透明基板2に研磨材を吹き付けるブラスト処理や、反応性イオンエッティング法、深掘り反応性イオンエッティング法などのドライエッティング法などによって透明基板2に貫通孔23を形成してもよい。

【0070】

(密着層形成工程)

10

図3は、図2に続く本実施形態による貫通電極基板1の製造方法を示す断面図である。貫通孔23を形成した後、図3に示すように、貫通孔23の側壁231上への側壁密着層31の形成と、第1表面21上への第1面密着層32の形成と、第2表面22上への第2面密着層33の形成とを行う。密着層31～33は、例えば、15～200nmの厚みに形成する。密着層31～33の形成は、例えば、ディップコート、スプレーコートまたはスピンドルコートなどのウェットプロセスで行うことができる。このうち、ディップコートによれば、すべての密着層31～33を同時に形成することができるので、製造効率を向上させることができる。

【0071】

(シード層形成工程)

20

図4は、図3に続く本実施形態による貫通電極基板1の製造方法を示す断面図である。密着層31～33を形成した後、図4に示すように、密着層31～33上にシード層7を形成する。シード層7は、例えば200～500nmの厚みに形成する。以下、密着層31～33が形成された透明基板2のことを、単に透明基板2とも呼ぶ。

【0072】

シード層7の形成においては、先ず、透明基板2を洗浄と、透明基板2の濡れ性を上げるための表面改質とを行う。洗浄および表面改質は、例えば、PH2以下の酸性水溶液またはPH11以上のアルカリ性水溶液を40～50に保持し、当該酸性水溶液またはアルカリ性水溶液中に透明基板2を5～15分間浸漬することで行うことができる。

【0073】

30

洗浄および表面改質を行った後、透明基板2を触媒化する。具体的には、無電解銅めっきの触媒となるPdイオンまたはSn/Pdコロイドを密着層31～33に吸着させる。触媒化は、例えば、Pdイオンを含有するPH9～11のアルカリ性水溶液またはSn/Pdコロイドを含有するPH2以下の酸性水溶液を40～50に保持し、当該酸性水溶液またはアルカリ性水溶液中に透明基板2を5～15分間浸漬することで行うことができる。

【0074】

触媒化を行った後、密着層31～33に吸着させたPdイオンのPdへの還元または密着層31～33に吸着させたSn/PdコロイドにおけるPdの活性化を行う。Pdの還元は、例えば、適当な還元剤を含むPH5～8の水溶液を50に保持し、この水溶液中に透明基板2を1～5分間浸漬することで行うことができる。Pdの活性化は、例えば、PH2以下の酸性水溶液またはPH11以上のアルカリ性水溶液を50に保持し、この水溶液中に透明基板2を1～5分間浸漬することで行うことができる。

40

【0075】

Pdイオンの還元またはPdの活性化を行った後、無電解銅めっきを行う。具体的には、密着層31～33に吸着されたPdを触媒とし、密着層31～33上に銅の被膜を形成する。無電解銅めっきは、例えば、銅イオン、水酸化ナトリウムおよびホルマリンを含有するアルカリ性水溶液を30～40に保持し、このアルカリ性水溶液中に透明基板2を5～30分間浸漬することで行うことができる。

【0076】

50

## (レジスト層形成工程)

図5は、図4に続く本実施形態による貫通電極基板1の製造方法を示す断面図である。シード層7を形成した後、図5に示すように、貫通電極4、第1面導電層51および第2面導電層52を形成すべき一部の領域を除いて、シード層7上にレジスト層9を形成する。レジスト層9の形成は、例えば、シード層7上にドライフィルムレジストをラミネートし、ラミネートされたドライフィルムレジストを露光および現像することで行うことができる。

## 【0077】

## (めっき層形成工程)

図6は、図5に続く本実施形態による貫通電極基板1の製造方法を示す断面図である。レジスト層9を形成した後、図6に示すように、レジスト層9をマスクとした電解めっき法により、レジスト層9によって覆われていないシード層7上にめっき層8を形成する。めっき層8は、例えば2～12μmの厚みに形成する。

## 【0078】

## (レジスト層除去工程)

図7は、図6に続く本実施形態による貫通電極基板1の製造方法を示す断面図である。めっき層8を形成した後、図7に示すように、透明基板2からレジスト層9を剥離すなわち除去する。レジスト層9は、例えば、アルカリ溶液への浸漬で除去することができる。

## 【0079】

## (シード層除去工程)

図8は、図7に続く本実施形態による貫通電極基板1の製造方法を示す断面図である。レジスト層9を除去した後、図8に示すように、シード層7のうちレジスト層9が形成されていた部分を除去する。シード層7は、例えば、ウェットエッティングで除去することができる。シード層7を除去することで、貫通電極4と、第1面導電層51と、第2面導電層52とが同時に形成される。

## 【0080】

## (密着層除去工程)

図9は、図8に続く本実施形態による貫通電極基板1の製造方法を示す断面図である。シード層7を除去した後、図9に示すように、第1面密着層32のうち第1面導電層51で覆われていない部分を除去するとともに、第2面密着層33のうち第2面導電層52で覆われていない部分を除去する。密着層32、33は、例えば、プラズマアッシングやアルカリ浸漬などで除去することができる。

## 【0081】

## (有機層形成工程)

密着層32、33を除去した後、図1に示すように、貫通孔23の内部に有機層6を形成する。具体的には、先ず、有機層6を構成するための樹脂層を含むフィルムを、透明基板2の第1表面21上及び第2表面22上に配置する。次いで、フィルムを加圧することにより、樹脂層を貫通孔23の内部に押し込む。その後、貫通孔23の内部に押し込まれた樹脂層を、樹脂層に光を照射することなどによって硬化させる。また、樹脂層の不要部分を除去する。このようにして、貫通孔23の内部に有機層6を設けることができる。

## 【0082】

## (実施例)

以下、本実施形態の実施例として、貫通電極基板1の試料に対して実施した観察および電気検査の結果について説明する。

## 【0083】

実施例では、密着層の厚みが互いに異なる試料No.1～No.7の7つの試料を作製した。各試料の作製にあたっては、先ず、各試料に共通の透明基板2として、厚み450μmの無アルカリガラスに90μmすなわちアスペクト比：5の貫通孔23を形成した透明基板2を準備した。

## 【0084】

10

20

30

40

50

透明基板2上への密着層31～33の形成においては、ポリイミドを主成分とする有機樹脂を、各試料毎にディップコートの有無または速度を変えて異なる厚みに形成した。具体的には、試料No.1については、ディップコートを行わず、密着層31～33を形成しなかった。その他の試料の密着層31～33の厚みは、試料No.2については15nm、試料No.3については22nm、試料No.4については98nm、試料No.5については185nm、試料No.6については203nm、試料No.7については210nmとした。

【0085】

シード層7の形成においては、各試料とも、無電解めっき法によって500nmの厚みを有するようにシード層7を形成した。

10

【0086】

シード層7上へのレジスト層9の形成においては、各試料とも、日立化成社製のRY5319をラミネートした後、膜表面から100μm離れた位置にフォトマスクを配置して、プロキシミティアライナにより、超高压水銀ランプでパターン露光した。パターン露光後、液温30℃、濃度1%の炭酸ナトリウム水溶液中に透明基板2を1分間浸漬して現像を行うことで、レジスト層9の未硬化部分を除去した。

【0087】

シード層7上へのめっき層8の形成においては、各試料とも、電解銅めっき法によって、レジスト層9で覆われていないシード層7上に5μmの厚みを有するように、めっき層8を形成した。

20

【0088】

めっき層8の形成後のレジスト層9の除去においては、各試料とも、濃度3%の水酸化ナトリウム水溶液を用いて3分間のスプレー剥離を行うことで、透明基板2からレジスト層9を剥離した。

【0089】

レジスト層9の除去後のシード層7の除去においては、各試料とも、銅除去剤であるメック社製SF-5420に透明基板2を1分間浸漬するウェットエッチングを行うことで、シード層7を除去した。

【0090】

シード層7の除去後の密着層32、33の除去においては、プラズマ照射により、めっき層8で覆われていない配線部間および配線部とパッド部との間の密着層32、33を除去した。

30

【0091】

密着層32、33の除去後は、各試料とも、窒素雰囲気下において200℃で30分間のアニール処理を行った。

【0092】

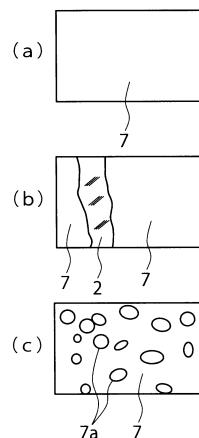

以上のようにして作製された試料No.1～No.7に対して、シード層の析出状態の観察と、アニール処理後のシード層の膨張状態の観察と、「JIS K5600 塗料一般試験方法」に規定されているクロスカット試験法によるシード層の剥離状態の観察とを行った。観察には、電子顕微鏡を使用した。また、電気検査として、シード層による電気信号の導通検査を行った。なお、クロスカット試験法は、既述したテープ試験と類似している。クロスカット試験法では、シード層が形成された透明基板の試験面に、カッターで透明基板に達する碁盤目状の切り傷を形成する。そして、碁盤目部分にテープを強く圧着させ、テープの端を45°の角度で一気に引き剥がし、碁盤目部分の状態を標準図と比較して評価する。実施例の観察結果および電気検査結果を以下の表1および図10(a)～図10(c)に示す。

40

【0093】

【表1】

| 試料No | 密着層膜厚  | 観察結果          |                |                         | 電気検査結果 |

|------|--------|---------------|----------------|-------------------------|--------|

|      |        | シード層の<br>析出状態 | アニール後の<br>膨張状態 | クロスカット<br>試験による<br>剥離状態 |        |

| 1    | 0 nm   | ×             | ○              | ×                       | ×      |

| 2    | 15 nm  | ○             | ○              | ○                       | ○      |

| 3    | 22 nm  | ○             | ○              | ○                       | ○      |

| 4    | 98 nm  | ○             | ○              | ○                       | ○      |

| 5    | 185 nm | ○             | ○              | ○                       | ○      |

| 6    | 203 nm | ○             | ○              | ○                       | ○      |

| 7    | 210 nm | ○             | ×              | ○                       | ×      |

## 【0094】

表1中の“○”は、結果が良好であることを示している。一方、表1中の“×”は、結果が悪いことを示している。また、図10(a)は、試料No.2～試料No.6に示される本実施形態による貫通電極基板1において、透明基板2上へのシード層7の形成状態を模式的に示す平面図である。図10(b)は、試料No.1に示される第1の比較例による貫通電極基板において、透明基板2上へのシード層7の形成状態を模式的に示す平面図である。図10(c)は、試料No.7に示される第2の比較例による貫通電極基板において、透明基板2上へのシード層7の形成状態を模式的に示す平面図である。

## 【0095】

表1および図10(a)に示すように、試料No.2～No.6においては、透明基板2上にシード層7が万遍なく形成され、アニールにともなうシード層7の膨張も殆ど無いことが確認された。更に、試料No.2～No.6においては、クロスカット試験によるシード層7の剥離が殆ど無く、また、導通状態が良好であることが確認された。このような試料No.2～試料No.6の結果は、試料No.2～試料No.6が適度な厚みの密着層31～33を有することで、シード層7の密着性を確保しつつアニールの際に密着層31～33から生じるガスの総量を抑制できることによるものと推測される。

## 【0096】

一方、試料No.1においては、表1および図10(b)に示すように、シード層7が形成されずに透明基板2が露出した箇所が確認された。更に、試料No.1においては、クロスカット試験によるシード層7の剥離量が多く、また、導通不良が生じることが確認された。このような試料No.1の結果は、試料No.1が密着層31～33を有しないことで、シード層7の密着性を確保できないことによるものと推測される。

## 【0097】

また、試料No.7においては、表1および図10(c)に示すように、アニールにともなうシード層7の膨張部7aが多数生じることが確認された。更に、試料No.7においては、導通不良が生じることが確認された。このような試料No.7の結果は、試料No.7の密着層31～33の厚みが過大であることで、アニールの際に密着層31～33から生じるガスの総量が多いことによるものと推測される。

## 【0098】

以上の実施例によれば、密着層31～33の厚みを15nm以上200nm以下とすることで、シード層7の密着性および電気特性が良好になることが確認された。

## 【0099】

以下、本実施形態によってもたらされる作用について説明する。

## 【0100】

図1に示したように、本実施形態によれば、側壁密着層31と、第1面密着層32と、第2面密着層33とを備えることで、透明基板2と貫通電極4との密着性だけでなく、透

明基板 2 と第 1 面導電層 5 1 および第 2 面導電層 5 2 との密着性も高めることができる。これにより、透明基板 2 からの貫通電極 4 および配線部 5 1 1、5 2 1 の剥離を同時に抑制することができる。

#### 【 0 1 0 1 】

また、本実施形態によれば、隣り合う配線部 5 1 1、5 2 1 間に密着層 3 2、3 3 が設けられていないため、隣り合う配線部 5 1 1、5 2 1 同士の間でのマイグレーションを抑制することができる。

#### 【 0 1 0 2 】

また、貫通孔 2 3 のアスペクト比  $T / D$  を 3 以上 3 3 以下とすれば、貫通電極 4 の配線密度を高めることができるとともに、貫通孔 2 3 の内部に貫通電極 4 を形成するために十分な内径  $D$  を確保することができる。

10

#### 【 0 1 0 3 】

また、密着層 3 1 ~ 3 3 の厚みを 1 5 nm 以上 2 0 0 nm 以下とすれば、貫通孔 2 3 のアスペクト比が高い場合においてもシード層 7 の析出性を向上させることができ、また、加熱工程において密着層 3 1 ~ 3 3 から発生したガスによる貫通電極 4 および配線部 5 1 1、5 2 1 の変形を抑制することができ、電気的特性の悪化を抑制することができる。

#### 【 0 1 0 4 】

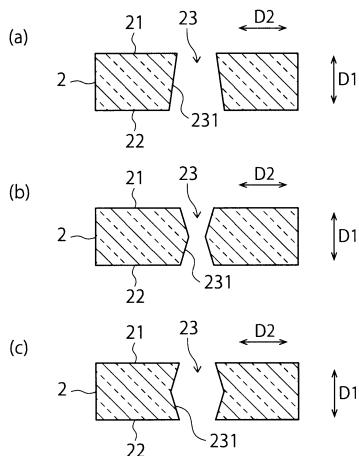

##### ( 第 1 の変形例 )

次に、第 1 の変形例として、貫通孔 2 3 の形状の変形例について説明する。図 1 1 ( a ) は、本実施形態の第 1 の変形例による貫通電極基板 1 として、貫通孔 2 3 の一変形例を示す断面図である。図 1 1 ( b ) は、図 1 1 ( a ) と異なる貫通孔 2 3 の変形例を示す断面図である。図 1 1 ( c ) は、図 1 1 ( a ) および図 1 1 ( b ) と異なる貫通孔 2 3 の変形例を示す断面図である。

20

#### 【 0 1 0 5 】

図 1 の例において、貫通孔 2 3 の側壁 2 3 1 は、厚み方向  $D 1$  の位置によらず内径が均一の円筒形状を有している。しかしながら、貫通孔 2 3 の形状が特に限られることはない。例えば、図 1 1 ( a ) に示すように、貫通孔 2 3 の側壁 2 3 1 は、第 1 表面 2 1 および第 2 表面 2 2 の一方から他方に向かうにしたがって内径が漸増するテーパ形状を有してもよい。また、図 1 1 ( b ) に示すように、貫通孔 2 3 の側壁 2 3 1 は、第 1 表面 2 1 および第 2 表面 2 2 から透明基板 2 の厚み方向  $D 1$  の中央部に向かうにしたがって内径が漸減する形状を有してもよい。また、図 1 1 ( c ) に示すように、貫通孔 2 3 の側壁 2 3 1 は、第 1 表面 2 1 および第 2 表面 2 2 から透明基板 2 の厚み方向  $D 1$  の中央部に向かうにしたがって内径が漸増する形状を有してもよい。また、貫通孔 2 3 の面方向  $D 2$  の断面は、円形状に限らず、例えば、多角形状であってもよい。

30

#### 【 0 1 0 6 】

第 1 の変形例においても、図 1 の例と同様に、側壁密着層 3 1 と、第 1 面密着層 3 2 と、第 2 面密着層 3 3 とを備えることで、透明基板 2 からの貫通電極 4 および配線部 5 1 1、5 2 1 の剥離を同時に抑制することができる。

#### 【 0 1 0 7 】

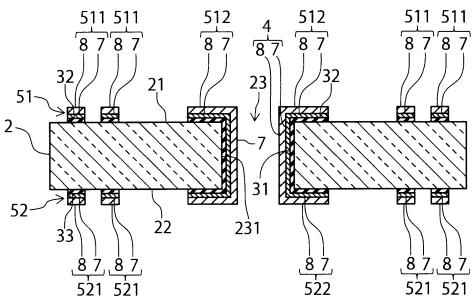

##### ( 第 2 の変形例 )

40

次に、第 1 面密着層 3 2 および第 2 面密着層 3 3 が全面的に形成された第 2 の変形例について説明する。図 1 2 は、本実施形態の第 2 の変形例による貫通電極基板 1 を示す断面図である。図 1 の例において、第 1 面密着層 3 2 は、第 1 面導電層 5 1 に対応するように第 1 表面 2 1 上に部分的に位置し、第 2 面密着層 3 3 は、第 2 面導電層 5 2 に対応するように第 2 表面 2 2 上に部分的に位置している。すなわち、第 1 面密着層 3 2 は、第 1 面導電層 5 1 が存在しない第 1 表面 2 1 上には設けられておらず、第 2 面密着層 3 3 は、第 2 面導電層 5 2 が存在しない第 2 表面 2 2 上には設けられていない。

#### 【 0 1 0 8 】

これに対して、第 2 の変形例の第 1 面密着層 3 2 は、図 1 2 に示すように、第 1 表面 2 1 上に全面的に位置している。また、第 2 面密着層 3 3 は、第 2 表面 2 2 上に全面的に位

50

置している。

【0109】

第2の変形例によれば、図9に示した密着層32、33の除去工程が不要となるので、製造工数を削減することができる。

【0110】

(第3の変形例)

次に、導電層51、52が密着層32、33の側壁を覆う第3の変形例について説明する。図13は、本実施形態の第3の変形例による貫通電極基板1を示す断面図である。

【0111】

図1の例において、第1面導電層51は、第1面密着層32に対して厚み方向D1の一方すなわち上方にのみ位置し、第2面導電層52は、第2面密着層33に対して厚み方向D1の他方すなわち下方のみに位置していた。

10

【0112】

これに対して、第3の変形例の第1面導電層51は、図13に示すように、第1面密着層32に対して厚み方向D1の一方に位置する第1部分51aと、第1面密着層32に対して面方向D2に位置する第2部分51bとを有している。第2部分51bは、第1面密着層32の側壁を覆っている。

【0113】

また、図13に示すように、第2面導電層52は、第2面密着層33に対して厚み方向D1の他方に位置する第1部分52aと、第2面密着層33に対して面方向D2に位置する第2部分52bとを有している。第2部分52bは、第2面密着層33の側壁を覆っている。

20

【0114】

第3の変形例の貫通電極基板1は、密着層31～33をパターニングした後にシード層7およびめっき層8を形成することによって製造することができる。

【0115】

第3の変形例によれば、第1面導電層51および第2面導電層52の断面積を増加することができる、配線抵抗を低減することができる。

【0116】

第1～第3の変形例は、これらを適宜組み合わせてもよい。

30

【0117】

(製品への適用例)

図14は、上記各態様の貫通電極基板1を適用できる製品の例を示す図である。本開示の実施形態に係る貫通電極基板1は、光学用途の様々な製品に適用できる。例えば、貫通電極基板1は、携帯電話110のカメラ、スマートフォン120のカメラ、デジタルビデオカメラ130、デジタルカメラ140等に搭載できる。

【0118】

本開示の態様は、上述した個々の実施形態に限定されるものではなく、当業者が想到しうる種々の変形も含むものであり、本開示の効果も上述した内容に限定されない。すなわち、特許請求の範囲に規定された内容およびその均等物から導き出される本開示の概念的な思想と趣旨を逸脱しない範囲で種々の追加、変更および部分的削除が可能である。

40

【符号の説明】

【0119】

1 貫通電極基板

2 透明基板

2 1 第1表面

2 2 第2表面

2 3 貫通孔

3 1 側壁密着層

3 2 第1面密着層

50

3 3 第2面密着層

4 貫通電極

5 1 第1面導電層

5 2 第2面導電層

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図9】

【図8】

【図10】

【図11】

【図13】

【図12】

【図14】

---

フロントページの続き

| (51)Int.Cl. |                   | F I     |       |

|-------------|-------------------|---------|-------|

| H 0 5 K     | 3/40 (2006.01)    | H 0 5 K | 3/40  |

| H 0 1 L     | 21/3205 (2006.01) | H 0 1 L | 21/88 |

| H 0 1 L     | 21/768 (2006.01)  |         | J     |

| H 0 1 L     | 23/522 (2006.01)  |         |       |

(72)発明者 千吉良 敦子

東京都新宿区市谷加賀町一丁目1番1号 大日本印刷株式会社内

(72)発明者 成田 祐治

東京都新宿区市谷加賀町一丁目1番1号 大日本印刷株式会社内

(72)発明者 古庄 宏樹

東京都新宿区市谷加賀町一丁目1番1号 大日本印刷株式会社内

(72)発明者 有吉 紗子

東京都新宿区市谷加賀町一丁目1番1号 大日本印刷株式会社内

審査官 ゆずりは 広行

(56)参考文献 特開2016-046267 (JP, A)

国際公開第2013/150940 (WO, A1)

(58)調査した分野(Int.Cl., DB名)

|         |               |

|---------|---------------|

| H 0 5 K | 1 / 0 3       |

| H 0 5 K | 1 / 1 1       |

| H 0 5 K | 3 / 3 8       |

| H 0 5 K | 3 / 4 0       |

| H 0 1 L | 2 1 / 3 2 0 5 |

| H 0 1 L | 2 1 / 7 6 8   |

| H 0 1 L | 2 3 / 3 2     |

| H 0 1 L | 2 3 / 5 2 2   |