#### (19) DEUTSCHE DEMOKRATISCHE REPUBLIK

### **PATENTSCHRIFT**

#### Wirtschaftspatent

Erteilt gemaeß § 5 Absatz 1 des Aenderungsgesetzes

ISSN 0433-6461

204 328

Int.Cl.3

3(51) G 06 F 3/02

G 06 F 3/03

#### AMT FUER ERFINDUNGS- UND PATENTWESEN

In der vom Anmelder eingereichten Fassung veroeffentlicht

(21)WP G 06 F/ 2384 755 (22)26.03.82 (44)23.11.83

(72)

ELLEND, WERNER, DIPL.-ING.; EBERT, MATTHIAS; DD;

(73) (74) INSTITUT FUER ELEKTRO-ANLAGEN BFN 1136 BERLIN STRASSE DER BEFREIUNG 1

#### (54) SCHALTUNGSANORDNUNG FUER EINE EINGABETASTATUR

(57) Die Erfindung betrifft eine Schaltungsanordnung für eine Eingabetastatur auf dem Gebiet der Digitaltechnik, insbesondere für parallel arbeitende gepufferte Eingabesysteme. Sie ist anwendbar bei der Charakterisierung von Abtastpunkten in Digitalisierprozessen. Erfindungsgemäß wird dies gelöst durch eine Schaltungsanordnung bestehend aus Tasten mit Umschaltkontaktsätzen, Widerständen, Speichern mit Ladeeingang und Negatoren. An allen Speichereingängen liegt im Grundzustand (keine Taste gedrückt) Low-Signal und am Ladeeingang High-Signal. Beim Betätigen einer Taste (gedrückter Zustand) hat der entsprechende Speichereingang High-Signal und der Ladeeingang Low-Signal. Damit wird der neue Wert in den Speicher übernommen und der alte Inhalt gelöscht. Dieser Zustand bleibt bei nichtgedrückter Taste erhalten, da beim Loslassen der Taste das High-Signal am Speichereingang länger anliegt als das Low-Signal am Ladeeingang. Für die Eingabeerweiterung können n-Speicher angesprochen werden. Fig. 1

# 238475 5

#### Schaltungsanordnung für eine Eingabetastatur

#### Anwendungsgebiet der Erfindung

Die Erfindung betrifft eine Schaltungsanordnung für eine Eingabetastatur auf dem Gebiet der Digitaltechnik, insbesondere für parallel arbeitende gepufferte Eingabesysteme. Sie ist anwendbar bei der Charakterisierung von Abtastpunkten in Digitalisierprozessen.

#### Charakteristik der bekannten technischen Lösungen

Bekannt sind eine Vielzahl von elektronischen Geräten, beispielsweise elektronische Taschenrechner, elektronische Rechenmaschinen oder Fernsteueranordnungen für Fernseh- oder

Rundfunkgeräte, die über Eingabetastaturen gesteuert werden.

Die Eingabetastaturen bestehen im allgemeinen aus Tastschaltern mit Einfach- oder Doppelkontakten und einer weiteren Beschaltung. Bei ihrer Betätigung werden elektrische Verbindungen zum datenverarbeitenden System hergestellt und gelöst.

Die Beschaltung der Taster erfolgt je nach Anwendung uncodiert, codiert oder in Matrixanordnung. Aus der Auslegeschrift (DE-AS 2756327) ist eine Schaltungsanordnung für eine

Eingabetastatur mit einer Matrixanordnung, bestehend aus mSpalten und n-Zeilen bekannt.

Bei dieser erfindungsgemäßen Lösung ist je Zeile bzw. Spalte nur ein Speicher einzusetzen. Durch den zusätzlichen Einsatz von elektronischen Schaltern und die anschließende Dekodierung der Zeilen- und Spaltenverschlüsselung erfordert eine derartige Schaltungsanordnung einen hohen Aufwand an Bauelementen. Weiterhin ist eine Tastaturanordnung für Dateneingabegeräte bekannt (DE-AS 1574670).

Mit jeder einzelnen Taste wird ein Impuls erzeugt, der über eine Codierschaltung die Übernahme eines entsprechenden Zeichens in einen Speicher veranlaßt. Die erfindungsgemäße Lösung besitzt einen hohen Bauelementeaufwand. Ein weiterer Nachteil besteht darin, daß die Schaltungsanordnung nicht von prellenden Kontakten entkoppelt ist, somit ist während dieser Phase kein definierter Ausgangszustand gegeben.

#### Ziel der Erfindung

Ziel der Erfindung ist, ein parallel arbeitendes gepuffertes Eingabesystem mit n Eingabetasten zu entwickeln und den Aufwand an Bauelementen zu verringern.

### Darlegung des Wesens der Erfindung

Der Erfindung liegt die Aufgabe zugrunde, digitale Informationseingaben mittels Tasten in einem Speicher einzugeben und den alten Inhalt gleichzeitig zu löschen.

Erfindungsgemäß wird die Aufgabe dadurch gelöst, daß der erste Eingang eines Speichers mit Ladeeingang an den Ausgang eines Negators angeschlossen ist und dessen Eingang mit dem Öffnerkontakt des ersten Tasters und mit dem ersten Anschluß des ersten Widerstandes verknüpft ist.

Der zweite Anschluß des ersten Widerstandes ist mit dem ersten Anschluß des zweiten, dritten, n-ten und (n+1)-ten Widerstandes verbunden.

Der zweite, dritte und n-te Eingang des Speichers mit Ladeeingang ist an den Öffnerkontakt des zweiten, dritten und n-ten Tasters und an den zweiten Anschluß des zweiten, dritten und n-ten Widerstandes angeschlossen. Der Ladeeingang des Speichers ist mit dem zweiten Anschluß des (n+1)-ten Widerstandes und dem Schließerkontakt des ersten, zweiten, dritten und n-ten Tasters zusammengeschaltet, wobei die Schaltkontakte des ersten, zweiten, dritten und n-ten Tasters miteinander verknüpft sind.

Durch die erfindungsgemäße Schaltungsanordnung werden die drei Zustände eines Umschaltkontaktes bei einem Taster für eine digitale Informationseingabe in einem Speicher mit Ladeeinheit technisch genutzt und damit eine kostengünstige Lösung durch Einsparung an Bauelementen geschaffen.

#### Ausführungsbeispiel

Die Erfindung soll nachstehend an einem Ausführungsbeispiel näher erläutert werden.

In der beiliegenden Zeichnung zeigt:

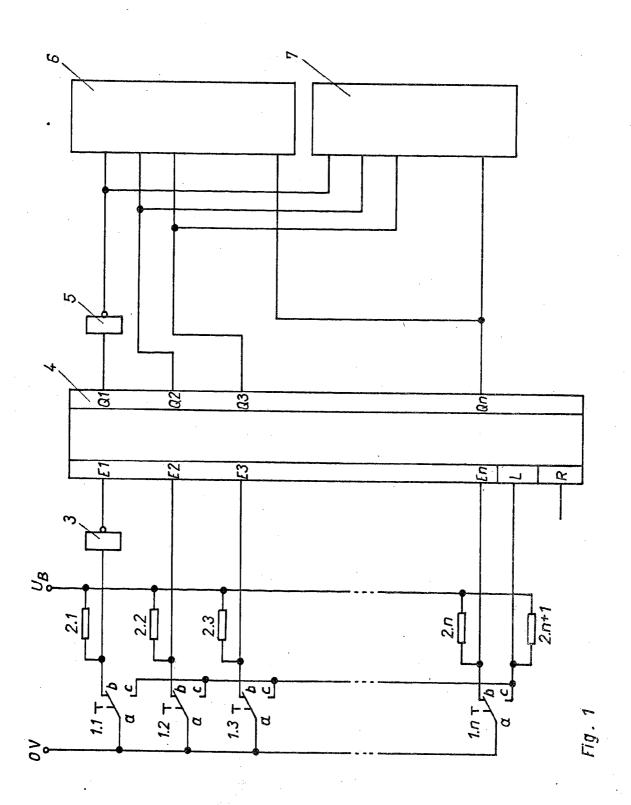

Fig. 1 Schaltungsanordnung für eine Eingabetastatur

Die erfindungsgemäße Schaltungsanordnung dient als Eingabetastatur für digitale Informationen in einem Speicher mit Ladeeinheit, wobei der prinzipielle Aufgabe eines Umschaltkontaktes ausgenutzt wird.

An den Speichereingangen  $E_2$ , ...,  $E_n$  liegt im Grundzustand (keine Taste gedrückt) Low-Signal bzw. am Speichereingang  $E_1$  High-Signal und am Ladeeingang L des Speichers 4 High-Signal.

Beim Betätigen der Taste 1.2 (gedrückter Zustand) hat der Speichereingang  $\rm E_2$  High-Signal und der Ladeeingang L Low-Signal. Damit erscheint das High-Signal am Ausgang  $\rm Q_2$ , wobei der alte Inhalt des Speichers gelöscht wird. Dieser Zustand bleibt beim Loslassen der Taste 1.2 erhalten, da das High-Signal am Speichereingang  $\rm E_2$  länger anliegt, als das Low-Signal am Ladeeingang L. Gleichartig sind die Signalzustände beim Betätigen der Tasten 1.3, ..., 1.n.

Beim Betätigen der Taste 1.1 (gedrückter Zustand) hat der Speichereingang E<sub>1</sub> durch den Negator 3 Low-Signal und der Ladeeingang L Low-Signal.

## -4- 238475 5

Damit erscheint das Low-Signal am Ausgang Q<sub>1</sub> und wird durch den Negator 5 für den Verstärker und die Anzeige 6 negiert.

Der alte Inhalt des Speichers 4 wird gelöscht. Die Rücksetzung des Speichers 4 erfolgt mit High-Signal an dem Rücksetzeingang R.

Der Speicherinhalt wird durch die Anzeige mit Verstärker 6 da rgestellt.

Die Schnittstelle Dekoder 7 stellt den Speicherinhalt kodiert zur weiteren Verarbeitung bereit.

Für die Eingabeerweiterung des Speichers 4 können n-Eingänge angesprochen werden. Die Anzahl n wird begrenzt durch den Kontaktsatz und deren Strombelastbarkeit, da die Summe aller Ladeströme über den Kontaktsatz fließt.

Bei Realisierung des Speichers 4 mit mehreren Speichergruppen sind die Lade- und Rücksetzeingänge parallel zu schalten.

### Erfindungsanspruch

Schaltungsanordnung für eine Eingabetastatur mittels Tasten und Widerständen, insbesondere für ein Digitalisiergerät, gekennzeichnet dadurch, daß

der erste Eingang (E1) eines Speichers mit Ladeeingang (4) an den Ausgang eines Negators (3) angeschlossen ist, dessen Eingang mit dem Öffnerkontakt (b) des ersten Tasters (1.1) und mit dem ersten Anschluß des ersten Widerstandes (2.1) verknüpft ist, wobei der Ausgang des ersten Widerstandes (2.1) mit dem des zweiten, dritten bis n-ten und (n+1)-ten Widerstandes (2.2; 2.3; ...; 2.n; 2.n+1) verbunden ist, der zweite, dritte bis n-te Eingang (E2; E3; ...; En) des Speichers mit Ladeeingang (4) an den Öffnerkontakt (b) des zweiten, dritten bis n-ten Tasters (1.2; 1.3; ...; 1.n) und an den Eingang des zweiten, dritten bis n-ten Widerstandes (2.2: 2.3; ...; 2.n) angeschlossen ist, der Ladeeingang (L) des Speichers (4) mit dem Eingang des (n+1)-ten Widerstandes (2 n+1) und dem Schließerkontakt (c) des ersten, zweiten, dritten bis n-ten Tasters (1.1; 1.2; 1.3; ...; 1.n) zusammengeschaltet ist, wobei die Schaltkontakte (a) des ersten, zweiten, dritten bis n-ten Tasters (1.1; 1.2; 1.3; ...; 1.n) miteinander verknüpft sind.

Hierzu 1 Seite Zeichnungen