(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第4233893号

(P4233893)

(45) 発行日 平成21年3月4日(2009.3.4)

(24) 登録日 平成20年12月19日(2008.12.19)

(51) Int.Cl.

G06F 11/28 (2006.01)

F 1

G06F 11/28 310A

請求項の数 18 (全 20 頁)

(21) 出願番号 特願2003-59371 (P2003-59371)

(22) 出願日 平成15年3月6日 (2003.3.6)

(65) 公開番号 特開2004-13896 (P2004-13896A)

(43) 公開日 平成16年1月15日 (2004.1.15)

審査請求日 平成17年3月28日 (2005.3.28)

(31) 優先権主張番号 0213149.8

(32) 優先日 平成14年6月7日 (2002.6.7)

(33) 優先権主張国 英国(GB)

(73) 特許権者 594154428

エイアールエム リミテッド

イギリス国 シービー1 9エヌジェイ

ケンブリッジ、チェリー ヒントン、フル

バーン ロード 110

(74) 代理人 100066692

弁理士 浅村 畏

(74) 代理人 100072040

弁理士 浅村 翼

(74) 代理人 100094673

弁理士 林 銀三

(74) 代理人 100091339

弁理士 清水 邦明

最終頁に続く

(54) 【発明の名称】データ処理システムにおける命令のトレーシング

## (57) 【特許請求の範囲】

## 【請求項 1】

データ処理装置であって、

(i) 一連の処理サイクルにわたって動作し、プログラム命令に応じてデータ処理動作を実行するデータ処理回路と、

(ii) 前記プログラム命令に応じた前記データ処理回路の動作を示す命令トレースデータを生成するトレーシング回路とからなり、

(iii) 前記命令トレースデータは、前記データ処理回路によって連続する処理サイクルにわたって実行される処理から発生する一連のトレース事象を符号化した所定の長さの命令トレースワードを少なくとも1つ含み、前記一連のトレース事象は、

(iv) 前記データ処理回路によるプログラム命令の実行に対応する少なくとも1つのトレース事象と、

(v) 前記データ処理回路によるプログラム命令の実行以外に対応する少なくとも1つのトレース事象と、

を含む、前記データ処理装置。

## 【請求項 2】

前記一連のトレース事象は前記データトレーシング回路によるプログラム命令の実行にそれぞれ対応する1つあるいはそれ以上のトレース事象と、実行されない条件付プログラム命令に対応するトレース事象との組み合わせからなる、請求項1に記載の装置。

## 【請求項 3】

10

20

前記データ処理回路によって実行されるプログラム命令の実行にそれぞれ対応する前記1つあるいはそれ以上のトレース事象は、実行されない条件付プログラム命令に対応する前記トレース事象の前に発生する、請求項2に記載の装置。

**【請求項4】**

前記一連のトレース事象は前記データ処理回路が待ち状態である前記データ処理回路の待ち処理サイクルにそれぞれ対応する1つあるいはそれ以上のトレース事象と、実行されるプログラム命令に対応するトレース事象の組み合わせからなる、請求項1に記載の装置。

**【請求項5】**

前記データ処理回路が待ち状態である前記データ処理回路の待ち処理サイクルにそれぞれ対応する前記1つあるいはそれ以上のトレース事象は実行されるプログラム命令に対応する前記トレース事象の前に発生する、請求項4に記載の装置。 10

**【請求項6】**

前記データ処理回路は処理パイプラインを含み、前記データ処理回路によって実行されるプログラム命令に対応する前記少なくとも1つのトレース事象は前記プログラム命令が前記処理パイプライン内の所定の位置に達したことを表す、請求項1に記載の装置。

**【請求項7】**

前記所定の位置は、

(i) 前記プログラム命令の実行開始、および

(ii) 前記プログラム命令の実行の完了のいずれかである、請求項6に記載の装置。 20

**【請求項8】**

前記トレーシング回路は前記データ処理回路によって処理されるデータ値を示すデータトレースデータを生成する、請求項1に記載の装置。

**【請求項9】**

前記データ値は前記データ処理回路に入力されるデータ値を含む、請求項8に記載の装置。

**【請求項10】**

前記データ値は前記データ処理回路から出力されるデータ値を含む、請求項8に記載の装置。

**【請求項11】**

前記命令トレースデータおよび前記データトレースデータは共通のトレースデータストリーム中でインターリーブされる、請求項8に記載の装置。 30

**【請求項12】**

前記トレーシング回路は、前記命令トレースデータに各処理サイクルにおける前記データ処理回路の処理動作を示す情報が含まれるサイクルアキュレートモードで動作する、請求項1に記載の装置。

**【請求項13】**

前記データ処理回路はプロセッサコアである、請求項1に記載の装置。

**【請求項14】**

前記トレーシング回路は前記装置からの出力に先立って命令トレースデータをバッファするためのトレースデータメモリを含む、請求項1に記載の装置。 40

**【請求項15】**

データ処理方法であって、

(i) データ処理回路の一連の処理サイクルにわたって、プログラム命令に応じたデータ処理動作を実行し、

(ii) 前記プログラム命令に応じた前記データ処理回路の動作を示す命令トレースデータを生成し、

(iii) 前記命令トレースデータは、前記データ処理回路によって連続する処理サイクルにわたって実行される処理から発生する一連のトレース事象を符号化した所定の長さの命令トレースワードを少なくとも1つ含み、前記一連のトレース事象は、

(iv) 前記データ処理回路によるプログラム命令の実行に対応する少なくとも1つのトレース事象と、

(v) 前記データ処理回路によるプログラム命令の実行以外に対応する少なくとも1つのトレース事象と、

を含む、前記データ処理方法。

## 【請求項16】

トレースデータ解析装置であって、

(i) データ処理回路によって連続する処理サイクルにわたって実行される処理から発生する一連のトレース事象を符号化した所定の長さの命令トレースワードを少なくとも1つ含む命令トレースデータに応答するアナライザロジックからなり、前記アナライザロジックは、

(ii) 前記データ処理回路によるプログラム命令の実行に対応する少なくとも1つのトレース事象と、

(iii) 前記データ処理回路によるプログラム命令の実行以外に対応する少なくとも1つのトレース事象と、

を含む一連のトレース事象を表す命令トレースデータを同定する、前記トレースデータ解析装置。

## 【請求項17】

トレースデータ解析方法であって、

(i) データ処理回路によって連続する処理サイクルにわたって実行される処理から発生する一連のトレース事象を符号化した所定の長さの命令トレースワードを少なくとも1つ含む命令トレースデータに応じて、

(ii) 前記データ処理回路によるプログラム命令の実行に対応する少なくとも1つのトレース事象と、

(iii) 前記データ処理回路によるプログラム命令の実行以外に対応する少なくとも1つのトレース事象と、

を含む一連のトレース事象を表す命令トレースワードを同定する、前記トレースデータ解析方法。

## 【請求項18】

トレースデータを解析するコンピュータを制御するためのコンピュータプログラムを有するコンピュータが読み出し可能な記録媒体であって、前記プログラムは、

(i) データ処理回路によって連続する処理サイクルにわたって実行される処理から発生する一連のトレース事象を符号化した所定の長さの命令トレースワードを少なくとも1つ含む命令トレースデータに応じて、

(ii) 前記データ処理回路によるプログラム命令の実行に対応する少なくとも1つのトレース事象と、

(iii) 前記データ処理回路によるプログラム命令の実行以外に対応する少なくとも1つのトレース事象と、

を含む一連のトレース事象を表す命令トレースワードを同定するための実行可能な識別コードを含む、前記記録媒体。

## 【発明の詳細な説明】

## 【0001】

## 【発明の属する技術分野】

本発明はデータ処理システムに関する。より詳細には、本発明はデータ処理回路によって実行中のプログラム命令のトレーシングに関する。

## 【0002】

## 【従来の技術】

データ処理システムの複雑化に伴って、たとえばシステムデバッギング等の一部としてかかるシステムの挙動を分析する包括的で有効なメカニズムを設けることが重要となってきている。さらに、データ処理システムの高速化の結果、通常それに含まれる集積素子の数

10

20

40

50

も増大し、それに伴い、生成されるトレースデータの量およびその生成速度も増大している。

#### 【0003】

データ処理システム用にオンチップトレース装置を設けることが知られており、これは集積回路にその回路の動作をトレースし、トレースデータを転送する、あるいはこのトレースデータをバッファし後に転送するための専用回路を設けるものである。ここで、生成可能なトレースデータの量が大きく、そのトレースデータのバッファリングに要するオンチップメモリの増大および／またはトレース機能に専用のピンの数の増大といった、チップからのトレースデータの送出に要する装置の増大が発生するという制約がある。そこで、生成されるトレースデータの量を低減する対策がきわめて有益となる。

10

#### 【0004】

ある特定の命令が実行されているかどうかを示す命令トレースデータが命令トレースワードで符号化されるシステムを設けることが知られている。これは、分岐命令で終わる順次の命令の実行を符号化することによって行われる。したがって、4つの命令の順次実行の後に分岐命令が続くことの検出がある特定の命令トレースワードを符号化する。

#### 【0005】

##### 【発明が解決しようとする課題】

本発明はデータ処理装置を提供するものであり、前記装置は、

(i) 一連の処理サイクルにわたってプログラム命令に応じたデータ処理動作を実行するデータ処理回路と、

20

(ii) 前記プログラム命令に応じた前記データ処理動作を示す命令トレースデータを生成するトレース回路とからなり、

(iii) 前記命令トレースデータは、前記データ処理回路によって連続する処理サイクルにわたって実行される処理から発生する一連のトレース事象を符号化した所定の長さの命令トレースワードを少なくとも1つ含み、前記一連のトレース事象は、

(iv) 前記データ処理回路によるプログラム命令の実行に対応する少なくとも1つのトレース事象と、

(v) 前記データ処理回路によるプログラム命令の実行以外に対応する少なくとも1つのトレース事象とを含む。

#### 【0006】

30

##### 【課題を解決するための手段】

本発明は、命令トレースワードとしての分岐によって終了する一連の実行を符号化する従来技術には、手書きあるいはコンパイルされたコードに短いループがよく用いられまた、かかるループの最後の分岐間の実行は比較的短いため、命令トレースワードによってこれらのループを圧縮された形態で表現することは非効率的であるという問題があるとの認識に立つものである。この問題に鑑み、本発明は、連続する処理サイクルにわたって実行され、命令の実行に対応する1つ以上のトレース事象とプログラム命令の実行以外のトレース事象に対応する1つ以上のトレース事象とを含む一連のトレース事象を表す命令トレースワードを提供することでこれを解決する。

#### 【0007】

40

一方、他に多くの方法が可能であり、好適な方法の1つとして、プログラム命令の実行に対応する1つ以上のトレース事象と実行されない条件付プログラム命令に対応するトレース事象との組み合わせからなるトレース事象のシーケンスを符号化するという方法がある。これは多くの実在のシステムにおける命令トレース動作を符号化する効率的かつ有効な方法であることがわかっている。

#### 【0008】

実行されない条件付プログラム命令は実行される1つ以上のプログラム命令の前後いずれでもよいことは明らかであるが、本発明の実施例においては、実行されない条件付プログラム命令は実行される1つ以上のプログラム命令の後に続くものとする。これによって、実施が容易となる。

50

**【 0 0 0 9 】**

プログラム命令へのデータ処理回路の応答を現す他の好適な方法として、待ち処理サイクルに対応する1つ以上の命令トレースワードと実行されるプログラム命令に対応するトレース事象との組み合わせからなるトレース事象シーケンスを符号化する命令トレースワードを使用する方法がある。

**【 0 0 1 0 】**

データ処理システムの複雑化、特に多数の異なる機能素子を用いたシステムオンチップ設計が多く用いられるようになった結果、サイクルアキュレート(cycle-accurate)な命令トレーシングを実現しうることが強く求められており、本発明の方法は、かかるサイクルアキュレートなトレーシングを命令トレースワードで効率的に表すことを可能にする。 10

**【 0 0 1 1 】**

かかる符号化は、実行されるプログラム命令に対応するトレース事象が、トレースされる1つ以上の待ちサイクルの後に続くようにすることによって簡単に実施することができる。

**【 0 0 1 2 】**

パイプライン処理システムにおいては、命令パイプライン内の異なる地点で複数のプログラム命令が有効に並列処理される。本発明の実施例では、プログラム命令が処理パイプライン内の所定の位置に到達したとき、そのプログラム命令に対応するトレース事象を処理することによってこれに対処する。

**【 0 0 1 3 】**

これはその命令の取り出し、復号、実行、あるいはパイプラインの他の地点でありうることは明らかである。プログラム命令はパイプライン内の所定の位置に到達した後打ち切られる場合があり、これは命令の実行が実際には完了しなかったことを示すデータを挿入する必要のある実行に対応するものと解釈される。 20

**【 0 0 1 4 】**

特に、パイプライン内でプログラム命令の実行に対応するとみなしうる簡便な位置としては、パイプラインの実行段内におけるそのプログラム命令の実行が開始される位置である。パイプライン内でプログラム命令の実行に対応するとみなしうる簡便な他の位置としては、パイプラインの実行段内におけるそのプログラム命令の実行が終了する位置がある。 30

**【 0 0 1 5 】**

命令トレースデータは他のトレースデータとは別のストリームとして設けることができることは明らかであるが、本発明の実施例ではデータ処理回路によって(たとえば、入力あるいは出力として)処理されるデータ値を示すデータトレースデータを生成し、このデータトレースデータと命令トレースデータとを共通のデータストリーム中でインターリーブする。これには、システムからのトレースデータの転送に要するリソースが低減され、また命令トレースデータをデータトレースデータと相關させることによって、データ処理回路の動作をより詳細に分析しうるという利点がある。

**【 0 0 1 6 】**

データ処理回路は様々な形態をとりうることは明らかであるが、本発明の技術は比較的複雑なプログラム命令と、プロセッサコアに関係付けられたかかる命令への応答とに関するトレースデータの生成に特に適している。 40

**【 0 0 1 7 】**

トレース回路は命令トレースデータを生成後ただちにシステムから直接転送するようにすることができるが、本発明の実施例ではトレース回路は命令トレースデータをバッファするトレースデータメモリを含む。これによってトレースデータを実動速度で迅速に収集することができ、また本発明の技術による命令トレースデータの符号化によれば、かかるトレースデータメモリを効率的に利用することができる。

**【 0 0 1 8 】**

また、本発明はデータ処理方法を提供するものであり、その方法は、

(i) プログラム命令に応じてデータ処理回路の一連の処理サイクルにわたってデータ処 50

理動作を実行し、

(ii) 前記プログラム命令に応じた前記データ処理回路の動作を示す命令トレースデータを生成し、

(iii) 前記命令トレースデータは、前記データ処理回路によって連続する処理サイクルにわたって実行される処理から発生する一連のトレース事象を符号化した所定の長さの命令トレースワードを少なくとも1つ含み、前記一連のトレース事象は、

(iv) 前記データ処理回路によるプログラム命令の実行に対応する少なくとも1つのトレース事象と、

(v) 前記データ処理回路によるプログラム命令の実行以外に対応する少なくとも1つのトレース事象とを含む。

また、上述した命令トレースデータ生成技術を補足する観点から、本発明は生成されたかかるデータを分析するメカニズムおよび技術を提供する。

#### 【0019】

したがって、本発明はまたトレースデータ分析装置を提供し、前記装置は、

(i) データ処理回路によって連続する処理サイクルにわたって実行される処理から発生する一連のトレース事象を符号化した所定の長さの命令トレースワードを少なくとも1つ含む命令トレースデータに応答するアナライザロジックからなり、前記アナライザロジックは、

(ii) 前記データ処理回路によるプログラム命令の実行に対応する少なくとも1つのトレース事象と、

(iii) 前記データ処理回路によるプログラム命令の実行以外に対応する少なくとも1つのトレース事象とを含む一連のトレース事象を表す命令トレースワードを識別する。

#### 【0020】

生成されたトレースデータの分析はまた分析の方法とみなすことができ、適当なコンピュータプログラムの制御のもとに動作する汎用コンピュータを用いて簡便に実行することができる。

#### 【0021】

本発明の上記の目的、特徴および効果、またその他の目的、特徴および効果は以下の実施例の詳細な説明および添付図面から明らかとなろう。

#### 【0022】

##### 【発明の実施の形態】

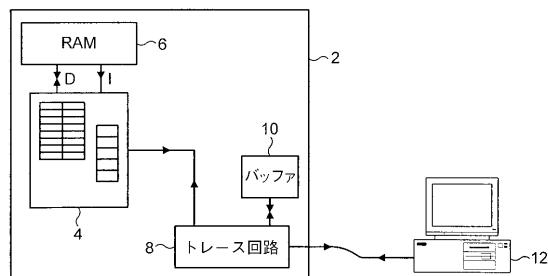

図1はメモリ6に記憶されたプログラム命令を実行するプロセッサコア4を内蔵するシステムオンチップ集積回路2を示す。メモリ6には実行すべきプログラム命令とプロセッサコア4への入力として用いられ、プロセッサコア4からの出力として生成されるデータ値の両方が記憶される。トレーシング回路8はプロセッサコア4および集積回路2の他の部分に関係付けられており、各回路の動作を示すとトレースデータを生成する。かかるトレーシング回路8の一般的機能については、英國ケンブリッジのARM社のETM製品の機能に準じるものとする。かかるETM回路はトレーシングを開始するためのトリガポイント等のオプションや、命令とデータの両方をトレースする機能を有する。本技術は命令トレースデータをかかるシステム内で表現する方法の改良に関する。

#### 【0023】

トレーシング回路8によって生成されるトレースデータは、バッファメモリ10に記憶される。このメモリはトレースデータメモリとして機能し、生成されるトレースデータが適当なインターフェース回路を介して集積回路2から分析コンピュータ12に送出される前に、通常は最高速度でこれを一時記憶する。バッファメモリ10の一般的な動作については、英國ケンブリッジのARM社の埋め込み型トレースバッファ(ETB)製品の提供する機能に準じるものとする。

#### 【0024】

簡略化のため図1には示さないが、集積回路2はシステムオンチップ設計の一部としてその他多くの機能素子を有することは明らかであり、かかる異なる要素の動作を詳細かつ効

率的にトレースすることはシステムオンチップ設計全体の開発およびデバッグにとつて非常に有益である。

#### 【0025】

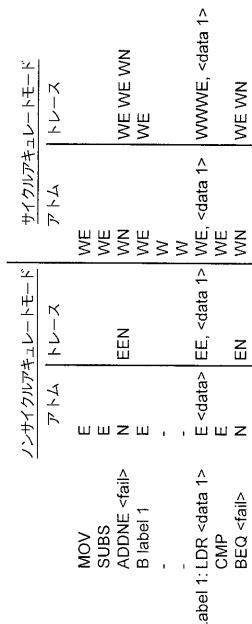

図2はプロセッサコア4によって実行される一連のプログラム命令（この場合ARM命令）を示す。トレーシングはユーザーの条件に応じて、サイクルノンアキュレートモードあるいはサイクルアキュレートモードで実行される。サイクルアキュレートモードは、より多くの情報を生成し、待ち状態が符号化されるように、この情報を表すためにより大きなスペースを要する。

#### 【0026】

命令トレースワードで表される命令処理動作のトレース事象をアトム(atom)と呼び、アトムはさまざまな形態をとりうる。ノンサイクルアキュレートモードでトレースされるアトムは、ある特定の命令が実行されたこと、あるいはある特定の条件付命令がその条件を満たさないために実行されなかったことを示すものである。したがって、図2の例ではMOV命令およびSUBS命令の両方が実行されてE個のアトムが得られ、ADDNE命令は不等条件コードを満たさないため実行されない。2つの命令の実行とそれに続く条件不満足によるADDNE命令の不実行とに対応するトレース事象シーケンスは符号化すべきシーケンスとして取り扱われ、所定の長さの命令トレースワードとして表される。

10

#### 【0027】

その後分岐命令Bが実行され、処理はLDR命令に移行する。LDR命令が実行され、データワード<data1>が転送される。B命令とLDR命令の実行は、これらを複合したデータストリームに埋め込まれたあるデータ事象の発生によって終了する連続する2つの実行として取り扱われる。

20

#### 【0028】

最後の2つの命令は、実行されるCMP命令と実行されないBEQ命令であり、BEQ命令は等条件を満たさず、したがってこの命令が実行されないため分岐が発生する。これらE個およびN個のアトムはシーケンスとして取り扱われ、命令トレースワードENとして符号化される。

#### 【0029】

サイクルアキュレートモードでも同じ命令シーケンスが実行される。このモードのアトムには、ある命令が実行され処理サイクルを消費することを示すWEアトム、ある命令が条件を満足せず実行されないが処理サイクルを消費することを示すWNアトム、およびたとえば多処理サイクル命令のWEアトムに待ちサイクルが設けられることを示すWアトムがある。

30

#### 【0030】

最初の3つの命令はWEWEWNを表す命令トレースワードとして符号化される。分岐命令Bは3つの処理サイクルを消費する。最初のサイクルはWEサイクルであり、それ自体の命令トレースワードとして符号化される。次の2つのサイクルは待ちサイクルであり、次のLDR命令のWEサイクルと組み合わせられ、WWWWEを表す命令トレースワードとして符号化される。最後の2つの命令はWEWNを表す命令トレースワードとして符号化される。

40

#### 【0031】

命令トレースワードの詳細な符号化はさまざまな形態をとりうることは明らかであるが、使用できる符号化の一例を次に説明する。

#### 【0032】

1 P - ヘッダ

1.1 初めに

ここでは、（上述した命令トレースワードを用いた）ETMv3におけるプロトコル変更のすべてを説明する。ETMv3は（英国ケンブリッジのARM社の提供する）ETMv2に対する互換性を有しない。

#### 【0033】

50

p - ヘッダはETMv2パイプスタッフによって現在与えられる情報からなり、他のデータと同じパケットストリームに現れる。その意味を正確に記述するには新たな技術を導入しなければならない。ETMv2中の16のパイプスタッフは以下の情報を表す。

- 命令がいつ実行されるか

- 実行されるそれぞれの命令が条件コードをパスしたか否か

- データがいつFIFOに入れられたか

- 上述の事象がそれぞれどのサイクルで発生したか

- トリガの発生

- トレース捕捉をいつ不能にすべきか

#### 【0034】

10

分岐ファンтомパイプスタッフはあるサイクルで2つの命令が実行されたことを示すものとみなすことができる。

#### 【0035】

ETMv3は不能化されたトリガとトレースを示す代替的なメカニズムを提供する。それらは、ここでの目的上それぞれパイプスタッフとWTに代わるものとみなすべきものである。トレースストリームに現れたデータは常に直近のサイクルまたは命令に対応する。その結果、それに続くデータがあるかどうかを示す必要はなく、したがって残る14のパイプスタッフをさらに7つの可能性に絞り込むことができる。それらは以下の3つのアトムの組み合わせを表すものと見ることができる。

- W : サイクルの境界（すべてのパイプスタッフはこれを表す）

- E : 条件コードをパスした命令

- N : 条件コードを満たさなかった命令

20

#### 【0036】

これらをマッピングすると次のようになる。

| パイプスタッフ    | アトム        |

|------------|------------|

| IE, DE     | <b>WE</b>  |

| IN, DN     | <b>WN</b>  |

| WT, DW     | <b>W</b>   |

| TR, TD     | なし         |

| PTIE, PTDE | <b>WEE</b> |

| PTIN, PTDN | <b>WEN</b> |

| PNIE, PNDE | <b>WNE</b> |

| PNIN, PNDN | <b>WNN</b> |

30

#### 【0037】

40

##### 1.2 エンコード

###### 1.2.1 P - ヘッダの意味

次に、かかるパイプスタッフのシーケンスをこれら3つのアトムのシーケンスとして表すことができる。サイクルアキュレートなトレーシングが要求されない場合、Wアトムを除くことによってよりわかりやすいストリームを生成することができる。この場合、ほとんどの命令が条件コードを満たすため、データトレーシングが不能化される場合、Eのストリングが発生する可能性が高い。データトレーシングがイネーブルされると、トレースストリームへのデータの挿入を可能にするためにこのシーケンスを終了しなければならない。しかし、この場合、データトレースのために生成されるトレース量がいずれにしてもパイプスタッフのトレースを上回る。サイクルアキュレートなトレーシングが要求される場

50

合、連続するサイクルで実行される命令の場合のWEのストリングと同様にWのストリングが発生する可能性が高い。

## 【0038】

## 1.2.2 配置

分岐アドレス以外のETMv2のあらゆるヘッダには、同じサイクルに後続のパケットがあつたか否かを示すCビットが含まれていた。トレースストリームにパイプスタート情報を埋め込むことによって、このビットは不要になる。これによって新たなヘッダを設けるスペースが得られる。新たなヘッダの符号化は次の通りである。

## 【0039】

| 値        | サイクル<br>アキュレート | 新ヘッダ | ペイロード(最大バイト)      | 説明                                                          |

|----------|----------------|------|-------------------|-------------------------------------------------------------|

| Cxxxxxx1 |                | no   | 追加アドレスバイト(4)      | 分岐アドレス                                                      |

| 00000000 |                | yes  | なし(繰り返し)          | A-sync                                                      |

| 00000100 | !cycacc        |      |                   | 予備                                                          |

| 00000100 | cycacc         | yes  | サイクル数(5)          | サイクル数: $1-2^{32} \times W$ (下記)                             |

| 00001000 |                | yes  | 下記(14)            | I-sync                                                      |

| 00001100 |                | yes  | なし                | トリガ                                                         |

| 0TTOSS00 |                | no   | データ(4)            | ロードミスデータ, TT = tag (1-3)                                    |

| 01x10000 |                |      |                   | 予備                                                          |

| 01A1TT00 |                | no   | アドレス(5)           | ロードミス発生, TT = tag (1-3),<br>A = 後続アドレス有り(アドレストレーシング<br>の場合) |

| 00x1xx00 |                |      |                   | 予備                                                          |

| 00AMSS10 |                | no   | アドレス(5)<br>データ(4) | 通常データ, A = 最初のデータパケット<br>(予想アドレス)                           |

| 010xxx10 |                |      |                   | 予備                                                          |

| 01100010 |                | yes  | なし                | データ抑制 (DSup)                                                |

| 01100110 |                | yes  |                   | 無視                                                          |

| 01101010 |                | no   | なし                | 値をトレースせず (VnT)                                              |

| 01101110 |                | no   | コンテキスト ID(4)      | コンテキスト ID                                                   |

| 0111xx10 |                |      |                   | 予備                                                          |

| 1NEEEE00 | !cycacc        | yes  | なし                | フォーマット 1: 0-15xE, 0-1xN                                     |

| 1000FF10 | !cycacc        | yes  | なし                | フォーマット 2: 1x(N/nE), 1x(N/nE) <sup>a</sup>                   |

| 1NOEEE00 | cycacc         | yes  | なし                | フォーマット 1: 0-7x(WE), 0-1xWN                                  |

| 1E1WWW00 | cycacc         | yes  | なし                | フォーマット 3: 1-8xW, 0-1xE                                      |

| 1000FF10 | cycacc         | yes  | なし                | フォーマット 2: 1xW, 1x(N/nE), 1x(N/nE) <sup>a</sup>              |

| 1001xx10 |                |      |                   | 予備                                                          |

| 101xxx10 |                |      |                   | 予備                                                          |

| 11xxxx10 |                |      |                   | 予備                                                          |

<sup>a</sup>: ビット1は最初の命令を表し、ビット2は2番目の命令を表す。

連続するサイクルにおける E のランレンジスはサイクル境界を無視する場合のランレンジスより小さいことが多いため、7つ以上の命令の実行に対応するヘッダースペースが再使用される。W の平均ランレンジスはこれより小さい。

#### 【0040】

##### 1. 2. 3 p - ヘッダの不在

サイクルアキュレートモードでは N で終わる多数の W を有するフォーマットはない。条件コードを満たさない命令はインターロックされそれらと前の命令との間で待ち状態が発生することはない。一般的に条件付命には、一般的に同じ条件コードを有する他の条件付命令か、条件コードを設定する命令のいずれかが先行する。これらは通常 1 サイクルで実行されるデータ処理命令である。

10

その結果、現在のところ、このフォーマットを使用する場合にヘッダースペースが正当化されることは少ないものと見られ、フォーマット 1 で十分である。

#### 【0041】

##### 1. 3 サイクルカウント

サイクルカウント p - ヘッダが設けられ、それに 1 ~ 5 バイトのデータが続く。各バイトのビット 7 の 1 は、分岐アドレスと同様に他のバイトが続くことを示す。このようにして最大で 32 ビットが出力され、不明の高位ビットはいずれも 0 である。この値は W の数である。非周期的な i-sync の後にこのパケットは発生した場合、これはその i-sync の前のトレースストリームにさらに挿入すべき W の数を示す。その後このパケットが発生した場合、他の p - ヘッダと同様に W はその出力ポイントで挿入しなければならない。

20

#### 【0042】

前者は必ず使用しなければならず、トレース領域間のサイクルの数を効率的に出力することができる。後者の使用は任意であり、あるトレース領域内の長いギャップをより効率的にトレースすることが可能となり、またトレース出力を不能化しながら、トレースを再度イネーブルする前に（ロードミスデータ等の）他のパケットを出力することができる。

#### 【0043】

サイクルカウントが 0 である場合、これはカウンタのオーバーフローを示す。この場合、ギャップの長さは不明となる。

#### 【0044】

##### 1. 4 p - ヘッダの生成

30

以下に p - ヘッダの生成規則を示す。これらの規則はアーキテクチャではなく具体化の過程で定義される。p - ヘッダは正しいアトム群にアンパックされるものであればよいが、十分ではない。これは、極端な場合、装置によって 1 サイクル当たり 1 つの p - ヘッダが生成されることを意味するが、それが好適な実施態様とはいえないことに注意しなければならない。下記の規則は ETM10J で実施されるものである。将来の実施においては改良されるものと考えられる。

#### 【0045】

分岐ファンтомとは他の実行される命令と並列する正しく予測された分岐を指し、それによって ETMv2においては P \* パイプスタットが作成される。これは他の命令と並列に実行されない折り返し分岐を指すものではない。

40

#### 【0046】

各サイクルで、ETM は出力される p - ヘッダを計算する。これはただちに出力されるか、あるいは次のサイクルまで保管される。保管される場合、次のサイクルで生成される p - ヘッダはそれに基づくものでなければならず、したがってアトムが失われることはない。

#### 【0047】

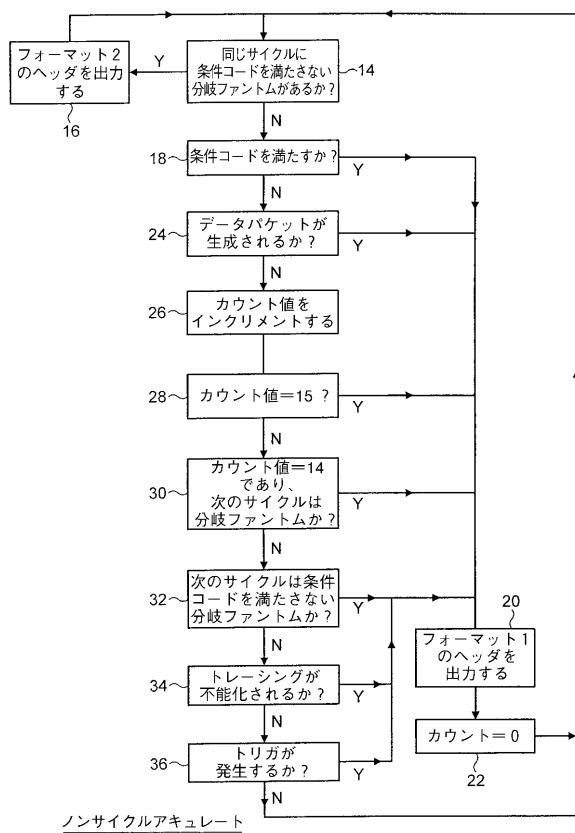

##### 1. 4. 1 ノンサイクルアキュレートモード

あるサイクルで 2 つの命令が実行される（すなわち、分岐ファンтом（phantom）が発生し）、第1の命令が条件コードを満たさない場合、フォーマット 2 が用いられる。これは P N \* パイプスタットに対応する。これ以外のすべての場合にフォーマット 1 が用いられ

50

る。

#### 【0048】

フォーマット2のp - ヘッダは常にただちに出力される。保管されたフォーマット1のp - ヘッダは以下の事象が発生したときに出力される。

- 条件コードを満たさなかった命令が実行される (Nビットがセットされる)

- 他のデータパケットが生成される

- Eのカウント値が15に達する

- Eのカウント値が14に達し、かつ次のサイクルに分岐ファンタムが含まれる

- 次のサイクルに条件コードを満たさない分岐ファンタムが含まれる (P N \*パイプスタッフト)

- トレーシングが不能になる

- トリガが発生する

Eのカウント値が14に達したとき常にフォーマット1のP - ヘッダを出力することが簡便である。

#### 【0049】

次のサイクルに(条件コードを満たさない)分岐ファンタムが含まれるか否かを見るための別途のパイプライン段は、かかる分岐ファンタムをトレースするか否かは問題ではないため不要である。これをトレースしない場合、トレーシングは不能となり、いずれにせよp - ヘッダを出力しなければならない。

#### 【0050】

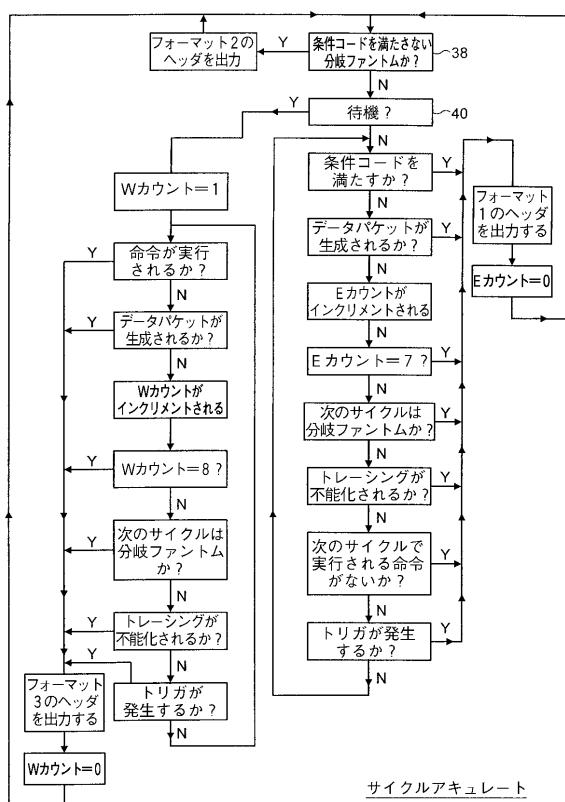

##### 1.4.2 サイクルアキュレートモード

条件コードを満たさない分岐ファンタムが発生した場合、前述したようにフォーマット2が用いられる。1つの命令が実行された場合、フォーマット1が用いられる。命令が実行されない場合、フォーマット3が用いられる。

#### 【0051】

フォーマット2のp - ヘッダは常にただちに出力される。保管されたフォーマット1のp - ヘッダは以下の事象が発生したときに出力される。

- 条件コードを満たさなかった命令が実行される (Nビットがセットされる)

- 他のデータパケットが生成される

- Eのカウント値が7に達する

- 次のサイクルに分岐ファンタムが含まれる (P \*パイプスタッフト)

- トレーシングが不能になる。

- 次のサイクルで命令が実行されない

- トリガが発生する

#### 【0052】

保管されたフォーマット3のp - ヘッダは以下の事象が発生したときに出力される。

- 命令が実行される

- 他のデータパケットが生成される

- Eのカウント値が8に達する

- 次のサイクルに分岐ファンタム (P \*パイプスタッフト) すなわち条件コードを満たさない命令が含まれる。

- トレーシングが不能になる。

- トリガが発生する

#### 【0053】

次のサイクルで実行される命令があるか否かを見るための別途のパイプライン段は、分岐ファンタムを見る場合と同じ理由で不要である。

#### 【0054】

サイクルカウント値は非周期的なi-syncの後にのみ出力される。これは、i-syncの後の最初のサイクルで出力され、かかるサイクルでは他のトレースは出力されない。理論的には他のp - ヘッダと平行して、あるいは分岐アドレス付きで出力されうるが、実施し易いも

10

20

30

40

50

のではない。カウンタ自体はあるトレース領域の最後の p - ヘッダに続くサイクルに 1 (0 ではない) にリセットされる。これによって、カウンタを出力に先立ってリセットすることが不要になる。

#### 【 0 0 5 5 】

##### 1 . 5 同期

同期には、a-sync (アライメント)、i-sync (命令フロー)、およびd-sync (データアドレス) の 3 つの形態がある。適正な同期を行うにはこの 3 つが周期的に発生しなければならない。

#### 【 0 0 5 6 】

##### 1 . 5 . 1 度数

各同期形態は一般にはトレースが出力される n サイクルにつき（すなわち TD サイクルはカウントされない）少なくとも一度は発生しなければならない。n は同期度数レジスタの値である ( $0 \times 78$ )。この実施態様では特殊なケースでは、通常はオーバーフローを防止するために、さらに最大で n サイクル同期が遅れる可能性がある。そのアルゴリズムは実際には実施態様によって定義される。ETM10Jは（トレースが実際に出力されるサイクルだけでなく）トレーシングがイネーブルされている間のすべてのサイクルをカウントするものと考えられ、したがって必要最小限より高い頻度でトレースを出力されるときこの定義に適合する。

#### 【 0 0 5 7 】

これは、ツールがETMv2の場合と同様にポート幅に基づいて同期度数カウンタの値を変化させようとしてすることを意味することに注意しなければならない。これは、ツールはバッファ内にある設定された数の同期ポイントを設けようと考えられ、また幅の狭いポートを用いるより広いポートを用いるときより少ないトレースサイクル数でバッファを満たすことができるためである。

#### 【 0 0 5 8 】

##### 1 . 5 . 2 A - sync (配列同期)

5 つ以上のa-sync p - ヘッダ (00000000) のシーケンスが周期的に出力され、それに 1 つの空白 p - ヘッダ (10000000) が続く。これは、4 7 以上の 0 ビットに 1 が続くストリングと等価である。A-sync (ヌル) バイトは圧縮解除プログラムには通常無視される。

#### 【 0 0 5 9 】

同期をとるには、圧縮解除プログラムはこのシーケンスを探さなければならず、これ以外の方法では発生し得ない。トレース捕捉装置は通常バイトに位置合わせされるが、サブバイトポートは必ずしもそうではない。したがって、圧縮解除プログラムは必要に応じてa-syncシーケンスに続くすべてのデータを位置合わせし直す必要がある。

#### 【 0 0 6 0 】

次のバイトはヘッダであるが、このヘッダは任意のタイプである。すなわち、i-syncヘッダである必要はなく、他の p - ヘッダであってもよい。

#### 【 0 0 6 1 】

たとえば、バイトに合わせたシステムにおいては、a-syncシーケンスとそれに続く単一の E p - ヘッダは 00 00 00 00 80 84 と表すことができる。しかし、捕捉の結果として、この同じシーケンスが 1 ビットポートから 1 ビットずれると、01 00 00 00 00

40 42 と表される。これはポートサイズが 1、2 あるいは 4 ビットである場合には発生せず、トレース捕捉装置はトレースの全実行過程にわたって完全に正確である。しかし、1 サイクルでもあやまって捕捉すると、すなわち TRACECTL ピンの不安定性のために余分なサイクルを捕捉するか 1 サイクルを捕捉しそこなうと、それ以降の捕捉にはすべてそれが生じる。各バイト内で新たに位置合わせを行うことによって、このエラーを局所に限定することができる。また、これによって 3 あるいは 6 ビットといったより一般的でないポートサイズで実施することが可能になる。

#### 【 0 0 6 2 】

##### 1 . 5 . 2 . 1 构造

10

20

30

40

50

47の0ビットのストリングには少なくとも5つの連続するゼロバイトがなければならない。連続するゼロバイトが4つしかない場合、構成しうるゼロビットの最大長はそれらのゼロバイトについては46:32、その周囲の各バイト（それ自体はゼロではない）については7である。したがって。5以上の連続するゼロバイトが生成されないことを証明しなければならない。

#### 【0063】

a-sync以外のゼロバイトが発生しうる場所は次の通りである（そのパケットタイプとともに示す）。

- 命令アドレスの最後のバイト（分岐アドレス、i-sync）

- データアドレスの最後のバイト（通常のデータ、ロードミス発生）

- サイクルカウントの最後のバイト（サイクルカウント）

- データ（通常のデータ、ロードミスデータ）

- コンテキストID（コンテキストID、i-sync）

- LSMアドレス（LSIP i-sync）

10

#### 【0064】

すべてのパケットがヘッダによって分離されなければならないため、単一のパケット内のバイトのシーケンスのみを考慮すればよい。上記のケースには可能な最大長である5バイト以上からなるものはない。上記のリスト中二度以上発生するパケットタイプは2つだけである。そのうち、i-sync中のコンテキストIDは一方の側にi-syncヘッダを、また他の側にi-sync情報バイトを有し、そのどちらのゼロではありえないため放棄することができる。残るのは次の2つのケースである。

20

-通常のデータ：データアドレスの最後のバイトはゼロであり、それにゼロデータが続く。データはゼロである場合圧縮される。圧縮を行うため、ゼロでありうるのはデータの最初のバイトだけであり、したがってこのケースは起こりえない。

-LSIP i-sync：LSMアドレスがゼロであり、それにゼロ分岐アドレスが続く。これは分岐を生じなかつたリセットベクトルのデータ命令を示し、それに他の例外ベクトルからのリセットベクトルへの直接分岐が続く。これが発生する可能性はきわめて低い。さらに、LSMアドレスの前にはそれがLSIPであることを示すようにセットされたビット7を有するi-syncバイトがある。最悪の場合、つまり次のアドレスが空白p-ヘッダ(0x80)である場合、ゼロビットの最大ランが47に減少する（5つのゼロバイトが40、p-ヘッダが7）。これはいずれにせよ有効なa-syncとして機能する。理由はp-ヘッダは無視することができ、トレースはこのシーケンスに位置合わせされていることである。次のヘッダが0x80である場合、ゼロの最大ランは46に減少し、これはa-syncに対しては無効である。したがって、このケースでは偽のa-syncが発生する可能性はない。

30

位置合わせ同期が達成された後は、a-syncバイトは圧縮解除プログラムに無視されるが、6以上の取り消しバイトが必要である場合（8バイトのポートサイズが実施される場合）これらを取り消しバイトとして用いることはできないことに注意しなければならない。したがって、別途の取り消しコードが必要である。空白p-ヘッダをこの目的に用いることができるが、それにかわって圧縮解除エラーの検出を容易にするために0x66が選ばれている。

40

#### 【0065】

##### 1.5.3 i-sync（命令同期）

圧縮解除プログラムはa-syncシーケンスを発見すると、i-syncヘッダを探さなければならぬ。これをまとめると次の通りである。

| 通常の i-sync        | LSiP i-sync       |

|-------------------|-------------------|

| i-sync ヘッダ(1 バイト) | i-sync ヘッダ(1 バイト) |

| コンテキストID(0-4 バイト) | コンテキストID(0-4 バイト) |

| 情報バイト(従来のTFOヘッダ)  | 情報バイト(従来のTFOヘッダ)  |

| 次の命令のアドレス(4 バイト)  | LSM アドレス(4 バイト)   |

|                   | 次命令のアドレス(1-5 バイト) |

10

**【 0 0 6 6 】**

これは以下の点を除いてETMv2におけるTFOパケットと同様である。

- i-sync p - ヘッダの後に来ること

- コンテキストIDは情報バイトの前に来ること(これは、a-sync値が5回連続して発生することを防止するためである)

- 情報バイトがゼロになり、a-syncと競合することを防止するために情報バイトのビット0は常にセットされること

**【 0 0 6 7 】**

ETMv2の場合と異なり、周期的なi-syncパケットが存在することは命令の実行を意味しない。むしろ、i-syncはいつでも発生しうる。命令アドレスは周期的な同期を行う場合にも常に実行すべき次の命令のアドレスを示す(従来は周期的同期は実行中の命令のアドレスを与えるものであった)。

20

**【 0 0 6 8 】**

前述した同期頻度の2倍以内で周期的同期が発生しない場合、オーバーフローが起こる。

**【 0 0 6 9 】****1 . 5 . 4 d-sync (データアドレス同期)**

これはETMv2の場合と同様に5バイトのデータアドレスを検索することによって行われる。

**【 0 0 7 0 】**

30

**1 . 6 他の新しいヘッダ****1 . 6 . 1 トリガ**

トリガが発生すると、必要な他のヘッダとともにトリガヘッダが出力される。TPAは機構を介してトリガを検出する。

**【 0 0 7 1 】****1 . 6 . 2 無効**

無効ヘッダには効果はない。これは、ポート全体を満たすだけのトレースがないときにトレースを出力しなければならない場合にトレースポートの未使用バイトに使用される。

**【 0 0 7 2 】****1 . 7 トレース捕捉装置(TCD)への信号**

40

上述したように、捕捉されたトレースは純粋なビットストリームである。しかし、TCDはこの情報からどのサイクルでデータを捕捉すべきか、またいつトリガが発生するかを判断することはできない。Error! Reference source not foundおよびError! Reference source not found..の項で説明したように、この情報をTRACEDATA[0]と関連づけて有する信号TRACECTLが出力される。

**【 0 0 7 3 】****1 . 8 プログラマのモデルチェンジ**

以下の場所にトレースポートサイズを記述するために3ビットのフィールドが設けられる。

- 制御レジスタのビット6 : 4 - 使用するポートサイズの選択

50

-PORTSIZE出力 - 使用されるポートサイズを示す

**【 0 0 7 4 】**

より幅の広いトレースポートを可能とするために新たな符号化が定義される。

| 値   | 新符号? | ポートサイズ |

|-----|------|--------|

| 000 |      | 4 ビット  |

| 001 |      | 8 ビット  |

| 010 |      | 16 ビット |

| 011 | 新符号  | 24 ビット |

| 100 | 新符号  | 32 ビット |

| 101 | 新符号  | 48 ビット |

| 110 | 新符号  | 64 ビット |

| 111 |      | 予備     |

10

48ビットおよび64ビットのポートはETM10Jによってサポートされない。ある特定の装置の FIFOの幅より大きなポートサイズ(たとえば、ETM7の場合の64ビット)はそのポートサイズがFIFOの幅に等しいことを示す。かかる装置はFIFOを有しない場合もある。

20

**【 0 0 7 5 】**

図3はノンサイクルアキュレートモードにおけるトレーシング回路8の動作の概略を示すフローチャートである。

**【 0 0 7 6 】**

最初にこのモードに入った時、すなわち命令トレースワードを生成したとき、処理はステップ14に進む。このとき考察対象である命令が、同じサイクルにおいて(たとえば分岐予測の結果)他の命令として発生する条件コードを満たさない分岐ファンタムであると考えられる場合、処理がステップ14に戻る前に、ステップ16においてフォーマット2の命令トレースワードの出力がトリガされる。同じサイクルにおける他の命令としての条件コードを満たさない分岐ファンタムが検出されない場合、処理はステップ18に進み、現在考察中の命令が条件コードを満たすか否かのテストが実行される。条件コードを満たさない場合、処理はステップ20に進み、フォーマット1の命令トレースワードが出力され、それに続いてステップ22で実行された命令のカウント値が0にリセットされ、処理はステップ14に進む。ステップ18においてフォーマット1の命令トレースワードの出力がトリガされない場合、処理はステップ24に進み、トレースデータストリームにおけるインターリープを必要とする処理動作によって生成されたデータパケットがあるかどうかが判定される。かかるインターリープが発生すると、これはステップ20において命令トレースワードを出力するためのトリガとして機能する。

30

**【 0 0 7 7 】**

データパケットが生成されていない場合、処理はステップ26に進み、カウント値がインクリメントされる。ステップ28においてカウント値が15に達したか否かが判定される。これはフォーマット1の命令トレースワード中で符号化することのできる最大の値であり、したがって15に達していた場合、ステップ20において命令トレースワードを出力しなければならない。ステップ28においてこの条件が満たされない場合、処理はステップ30に進み、カウント値は現在14であり、次のサイクルが分岐ファンタムであるか否かが判定される。この条件が満たされると、処理はステップ20に進む。次に、ステップ32、34および36が実行され、各ステップは、それに対応する次のサイクルの条件が条件コードを満たさない分岐ファンタムであること、トレーシング動作の不能化、あるいはトレーシングトリガ事象の発生であることを検出すると、フォーマット1の命令トレー

40

50

スワードのトリガとして機能する。ステップ32あるいは34でテストされる事象の1つが発生すると、フォーマット1の命令トレースワードがトリガされるため、後続のテストは実行されないことが理解されよう。

#### 【0078】

全体として見ると、図3の処理は終了事象が発生する前に、すなわちステップ18で条件コードを満たさない命令が見つかる前に（カウント値15で示される）最大で16までの隣接して実行される命令を有效地にカウントする機能を有する。

#### 【0079】

図4はサイクルアキュレートモードでトレース回路8によって実行される処理の概略を示す。ステップ38で条件コードを満たさない分岐ファンタムの初期テストが実行された後、ステップ40でテストが実行され、考察中のサイクルが待ち処理サイクルであるか否かが判定される。待ち処理サイクルである場合、処理は、命令の実行、データパケットの生成、カウント値が8に到達すること、次のサイクルでの分岐ファンタムの発見、トレーシングの不能化、あるいはトリガ事象の発生といった終了事象が発生するまで待ちサイクルWをカウントするループに進み、終了事象が発生すると、フォーマット3の命令トレースワードの出力がトリガされ、待ちサイクルのカウント値は0にリセットされる。

10

#### 【0080】

ステップ40のテストで待ちサイクルが検出されない場合、終了事象が発生するまで実行される命令をカウントするループに入り、終了事象が発生すると、フォーマット1の命令トレースワードが生成され、実行カウント値が0にリセットされる。終了事象は、データパケットの生成、カウント値が7に達すること、次の分岐ファンタムが検出されること、トレーシングの不能化、次のサイクルで命令が実行されないこと、あるいはトリガ事象の発生である。このループはおおむね図3のループと同様であるが、符号化が多少異なり、特に最大実行命令カウント値は、ランを短い長さに制限する3つのビットによってのみ表される。

20

#### 【0081】

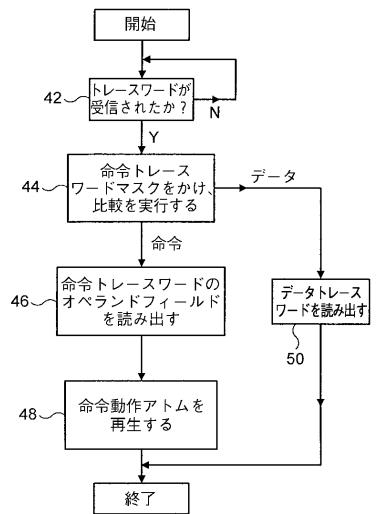

図5は、上述した技術にしたがって（コンピュータ12等で）命令トレースワードを含むトレースデータを解析する際に実行される処理の概略を示すフローチャートである。ステップ42において、システムはトレースデータワードが受信されるまで待機する。ステップ44において、受信されたトレースワードに一連のマスクがかけられ、比較動作が実行されて、そのトレースワードが上述した符号化にしたがった命令トレースワードであるかどうかが識別される。この種の動作は命令の復号と同様であるとみなすことができる。

30

#### 【0082】

ステップ44で命令トレースワードが同定されると、処理はステップ46に進み、その命令トレースワード中のフィールド値が読み出され、ステップ48において、その命令トレースワードによって表され、したがって分析者に利用可能となるべき命令トレース事象動作アトムを再生するのに用いられる。ステップ44でのテストで命令トレースワードが同定されない場合、処理はステップ50に進み、そのトレースワードはデータトレースワードとして取り扱われる。

#### 【0083】

40

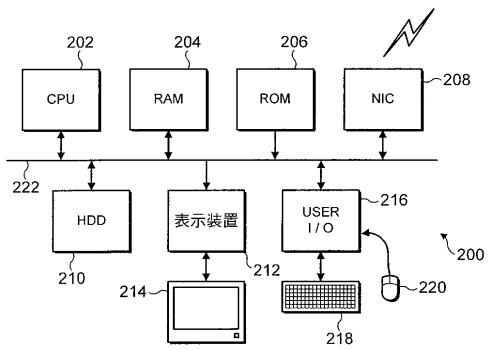

図5の処理はこの方法にしたがって動作する特殊なハードウェアあるいはコンピュータプログラムの制御下で動作する汎用コンピュータによって実行しうることは明らかである。図5に示す処理の実行に使用可能なかかる汎用コンピュータの一例のアーキテクチャを以下に説明する。

#### 【0084】

図6は上述した技術の実施に使用しうるタイプの汎用コンピュータ200の概略を示す。汎用コンピュータ200は中央演算処理装置202、ランダムアクセスメモリ204、リードオンリーメモリ206、ネットワークインターフェースカード208、ハードディスクドライブ210、表示ドライバ212およびモニタ214、およびキーボード218とマウス220を有するユーザー入出力回路216を含み、これらはすべて共通バス222

50

を介して接続されている。動作時において、中央演算処理装置 202 はコンピュータプログラム命令を実行し、それらの命令はランダムアクセスメモリ 204、リードオンリーメモリ 206、ハードディスクドライブ 210 のうち 1 つ以上に記憶されるか、あるいはネットワークインターフェースカード 208 を介して動的にダウンロードされる。この処理の実行結果は表示ドライバ 212 およびモニタ 214 を介してユーザーに表示することができる。汎用コンピュータ 200 の動作を制御するためのユーザー入力は、キーボード 218 あるいはマウス 220 からユーザー出力回路 216 を介して受信することができる。コンピュータプログラムはさまざまなコンピュータ言語で記述しうることは明らかである。コンピュータプログラムは記録媒体で記憶および分配するか、汎用コンピュータ 200 に動的にダウンロードすることができる。適当なコンピュータプログラムの制御下で動作しているとき、汎用コンピュータ 200 は上述した技術を実行することができ、上述した技術を実行する装置を形成するとみなすことができる。この汎用コンピュータ 200 のアーキテクチャにはかなりの変更が可能であり、図 6 は一例に過ぎない。

10

#### 【0085】

本発明の実施例を添付図面を参照して詳細に説明したが、本発明はこれら詳細な実施例には限定されることは明らかであり、特許請求の範囲に述べる本発明の範囲および要旨から逸脱することなくさまざまな変更が可能である。

#### 【図面の簡単な説明】

【図 1】生成されるトレースデータを解析する汎用コンピュータに接続された、プログラム命令に応答するデータ処理回路およびオンチップトレーシング回路を含むデータ処理装置の概略図である。

20

【図 2】一連のプログラム命令と、かかる命令をノンサイクルアキュレートモードおよびサイクルアキュレートモードの両方で命令トレースワードに符号化する方法を示す。

【図 3】ノンサイクルアキュレートモードにおけるトレーシング回路の符号化動作の概略を示すフローチャートである。

【図 4】サイクルアキュレートモードにおけるトレーシング回路の符号化動作の概略を示すフローチャートである。

【図 5】命令トレースワードを含むトレースデータの解析の概略を示すフローチャートである。

【図 6】図 5 の解析技術の実施に用いることのできる汎用コンピュータのアーキテクチャの概略図である。

30

#### 【符号の説明】

- 2 集積回路

- 4 プロセッサコア

- 6 ランダムアクセスメモリ

- 8 トレース回路

- 10 バッファ

- 12 分析コンピュータ

- 202 中央演算処理装置

- 204 ランダムアクセスメモリ

- 206 リードオンリーメモリ

- 208 ネットワークインターフェースカード

- 210 ハードディスクドライブ

- 212 表示ドライバ

- 214 モニタ

- 216 ユーザー入出力回路

- 218 キーボード

- 220 マウス

【図1】

【図2】

( 3 )

〔 4 〕

【図5】

【図6】

---

フロントページの続き

(72)発明者 アンドリュー ブルックフィールド スウェイン

イギリス国 ウェルワイン ガーデン シティ、ターモア デイル 29

審査官 多胡 滋

(56)参考文献 特開2002-149442 (JP, A)

特開2000-194581 (JP, A)

特開2000-163281 (JP, A)

特開2000-003295 (JP, A)

特開平11-353205 (JP, A)

特開平05-298144 (JP, A)

特開平03-025631 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G06F 11/28

G06F 11/36