(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2015-22363

(P2015-22363A)

(43) 公開日 平成27年2月2日(2015.2.2)

(51) Int.Cl.

**G06F 3/12 (2006.01)**

**G06F 13/28 (2006.01)**

**B41J 5/30 (2006.01)**

F 1

GO 6 F 3/12

GO 6 F 13/28

B 4 1 J 5/30

B

3 1 O E

Z

テーマコード(参考)

2 C 1 8 7

5 B 0 6 1

審査請求 未請求 請求項の数 5 O L (全 17 頁)

(21) 出願番号

(22) 出願日

特願2013-147907 (P2013-147907)

平成25年7月16日 (2013.7.16)

(71) 出願人 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100126240

弁理士 阿部 琢磨

(74) 代理人 100124442

弁理士 黒岩 創吾

(72) 発明者 中村 宏典

東京都大田区下丸子3丁目30番2号キヤ

ノン株式会社内

F ターム(参考) 2C187 AC02 AC08 AF03 BF14 BG06

BG08 DB28 FC07 FC08

5B061 DD01

(54) 【発明の名称】データ転送制御装置、データ転送制御方法、及びプログラム

## (57) 【要約】

【課題】 メモリの使用量の増大を抑制しつつ、複数のメモリ領域に分割されたデータを一連のデータとして転送可能なデータ転送制御装置、データ転送制御方法及びプログラムを提供することを課題とする。

【解決手段】 第1メモリ領域と第2メモリ領域を含む複数のメモリ領域に亘って格納される複数ラインからなる入力データの処理部への転送を制御する際に、前記処理部から出力される複数ラインからなる出力データのうち出力したい着目ラインの位置を特定し、特定された着目ラインの位置に応じて、前記第1のメモリ領域から転送する入力データのライン数及びそのアドレスを決定すると共に、前記第2のメモリ領域から転送する入力データのライン数及びそのアドレスを決定する。その決定に基づいて、前記第1のメモリ領域から所定のライン数の入力データを転送せると共に前記第2のメモリ領域から所定のライン数の入力データの転送を転送させるよう制御する。

【選択図】 図5

**【特許請求の範囲】****【請求項 1】**

第1メモリ領域と第2メモリ領域を含む複数のメモリ領域に亘って格納される複数ラインからなる入力データの処理部への転送を制御するデータ転送制御装置であって、

前記処理部から出力される複数ラインからなる出力データのうち出力対象の着目ラインの位置を特定する特定手段と、

前記特定手段により特定された着目ラインの位置に応じて、前記第1のメモリ領域から転送する入力データのライン数及びそのアドレスを決定すると共に、前記第2のメモリ領域から転送する入力データのライン数及びそのアドレスを決定する決定手段と、

前記決定手段の決定に基づいて、前記第1のメモリ領域から所定のライン数の入力データを転送させると共に前記第2のメモリ領域から所定のライン数の入力データの転送を転送させるように制御する制御手段と、

を備えることを特徴とするデータ転送制御装置。

**【請求項 2】**

前記決定手段の決定に基づいて、前記第1のメモリ領域から転送する入力データのライン数を特定する情報を格納する第1格納手段と、

前記決定手段の決定に基づいて、前記第1のメモリ領域から転送する入力データの先頭アドレスを特定する情報を格納する第2格納手段と、

前記決定手段の決定に基づいて、前記第2のメモリ領域から転送する入力データのライン数を特定する情報を格納する第3格納手段と、

前記決定手段の決定に基づいて、前記第2のメモリ領域から転送する入力データの先頭アドレスを特定する情報を格納する第4格納手段と、

前記特定手段により特定された着目ラインの位置に応じて、前記第1格納手段、前記第2格納手段、前記第3の格納手段、及び／又は前記第4の格納手段の更新を行う更新手段と、

を備えることを特徴とする請求項1に記載のデータ転送制御装置。

**【請求項 3】**

前記決定手段は、前記処理部が前記入力データに対して変倍処理を行う場合、前記特定手段により特定された着目ラインの位置及び変倍率に基づいて、前記第1のメモリ領域から転送する入力データのライン数及びそのアドレスを決定すると共に、前記第2のメモリ領域から転送する入力データのライン数及びそのアドレスを決定することを特徴とする請求項1又は2に記載のデータ転送制御装置。

**【請求項 4】**

前記入力データのうち所定の処理単位の入力データにおける有効データがないラインを特定する情報を取得する取得手段を備え、

前記特定手段は、前記取得手段により取得した情報を、前記特定手段により特定された着目ラインの位置に応じて、前記第1のメモリ領域から転送する入力データのライン数及び／又は前記第2のメモリ領域から転送する入力データのライン数を変更することを特徴とする請求項1～3のいずれか一項に記載のデータ転送制御装置。

**【請求項 5】**

第1メモリ領域と第2メモリ領域を含む複数のメモリ領域に亘って格納される複数ラインからなる入力データの処理部への転送を制御するデータ転送制御方法であって、

前記処理部から出力される複数ラインからなる出力データのうち出力対象の着目ラインの位置を特定する特定工程と、

前記特定工程により特定された着目ラインの位置に応じて、前記第1のメモリ領域から転送する入力データのライン数及びそのアドレスを決定すると共に、前記第2のメモリ領域から転送する入力データのライン数及びそのアドレスを決定する決定工程と、

前記決定工程の決定に基づいて、前記第1のメモリ領域から所定のライン数の入力データを転送させると共に前記第2のメモリ領域から所定のライン数の入力データの転送を転送させるように制御する制御工程と、

10

20

30

40

50

を備えることを特徴とするデータ転送制御方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、データの転送を行うデータ転送制御装置、データ転送制御方法及びプログラムに関し、より具体的には、着目ラインの処理に際して周辺ラインを参照するような処理を行う際に好適なデータ転送制御装置、データ転送制御方法及びプログラムに関する。

【背景技術】

【0002】

プリンタ等の画像形成装置においては、ホストPCから多値画像データを受信して、その画像データに対して周辺画素を参照する画像処理を含めたデータ処理を施した後、所定の媒体（例えば、紙、印画紙、ハガキ等）に画像を形成するものが知られている。周辺画素を参照する画像処理とは、着目画素に対して上下左右等に配置される他の参照画素の内容に基づき処理内容を決定する画像処理のことである。例えば、多値画像データを拡大する拡大処理や、多値画像データに対して先鋭化処理を施すUSM（アンシャープマスク）処理などが挙げられる。また、画像形成装置では、受信した画像データを複数のライン単位で複数のバッファへ分割して格納したり、リングバッファのようにメモリ領域の下限へ達したらメモリ領域の先頭に格納するなど、一連の画像データを分割して格納するものがある。データを分割して格納する場合、受信した画像データを格納中のメモリ領域以外のメモリ領域を用いて画像処理を実施できるため、データの受信と画像処理は並列に実施することができる。

10

20

30

【0003】

このとき、参照画像データの格納場所が分割されていた場合、一連の画像データであるかのように分割された複数の格納先からそれぞれ画像データを読み込み、画像処理部に供給する必要があった。

【0004】

そこで、特許文献1には、2つのメモリアドレスを設定し、1つ目のアドレスから転送を開始して転送が終了したと判断すると、2つ目のアドレスから転送を再開する方法が開示されている。このような手法を用いれば、画像データが複数のメモリ領域に分割されても一連の画像データとして転送することが可能になる。

30

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開平8-166921号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、特許文献1に記載のデータ転送方法は、一度だけ途中で転送アドレスを切り替えるものであるため、分割して格納されている画像データを何度も一連の画像データとして転送することが必要な場合には対応できない。したがって、例えば、画像データを複数ラインごとに分割して複数のバンドを生成し、バンドごとにバンド処理を行う場合、1バンド内で何度もメモリ領域を切り替えることになるが、メモリ領域を切り替えるたびにデータ転送のパラメータの再設定が必要となる。

40

【0007】

そこで、メモリ領域の境界にオーバーラップ領域を設けて、途中で画像データが途切れないようにオーバーラップ領域に画像データを配置する手法も考えられる。しかしながら、オーバーラップ領域のために余分なメモリの確保が必要であるという問題がある。また、対象となる画像データを一のメモリ領域から他のメモリ領域のオーバーラップ領域へコピーするコピー処理が必要であり、コピー処理のためのメモリアクセスによるCPUへの

50

負荷も問題となる。

【0008】

本発明は、上述した事情に鑑み、メモリの使用量の増大を抑制しつつ、複数のメモリ領域に分割されたデータを一連のデータとして転送可能なデータ転送制御装置、データ転送制御方法及びプログラムを提供することを目的とする。

【課題を解決するための手段】

【0009】

上記課題を解決する本発明の画像処理装置は、第1メモリ領域と第2メモリ領域を含む複数のメモリ領域に亘って格納される複数ラインからなる入力データの処理部への転送を制御するデータ転送制御装置であって、前記処理部から出力される複数ラインからなる出力データのうち出力対象となる着目ラインの位置を特定する特定手段と、前記特定手段により特定された着目ラインの位置に応じて、前記第1のメモリ領域から転送する入力データのライン数及びそのアドレスを決定すると共に、前記第2のメモリ領域から転送する入力データのライン数及びそのアドレスを決定する決定手段と、前記決定手段の決定に基づいて、前記第1のメモリ領域から所定のライン数の入力データを転送させると共に前記第2のメモリ領域から所定のライン数の入力データの転送を転送させるように制御する制御手段と、を備えることを特徴とする。

10

【発明の効果】

【0010】

本発明によれば、出力対象の着目ライン位置を特定し、その位置に応じて複数のメモリ領域のどの位置からデータを参照するかを制御することで、複数のメモリ領域に分割されたデータを一連のデータとして容易に供給することができる。

20

【画面の簡単な説明】

【0011】

【図1】実施形態1に係る記録装置のコントローラ部の概略構成図である。

30

【図2】実施形態1に係るデータ処理部の内部構成図である。

【図3】実施形態1における拡大処理を施す際の参照画像と着目画像を説明する図である。

【図4】実施形態1におけるバッファ境界におけるバンド単位での拡大処理の説明図である。

30

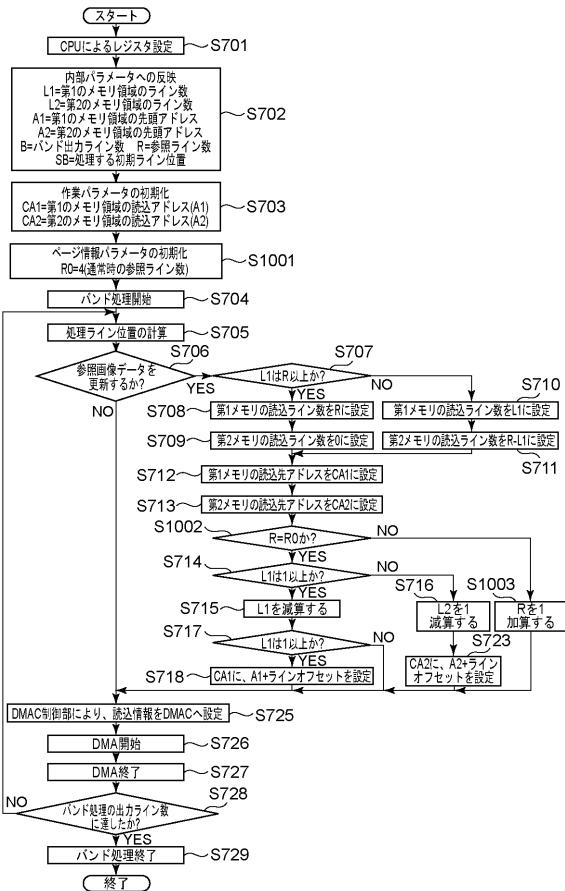

【図5】実施形態1におけるデータ処理部407の制御フローチャートを示す図である。

【図6】実施形態1における画像データを処理する際にメモリから読み出すライン数及び読み出し時の先頭アドレスの位置を示す図である。

【図7】実施形態2におけるバッファ境界におけるバンド単位での拡大処理の説明図である。

40

【図8】実施形態2におけるデータ処理部407のデータ供給時のライン管理の制御フローチャートを示した図である。

【図9】実施形態2における画像データを処理する際にメモリから読み出すライン数及び読み出し時の先頭アドレスの位置を示す図である。

【発明を実施するための形態】

【0012】

以下、図面を参照して本発明の実施形態を詳細に説明する。なお、以下の実施の形態は特許請求の範囲に係る本発明を限定するものでない。

【0013】

(実施形態1)

本実施形態では、データ転送制御装置として、インクジェット記録装置(以下、記録装置)を例に挙げて実施形態を説明する。

【0014】

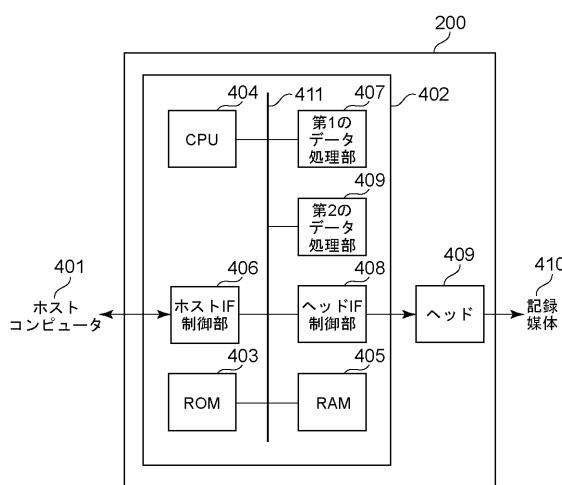

図1は、本発明の実施形態1に係る記録装置の構成の一例を示すブロック図である。

【0015】

50

本実施形態に係る記録装置 200 は、コントローラ 402 と、ヘッド 410 と、を備えており、外部のホストコンピュータ 401 と接続可能となっている。

【0016】

コントローラ 402 は、記録装置 200 の制御を行う制御装置である。コントローラ 402 は、ROM 403 と、CPU 404 と、RAM 405 と、ホストIF制御部 406 と、第1のデータ処理部 407 と、ヘッドIF制御部 408 と、第2のデータ処理部 409 と、を備えている。また、これらは共有バス 411 で接続されている。この共有バス 411 を通じて、接続されたもの同士で通信が可能となる。

【0017】

ROM 403 は、記録装置 200 を制御するためのプログラムを格納している読み出しが可能なメモリである。CPU 404 は、ROM 403 に格納されたプログラムを実行することにより記録装置 200 の制御を行う。

10

【0018】

RAM 405 は、プログラムの実行領域や画像データ等のデータの格納領域として使用される読み書き可能なメモリである。また、本実施形態に係る RAM 405 は、複数のバッファを有し、バッファ毎にメモリ領域が分割される構成になっており、画像データを格納する際に各バッファへ画像データの一部を複数のライン単位で分割して格納する。このため、一連の画像データは、バッファの境界で RAM 405 のメモリアドレス上で分割される。RAM 405 は、例えば、ホストデータ受信用バッファ、拡大処理参照用バッファ、拡大処理後格納用バッファ、低階調化処理用バッファを備えるものとし、バッファ単位で処理内容を独立させる。RAM 405 をこのような構成とすることにより、排他的にメモリアクセスすることが可能となり、全体の処理を効率よく実行することができる。なお、以下、バッファの先頭アドレスと最終アドレスを「メモリアドレスの境界」とし、参照アドレスを、あるバッファの最終アドレスから他方のバッファの先頭アドレスに切り替えることを「メモリアドレスの境界を跨ぐ」と記載する。また、RAM 405 内の複数のバッファを第1のメモリ領域、第2のメモリ領域と記載するが、異なる RAM 405 ではない。

20

【0019】

ホストIF制御部 406 は、ホストコンピュータ 401 との通信を行い、印刷ジョブ等のデータの受信などを行い、受信したデータを RAM 405 へ格納する。本実施形態では、ホストIF制御部 406 が受信する印刷ジョブに含まれる画像データは、1画素が R, G, B の3色で表され、1色の階調が8ビットである多階調の画像データ（以下、画像データ）とする。

30

【0020】

第1のデータ処理部 407 は、印刷ジョブに含まれる印刷条件に従って RAM 405 に格納された画像データを変倍する処理を行う。本実施形態では、変倍処理として、画像データを拡大する処理を行う。第1のデータ処理部 407 で拡大された画像データは、RAM 405 へ格納される。

【0021】

第2のデータ処理部 409 は、印刷ジョブに含まれる印刷条件に従って RAM 405 に格納された拡大された画像データから、インク色の画像データを生成する処理を行う。本実施形態では、多値の R, G, B データを多値の C (シアン), M (マゼンタ), Y (イエロー), K (ブラック) のインク色に変換して、インク色の画像データを生成する。さらに、インク色の画像データから記録装置 200 が印刷に用いる印刷可能な2値画像データを生成する低階調化処理を行い、生成された2値画像データは RAM 405 へ格納される。

40

【0022】

ヘッドIF制御部 408 は、RAM 405 に格納された2値画像データをヘッド 410 に出力する。

【0023】

50

ヘッド 410 は、2 値画像データに基づいて被記録媒体 420 にインクを付与して画像を記録する。

【0024】

ホストコンピュータ 401 は、印刷するために必要な画像データ情報や印刷条件情報を含む印刷ジョブの作成等を行う情報処理装置である。

【0025】

本実施形態に係るシリアル型の記録装置(200)は、記録ヘッドが主走査方向に一定の速度で移動するキャリッジに搭載され、上記一定の速度に対応した周波数でインクを滴として吐出して記録用紙等の被記録媒体に印字する。1回の記録主走査が終了するごとに、被記録媒体は、主走査方向の垂直向きの副走査方向に所定の量だけ搬送される。このような記録主走査と搬送動作とを間欠的に繰り返すことにより、被記録媒体に段階的に画像が記録される。なお、記録ヘッドには、それぞれのインクを吐出するための複数の記録素子によって構成されている。コントローラ 402 は、このような動作を制御する。

10

【0026】

ここで、第 1 のデータ処理部 407 の内部構成について詳細に説明する。

【0027】

本実施形態では、第 1 のデータ処理部 407 は、拡大処理を実行する際にはバイキューピック法により拡大処理を実行する。ここで、バイキューピックアルゴリズムによる拡大処理について簡単に説明する。バイキューピックアルゴリズムは、出力対象の画素を「着目画素」とした場合、その着目画素の位置を中心に周辺の 16 点 ( $4 \times 4$  マトリクス) の画素を参照して(以下、参照画素ともいう)、着目画素の画素値を決定するアルゴリズムである。この  $4 \times 4$  マトリクスの参照画素の位置を着目画素に応じて移動させていくことで、元の画像データを拡大させることができる。すなわち、バイキューピックアルゴリズムでは、1 ラインの画素を出力するために、4 ラインの画素を参照する。

20

【0028】

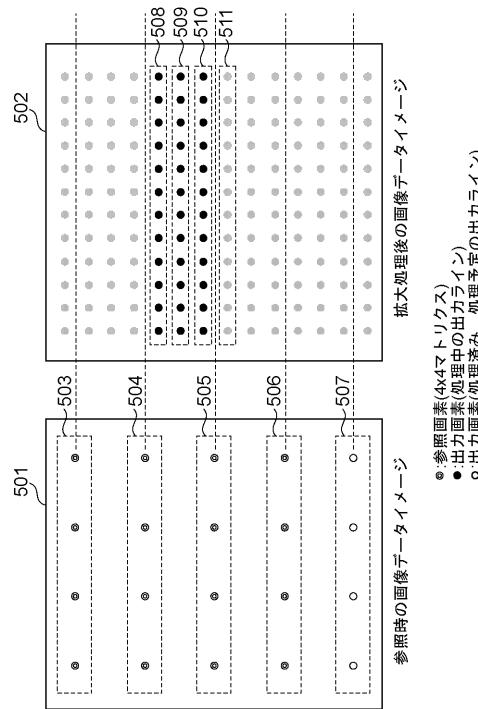

図 3 は、拡大処理時のイメージを示した図である。本実施形態では、拡大率 3 倍で拡大処理を行う場合について説明する。図 3 に示す画像データイメージ 501 は、着目画素が参照する  $4 \times 4$  マトリクスの参照画素の位置を示した図であり、画像データイメージ 502 は、参照画素を参照して拡大処理した際の拡大処理結果(出力結果)を示した図である。

30

【0029】

拡大処理では、まず、着目画素の画素位置を決定し、それに対応した参照画素の位置を決定する。着目画素の画素位置とは、出力したい画素の位置を指す。本実施形態では、着目画素をライン単位とし、以下、ライン単位の着目画素を「着目ライン」又は「処理ライン」という。まず、画像データイメージ 502 のライン位置 508 を着目ラインとする。そして、着目ラインの位置(ライン位置 508)が、画像データイメージ 501 のライン位置 504 と 505 の間であるため、参照する画素データのライン位置は 503, 504, 505, 506 になる。すなわち、この 4 ライン(503, 504, 505, 506)を参照して、1 ライン(ライン位置 508)の出力画素が生成されることになる。本実施形態では、拡大率が 3 倍であるため、画像データイメージ 502 のライン位置 509 の画素を着目画素とした場合及びライン位置 510 の画素を着目画素とした場合も同様に、画像データイメージ 502 のライン位置 504 と 505 の間である。したがって参照する画像データのライン位置は、ライン位置 508 の場合と同じとなる。次に、ライン位置 511 を着目ラインとした場合は、画像データイメージ 501 のライン 505 と 506 の間になるため、参照する画像データのライン位置は 504, 505, 506, 507 になる。このようにして、処理する着目画素のライン位置に応じて、参照するライン位置が変わっていく。本実施形態では、バンド単位で処理を行うため、バンド内で参照ライン位置が更新されていく。なお、RAM 405 が上述した複数のバッファ構成であると、バンド処理の途中で参照するバッファが切り替わることから、着目ラインの位置によっては、参照ライン位置がメモリアドレスの境界を跨ぐことがある。

40

50

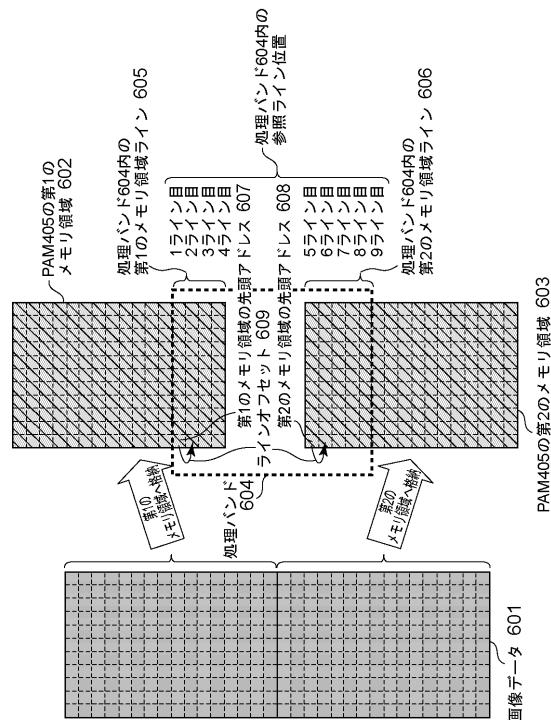

## 【0030】

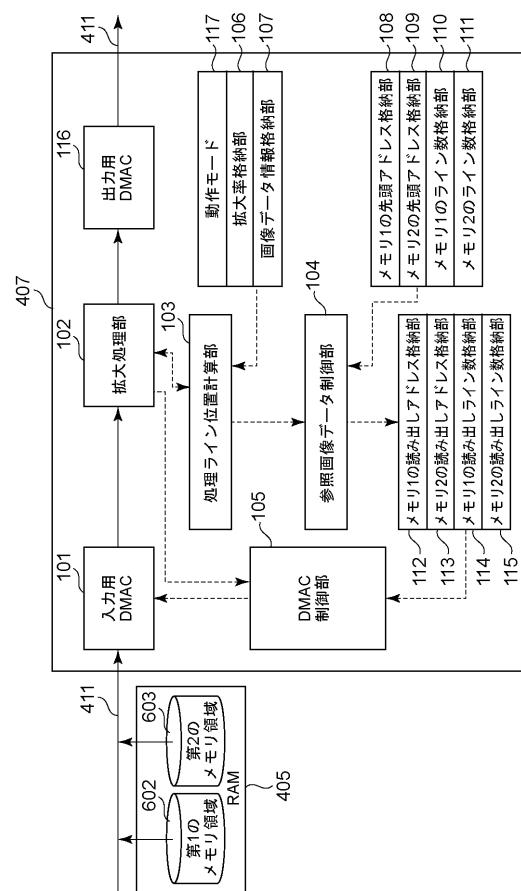

図2は、第1のデータ処理部407の内部構成を示すブロック図である。本実施形態では、拡大処理で参照する多値画像データが格納される複数のバッファを2つとし、その2つのバッファはそれぞれRAM405内の第1のメモリ領域602と第2のメモリ領域603とする。

## 【0031】

入力用DMAC101は、DMAC制御部105からの指示に従って、RAM405から参照する画像データ(入力データ)を読み出して、拡大処理部102へ供給するDMACである。拡大処理部102は、参照する画像データをバイキューピックアルゴリズムにより指定された倍率に拡大する処理を行い、生成された拡大後の画像データを出力用DMAC116へ送信する。出力用DMAC116は、拡大後の画像データ(出力データ)を共有バス411を介してRAM405へ書き込む。

10

## 【0032】

拡大率格納部106は、拡大処理における倍率値(拡大率)を格納する。画像データ情報格納部107は、後述する処理バンドで処理を行う着目ライン位置の初期ライン位置を格納する。動作モード117には、拡大処理で用いる拡大アルゴリズムに応じたモードが設定される。本実施形態では、バイキューピックの動作モードが設定される。これらには、バンド処理を開始する前に、パラメータが設定される。

## 【0033】

メモリ1の先頭アドレス格納部108は、着目ラインが第1のメモリ領域602におけるバンド内で参照する先頭画素のメモリアドレス値を格納する。メモリ1のライン数格納部110は、着目ラインが第1のメモリ領域602におけるバンド内で参照するライン数を格納する。メモリ2の先頭アドレス格納部109は、着目ラインが第2のメモリ領域におけるバンド内で参照する先頭画素のメモリアドレス値を格納する。メモリ2のライン数格納部111は、着目ラインが第2のメモリ領域におけるバンド内で参照するライン数を格納する。拡大率格納部106、画像データ情報格納部107、メモリ1の先頭アドレス格納部108、メモリ2の先頭アドレス格納部109、メモリ1のライン数格納部110、メモリ2のライン数格納部111は、バンド処理が開始される前にCPU404により設定される。

20

## 【0034】

処理ライン位置計算部103は、CPU404からバンド処理スタートの通知を受信すると、拡大率格納部106から拡大率を取得して、拡大処理を行う着目画素の位置(以下、着目ライン位置ともいう)を決定する。すなわち、バンド処理が開始すると、拡大率と処理を開始する着目画素の座標位置から処理するライン位置を算出する。

30

## 【0035】

参照画像データ制御部104は、算出された着目ライン位置と、格納部108、109、110、111と、の情報に基づいて、画像データのいずれのライン位置を参照するかの情報を生成する。この参照画像データ制御部104は、着目ラインの位置に基づいて、参照する画像データの読み出しアドレスや読み出すライン数を決定する。具体的には、第1のメモリ領域602から読み出す先頭アドレス値をメモリ1の読み出しアドレス格納部112へ格納し、第1のメモリ領域602から読み出すライン数をメモリ1の読み出しライン数格納部114へ格納する。同様に、第2のメモリ領域603から読み出す先頭アドレス値をメモリ2の読み出しアドレス格納部113へ格納し、第2のメモリ領域603から読み出すライン数をメモリ2の読み出しライン数格納部115へ格納する。参照画像データ制御部104は、処理ライン位置が変更される度に、格納部112～115の値を更新する。

40

## 【0036】

DMAC制御部105は、格納部112、113、114、115の情報に基づいて、入力用DMACに第1のメモリ領域602のいずれから何ラインを読み出すかを指示し、同様に第2のメモリ領域603のいずれから何ラインを読み出すかを指示する。このDM

50

A C 制御部 105 は、着目画素のライン位置（処理ライン位置）が変わるたびに、格納部 112～115 の内容を取得し、それに基づき読み出し開始位置と読み出し量とを DMA C 101 へ設定し、DMAC 101 へ読み出しスタートを指示する。

【0037】

図 4 は、本実施形態におけるバンド単位での拡大処理の説明図である。本実施形態では、多値画像データの一部である 64 ライン分の画像データ 601 を 32 ラインずつに分けて、それぞれ RAM 405 の第 1 のメモリ領域 602 と第 2 のメモリ領域 603 に配置する。本実施形態では、拡大処理による拡大率は 3 倍（300%）とし、1 バンドで出力するバンドライン数を 16 ラインとする。1 バンドで出力するバンドライン数を 16 ライン固定として、複数のバンド単位で拡大処理をしていくと、次のバンドで参照する画像データの先頭ライン位置は、 $16 \text{ ライン} \div 3 \text{ 倍} = 5.3 \text{ ライン}$  となる。すなわち、次のバンドで参照する画像データの先頭ライン位置は、現在のバンドで参照する画像データの先頭ライン位置と比較して 5 ライン又は 6 ラインインクリメントする。したがって、拡大率が 3 倍の場合、バンド内のいずれのラインでバッファの境界（メモリアドレスの境界）を跨ぐことになるかは固定されない。すなわち、拡大率が 3 倍である場合、バッファを跨ぐ場合とバッファを跨がない場合があり、さらに、跨ぐ時のライン位置が毎回変わる。そのため、本実施形態のような拡大処理の処理位置を算出してその都度参照する画像データのライン位置を算出する必要がある。なお、1 バンドで出力するバンドライン数が 16 ライン固定の場合、倍率が奇数であれば同様である。さらに言えば、16 ライン固定ではない場合であっても、（出力バンドライン数） $\div$ （拡大率）の値が整数ではない場合は、バンド内のどのラインでバッファの境界を跨ぐことになるかは固定されない。

【0038】

ここで、複数のバンドのうち処理バンド 604 を例に挙げて、バッファ境界におけるライン位置の拡大処理について説明する。処理バンド 604 が参照する画像データのライン数は、（出力ライン数  $\div$  倍率） $+ (各ラインの参照ライン数) - 1$  で求められる。したがって、本実施形態では、 $16 \text{ (ライン)} \div 3 \text{ (倍)} + 4 - 1 = 8.3$  となり、処理バンド 604 内で参照するライン数は、切り上げた 9 ラインとなる。その 9 ラインうち、上の 4 ラインは第 1 のメモリ領域 602 に含まれるライン（605）で、下の 5 ラインは第 2 のメモリ領域 603 に含まれるライン（606）となる。すなわち、メモリアドレス上で連続していないのは、処理バンド 604 内の 4 ライン目と 5 ライン目となる。図 4 において、607 は処理バンド 604 が第 1 のメモリ領域で参照するラインのうち先頭ラインの先頭画素のアドレスであり、以下、「処理バンド 604 の第 1 のメモリ領域の先頭画素アドレス」とする。また、608 は処理バンド 604 が第 2 のメモリ領域で参照するラインのうち先頭ラインの先頭画素のアドレスであり、以下、「処理バンド 604 の第 2 のメモリ領域の先頭画素アドレス」とする。

【0039】

609 はライン毎の左端画素のアドレスの差を示したアドレス値であり、以下、「ラインオフセット」とする。また、処理バンド 604 における着目ライン位置の初期ライン位置は、倍率が 3 倍であるため、図 3 の 508、509、510 を選択でき、いずれを選択してもよいが、本実施形態では初期ライン位置を 508 とする。

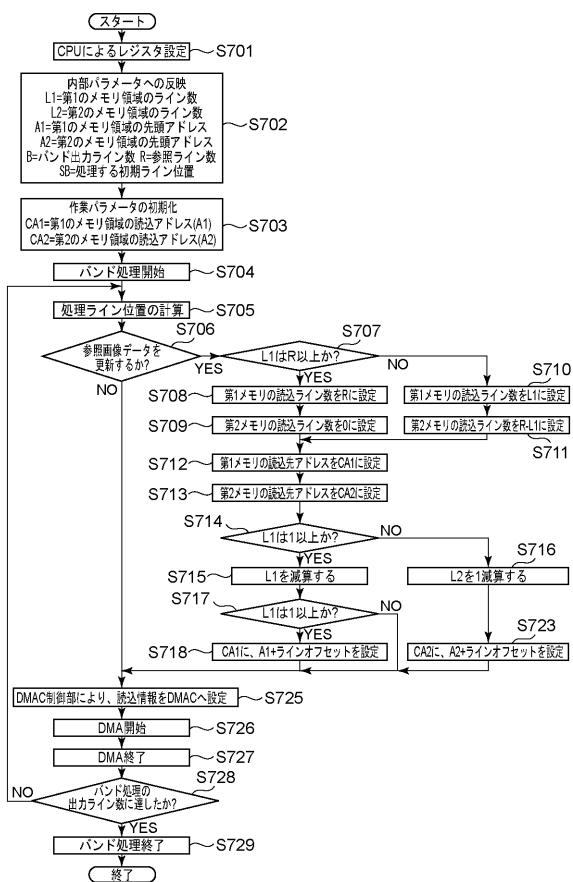

【0040】

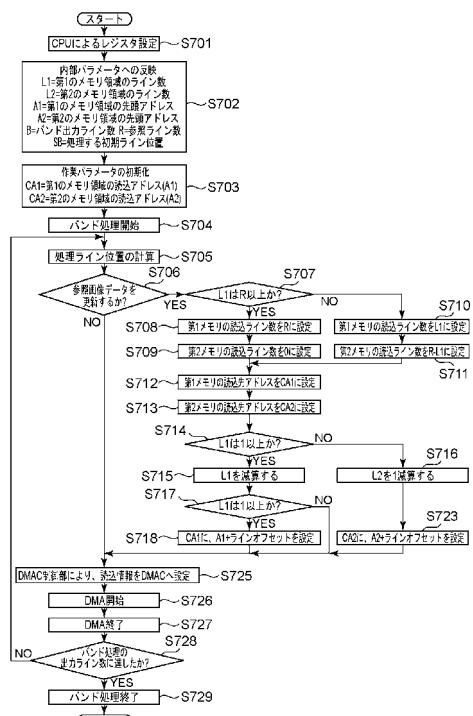

図 5 は、第 1 のデータ処理部 407 が拡大処理部 102 へデータ供給する際のライン管理に関する制御フローチャートを示す図である。図 4 の処理バンド 604 を拡大処理する際のデータフローを例に挙げて説明する。なお、本実施形態では、処理バンド 604 は、拡大倍率が 3 倍で、出力ライン数が 16 ラインであるため、拡大画像処理を 16 回行うことになる。

【0041】

まず、ステップ S701 で、CPU 404 により、データ処理部 407 内のレジスタ（106、107、108、109、110、111、116、117）の設定を行う。

【0042】

10

20

30

40

50

次に、ステップ S 702 で、各レジスタ設定値を L1、L2、A1、A2、B、R、SB の内部パラメータへ反映させる。具体的には、L1 へメモリ1 のライン数格納部 110 のライン数を設定し、A1 へメモリ1 の先頭アドレス格納部 108 のアドレス値を設定する。L2 へメモリ2 のライン数格納部 111 のライン数を設定し、A2 へメモリ2 の先頭アドレス格納部 109 のアドレス値を設定する。B へ画像出力ライン数格納部 116 のライン数をバンド出力ライン数として設定する。R には、参照ライン数を設定する。本実施形態では、動作モードがバイキューピックアルゴリズムであるため参照ライン数として、R には 4 ラインを設定する。SB へ画像データ情報格納部 107 の初期ライン位置である 1 ライン目を指定する。

【0043】

10

ステップ S 703 で、作業パラメータの初期化を行う。CA1 は、DMA C 開始時の第 1 のメモリ領域から読み出す先頭画素アドレスを示すパラメータであり、CA1 の初期値として A1 の設定値を設定する。CA2 は、DMA C 開始時の第 2 のメモリ領域から読み出す先頭画素アドレスを示すパラメータであり、CA2 の初期値として A2 の設定値を設定する。

【0044】

ステップ S 704 で、CPU404 がバンド処理を開始する指示をする。

【0045】

20

ステップ S 705 で、処理ライン位置計算部 103 に拡大処理を行う処理ラインの位置を計算させる。処理バンド 604 の最初の処理の場合、図 4 の処理バンド 604 内の 1, 2, 3, 4 ライン目が参照ラインとなり、SB が 1 ライン目であることから、着目ライン位置は、処理バンド 604 内の 2, 3 ライン目の間となる。バンド 604 内の 1 ~ 4 ライン目が図 3 の 503 ~ 506 に対応する場合、着目ラインの位置は、図 3 のライン位置 508 となる。

【0046】

続いて、ステップ S 706 で、参照画像データ制御部 104 が参照画像データのライン位置を更新するかを判定する。参照画像データのライン位置を更新する場合は、S 707 へ進み、参照画像データのライン位置を更新しない場合は、S 725 へ進む。ここでは、バンド処理の最初の処理であり更新が必要であるため、ステップ S 707 へ進む。

【0047】

30

ステップ S 707 で、参照画像データ制御部 104 が L1 のライン数が R のライン数以上であるかを判定する。R のライン数以上ならばステップ S 708 へ進み、R のライン数に満たない場合はステップ S 710 へ進む。ここでは、処理バンド 604 の最初の処理であるため、L1 は 4 ラインであり R のライン数 (4 ライン) 以上であるため、ステップ S 708 へ進む。

【0048】

40

ステップ S 708 で、参照画像データ制御部 104 がメモリ1 の読み出しライン数格納部 114 へ R を設定する。ここでは、R へ 4 ラインを設定する。ステップ S 709 で、参照画像データ制御部 104 がメモリ2 の読み出しライン数格納部 115 へ 0 ラインを設定する。続いて、ステップ S 712 で、参照画像データ制御部 104 がメモリ1 の読み出しアドレス格納部 112 へ CA1 を設定する。続いて、参照画像データ制御部 104 がメモリ2 の読み出しアドレス格納部 113 へ CA2 を設定する。上述した S 708 ~ S 713 により、DMA C に設定するパラメータの生成を終える。

【0049】

次に、次の参照画像データを更新する際のパラメータを準備する処理を行う。まず、ステップ S 714 で、参照画像データ制御部 104 が、L1 が 1 以上かを判定する。L1 が 1 以上であれば S 715 へ進み、L1 が 0 であれば S 716 へ進む。処理 1 回目では、L1 は 4 ラインであるため、ステップ S 715 へ進む。ステップ S 715 で、参照画像データ制御部 104 が L1 を 1 減算し、L1 は 3 ラインとなり、ステップ S 717 へ進む。ステップ S 717 で、参照画像データ制御部 104 が、再度 L1 が 1 以上かを判定する。L1

50

1が1以上である場合はS718へ進み、L1が0の場合はS725へ進む。ここでは、L1は3ラインであるため、ステップS718へ進む。ステップS718で、参照画像データ制御部104が、A1にラインオフセットを加算したアドレス値をCA1に設定する。CA2は第2のメモリ領域から参照データを読み出すことがないため、更新をせずに、ステップS725へ進む。S714～S718が、次回更新時のパラメータを準備するための処理フローになる。

#### 【0050】

続いて、ステップS725で、DMAC制御部105により、メモリ1の読み出しアドレス格納部112、メモリ2の読み出しアドレス格納部113、メモリ1の読み出しライン数格納部114、メモリ2の読み出しライン数格納部115の設定値を取り出す。DMAC制御部105が設定値を取りだした後、その設定値を入力用DMAC101へ設定する。

10

#### 【0051】

ステップS726で、DMAC制御部105が入力用DMAC101への設定が完了後、DMA転送の開始を入力用DMACへ通知し、入力用DMAC101は設定指示に従ってDMA転送を開始する。具体的には、DMAC101では、まず、第1のメモリ領域602から、メモリ1の読み出しアドレスから参照ラインの1ライン目の32画素分を32Byteのバースト転送で読み出す。続いて、メモリ1の読み出しアドレスにラインオフセット609を足したアドレスから参照ラインの2ライン目の32画素分を32Byteのバースト転送で読み出す。同様に、ラインオフセット609を用いて、3ライン目、4ライン目もメモリ1から読み出す。なお、本実施形態では、メモリからの読み出しはバースト転送により行ったが、これに限定されるものではない。4ライン目まで読み出すと、拡大処理部102に参照ラインの4ラインの左端の32画素分を供給できるようになり、拡大の画像処理が開始される。拡大された画像データは出力用DMAC116へ送信され、出力用DMAC116がこれをRAM405へ格納する。本実施形態では、32画素の3倍である96画素分出力されると、再度入力用DMAC101が先ほどの続きから4ライン分の32画素のデータを読み出し、拡大処理部102へ供給し、同様に画像処理を行う。このような処理を画像データの右端になるまで繰り返す。

20

#### 【0052】

ステップS727で、画像データの右端まで拡大処理が行われた後、DMAC制御部105は、拡大処理部102から画像処理終了の通知を受け、ステップS728へ進む。

30

#### 【0053】

ステップS728で、処理ライン位置計算部103がバンド処理の出力ライン数に達したかを判定する。バンド処理の出力ライン数に達した場合はS729へ進み、出力ライン数に達していない場合はS705へ戻る。出力ライン数は16ラインで、今は1ライン目であるため、ステップS705へ戻る。

#### 【0054】

以上が、処理バンド604の1回目の処理における制御フローとなる。

#### 【0055】

続いて、処理バンド604の2回目の処理における制御フローを簡単に説明する。まず、ステップS705で、処理ライン位置計算部103が処理ライン位置を1ラインインクリメントし、処理ライン位置は、図3のライン位置509になる。ステップS706で、着目ライン位置509が図4の処理バンド内の2、3ライン目の間にになり、上下2ラインの参照するライン位置と変わらないため、参照画像データのライン位置を変更する必要がないと判断し、ステップS725へ進む。ステップS725、S726、727では、1回目と同じ設定をDMAC101へ設定してDMA転送をスタートし、DMA転送を終了する。そして、ステップS728で、2回目の処理であるため、再び、ステップS705へ戻る。以上が、処理バンド604の2回目の処理における制御フローとなる。

40

#### 【0056】

なお、拡大率が3倍の場合は、3回に1度参照画像データのライン位置を更新すればよ

50

い。したがって、ステップ S 725 で参照画像データのライン位置を更新しないと判定するのは、2回目の処理だけでなく、3回目、5回目、6回目、8回目、9回目、11回目、12回目、14回目、15回目も同様である。これらは、2回目の処理と同様のフローとなるため説明を省略する。

#### 【0057】

続いて、処理バンド 604 の 4 回目の処理における制御フローを説明する。ステップ S 705 で、処理ライン位置計算部 103 が処理ライン位置を 1 ラインインクリメントし、処理ラインの位置は、図 3 のライン位置 511 になる。すなわち、処理ラインの位置は、図 4 の処理バンド内の 3, 4 ライン目の間となり、参照するライン位置が図 4 の処理バンド内の 2, 3, 4, 5 ライン目となる。そのため、ステップ S 705 で、参照画像データの読み出し情報を更新すること判断し、ステップ S 707 へ進む。ステップ S 707 で、L1 は 3 ラインであるため、ステップ S 710 へ進む。ステップ S 710 で、参照画像データ制御部 104 がメモリ 1 の読み出しライン数格納部 114 へ L1 の 3 ラインを設定する。ステップ S 711 で、参照画像データ制御部 104 がメモリ 2 の読み出しライン数格納部 115 へ R - L1 (ここでは、4 ライン - 3 ライン) の 1 ラインを設定する。そして、ステップ S 712, S 713 で、参照画像データ制御部 104 がメモリ 1 の読み出しアドレス格納部 112、メモリ 2 の読み出しアドレス格納部 112 へ CA1 と CA2 をそれぞれ設定する。続いて、ステップ S 714 からステップ S 718 を経由して S 728 まで進む。ステップ S 728 で、4 回目の処理であるため、再び、ステップ S 705 へ戻る。なお、バンド処理の 7 回目も同様のフローとなるため、説明を省略する。

10

20

#### 【0058】

次に、処理バンド 604 の 10 回目、13 回目、16 回目の処理について説明する。10 回目、13 回目、16 回目の処理の場合、処理ラインの位置が参照ラインの 2 ライン目と 3 ライン目の間ではなくなるため、ステップ S 706 で参照ラインの位置を更新すると判断し、ステップ S 707 へ進む。

#### 【0059】

まず、処理バンド 604 の 10 回目の処理における制御フローを説明する。10 回目の処理では、ステップ S 707 へ進んだ後、S 710 を経由してステップ S 717 へ進む。ステップ S 717 で、L1 は、0 ラインであるため、CA1 及び CA2 の更新をせずに、ステップ S 725 を経由してステップ S 728 へ進む。ステップ S 728 で、10 回目の処理であるためバンド処理の出力ライン数に達していないと判断し、再び、ステップ S 705 へ戻る。つまり、次回の更新するタイミングであるバンド処理の 13 回目では、メモリ 1 からの参照データの読み出しが発生しないことになる。

30

#### 【0060】

処理バンド 604 の 13 回目及び 16 回目の処理では、ステップ S 707 へ進んだ後、S 710 を経由してステップ S 714 へ進む。ステップ S 714 で、L1 は、0 ラインであるため、ステップ S 716 へ進む。ステップ S 716 で、L2 が 5 ラインであるため、参照画像データ制御部 104 が L2 のライン数を 1 減算して L2 は 4 ラインとなる。ステップ S 723 では、参照画像データ制御部 104 が CA2 へ A2 にラインオフセットを加算したアドレス値を設定し、ステップ S 725 を経由してステップ S 728 へ進む。なお、CA1 は L1 が 0 ラインであるため、使用しないことから設定を更新しない。ステップ S 728 で、10 回目の処理のときは、バンド処理の出力ライン数に達していないと判断し、再び、ステップ S 705 へ戻る。一方、16 回目の処理では、処理回数が 16 回であり、出力ライン数に達したと判断し、ステップ S 729 へ進む。ステップ S 729 で、バンド処理が終了したことが CPU404 へ通知され、CPU405 がバンド処理を完了したことを検知する。

40

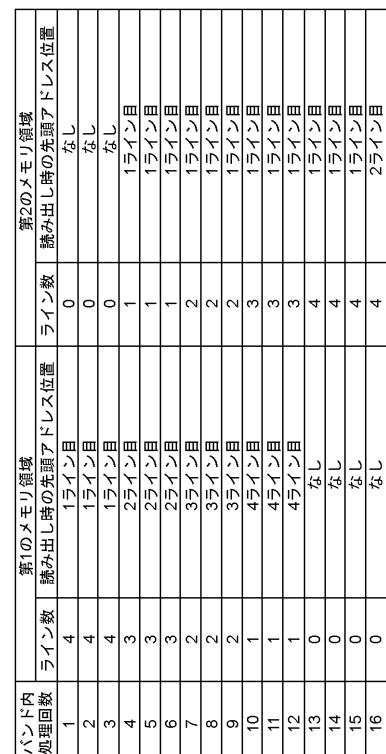

#### 【0061】

図 6 は、処理バンド 604 において、参照する画像データを処理する際にメモリから読み出すライン数及び読み出し時の先頭アドレスの位置を処理回数毎に整理した図である。ここで、第 1 のメモリ領域のライン数は L1 に対応し、第 2 のメモリ領域のライン数は L

50

2に対応する。

【0062】

図6に示すように、拡大率が3倍であるため、バンド内の処理回数が1～12回目の場合は、バンド内の処理回数が3の倍数のときに第1のメモリ領域の読み出し時の先頭アドレスの位置が変わる。そして、処理回数が13回目以降は、参照ラインがすべて第2のメモリ領域となる。本実施形態では、出力対象である着目ラインの位置を算出し、その着目ラインの位置に応じて参照すべきライン位置をメモリ領域毎に決定する。これにより、バンド内で参照画像データが2つのメモリ領域に分割されても拡大処理部へデータを供給することができる。したがって、2つのメモリ領域の画像データを参照するような画像処理であっても、DMAを用いることにより、CPUが途中で介在することなく、バンド処理することが可能になる。また、メモリ上のデータコピーなどによるメモリ使用量を増大させることなく、バンド処理することが可能になる。すなわち、画像データを複数ラインずつに分割して複数のバンドを生成し、バンド毎に画像処理を実行する際に、DMAを用いることにより、CPUが途中で介在することなく複数ラインを一度に処理することが可能となる。また、無駄なメモリアクセスを抑制することができる。したがって、周辺画素を参照する画像処理において、より高速な画像処理を行うことができる。

【0063】

(実施形態2)

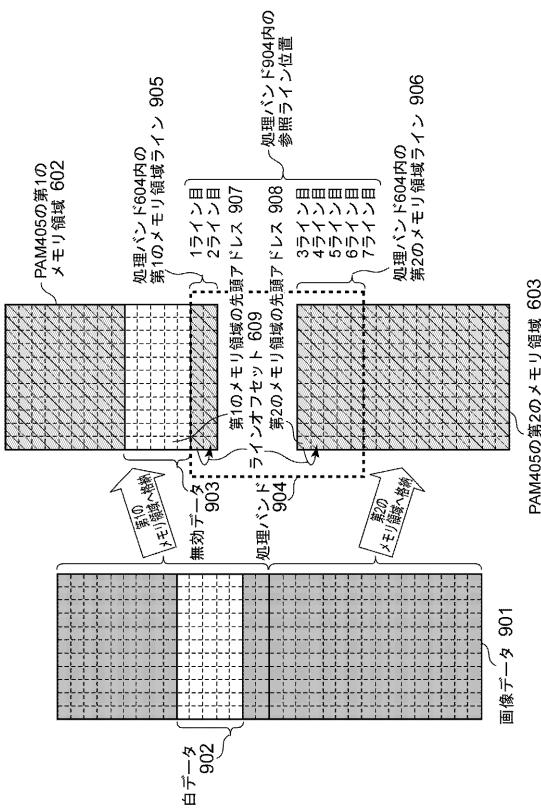

図7～9は、実施形態2に係る画像処理を説明する図である。本実施形態では、実施形態1と同様の部分については重複する説明は省略する。

【0064】

実施形態1では、メモリ領域(第1のメモリ領域602, 第2のメモリ領域603)を跨ぐ画像データとして、図4の画像データ601のように連続した画像データを例に挙げて説明した。本実施形態では、さらに、オリジナルの画像データが全て白データというラインを含む場合、ホストコンピュータからそのラインを送信しない又はホストコンピュータとプリンタ間の転送帯域を下げる。

【0065】

ここで、例えば、図7の画像データ901のように有効な画像データの間に白データ902が5ラインある場合について説明する。白データ902は実際にはメモリ領域に転送されてこないため、メモリ管理上は無効データが白データ902分存在することになる。例えば、メモリ管理上、第1のメモリ領域602の16ライン分の領域のうち、上9ラインが有効画像データで、中5ラインが無効データ903で、下2ラインが有効データ(905)として格納される。この有効データの参照ライン905を含んだ画像を処理する際、例えば、上2ラインを白データ、下2ラインを参照ライン905の2ラインとして、このうちの半分の有効な参照ライン905を参照して処理することが望まれる。そのような場合、上2ラインの白データをメモリ上から読み出すのではなく、画像処理内部で自動生成して白データを補完することで、読み出す参照ラインを2ラインとして効率的にデータを供給及び処理する。本実施形態では、画像データの上端や下端、すなわち、参照ラインが一部存在しない部分についても、白データの補完処理を行うことにより、バンド処理単位で拡大処理を行う。すなわち、補完処理による参照ライン数の読み出しライン数を可変に対応することができる。

【0066】

例えば、図7の処理バンド904を拡大処理する場合、参照する画像データは7ラインあり、そのうち、上の2ラインは第1のメモリ領域(905)で、下の5ラインは第2のメモリ領域(906)になる。つまり、処理バンド904のメモリアドレス上連続していないのは、バンド内の2ライン目と3ライン目となる。

【0067】

ここで、図7において、907は処理バンド904の第1のメモリ領域602の先頭画素アドレスであり、908は第2のメモリ領域603の先頭画素アドレスである。ラインオフセットは図4のラインオフセット609と同じである。また、拡大倍率が3倍である

10

20

30

40

50

ため、処理バンド904における着目ライン位置において初期ライン位置を図3の508, 509, 510から選択できるが、本実施形態では、実施形態1と同様に初期ライン位置を508とする。また、処理バンド904が画像データの上端であるという情報を図1のCPU404が画像データ情報格納部107へバンド処理開始前に設定する。

#### 【0068】

ライン管理に着目した制御フローを図8に示す。図8の制御フローは、図5の制御フローに、ステップS1001とS1002とS1003が追加されたものである。図8の制御フローでは、処理回数に応じて参照ライン数を増加させていくことで画像データの上端位置でのデータ供給を実現している。まず、ステップS701で、画像データの上端であることをCPUが設定し、ステップS702で、CPU404は、各レジスタ設定値をL1、L2、A1、A2、B、R、SBの内部パラメータへ反映させる。本実施形態では、L1、L2、A1、A2、B、SBは実施形態1と同様に設定するが、参照ライン数の初期値Rは、4ラインではなく、2ラインに設定する。ステップS1001では、通常時の参照ライン数、すなわち、白ラインが存在しない場合のライン数をR0に設定する。ここでは、バイキューピックアルゴリズムでの参照ラインを通常時の参照ラインとして、R0に4ラインを設定する。その後のS704～S713までのフローは、図5と同じであるため説明を省略する。

10

#### 【0069】

ステップS1002で、参照画像データ制御部104は、現在の参照ライン数RがR0と同じであるかを判定し、RがR0に満たない場合はステップS1003に進み、R=R0の場合はステップS714へ進み、読み出すライン数やアドレスの更新処理を行う。ステップS1003では、参照画像データ制御部104が参照ラインRに対して1ライン加算する処理を行い、読み出すライン数やアドレスの更新の処理をスキップする。このようにして、ステップS706で参照画像データを更新すると判断される毎に参照ラインRのライン数をR0まで増やしていくことにより、画像データの上端で異なるメモリ間を跨ぐ場合でもデータを供給することができる。

20

#### 【0070】

図9に、処理バンド904において、参照する画像データをメモリから読み出すためのライン数及び読み出し時の先頭アドレスの位置、有効データの参照ライン数及び補完ライン数を処理回数毎に整理した図を示す。図9に示すように、バンド内の処理回数がいずれの場合も、有効データの参照ライン数と補完ライン数の合計が4となる。ここで、参照ライン数は、各メモリ領域から読み込むライン数であり、補完ライン数とは、補完処理により生成される補完データのライン数である。

30

#### 【0071】

本実施形態では、上端に白データがある場合について説明したが、下端に白データがある場合も同様である。具体的には、画像データ情報格納部107に画像データの下端である情報を設定し、処理ライン位置に応じて参照ラインのRを徐々に減らしていくことで対応することができる。

#### 【0072】

本実施形態では、実施形態1と同様に、バンド内で参照画像データが2つのメモリ領域に分割されても拡大処理部へデータを供給することができる。したがって、2つのメモリ領域の画像データを参照するような画像処理であっても、DMAを用いることにより、CPUによる途中介在や、メモリ上のデータコピーなどを行うことなく、バンド処理することが可能になる。

40

#### 【0073】

また、本実施形態によれば、メモリ上に存在しない白データ（補完データ）を生成する場合であっても、DMAを用いることにより、CPUが途中で介在することなく、バンド処理することが可能になる。また、メモリ上のデータコピーなどによるメモリ使用量を増大させることなく、バンド処理することが可能になる。

#### 【0074】

50

(他の実施形態)

以上、本発明の各実施形態を説明したが、本発明の基本的構成は上述したものに限定されるものではない。例えば、上述した実施形態では、拡大処理の倍率を3倍としたが、拡大処理の倍率は特に限定されるものではない。なお、倍率を変更することにより、ステップS706での更新をする処理回数が変更され、また、倍率によっては、バッファを跨ぐときのライン位置が固定されることがある。

【0075】

上述した実施形態では、バンド内の拡大処理が1回につき拡大された画像データを1ラインずつ出力するものを例に挙げて説明したが、複数ライン同時に出力する場合も同様である。

10

【0076】

また、上述した実施形態では、処理バンド604の初期ライン位置を3通りのうち1ライン目として説明したが、これに限定されるものではなく、2ライン目であっても3ライン目であってもよい。例えば、2ライン目であった場合、ステップ706で更新するタイミングがシフトされるだけであり、例えば、4回目で更新するのではなく、3回目で更新することになり、図6の結果に対して全体的に1処理分早くシフトされた結果となる。

【0077】

また、上述した実施形態では、第1のデータ処理部407は、印刷ジョブに含まれる印刷条件に従ってRAM405に格納された画像データの拡大処理を行うものとしたが、縮小処理を行うものとしてもよい。この場合は、着目ラインの位置及び縮小率(変倍率)に基づいて、各メモリ領域から転送する入力データのライン数及びそのアドレスを決定するようすればよい。

20

【0078】

上述した実施形態では、バッファの数を2つの場合を例に挙げて説明したが、1つのバンド処理で参照する画像データのメモリ領域を跨ぐようなメモリ配置であれば、本発明を適用可能である。すなわち、例えば、1つのバンド処理で参照する画像データが3以上のバッファを跨ぐようなメモリ配置であってもよく、バッファはリングバッファであってよい。

【0079】

上述した実施形態では、複数のバッファをRAM405内に設ける構成としたが、RAMを複数個用意してそれぞれを1つのバッファとする構成であってもよい。

30

【0080】

上述した実施形態では、拡大処理のアルゴリズムとして4ラインを参照するバイキューピックを例に挙げて説明したが、これに限定されず、上下の画素を参照して処理を行うものであれば本発明を適用可能である。例えば、拡大処理のアルゴリズムとしてバイキューピックの代わりに2ラインを参照するバイリニアを用いてもよい。

【0081】

上述した実施形態では、拡大処理を例にて説明したが、本発明に係る画像処理のデータ転送方法は、これに限定されるものではなく、上下の画素を参照して処理を行うものであり、メモリ領域を跨ぐことになるものであればよい。例えば、縮小処理やアンシャープマスクのような画像処理であってもよい。

40

【0082】

上述した実施形態では、画像処理の一例として拡大処理について説明したが、本発明は、これに限定されず、バンド間を跨ぐ画像処理の際には適用することができる。

【0083】

上述した実施形態では、インクジェットプリンタを例に挙げて説明したが、上下画素を参照する画像処理を備えていれば、本発明を適用することができる。したがって、画像形成装置は、インクジェットプリンタに限定されるものではなく、例えば、レーザプリンタや複写機のような印刷機であってもよく、ファクシミリ装置、携帯電話、PDA、画像ビューワー、デジタルカメラなどの他の画像形成装置であってもよい。

50

## 【0084】

また、上述した実施形態の処理の全てをハードウェアで実行する必要はなく、一部をソフトウェアによって構成してもよい。

## 【符号の説明】

## 【0085】

- 101 入力用 DMA C

- 116 出力用 DMA C

- 102 拡大処理部

- 103 処理ライン位置計算部

- 104 参照画像データ制御部

- 105 DMA C制御部

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

| バンド内<br>処理回数 | 参照<br>ライン数 | 補完<br>ライン数 | 第1のメモリ領域       |                | 第2のメモリ領域 |

|--------------|------------|------------|----------------|----------------|----------|

|              |            |            | 読み出し時の先頭アドレス位置 | 読み出し時の先頭アドレス位置 |          |

| 1            | 2          | 2          | 1ライイン目         | 0              | なし       |

| 2            | 2          | 2          | 1ライイン目         | 0              | なし       |

| 3            | 2          | 2          | 1ライイン目         | 1              | なし       |

| 4            | 3          | 1          | 1ライイン目         | 1              | 1ライイン目   |

| 5            | 3          | 1          | 1ライイン目         | 1              | 1ライイン目   |

| 6            | 3          | 1          | 1ライイン目         | 1              | 1ライイン目   |

| 7            | 4          | 0          | 2              | 1ライイン目         | 2        |

| 8            | 4          | 0          | 2              | 1ライイン目         | 2        |

| 9            | 4          | 0          | 2              | 1ライイン目         | 2        |

| 10           | 4          | 0          | 1              | 2ライイン目         | 3        |

| 11           | 4          | 0          | 1              | 2ライイン目         | 3        |

| 12           | 4          | 0          | 1              | 2ライイン目         | 3        |

| 13           | 4          | 0          | 0              | なし             | 4        |

| 14           | 4          | 0          | 0              | なし             | 4        |

| 15           | 4          | 0          | 0              | なし             | 4        |

| 16           | 4          | 0          | 0              | なし             | 4        |