(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4591451号

(P4591451)

(45) 発行日 平成22年12月1日(2010.12.1)

(24) 登録日 平成22年9月24日(2010.9.24)

(51) Int.Cl.

F 1

|             |           |            |      |

|-------------|-----------|------------|------|

| HO1L 29/786 | (2006.01) | HO1L 29/78 | 623Z |

| HO1L 51/05  | (2006.01) | HO1L 29/78 | 618B |

| GO9F 9/30   | (2006.01) | HO1L 29/78 | 616T |

| GO2F 1/1368 | (2006.01) | HO1L 29/78 | 617N |

|             |           | HO1L 29/28 | 100A |

請求項の数 8 (全 30 頁) 最終頁に続く

(21) 出願番号

特願2007-1930 (P2007-1930)

(22) 出願日

平成19年1月10日 (2007.1.10)

(65) 公開番号

特開2008-171907 (P2008-171907A)

(43) 公開日

平成20年7月24日 (2008.7.24)

審査請求日

平成21年11月27日 (2009.11.27)

(73) 特許権者 000002185

ソニー株式会社

東京都港区港南1丁目7番1号

(74) 代理人 100098785

弁理士 藤島 洋一郎

(74) 代理人 100109656

弁理士 三反崎 泰司

(74) 代理人 100130915

弁理士 長谷部 政男

(74) 代理人 100155376

弁理士 田名網 孝昭

(72) 発明者 八木 巍

東京都品川区北品川6丁目7番35号 ソニー株式会社内

最終頁に続く

(54) 【発明の名称】半導体装置および表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

ゲート電極と、前記ゲート電極の上層にゲート絶縁膜を間にして設けられたソース／ドレイン電極と、有機半導体薄膜で構成され、前記ソース電極とドレイン電極との間に設けられたチャネル層とを基板上に有するボトムゲート型の薄膜トランジスタと、

前記薄膜トランジスタの上部に絶縁膜を介して設けられた電極とを備えた半導体装置において、

前記薄膜トランジスタと前記電極との間に、導電性のシールド層が配置され、

前記シールド層は、前記薄膜トランジスタおよび前記電極それとの間に絶縁性を保つと共に、前記チャネル層および前記ソース／ドレイン電極の全面を覆う状態で形成されている

半導体装置。

## 【請求項 2】

前記シールド層は、前記薄膜トランジスタの前記ゲート電極または前記ソース電極と接続されている

請求項1記載の半導体装置。

## 【請求項 3】

前記シールド層は、前記薄膜トランジスタに対して独立して電位制御される

請求項1記載の半導体装置。

## 【請求項 4】

前記電極は、前記シールド膜に設けられた開口部を介して前記薄膜トランジスタに接続されている

請求項 1 記載の半導体装置。

**【請求項 5】**

前記基板上には前記薄膜トランジスタが複数配置され、

前記シールド層は、複数の前記薄膜トランジスタを覆う状態で共通に設けられている

請求項 1 記載の半導体装置。

**【請求項 6】**

ゲート電極と、前記ゲート電極の上層にゲート絶縁膜を間にして設けられたソース／ドレイン電極と、有機半導体薄膜で構成され、前記ソース電極とドレイン電極との間に設けられたチャネル層とを基板上に有するボトムゲート型の薄膜トランジスタと、前記薄膜トランジスタの上部に絶縁膜を介して設けられた電極とを備えた表示装置において

10

前記薄膜トランジスタと前記電極との間に、導電性のシールド層が配置され、

前記シールド層は、前記薄膜トランジスタおよび前記電極それとの間に絶縁性を保つと共に、前記チャネル層の全面および前記ソース／ドレイン電極の少なくとも一部を覆う状態で形成されている

表示装置。

**【請求項 7】**

20

前記薄膜トランジスタの上部に設けられた電極は、当該薄膜トランジスタに接続された画素電極である

請求項 6 記載の表示装置。

**【請求項 8】**

前記基板上には前記薄膜トランジスタが複数配置され、

前記薄膜トランジスタの上部に設けられた電極は、複数の当該薄膜トランジスタに対して共通に対向配置された共通電極である

請求項 6 記載の表示装置。

**【発明の詳細な説明】**

**【技術分野】**

30

**【0001】**

本発明は半導体装置および表示装置に関し、特には有機半導体薄膜を用いた半導体装置、およびこの半導体装置を用いた表示装置に関する。

**【背景技術】**

**【0002】**

薄膜トランジスタ (thin film transistor : TFT) は、アクティブマトリックス駆動のフラットパネル型表示装置における画素電極のスイッチング素子として広く用いられている。このような薄膜トランジスタにおいて、チャネル層に有機半導体薄膜を用いた有機薄膜トランジスタは、真空処理装置を用いずにチャネル層（有機半導体薄膜）を塗布成膜することが可能である。このため、チャネル層にシリコン薄膜を用いた無機薄膜トランジスタと比較して、低コスト化に有利である。

40

**【0003】**

上記表示装置において、有機薄膜トランジスタが設けられた駆動基板の構成は、次のようにある。すなわち、絶縁性の基板上における表示領域には、走査線と信号線とが絶縁性を保って交差配設されている。そして、これらの配線の交差地点に、例えばボトムゲート型の有機薄膜トランジスタが設けられている。また、有機薄膜トランジスタを覆う絶縁膜には各有機薄膜トランジスタに達するコンタクトホールが設けられており、この絶縁膜上にはコンタクトホールを介して各有機薄膜トランジスタに接続された画素電極が配列形成されている（以上、例えば下記特許文献 1 参照）。

**【0004】**

50

【特許文献 1】特開 2006 - 86502 号公報（特に図 1～3 および関連の記載部参照）

【発明の開示】

【発明が解決しようとする課題】

【0005】

ところで、有機薄膜トランジスタの構成は、製造工程の容易性だけではなくキャリアの移動特性の観点からボトムゲート型が有利と考えられている。つまり、基板上に成膜された有機半導体薄膜は、上面側と比較して下面側の平坦性が高く、このため下面側にチャネル部が形成されるボトムゲート型においてキャリアの移動特性が良好になると考えられるためである。

10

【0006】

しかしながら、ボトムゲート型の有機薄膜トランジスタを用いた半導体装置および表示装置においては、有機薄膜トランジスタを覆う絶縁膜上の電極や配線が、チャネル部を構成する有機半導体薄膜と非常に近い距離に配置されることになる。このため、電極や配線等に印加される電位の影響により、有機薄膜トランジスタのトランジスタ特性が劣化しやすいと言う問題が発生する。

【0007】

例えば表示装置であれば、有機薄膜トランジスタの上部に画素電極が積層配置されることにより、画素電極に印加される電位により有機薄膜トランジスタが電位変調を受ける。このような電位変調により、画素電極の駆動が不安定になり表示の信頼性が劣化する。また、有機薄膜トランジスタをスイッチングさせるための動作電圧の振幅が増大し、消費電力の上昇が引き起こされる。

20

【0008】

また、特に表示装置が有機電界発光素子を用いた有機 EL (electroluminescence) 表示装置であれば、有機薄膜トランジスタ上方の近い位置に、画素電極に対向する共通電極が配置されることもある。このような場合であっても、共通電極に印加される電位により有機薄膜トランジスタが電位変調を受けるため、同様の問題が発生する。

【0009】

そこで本発明は、ボトムゲート型の有機薄膜トランジスタにおける動作特性を、その上層に設けた電極の影響を受けることなく安定した特性に維持することが可能な半導体装置を提供すること、および半導体装置を駆動基板として用いることにより信頼性の高い表示が可能な表示装置を提供することを目的とする。

30

【課題を解決するための手段】

【0010】

このような目的を達成するための本発明の半導体装置は、ゲート電極と、ゲート電極の上層にゲート絶縁膜を間に設けられたソース／ドレイン電極と、有機半導体薄膜で構成され、ソース電極とドレイン電極との間に設けられたチャネル層とを基板上有するボトムゲート型の薄膜トランジスタと、薄膜トランジスタの上部に絶縁膜を介して設けられた電極とを備えた半導体装置であり、特に薄膜トランジスタと電極との間に、導電性のシールド層が配置され、シールド層は、薄膜トランジスタおよび電極それぞれとの間に絶縁性を保つと共に、チャネル層およびソース／ドレイン電極の全面を覆う状態で形成されたものである。

40

【0011】

また本発明の表示装置は、上述した半導体装置を駆動基板として用いたものであり、薄膜トランジスタの上部に設けられた電極は、当該薄膜トランジスタに接続された画素電極である。

【0012】

このような構成の半導体装置および表示装置では、ボトムゲート型の薄膜トランジスタとその上部に配置された電極との間に導電性のシールド層を配置したことにより、電極に印加された電位がボトムゲート型の薄膜トランジスタのチャネル層に影響を及ぼすことが

50

防止される。

【発明の効果】

【0013】

以上説明したように本発明によれば、シールド層によって、電極に印加された電位が、ボトムゲート型の薄膜トランジスタのチャネル層に影響を及ぼすことを防止できるため、ボトムゲート型の薄膜トランジスタにおける動作特性を、その上層に設けた電極の影響を受けることなく安定した特性に維持することが可能になる。そして、画素電極の駆動用としてボトムゲート型の薄膜トランジスタを用いた表示装置において、信頼性の高い表示を行うことが可能になる。

【発明を実施するための最良の形態】

10

【0014】

以下、本発明の半導体装置および表示装置の実施の形態を図面に基づいて詳細に説明する。尚、各実施の形態においては、本発明の半導体装置を駆動基板として用いた表示装置の構成を説明する。

【0015】

<第1実施形態>

第1実施形態においては、アクティブマトリックス方式の液晶表示装置に本発明を適用した実施の形態を説明する。

【0016】

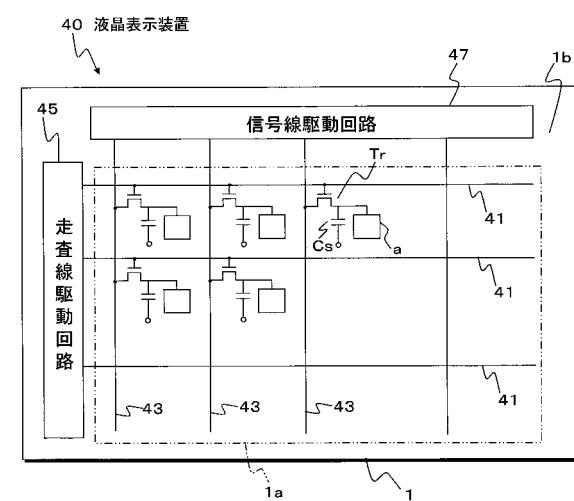

図1は液晶表示装置の一構成例を説明するための概略の回路構成図である。この図に示すように、液晶表示装置40の基板1上には、表示領域1aとその周辺領域1bとが設定されている。表示領域1aには、複数の走査線41と複数の信号線43とが縦横に配線されており、それぞれの交差部に対応して1つの画素が設けられた画素アレイ部として構成されている。また周辺領域1bには、走査線43を走査駆動する走査線駆動回路45と、輝度情報に応じた映像信号(すなわち入力信号)を信号線43に供給する信号線駆動回路47とが配置されている。

20

【0017】

走査線41と信号線43との各交差部に設けられる画素回路は、例えば薄膜トランジスタTr、保持容量Cs、および画素電極aで構成されている。そして、走査線駆動回路45による駆動により、薄膜トランジスタTrを介して信号線47から書き込まれた映像信号が保持容量Csに保持され、保持された信号量に応じた電圧が画素電極aに供給され、この電圧に応じて液晶層を構成する液晶分子が傾斜して表示光の透過が制御される。

30

【0018】

尚、以上のような画素回路の構成は、あくまでも一例であり、必要に応じて画素回路内に容量素子を設けたり、さらに複数のトランジスタを設けて画素回路を構成しても良い。また、周辺領域1bには、画素回路の変更に応じて必要な駆動回路が追加される。

【0019】

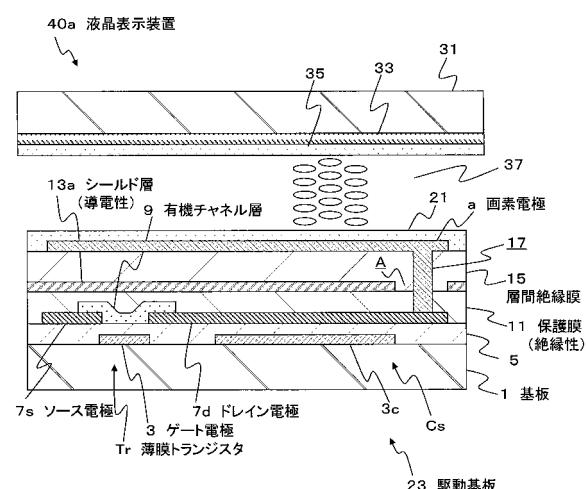

図2には、本第1実施形態の液晶表示装置40aの特徴部を説明するための1画素分の断面図を示す。また図3には本第1実施形態の液晶表示装置40aの特徴部を説明するための駆動基板側の4画素分の平面図を示す。尚、平面図は、説明のために一部を切り欠いており、さらに全体を覆う絶縁性材料からなる膜の図示を省略している。尚、図1と同一構成要素には同一符号を付している。

40

【0020】

これらの図に示すように、第1実施形態の液晶表示装置40aにおける各画素には、基板1上にゲート電極3、ゲート絶縁膜5、ソース電極7sおよびドレイン電極7d、および有機半導体材料からなるチャネル層(以下、有機チャネル層と記す)9をこの順に積層したボトムゲート型の薄膜トランジスタTrが設けられている。またゲート電極3と同一層には保持容量Csの下部電極3cが設けられており、さらにソース電極7sおよびドレイン電極7dと同一層には、ドレイン電極7dから延設された保持容量Csの上部電極が設けられている。さらに平面図に示すように、ゲート電極3は同一層で構成された走査線

50

4 1 から延設され、ソース電極 7 s は同一層で構成された信号線 4 3 から延設され、保持容量 C s の下部電極 3 c は複数画素の共通電極として配線されている。

**【 0 0 2 1 】**

以上のような薄膜トランジスタ T r および保持容量 C s を覆う絶縁性の保護膜 1 1 上に、本第 1 実施形態に特徴的な導電性のシールド層 1 3 a が設けられている。このシールド層 1 3 a は、少なくとも有機チャネル層 9 上を覆う状態で設けられていることとし、特に本第 1 実施形態においては表示領域の全面を覆う状態で設けられていることとする。ただし、このシールド層 1 3 a には、保持容量 C s の上部電極に臨む開口部 A が画素毎に設けられていることとする。

**【 0 0 2 2 】**

このようなシールド層 1 3 a は、表示領域から周辺領域に引き出されて配線され、他の電極および配線に対して独立に電位制御可能な構成となっている。

**【 0 0 2 3 】**

以上のようなシールド層 1 3 a を覆う層間絶縁膜 1 5 上に、画素電極 a ( 平面図では二点鎖線で図示 ) が設けられている。各画素電極 a は、開口部 A の内側に設けたコントラクト部 1 7 を介して保持容量 C s の上部電極 ( ドレイン電極 7 d ) に接続されている。

**【 0 0 2 4 】**

そしてこれらの画素電極 a を覆う状態で、例えば表面ラビング処理された配向膜 2 1 が設けられ、駆動基板 2 3 が構成されている。

**【 0 0 2 5 】**

以上のような構成の駆動基板 2 3 を構成する各層は一般的な材料を用いて構成することができ、特にこれを限定しない。また、各層は機能を損なわない限り、複数の材料からなる多層構造を有していてもよい。これらの例としては、下地との密着性確保のため電極下部への密着層の導入や、電極上へのエッチストップ層の導入、ガスバリア性確保や延性確保のための積層メタル構造導入などがある。各材料の代表的な例を下記に示す。

**【 0 0 2 6 】**

ゲート電極 3 ... アルミニウム、金、金 / クロムの積層膜、銀、パラジウム、さらにはこれらの積層膜。

ゲート絶縁膜 5 ... 酸化シリコン、窒化シリコン、ポリビニルフェノール、ポリメチルメタクリレート ( PMMA ) など。

ソース・ドレイン電極 7 s , 7 d ... 金、金 / クロムの積層膜、銀、白金、パラジウム、さらにはこれらの積層膜。

有機チャネル層 9 ... ペンタセン、ゼキシチオフェンなどのチオフェンオリゴマー、ポリチオフェンなど。

保護膜 1 1 ... 窒化シリコン、酸化シリコン、ポリパラキシリレン、ポリビニルアルコールなど。

シールド層 1 3 a ... 金、金 / クロムの積層膜、銀、アルミニウム、さらにはこれらの積層膜。

層間絶縁膜 1 5 ... 窒化シリコン、ポリパラキシリレン、PMMA などのアクリル系樹脂、ポリビニルアルコールなど。

画素電極 a ... アルミニウム、金、金 / クロムの積層膜、銀、パラジウム、これらの積層膜。

**【 0 0 2 7 】**

また、各層の形成および加工方法に関しては、公知の技術を広く用いることができる。例えば、真空蒸着、スパッタリングや CVD といった一般的な成膜方法、スピンドルコートやキャップコート、スクリーン印刷、インクジェット印刷等の溶液を用いた成膜方法、フォトリソグラフィー法、電子線リソグラフィー法、マイクロプリンティング法、ナノインプリント法などのパターン転写方法、ウェットエッチング法、ドライエッチング法、リフトオフなどのエッチングおよびパターン形成技術を広く組み合わせることができる。これらを組み合わせるにあたり、必要となる加熱や洗浄と言った一般的な半導体形成技術も当然

10

20

30

40

50

用いることができる。

**【0028】**

尚、シールド層13aが遮光機能を備えている場合、シールド層13aの形成より後の工程で行われるリソグラフィーなどの光を用いたプロセスに対して、有機チャネル層9の耐性が向上する。

**【0029】**

また、各層の厚みに関しても機能を損なわない限りこれを限定しない。例えば、ゲート電極3、ソース・ドレイン電極7s, 7d、シールド層13a、画素電極a、ゲート絶縁膜5、および有機チャネル層9は、 $1\mu m$ 以下、より好ましくは $500 nm$ 以下である。

また、保護膜11および層間絶縁膜15は、 $5\mu m$ 以下、より好ましくは $3\mu m$ 以下である。

10

**【0030】**

さらに、画素電極aと保持容量Csとの間のコンタクト部17を構成する接続孔の形状、大きさに関してもこれを限定しない。この場合、層間絶縁膜15の接続孔と保護膜11の接続孔とが、形状および大きさが必ずしも一致している必要はなく、例えば〔層間絶縁膜15の開口形状>保護膜11の開口形状〕である構成や、〔層間絶縁膜の開口形状<保護膜の開口形状〕である構成も含まれる。

**【0031】**

また基板1に関しても、製造プロセスにおける熱履歴に対して耐熱性を有する範囲において、特に材質や板厚が限定されることはない。例えば、ガラスなどの硬い材料から、ポリエーテルスルフォン(PES)やポリエチレンナフタレート(PEN)と言ったやわらかいプラスチック材料も用いることができる。また、ゲート電極3よりも下層の構造を基板1と考えれば、前述ガラスやプラスチック上に保護膜やバッファー層があつてもよい。例えば、ガラス基板上に窒化シリコン(SiNx)薄膜がガスバリアの目的でついている場合や、プラスチックフィルム上にSiNxや表面保護と平坦化用のアクリル系薄膜などが設けられている構成であつても良い。

20

**【0032】**

また、駆動基板23の作製手順が特に限定されることはない。例えば、画素電極aと保持容量Csとの間のコンタクト部17を構成する接続孔を保護膜11に形成する工程は、シールド層13aを形成する前、シールド層13aを形成した後、さらには層間絶縁膜15に形成する接続孔と同時の何れであつても良い。

30

**【0033】**

以上のような駆動基板23は、画素電極aを反射材料で構成することにより、液晶表示装置40aにおける背面板として用いられている。

**【0034】**

以上のような駆動基板23の配向膜21側には、対向基板31が配置されている。この対向基板31は、ガラス基板のような透明基板からなり、駆動基板23側に向かって全画素の共通の対向電極33および配向膜35がこの順に配置されている。尚、このような対向基板31側の構成材料についても、一般的な液晶表示装置の構成材料を適用して良い。

**【0035】**

40

そして、このような駆動基板23と対向基板31との間に、ここでの図示を省略したスペーサが挟持され、さらに液晶層37が充填封止されて液晶表示装置40aが構成されている。尚、図中には明記していないが、例えば対向基板31の外面上に反射防止膜等の外光の反射を抑制する機能を有する部位が存在してもよく、この場合は該機能を有する部位を形成した後に、駆動基板23と対向基板31との間にスペーサを挟持させて液晶層37を充填封止する組み立て工程を行えば良い。また、対向基板31側には、必要に応じてカラーフィルタ層を設けても良い。

**【0036】**

以上のような第1実施形態の構成の液晶表示装置(半導体装置)40aにおいては、ボトムゲート型の薄膜トランジスタTrとその上部に配置された画素電極aとの間に導電性

50

のシールド層 13a を配置したことにより、画素電極 a に印加された電位が薄膜トランジスタ Tr の有機チャネル層 9 に影響を及ぼすことが防止される。このため、ボトムゲート型の薄膜トランジスタ Tr における動作特性を、画素電極 a に印加される電圧に影響されることなく安定した特性に維持することが可能になる。この結果、画素電極 a に印加される電圧の安定化が図られるため、信頼性の高い表示を行うことが可能になる。

#### 【0037】

また、表示領域のほぼ全面がシールド層 13a で覆われた構成であるため、シールド層 13a が、有機チャネル層 9 に対して最も高いガスバリア性能を示すことができる。このため、有機チャネル層 9 の劣化が防止され、薄膜トランジスタ Tr の信頼性の向上を図ることができる。

10

#### 【0038】

さらに、有機チャネル層 9 に対向配置されたシールド層 13a の電位を、他の電極に対して独立に制御することができるため、このシールド層 13a に印加する電位によって薄膜トランジスタ Tr の動作特性を制御することも可能になる。具体的な一例としては、シールド層 13a に任意の電位(例えば 0V)を加えることで、画素電極 a の電位を遮蔽し、薄膜トランジスタ Tr の安定動作を実現し、省電力化に貢献する。また、動作電圧内において、薄膜トランジスタ Tr のオフ電流とオン電流の調整が可能になるため、これを用いて表示の際のコントラストの制御を行うことが可能になる。

#### 【0039】

尚、本第 1 実施形態においては、少なくとも薄膜トランジスタ Tr の有機チャネル層 9 を覆う状態で設けられたシールド層 13a が、独立して電位制御できる構成であれば良く、シールド層 13a はパターニングされていても良い。例えば、同色の光を取り出す画素毎にシールド層 13a をパターニングしても良く、信号線 43 に沿って赤、緑、青の各画素が配列されている場合には、信号線 43 に沿ってシールド層 13a をパターニングすれば良い。そして、各色毎にシールド層 13a に印加する電位を制御する構成とすることにより、色調補正を行うことが可能になる。

20

#### 【0040】

##### <第 2 実施形態>

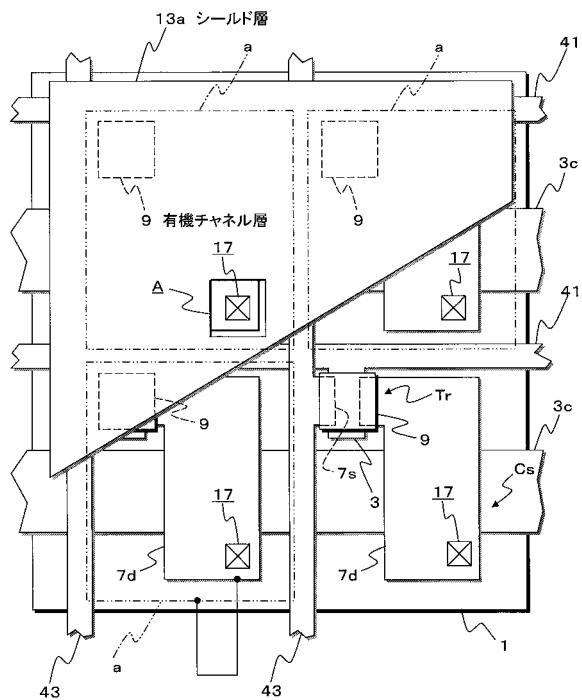

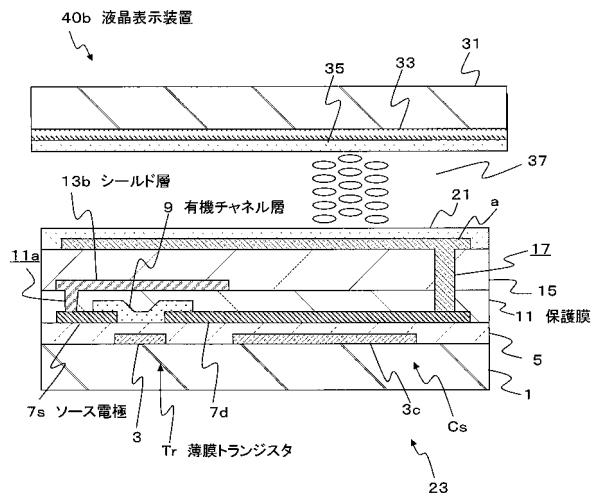

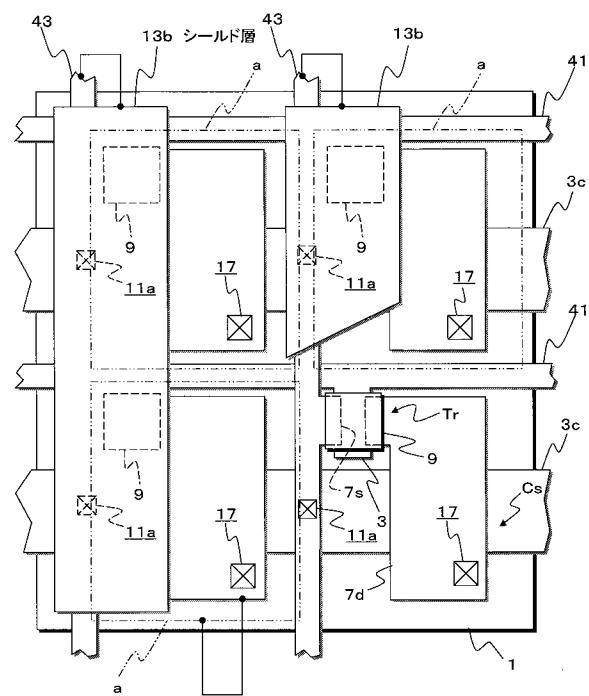

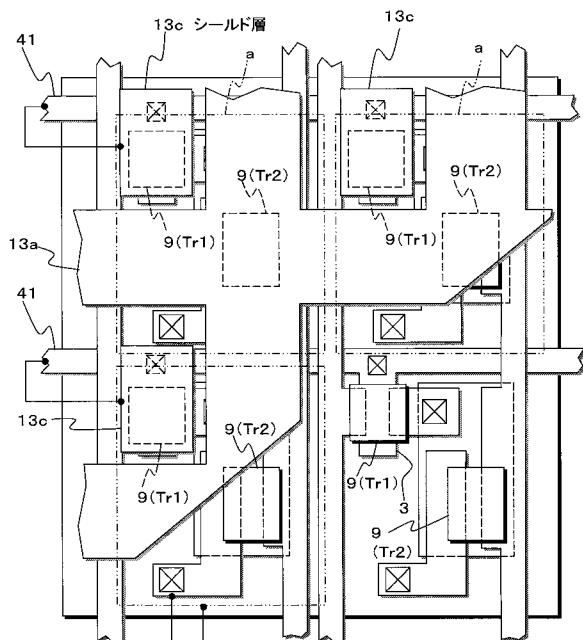

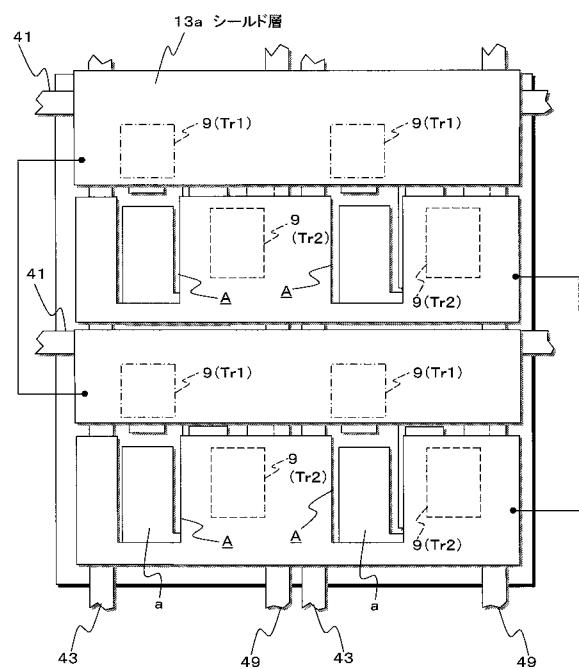

図 4 には、本第 2 実施形態の液晶表示装置 40b の特徴部を説明するための 1 画素分の断面図を示す。また図 5 には本第 2 実施形態の液晶表示装置 40b の特徴部を説明するための駆動基板側の 4 画素分の平面図を示す。尚、平面図は、説明のために一部を切り欠いており、さらに全体を覆う絶縁性材料からなる膜の図示を省略している。また、液晶表示装置の一構成例を説明するための概略の回路構成は、第 1 実施形態において図 1 を用いて説明した構成と同様であって良い。

30

#### 【0041】

これらの図に示す第 2 実施形態の液晶表示装置 40b が、図 2, 3 を用いて説明した第 1 実施形態の液晶表示装置と異なるところは、シールド層 13b の構成にあり、他の構成は同様であることとする。

#### 【0042】

すなわち第 2 実施形態の液晶表示装置 40b におけるシールド層 13b は、保護膜 11 に設けた接続孔とこの内部を埋め込む導電性材料とからなるコンタクト部 11a を介してソース電極 7s に接続されているところが特徴的である。ただし、このシールド層 13b は、ソース電極 7s に接続されていれば良いため、コンタクト部 11a のレイアウトを考慮してソース電極 7s から延設された信号線 43 の部分に接続されていても良い(平面図参照)。また、1 つの信号線 43 を共有する状態で複数の薄膜トランジスタ Tr を覆う各シールド層 13b は、少なくとも 1 箇所で信号線 43 に接続されれば良く、その接続箇所は周辺領域であっても良い。

40

#### 【0043】

各シールド層 13b は、1 つの信号線 43 を共有する薄膜トランジスタ Tr を覆う部分毎に分割されており、少なくとも薄膜トランジスタ Tr の有機チャネル層 9 を覆う状態で

50

信号線 4 3 に沿ってパターニングされていることとする。尚、各シールド層 1 3 b は、各ソース電極 7 s またはその延長上の信号線 4 3 に接続されていれば良いため、画素毎にパターニングされていても良い。

#### 【 0 0 4 4 】

以上のような第 2 実施形態の構成の液晶表示装置（半導体装置）4 0 b であっても、ボトムゲート型の薄膜トランジスタ Tr とその上部に配置された画素電極 a との間に導電性のシールド層 1 3 b が配置されている。このため、第 1 実施形態と同様に、ボトムゲート型の薄膜トランジスタ Tr における動作特性を安定した特性に維持することが可能になり、また画素電極 a に印加される電圧の安定化が図られるため、信頼性の高い表示を行うことが可能になる。

10

#### 【 0 0 4 5 】

##### < 第 3 実施形態 >

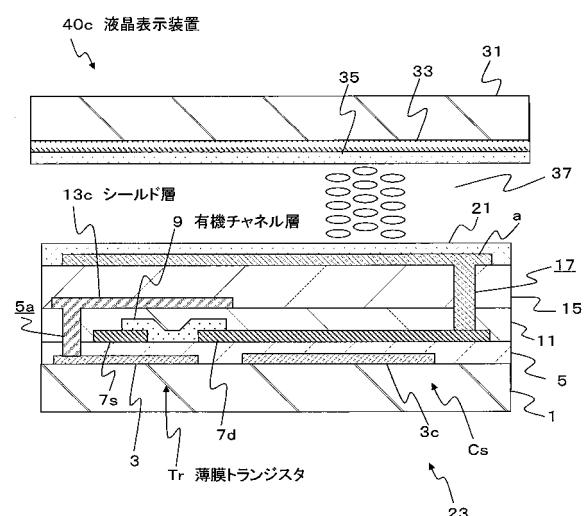

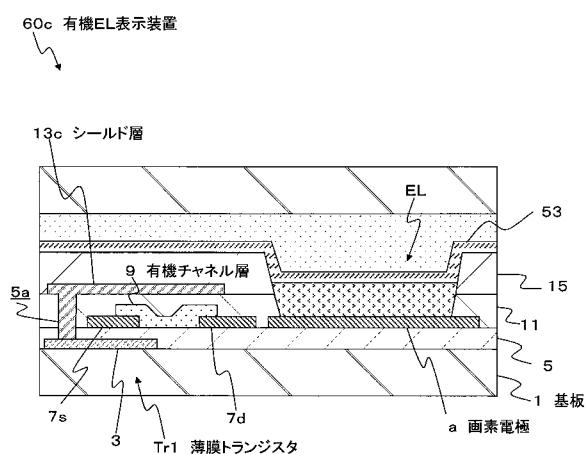

図 6 には、本第 3 実施形態の液晶表示装置 4 0 c の特徴部を説明するための 1 画素分の断面図を示す。また図 7 には本第 3 実施形態の液晶表示装置 4 0 c の特徴部を説明するための駆動基板側の 4 画素分の平面図を示す。尚、平面図は、説明のために一部を切り欠いており、さらに全体を覆う絶縁性材料からなる膜の図示を省略している。また、液晶表示装置の一構成例を説明するための概略の回路構成は、第 1 実施形態において図 1 を用いて説明した構成と同様であって良い。

#### 【 0 0 4 6 】

これらの図に示す第 3 実施形態の液晶表示装置 4 0 c が、図 2 ~ 図 5 を用いて説明した第 1 実施形態および第 2 実施形態の液晶表示装置と異なるところは、シールド層 1 3 c の構成にあり、他の構成は同様であることとする。

20

#### 【 0 0 4 7 】

すなわち第 3 実施形態の液晶表示装置 4 0 c におけるシールド層 1 3 c は、保護膜 1 1 およびゲート絶縁膜 5 に設けた接続孔とこの内部を埋め込む導電性材料とからなるコンタクト部 5 a を介してゲート電極 3 に接続されているところが特徴的である。ただし、このシールド層 1 3 c は、ゲート電極 3 に接続されれば良いため、コンタクト部 5 a のレイアウトを考慮してゲート電極 3 から延設された走査線 4 1 の部分で接続されていても良い（平面図参照）。また、1 つの走査線 4 1 を共有する状態で複数の薄膜トランジスタ Tr を覆う各シールド層 1 3 c は、少なくとも 1 箇所で走査線 4 1 に接続されれば良く、その接続箇所は周辺領域であっても良い。

30

#### 【 0 0 4 8 】

各シールド層 1 3 c は、1 つの走査線 4 1 を共有する薄膜トランジスタ Tr を覆う部分毎に分割されており、少なくとも薄膜トランジスタ Tr の有機チャネル層 9 を覆う状態で走査線 4 1 に沿ってパターニングされていることとする。尚、各シールド層 1 3 c は、各ゲート電極 3 またはその延長上の走査線 4 1 に接続されれば良いため、画素毎にパターニングされていても良い。

#### 【 0 0 4 9 】

以上のような第 3 実施形態の構成の液晶表示装置（半導体装置）4 0 c であっても、ボトムゲート型の薄膜トランジスタ Tr とその上部に配置された画素電極 a との間に導電性のシールド層 1 3 c が配置されている。このため、第 1 実施形態と同様に、ボトムゲート型の薄膜トランジスタ Tr における動作特性を安定した特性に維持することが可能になり、また画素電極 a に印加される電圧の安定化が図られるため、信頼性の高い表示を行うことが可能になる。

40

#### 【 0 0 5 0 】

さらに、有機チャネル層 9 に対向配置されたシールド層 1 3 c をゲート電極 3 と接続させしたことにより、Tr 1 に対する画素電極 a の影響を排除すると同時にトランジスタの駆動能力が向上させることができる。

#### 【 0 0 5 1 】

##### < 第 4 実施形態 >

50

第4実施形態においては、発光素子として有機電界発光素子を用いたアクティブマトリックス方式の有機EL表示装置に本発明を適用した実施の形態を説明する。尚、以下の各図においては、上述した第1実施形態～第3実施形態と同一の構成要素には同一の符号を付して説明を行うこととする。

#### 【0052】

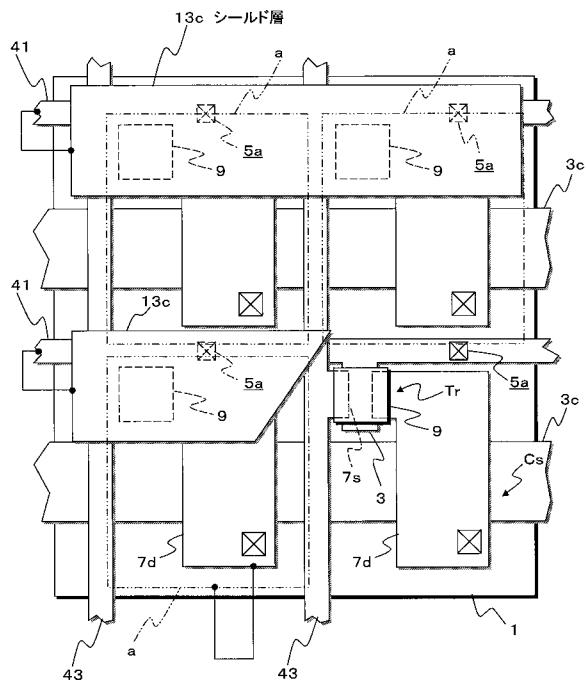

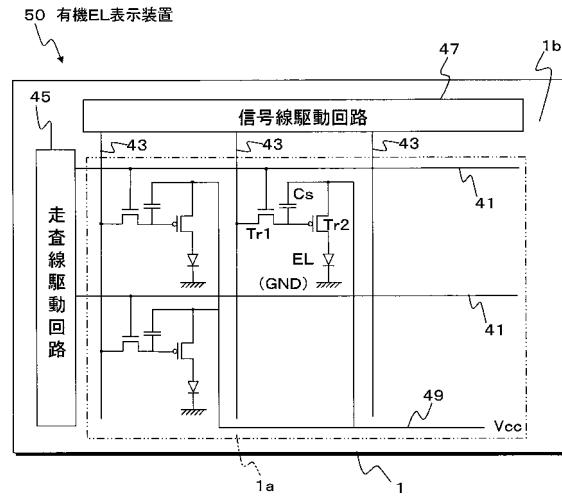

図8は有機EL表示装置の一構成例を説明するための概略の回路構成図である。この図に示すように、有機EL表示装置50の基板1上には、表示領域1aとその周辺領域1bとが設定されている。表示領域1aには、複数の走査線41と複数の信号線43とが縦横に配線されており、それぞれの交差部に対応して1つの画素が設けられた画素アレイ部として構成されている。また周辺領域1bには、走査線43を走査駆動する走査線駆動回路45と、輝度情報に応じた映像信号（すなわち入力信号）を信号線43に供給する信号線駆動回路47とが配置されている。10

#### 【0053】

走査線41と信号線43との各交差部に設けられる画素回路は、例えばスイッチング用の薄膜トランジスタTr1、駆動用の薄膜トランジスタTr2、保持容量Cs、および有機電界発光素子ELで構成されている。そして、走査線駆動回路45による駆動により、スイッチング用の薄膜トランジスタTr1を介して信号線43から書き込まれた映像信号が保持容量Csに保持され、保持された信号量に応じた電流が駆動用の薄膜トランジスタTr2から有機電界発光素子ELに供給され、この電流値に応じた輝度で有機電界発光素子ELが発光する。尚、駆動用の薄膜トランジスタTr2と保持容量Csとは、共通の電源供給線(Vcc)49に接続されている。20

#### 【0054】

尚、以上のような画素回路の構成は、あくまでも一例であり、必要に応じて画素回路内に容量素子を設けたり、さらに複数のトランジスタを設けて画素回路を構成しても良い。また、周辺領域1bには、画素回路の変更に応じて必要な駆動回路が追加される。

#### 【0055】

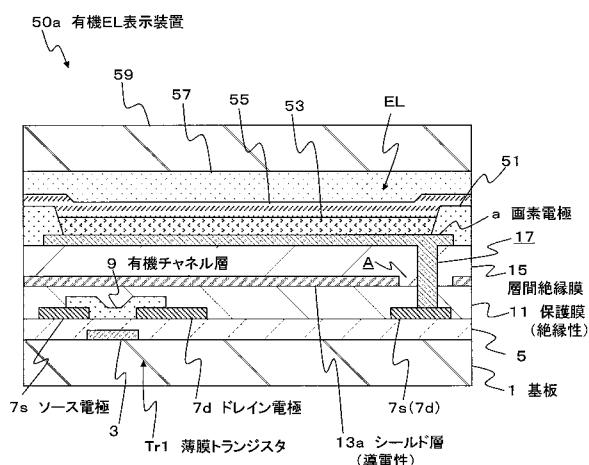

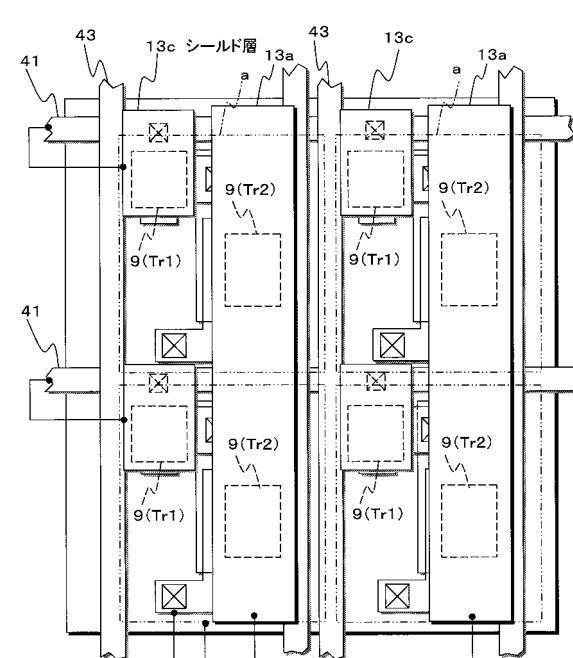

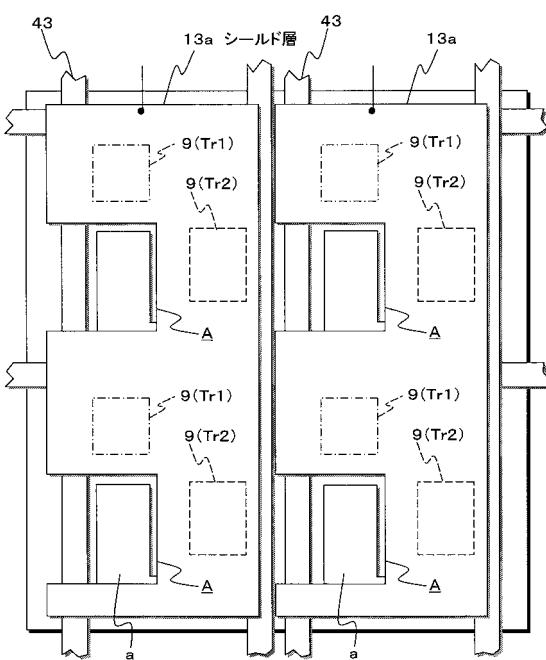

図9には、本第4実施形態の有機EL表示装置50aの特徴部を説明するための1画素分の断面図を示す。また図10には本第4実施形態の有機EL表示装置50aの特徴部を説明するための要部平面図を示す。尚、平面図は、説明のために一部を切り欠いており、さらに全体を覆う絶縁性材料からなる膜の図示を省略している。尚、図8と同一構成要素には同一符号を付している。30

#### 【0056】

これらの図に示すように、第4実施形態の有機EL表示装置50aにおける各画素には、第1実施形態の薄膜トランジスタと同一の積層構成からなるボトムゲート型の薄膜トランジスタTr1, Tr2、および保持容量Csが設けられている。尚、断面図においては薄膜トランジスタTr1のみを図示している。

#### 【0057】

そして、以上のような薄膜トランジスタTr1, Tr2および保持容量Csを覆う絶縁性の保護膜11上に、本第4実施形態に特徴的な導電性のシールド層13aが設けられている。このシールド層13aは、少なくとも薄膜トランジスタTr1, Tr2の有機チャネル層9上を覆う状態で設けられていることとし、特に本第4実施形態においては表示領域の全面を覆う状態で設けられていることとする。ただし、このシールド層13aには、薄膜トランジスタTr2のソース7s（またはドレイン電極7d）に臨む開口部Aが画素毎に設けられていることとする。40

#### 【0058】

このようなシールド層13aは、表示領域から周辺領域に引き出されて配線され、他の電極および配線に対して独立に電圧制御可能な構成となっている。

#### 【0059】

以上のようなシールド層13aを覆う層間絶縁膜15上には画素電極a（平面図では二点鎖線で図示）が設けられている。各画素電極aは、開口部Aの内側に設けたコンタクト50

部 17 を介して薄膜トランジスタ Tr 2 のソース 7 s (またはドレイン電極 7 d) に接続されている。この画素電極 a は、陽極または陰極として用いられるものであり、ここではさらに反射電極として形成されることとする。

#### 【 0 0 6 0 】

これらの画素電極 a は、中央部を広く露出させた状態で周縁部が画素間絶縁膜 5 1 で覆われている。この画素間絶縁膜 5 1 は、例えば有機絶縁材料をスピンドルコートやバーコーター等で塗布し、フォトリソグラフィーによって加工することで形成できる。そして、画素間絶縁膜 5 1 から露出している画素電極 a 上には、有機 EL 材料層 5 3 が所定の順序で積層成膜されている。この有機 EL 材料層 5 3 は、真空蒸着法やインクジェット法等により形成される。このとき、表示部に多色表示機能を付加したい場合には、画素ごとに表示色を塗り分ければ良い。10

#### 【 0 0 6 1 】

また、画素間絶縁膜 5 1 および有機 EL 材料層 5 3 上には、これらの層によって画素電極 a に対して絶縁性を保った状態で共通電極 5 5 が設けられている。この共通電極 5 5 は、画素電極 a と逆に陰極または陽極として用いられるものであり、ここではさらに透明電極として構成されていることとする。この共通電極 5 5 は、真空蒸着法やスパッタ法によって形成される。そして、画素電極 a と共通電極 5 5 とによって有機 EL 材料層 5 3 が挟持された各部分が、有機電界発光素子 EL として機能する部分になる。

#### 【 0 0 6 2 】

そして、以上のような共通電極 5 5 上に、光透過性を有する接着剤層 5 7 を介して透明基 5 9 が貼り合わせられ、有機 EL 表示装置 5 0 a が構成されている。なお、ここでの図示は省略したが、透明基板 5 9 側は、例えばカラーフィルタや反射防止膜などの画質改良のための層を有していてもよい。また、接着剤層 5 7 は必ずしもすべての画素上に均一に存在する必要はなく、例えば周辺領域のみに存在していてもよい。この場合、電極 5 3 と透明基板 5 9 の間には物理的空間が存在するが、動作に支障がない限りこれでもよい。20

#### 【 0 0 6 3 】

このような構成の有機 EL 表示装置 5 0 a は、有機電界発光素子 EL における発光光が透明基板 5 9 側から取り出されるトップエミッション型となる。

#### 【 0 0 6 4 】

そして、以上のような第 4 実施形態の構成の有機 EL 表示装置 5 0 a であっても、ボトムゲート型の薄膜トランジスタ Tr とその上部に配置された画素電極 a との間に導電性のシールド層 13 a が配置されている。このため、第 1 実施形態と同様に、ボトムゲート型の薄膜トランジスタ Tr における動作特性を安定した特性に維持することが可能になり、また画素電極 a に印加される電圧の安定化が図られるため、信頼性の高い表示を行うことが可能になる。また、表示領域のほぼ全面がシールド層 13 a で覆われた構成であるため、シールド層 13 a の高いガスバリア性によって有機チャネル層 9 の劣化が防止されて信頼性の向上を図ることができる。30

#### 【 0 0 6 5 】

さらに、薄膜トランジスタ Tr 1 , Tr 2 における有機チャネル層 9 に対向配置されたシールド層 13 a の電位を、他の電極に対して独立に制御することができるため、このシールド層 13 a に印加する電位によって薄膜トランジスタ Tr 1 , Tr 2 の動作特性を制御することができることも、第 1 実施形態と同様である。40

#### 【 0 0 6 6 】

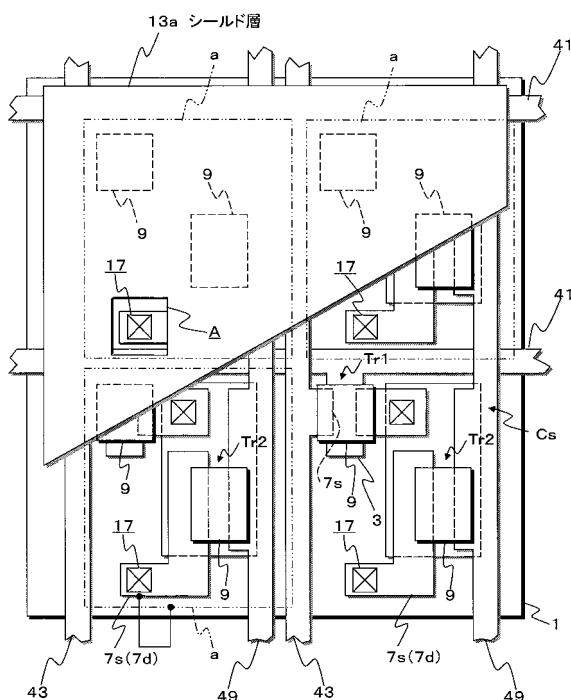

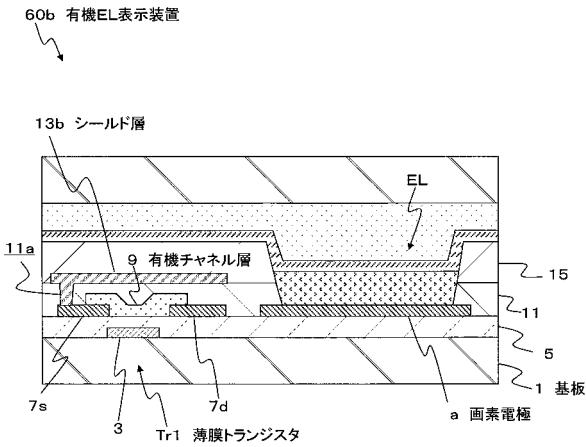

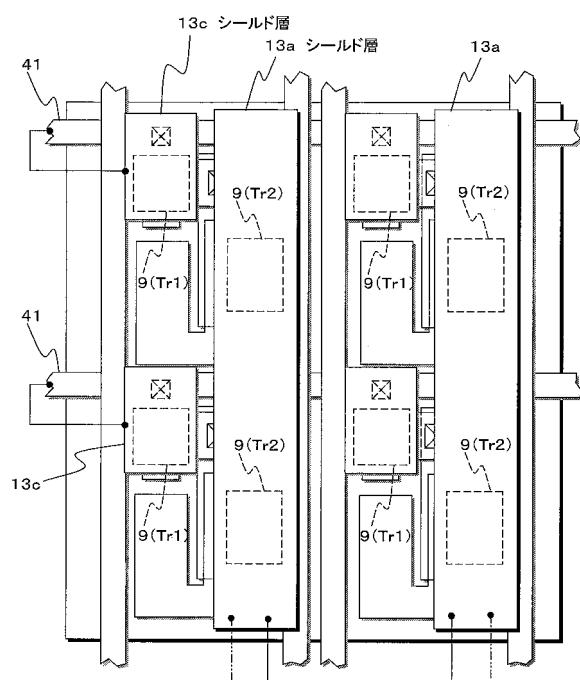

< 第 5 実施形態 >

図 1 1 には、本第 5 実施形態の有機 EL 表示装置 5 0 a の特徴部を説明するための駆動基板側の 4 画素分の平面図を示す。この図に示す第 5 実施形態は、第 4 実施形態の変形例的な実施形態である。

#### 【 0 0 6 7 】

図 1 1 に示すように、本第 5 実施形態においては、シールド層 13 a が薄膜トランジスタ Tr 1 の有機チャネル層 9 を覆う部分と、薄膜トランジスタ Tr 2 のチャネル層 9 を覆50

う部分とに分割されてパターン形成されている。そして、薄膜トランジスタTr1を覆うシールド層13aは、相互に接続され、表示領域から周辺領域に引き出されて配線され、他の電極および配線に対して独立に電圧制御可能な構成となっている。同様に、薄膜トランジスタTr2を覆うシールド層13aも、相互に接続され、表示領域から周辺領域に引き出されて配線され、他の電極および配線に対して独立に電圧制御可能な構成となっている。これ以外の構成は、第4実施形態と同様であることとする。

#### 【0068】

このような第5実施形態の構成の有機EL表示装置50aでは、各画素のスイッチング用の薄膜トランジスタTr1と、有機電界発光素子ELに流す電流を制御する駆動用の薄膜トランジスタTr2とを個別に覆う状態でパターニングされた各シールド層13aに、異なる電位を印加することができる。したがって、各薄膜トランジスタTr1, Tr2の動作特性を考慮した上で、それぞれの動作に見合った制御を行うことが可能となる。10

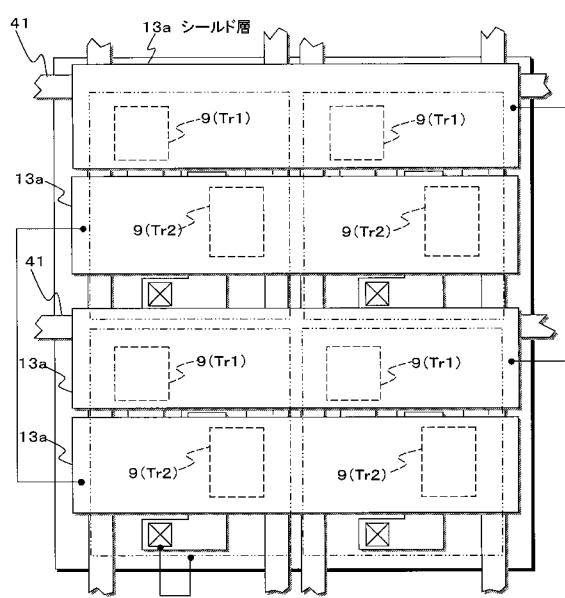

#### 【0069】

##### <第6実施形態>

図12には、第6実施形態の有機EL表示装置50aの特徴部を説明するための駆動基板側の4画素分の平面図を示す。この図に示す第6実施形態は、第4実施形態の変形例的な実施形態のさらに他の例である。

#### 【0070】

図12に示すように、本第6実施形態においては、シールド層13aが同色の光を取り出す画素毎に分割されてパターン形成されている。図示した例においては、信号線43に沿って赤、緑、青の各画素が配列されている例であり、信号線43に沿ってシールド層13aがパターニングされている場合を例示している。20

#### 【0071】

そして、パターニングされたシールド層13aは、各色毎に相互に接続され、表示領域から周辺領域に引き出されて配線され、他の電極および配線に対して独立に電圧制御可能な構成となっている。

#### 【0072】

そして、以上のような第6実施形態の構成の有機EL表示装置50aでは、赤、緑、青の各表示色毎にパターニングされた各シールド層13aに異なる電位を印加することができる。つまり、赤用のシールド層、緑用のシールド層、青用のシールド層を独立に制御することが可能になるため、例えばシールド層13aに印加する電位を制御することで色調補正を行うことが可能になる。30

#### 【0073】

##### <第7実施形態>

#### 【0074】

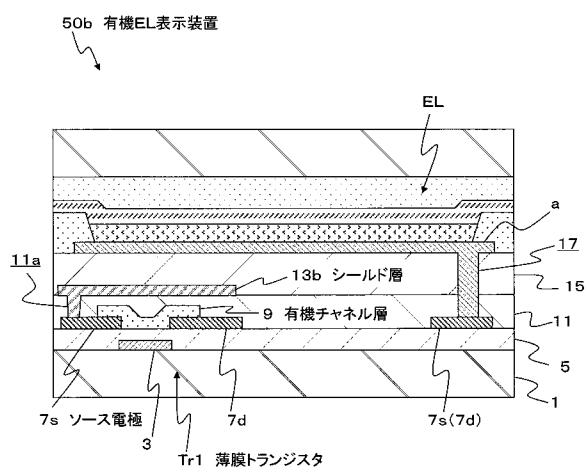

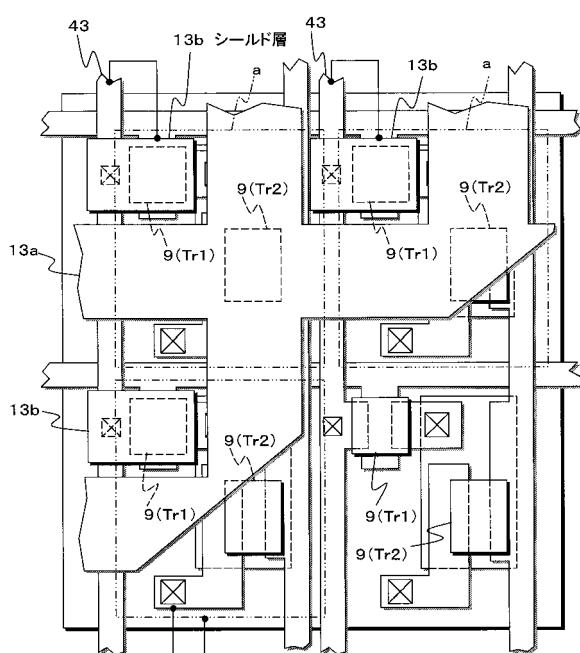

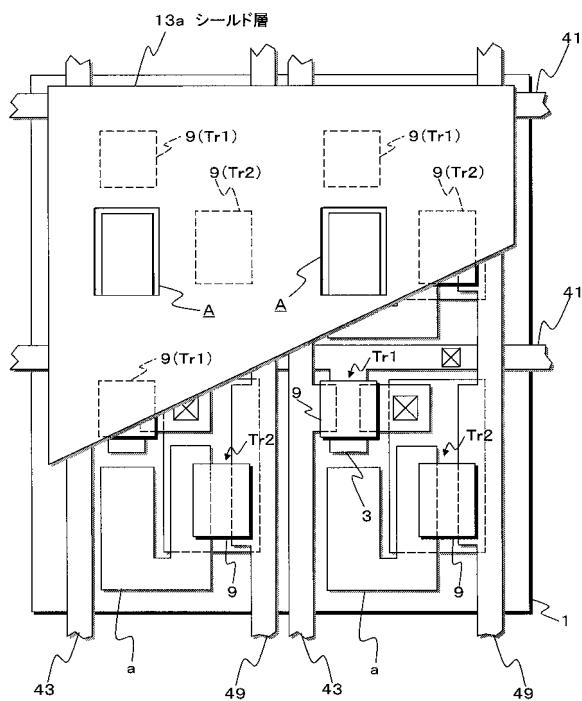

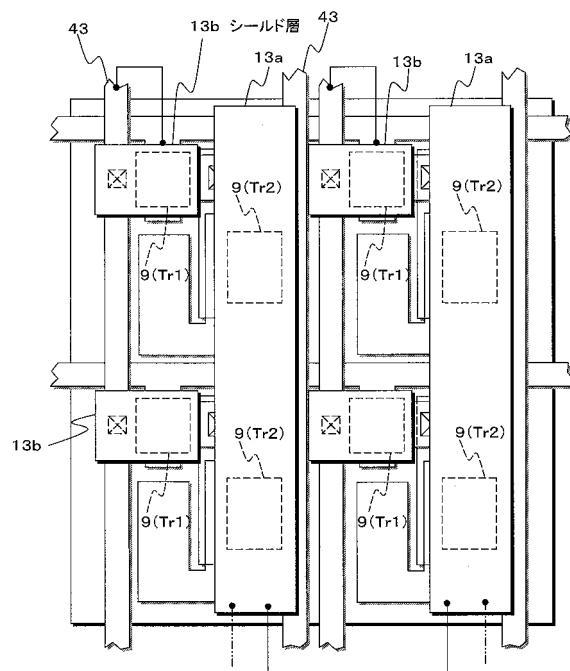

図13には、第7実施形態の有機EL表示装置50bの特徴部を説明するための1画素分の断面図を示す。また図14には第7実施形態の有機EL表示装置50bの特徴部を説明するための要部平面図を示す。尚、平面図は、説明のために一部を切り欠いており、さらに全体を覆う絶縁性材料からなる膜の図示を省略している。また、有機EL表示装置の一構成例を説明するための概略の回路構成は、第4実施形態において図8を用いて説明した構成と同様であって良く、上述した第4実施形態～第6実施形態と同一の構成要素には同一の符号を付して説明を行うこととする。40

#### 【0075】

これらの図に示す第7実施形態の有機EL表示装置50bが、図9を用いて説明した第4実施形態およびその他の実施形態の有機EL表示装置と異なるところは、シールド層13a, 13bの構成にあり、他の構成は同様であることとする。

#### 【0076】

すなわち第7実施形態の有機EL表示装置50bには、各画素に共通に設けられたシールド層13aによって薄膜トランジスタTr2が覆われている。このシールド層13aは、表示領域から周辺領域に引き出されて配線され、他の電極および配線に対して独立に電50

圧制御可能な構成となっている。

**【0077】**

また、各画素毎にパターニングされたシールド層13bによって薄膜トランジスタTr1が覆われている。これらのシールド層13bは、保護膜11に設けた接続孔とこの内部を埋め込む導電性材料とからなるコンタクト部11aを介して薄膜トランジスタTr1のソース電極7sに接続されている。ただし、このシールド層13bは、薄膜トランジスタTr1のソース電極7sに接続されていれば良いため、コンタクト部11aのレイアウトを考慮してソース電極7sから延設された信号線43の部分に接続されていても良い(平面図参照)。

**【0078】**

尚、各シールド層13bは、画素レイアウト上可能であれば1つの信号線43を共有する薄膜トランジスタTr1を覆う部分毎に分割されていても良く、少なくとも薄膜トランジスタTr1の有機チャネル層9を覆う状態で信号線43に沿ってパターニングされていても良い。この場合、1つの信号線43を共有する状態で複数の薄膜トランジスタTrを覆う各シールド層13bは、少なくとも1箇所で信号線43に接続されれば良く、その接続箇所が周辺領域であっても良い。この場合であっても、薄膜トランジスタTr2を覆うシールド層13aは、表示領域の周縁において相互に接続されて共通に駆動される構成であれば良い。

**【0079】**

以上のような第7実施形態の構成の有機EL表示装置50bでは、駆動用の薄膜トランジスタTr2のシールド層13aが全画素で共通になっているため、一度に全ての画素における駆動用の薄膜トランジスタTr2を制御して輝度を調整することが可能である。さらに、スイッチング用の薄膜トランジスタTr1の有機チャネル層9に対向配置されたシールド層13bをソース電極7sと接続させることにより、画素電極aの電位のTr1への影響をなくし、Tr1の安定動作と動作電圧低減が可能になる。

**【0080】**

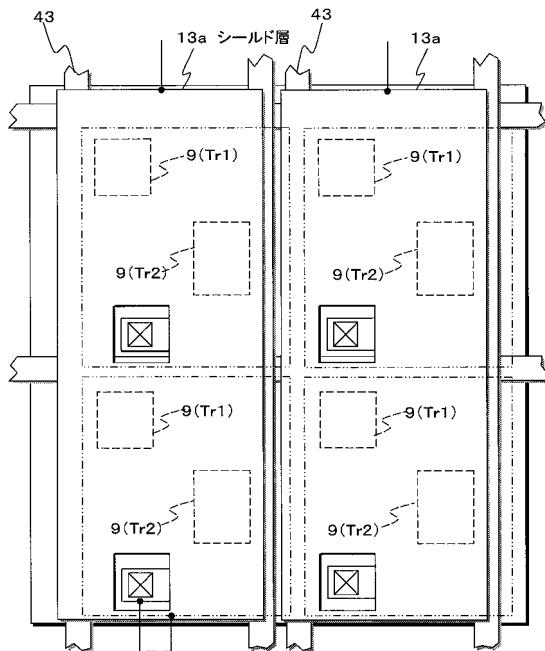

<第8実施形態>

図15には、本第8実施形態の有機EL表示装置50bの特徴部を説明するための駆動基板側の4画素分の平面図を示す。この図に示す第8実施形態は、第7実施形態の変形例的な実施形態である。

**【0081】**

図15に示すように、本第8実施形態においては、薄膜トランジスタTr2を覆うシールド層13aが同色の光を取り出す画素毎に分割されてパターン形成されている。図示した例においては、信号線43に沿って赤、緑、青の各画素が配列されている例であり、信号線43に沿ってシールド層13aがパターニングされている場合を例示している。

**【0082】**

またこのような構成においても、各シールド層13bは、1つの信号線43を共有する薄膜トランジスタTr1を覆う部分毎に分割されていても良く、少なくとも薄膜トランジスタTr1の有機チャネル層9を覆う状態で信号線43に沿ってパターニングされていても良い。そして、1つの信号線43を共有する状態で複数の薄膜トランジスタTrを覆う各シールド層13bは、少なくとも1箇所で信号線43に接続されれば良く、その接続箇所は周辺領域であっても良い。

**【0083】**

そして、以上のような第8実施形態の構成の有機EL表示装置50bでは、赤、緑、青の各表示色毎にパターニングされた各シールド層13aに異なる電位を印加することができる。つまり、赤用のシールド層、緑用のシールド層、青用のシールド層を独立に制御することが可能になるため、例えばシールド層13aに印加する電位を制御することで色調補正を行うことが可能になる。さらに、スイッチング用の薄膜トランジスタTr1の有機チャネル層9に対向配置されたシールド層13bをソース電極7sと接続させたことにより、画素電極aの電位のTr1への影響をなくし、Tr1の安定動作と動作電圧低減が可

10

20

30

40

50

能になる。

**【0084】**

<第9実施形態>

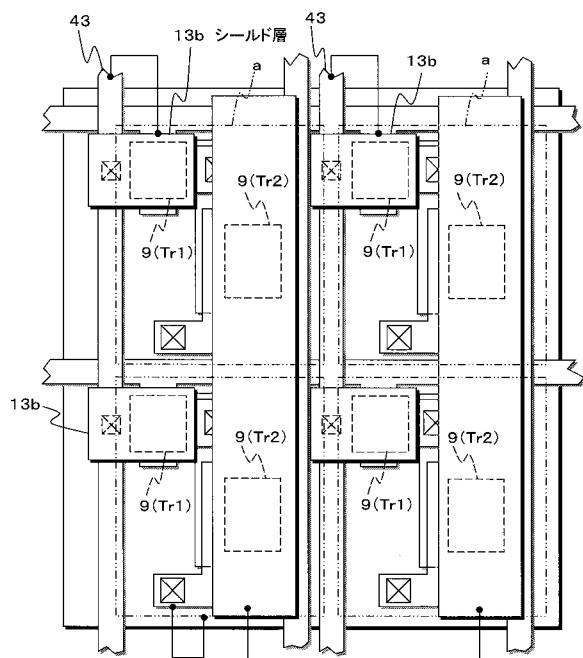

図16には、本第9実施形態の有機EL表示装置50cの特徴部を説明するための1画素分の断面図を示す。また図17には本第9実施形態の有機EL表示装置50cの特徴部を説明するための要部平面図を示す。尚、平面図は、説明のために一部を切り欠いており、さらに全体を覆う絶縁性材料からなる膜の図示を省略している。また、有機EL表示装置の一構成例を説明するための概略の回路構成は、第4実施形態において図8を用いて説明した構成と同様であって良く、上述した第4実施形態～第7実施形態と同一の構成要素には同一の符号を付して説明を行うこととする。

10

**【0085】**

これらの図に示す第9実施形態の有機EL表示装置50cが、図9を用いて説明した第4実施形態およびその他の実施形態の有機EL表示装置と異なるところは、シールド層13a, 13cの構成にあり、他の構成は同様であることとする。

**【0086】**

すなわち第9実施形態の有機EL表示装置50cには、各画素に共通に設けられたシールド層13aによって薄膜トランジスタTr2が覆われている。このシールド層13aは、表示領域から周辺領域に引き出されて配線され、他の電極および配線に対して独立に電圧制御可能な構成となっている。

20

**【0087】**

また、各画素毎にパターニングされたシールド層13cによって薄膜トランジスタTr1が覆われている。これらのシールド層13cは、保護膜11およびゲート絶縁膜5に設けた接続孔とこの内部を埋め込む導電性材料からなるコンタクト部5aを介して薄膜トランジスタTr1のゲート電極5に接続されている。ただし、このシールド層13cは、薄膜トランジスタTr1のゲート電極3に接続されなければ良いため、コンタクト部11aのレイアウトを考慮して走査線41の部分で接続されても良い(平面図参照)。

**【0088】**

尚、各シールド層13cは、画素レイアウト上可能であれば1つの走査線41を共有する薄膜トランジスタTrを覆う部分毎に分割されていても良く、少なくとも薄膜トランジスタTr1の有機チャネル層9を覆う状態で走査線41に沿ってパターニングされていても良い。この場合、1つの走査線41を共有する状態で複数の薄膜トランジスタTrを覆う各シールド層13cは、少なくとも1箇所で走査線41に接続されれば良く、その接続箇所は周辺領域であっても良い。この場合であっても、薄膜トランジスタTr2を覆うシールド層13aは、表示領域の周縁において相互に接続されて共通に駆動される構成であれば良い。

30

**【0089】**

以上のような構成の第9実施形態の有機EL表示装置50cでは、駆動用の薄膜トランジスタTr2のシールド層13aが全画素で共通になっているため、一度に全ての画素における駆動用の薄膜トランジスタTr2を制御して輝度を調整することが可能である。さらに、有機チャネル層9に対向配置されたシールド層13cをゲート電極3と接続させたことにより、Tr1に対する画素電極aの影響を排除すると同時にトランジスタの駆動能力が向上させることができる。

40

**【0090】**

<第10実施形態>

図18には、本第10実施形態の有機EL表示装置50cの特徴部を説明するための駆動基板側の4画素分の平面図を示す。この図に示す第10実施形態は、第9実施形態の変形例的な実施形態である。

**【0091】**

本第10実施形態においては、図18に示すように、薄膜トランジスタTr2を覆うシールド層13aが同色の光を取り出す画素毎に分割されてパターン形成されている。図示

50

した例においては、信号線 4 3 に沿って赤、緑、青の各画素が配列されている例であり、信号線 4 3 に沿ってシールド層 1 3 a がパターニングされている場合を例示している。

#### 【 0 0 9 2 】

そして、以上のような第 1 0 実施形態の構成の有機 E L 表示装置 5 0 c では、赤、緑、青の各表示色毎にパターニングされた各シールド層 1 3 a に異なる電位を印加することができる。つまり、赤用のシールド層、緑用のシールド層、青用のシールド層を独立に制御することが可能になるため、例えばシールド層 1 3 a に印加する電位を制御することで色調補正を行うことが可能になる。さらに、有機チャネル層 9 に対向配置されたシールド層 1 3 c をゲート電極 3 と接続させることにより、Tr 1 に対する画素電極 a の影響を排除すると同時にトランジスタの駆動能力が向上させることができる。

10

#### 【 0 0 9 3 】

##### < 第 1 1 実施形態 >

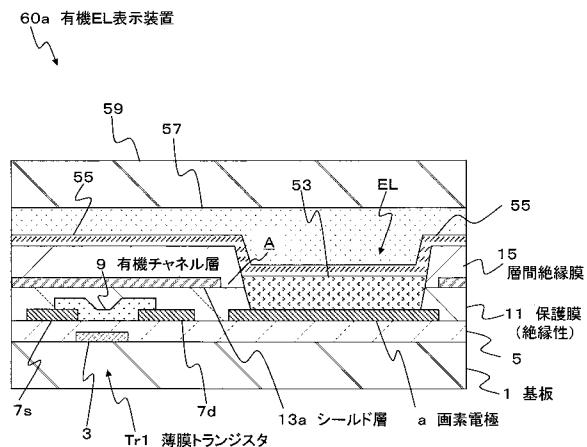

図 1 9 には、本第 1 1 実施形態の有機 E L 表示装置 6 0 a の特徴部を説明するための 1 画素分の断面図を示す。また図 2 0 には本第 1 1 実施形態の有機 E L 表示装置 6 0 a の特徴部を説明するための要部平面図を示す。尚、平面図は、説明のために一部を切り欠いており、さらに全体を覆う絶縁性材料からなる膜の図示を省略している。また、有機 E L 表示装置の一構成例を説明するための概略の回路構成は、第 4 実施形態において図 8 を用いて説明した構成と同様であって良く、上述した第 4 実施形態～第 1 0 実施形態と同一の構成要素には同一の符号を付して説明を行うこととする。

#### 【 0 0 9 4 】

20

これらの図に示す第 1 1 実施形態の有機 E L 表示装置 6 0 a が、図 9 および図 1 0 を用いて説明した第 4 実施形態のトップエミッション型の有機 E L 表示装置と異なるところは、画素電極 a の構成およびシールド層 1 3 a の構成にあり、他の構成は同様であることとする。

#### 【 0 0 9 5 】

すなわち第 1 1 実施形態の有機 E L 表示装置 6 0 a においては、薄膜トランジスタ Tr 1 , Tr 2 のソース電極 7 s およびドレイン電極 7 d と同一層で画素電極 a が構成されている。各画素電極 a は、薄膜トランジスタ Tr 2 のソース電極 7 s ( またはドレイン電極 7 d ) から延設された状態で設けられている。また、これらの画素電極 a は、陽極または陰極として用いられるものであるが、ここでは可視光に対する光透過性を有するかまたは半透過性を有する ( 可視光に対して有限の透過率を有する ) 導電性材料で形成されていることとする。このとき、画素電極 a は可視光に対して好ましくは 7 0 % 程度の透過率を持つことが好ましい。

30

#### 【 0 0 9 6 】

また、薄膜トランジスタ Tr 1 , Tr 2 および保持容量 C s を覆う絶縁性の保護膜 1 1 が、画素電極 a の中央部を広く露出させた状態で周縁部を覆う形状にパターニングされた画素間絶縁膜として形成されている。

#### 【 0 0 9 7 】

40

そして、この保護膜 1 1 上に設けられたシールド層 1 3 a は、少なくとも薄膜トランジスタ Tr 1 , Tr 2 の有機チャネル層 9 上を覆う状態で設けられていることとし、特に本第 1 1 実施形態においては画素電極 a を広く露出させる開口部 A が画素毎に設けられることとする。このようなシールド層 1 3 a は、表示領域から周辺領域に引き出されて配線され、他の電極および配線に対して独立に電圧制御可能な構成となっている。

#### 【 0 0 9 8 】

また、このシールド層 1 3 a を覆う層間絶縁膜 1 5 も、画素電極 a の中央部を広く露出させた状態で画素電極 a の周縁部を覆う形状にパターニングされた画素間絶縁膜として形成されている。ただし、層間絶縁膜 1 5 によってシールド層 1 3 a が完全に覆われた状態となっていることとする。

#### 【 0 0 9 9 】

このような画素間絶縁膜を構成する保護膜 1 1 と層間絶縁膜 1 5 とには、連続したバタ

50

ーンエッティングによって画素電極 a を露出させる開口部分を形成しても良い。

#### 【 0 1 0 0 】

尚、画素間絶縁膜から露出している画素電極 a 上に有機 E L 材料層 5 3 が積層成膜されていること、画素間絶縁膜と有機 E L 材料層 5 3 とによって画素電極 a に対して絶縁性を保った状態で共通電極 5 5 が設けられていること、そして、画素電極 a と共に電極 5 5 とで有機 E L 材料層 5 3 が挟持された各部分が有機電界発光素子 E L として機能することは、第 4 実施形態で説明したと同様である。ただし、共通電極 5 5 は、ここでは反射電極として構成されていることとする。

#### 【 0 1 0 1 】

このような構成の有機 E L 表示装置 6 0 a は、有機電界発光素子 E L における発光光が 10 画素電極 a を透過して基板 1 側から取り出されるボトムエミッション型となる。

#### 【 0 1 0 2 】

そして、以上のような第 1 1 実施形態の構成の有機 E L 表示装置 6 0 a では、ボトムゲート型の薄膜トランジスタ T r 1 , T r 2 とその上部に配置された共通電極 5 5 との間に導電性のシールド層 1 3 a が配置されている。このため、第 1 実施形態と同様の効果を得ることができ。すなわち、共通電極 5 5 に印加される電位に影響されることなく、ボトムゲート型の薄膜トランジスタ T r における動作特性を安定した特性に維持することができる。また画素電極 a に印加される電圧の安定化が図られるため、信頼性の高い表示を行うことが可能になる。また、表示領域のほぼ全面がシールド層 1 3 a で覆われた構成 20 であるため、シールド層 1 3 a の高いガスバリア性によって有機チャネル層 9 の劣化が防止されて信頼性の向上を図ることができる。

#### 【 0 1 0 3 】

さらに、薄膜トランジスタ T r 1 , T r 2 における有機チャネル層 9 に対向配置されたシールド層 1 3 a の電位を、他の電極に対して独立に制御することができるため、このシールド層 1 3 a に印加する電位によって薄膜トランジスタ T r 1 , T r 2 の動作特性を制御することが可能なことも、第 1 実施形態と同様である。

#### 【 0 1 0 4 】

##### < 第 1 2 実施形態 >

図 2 1 には、第 1 2 実施形態の有機 E L 表示装置 6 0 a の特徴部を説明するための駆動基板側の 4 画素分の平面図を示す。この図に示す第 1 2 実施形態は、第 1 1 実施形態の変形例的な実施形態である。 30

#### 【 0 1 0 5 】

図 2 1 に示すように、本第 1 2 実施形態においては、シールド層 1 3 a が薄膜トランジスタ T r 1 の有機チャネル層 9 を覆う部分と、薄膜トランジスタ T r 2 のチャネル層 9 を覆う部分とに分割されてパターン形成されている。そして、薄膜トランジスタ T r 1 を覆うシールド層 1 3 a は相互に接続され、表示領域から周辺領域に引き出されて配線され、他の電極および配線に対して独立に電圧制御可能な構成となっている。同様に、薄膜トランジスタ T r 2 を覆うシールド層 1 3 a も相互に接続され、表示領域から周辺領域に引き出されて配線され、他の電極および配線に対して独立に電圧制御可能な構成となっている。これ以外の構成は、第 1 1 実施形態と同様であることとする。 40

#### 【 0 1 0 6 】

このような第 2 1 実施形態の構成の有機 E L 表示装置 6 0 a では、各画素のスイッチング用の薄膜トランジスタ T r 1 と、有機電界発光素子 E L に流す電流を制御する駆動用の薄膜トランジスタ T r 2 を個別に覆う状態でパターニングされた各シールド層 1 3 a に、異なる電位を印加することができる。したがって、各薄膜トランジスタ T r 1 , T r 2 の動作特性を考慮した上で、それぞれの動作に見合った制御を行うことが可能となる。

#### 【 0 1 0 7 】

##### < 第 1 3 実施形態 >

図 2 2 には、第 1 3 実施形態の有機 E L 表示装置 6 0 a の特徴部を説明するための駆動基板側の 4 画素分の平面図を示す。この図に示す第 1 3 実施形態は、第 1 1 実施形態の変 50

形例的な実施形態のさらに他の例である。

**【0108】**

図22に示すように、本第13実施形態においては、シールド層13aが同色の光を取り出す画素毎に分割されてパターン形成されている。図示した例においては、信号線43に沿って赤、緑、青の各画素が配列されている例であり、信号線43に沿ってシールド層13aがパターニングされている場合を例示している。

**【0109】**

そして、パターニングされたシールド層13aは、各色毎に相互に接続され、表示領域から周辺領域に引き出されて配線され、他の電極および配線に対して独立に電圧制御可能な構成となっている。

10

**【0110】**

そして、以上のような第22実施形態の構成の有機EL表示装置60aでは、赤、緑、青の各表示色毎にパターニングされた各シールド層13aに異なる電位を印加することができる。つまり、赤用のシールド層、緑用のシールド層、青用のシールド層を独立に制御することが可能になるため、例えばシールド層13aに印加する電位を制御することで色調補正を行うことが可能になる。

**【0111】**

<第14実施形態>

図23には、第14実施形態の有機EL表示装置60bの特徴部を説明するための1画素分の断面図を示す。また図24には本第14実施形態の有機EL表示装置60bの特徴部を説明するための要部平面図を示す。尚、平面図は、説明のために一部を切り欠いており、さらに全体を覆う絶縁性材料からなる膜の図示を省略している。また、有機EL表示装置の一構成例を説明するための概略の回路構成は、第4実施形態において図8を用いて説明した構成と同様であって良く、上述した実施形態と同一の構成要素には同一の符号を付して説明を行うこととする。

20

**【0112】**

これらの図に示す第14実施形態の有機EL表示装置60bが、図19を用いて説明した第11実施形態およびその他の実施形態のボトムエミッション型の有機EL表示装置と異なるところは、シールド層13a, 13bの構成にあり、他の構成は同様であることとする。

30

**【0113】**

すなわち第14実施形態の有機EL表示装置60bには、各画素に共通に設けられたシールド層13aによって薄膜トランジスタTr2が覆われている。このシールド層13aは相互に接続され、表示領域から周辺領域に引き出されて配線され、他の電極および配線に対して独立に電圧制御可能な構成となっている。

**【0114】**

また、各画素毎にパターニングされたシールド層13bによって薄膜トランジスタTr1が覆われている。これらのシールド層13bは、保護膜11に設けた接続孔とこの内部を埋め込む導電性材料とからなるコンタクト部11aを介して薄膜トランジスタTr1のソース電極7sに接続されている。ただし、このシールド層13bは、薄膜トランジスタTr1のソース電極7sに接続されなければ良いため、コンタクト部11aのレイアウトを考慮してソース電極7sから延設された信号線43の部分に接続されていても良い(平面図参照)。

40

**【0115】**

尚、各シールド層13bは、画素レイアウト上可能であれば、1つの信号線43を共有する薄膜トランジスタTr1を覆う部分毎に分割されており、少なくとも薄膜トランジスタTr1の有機チャネル層9を覆う状態で信号線43に沿ってパターニングされていても良い。この場合、1つの信号線43を共有する状態で複数の薄膜トランジスタTrを覆う各シールド層13bは、少なくとも1箇所で信号線43に接続されれば良く、その接続箇所は周辺領域であっても良い。この場合であっても、薄膜トランジスタTr2を覆う

50

シールド層 13a は、表示領域の周縁において相互に接続されて共通に駆動される構成であれば良い。

**【 0 1 1 6 】**

以上のような第 14 実施形態の構成の有機 EL 表示装置 60b では、駆動用の薄膜トランジスタ Tr2 のシールド層 13a が全画素で共通になっているため、一度に全ての画素における駆動用の薄膜トランジスタ Tr2 を制御して輝度を調整することが可能である。さらに、スイッチング用の薄膜トランジスタ Tr1 の有機チャネル層 9 に対向配置されたシールド層 13b をソース電極 7s と接続させることにより、画素電極 a の電位の Tr1 への影響をなくし、Tr1 の安定動作と動作電圧低減が可能になる。

**【 0 1 1 7 】**

尚、本第 14 実施形態においては、少なくとも薄膜トランジスタ Tr2 の有機チャネル層 9 を覆う状態で設けられたシールド層 13a の電位が独立に制御できれば良い。このため、同色の光を取り出す画素毎にシールド層 13a が信号線 43 に沿ってパターニングされている場合、図中二点鎖線で示す端子により、各色毎にシールド層 13a に印加する電位を個別に制御する構成とすることもできる。これにより、赤、緑、青の各表示色毎にパターニングされた各シールド層 13a に異なる電位を印加することができる。つまり、赤用のシールド層、緑用のシールド層、青用のシールド層を独立に制御することが可能になるため、例えばシールド層 13a に印加する電位を制御することで色調補正を行うことが可能になる。

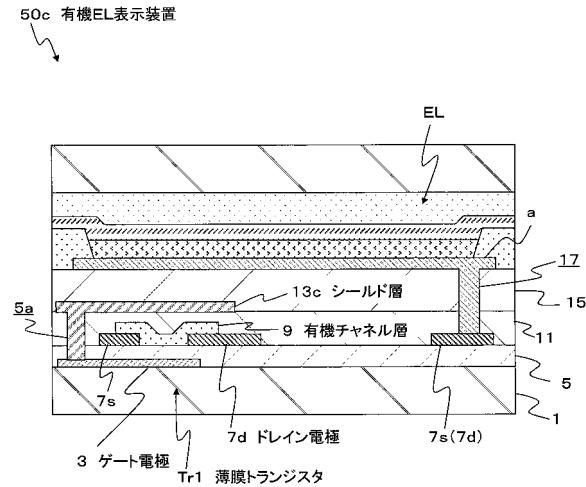

**【 0 1 1 8 】**

< 第 15 実施形態 >

図 25 には、第 15 実施形態の有機 EL 表示装置 60c の特徴部を説明するための 1 画素分の断面図を示す。また図 26 には本第 15 実施形態の有機 EL 表示装置 60c の特徴部を説明するための要部平面図を示す。尚、平面図は、説明のために一部を切り欠いており、さらに全体を覆う絶縁性材料からなる膜の図示を省略している。また、有機 EL 表示装置の一構成例を説明するための概略の回路構成は、第 4 実施形態において図 8 を用いて説明した構成と同様であって良く、上述した実施形態と同一の構成要素には同一の符号を付して説明を行うこととする。

**【 0 1 1 9 】**

これらの図に示す第 15 実施形態の有機 EL 表示装置 60c が、図 19 を用いて説明した第 11 実施形態およびその他の実施形態のボトムエミッション型の有機 EL 表示装置と異なるところは、シールド層 13a, 13c の構成にあり、他の構成は同様であることとする。

**【 0 1 2 0 】**

すなわち第 9 実施形態の有機 EL 表示装置 60c には、各画素に共通に設けられたシールド層 13a によって薄膜トランジスタ Tr2 が覆われている。このシールド層 13a は相互に接続され、表示領域から周辺領域に引き出されて配線され、他の電極および配線に対して独立に電圧制御可能な構成となっている。

**【 0 1 2 1 】**

また、各画素毎にパターニングされたシールド層 13c によって薄膜トランジスタ Tr1 が覆われている。これらのシールド層 13c は、保護膜 11 およびゲート絶縁膜 5 に設けた接続孔とこの内部を埋め込む導電性材料とからなるコンタクト部 5a を介して薄膜トランジスタ Tr1 のゲート電極 5 に接続されている。ただし、このシールド層 13c は、薄膜トランジスタ Tr1 のゲート電極 3 に接続されなければ良いため、コンタクト部 11a のレイアウトを考慮して走査線 41 の部分で接続されていても良い（平面図参照）。

**【 0 1 2 2 】**

尚、各シールド層 13c は、画素レイアウト上可能であれば、1つの走査線 41 を共有する薄膜トランジスタ Tr を覆う部分毎に分割されており、少なくとも薄膜トランジスタ Tr1 の有機チャネル層 9 を覆う状態で走査線 41 に沿ってパターニングされていても良い。この場合、1つの走査線 41 を共有する状態で複数の薄膜トランジスタ Tr を覆う各

10

20

30

40

50

シールド層 13c は、少なくとも 1箇所で走査線 41 に接続されていれば良く、その接続箇所は周辺領域であっても良い。この場合であっても、薄膜トランジスタ Tr2 を覆うシールド層 13a は、表示領域の周縁において相互に接続されて共通に駆動される構成であれば良い。

#### 【 0 1 2 3 】

以上のような構成の第 15 実施形態の有機 EL 表示装置 60c では、駆動用の薄膜トランジスタ Tr2 のシールド層 13a が全画素で共通になっているため、一度に全ての画素における駆動用の薄膜トランジスタ Tr2 を制御して輝度を調整することが可能である。さらに、有機チャネル層 9 に対向配置されたシールド層 13c をゲート電極 3 と接続させたことにより、Tr1 に対する画素電極 a の影響を排除すると同時にトランジスタの駆動能力が向上させることができる。10

#### 【 0 1 2 4 】

尚、本第 15 実施形態においては、少なくとも薄膜トランジスタ Tr2 の有機チャネル層 9 を覆う状態で設けられたシールド層 13a の電位が独立に制御できれば良い。このため、同色の光を取り出す画素毎にシールド層 13a が信号線 43 に沿ってパターニングされている場合、図中二点鎖線で示す端子により、各色毎にシールド層 13a に印加する電位を個別に制御する構成とすることもできる。これにより、赤、緑、青の各表示色毎にパターニングされた各シールド層 13a に異なる電位を印加することができる。つまり、赤用のシールド層、緑用のシールド層、青用のシールド層を独立に制御することができるため、例えばシールド層 13a に印加する電位を制御することで色調補正を行うことが可能になる。20

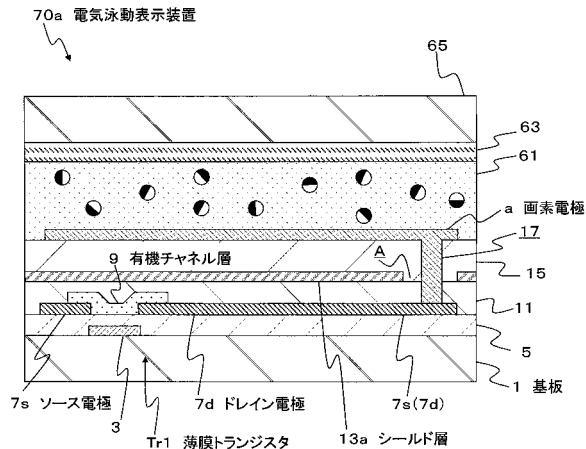

#### 【 0 1 2 5 】

##### < 第 16 実施形態 >

第 16 実施形態においては、アクティブマトリックス方式の電気泳動型表示装置に本発明を適用した実施の形態を説明する。

#### 【 0 1 2 6 】

図 27 には、第 16 実施形態の電気泳動型表示装置 70a の特徴部を説明するための 1 画素分の断面図を示す。尚、電気泳動型表示装置 70a の一構成例を説明するための概略の回路構成は、第 1 実施形態において図 1 を用いて説明した構成と同様であって良く、上述した実施形態と同一の構成要素には同一の符号を付して説明を行うこととする。30

#### 【 0 1 2 7 】

この電気泳動型表示装置 70a は、第 1 実施形態において図 2, 3 を用いて説明した液晶表示装置と同様に、基板 1 側から画素電極 a までが構成されている。

#### 【 0 1 2 8 】

つまり、薄膜トランジスタ Tr および保持容量 Cs を覆う絶縁性の保護膜 11 上に、少なくとも有機チャネル層 9 上を覆う状態で（ここでは表示領域の全面を覆う状態で）シールド層 13a が設けられており、シールド層 13a は、表示領域から周辺領域に引き出されて配線され、他の電極および配線に対して独立に電圧制御可能な構成となっている。

#### 【 0 1 2 9 】

そして、この画素電極 a 上を覆う状態で、シート状の電気泳動型表示部 61、画素電極 a に対向配置される共通電極 63、および透明基板 65 が設けられている。これらは、共通電極 63 および電気泳動型表示部 61 が積層成膜された透明基板 65 を、画素電極 a 側に貼り合わせる（ラミネーションする）ことによって基板 1 の上方に設けられている。40

#### 【 0 1 3 0 】

尚、ここでの図示は省略したが、透明基板 65 側には、例えばカラーフィルタや反射防止膜などの画質改良のための層が設けられていても良い。この場合、画素電極 a 上に透明基板 65 を貼り合わせた後に、これらの画質改良のための層が形成される。

#### 【 0 1 3 1 】

以上のような第 16 実施形態の構成の電気泳動表示装置（半導体装置）70a においては、第 1 実施形態の液晶表示装置と同様の効果を得ることができる。50

**【 0 1 3 2 】**

尚、本アクティブマトリックス型の電気泳動表示装置においても、シールド層を第2実施形態(図4,5)や第3実施形態(図6,7)と同様の構成とすることにより、これらの各実施形態と同様の効果を得ることが可能になる。

**【 0 1 3 3 】**

そして、以上説明した各実施形態では、液晶表示装置を例示して1個の薄膜トランジスタによってアクティブマトリックス型の画素回路が構成されている場合を説明し、有機EL表示装置を例示して2個の薄膜トランジスタによってアクティブマトリックス型の画素回路が構成されている場合を説明した。しかしながら、本発明はさらに3個以上の薄膜トランジスタによって画素回路が構成されている液晶表示装置、有機EL表示装置、電気泳動表示装置、さらには他のアクティブマトリックス型の表示装置にも適用可能であり、同様の効果を得ることができる。また3個以上の薄膜トランジスタによって画素回路が構成されている場合であれば、それぞれの機能の薄膜トランジスタ毎にシールド層を分割して良く、その分割のパターンや電極へ接続が適宜なされれば良い。10

**【 0 1 3 4 】**

つまり、画素回路を構成する薄膜トランジスタTrの数によらずに、各薄膜トランジスタの動作条件を考慮してシールド層の配線を工夫することにより、各薄膜トランジスタの役割に合わせた補償が可能になるのである。

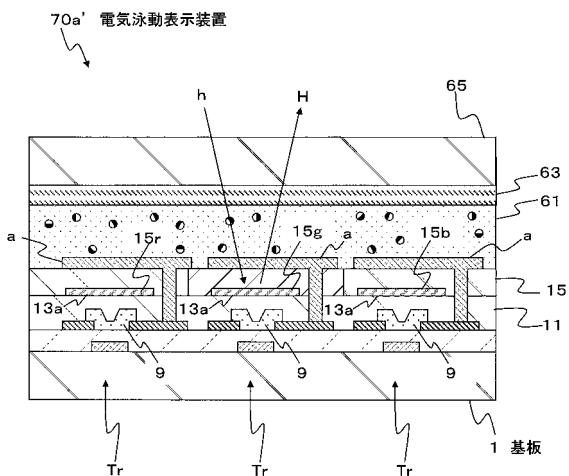

**【 0 1 3 5 】**

<第17実施形態>20

図28は、本発明を適用した電気泳動型表示装の断面図である。この図に基づいて、本発明を適用したカラー表示のアクティブマトリックス型表示装置の実施の形態を説明する。

**【 0 1 3 6 】**

この図に示す電気泳動表示装置70a'は、例えば光の3原色である赤色(R)画素、緑色(G)画素、および青色(B)画素を1組とし、複数組が基板1上に配列されている。各画素の構成が、第16実施形態と異なるところは、シールド層13aが反射材料からなるものに限定される点、これを覆う層間絶縁膜15が各画素毎に異なる構成で設けられている点、さらには画素電極aが透明電極で構成されている点にある。他の構成は第16実施形態と同様である。30

**【 0 1 3 7 】**

すなわちシールド層13aは、例えばアルミなどの可視光を反射する物質から構成されている。特に、このシールド層13aの可視光反射率が、表示性能を左右する重要な要因となる。従って、シールド層13aの可視光反射率を向上させるために、シールド層13a表面に不規則な凹凸を作製してもよい。

**【 0 1 3 8 】**

また、層間絶縁膜15は、赤色(R)画素、緑色(G)画素、および青色(B)画素毎に着色した各層間絶縁膜15r, 15g, 15bで構成されており、カラーフィルター機能(色選択機能)を有している。つまり、赤色(R)画素には赤色光のみを透過させるフィルター機能を備えた層間絶縁膜15rが設けられ、その他、各色の画素毎に同様の層間絶縁膜15g、15bが設けられているのである。尚、層間絶縁膜15r、15g、15bは、例えば表示光の色純度を高めるために、それぞれに適する膜厚、透過率、色合いに調整さえていることとする。40

**【 0 1 3 9 】**

このような層間絶縁膜15は、先ず各色に着色した層間絶縁膜を所定膜厚で塗布し、次にフォトリソグラフィー法などで必要部位のみが残るように加工する手順を、各色毎に3回繰り返し行うことによって形成される。

**【 0 1 4 0 】**

以上のような構成により、電気泳動表示装置70a'における透明基板65側から入射した外光hは、電気泳動型表示部61を通過し、さらに各画素の層間絶縁膜15r、15g、15bを透過する。50

g、15bを通過することで色選択されると共に、シールド層13aで反射して再び透明基板65側から各色光Hとして取り出される。

【0141】

これにより、本発明に特徴的に設けられるシールド層13aを反射層として用いたカラーディスプレイが可能になる。

【0142】

尚、上述した構成は、特に表示領域の全面を覆う状態で反射層となるシールド層13aが設けられた構成において有効であるが、アクティブマトリックス型の電気泳動表示装置のシールド層として、第2実施形態(図4,5)や第3実施形態(図6,7)で説明したシールド層を用いた構成にも適用可能である。

10

【0143】

<第18実施形態>

本第18実施形態においては、上述した各実施形態の表示装置のうち、各電極や配線に対して独立してシールド層の電位を制御することが可能な構成の表示装置においてのシールド層の制御の一例を説明する。

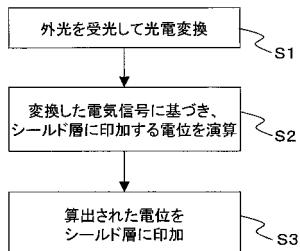

【0144】

図29には、このような制御を行うためのフローチャートを示した。ここでは、シールド層の電位制御により動作環境に応じた輝度での表示を行う手順を、フローチャートに沿って説明する。

20

【0145】

先ず第1ステップS1においては、受光素子によって表示装置の動作環境の明るさ(外光)を感知して光電変換する。

【0146】

次に、第2ステップS2においては、受光素子によって光電変換された電気信号に基づき、動作環境の明るさに適する輝度表示が行われるようにシールド電位に印加する電位を算出する。

【0147】

その後、第3ステップS3においては、算出された電位をシールド層に印加して表示を行う。

【0148】

30

以上のような制御を行うために、本発明のシールド層を設けた表示装置の周辺領域には、ステップ1の光電変換を行うための受光素子、およびステップS2の処理を行うための画面輝度制御回路が設けられていることとする。

【0149】

以上のような制御を行うことにより、動作環境(暗い・明るい)に応じた輝度が得られるように、シールド層に適切な電位を印加した表示を行うことが可能になる。

【0150】

尚、上述した各第1～第18実施形態においては、本発明を表示装置に適用した構成を説明した。しかしながら本発明は、表示装置への適用に限定されることはなく、ボトムゲート型の薄膜トランジスタ上に絶縁膜を介して配線や電極が設けられている構成であれば、メモリーやセンサー等の半導体装置に広く適用可能である。

40

【0151】

このような構成の半導体装置において、薄膜トランジスタと電極との間に、絶縁性を保つ導電性のシールド層が配置することにより、薄膜トランジスタの動作特性を安定化させることができるのである。またトランジスタの負荷動作に伴う特性変動(バイアスストレスによる閾値変動)をシールド層に加える電位で補償できるため、トランジスタの長寿命化を達成することが可能である。さらに、シールド層としてガスバリア性のよい金属を用いることにより保護膜のガスバリア性を強化でき、トランジスタのストレージライフを改善できる。

【0152】

50

また、これらのトランジスタに関する効果は、上述した表示装置の実施形態に対して同様に得られる効果もある。

【図面の簡単な説明】

【0153】

【図1】本発明が適用される液晶表示装置の一構成例を説明するための概略の回路構成図である。

【図2】第1実施形態の液晶表示装置の特徴部を説明するための1画素分の断面図である。

【図3】第1実施形態の液晶表示装置の特徴部を説明するための駆動基板側の4画素分の平面図である。

10

【図4】第2実施形態の液晶表示装置の特徴部を説明するための1画素分の断面図である。

【図5】第2実施形態の液晶表示装置の特徴部を説明するための駆動基板側の4画素分の平面図である。

【図6】第3実施形態の液晶表示装置の特徴部を説明するための1画素分の断面図である。

【図7】第3実施形態の液晶表示装置の特徴部を説明するための駆動基板側の4画素分の平面図である。

20

【図8】本発明が適用される有機EL表示装置の一構成例を説明するための概略の回路構成図である。

【図9】第4実施形態の有機EL表示装置の特徴部を説明するための1画素分の断面図である。

【図10】第4実施形態の有機EL表示装置の特徴部を説明するための4画素分の要部平面図である。

【図11】第5実施形態の有機EL表示装置の特徴部を説明するための4画素分の要部平面図である。

【図12】第6実施形態の有機EL表示装置の特徴部を説明するための4画素分の要部平面図である。

【図13】第7実施形態の有機EL表示装置の特徴部を説明するための1画素分の断面図である。

30

【図14】第7実施形態の有機EL表示装置の特徴部を説明するための4画素分の要部平面図を示す。

【図15】第8実施形態の有機EL表示装置の特徴部を説明するための4画素分の要部平面図を示す。

【図16】第9実施形態の有機EL表示装置の特徴部を説明するための1画素分の断面図である。

【図17】第9実施形態の有機EL表示装置の特徴部を説明するための4画素分の要部平面図を示す。

【図18】第10実施形態の有機EL表示装置の特徴部を説明するための4画素分の要部平面図を示す。

40

【図19】第11実施形態の有機EL表示装置の特徴部を説明するための1画素分の断面図である。

【図20】第11実施形態の有機EL表示装置の特徴部を説明するための4画素分の要部平面図を示す。

【図21】第12実施形態の有機EL表示装置の特徴部を説明するための4画素分の要部平面図である。

【図22】第13実施形態の有機EL表示装置の特徴部を説明するための4画素分の要部平面図である。

【図23】第14実施形態の有機EL表示装置の特徴部を説明するための1画素分の断面図である。

50

【図24】第14実施形態の有機EL表示装置の特徴部を説明するための4画素分の要部平面図を示す。

【図25】第15実施形態の有機EL表示装置の特徴部を説明するための1画素分の断面図である。

【図26】第15実施形態の有機EL表示装置の特徴部を説明するための4画素分の要部平面図を示す。

【図27】第16実施形態の電気泳動表示装置の特徴部を説明するための1画素分の断面図である。

【図28】第17実施形態を説明する断面図である。

【図29】第18実施形態を説明する断面図である。

10

#### 【符号の説明】

##### 【0154】

1...基板、3...ゲート電極、7s...ソース電極、9...有機チャネル層、11...保護膜(絶縁膜)、13a, 13b, 13c...シールド層(導電性)、15...層間絶縁膜、40a, 40b, 40c...液晶表示装置、50a, 50b, 50c...有機EL表示装置(トップエミッション型)、53...共通電極、60a, 60b, 60c...有機EL表示装置(ボトムエミッション型)、70a...電気泳動表示装置、a...画素電極、Tr...薄膜トランジスタ(ボトムゲート型)

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図 19】

【図 20】

【図 21】

【図 22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

---

フロントページの続き

(51)Int.Cl.

F I

G 0 9 F 9/30 3 3 8

G 0 2 F 1/1368

(72)発明者 湯本 昭

東京都品川区北品川6丁目7番35号 ソニー株式会社内

審査官 河本 充雄

(56)参考文献 特開2004-103488 (JP, A)

特開2000-352941 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 0 1 L 2 9 / 7 8 6

H 0 1 L 2 1 / 3 3 6

H 0 1 L 5 1 / 0 5

G 0 2 F 1 / 1 3 6 8

G 0 9 F 9 / 3 0