## 【請求項 5】

前記誘電体材料は  $\text{Al}_2\text{O}_3$  よりなり、前記気相分子化合物は  $\text{Al}(\text{1}-\text{OC}_3\text{H}_7)_3$  および  $(\text{CH}_3)_3\text{Al}$  のいずれかであることを特徴とする請求項 1 記載の誘電体膜の形成方法。

## 【請求項 6】

前記気相分子化合物を分解させる工程は、前記気相分子化合物で覆われた前記  $\text{Si}$  基板を、前記気相分子化合物の熱分解温度を超える温度に加熱する工程よりなることを特徴とする請求項 1 ~ 5 のうち、いずれか一項記載の誘電体膜の形成方法。

## 【請求項 7】

前記気相分子化合物を分解させる工程は、前記気相分子化合物で覆われた前記基板を、

$\text{H}_2\text{O}$ ,  $\text{O}_3$ ,  $\text{NO}_2$  のいずれかより選ばれる雰囲気に曝露する工程を含むことを特徴とする請求項 1 ~ 6 のうち、いずれか一項記載の誘電体膜の形成方法。

## 【請求項 8】

前記  $\text{Si}$  基板表面に前記絶縁性層を形成する工程は、 $\text{Si}$  基板表面に  $\text{Si}$  の気相分子化合物を吸着させ、前記  $\text{Si}$  基板表面を前記  $\text{Si}$  の気相分子化合物により、少なくとも 1 回、実質的に一様に覆う工程と、前記  $\text{Si}$  の気相分子化合物を加水分解する工程とを含み、前記  $\text{Si}$  の気相分子化合物は、 $\text{SiCl}_4$ ,  $\text{SiH}_2\text{Cl}_2$ , および  $\text{Si}(\text{OC}_2\text{H}_5)_5$  よりなる群より選ばれることを特徴とする請求項 1 ~ 7 のうち、いずれか一項記載の誘電体膜の形成方法。

## 【請求項 9】

前記  $\text{Si}$  基板表面に前記絶縁性層を形成する工程は、前記  $\text{Si}$  基板表面を熱酸化する工程を含むことを特徴とする請求項 1 ~ 8 のうち、いずれか一項記載の誘電体膜の形成方法。

## 【請求項 10】

前記誘電体材料の分子層を形成する工程は、前記絶縁性分子層上に、組成が  $\text{ZrSiO}_4$  で表される誘電体膜を形成する工程を含み、前記誘電体膜を形成する工程は、前記  $\text{Si}$  基板界面において  $\text{Zr}$  濃度が低く、前記  $\text{Si}$  基板界面から離れるにつれて徐々に増大するように実行されることを特徴とする請求項 1 ~ 9 のうち、いずれか一項記載の誘電体膜の形成方法。

## 【請求項 11】

前記誘電体膜を形成する工程は、 $\text{SiO}_2$  分子層と  $\text{ZrO}_2$  分子層とを順に堆積する工程を含み、前記  $\text{SiO}_2$  分子層を形成する工程は、下地層上に  $\text{Si}$  を含む第 1 の気相原料分子を吸着させる工程と、前記第 1 の気相原料分子を分解させる工程とを含み、一方前記  $\text{ZrO}_2$  分子層を形成する工程は、下地層上に  $\text{Zr}$  を含む第 2 の気相原料分子を吸着させる工程と、前記第 2 の気相原料分子を分解する工程とを含むことを特徴とする請求項 10 記載の誘電体膜の形成方法。

## 【請求項 12】

前記絶縁性層を形成する工程の前に、前記  $\text{Si}$  基板の表面を露出する工程を含む請求項 1 記載の誘電体膜の形成方法。

## 【請求項 13】

前記気相分子化合物を分解する工程は、加水分解により前記気相分離化合物を分解する工程である請求項 1 記載の誘電体膜の形成方法。

## 【発明の詳細な説明】

## 【0001】

## 【発明の属する技術分野】

本発明は半導体装置に係り、特に高誘電体膜を有する、超微細化高速半導体装置の製造方法に関する。

## 【0002】

今日の超高速高速半導体装置では、微細化プロセスの進歩とともに、 $0.1 \mu\text{m}$  以下のゲート長が可能になりつつある。一般に微細化とともに半導体装置の動作速度は向上するが

10

20

30

40

50

、このように非常に微細化された半導体装置では、ゲート絶縁膜の膜厚を、微細化によるゲート長の短縮に伴って、スケーリング則に従って減少させる必要がある。

### 【0003】

#### 【従来の技術】

しかしゲート長が $0.1\mu\text{m}$ 以下になると、ゲート絶縁膜の厚さも、 $\text{SiO}_2$ を使った場合、 $1\sim2\text{nm}$ 、あるいはそれ以下に設定する必要があるが、このように非常に薄いゲート絶縁膜ではトンネル電流が増大し、その結果ゲートリーケ電流が増大する問題を回避することができない。このため、例えば特開平11-87341号公報に記載されているように、 $\text{Si}$ 基板表面に非常に薄い $\text{SiN}$ 膜を、前記 $\text{Si}$ 基板表面に $\text{Si}$ を含む気相原料を吸着させ、ついでこれに $\text{N}$ のラジカルを含む雰囲気を作成させることにより形成することができる。しかし、 $\text{SiN}$ 膜の比誘電率は $\text{SiO}_2$ 膜の比誘電率よりは大きいものの、8程度でしかなく、このため $\text{SiN}$ 膜を使った場合には、スケーリング則による微細化の要請を満足し、しかもトンネル電流を効果的に遮断できるような実質的な膜厚にゲート絶縁膜を形成することはできない。また、前記特開平11-87341号公報に記載の方法では、 $\text{N}$ のラジカルを発生させるためにプラズマを発生させる必要があるが、プラズマ発生源の近傍において基板表面を処理すると、プラズマに起因する電子やイオンなどの荷電粒子が $\text{SiN}$ 膜中に取り込まれて準位を形成するため、得られる $\text{SiN}$ 膜のリーク電流特性および $\text{CV}$ 特性が劣化してしまう。一方、この問題を回避しようとしてプラズマ発生源を前記基板から離れた位置に設けると、必要な $\text{N}$ ラジカルの量が大きく減少してしまい、 $\text{N}$ の吸着を行うことが難しくなる。

10

20

### 【0004】

このような事情で従来より、比誘電率が $\text{SiO}_2$ 膜のものよりもはるかに大きく、このため実際の膜厚が大きくても $\text{SiO}_2$ 膜に換算した場合の膜厚が小さい $\text{Ta}_2\text{O}_5$ のような高誘電体材料をゲート絶縁膜に対して適用することが提案されている。このような $\text{Ta}_2\text{O}_5$ などの高誘電体材料を使うことにより、ゲート長が $0.1\mu\text{m}$ 以下と、非常に短い超高速半導体装置においても $10\mu\text{m}$ 程度の膜厚のゲート絶縁膜を使うことができ、トンネル効果によるゲートリーケ電流を抑制することができる。

### 【0005】

従来より、 $\text{Ta}_2\text{O}_5$ 膜は $\text{Ta}(\text{OC}_2\text{H}_5)_5$ および $\text{O}_2$ を気相原料とした $\text{CVD}$ 法により形成できることが知られている。典型的な場合、 $\text{CVD}$ プロセスは減圧環境下、約 $480^\circ\text{C}$ 、あるいはそれ以上の温度で実行される。このようにして形成された $\text{Ta}_2\text{O}_5$ 膜は、さらに酸素雰囲気中において熱処理され、その結果、膜中の酸素欠損が解消され、また膜自身が結晶化する。このようにして結晶化された $\text{Ta}_2\text{O}_5$ 膜は大きな比誘電率を示す。

30

### 【0006】

#### 【発明が解決しようとする課題】

一方、 $\text{Ta}_2\text{O}_5$ 等の高誘電体膜を $\text{CVD}$ 法により $\text{Si}$ 基板上に成長させる場合、核生成過程に関連して、 $\text{CVD}$ プロセスを開始しても直ちには高誘電体膜の堆積は始まらず、あるインキュベーション時間が経過した後で初めて膜の堆積が始まることが知られている。

### 【0007】

本発明の基礎となる実験において、本発明の発明者は、このインキュベーション時間が前記高誘電体膜を堆積する下地の性質によって変化することを見出した。例えば、下地が酸化膜を除去された清浄な $\text{Si}$ 基板であれば、インキュベーション時間はわずかであるが、 $\text{Si}$ 基板の表面に $\text{SiO}_2$ 膜あるいは $\text{SiN}$ 膜、あるいは $\text{SiON}$ 膜が存在していると、インキュベーション時間は増大する。また、インキュベーション時間は、かかる $\text{SiO}_2$ 膜、 $\text{SiN}$ 膜あるいは $\text{SiON}$ 膜の膜厚にも依存することが見出された。このことは、 $\text{SiO}_2$ 膜、 $\text{SiN}$ 膜あるいは $\text{SiON}$ 膜上に形成される高誘電体膜の膜厚が、下地膜の膜厚の変動を受け、その結果、下地膜の膜厚変動が増幅される傾向があることを意味する。また、このように $\text{CVD}$ 法により形成される高誘電体膜の膜厚が下地の影響を受けるということは、ゲート絶縁膜等に使われる高誘電体膜の膜質が、不均一になりやすいことを意味している。

40

50

## 【0008】

このような高誘電体膜中における膜質の不均一を抑制するには、インキュベーション時間可能な限り減少させるのが望ましい。

## 【0009】

さらに、かかる高誘電体膜をゲート絶縁膜に使った半導体装置では、高誘電体膜を直接に Si 基板上に形成した方が、絶縁膜の SiO<sub>2</sub>換算実効膜厚を減少させるためには好ましいものの、ゲートチャネル中のキャリアモビリティーを向上させる観点からは、高誘電体ゲート酸化膜と Si 基板との間に、きわめて薄い酸化膜を介在させるのが好ましい。その際、前記高誘電体膜を使うことによる効果を最大化するためには、かかる高誘電体膜の膜質、特に組成を、膜厚方向に変化させることのできる技術が必要になる。前記酸化膜の厚さが厚い場合、あるいは前記高誘電体膜中に実質的な厚さにわたり、Si に富む領域が形成されている場合、高い誘電率を特徴とする高誘電体膜の効果は実質的に減少してしまう。

10

## 【0010】

そこで、本発明は上記の課題を解決した、新規で有用な誘電体膜の形成方法を提供することを具体的な課題とする。

## 【0011】

本発明のより具体的な課題は、気相堆積法による誘電体膜の形成方法において、前記誘電体膜への荷電粒子によるダメージの問題を発生させることなく、前記誘電体膜堆積の際のインキュベーション時間を最小にし、また表面ラフネスを低減することにある。

20

## 【0012】

本発明の他の課題は、気相堆積法による誘電体膜の形成方法において、前記誘電体膜への荷電粒子によるダメージの問題を発生させることなく、前記誘電体膜の膜厚方向における組成分布を自在に制御できる方法を提供することにある。

## 【0013】

## 【課題を解決するための手段】

本発明は、上記の課題を Si 基板上への誘電体膜の形成方法において、

前記 Si 基板上に絶縁性層を形成する工程と、

前記絶縁性層上に少なくとも 1 回、金属元素の気相分子化合物を実質的に一様に吸着させ、前記絶縁性層上を前記気相分子化合物により覆う工程と、

30

前記絶縁層を覆う前記気相分子化合物を酸化雰囲気中で分解し、前記絶縁層上に前記金属元素を含む誘電体材料の分子層を形成する工程と、を含み、

前記気相分子化合物を分解させる工程の後、前記誘電体の分子層上に高誘電体膜を CVD 法により形成する工程を含むことを特徴とする誘電体膜の形成方法により、解決する。

## 【0014】

## 【発明の実施の形態】

## [第1実施例]

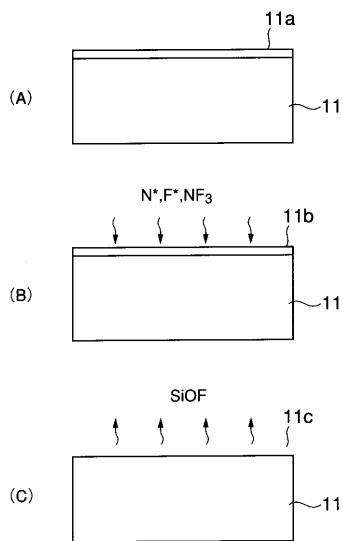

図 1 (A) ~ (C) は、本発明の第 1 実施例による、Ta<sub>2</sub>O<sub>5</sub> 膜の形成方法を示す。

40

## 【0015】

図 1 (A) を参照するに、Si 基板 11 は 133 ~ 399 Pa (1 ~ 3 Torr) の内圧に減圧された反応容器 (図示せず) 中に室温よりも低い温度で保持されており、この状態で前記反応容器中に、N<sub>2</sub> と H<sub>2</sub> の混合ガスのプラズマ活性化により形成した窒素ラジカル N\* と水素ラジカル H\* を、NF<sub>3</sub> ガスと共に供給することにより、前記 Si 基板 11 表面の酸化膜 11a を除去する。かかる酸化膜除去工程を低温で行うことにより、前記 Si 基板 11 表面には、図 1 (B) に示すように、前記酸化膜 11a の除去と同時に、N-O-Si-H の組成を有する保護膜 11b が形成される。典型的には H<sub>2</sub>, NF<sub>3</sub> および N<sub>2</sub> ガスを、それぞれ 10 sccm, 30 sccm および 100 sccm の流量で供給し、H<sub>2</sub> ガスと N<sub>2</sub> ガスのプラズマ活性化を 50 W のプラズマ電力により行う。図 1 (A) の酸化膜除去処理は 3 分間程度で十分である。

50

## 【0016】

このようにして形成された保護膜11bは揮発性の膜であり、図1(C)の工程において前記Si基板11を前記反応容器中において引き続き真空中、約120°Cの温度で熱処理することにより容易に昇華・除去され、その結果Si基板11においては、新鮮なSi表面11cが露出される。

## 【0017】

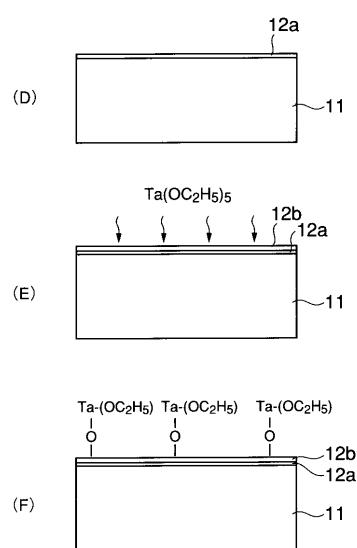

次に図2(D)の工程において、前記反応容器の内圧を1.33~13.3Pa(0.01~0.1Torr)に、また基板温度を200~350°Cに設定し、図1(C)の工程に連続して前記反応容器中にSiCl<sub>4</sub>ガスを流量が約50sccmのHeキャリアガスと共に0.1~5mg/minの割合で導入し、前記Si基板表面11cにSiCl<sub>4</sub>分子を吸着させる。さらに、前記反応容器中にH<sub>2</sub>Oを前記Heキャリアガスと共に約1sccmの流量で導入し、前記Si基板表面11cに吸着しているSiCl<sub>4</sub>分子を加水分解する。その結果、前記Si基板11の表面に非常に薄い、典型的には1~数分子層のSiO<sub>2</sub>を含むSiO<sub>2</sub>分子層12aが形成される。図1(D)の工程では、必要に応じて前記SiCl<sub>4</sub>ガスの導入工程および吸着されたSiCl<sub>4</sub>分子の加水分解工程を繰り返すことにより、前記SiO<sub>2</sub>分子層12aを所望の厚さに形成することも可能である。また、図1(D)の工程において前記Si基板11の表面11cに吸着したSiCl<sub>4</sub>分子をNH<sub>3</sub>ガスにより処理することにより、SiN分子層を、前記SiO<sub>2</sub>分子層12aの代わりに形成することもできる。また、前記SiO<sub>2</sub>分子層とSiN分子層とを適宜積層することにより、前記SiO<sub>2</sub>分子層12aのかわりにSiON分子層を形成することもできる。また、通常の熱酸化によるSiO<sub>2</sub>膜も、プロセス制御に関連して豊富なデータが利用できるため、実用上、使用可能である。

## 【0018】

次に図2(E)の工程において、基板温度を350°C以下、好ましくは約300°C以下、より好ましくは約280°Cに設定し、内圧を前と同じく0.01~0.1Torrに設定された前記反応容器中にTa(O<sub>2</sub>C<sub>2</sub>H<sub>5</sub>)O<sub>5</sub>ガスとO<sub>2</sub>ガスとを、Heキャリアガスと共に、それぞれ約5mg/minおよび100sccmの流量で1分間程度供給する。Heキャリアガスの流量は、約100sccmに設定する。その結果、図2(F)に示すように、前記SiO<sub>2</sub>膜12a上に前記Ta(O<sub>2</sub>C<sub>2</sub>H<sub>5</sub>)O<sub>5</sub>分子が吸着され、Ta(O<sub>2</sub>C<sub>2</sub>H<sub>5</sub>)O<sub>5</sub>吸着分子層12bが前記SiO<sub>2</sub>分子層12a上に形成される。

## 【0019】

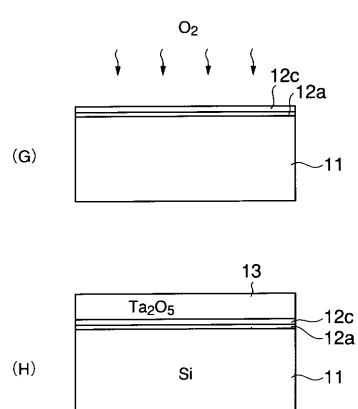

さらに図3(G)の工程において前記基板温度をO<sub>2</sub>などの酸化雰囲気中において約350°Cに上昇させ、前記吸着されたTa(O<sub>2</sub>C<sub>2</sub>H<sub>5</sub>)O<sub>5</sub>分子を酸化または加水分解し、前記吸着分子層12bをTa<sub>2</sub>O<sub>5</sub>分子層12cに変換する。

## 【0020】

さらに図3(H)の工程において、基板温度を510°Cに、また前記反応容器の内圧を13.3~1330Pa(0.1~10Torr)に設定し、前記反応容器中にTa(O<sub>2</sub>C<sub>2</sub>H<sub>5</sub>)O<sub>5</sub>ガスとO<sub>2</sub>ガスとを、Heキャリアガスと共に供給し、前記Ta<sub>2</sub>O<sub>5</sub>分子層12c上に、通常のCVDプロセスによりTa<sub>2</sub>O<sub>5</sub>膜13を所望の厚さ、例えば4~5nmの厚さに形成する。

## 【0021】

さらに、図示は省略するが、このようにして形成されたTa<sub>2</sub>O<sub>5</sub>膜13に対してO<sub>2</sub>雰囲気中に熱処理を施すことにより、膜13中の酸素欠損が補償され、また膜13が結晶化する。このようにして結晶化されたTa<sub>2</sub>O<sub>5</sub>膜13は、大きな比誘電率を示す。また、前記Si基板11とTa<sub>2</sub>O<sub>5</sub>膜13との界面には前記SiO<sub>2</sub>分子層12aが形成されているため、Si基板上に形成された素子においてゲートチャネルの大きなキャリアモビリティが保証される。すなわち、このようにして形成された半導体装置は、非常に高速に動作する。

## 【0022】

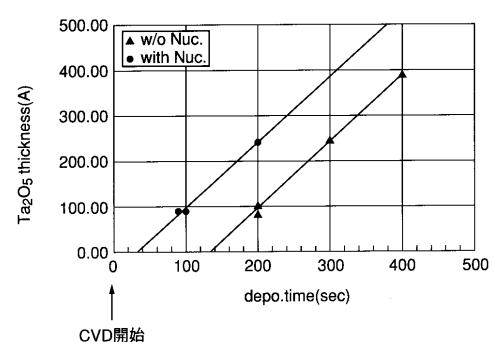

図4は、先の図3(H)のCVD工程における堆積時間と、その結果堆積したTa<sub>2</sub>O<sub>5</sub>膜

10

20

30

40

50

13との関係を、従来のTa<sub>2</sub>O<sub>5</sub>膜のCVD工程の場合と比較して示す。ただし、前記堆積時間は、CVD工程の開始時点から測っている。図4中、(1)は本実施例によるTa<sub>2</sub>O<sub>5</sub>膜13の堆積を、一方(2)は従来のCVD工程におけるTa<sub>2</sub>O<sub>5</sub>膜の堆積を示す。ただし(1)で示す従来の場合には、図2(D)において前記SiO<sub>2</sub>分子層12a上にTa<sub>2</sub>O<sub>5</sub>膜をCVD法により、直接に堆積させている。

#### 【0023】

図4を参照するに、従来のCVD工程では、CVDプロセスを開始してから実際にTa<sub>2</sub>O<sub>5</sub>膜の堆積が生じるまでに、約140秒間のインキュベーション時間が必要であるのにに対し、本実施例による工程では、CVDプロセスを開始してからわずか40秒後にはTa<sub>2</sub>O<sub>5</sub>膜の堆積が始まっている。すなわち、本実施例の構成により、Ta<sub>2</sub>O<sub>5</sub>膜をCVD法により形成する際のインキュベーション時間を実質的に減少させることが可能である。

10

#### 【0024】

図5(A), (B)は、従来のCVD工程により、Si基板11表面を覆うSiON膜上に形成したTa<sub>2</sub>O<sub>5</sub>膜の表面構造をAFMにより観察した結果を示す。ただし、図5(A)では、前記Ta<sub>2</sub>O<sub>5</sub>膜を基板温度510°CでのCVD法により、一方図5(B)では、前記Ta<sub>2</sub>O<sub>5</sub>膜を、基板温度480°CでのCVD法により、形成している。

#### 【0025】

図5(A), (B)を参照するに、このようにして形成されたCVD-Ta<sub>2</sub>O<sub>5</sub>膜は、下地のSiON膜の膜厚変動を反映して、非常に大きな膜厚の変動を示すことがわかる。換言すると、従来のCVD-Ta<sub>2</sub>O<sub>5</sub>膜では、下地膜の膜厚変動が増幅され、その結果得られるTa<sub>2</sub>O<sub>5</sub>膜の膜厚が不均一になってしまう。

20

#### 【0026】

これに対し、図6(A)は、前記図1(A)～図3(G)の本実施例による工程により形成されたTa<sub>2</sub>O<sub>5</sub>膜の表面構造を示す。ただし、図6(A)では、前記SiO<sub>2</sub>分子層12aの代わりに、SiON分子層を使っている。一方図6(B)は、図1(C)の構造上に、すなわち前記露出されたSi基板表面11c上に、直接にTa<sub>2</sub>O<sub>5</sub>膜のCVD法による堆積を行った場合のTa<sub>2</sub>O<sub>5</sub>膜の表面構造を示す。図6(A), (B)のいずれの場合にも、前記Ta<sub>2</sub>O<sub>5</sub>膜の表面構造はAFM観察により求めている。

#### 【0027】

図6(A)を参照するに、本実施例による工程を採用することにより、CVD法により形成されるTa<sub>2</sub>O<sub>5</sub>膜表面の凹凸が実質的に減少し、Si基板上に直接に形成した場合に近い状態になることがわかる。これは先に図4で説明した、下地のSiON膜上にTaの気相分子化合物Ta(O<sub>2</sub>C<sub>2</sub>H<sub>5</sub>)<sub>5</sub>を吸着させ、これを酸化させてTa<sub>2</sub>O<sub>5</sub>分子層12cを形成し、かかるTa<sub>2</sub>O<sub>5</sub>分子層12c上にTa<sub>2</sub>O<sub>5</sub>膜13をCVD法により形成した場合に得られるインキュベーション時間の短縮の結果を反映しているものと考えられる。すなわち、インキュベーション時間が短縮することにより、下地膜の膜質によるインキュベーション時間の変動が抑制され、その結果、CVD法により堆積されるTa<sub>2</sub>O<sub>5</sub>膜13の膜厚変動が抑制される。

30

#### 【0028】

なお、本実施例において使用可能なTa<sub>2</sub>O<sub>5</sub>分子層12c形成時に使われる気相分子化合物は先に説明したTa(O<sub>2</sub>C<sub>2</sub>H<sub>5</sub>)<sub>5</sub>に限定されるものではなく、例えばTaCl<sub>5</sub>を使うことも可能である。この場合にも、前記TaCl<sub>5</sub>分子の吸着工程は、反応容器の内圧を0.133～13.3Pa(0.001～0.1Torr)程度に設定し、200～300°C程度の基板温度において、TaCl<sub>2</sub>を0.1～5mg/min程度の流量で供給しながら行えばよい。

40

#### 【0029】

さらに、本実施例の方法は、Ta<sub>2</sub>O<sub>5</sub>膜の形成に限定されるものではなく、以下の表1, 表2に示すように、SiO<sub>2</sub>, ZrO<sub>2</sub>あるいはHfO<sub>2</sub>、さらにはAl<sub>2</sub>O<sub>3</sub>等の酸化物膜の形成にも適用可能である。ただし、表1は図2(F), 図3(G)の気相分子化合物の吸着工程および酸化工程のプロセス条件を、また表2は図3(H)のCVD工程のプロセ

50

ス条件を、まとめて示す。

【0030】

【表1】

| 吸着工程 | 吸着させる原料    | Ta(OC2H5)5             | TaCl5        | Zn(OC4H9)4   | ZrCl4        | Al(i-OC3H7)3 | (CH3)3Al     | SiCl4        | Si(OC2H5)4   |

|------|------------|------------------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|

|      | 吸着プロセス真空度  | 0.001~0.1torr          | 0.01~0.1torr |

|      | 吸着プロセスガス条件 | 0.1~5mg/min            | 0.1~5mg/min  | 0.1~5mg/min  | 0.1~5mg/min  | 0.1~5mg/min  | 0.1~5mg/min  | 0.1~5mg/min  | 0.1~5mg/min  |

|      | 吸着プロセス温度   | 200~350°C              | 1            | ↓            | ↓            | ↓            | ↓            | ↓            | ↓            |

| 酸化工程 | 酸化ガス:H2O   | 200~350°C、10~0.001torr | ↓            | ↓            | ↓            | ↓            | ↓            | ↓            | ↓            |

|      | 酸化ガス:NO2   | 200~350°C、10~0.001torr | ↓            | ↓            | ↓            | ↓            | ↓            | ↓            | ↓            |

|      | 酸化ガス:O2    | 300~400°C、10~0.001torr | ↓            | ↓            | ↓            | ↓            | ↓            | ↓            | ↓            |

|      | 酸化ガス:O3    | 200~300°C、10~0.001torr | ↓            | ↓            | ↓            | ↓            | ↓            | ↓            | ↓            |

10

20

30

40

【0031】

【表2】

|      |        |                                |                       |                                                                |                |

|------|--------|--------------------------------|-----------------------|----------------------------------------------------------------|----------------|

| 成膜工程 | 成膜原料   | Ta <sub>2</sub> O <sub>5</sub> | 400~600°C, 0.1~10torr | Ta(OC <sub>2</sub> H <sub>5</sub> ) <sub>5</sub>               | O <sub>2</sub> |

|      | 成膜温度範囲 | ZrO <sub>2</sub>               | ↓                     | Zr(t-OC <sub>4</sub> H <sub>9</sub> ) <sub>4</sub>             | ↓              |

|      |        | HfO <sub>2</sub>               | ↓                     | Hf(C <sub>5</sub> H <sub>7</sub> O <sub>2</sub> ) <sub>4</sub> | ↓              |

|      |        | SiO <sub>2</sub>               | ↓                     | Si(OC <sub>2</sub> H <sub>5</sub> ) <sub>5</sub>               | ↓              |

|      |        | Al <sub>2</sub> O <sub>3</sub> | ↓                     | Al(t-OC <sub>3</sub> H <sub>7</sub> ) <sub>3</sub>             | ↓              |

10

20

30

表1を参照するに、図2(F)の工程において吸着した前記Ta(OC<sub>2</sub>H<sub>5</sub>)<sub>5</sub>分子あるいはTaCl<sub>2</sub>分子を酸化または加水分解してTa<sub>2</sub>O<sub>5</sub>分子層12cを形成する際には、雰囲気はO<sub>2</sub>雰囲気には限られるものではなく、H<sub>2</sub>O, NO<sub>2</sub>, O<sub>3</sub>等の雰囲気中において酸化を行ってもよい。図3(G)の酸化工程を先に説明したようにO<sub>2</sub>雰囲気中において行う場合には、前記反応室の内圧を0.133~1330Pa(0.01~10Torr)程度に設定し、基板温度を300~400°C程度に設定すればよい。一方、前記図3(G)の酸化工程をH<sub>2</sub>OあるいはNO<sub>2</sub>雰囲気中において行う場合には、前記反応容器の内圧を0.133~1330Pa(0.001~10Torr)に設定し、基板温度を200~350°Cに設定すればよい。さらに、前記図3(G)の酸化工程をO<sub>3</sub>雰囲気中において行う場合には、前記反応容器の内圧を0.133~1330Pa(0.001~10Torr)に設定し、基板温度を200~300°Cに設定すればよい。

### 【0032】

また、表1よりわかるように、前記図2(F)の工程において前記分子層12cとしてZrO<sub>2</sub>分子層を形成する場合には、Zrの気相分子化合物としてZr(t-OC<sub>4</sub>H<sub>9</sub>)<sub>4</sub>あるいはZrCl<sub>4</sub>を吸着させ、これを先のTaの気相分子化合物の場合と同じような条件下で酸化処理することにより、所望のZrO<sub>2</sub>分子層が得られる。同様に、Hf(t-

40

50

$C_4H_9)_4$ あるいは $HfCl_4$ を $S$ 前記 $SiO_2$ 分子層 $12a$ に、前記 $Ta_2O_5$ 分子層形成の場合と同様な条件下で吸着させ、これを同様な条件下で酸化または加水分解することにより、前記分子層 $12c$ として、 $HfO_2$ 層を形成することも可能である。また、 $Al(1-OCH_3)_3$ あるいは $(CH_3)_3Al$ を前記 $SiO_2$ 分子層 $12a$ に、前記 $Ta_2O_5$ 分子層の場合と同様な条件下で吸着させ、これを同様な条件下で酸化または加水分解することにより、前記分子層 $12c$ として、 $Al_2O_5$ 層を形成することも可能である。また、もちろん $Si(OCH_2H_5)_4$ あるいは $SiCl_4$ を前記 $SiO_2$ 分子層 $12a$ に、前記 $Ta_2O_5$ 分子層の場合と同様な条件下で吸着させ、これを同様な条件下で酸化または加水分解することにより、前記分子層 $12c$ として、 $SiO_2$ 層を形成することも可能である。

## 【0033】

10

さらに、このようにして形成された酸化物分子層 $12c$ 上に表2の条件に従ってCVDプロセスを実行することにより、 $Ta_2O_5$ 、 $ZrO_2$ 、 $HfO_2$ 、 $SiO_2$ あるいは $Al_2O_3$ のCVD膜を、前記膜 $13$ に対応して形成することができる。

## [第2実施例]

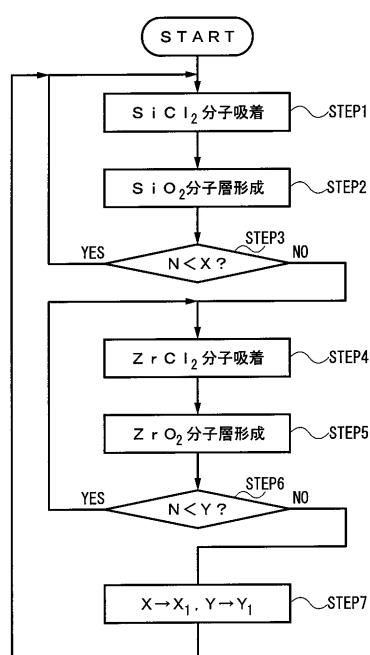

図7は、本発明の第2実施例による誘電体膜の形成方法を示すフローチャートである。

## 【0034】

図7を参照するに、図2(D)の $SiO_2$ 分子層 $12a$ 上に、ステップS1において図2(E)、(F)に対応する工程により $SiCl_4$ 分子が吸着され、ステップS2において、図3(G)に対応する工程において酸化あるいは加水分解され、 $SiO_2$ 分子層が形成される。さらにステップS3において前記ステップS1およびステップS2が交互に所定回数Xだけ繰り返された後、ステップ4に進み、前記図2(E)、(F)に対応する工程により $ZrCl_4$ 分子あるいは $Zr(t-OCH_3)_4$ 分子を先のステップS1およびS2で形成された $SiO_2$ 分子層上に吸着させる。さらに図3(G)に対応するステップ5の工程において前記吸着した $Zr$ の気相分子化合物は酸化あるいは加水分解され、その結果 $ZrO_2$ 分子層が形成される。さらにステップ6において前記ステップS4およびS5が交互に所定回数Yだけ繰り返された後、ステップ7において前記所定回数Xおよび所定回数Yはそれぞれ $X_1$ および $Y_1$ に変化され、プロセスは前記ステップ1に戻る。

20

## 【0035】

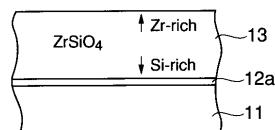

このようにして、新たな所定回数 $X_1$ および $Y_1$ を使ってステップ1～7を実行し、さらに前記所定回数を変化しながら前記ステップ1～7を繰り返し実行することにより、図8に示すように、 $Zr$ と $Si$ の比率が膜厚方向に連続的に変化する、組成が $ZrSiO_4$ で表される誘電体膜を、前記 $Si$ 基板 $11$ 上に形成することができる。ただし、図8中、先に説明した部分は対応する参照符号で示してある。

30

## 【0036】

図8を参照するに、図示の例では、前記誘電体膜中の $Zr$ の組成が、前記 $Si$ 基板 $11$ との界面近傍において小さく、前記界面から離れるにつれて徐々に減少するように制御されている。このように組成を制御された $ZrSiO_4$ 膜では、前記 $Si$ 基板 $11$ との界面近傍において $Si$ 濃度が高いため、 $Si$ 基板に対して優れた密着性が得られ、さらに $ZrSiO_4$ 膜の表面近傍では $Zr$ 濃度が高いため大きな誘電率が得られると共に、膜中を流れりーク電流を抑制することが可能になる。また、前記 $ZrSiO_4$ 膜を、膜中において $Zr$ と $Si$ とが1分子層毎に互に配列するように形成することも可能である。

40

## [第3実施例]

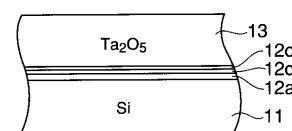

図9は、本発明の第3実施例による誘電体膜構造を示す。ただし図9中、先に説明した部分には対応する参照符号を付し、説明を省略する。

## 【0037】

図9を参照するに、本実施例では前記 $SiO_2$ 分子層 $12a$ が形成された後、 $SiCl_4$ 分子を前記 $SiO_2$ 分子層 $12a$ に吸着させ、さらに $NH_3$ ガスで前記吸着した $SiCl_4$ 分子層を処理し、 $SiN$ 分子層 $12d$ に変換する。かかる $SiN$ 分子層 $12d$ の形成の後、前記 $SiN$ 分子層 $12d$ に $Ta(OCH_2H_5)_5$ 分子を吸着させ、さらにこれを酸化させて前記 $Ta_2O_5$ 分子層 $12c$ を形成した後、前記 $Ta_2O_5$ 分子層 $12c$ 上に前記CVD-T

50

$\text{Ta}_2\text{O}_5$  膜 13 を形成する。

【0038】

図9の構造では、前記  $\text{Ta}_2\text{O}_5$  膜 13 と Si 基板 11 との間に SiN 分子層 12d が介在しているため、例えば前記  $\text{Ta}_2\text{O}_5$  膜 13 上に B でドープしたポリシリコン膜を堆積したような場合でも、B の Si 基板 11 中への拡散が前記 SiN 分子層 12d により阻止されるため、前記  $\text{Ta}_2\text{O}_5$  膜 13 をゲート絶縁膜に使った半導体装置において、しきい値電圧の変動を抑制することが可能になる。

【第4実施例】

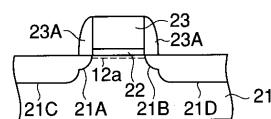

図10は、本発明の第4実施例による半導体装置の構成を示す。

【0039】

10

図10を参照するに、p型 Si 基板 21 上には先に説明したいづれかの実施例に従って、 $\text{Ta}_2\text{O}_5$  よりなるゲート絶縁膜 22 が形成されており、前記ゲート絶縁膜 22 上にはポリシリコンゲート電極 23 が形成されている。

【0040】

さらに前記 Si 基板 21 中には、前記ゲート電極 23 に隣接して  $n^-$  型の拡散領域 21A, 21B が形成されており、前記ポリシリコンゲート電極 23 の側表面は側壁絶縁膜 23a, 23b により覆われている。さらに前記 Si 基板 21 中には、前記側壁絶縁膜 23a, 23b の外側に、 $n^+$  型の拡散領域 21C, 21D が形成されている。

【0041】

図10の半導体装置では、ゲート絶縁膜 22 として  $\text{Ta}_2\text{O}_5$  を使うため、0.1nm 以下の厚さの  $\text{SiO}_2$  膜に実質的に等価な実効膜厚が得られ、その結果ゲート長を短縮することにより、ゲートリーク電流を抑制しつつ、非常に高速な動作を実現することが可能になる。その際、先に説明した実施例に従って前記  $\text{Ta}_2\text{O}_5$  膜 22 を形成することにより、膜厚の変動を抑制でき、得られる半導体装置の特性を安定化させることができる。特に、前記  $\text{Ta}_2\text{O}_5$  膜 22 の直下に数分子層程度の  $\text{SiO}_2$  分子層 12a を介在させることにより、ゲート電極 23 から Si 基板 21 への不純物元素の拡散が阻止され、半導体装置の特性が安定化する。さらに、前記ゲート絶縁膜 22 を、 $\text{Ta}_2\text{O}_5$  を含む様々な酸化物材料により、一分子層ずつ形成することにより、前記ゲート絶縁膜 22 内部の厚さ方向への組成分布を、自在に制御することが可能になる。その結果、Si 基板との界面において密着性が高く、ゲート電極 23 との界面において比誘電率の大きい構造を容易に得ることが可能になる。その際、本発明では前記基板上への誘電体分子層の形成を、吸着された気相原料分子に対してプラズマ励起ラジカルを作用させるのではなく、吸着された気相原料分子を加水分解させることにより行うが、このように加水分解反応を使うことにより、従来の技術、特に先に説明した特開平11-87341号公報記載の技術と異なり、荷電粒子が誘電体膜中に取り込まれ、これがリーク電流路を形成する問題を回避することが可能になる。また、加水分解反応では、熱的に安定な反応しか生じないので、制御が容易である。

【0042】

30

【発明の効果】

本発明の特徴によれば、Si 基板上に、薄い絶縁膜を隔てて  $\text{Ta}_2\text{O}_5$  等の高誘電体膜、あるいは様々な組成の誘電体膜を CVD 法により形成する際に、インキュベーション時間が実質的に減少し、その結果、形成される誘電体膜の均一性が向上する。さらに、形成される誘電体膜の膜厚方向への組成の制御を自在に行うことが可能で、また必要に応じて、1分子層程度の非常に薄い拡散障壁膜を、前記誘電体膜中に作りこむことが可能になる。本発明ではかかる誘電体膜の形成の際に、プラズマ励起されたラジカルを吸着させる工程が含まれないので、形成される誘電体膜は電荷の伴う準位等の欠陥を含まず、このため優れたリーク電流特性を示す。

40

【図面の簡単な説明】

【図1】(A) ~ (C) は、本発明の第1実施例による誘電体膜の形成方法を示す図(その1)である。

【図2】(D) ~ (F) は、本発明の第1実施例による誘電体膜の形成方法を示す図(そ

50

の 2 ) である。

【図 3】( G ) ~ ( H ) は、本発明の第 1 実施例による誘電体膜の形成方法を示す図 ( そ

の 3 ) である。

【図 4】本発明の効果を示す図である。

【図 5】( A ) , ( B ) は、従来の C V D 法により S i O N 膜上に形成した T a 2 O 5 膜

の表面構造を示す図である。

【図 6】( A ) は、本発明の方法により S i O N 膜上に形成した T a 2 O 5 膜の表面構造を

示す図、( B ) は、 S i 基板の表面に直接に形成された T a 2 O 5 膜の表面構造を示す図で

ある。

【図 7】本発明の第 2 実施例による誘電体膜の形成方法を示すフローチャートである。 10

【図 8】本発明の第 2 実施例により形成された誘電体膜の構造を示す図である。

【図 9】本発明の第 3 実施例により形成された誘電体膜の構造を示す図である。

【図 10】本発明の第 4 実施例による半導体装置の構成を示す図である。

【符号の説明】

1 1 , 2 1 S i 基板

1 1 a 自然酸化膜

1 1 b 保護膜

1 1 c S i 基板表面

1 2 a S i O 2 分子層

1 2 b T a ( O C 2 H 5 ) 5 分子層

20

1 2 c T a 2 O 5 分子層

1 2 d S i N 分子層

1 3 C V D 膜

2 2 ゲート絶縁膜

2 3 ゲート電極

2 3 A , 2 3 B 側壁絶縁膜

2 1 A , 2 1 B L D D 拡散領域

2 1 C , 2 1 D 拡散領域

【図1】

(A)～(C)は、本発明の第1実施例による誘電体膜の形成方法を示す図(その1)

【図2】

(D)～(F)は、本発明の第1実施例による誘電体膜の形成方法を示す図(その2)

【図3】

(G)～(H)は、本発明の第1実施例による誘電体膜の形成方法を示す図(その3)

【図4】

本発明の効果を示す図

【図5】

従来のCVD法によりSiON膜上に形成したTa<sub>2</sub>O<sub>5</sub>膜の表面構造を示す図

【図6】

(A)は本発明の方法によりSiON膜上に形成したTa<sub>2</sub>O<sub>5</sub>膜の表面構造を示す図

(B)はSi基板の表面の直接に形成されたTa<sub>2</sub>O<sub>5</sub>膜の表面構造を示す図

【図7】

本発明の第2実施例による誘電体膜の形成方法を示すフローチャート

【図8】

本発明の第2実施例により形成された誘電体膜の構造を示す図

【図9】

本発明の第3実施例により形成された誘電体膜の構造を示す図

【図10】

本発明の第4実施例による半導体装置の構成を示す図

---

フロントページの続き

(72)発明者 神力 博

山梨県韮崎市穂坂町三ツ沢650 東京エレクトロン株式会社内

審査官 宮本 靖史

(56)参考文献 特開平02-283022 (JP, A)

特開平02-196427 (JP, A)

特開平09-077593 (JP, A)

特開平07-131007 (JP, A)

特開平05-102189 (JP, A)

特開平09-232542 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/316

C23C 16/40

H01L 29/78