(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第6240745号 (P6240745)

(45) 発行日 平成29年11月29日(2017.11.29)

(24) 登録日 平成29年11月10日(2017.11.10)

(51) Int.Cl. F 1

**GO6F** 9/46 (2006.01) GO6F 9/46 350 **GO6F** 12/10 (2016.01) GO6F 12/10 553Z

請求項の数 31 (全 19 頁)

(21) 出願番号 特願2016-501236 (P2016-501236)

(86) (22) 出願日 平成26年3月11日 (2014.3.11) (65) 公表番号 特表2016-529568 (P2016-529568A)

(43) 公表日 平成28年9月23日 (2016. 9. 23)

(86) 国際出願番号 PCT/US2014/023445 (87) 国際公開番号 W02014/159405

(87) 国際公開日 平成26年10月2日 (2014.10.2) 審査請求日 平成29年2月24日 (2017.2.24)

(31) 優先権主張番号 13/829,023

(32) 優先日 平成25年3月14日 (2013.3.14)

(33) 優先権主張国 米国(US)

早期審査対象出願

(73)特許権者 507364838

クアルコム、インコーポレイテッド アメリカ合衆国 カリフォルニア 921 21 サン ディエゴ モアハウス ドラ

イブ 5775

(74)代理人 100108453

弁理士 村山 靖彦

(74)代理人 100163522

弁理士 黒田 晋平 (72)発明者 エリック・ジェームズ・プロンドケ

> アメリカ合衆国・カリフォルニア・921 21-1714・サン・ディエゴ・モアハ ウス・ドライヴ・5775

> > 最終頁に続く

(54) 【発明の名称】複数のハイパーバイザを実行するシステムおよび方法

#### (57)【特許請求の範囲】

## 【請求項1】

プライマリハイパーバイザを実行させる第1の命令セットアーキテクチャのハードウェアプロセッサの第1のセットであって、前記プライマリハイパーバイザは、ハードウェアプロセッサの前記第1のセットで実行するために第1の仮想プロセッサタスクをスケジューリングする、ハードウェアプロセッサの第1のセットと、

セカンダリハイパーバイザを実行させる第2の命令セットアーキテクチャのハードウェアプロセッサの第2のセットであって、前記セカンダリハイパーバイザは、ハードウェアプロセッサの前記第2のセットで実行するために第2の仮想プロセッサタスクをスケジューリングし、前記第2の命令セットアーキテクチャは、前記第1の命令セットアーキテクチャとは異なる、ハードウェアプロセッサの第2のセットと、

前記プライマリハイパーバイザおよび前記セカンダリハイパーバイザに<u>よって</u>アクセス可能であるメモリアドレス変換マッピングデータを格納するストレージデバイスであって、前記プライマリハイパーバイザは、前記メモリアドレス変換マッピングデータをプログラムするように構成され、前記セカンダリハイパーバイザは、前記メモリアドレス変換マッピングデータを使用するように構成される、ストレージデバイスとを含む、装置。

#### 【請求項2】

ハードウェアプロセッサの前記第1のセットは、単一のハードウェアプロセッサを含み

20

10

.

ハードウェアプロセッサの前記第2のセットは、単一のハードウェアプロセッサ、またはそれらの任意の組合せを含む、請求項1に記載の装置。

## 【請求項3】

ハードウェアプロセッサの前記第1のセットは、複数のプロセッサを含み、

ハードウェアプロセッサの前記第2のセットは、複数のプロセッサ、またはそれらの任意の組合せを含む、請求項1に記載の装置。

#### 【請求項4】

前記プライマリハイパーバイザは、前記メモリアドレス変換マッピングデータへの読み 取り書き込みアクセスを有し、

前記セカンダリハイパーバイザは、前記メモリアドレス変換マッピングデータへの読み取り専用アクセスを有する、請求項1に記載の装置。

#### 【請求項5】

前記セカンダリハイパーバイザは、プロセッサ仮想化を実行するために、前記メモリアドレス変換マッピングデータにアクセスするように構成されている、請求項1に記載の装置。

#### 【請求項6】

前記プライマリハイパーバイザは、第1のスケジューリングアルゴリズムにより前記第1 の仮想プロセッサタスクをスケジューリングし、

前記セカンダリハイパーバイザは、前記第1のスケジューリングアルゴリズムとは異なる第2のスケジューリングアルゴリズムにより前記第2の仮想プロセッサタスクをスケジューリングする、請求項1に記載の装置。

#### 【請求項7】

前記第1のスケジューリングアルゴリズムおよび前記第2のスケジューリングアルゴリズムの少なくとも1つは、タイムスライススケジューリングを含む、請求項6に記載の装置。

#### 【請求項8】

前記第1のスケジューリングアルゴリズムおよび前記第2のスケジューリングアルゴリズムの少なくとも1つは、優先度ベースのスケジューリングを含む、請求項6に記載の装置。

#### 【請求項9】

ハードウェアプロセッサの前記第1のセットに関して実行可能である第1のゲストオペレーティングシステムと、

ハードウェアプロセッサの前記第2のセットに関して実行可能である第2のゲストオペレーティングシステムと

をさらに含む、請求項1に記載の装置。

## 【請求項10】

ハードウェアプロセッサの前記第1のセットの少なくとも1つのプロセッサおよびハードウェアプロセッサの前記第2のセットの少なくとも1つのプロセッサで同時に実行するように構成されたゲストオペレーティングシステムをさらに含む、請求項1に記載の装置。

#### 【請求項11】

前記プライマリハイパーバイザ、前記セカンダリハイパーバイザ、またはそれらの組合せに関連付けられた仮想化されたデバイスをさらに含む、請求項1に記載の装置。

# 【請求項12】

前記仮想化されたデバイスは、タイマを含み、

ハードウェアプロセッサの前記第1のセットは、ハードウェアプロセッサの前記第2のセットと区別される、請求項11に記載の装置。

#### 【請求項13】

ハードウェアプロセッサの前記第1のセットの少なくとも1つのプロセッサによって実行可能な第1のゲストオペレーティングシステムであって、前記ストレージデバイスへの第2のメモリアドレス変換マッピングデータをプログラムするように構成される、第1のゲストオペレーティングシステムと、

ハードウェアプロセッサの前記第2のセットの少なくとも1つのプロセッサによって実行

20

10

- -

30

40

可能な第2のゲストオペレーティングシステムであって、前記ストレージデバイスへの第3のメモリアドレス変換マッピングデータをプログラムするように構成される、第2のゲストオペレーティングシステムと

をさらに含む、請求項1に記載の装置。

#### 【請求項14】

プライマリハイパーバイザを実行させる第1の命令セットアーキテクチャのハードウェアプロセッサの第1のセットであって、前記プライマリハイパーバイザは、ハードウェアプロセッサの前記第1のセットで実行するために第1の仮想プロセッサタスクをスケジューリングし、第1のスケジューリングアルゴリズムに関連付けられた第1のタスクスケジューラを含む、ハードウェアプロセッサの第1のセットと、

セカンダリハイパーバイザを実行させる第2の命令セットアーキテクチャのハードウェアプロセッサの第2のセットであって、前記セカンダリハイパーバイザは、ハードウェアプロセッサの前記第2のセットで実行するために第2の仮想プロセッサタスクをスケジューリングし、前記第1のスケジューリングアルゴリズムと区別される第2のスケジューリングアルゴリズムに関連付けられた第2のタスクスケジューラを含み、前記第2の命令セットアーキテクチャは、前記第1の命令セットアーキテクチャとは異なる、ハードウェアプロセッサの第2のセットと、

前記プライマリハイパーバイザおよび前記セカンダリハイパーバイザに<u>よって</u>アクセス可能であるメモリアドレス変換マッピングデータを格納するストレージデバイスであって、前記プライマリハイパーバイザは、前記メモリアドレス変換マッピングデータをプログラムするように構成され、前記セカンダリハイパーバイザは、前記メモリアドレス変換マッピングデータを使用するように構成される、ストレージデバイスとを含む、装置。

#### 【請求項15】

前記プライマリハイパーバイザは、ストレージデバイスへのメモリアドレス変換マッピングデータをプログラムするように構成され、

前記セカンダリハイパーバイザは、前記プライマリハイパーバイザによってプログラムされた前記メモリアドレス変換マッピングデータを使用するように構成されている、請求項14に記載の装置。

# 【請求項16】

前記メモリアドレス変換マッピングデータは、中間物理アドレスから物理アドレスへの 変換を示す、請求項15に記載の装置。

# 【請求項17】

プライマリハイパーバイザを実行させる第1の命令セットアーキテクチャのハードウェアプロセッサの第1のセットであって、前記プライマリハイパーバイザは、ハードウェアプロセッサの前記第1のセットで実行するために第1の仮想プロセッサタスクをスケジューリングする、ハードウェアプロセッサの第1のセットと、

セカンダリハイパーバイザを実行させる第2の命令セットアーキテクチャのハードウェアプロセッサの第2のセットであって、前記セカンダリハイパーバイザは、ハードウェアプロセッサの前記第2のセットで実行するために第2の仮想プロセッサタスクをスケジューリングし、前記第2の命令セットアーキテクチャは、前記第1の命令セットアーキテクチャとは異なる、ハードウェアプロセッサの第2のセットと、

前記プライマリハイパーバイザおよび前記セカンダリハイパーバイザに<u>よって</u>アクセス可能であるリソースのメモリアドレス変換設定データを格納するストレージデバイスであって、前記プライマリハイパーバイザは、前記ストレージデバイスに格納された前記メモリアドレス変換設定データをプログラムするように構成され、前記セカンダリハイパーバイザは、前記メモリアドレス変換設定データに基づいて前記リソースを使用するように構成される、ストレージデバイスと

#### を含む、装置。

【請求項18】

10

20

30

40

前記リソースは、少なくともメモリの一部、メモリがマップされたデバイス、またはそれらの任意の組合せを含む、請求項17に記載の装置。

#### 【請求項19】

前記メモリアドレス変換設定データは、メモリアドレス変換マッピングデータを含む、 請求項18に記載の装置。

## 【請求項20】

前記プライマリハイパーバイザは、第1のスケジューリングアルゴリズムに関連付けられた第1のタスクスケジューラを含み、

前記セカンダリハイパーバイザは、前記第1のスケジューリングアルゴリズムと区別される第2のスケジューリングアルゴリズムに関連付けられた第2のスケジューラを含む、請求項17に記載の装置。

#### 【請求項21】

第2の命令セットアーキテクチャのハードウェアプロセッサの第2のセットで実行中のセカンダリハイパーバイザによって、第1の命令セットアーキテクチャのハードウェアプロセッサの第1のセットで実行中のプライマリハイパーバイザによってプログラムされたメモリアドレス変換マッピングデータから、1つまたは複数のアドレス変換を決定するステップであって、前記プライマリハイパーバイザは、ハードウェアプロセッサの前記第1のセットで実行するために第1の仮想プロセッサタスクをスケジューリングし、前記セカンダリハイパーバイザは、ハードウェアプロセッサの前記第2のセットで実行するために第2の仮想プロセッサタスクをスケジューリングし、前記第2の命令セットアーキテクチャは、前記第1の命令セットアーキテクチャとは異なる、ステップと、

データアクセス動作の間に、メモリにアクセスするために前記1つまたは複数のメモリアドレス変換を使用するステップであって、前記1つまたは複数のメモリアドレス変換は、前記プライマリハイパーバイザおよび前記セカンダリハイパーバイザに<u>よって</u>アクセス可能であるストレージデバイスに格納されている、ステップとを含む方法。

#### 【請求項22】

前記1つまたは複数のメモリアドレス変換は、中間物理アドレスから物理アドレスへの 変換を含む、請求項21に記載の方法。

# 【請求項23】

前記データアクセス動作は、読み取り動作または書き込み動作を含む、請求項21に記載の方法。

#### 【請求項24】

前記プライマリハイパーバイザは、前記メモリアドレス変換マッピングデータへの読み取り書き込みアクセスを有し、

前記セカンダリハイパーバイザは、前記メモリアドレス変換マッピングデータへの読み取り専用アクセスを有する、請求項21に記載の方法。

#### 【請求項25】

前記セカンダリハイパーバイザのスケジューラによって、ハードウェアプロセッサの前記第2のセットで実行するために仮想プロセッサをスケジューリングするステップをさらに含み、

前記仮想プロセッサは、前記セカンダリハイパーバイザによって実行されているゲストオペレーティングシステムのタスクに対応し、

前記スケジューラによる前記仮想プロセッサの前記スケジューリングは、前記プライマリハイパーバイザによって実行されるスケジューリングと無関係に実行される、請求項21に記載の方法。

#### 【請求項26】

第1の命令セットアーキテクチャのハードウェアプロセッサの第1のセットを使用して、 ハードウェアプロセッサの前記第1のセットで実行するために第1の仮想プロセッサタスク をスケジューリングし、かつ、メモリアドレス変換マッピングデータをプログラムするた

10

20

30

40

めのプライマリハイパーバイザを実行するための手段と、

第2の命令セットアーキテクチャのハードウェアプロセッサの第2のセットを使用して、ハードウェアプロセッサの前記第2のセットで実行するために第2の仮想プロセッサタスクをスケジューリングし、かつ、前記メモリアドレス変換マッピングデータを使用するためのセカンダリハイパーバイザを実行するための手段であって、前記第2の命令セットアーキテクチャは、前記第1の命令セットアーキテクチャとは異なり、前記プライマリハイパーバイザを実行するための手段および前記セカンダリハイパーバイザを実行するための手段は、ハードウェアプロセッサの前記第1のセットおよびハードウェアプロセッサの前記第2のセットでそれぞれ実行され、前記メモリアドレス変換マッピングデータは、前記プライマリハイパーバイザおよび前記セカンダリハイパーバイザによってアクセス可能であり、かつ、メモリに格納される、手段と

10

を含む装置。

## 【請求項27】

コンピュータによって実行されたとき、前記コンピュータに、

第2の命令セットアーキテクチャのハードウェアプロセッサの第2のセットで実行中のセカンダリハイパーバイザによって、第1の命令セットアーキテクチャのハードウェアプロセッサの第1のセットで実行中のプライマリハイパーバイザによってストレージデバイスに対してプログラムされたメモリアドレス変換マッピングデータから、1つまたは複数のアドレス変換を決定するステップであって、前記プライマリハイパーバイザは、ハードウェアプロセッサの前記第1のセットで実行するために第1の仮想プロセッサタスクをスケジューリングし、前記セカンダリハイパーバイザは、ハードウェアプロセッサの前記第2のセットで実行するために第2の仮想プロセッサタスクをスケジューリングし、前記第2の命令セットアーキテクチャは、前記第1の命令セットアーキテクチャとは異なる、ステップと、

20

メモリに対するデータアクセス動作の間に、メモリの一部にアクセスするために前記1つまたは複数のメモリアドレス変換を使用するステップであって、前記1つまたは複数のメモリアドレス変換は、前記プライマリハイパーバイザおよび前記セカンダリハイパーバイザによってアクセス可能であるストレージデバイスに格納されている、ステップとを実行させる命令を含む非一時的コンピュータ可読記録媒体。

# 【請求項28】

30

前記1つまたは複数のアドレス変換は、中間物理アドレスから物理アドレスへの変換を含む、請求項27に記載の非一時的コンピュータ可読記録媒体。

# 【請求項29】

前記プライマリハイパーバイザは、前記メモリアドレス変換マッピングデータへの読み取り書き込みアクセスを有し、

前記セカンダリハイパーバイザは、前記メモリアドレス変換マッピングデータへの読み取り専用アクセスを有する、請求項27に記載の非一時的コンピュータ可読記録媒体。

#### 【請求項30】

前記第2のメモリアドレス変換マッピングデータは、第1の仮想アドレスから第1の中間 物理アドレスへの第1の変換を示し、

40

前記プライマリハイパーバイザによってプログラムされた前記メモリアドレス変換マッピングデータは、前記第1の中間物理アドレスから第1の物理アドレスへの第2の変換を示す、請求項13に記載の装置。

# 【請求項31】

前記第3のメモリアドレス変換マッピングデータは、第2の仮想アドレスから第2の中間物理アドレスへの第3の変換を示し、

前記プライマリハイパーバイザによってプログラムされた前記メモリアドレス変換マッピングデータは、前記第2の中間物理アドレスから第2の物理アドレスへの第4の変換を示す、請求項30に記載の装置。

# 【発明の詳細な説明】

20

30

40

50

#### 【技術分野】

## [0001]

#### 関連出願の相互参照

本出願は、2013年3月14日に出願した本願の所有者が所有する米国非仮特許出願第13/82 9,023号の優先権を主張するものであり、2013年3月14日に出願した同時係属中の米国非仮特許出願第13/828,183号および2013年2月26日に出願した同時係属中の米国非仮特許出願第13/777,314号に関する。これらの出願の各々の内容は、参照によりそれらの全体が組み込まれている。

# [0002]

本開示は、一般的に、複数のハイパーバイザを使用するオペレーティングシステムの仮想化に関する。

#### 【背景技術】

## [0003]

技術の進歩の結果として、より小型かつより強力なコンピューティングデバイスが登場した。たとえば、現在、小型、軽量、かつユーザによって容易に携行される、携帯無線電話機、携帯情報端末(PDA)、タブレットコンピュータ、およびページング装置など、ワイヤレスコンピューティングデバイスを含む、様々なポータブルパーソナルコンピューティングデバイスが存在する。そのような多くのコンピューティングデバイスは、そこに組み込まれた他のデバイスを含む。たとえば、ワイヤレス電話は、また、デジタルスチールカメラ、デジタルビデオカメラ、デジタルレコーダ、およびオーディオファイルプレーヤを含む可能性がある。また、そのようなコンピューティングデバイスは、インターネットにアクセスするために使用できるウェブブラウザアプリケーション、およびスチールカメラまたはビデオカメラを利用し、マルチメディア再生機能を提供するマルチメディアアプリケーションなど、ソフトウェアアプリケーションを含む、実行可能命令を処理することができる。

#### [0004]

モバイル電話などのコンピューティングデバイスは、複数のプロセッサを含み得る。たとえば、モバイル電話は、中央処理装置(CPU)(アプリケーションプロセッサとも呼ばれる)およびデジタル信号プロセッサ(DSP)を含み得る。各プロセッサは、特定の計算タスクを実行するために他方のプロセッサよりも適している場合がある。たとえば、主要なプロセッサとして機能することができ、モバイル電話のオペレーティングシステムを実行できるCPUは、ウェブブラウザおよびユーザインターフェースコードなど、「制御コード」を実行するときにより効率的な場合がある。一方、信号処理および他の数値演算集約的な機能を実行する場合、DSPはCPUよりも効率的な場合がある。CPUおよびDSPは、別個の命令セットアーキテクチャを有することができる。したがって、CPUで実行するように設計されたアプリケーションは、DSPと互換性がない場合があり、その逆もあり得る。

# [0005]

状況によっては、単一のコンピューティングデバイスで複数のオペレーティングシステムを実行することが有利な場合がある。複数のオペレーティングシステムを実行するコンピューティングデバイスでは、オペレーティングシステムに使用可能なハードウェアリソースの抽象的概念を提供するために、ハイパーバイザ(仮想コンピュータモニタとしても知られている)を使用することができる。したがって、ハイパーバイザは、複数のオペレーティングシステムに対するオペレーティングシステムとして機能することができる。しかしながら、異なる命令セットアーキテクチャを有するプロセッサのセットを横断して同時に実行され得るハイパーバイザを設計するのは難しい場合がある。

#### 【発明の概要】

## 【課題を解決するための手段】

## [0006]

プロセッサの複数のセットを横断するハイパーバイザ実行のシステムおよび方法が開示される。記述した技術によると、システムのハイパーバイザの1つは「プライマリ」ハイ

パーバイザでありの場合があり、システムの残りのハイパーバイザは「セカンダリ」ハイパーバイザの場合がある。プライマリハイパーバイザは、セカンダリハイパーバイザとは異なるプロセッサのセットで実行することができる。たとえば、プライマリハイパーバイザは、セカンダリハイパーバイザとは異なる命令セットアーキテクチャと互換性を有する場合がある。

#### [0007]

プライマリハイパーバイザは、セカンダリハイパーバイザが特定の動作を実行することを限定することができ、代わりに、限定された動作を実行するために、プライマリハイパーバイザに依存することをセカンダリハイパーバイザに強制することができる。たとえば、プライマリハイパーバイザは、セキュリティ目的のためにセカンダリハイパーバイザのために物理アドレスマッピングを決定することができる。(たとえば、複数のセカンダリハイパーバイザが同じ物理アドレスへのマッピングを作成することを試みる状況を防ぐため)。

## [0008]

セカンダリハイパーバイザは、プライマリハイパーバイザに依存せずに、特定の動作を実行することができる。たとえば、セカンダリハイパーバイザは、プライマリハイパーバイザによる干渉なくタスクスケジューリングを実行できる場合がある。セカンダリハイパーバイザが自身のタスクスケジューリングを実行できるようにすることで、セカンダリハイパーバイザで実行されているゲストオペレーティングシステムに対して、セカンダリハイパーバイザがサービス品質(QoS)保証(たとえば遅延保証)を維持することを可能にすることができる。

#### [0009]

特定の実施形態では、装置は、プロセッサの第1のセットで実行可能なプライマリハイパーバイザおよびプロセッサの第2のセットで実行可能なセカンダリハイパーバイザを含む。プライマリハイパーバイザは、メモリアドレス変換マッピングをプログラムするように構成され、セカンダリハイパーバイザは、メモリアドレス変換マッピングを使用するように構成される。

### [0010]

別の具体的な実施形態では、装置は、プロセッサの第1のセットで実行可能なプライマリハイパーバイザおよびプロセッサの第2のセットで実行可能なセカンダリハイパーバイザを含む。プライマリハイパーバイザは、第1のスケジューラを含み、セカンダリハイパーバイザは、第1のスケジューラとは異なる第2のスケジューラを含む。

#### [0011]

別の具体的な実施形態では、装置は、プロセッサの第1のセットで実行可能なプライマリハイパーバイザおよびプロセッサの第2のセットで実行可能なセカンダリハイパーバイザを含む。プライマリハイパーバイザは、リソースの設定を定義するように構成され、セカンダリハイパーバイザは、設定に基づいてリソースを使用するように構成される。

#### [0012]

別の具体的な実施形態では、方法は、プロセッサの第2のセットで実行されるセカンダリハイパーバイザによって、プロセッサの第1のセットで実行されるプライマリハイパーバイザによってプログラムされた1つまたは複数のメモリアドレス変換マッピングを取り出すステップを含む。方法は、また、データアクセス動作の間に、取り出された1つまたは複数のメモリアドレス変換マッピングを使用するステップを含む。

# [0013]

別の具体的な実施形態では、装置は、処理するための第1の手段および処理するための第2の手段を含む。装置は、また、メモリアドレス変換をプログラムするための手段を含み、プログラムするための手段は、処理するための第1の手段で実行可能である。装置は、メモリアドレス変換を使用するための手段をさらに含み、使用するための手段は、処理するための第2の手段で実行可能である。

## [0014]

50

10

20

30

別の具体的な実施形態では、非一時的コンピュータ可読媒体は、コンピュータによって実行されたとき、コンピュータが、プロセッサの第2のセットで実行されているセカンダリハイパーバイザによって、プロセッサの第1のセットで実行されているプライマリハイパーバイザによってプログラムされた1つまたは複数のメモリアドレス変換マッピングを取り出すことを生じさせる命令を含む。命令は、また、コンピュータによって実行されたとき、コンピュータが、データアクセス動作の間に、取り出された1つまたは複数のメモリアドレス変換マッピングを使用することを生じさせる。

#### [0015]

開示した実施形態の少なくとも1つによって提供される特定の利点の1つは、プロセッサの異なるセット(たとえば、異なる命令セットアーキテクチャを有するプロセッサのセット)で複数のハイパーバイザの実行をサポートする能力である。本開示の他の態様、利点、および機能は、図面の簡単な説明、発明を実施するための形態、および特許請求の範囲の節を含む出願全体を検討した後に明白になるであろう。

【図面の簡単な説明】

#### [0016]

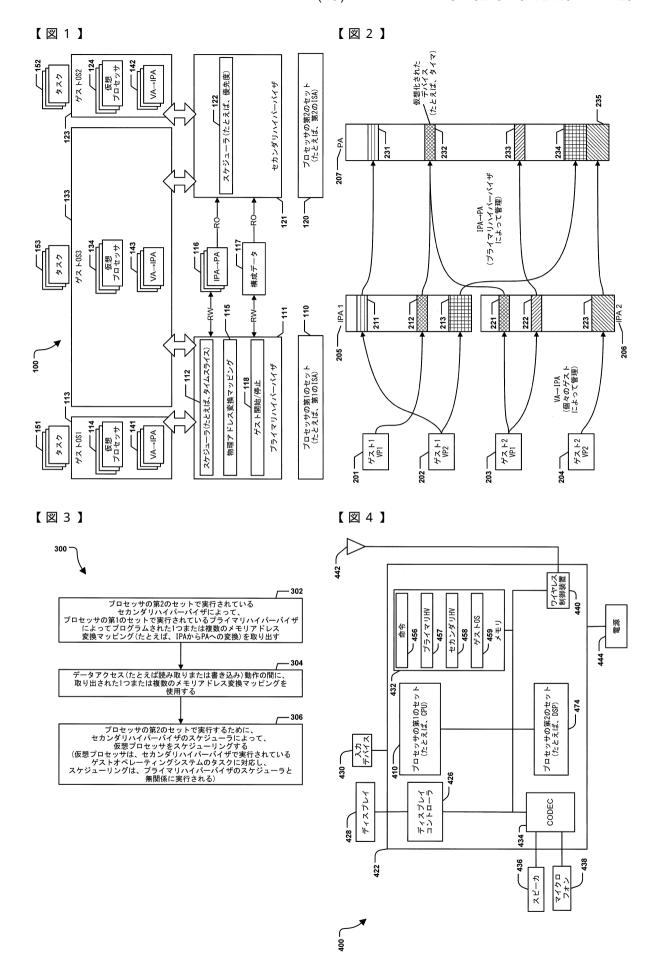

【図1】複数のハイパーバイザを実行するように動作可能なシステムの具体的な実施形態を示す図である。

【図2】図1のシステムによって使用され得るアドレス変換マッピングの具体的な実施形態を示す図である。

【図3】複数のハイパーバイザを実行する方法の具体的な実施形態を示す流れ図である。

【図4】複数のハイパーバイザの実行をサポートするように動作可能な構成要素を含むワイヤレスデバイスを示すブロック図である。

【発明を実施するための形態】

#### [0017]

図1は、複数のハイパーバイザを実行するように動作可能なシステム100の具体的な実施形態を示す図である。システム100は、プロセッサの第1のセット110で実行可能なプライマリハイパーバイザ111およびプロセッサの第2のセット120で実行可能なセカンダリハイパーバイザ121を含む。プロセッサのセット110、120の各々は、本明細書にさらに記述するように、1つまたは複数のプロセッサ、処理ユニット、コア、および/またはハードウェアスレッドを含むことができる。マルチスレッドのプロセッサは、同時に実行されている複数のハードウェア実行コンテキストを用いるプロセッサを介して、または単一のハードウェア実行コンテキストを用いる複数のプロセッサとして(たとえば、対称型マルチプロセッシング(SMP)クラスタ)実装され得る。

## [0018]

たとえば、プライマリハイパーバイザ111は、第1の(たとえばCPUに特有の)命令セットアーキテクチャに従って、1つまたは複数の中央処理装置(CPU)コア/ハードウェアスレッドで実行することができ、セカンダリハイパーバイザ121は、第2の(たとえばDSPに特有の)命令セットアーキテクチャに従って、1つまたは複数のデジタル信号プロセッサ(DSP)コア/ハードウェアスレッドで実行することができる。本明細書に記載のCPUおよびDSPの記述は、例示のみを目的とすることに注意されたい。ネットワーク処理ユニット(NPU)、グラフィック処理ユニット(GPU)など、他のプロセッサまたはプロセッサのセットもシステム100に含まれ得る。

## [0019]

各ハイパーバイザ111、121は、1つまたは複数のゲストオペレーティングシステムによって、プロセッサ110、120へのアクセスを調停することができる。ゲストオペレーティングシステムは、アプリケーションプログラミングインターフェース(API)、共有されたメモリ区域を使用するか、または他の何らかのメカニズムを介して、ハイパーバイザ111、121と通信することができる。プライマリハイパーバイザ111は、プロセッサの第1のセット110で実行されるゲストオペレーティングシステム(複数可)のために「ローカル」スケジューリングを実行するように構成された第1のスケジューラ112を含むことができる。ハイ

10

20

30

40

20

30

40

50

パーバイザによる「ローカル」スケジューリングは、ハイパーバイザに対応するプロセッサのセットで排他的に実行されるゲストオペレーティングシステムのためにハイパーバイザによって実行される動作をスケジューリングすることを表す場合がある。たとえば、プライマリハイパーバイザ111は、プロセッサの第1のセット110で実行するために第1のゲストオペレーティングシステム113の仮想プロセッサ114をスケジューリングすることができる。仮想プロセッサ114の各々は、第1のゲストオペレーティングシステム113のタスク151に対応する場合がある(たとえば、第1のゲストオペレーティングシステム113で実行されているアプリケーションによって作成されたタスク)。

# [0020]

セカンダリハイパーバイザ121は、プロセッサの第2のセット120で実行されるゲストオペレーティングシステム(複数可)のために「ローカル」スケジューリングを実行するように構成された第2のスケジューラ122を含むことができる。たとえば、セカンダリハイパーバイザ121は、プロセッサの第2のセット120で実行するために第2のゲストオペレーティングシステム123の仮想プロセッサ124をスケジューリングすることができる。仮想プロセッサ124の各々は、第2のゲストオペレーティングシステム123のタスク152に対応する場合がある(たとえば、第2のゲストオペレーティングシステム123で実行されているアプリケーションによって作成されたタスク)。したがって、ハイパーバイザ111、121の観点から、仮想プロセッサ114、124の各々は、スケジューリング可能なエンティティである。反対に、ゲストオペレーティングシステム113および123の観点から、仮想プロセッサ114、124の各々は、ハードウェアリソースの抽象的概念である。

#### [0021]

スケジューラ112、122は、同じスケジューリングアルゴリズムを使用することも、または異なるスケジューリングアルゴリズムを使用することもできる。たとえば、図1において、第1のスケジューラ112は、タイムスライススケジューリングを実行し、第2のスケジューラ122は、優先度ベースのスケジューリングを実行する。説明するために、第2のスケジューラ122は、仮想プロセッサ124の優先度に基づいて、優先度ベースのスケジューリングを実行することができる。各ハイパーバイザ111、121がローカルスケジューリングに対する責任を保持することを可能にすることによって、図1のシステム100は、各ハイパーバイザ111、121が、サービスの品質(QoS)保証を維持することを可能にできる場合があることを理解されるであろう。たとえば、プロセッサの第2のセット120は、モバイル電話のDSPに対応する場合があり、セカンダリハイパーバイザ121は、モデムオペレーティングシステムまたはオーディオ/音声処理オペレーティングシステムなど、ゲストリアルタイムオペレーティングシステム(RTOS)に対する遅延制約に準拠するために、特定のスケジューリングアルゴリズムを実行することができる。

### [0022]

仮想アドレス(VA)、中間物理アドレス(IPA)、および物理アドレス(PA)という、3タイプのメモリアドレスをシステム100で使用することができる。各仮想アドレスは、仮想アドレス空間に関連付けられ得て、複数の仮想アドレス空間は、システム100で使用されている場合がある。たとえば、各ゲストオペレーティングシステム113、123は、異なる仮想アドレス空間を使用することができる。各中間物理アドレスは、中間物理アドレス空間に関連付けられ得て、複数の中間物理アドレス空間は、システム100で使用されている場合がある。たとえば、各ゲストオペレーティングシステム113、123は、異なる中間物理アドレス空間を使用することができる。メモリの区域(たとえばランダムアクセスメモリ(RAM)、ディスクベースのメモリ、キャッシュメモリ、レジスタメモリなど)に直接的にアクセスするために使用され得る物理アドレス、およびメモリがマッピングされたデバイス(たとえば入力/出力(I/O)デバイス)は、単一の物理アドレス空間に属する場合がある。

#### [0023]

仮想アドレス、中間物理アドレス、および物理アドレスがシステム100で使用されている場合、2つのタイプのアドレス変換マッピングがシステム100で定義され得る。第1のタイプのアドレス変換マッピングは、仮想アドレスから中間物理アドレスへの場合があり、

20

30

40

50

第2のタイプのアドレス変換マッピングは、中間物理アドレスから物理アドレスへの場合がある。したがって、システム100の仮想アドレスに対する「完全な」アドレス変換マッピングは、仮想アドレスから中間物理アドレスへの「第1段階の」変換と、それに続く中間物理アドレスから物理アドレスへの「第2段階の」変換を含むことができる。第1段階および第2段階の変換の実施例については、図2に関してさらに記述する。

#### [0024]

特定の実施形態では、タスク151および第1のゲストオペレーティングシステム113は、第1の仮想アドレス空間の一部である仮想アドレスを使用して、メモリおよびメモリがマッピングされたデバイスに格納されたデータを参照する場合がある。タスク152および第2のオペレーティングシステム123は、第2の仮想空間の一部である仮想アドレスを使用して、メモリおよびメモリがマッピングされたデバイスに格納されたデータを参照する場合がある。ゲストオペレーティングシステム113、123の各々は、それぞれの仮想アドレス空間に対して第1段階(つまりVAからIPA)の変換141、142を定義することができる。IPAは、メモリまたはメモリがマッピングされたデバイスにアクセスするために直接的に使用され得ないので、各ゲストオペレーティングシステム113、123が、それ自身の第1段階の変換141、142を定義することを許可することは、セキュリティのリスクをもたらさないことを理解されるであろう。

## [0025]

物理アドレスマッピング(つまり第2段階の変換)を決定するための責任は、セキュリティの理由のために、プライマリハイパーバイザ111のみに割り当てられ得る。たとえば、プライマリハイパーバイザ111だけがメモリの物理アドレスに対するマッピングを決定することを許可することで、セカンダリハイパーバイザ121が、プライマリハイパーバイザ11および/または別のセカンダリハイパーバイザによって定義されたマッピングに競合する物理アドレスマッピングを定義することを試みるという状況を防ぐことができる。セカンダリハイパーバイザ121は、したがって、特定の機能(たとえば第2段階の変換の決定すること)のためにプライマリハイパーバイザ111に依存する「シン(thin)」ハイパーバイザの場合がある。

#### [0026]

第2段階の変換を決定するために、プライマリハイパーバイザ111は、物理アドレス変換マッピングモジュール115を含むことができる。特定の実施形態では、物理アドレス変換マッピングモジュール115は、第2段階の変換116をプログラムし、構成データ117を決定することができる(たとえば、メモリの第2段階の変換116の位置)。物理アドレス変換マッピングモジュール115は、プロセッサの第2のセット120に関して排他的に実行されるゲストオペレーティングシステムを含む(たとえばゲストオペレーティングシステム123)システム100のすべてのゲストオペレーティングシステムに対して第2段階の変換116をプログラムすることができる。本明細書で使用する場合、特定のプロセッサまたはプロセッサのセットで実行するために、(たとえばハイパーバイザによって)ゲストオペレーティングシステム(またはタスクに対応する少なくとも1つの仮想プロセッサ)の少なくとも1つのタスクをスケジューリングされ得る場合、ゲストオペレーティングシステムは、特定のプロセッサまたはプロセッサのセット「に関して」実行することができる。したがって、物理アドレス変換マッピングモジュール115は、第1のゲストオペレーティングシステム113と第2のゲストオペレーティングシステム113と第2のゲストオペレーティングシステム123の両方に対して第2段階の変換116をプログラムすることができる。

# [0027]

第2のゲストオペレーティングシステム123によって提供される仮想アドレスに対してアドレス変換を実行する場合、第2段階の変換116を提供するために、セカンダリハイパーバイザ121は、プライマリハイパーバイザ111に依存する場合がある。セカンダリハイパーバイザ121は、プロセッサ仮想化を実行するために、プライマリハイパーバイザ111によって提供される第2段階の変換116を使用することができる。したがって、図1に示すように、プライマリハイパーバイザ111は、第2段階の変換116および構成データ117への読み取り/

書き込み(RW)アクセスを有することができる一方、セカンダリハイパーバイザ121は、第2段階の変換116および構成データ117への読み取り専用(RO)アクセスを有する。

#### [0028]

特定の実施形態では、プライマリハイパーバイザ111は、プロセッサの第2のセット120に関して排他的に実行されるゲストオペレーティングシステムを含む、すべてのゲストオペレーティングシステムを開始および停止するように構成された開始/停止モジュール118 は、セカンダリハイパーバイザ121からの要求に応じて第2のゲストオペレーティングシステム123を開始または停止することができる。

# [0029]

特定の実施形態では、システム100は、異なる命令セットアーキテクチャを有するプロセッサでゲストオペレーティングシステムの単一のインスタンスの同時実行をサポートすることができる。たとえば、第3のゲストオペレーティングシステム133は、プロセッサの第1のセット110およびプロセッサの第2のセット120で同時に実行可能な場合がある。第3のゲストオペレーティングシステム133のタスク153に対応する第3のゲストオペレーティングシステム133の仮想プロセッサ134は、スケジューラ112、122のいずれかによってスケジューリングすることができる。第3のゲストオペレーティングシステム133は、それ自身の第1段階の変換143を定義することができるが、第2段階の変換116のためにプライマリハイパーバイザ111に依存する場合がある。

## [0030]

動作の間に、プライマリハイパーバイザ111のゲスト開始/停止モジュール118は、第1のゲストオペレーティングシステム113を開始することができる。ゲスト開始/停止モジュール118は、また、セカンダリハイパーバイザ121からの要求に応じて、第2のゲストオペレーティングシステム123を開始することができる。第1のゲストオペレーティングシステム113は、ハードウェアプロセッサの第1のセット110で実行するために仮想プロセッサ114をスケジューリングすることができ、第2のゲストオペレーティングシステム123は、ハードウェアプロセッサの第2のセット120で実行するために仮想プロセッサ124をスケジューリングすることができる。

## [0031]

メモリがシステム100で割り当てられると、ゲストオペレーティングシステム113、123の各々は、それぞれの第1段階の変換141、142を定義することができる。すべての第2段階の変換116は、プライマリハイパーバイザ111の物理アドレス変換モジュール115によって定義され得る。物理アドレス変換モジュール115は、また、リソース設定(たとえば構成データ117)を定義することができる。したがって、プライマリハイパーバイザ111は、第2段階の変換116および構成データ117への読み取り書き込みアクセスを有することができる(たとえば、システム100のすべてのハイパーバイザのためのページテーブルを確立および修正するため)。第2段階の変換116および構成データ117は、アドレス変換を実行するために、セカンダリハイパーバイザ121によって読み取り専用の方法でアクセスされ得る。たとえば、第2段階の変換116は、仮想プロセッサ124の1つへのコンテキスト切り換え時にセカンダリハイパーバイザ121によってロードされ得る。したがって、図1のシステム100はシステム(プライマリハイパーバイザ111は、1つまたは複数のリソースの設定を定義し(たとえば物理メモリに対するアドレスマッピング)、セカンダリハイパーバイザ121は、様々な動作(たとえばアドレス変換)を実行するためにプライマリハイパーバイザ111によって定義されたリソースの設定を使用する)を提供する。

#### [0032]

特定の実施形態では、図1に示した論理モジュールおよび/または機能モジュールの各々(たとえば、スケジューラ112、122、物理アドレス変換マッピングモジュール115、およびゲスト開始/停止モジュール118)は、プロセッサ110または120によって実行可能なソフトウェア命令を使用して実装される。あるいは、そのような機能は、コントローラ、特定用途向け集積回路(ASIC)、フィールドプログラマブルゲートアレイ(FPGA)デバイス、または

10

20

30

40

20

30

40

50

他の何らかのデバイスなど、ハードウェアデバイスを使用して実装され得る。しかし、様々なモジュール間の動作の分割は、例示のみを目的としていることに注意するべきである。代替実施形態では、特定のモジュールに関して記述した機能は、より多くのモジュールまたはより少ないモジュールを使用して実行され得る。

## [0033]

図1のシステム100は、したがって、異種混合の命令セットアーキテクチャを有するプロセッサを含む、プロセッサの異なるセットで複数のハイパーバイザの同時実行を可能にすることができる。有利なことに、図1のシステム100は、他のハイパーバイザ動作の複製を限定しながら、特定のハイパーバイザ動作の複製を可能にできる場合がある。たとえば、図1のシステム100は、すべてのハイパーバイザがスケジューリングを実行することを可能にすることによって、QoSを維持するコンピュータ環境を提供することができる。図1のシステム100は、プライマリハイパーバイザだけが第2段階の変換を定義すること、およびゲストオペレーティングシステムを開始/停止することを可能にすることによって、セキュリティを維持することができる。

#### [0034]

図2は、アドレス変換マッピングの実施例を示している。図1に関して記述したように、アドレス変換は、2つの段階で発生する場合がある。各ゲストオペレーティングシステムの仮想プロセッサは、仮想アドレスを使用してデータを参照することができ、各ゲストオペレーティングシステムは、中間物理アドレスに仮想アドレスをマッピングすることができる。たとえば、図2は、第1のゲストオペレーティングシステムの仮想プロセッサ(VP)201、202(たとえば図1の第1のゲストオペレーティングシステム113)および第2のゲストオペレーティングシステムの仮想プロセッサ203、204(たとえば、図1の第2のゲストオペレーティングシステム123)を示している。

#### [0035]

仮想プロセッサ201、202によって使用される仮想アドレスは、図示するように、第1のゲストオペレーティングシステムによって、第1の中間物理アドレス空間205(「IPA1」と記載)にマッピングされ得る。第2のゲストオペレーティングシステムの仮想プロセッサ203、204によって使用される仮想アドレスは、図示するように、第2のゲストオペレーティングシステムによって、第2の中間物理アドレス空間206(「IPA2」と記載)にマッピングされ得る。図1に関して記述したように、中間アドレスは、物理アドレスにマッピングされ得て、そのようなすべてのIPAからPAへのマッピングは、プライマリハイパーバイザによって処理されて定義され得る。

### [0036]

たとえば、第1の仮想プロセッサ201は、中間物理アドレス212の範囲にマッピングされた仮想アドレスの範囲を使用することができる。第2の仮想プロセッサ202は、中間物理アドレス211、213の範囲にマッピングされた仮想アドレスの範囲を使用することができる。第3の仮想プロセッサ203は、第2のゲストオペレーティングシステムによって、中間物理アドレス221および222の範囲にマッピングされた仮想アドレスの範囲を使用することができる。第4の仮想プロセッサ204は、物理アドレス223の範囲にマッピングされた仮想アドレスの範囲を使用することができる。

# [0037]

中間物理アドレス211~213、221~223の各範囲は、図示するように、単一の物理アドレス空間(「PA」と記載)207内の物理アドレス231~235の対応する範囲にマッピングされ得る。特定の実施形態では、異なる中間物理アドレス空間からのアドレス範囲は、同じ物理アドレスにマッピングされ得る。たとえば、図2は、中間物理アドレス212および221の両方の範囲が物理アドレス232の同じ範囲にマッピングされていることを示している。そのような共有されたマッピングは、第1のゲストオペレーティングシステムと第2のゲストオペレーティングシステムの両方は、物理アドレス232の範囲に対応するデータまたはメモリがマッピングされたデバイスにアクセスすることを示す場合がある。たとえば、物理アドレス232の範囲は、タイマなどゲストオペレーティングシステム(およびハイパーバイザ

)間で共有される仮想化されたデバイスを表す場合がある。

## [0038]

第1のハイパーバイザが、仮想デバイスに対してメモリがマッピングされた区域を含むが、第2のハイパーバイザが、仮想デバイスに対してメモリがマッピングされた区域を含まない場合、第1のハイパーバイザは、そのゲストオペレーティングシステムに仮想デバイスへのアクセスを提供できるが、第2のハイパーバイザは、そのゲストオペレーティングシステムに仮想デバイスへのアクセスを提供できない場合がある。両方のハイパーバイザが仮想デバイスに対してメモリがマッピングされた区域を含む場合、一方のハイパーバイザは、そのゲストオペレーティングシステムに仮想デバイスへのアクセスを提供することができる。

[0039]

図3は、複数のハイパーバイザを実行する方法300の具体的な実施形態を示す流れ図である。例示的な一実施形態では、方法300は、図1のシステム100で実行され得る。

## [0040]

方法300は、プロセッサの第2のセットで実行されているセカンダリハイパーバイザによって、302でプロセッサの第1のセットで実行されているプライマリハイパーバイザによってプログラムされた1つまたは複数のメモリアドレス変換マッピングを取り出すステップを含むことができる。1つまたは複数のメモリアドレス変換マッピングは、第2段階の変換(たとえばIPAからPAへの変換)を含む場合がある。たとえば、図1を参照すると、セカンダリハイパーバイザ121は、プライマリハイパーバイザ111によってプログラムされた第2段階の変換116を取り出すことができる。

[0041]

方法300は、また、304で、データアクセス動作の間に、取り出された1つまたは複数のメモリアドレス変換マッピングを使用するステップを含むことができる。データアクセス動作は、読み取り動作または書き込み動作の場合がある。たとえば、図1を参照すると、セカンダリハイパーバイザ121は、読み取り動作または書き込み動作のターゲットである特定の物理アドレスを決定するために、読み取り動作または書き込み動作の間に、第2段階の変換116を使用することができる。

## [0042]

方法300は、また、306で、セカンダリハイパーバイザのスケジューラによって、プロセッサの第2のセットで実行するために仮想プロセッサをスケジューリングするステップを含むことができる。仮想プロセッサは、セカンダリハイパーバイザで実行されている第2のゲストオペレーティングシステムのタスクに対応する。スケジューリングは、プライマリハイパーバイザのスケジューラと無関係に実行される。たとえば、図1を参照すると、スケジューラ122は、プロセッサの第2のセット120で実行するためにタスク152の1つに対応する仮想プロセッサ124の1つをスケジューリングすることができる。スケジューラ122の動作は、プライマリハイパーバイザ111のスケジューラ112の動作に依存しない場合がある(たとえば、スケジューラ112、122の両方は、他方のスケジューラと無関係に異なるスケジューリングアルゴリズムを使用して、「ローカル」スケジューリングを実行することができる)。

[0043]

図3の方法300は、デジタル信号プロセッサ(DSP)、中央処理装置(CPU)などの処理ユニット、コントローラ、フィールドプログラマブルゲートアレイ(FPGA)デバイス、特定用途向け集積回路(ASIC)、別のハードウェアデバイス、ファームウェアデバイス、またはそれらの任意の組合せによって実装され得る。例を挙げると、図4に関して記述したように、図3の方法300は、命令を実行するプロセッサによって実行され得る。

#### [0044]

図4を参照すると、電子デバイス400のブロック図が示されている。電子デバイス400は、中央処理装置(CPU)(複数可)などプロセッサの第1のセット410およびデジタル信号プロセッサ(DSP)(複数可)などプロセッサの第2のセット474を含み、それぞれがメモリ432に結

10

20

30

40

20

30

40

50

合されている。プロセッサの第1のセット410およびプロセッサの第2のセット474は、異なる命令セットアーキテクチャを有することができる。例示的な一実施形態では、プロセッサの第1のセット410は、図1のプロセッサの第1のセット110であり、プロセッサの第2のセット474は、図1のプロセッサの第2のセット120である。電子デバイス400、またはその構成要素は、セットトップボックス、音楽プレーヤ、ビデオプレーヤ、エンターテイメントユニット、ナビゲーションデバイス、通信デバイス、携帯情報端末(PDA)、固定された位置データユニット、コンピューティングデバイス、またはそれらの任意の組合せに含まれ得る。

## [0045]

図4は、また、プロセッサのセット410、474およびディスプレイ428に結合されたディスプレイコントローラ426を示している。符号器 / 復号器 (CODEC) 434は、また、プロセッサのセット410、474に結合され得る。スピーカ436およびマイクロフォン438は、CODEC434に結合され得る。図4は、また、ワイヤレス制御装置440は、(たとえば無線周波数 (RF) インターフェースを介して) プロセッサのセット410、474およびアンテナ442に結合され得ることを示している。

#### [0046]

メモリ432は、実行可能命令456を含む有形の非一時的コンピュータ可読の記憶媒体またはプロセッサ可読の記憶媒体の場合がある。命令456は、図3の方法300を含む、本明細書に記述した様々な機能および方法を実行するために、プロセッサのセット410、474など、プロセッサ(複数可)によって実行され得る。メモリ432は、また、プライマリハイパーバイザ457(たとえば図1のプライマリハイパーバイザ111)、セカンダリハイパーバイザ458(たとえば図1のセカンダリハイパーバイザ121)、および1つまたは複数のゲストオペレーティングシステム459(たとえば、図1のゲストオペレーティングシステム113、123、および/または133の1つまたは複数)に対応する命令を格納することができる。

#### [0047]

特定の実施形態では、プロセッサのセット410、474、ディスプレイコントローラ426、メモリ432、CODEC434、およびワイヤレス制御装置440は、システムインパッケージまたはシステムオンチップのデバイス422に含まれている。特定の実施形態では、入力デバイス430および電源444は、システムオンチップデバイス422に結合される。その上、具体的な実施形態では、図4に示すように、ディスプレイ428、入力デバイス430、スピーカ436、マイクロフォン438、アンテナ442、および電源444は、システムオンチップデバイス422の外部にある。しかしながら、ディスプレイ428、入力デバイス430、スピーカ436、マイクロフォン438、アンテナ442、および電源444の各々は、インターフェースまたはコントローラなど、システムオンチップデバイス422の構成要素に結合され得る。

### [0048]

記述した実施形態に関連して、装置は、処理するための第1の手段および処理するための第2の手段を含む。たとえば、処理するための第1の手段は、図1のプロセッサの第1のセット110もしくは図4のプロセッサの第1のセット410のプロセッサなどハードウェアプロセッサ、データを処理するための1つまたは複数の他のデバイスもしくは回路、またはそれらの任意の組合せを含むことができる。処理するための第2の手段は、図1のプロセッサの第2のセット120もしくは図4のプロセッサの第2のセット474のプロセッサなどハードウェアプロセッサ、データを処理するための1つまたは複数の他のデバイスもしくは回路、またはそれらの任意の組合せを含むことができる。特定の実施形態では、処理するための第1の手段は、第1の命令セットアーキテクチャに関連付けられ、処理するための第2の手段は、第1の命令セットアーキテクチャとは異なる第2の命令セットアーキテクチャに関連付けられる。

#### [0049]

装置は、また、メモリアドレス変換をプログラムするための手段を含み、プログラムするための手段は、処理するための第1の手段で実行可能である。たとえば、プログラムするための手段は、図1の物理アドレス変換マッピングモジュール115、図4のプライマリハ

20

30

40

50

イパーバイザ457、1つまたは複数の他のデバイス、回路、モジュール、もしくはメモリアドレス変換をプログラムするための命令、またはそれらの任意の組合せの場合がある。装置は、メモリアドレス変換を使用するための手段をさらに含むことができ、使用するための手段は、処理するための第2の手段で実行可能である。たとえば、使用するための手段は、図1のセカンダリハイパーバイザ121、図4のセカンダリハイパーバイザ458、1つまたは複数の他のデバイス、回路、モジュール、もしくメモリアドレス変換を使用するための命令、またはそれらの任意の組合せを含むことができる。

## [0050]

装置は、処理するための第1の手段で実行するために仮想プロセッサをスケジューリングするための第1の手段および処理のための第2の手段で実行するために仮想プロセッサをスケジューリングするための第2の手段を含むことができる。たとえば、スケジューリングするための第1の手段は、図1の第1のスケジューラ112、1つまたは複数の他のデバイス、回路、モジュール、もしくは実行するために仮想プロセッサをスケジューリングするための命令、またはそれらの任意の組合せを含むことができる。スケジューリングするための第2の手段は、図1の第2のスケジューラ122、1つまたは複数の他のデバイス、回路、モジュール、もしくは実行するために仮想プロセッサをスケジューリングするための命令、またはそれらの任意の組合せを含むことができる。

## [0051]

本明細書に開示された実施形態に関して記述された論理ブロック、構成、モジュール、回路、およびアルゴリズムのステップは、電子ハードウェア、プロセッサによって実行されるコンピュータソフトウェア、または両方の組合せとして実装できることを当業者はさらに理解されるであろう。様々な実例となる構成要素、ブロック、構成、モジュール、回路、およびステップについて、それらの機能の点から一般的に記述してきた。そのような機能がハードウェアまたはプロセッサの実行可能命令として実装されるかどうかは、特定のアプリケーションおよびシステム全体に課された設計制約に依存する。熟練者であれば、特定の各アプリケーションに対して様々な方法で記述した機能を実装することができるが、そのような実装の決定は、本開示の範囲からの逸脱するものとして解釈するべきでない。

## [0052]

本明細書に開示した実施形態に関して記述した方法またはアルゴリズムのステップは、ハードウェア、プロセッサによって実行されるソフトウェアモジュール、または2つの組合せで直接的に具体化または実装され得る。ソフトウェアモジュールは、ランダムアクセスメモリ(RAM)、フラッシュメモリ、読み取り専用メモリ(ROM)、プログラム可能読み取り専用メモリ(PROM)、消去可能プログラム可能ROM(EPROM)、電気的消去可能PROM(EEPROM)、レジスタ、ハードディスク、リムーバブルディスク、コンパクトディスク読み取り専用メモリ(CD-ROM)、または当技術分野で知られている非一時的な記憶媒体の他の形態に常駐することができる。代表的な記憶媒体は、プロセッサが記憶媒体から情報を読み出し、かつ情報を書き込めるようにプロセッサに結合される。代替案では、記憶媒体はプロセッサと一体型でもよい。プロセッサおよび記憶媒体は、特定用途向け集積回路(ASIC)に常駐することができる。ASICは、コンピューティングデバイス、通信デバイス、またはユーザ端末に常駐することができる。代替案では、プロセッサおよび記憶媒体は、コンピューティングデバイス、通信デバイス、またはユーザ端末に常駐することができる。代替案では、プロセッサおよび記憶媒体は、コンピューティングデバイス、通信デバイス、またはユーザ端末の個別の構成要素として常駐することができる。

# [0053]

開示した実施形態の前述の説明は、当業者が開示された実施形態を構成または使用できるように提供するものである。これらの実施形態に対する様々な修正は、当業者には容易に明白になろう。また、本明細書に規定した原理は、本開示の範囲から逸脱するとなく他の実施形態に適用され得る。したがって、本開示は、本明細書に示した実施形態に限定することを意図するものではなく、以下の請求項によって規定されるような原理および新規な機能に一致する可能な限り広い範囲を与えられるものである。

#### 【符号の説明】

## [0054]

- 100 システム

- 110 プロセッサ

- 110 プロセッサの第1のセット

- 111 プライマリハイパーバイザ

- 112 第1のスケジューラ

- 112 スケジューラ

- 113 第1のゲストオペレーティングシステム

- 113 ゲストOS1

- 114 仮想プロセッサ

- 115 物理アドレス変換マッピングモジュール

- 115 物理アドレス変換マッピング

- 116 第2段階の変換

- 116 IPA PA

- 117 構成データ

- 118 開始/停止モジュール

- 118 ゲスト開始/停止

- 120 プロセッサ

- 120 プロセッサの第2のセット

- 121 セカンダリハイパーバイザ

- 122 第2のスケジューラ

- 122 スケジューラ

- 123 第2のゲストオペレーティングシステム

- 123 ゲストOS2

- 124 仮想プロセッサ

- 133 第3のゲストオペレーティングシステム

- 133 ゲストOS3

- 134 仮想プロセッサ

- 141 第1段階の変換

- 141 VA IPA

- 142 第1段階の変換

- 142 VA IPA

- 143 第1段階の変換

- 143 VA IPA

- タスク 151

- 152 タスク

- 153 タスク

- 201 仮想プロセッサ

- 201 ゲスト1VP1

- 202 仮想プロセッサ

- 202 ゲスト1VP2

- 203 仮想プロセッサ

- 203 ゲスト2VP1

- 204 仮想プロセッサ

- 204 ゲスト2VP2

- 205 第1の中間物理アドレス空間

- 206 第2の中間物理アドレス空間

- 207 物理アドレス空間

- 211 中間物理アドレス

10

20

30

40

- 212 中間物理アドレス

- 213 中間物理アドレス

- 221 中間物理アドレス

- 222 中間物理アドレス

- 223 物理アドレス

- 231 物理アドレス

- 232 物理アドレス

- 233 物理アドレス

- 234 物理アドレス

- 235 物理アドレス

- 400 電子デバイス

- 410 プロセッサ

- 410 プロセッサの第1のセット

- 422 システムオンチップデバイス

- 426 ディスプレイコントローラ

- 428 ディスプレイ

- 430 入力デバイス

- 432 メモリ

- 434 符号器/復号器(CODEC)

- 436 スピーカ

- マイクロフォン 438

- ワイヤレス制御装置 440

- 442 アンテナ

- 444 電源

- 456 命令

- 457 プライマリハイパーバイザ

- 457 プライマリHV

- セカンダリハイパーバイザ 458

- 458 セカンダリHV

- ゲストオペレーティングシステム 459

- 459 ゲストOS

- 474 プロセッサ

- 474 プロセッサの第2のセット

20

#### フロントページの続き

(72)発明者 ルシアン・コドレスク

アメリカ合衆国・カリフォルニア・92121 - 1714・サン・ディエゴ・モアハウス・ドライヴ・5775

(72)発明者 クリストファー・エドワード・クーブ

アメリカ合衆国・カリフォルニア・92121 - 1714・サン・ディエゴ・モアハウス・ドライヴ・5775

(72)発明者 ピユシュ・パテル

アメリカ合衆国・カリフォルニア・92121 - 1714・サン・ディエゴ・モアハウス・ドライヴ・5775

(72)発明者 トーマス・アンドリュー・サルトリウス

アメリカ合衆国・カリフォルニア・92121 - 1714・サン・ディエゴ・モアハウス・ドライヴ・5775

審査官 大桃 由紀雄

(56)参考文献 米国特許出願公開第2011/0296406 (US, A1)

米国特許第06286092(US,B1)

特開2012-220990(JP,A)

国際公開第2005/029326(WO,A1)

(58)調査した分野(Int.CI., DB名)

G06F 9/46

G06F 12/10