(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5049717号

(P5049717)

(45) 発行日 平成24年10月17日(2012.10.17)

(24) 登録日 平成24年7月27日(2012.7.27)

|                      |              |

|----------------------|--------------|

| (51) Int.Cl.         | F 1          |

| H05K 1/02 (2006.01)  | H05K 1/02 N  |

| H05K 3/46 (2006.01)  | H05K 3/46 Z  |

| H05K 3/00 (2006.01)  | H05K 3/00 X  |

| H01L 23/12 (2006.01) | H01L 23/12 E |

|                      | H01L 23/12 N |

請求項の数 5 (全 16 頁)

(21) 出願番号 特願2007-244878 (P2007-244878)

(22) 出願日 平成19年9月21日 (2007.9.21)

(65) 公開番号 特開2009-76721 (P2009-76721A)

(43) 公開日 平成21年4月9日 (2009.4.9)

審査請求日 平成22年8月12日 (2010.8.12)

(73) 特許権者 000190688

新光電気工業株式会社

長野県長野市小島田町80番地

(74) 代理人 100070150

弁理士 伊東 忠彦

(72) 発明者 堀内 章夫

長野県長野市小島田町80番地 新光電氣

工業株式会社内

(72) 発明者 松下 徳孝

長野県長野市小島田町80番地 新光電氣

工業株式会社内

審査官 吉澤 秀明

最終頁に続く

(54) 【発明の名称】多層配線基板

## (57) 【特許請求の範囲】

## 【請求項 1】

電源プレーンとグランドプレーンの何れか一方又はその両方が形成された配線層を含む多層配線基板であって、

前記電源プレーンとグランドプレーンの何れか一方又はその両方は、ジグザグのラインを含む所定の切断ラインで切断され、複数の電源プレーン片とグランドプレーン片の何れか一方又はその両方に分割されており、

前記電源プレーン片とグランドプレーン片の何れか一方又はその両方は、前記多層配線基板の内層に前記多層配線基板の中央から放射状に形成されており、

前記配線層の前記電源プレーン片とグランドプレーン片の何れか一方又はその両方と、他の配線層の電源プレーン片とグランドプレーン片の何れか一方又はその両方とは、前記配線層と前記他の配線層との間に配置された絶縁層に形成されたビアを介して電気的に接続されていることを特徴とする多層配線基板。

## 【請求項 2】

前記切断ラインは、平面視矩形状の多層配線基板の対角線上に形成されていることを特徴とする請求項 1 に記載の多層配線基板。

## 【請求項 3】

前記電源プレーンとグランドプレーンの何れか一方又はその両方は、前記ビアが形成される領域を囲うように枠状に形成されていることを特徴とする請求項 1 又は 2 に記載の多層配線基板。

10

20

**【請求項 4】**

前記電源プレーンとグランドプレーンの何れか一方又はその両方は、前記多層配線基板の厚み方向に対称に配置されていることを特徴とする請求項 1 乃至 3 の何れか一項に記載の多層配線基板。

**【請求項 5】**

前記複数の電源プレーン片とグランドプレーン片の何れか一方又はその両方は、略合同であることを特徴とする請求項 1 乃至 4 の何れか一項に記載の多層配線基板。

**【発明の詳細な説明】****【技術分野】****【0001】**

10

本発明は、多層配線基板に関し、特に、電源プレーン及び／又はグランドプレーンが形成された配線層を含む多層配線基板に関する。

**【背景技術】****【0002】**

従来から、コア基板上に樹脂層と配線層を多層に積み重ねた多層配線構造を有する多層配線基板（ビルドアップ基板）が知られているが、近年の薄型化、省スペース化の要求により、コア基板を有せず、多層配線構造に形成されたコアレスの多層配線基板が提案されている。かかるコアレスの多層配線基板においては、電源プレーン及び／又はグランドプレーンが形成された配線層を有し、信号用の配線パターンに電位供給を行うのが一般的である。

20

**【0003】**

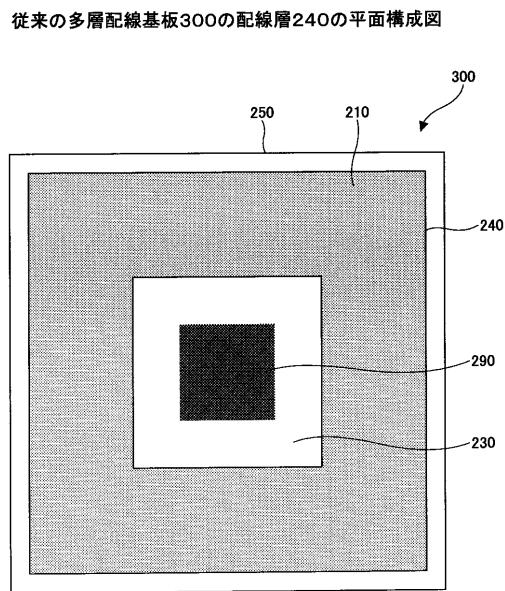

図 9 は、従来の多層配線基板 300 の電源プレーン及び／又はグランドプレーン 210 が形成された配線層 240 の平面構成図である。なお、配線層 240 の周囲には、配線層 240 の上層又は下層に存在する絶縁層 250 が示されている。

**【0004】**

多層配線基板 300 においては、信号用の配線パターンの他、これに電源又はグランド電位を供給するため、電源プレーン及び／又はグランドプレーン 210 が形成された配線層 240 を有する場合が多い。一例として、電源プレーン及び／又はグランドプレーン 210 は、多層配線基板 300 の半導体素子搭載面に搭載される仮想的な半導体素子 290 の周囲の中央部 230 を取り囲むように、いわゆるベタ状態で配線層 240 の大部分を連続した金属で覆う配線パターンとして形成される。電源プレーン及び／又はグランドプレーン 210 は、配線パターンの上方又は下方にビア（図示せず）が形成され、これを介して電源又はグランドに接続され、配線層 240 への電位供給が行われる。そして更に、配線層 240 から信号用の配線パターンが形成された配線層への電位供給が行われる。かかる配線層 240 及び絶縁層 250 を有する多層配線基板 300 において、電源プレーン及び／又はグランドプレーン 210 には銅が用いられることが多く、絶縁層 250 にはエポキシ樹脂が用いられることが多い。

30

**【0005】**

なお、かかるコアレスの多層配線基板においては、配線基板が薄くなり基板自体の強度が弱まることから、搬送等の取扱性を向上させるべく、基板の端部に金属製の枠体を設けた技術が知られている（例えば、特許文献 1 参照）。

40

**【特許文献 1】特開 2000 - 323613 号公報****【発明の開示】****【発明が解決しようとする課題】****【0006】**

しかしながら、上述の図 9 に示した従来技術の構成では、多層配線基板 300 の製造工程で熱処理を行っているときには多層配線基板 300 に反りを生じていなくても、製造工程が終わって多層配線基板 300 が通常温度になると、絶縁層 250 のエポキシ樹脂が収縮し、多層配線基板 300 が反りを生ずるという問題があった。

**【0007】**

50

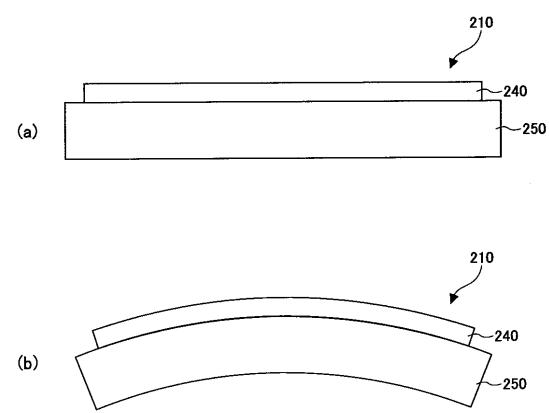

図10は、従来の配線基板300の、電源プレーン及び／又はグランドプレーン210が形成された配線層240と、その下層の絶縁層250の断面構造を示した断面構成図である。

#### 【0008】

図10(a)は、配線基板300製造時における、例えば150度に加熱している状態の配線層240及び絶縁層250の断面構成を示した図である。図10(a)において、エポキシ樹脂で形成された絶縁層250の上層に、銅で形成された電源プレーン及び／又はグランドプレーン210が形成された配線層240が配置されている。配線基板300製造中の150度の環境下では、両者は平行な層を形成している。

#### 【0009】

図10(b)は、配線基板300の温度が下がった状態における、配線層240及び絶縁層250の断面構成を示した図である。エポキシ樹脂の熱膨張係数は $30 \sim 40 [10^6 / K]$ であり、銅の熱膨張係数は $17 \sim 18 [10^6 / K]$ であるため、両者の熱膨張係数には大きな差があり、従って、配線層240の収縮率よりも、絶縁層250の収縮率の方が大きく、同じ温度に低下した場合には、絶縁層250の方が配線層240よりも収縮量が大きい。よって、図10(b)に示すように、配線層240が絶縁層250に引っ張られるような状態になってしまい、配線基板300に反りが発生してしまう。配線基板300製造時にかかる反りが生じた場合には、反り修正を行う必要があるが、これにより製造工程の効率ダウン及びコスト増を招くという問題があった。

#### 【0010】

また、上述の特許文献1に記載の構成では、搬送時の取扱性の向上については配慮されているものの、配線基板の製造工程で生ずる反りの問題については何ら考慮されていない。よって、製造工程でコアレスの多層配線基板に反りが生じた場合には、やはり反りの修正を必要とし、製造工程の効率低下とコスト増を招くという問題があった。

#### 【0011】

また、コア基板を有する配線基板においても、基板に反りが生じた場合には、やはり反りの修正が必要となり、製造工程の効率低下とコスト増が同様に問題となっていた。

#### 【0012】

そこで、本発明は、温度低下時においても配線基板の反りの発生を抑制し、配線基板製造時にも反りの修正を行う必要の無い多層配線基板を提供することを目的とする。

#### 【課題を解決するための手段】

#### 【0013】

上記目的を達成するため、本発明に係る多層配線基板は、電源プレーンとグランドプレーンの何れか一方又はその両方が形成された配線層を含む多層配線基板であって、前記電源プレーンとグランドプレーンの何れか一方又はその両方は、ジグザグのラインを含む所定の切断ラインで切断され、複数の電源プレーン片とグランドプレーン片の何れか一方又はその両方に分割されており、前記電源プレーン片とグランドプレーン片の何れか一方又はその両方は、前記多層配線基板の内層に前記多層配線基板の中央から放射状に形成されており、前記配線層の前記電源プレーン片とグランドプレーン片の何れか一方又はその両方と、他の配線層の電源プレーン片とグランドプレーン片の何れか一方又はその両方とは、前記配線層と前記他の配線層との間に配置された絶縁層に形成されたビアを介して電気的に接続されていることを特徴とする。

#### 【0014】

これにより、金属と樹脂との熱膨張係数の差によって配線基板に反りが生じたとしても、応力を切断ラインの部分に逃がすことができ、配線基板が全体で大きく反ることを防止することができる。

#### 【0016】

これにより、配線基板の反りを、搭載される半導体素子を中心として抑制することができ、搭載される半導体素子への影響を抑制することができる。

#### 【発明の効果】

10

20

30

40

50

**【0031】**

本発明によれば、多層配線基板及び複数の多層配線基板が配列された基板の反りを抑制することができる。

**【発明を実施するための最良の形態】****【0032】**

以下、図面を参照して、本発明を実施するための最良の形態の説明を行う。

**【実施例1】****【0033】**

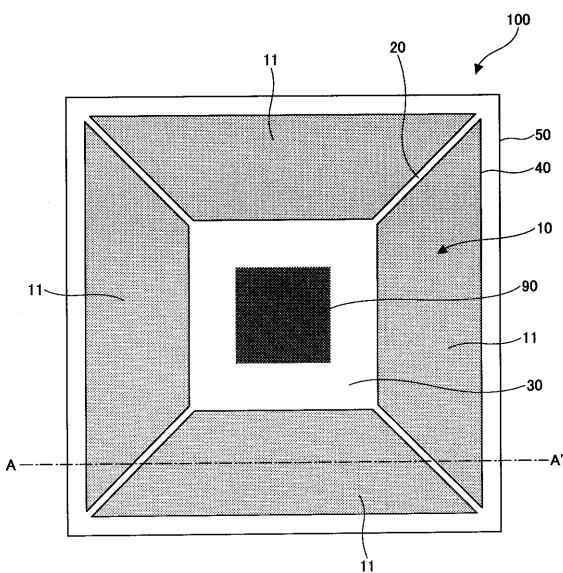

図1は、本発明を適用した実施例1に係る多層配線基板100の、電源プレーン及び/又はグランドプレーン10が形成された配線層40の平面構成を示した平面構成図である

10

。

**【0034】**

図1において、電源プレーン及び/又はグランドプレーン10は、絶縁層50の上層又は下層に形成され、多層配線基板100表面の半導体素子搭載面に搭載される仮想的な半導体素子90の周囲の中央部30を除き、配線層240の大部分を、銅やアルミ等の金属により覆った配線パターンとなっている。そして、電源プレーン及び/又はグランドプレーン10は、全体で1つの連続したベタ膜となっているのではなく、中央部30から4隅に延在する4本の切断ライン20により、4つの電源プレーン片及び/又はグランドプレーン片11に分割されている。

**【0035】**

20

このように、電源プレーン及び/又はグランドプレーン10を、配線層240全体を覆う1枚のベタ膜で構成するのではなく、電源プレーン及び/又はグランドプレーン10の所定位置に適宜スリット状の切断ライン20を設け、これを複数の電源プレーン片及び/又はグランドプレーン片11で構成することにより、熱ストレスを切断ライン20で開放し、多層配線基板100全体の反りを低減することができる。

**【0036】**

熱ストレスが生じるのは、金属と樹脂の熱膨張係数の大きさの相違により、樹脂が熱硬化すると、金属よりも樹脂の方が大きく収縮し、樹脂の絶縁層50上に形成された金属の配線層40が、絶縁層50に引っ張られるように収縮するからである。例えば、配線層40上の電源プレーン及び/又はグランドプレーン10が銅であり、絶縁層50がエポキシ樹脂の場合には、銅の熱膨張係数は $17 \sim 18 [10^{-6} / K]$ であり、エポキシ樹脂の熱膨張係数は $30 \sim 40 [10^{-6} / K]$ であるので、エポキシ樹脂の熱膨張係数は、銅の熱膨張係数の2倍前後あることになる。この場合に、150程度の製造工程では多層配線基板100が反っていなかった場合でも、製造工程が一通り終了して温度が下がった場合には、多層配線基板100に上述のような熱膨張係数の違いによる変形ストレスが生じてしまう。

30

**【0037】**

そこで、多層配線基板10の電源プレーン及び/又はグランドプレーン10が形成された配線層40において、切断ライン20により電源プレーン及び/又はグランドプレーン10が小片の電源プレーン片及び/又はグランドプレーン片11に分割されていれば、切断ライン20が変形ストレスの逃げ道となり、多層配線基板100全体の変形度合を小さくすることができる。

40

**【0038】**

図1において、電源プレーン及び/又はグランドプレーン10は、中央部30から4隅に延在する4本のスリット状の切断ラインにより、4つの合同かつ対称な電源プレーン片及び/又はグランドプレーン片11に分割されている。切断ライン20は、種々の任意の位置に設けられてよいが、例えば、図1に示すように、中央部から外側に延在する放射状の切断ラインであってもよい。例えば、半導体素子90が多層配線基板100の中央部に搭載される場合には、半導体素子90に対して、多層配線基板100の反りの方向が対称となるように構成されるので、搭載される半導体素子90への影響を小さくすることができ

50

きる。

**【0039】**

また、図1に示すように、切断ライン20は、電源プレーン及び/又はグランドプレーン10を、線対称に分割する位置に設けられてもよい。これにより、切断ライン20により分割される個々の電源プレーン片及び/又はグランドプレーン片11が合同となり、かつ隣接する電源プレーン片及び/又はグランドプレーン片11が切断ライン20に関して対称となるので、切断ライン20に両側から逃げ込む応力が、左右で等しくなり、左右均等にバランスよく応力を開放することができる。

**【0040】**

なお、配線層40に形成された電源プレーン及び/又はグランドプレーン10は、電源プレーンのみで構成されてもよいし、グランドプレーンのみで構成されてもよいし、更には両者の組み合わせであってもよい。配線層40に電源プレーン及びグランドプレーンの双方が形成される場合には、電源プレーン10とグランドプレーン10は最初から分割されており、2つの配線パターン片から構成された状態となっている。この場合であっても、2つの配線パターン片がベタ膜で構成された場合には、2つの配線パターン片で配線層40全体を覆うことになるので、やはり基板の反りは大きくなってしまう。従って、図1に示すように、電源プレーン及びグランドプレーン10を各々2つずつの電源プレーン片及びグランドプレーン片11で構成するようにすれば、やはり本実施例により多層配線基板100の反りを低減することができる。

**【0041】**

また、切断ライン20の位置や数は任意に設定することができ、例えば、もっと細かく分割して、個々の電源プレーン片及び/又はグランドプレーン片11の大きさを小さくするとともに、切断ライン20の数を増やせば、個々の電源プレーン片及び/又はグランドプレーン片11の変形が小さくなるとともに、応力の逃げ道の数は増加するので、更に多層配線基板100の反りを抑制することができる。

**【0042】**

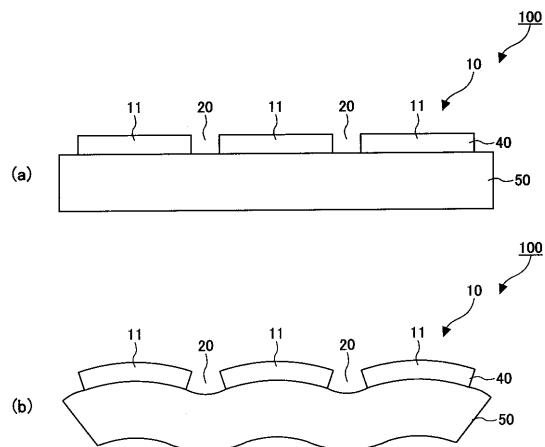

図2は、図1に係る多層配線基板100の配線層40及び絶縁層50を、A-A'断面で切った断面構成図である。

**【0043】**

図2(a)は、温度が150程度の、多層配線基板100製造中の状態を示した断面図である。なお、図1とは、若干電源プレーン片及び/又はグランドプレーン片11の長さの比率が異なるが、理解の容易のために、略3等分した図で説明する。図2(a)において、絶縁層50の上に配線層40が形成されており、配線層40には、電源プレーン及び/又はグランドプレーン10が形成されているが、1つの連続して繋がった状態のいわゆるベタ膜ではなく、切断ライン20により空隙が形成されている。この多層配線基板100の製造中の温度150程度の状態においては、絶縁層50及び配線層40の双方に収縮は発生せず、両者は平行な層として形成されている。

**【0044】**

図2(b)は、温度が下がった状態における多層配線基板100の断面構成図である。図2(b)において、金属と樹脂の熱膨張係数は異なるので、樹脂が硬化した状態では、絶縁層50の方の収縮量が配線層40より大きくなるが、図2(b)に示すように、電源プレーン及び/又はグランドプレーン10が、スリット状の切断ライン20により3つの電源プレーン片及び/又はグランドプレーン片11に分割されているため、配線層40及び絶縁層50は3つの変形を生じるが、個々の変形は小さくなり、多層配線基板100全体としての反りは、小さく抑えられる。

**【0045】**

このように、本実施例に係る多層配線基板100によれば、電源プレーン及び/又はグランドプレーン10を所定の切断ライン20でより小さな単位に分割したことにより、個々の反りの大きさを小さくし、多層配線基板100全体としての反りを小さくすることができる。

10

20

30

40

50

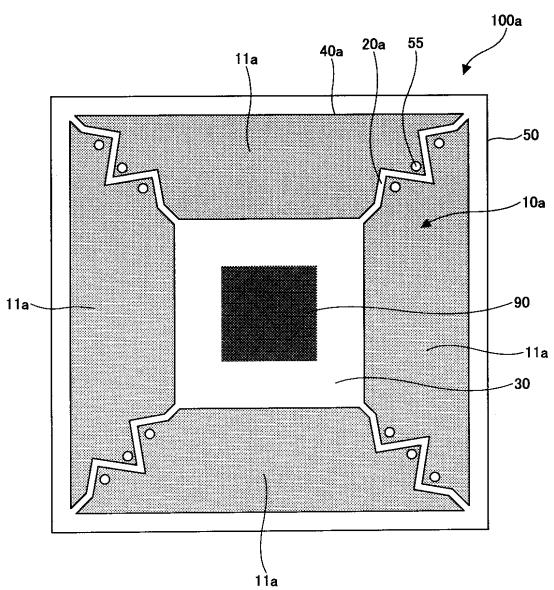

**【実施例 2】****【0046】**

図3は、本発明を適用した実施例2に係る多層配線基板100aの電源プレーン及び/又はグランドプレーン10aが形成された配線層40aの平面構成図である。図3において、絶縁層50上に配線層40aが形成され、配線層40a上には、中央部30から4隅に延在する4本の放射状の切断ライン20aにより形成された4つの電源プレーン片及び/又はグランドプレーン片11aからなる電源プレーン及び/又はグランドプレーン10aが形成されている点で、実施例1に係る電源プレーン及び/グランドプレーン10と同様であるが、所定の切断ライン20aが、直線的なスリットではなく、ジグザグのラインを含んでいる点で、実施例1の態様とは異なっている。そして、所定の切断ライン20aのジグザグラインを形成する部分には、配線層40の上層又は下層に存在するビア55の存在が示されている。なお、ジグザグに形成された切断ライン20aは、角部を有さない曲線状ラインに形成してもよい。この場合、角部への応力集中が無いため、より好適に応力を分散させて逃がすことができる。

**【0047】**

このように、ビア55の配置位置と、配線層40の配線パターンとの関係により、所定の切断ライン20aは、ビア55と所望の電源プレーン片及び/又はグランドプレーン片11aとの接続がなされるような形状に構成してよい。実施例2によれば、所定の切断ライン20aのライン形状は、配線パターンに応じて、所望のライン形状とすることができ、かかる配線層40の平面構成によつても、切断ライン20aに応力を開放し、多層配線基板100aの反りを低減することができる。

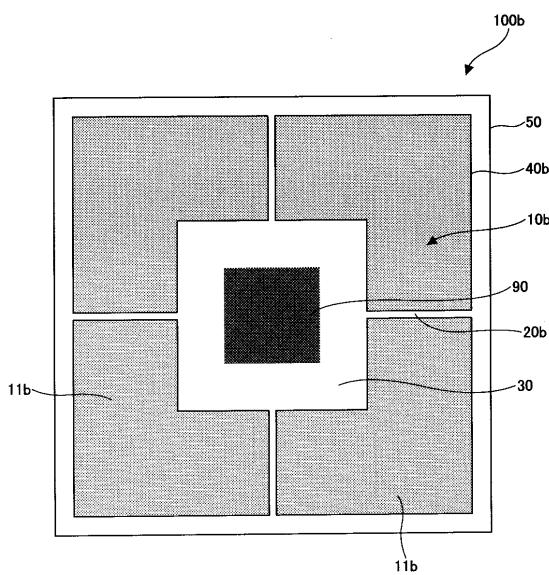

**【実施例3】****【0048】**

図4は、本発明を適用した実施例3に係る多層配線基板100bの電源プレーン及び/又はグランドプレーン10bが形成された配線層40bの平面構成図である。

**【0049】**

図4において、電源プレーン及び/又はグランドプレーン10bが、4つの切断ライン20bにより4つの電源プレーン片及び/又はグランドプレーン片40bに分割されている点では、実施例1及び実施例2と同様であるが、切断ライン20bが、中央部30から配線層40を形成する4辺の中点に延在している点で、実施例1及び実施例2とは異なっている。

**【0050】**

このように、切断ライン20bは、電源プレーン及び/又はグランドプレーン10bを、4つの長方形の電源プレーン片及び/又はグランドプレーン片11bに分割するラインであつてもよい。この場合も、切断ライン20bは隣接する電源プレーン片及び/又はグランドプレーン片11bを線対称に分割するラインとなっており、かつ4つの電源プレーン片及び/又はグランドプレーン片10bは総て合同である。従って、個々の電源プレーン片及び/又はグランドプレーン片10bに加わる応力は等しくなり、切断ライン40bに逃げる応力も総て左右等しくなりバランスするので、多層配線基板100bの反りを適切に抑制することができる。

**【実施例4】****【0051】**

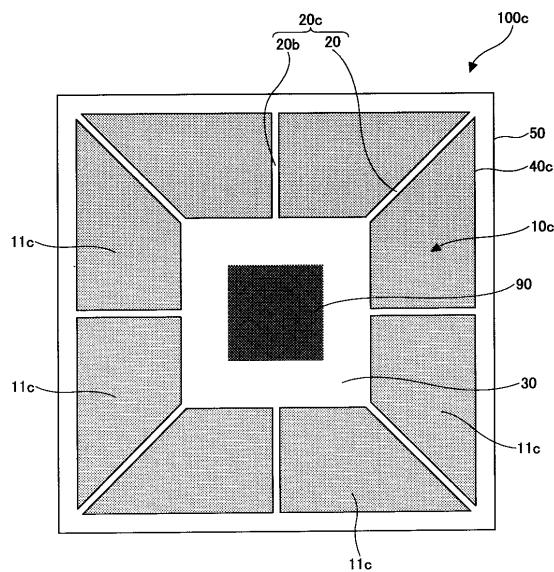

図5は、本発明を適用した実施例4に係る多層配線基板100cの電源プレーン及び/又はグランドプレーン10cが形成された配線層40cの平面構成図である。

**【0052】**

図5において、電源プレーン及び/又はグランドプレーン10cが、8本の切断ライン20cにより切断され、8つの電源プレーン片及び/又はグランドプレーン片11cに分割されている点で、実施例1~3とは異なっている。このように、切断ライン20cの数を増やし、電源プレーン及び/又はグランドプレーン10cをより多くの電源プレーン片及び/又はグランドプレーン片11cに分割するようにしても良い。個々の電源プレーン

片及び／又はグランドプレーン片 11c の大きさを小さくできるので、個々の電源プレーン片及び／又はグランドプレーン片 11c に加わる応力及び変形の大きさを更に小さくすることができる。また、応力の逃げ道となる切断ライン 20c の数が増加するので、熱ストレスの開放がより細かな単位で行うことができ、多層配線基板 100c の全体の反り量を減少させることができる。

#### 【0053】

なお、図 5において、切断ライン 20c は、実施例 1 で示した中央部 30 から配線層 40 の 4 隅に延在する切断ライン 20 と、実施例 3 で示した中央部 30 から配線層 40 の 4 辺の中点に延在する切断ライン 20b との組み合わせとなっている。このように、総ての切断ライン 20c は同一でなくてもよく、複数のライン形状の組み合わせであってもよい。所望の切断ライン 20、20b を組み合わせることにより、用途に応じて適切な電源プレーン及び／又はグランドプレーン 10c の配線パターンを構成することができる。10

#### 【0054】

また、図 5において、所定の切断ライン 20c は、総て隣接する電源プレーン片及び／又はグランドプレーン片 11c を線対称に分割しており、個々の電源プレーン片及び／又はグランドプレーン片 11c は総て合同な形状となっている。これにより、切断ライン 20c に向かう応力を、切断ライン 20c の両側で等しくすることができ、多層配線基板 100c の反りをバランスよく均等に抑制することができる。

#### 【0055】

このように、実施例 1～4 で説明したように、電源プレーン及び／又はグランドプレーン 10、10a～10c 及び所定の切断ライン 20、20a～20c は、用途に応じて種々の態様を適用することが可能である。また、実施例 1～4 においては、電源プレーン片及び／又はグランドプレーン片 11、11a～11c が合同となる態様を説明したが、これに制限されることはなく、これも用途に応じて種々の態様を適用してよい。例えば、電源プレーン片及び／又はグランドプレーン片 11、11a～11c は、異なる形状や大きさの電源プレーン片及び／又はグランドプレーン片 11、11a～11c を含んでもよい。また、配線層 40、40a～40c は、必ずしも電源プレーン及び／又はグランドプレーン 10、10a～10c のみで形成される必要は無く、他に信号用の配線パターン等が形成されている部分を含んでもよい。20

#### 【0056】

また、実施例 1～4 に係る多層配線基板 100、100a～100c は、反りの問題を生じ易いコアレスの多層配線基板に適用するのが最適であるが、コア基板を有する多層配線基板であっても、好適に適用可能である。本発明は、コア基板を有しないコアレスの多層配線基板のみならず、コア基板を有する多層配線基板にも好適に適用することができる。30

#### 【実施例 5】

#### 【0057】

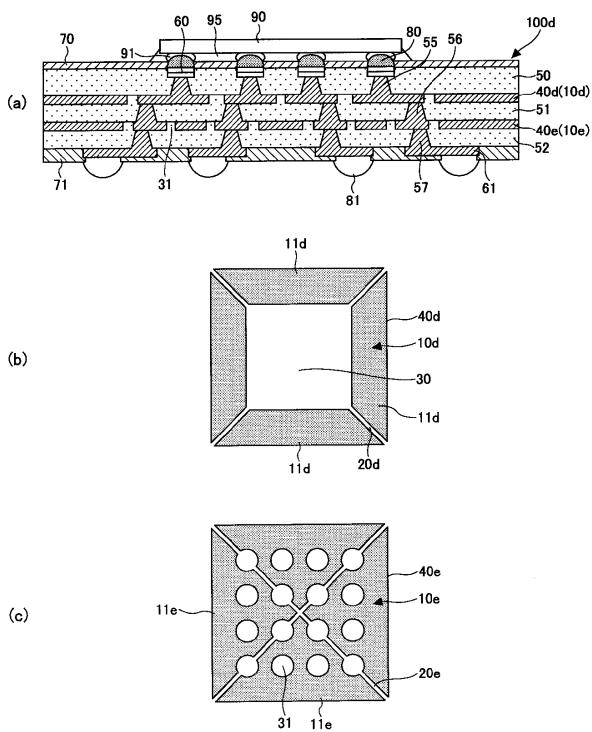

図 6 は、本発明を適用した実施例 5 に係る多層配線基板 100d を説明するための図である。実施例 5 においては、電源プレーン及び／又はグランドプレーン 10d、10e が形成された配線層 40d、40e を含む多層配線基板 100d の断面構成の例について説明する。40

#### 【0058】

図 6 (a) は、実施例 5 に係る多層配線基板 100d の断面構成を示した図である。図 6 (a) において、多層配線基板 100d は、表面に半導体素子搭載用の端子パッド 60 を備え、反対面には、外部端子接続用の端子パッド 61 を備えており、半導体パッケージとして構成されている。また、多層配線基板 100d の半導体素子搭載面の端子パッド 60 以外の部分は、ソルダレジスト 70 で覆われており、同様に、外部端子接続面の端子パッド 61 以外の部分も、ソルダレジスト 71 で覆われている。

#### 【0059】

半導体素子搭載用の端子パッド 60 には、プリソルダ 80 が形成され、半導体素子 90

50

の電極端子に形成されたバンプ 9 1 と半田接合され、半導体素子 9 0 が多層配線基板 1 0 0 d に搭載されている。半導体素子 9 0 と多層配線基板 1 0 0 dとの間には、アンダーフィル樹脂 9 5 が充填されている。一方、多層配線基板 1 0 0 d の反対面の外部端子接続用の端子パッド 6 1 には、外部接続端子として半田ボール 8 1 が形成され、マザーボード等に接続可能に構成されている。なお、半田ボール 8 1 は、半田バンプであってもよいし、ピンやランド形状であってもよい。

#### 【 0 0 6 0 】

本実施例に係る多層配線基板 1 0 0 d は、このような半導体パッケージとして適用されてもよい。次に、多層配線基板 1 0 0 d の多層配線構造について説明する。

#### 【 0 0 6 1 】

図 6 において、半導体素子搭載用の端子パッド 6 0 の下層には、第 1 層目絶縁層 5 0 が形成されており、第 1 層目絶縁層 5 0 の端子パッド 6 0 の直下には、ビア 5 5 が形成され、金属が充填されている。そして、ビア 5 5 を充填した金属と同一層に、電源プレーン及び / 又はグランドプレーン 1 0 d が形成された配線層 4 0 d が形成されている。

#### 【 0 0 6 2 】

また、配線層 4 0 d は、第 2 層目絶縁層 5 1 で覆われるとともに、配線層 4 0 d と電気的接続を図るためにビア 5 6 が第 2 層目絶縁層 5 1 の配線層 4 0 d の直下に形成され、これに金属が充填されて形成された金属層と同一層に、電源プレーン及び / 又はグランドプレーン 1 0 e が形成された配線層 4 0 e が形成されている。そして、配線層 4 0 e は、第 3 層目絶縁層 5 2 に覆われ、第 3 層目絶縁層 5 2 に形成されたビア 5 7 により、外部端子接続用の端子パッド 6 1 との電気的接続がなされている。また、ビア 5 6 及びビア 5 7 を通すため、配線層 4 0 e には、開口 3 1 が形成されている。

#### 【 0 0 6 3 】

このように、電源プレーン及び / 又はグランドプレーン 1 0 d 、 1 0 e は、多層配線基板 1 0 0 d の基板内層に設けるようにしてよい。多層配線基板 1 0 0 d の反りの発生は、上述のように金属と樹脂との熱膨張率の相違で生じるが、多層配線基板 1 0 0 d の基板内層に金属のベタ膜のパターンが存在する方が、多層配線基板 1 0 0 d の厚み方向（積層方向）での対称性が良くなるため、基板の反りを低減することができる。

#### 【 0 0 6 4 】

なお、本実施例においては、電源プレーン及び / 又はグランドプレーン 1 0 d 、 1 0 e を有する配線層 4 0 d 、 4 0 e が 2 層設けられている例について説明したが、電源プレーン及び / 又はグランドプレーン 1 0 d 、 1 0 e が形成された配線層 4 0 d 、 4 0 e は、1 層であっても、複数層であってもよい。多層配線基板 1 0 0 d の用途と態様により、電源プレーン及びグランドプレーン 1 0 d 、 1 0 e を有する配線層 4 0 d 、 4 0 e は、種々の態様とすることができます。

#### 【 0 0 6 5 】

次に、本実施例に係る多層配線基板 1 0 0 d の電源プレーン及び / 又はグランドプレーン 1 0 d 、 1 0 e が形成された配線層 4 0 d 、 4 0 e の平面構成例について説明する。

#### 【 0 0 6 6 】

図 6 ( b ) は、電源プレーン及び / 又はグランドプレーン 1 0 d が形成された配線層 4 0 d の平面構成例を示した図である。図 6 ( b ) において、配線層 4 0 d は、中央部 3 0 の周囲を囲む電源プレーン及び / 又はグランドプレーン 1 0 d を有しており、電源プレーン及び / 又はグランドプレーン 1 0 d は、配線層 4 0 d の対角線上にある 4 本の切断ライン 2 0 d により 4 個の電源プレーン片及び / 又はグランドプレーン片 1 1 d に分割されている。

#### 【 0 0 6 7 】

このように構成することにより、配線層 4 0 d と上下の絶縁層 5 0 、 5 1 との間で熱膨張係数が異なっていても、発生する応力を逃がして多層配線基板 1 0 d の反りを低減することができる。

#### 【 0 0 6 8 】

10

20

30

40

50

図6(c)は、電源プレーン及び/又はグランドプレーン10eが形成された配線層40eの平面構成例を示した図である。配線層40eにおいては、ビア56が形成される複数の開口31の周囲の各々を囲むように、電源プレーン及び/又はグランドプレーン10eが形成されている。そして、電源プレーン及び/又はグランドプレーン10eは、配線層40eの対角線上に形成された2本の切断ライン20eにより、4個の電源プレーン片及び/又はグランドプレーン片11eに分割されている。

#### 【0069】

このように、配線層40eの平面構成は、中央部30が開いた場合だけではなく、複数のビア56の周囲に開口31が複数設けられた様の場合もあり得るが、このような様の配線層40eにおいても、電源プレーン及び/又はグランドプレーン10eを所定の切断ライン20eで切断することにより、小さな面積の電源プレーン片及び/又はグランドプレーン片11eに分割し、多層配線基板100dの反りを低減することができる。10

#### 【0070】

また、上述のように、実施例5においては、電源プレーン及び/又はグランドプレーン10d、10eが形成された配線層40d、40eは、ともに多層配線基板100dの内層に厚み方向に略対称に配置されているので、多層配線基板100dの反りは、効果的に相殺される。

#### 【0071】

なお、実施例5において、電源プレーン及び/又はグランドプレーン10d、10eが形成された配線層40d、40eは、一方の配線層40d、40eが電源プレーン層として用いられ、他方の配線層40d、40eがグランドプレーン層として用いられるように構成してもよいし、電源プレーンと電源プレーンが混在した配線層40d、40eとして形成されてもよい。その組み合わせは、用途に応じて種々の様とすることができる。20

#### 【0072】

また、実施例5において、配線層40d、40e以外に配線層を設けていないが、他の配線層を設け、これとビアを用いて、同一配線層40e、40d内に形成された電源プレーン片及び/又はグランドプレーン片11d、11e同士の電気的接続を図るようにしてもよい。例えば、配線層40dの4個の電源プレーン片及び/又はグランドプレーン片11dの総てを同一電位に接続したい場合には、ビアと他の配線層を介してこれらを接続するようにしてもよい。30

#### 【0073】

また、同一配線層40d、40e上に形成された複数の電源プレーン片及び/又はグランドプレーン片11d、11eのうち、任意の電源プレーン片及び/又はグランドプレーン片11d、11e同士で電気的接続を図りたい場合には、電気的接続を図りたい電源プレーン片及び/又はグランドプレーン片11d、11eの間の切断ライン20d、20eの一部を未切断として残しておき、電気的接続を図るようにしてもよい。

#### 【0074】

このように、本来はベタ膜である電源プレーン及び/又はグランドプレーン10d、10eを面積の小さい複数の電源プレーン片及び/又はグランドプレーン片11d、11eに分割するとともに、これらを電気的に接続する電気接続手段を設けることにより、従来のままの電気的接続関係は維持しつつ、多層配線基板100dの反りを抑制した構成とすることができる。40

#### 【0075】

なお、実施例5における電気的接続の説明は、今まで説明した実施例1～4の多層配線基板100、100a～100cに総て適用することができる。

#### 【0076】

また、実施例1～4に係る配線層40、40a～40cの平面構成も、総て実施例5に係る多層配線基板100dの断面構成に適用してよい。

#### 【実施例6】

#### 【0077】

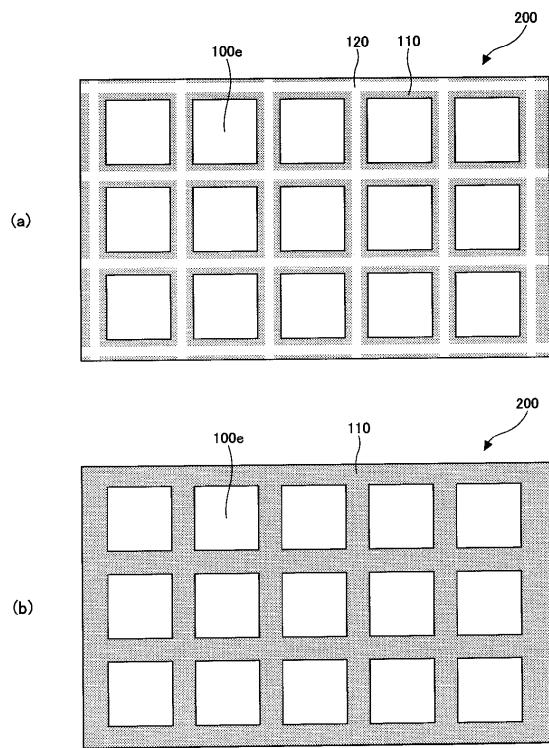

図7は、本発明を適用した実施例6に係る大判基板200を説明するための図面である。図7(a)は、実施例6に係る大判基板200を示した平面構成図である。大判基板200は、複数の多層配線基板100eの集合体であって、大判状の基板200に、個々の多層配線基板100eとなる配線層が形成された集合基板である。

#### 【0078】

実施例1～5において説明した多層配線基板100、100a～100dの製造においては、このような大判状の基板200上に個々の多層配線基板100、100a～100dとなる配線層を形成し、最後に大判状の基板200を切断し、個々の多層配線基板100、100a～100dを得ている場合がある。実施例6においては、このような製造方法による場合に、本発明を大判基板200に適用する例について説明する。なお、大判基板200に適用される個々の多層配線基板は、種々の態様が適用可能であるので、以後統一的に、多層配線基板100eと参照符号を付することとする。

10

#### 【0079】

図7(a)において、大判基板200は、中央の多層配線基板100eが形成されている部分と、これを外側から枠状に支持する枠部110を有する。個々の多層配線基板100eは、例えば半導体素子搭載用の半導体パッケージであってもよく、その配線構造部分には、電源プレーン及び／又はグランドプレーンを含む配線層が形成されている。また、枠部110は、個々の多層配線基板100eを外側から支持する支持体である。このような大判基板200において、個々の多層配線基板100eの配線層中に電源プレーン及び／又はグランドプレーンを形成する場合、枠部110に金属部材が被着されたベタ状の配線パターンが形成される。

20

#### 【0080】

図7(b)は、大判基板200の枠部110の表面に金属部材が被着し、ベタ状の配線パターンが形成された状態を示した図である。図7(b)のように、大判基板200の枠部110のベタ状の配線パターンが形成されたまま多層配線基板100eを製造してゆくと、樹脂と金属の熱膨張係数の差により、製造中に大判基板200が反りを生じてしまう。

#### 【0081】

そこで、本実施例に係る大判基板200は、図7(a)に示すように、大判基板200の周囲に配置された枠部110に切断ライン120によるスリットを設け、応力を緩和するようにしている。

30

#### 【0082】

つまり、図7(a)においては、大判基板200の外枠を形成する外側の枠部110に、所定の切断ライン120を形成している。本実施例に係る大判基板200においては、かかる枠部110に、各多層配線基板100eの縦横の配列ラインを外側に延長するように、縦横の配列ラインの延長線上に切断ライン120を入れている。なお、縦横の配列ラインは、個々の多層配線基板100eの四辺を延長したものと考えてもよい。

#### 【0083】

これにより、大判基板200の製造中に熱膨張係数の差により変形が生じても、これに起因する応力は切断ライン120に逃げて開放され、大判基板200全体の反りを抑制することができる。

40

#### 【0084】

なお、本実施例においては、切断ライン120は、多層配線基板100eの縦横の配列ラインの延長線上に設けているが、これにより、応力の開放位置が、各多層配線基板100eに最も影響が少ない位置となる。つまり、各多層配線基板100eの辺の途中ではなく、多層配線基板100eが隣接する切れ目に応力の逃げ道ができるので、多層配線基板100e自体には応力が加わり難くなる。

#### 【0085】

但し、切断ライン120の位置は、本実施例に限定されるものではなく、態様に応じて、適切な位置に設けるようにしてよい。

50

**【0086】**

なお、大判基板200の中央に形成された個々の多層配線基板100eの電源プレーン及び／又はグランドプレーンには、例えば実施例1～4において説明したような、スリット状の切断ライン20、20a～20eが形成されていてよい。また、この場合、大判基板200の枠部110への切断ライン120の形成は、個別の多層配線基板100eの配線層に設けられた電源プレーン及び／又はグランドプレーンに切断ライン20、20a～20eを設ける際に同時にあってよい。

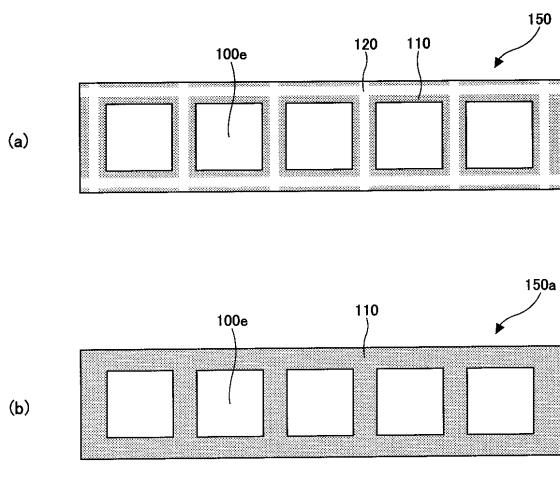

**【0087】**

図8は、大判基板200を、短冊状に切断した状態を示した図である。図8(a)は、実施例6に係る大判基板200を、短冊状に切断した状態を示した短冊状基板150を示した平面構成図である。一例として、図8(a)に示した短冊状基板150の状態で、半導体素子90の実装を行い、その後、個々の多層配線基板100eに切断し、半導体パッケージが完成する。

10

**【0088】**

図8(b)は、枠部110がベタ状の配線パターンに形成された短冊状基板150aを示した図である。この状態で、個々の多層配線基板100eに対して半導体素子90の実装を行うと、実装時の加熱により短冊状基板150aが反ってしまい、半導体素子90の実装が良好に実施できない。

**【0089】**

一方、図8(a)は、本実施例に係る短冊状基板150を示した平面構成図であるが、枠部110に切断ライン120が入っているため、応力を逃がすことができ、半導体素子90の実装を良好に行える。そして、半導体素子90実装後は、個々の多層配線基板100eに切断し、半導体素子90の実装が良好になされた半導体パッケージとすることができる。

20

**【0090】**

このように、本発明は、個々の多層配線基板100、100a～100eのみならず、大判基板200及び短冊状基板150にも好適に適用可能である。

**【0091】**

以上、本発明の好ましい実施例について詳説したが、本発明は、上述した実施例に制限されることはなく、本発明の範囲を逸脱することなく、上述した実施例に種々の変形及び置換を加えることができる。

30

**【図面の簡単な説明】****【0092】**

【図1】実施例1に係る多層配線基板100の配線層40の平面構成図である。

【図2】図1に係る配線層40及び絶縁層50をA-A'断面で切った断面構成図である。図2(a)は、多層配線基板100製造中の状態を示した断面図である。図2(b)は、反りが生じた状態の多層配線基板100の断面図である。

【図3】実施例2に係る多層配線基板100aの配線層40aの平面構成図である。

【図4】実施例3に係る多層配線基板100bの配線層40bの平面構成図である。

【図5】実施例4に係る多層配線基板100cの配線層40cの平面構成図である。

40

【図6】実施例5に係る多層配線基板100dの説明図である。図6(a)は、実施例5に係る多層配線基板100dの断面構成図である。図6(b)は、配線層40dの平面構成図である。図6(c)は、配線層40eの平面構成図である。

【図7】実施例6に係る大判基板200を説明するための図面である。図7(a)は、実施例6に係る大判基板200を示した平面構成図である。図7(b)は、大判基板200の枠部110にベタ状の配線パターンが形成された状態を示した図である。

【図8】大判基板200を、短冊状に切断した状態を示した図である。図8(a)は、実施例6に係る大判基板200を、短冊状に切断した短冊状基板150を示した平面構成図である。図8(b)は、枠部110がベタ状の配線パターンに形成された短冊状基板150aを示した図である。

50

【図9】従来の多層配線基板300の配線層240の平面構成図である。

【図10】従来の配線基板300の配線層240と絶縁層250の断面構成図である。図10(a)は、配線基板300製造時の配線層240及び絶縁層250の断面構成図である。図10(b)は、温度が下がった状態の配線層240及び絶縁層250の断面構成図である。

【符号の説明】

【0093】

|                |                   |    |

|----------------|-------------------|----|

| 10、10a～10e     | 電源プレーン、グランドプレーン   |    |

| 11、11a～11e     | 電源プレーン片、グランドプレーン片 |    |

| 20、20a～20e、120 | 切断ライン             | 10 |

| 30             | 中央部               |    |

| 31             | 開口部               |    |

| 40、40a～40e     | 配線層               |    |

| 50、51、52       | 絶縁層               |    |

| 55、56、57       | ビア                |    |

| 60、61          | 端子パッド             |    |

| 70、71          | ソルダレジスト           |    |

| 80             | プリソルダ             |    |

| 81             | 半田ボール             |    |

| 90             | 半導体素子             | 20 |

| 91             | パンプ               |    |

| 95             | アンダーフィル樹脂         |    |

| 100、100a～100e  | 多層配線基板            |    |

| 110            | 枠部                |    |

| 150            | 短冊状基板             |    |

| 200            | 大判基板              |    |

【図1】

実施例1に係る多層配線基板100の配線層40の平面構成図

【図2】

図1に係る配線層40及び絶縁層50をA-A'断面で切った断面構成図

(a)は多層配線基板100製造中の状態を示した断面図

(b)は反りが生じた状態の多層配線基板100の断面図

【図3】

実施例2に係る多層配線基板100aの配線層40aの平面構成図

【図4】

実施例3に係る多層配線基板100bの配線層40bの平面構成図

【図5】

実施例4に係る多層配線基板100cの配線層40cの平面構成図

【図6】

実施例5に係る多層配線基板100dの説明図

(a)は実施例5に係る多層配線基板100dの断面構成図、

(b)は配線層40dの平面構成図、(c)は配線層40eの平面構成図

【図7】

実施例6に係る大判基板200を説明するための図面

(a)は実施例6に係る大判基板200を示した平面構成図

(b)は大判基板200の枠部110にベタ状の配線パターンが

形成された状態を示した図

【図8】

大判基板200を、短冊状に切断した状態を示した図

(a)は実施例6に係る大判基板200を短冊状に切断した

短冊状基板150を示した平面構成図

(b)は枠部110がベタ状の配線パターンに形成された

短冊状基板150aを示した図

【図9】

【図10】

従来の配線基板300の配線層240と絶縁層250の断面構成図

(a)配線基板300製造時の配線層240及び絶縁層250の断面構成図

(b)温度が下がった状態の配線層240及び絶縁層250の断面構成図

---

フロントページの続き

(56)参考文献 特開2000-114676(JP,A)

特開2006-114623(JP,A)

特開2006-278808(JP,A)

特開2003-110203(JP,A)

特開2001-015638(JP,A)

特開2002-111145(JP,A)

特開2001-237505(JP,A)

(58)調査した分野(Int.Cl., DB名)

H05K 1/02

H01L 23/12

H05K 3/00

H05K 3/46