US 20150380583A1

# (19) United States (12) Patent Application Publication (10) Pub. No.: US 2015/0380583 A1

# Black et al.

# Dec. 31, 2015 (43) **Pub. Date:**

#### (54) NECKLACES OF SILICON NANOWIRES

- (71) Applicant: ADVANCED SILICON GROUP, INC., Lincoln,, MA (US)

- (72) Inventors: Marcie R. Black, Salem, NH (US); Jeff Miller, Salem, NH (US); Michael Jura, Salem, NH (US); Claire Kearns-McCoy, Boston, MA (US); Joanne Yim, Salem, NH (US); Brian P. Murphy, Salem, NH (US)

- (73) Assignee: ADVANCED SILICON GROUP, INC., Lincoln, MA (US)

- (21) Appl. No.: 14/764,863

- (22) PCT Filed: Jan. 29, 2014

- (86) PCT No.: PCT/US2014/013677 § 371 (c)(1), (2) Date: Jul. 30, 2015

#### **Related U.S. Application Data**

(60) Provisional application No. 61/758,474, filed on Jan. 30, 2013.

#### **Publication Classification**

| ) | Int. Cl.     |           |

|---|--------------|-----------|

| ĺ | H01L 31/0352 | (2006.01) |

|   | H01L 21/285  | (2006.01) |

|   | H01L 21/288  | (2006.01) |

|   | H01L 31/0224 | (2006.01) |

|   | H01L 29/06   | (2006.01) |

|   | H01L 31/028  | (2006.01) |

|   | H01L 29/16   | (2006.01) |

|   | H01L 31/18   | (2006.01) |

|   | H01L 21/3213 | (2006.01) |

|   | H01L 21/02   | (2006.01) |

| 5 |              | ```       |

(52) U.S. Cl.

(51

CPC .. H01L 31/035227 (2013.01); H01L 21/32134 (2013.01); H01L 21/2855 (2013.01); H01L 21/28568 (2013.01); H01L 21/288 (2013.01); H01L 21/02068 (2013.01); H01L 29/0669 (2013.01); H01L 31/028 (2013.01); H01L 29/16 (2013.01); H01L 31/1804 (2013.01); H01L 31/022408 (2013.01); B82Y 40/00 (2013.01)

ABSTRACT (57)

In an embodiment of the disclosure, a structure is provided which comprises a silicon substrate and a plurality of necklaces of silicon nanowires which are in direct physical contact with a surface of the silicon substrate, wherein the necklaces cover an area of the silicon substrate.

FIG. 2

## NECKLACES OF SILICON NANOWIRES

#### CROSS-REFERENCE TO RELATED APPLICATIONS

**[0001]** This application claims priority to U.S. Provisional Application Ser. No. 61/758474, filed Jan. 30, 2013, which is incorporated by reference in its entirety.

#### BACKGROUND OF THE INVENTION

[0002] Nanowire arrays are seeing increasing use in a variety of applications. See, e.g., U.S. Published Patent Application No. 2009/256134. An exemplary silicon nanowire array might consist of a collection of silicon nanowires, on the order of 100 nm in diameter, on the rough order of one micrometer in height, and of approximately cylindrical or frustoconical shape. The axes of the nanowires run approximately parallel to each other. Each is attached at an end to a silicon substrate. [0003] A silicon nanowire array on top of a silicon substrate, can alter the opto-electrical properties of the bulk silicon substrate. For example, a silicon nanowire array may reduce the reflection of the silicon substrate, reduce the reflection at off-angles of incidence, and increase the absorption of the silicon in ways similar to traditional pyramids or light trapping mechanisms used in solar cells.

**[0004]** A common method for growing silicon nanowires is metal-enhanced etching of a silicon-containing substrate. This is discussed, for example, in U.S. Patent Application No. 2009/256134 where further references are provided. In metal-enhanced etching, a metal is deposited on top of a silicon substrate and placed in a solution in which the etch is enhanced wherever the silicon touches metal. Since the metal coverage is not uniform, parts of the silicon are not etched leaving a graded index silicon, cliffs, or nanowires. The metal used can be, for example, gold, platinum, or silver.

**[0005]** Other known processes for obtaining silicon nanowires include reactive ion etching and VLS (vapor-liquid-solid). In VLS, nanowires are commonly grown on a substrate using a metal catalyst and silane.

**[0006]** There is a need to further improve the process by which arrays of silicon nanowires can be formed.

#### SUMMARY OF THE INVENTION

**[0007]** In an embodiment of the disclosure, a structure is provided which comprises a silicon substrate and a plurality of necklaces of silicon nanowires which are in direct physical contact with a surface of the silicon substrate, wherein the necklaces cover an area of the silicon substrate.

#### BRIEF DESCRIPTION OF THE FIGURES

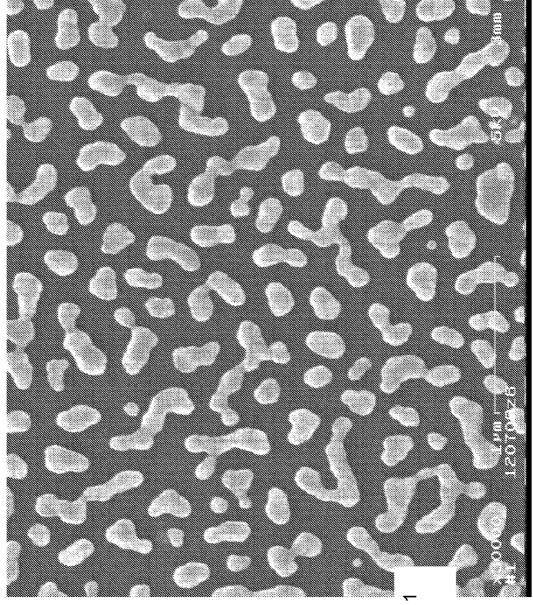

**[0008]** FIG. 1 depicts silver on a silicon substrate after annealing in the box furnace as described in Exemplary Process 1.

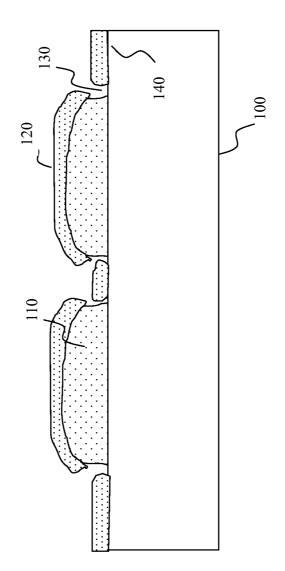

**[0009]** FIG. **2** schematically depicts a cross-sectional view of a wafer after the second deposition step.

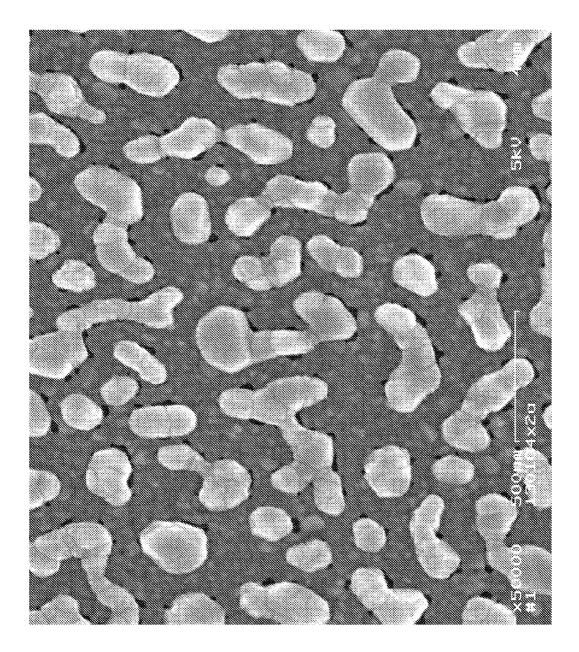

**[0010]** FIG. **3** is an SEM top view of a sample after the second layer of silver is deposited but before the metal-enhanced etch is preformed.

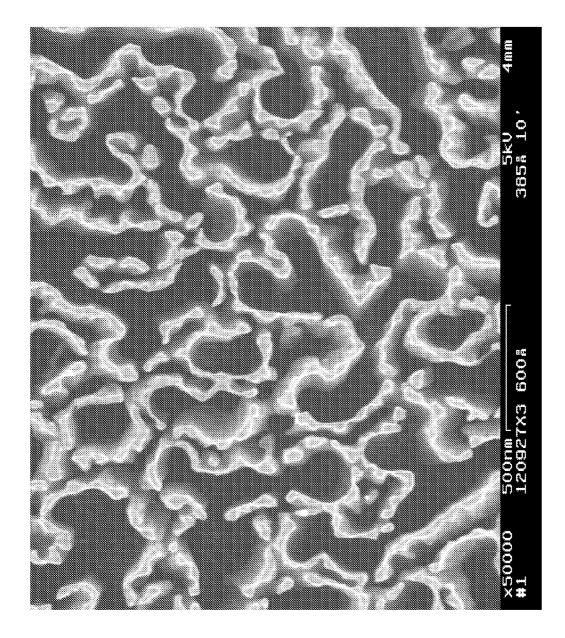

**[0011]** FIG. **4** is a top view SEM of a nanowire array formed by Exemplary Process 1.

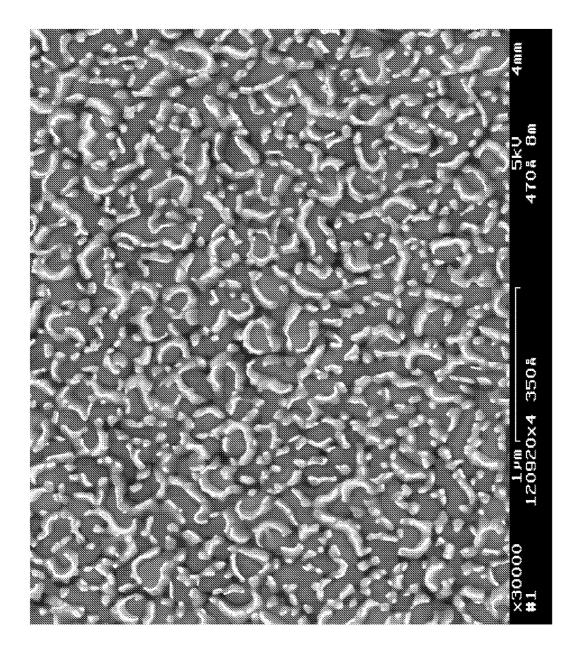

**[0012]** FIG. **5** is a top view SEM of a second nanowire array formed by Exemplary Process 1.

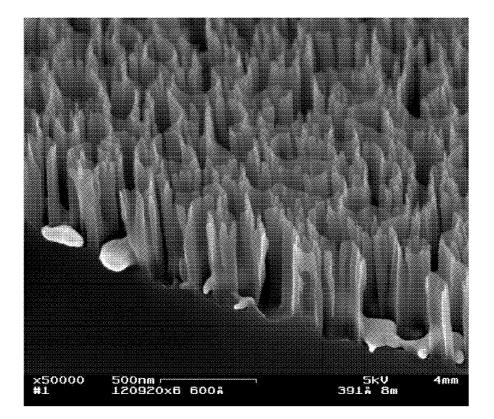

**[0013]** FIG. **6** is tilted top view SEM image of a nanowire array formed by Exemplary Process 1.

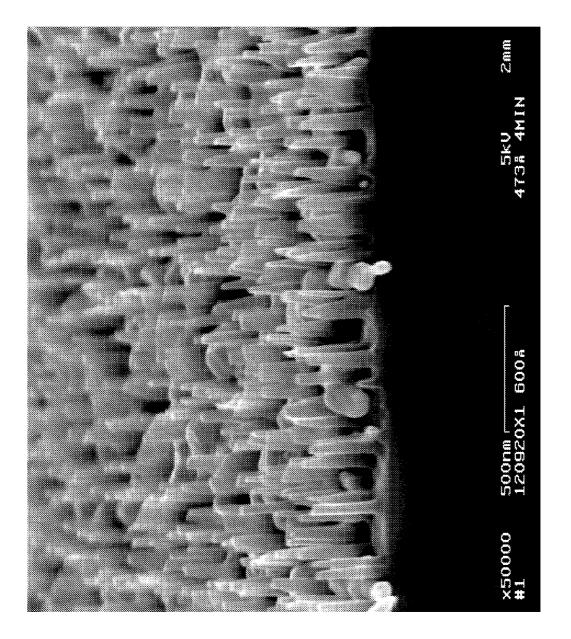

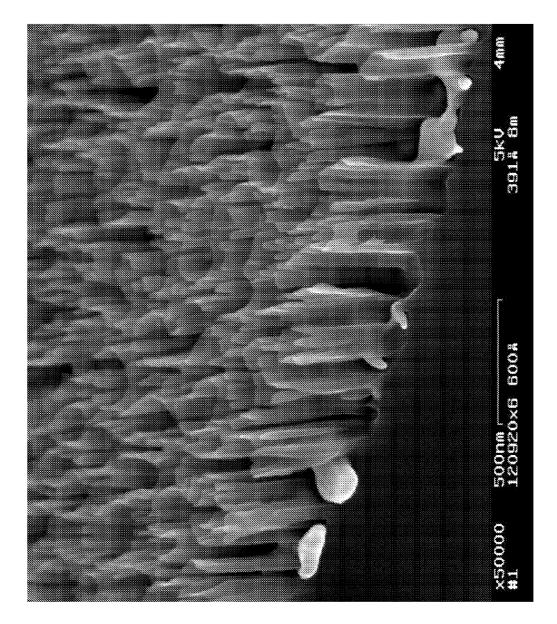

**[0014]** FIG. **7** is tilted top view SEM image of a nanowire array formed by a variant of Exemplary Process 1.

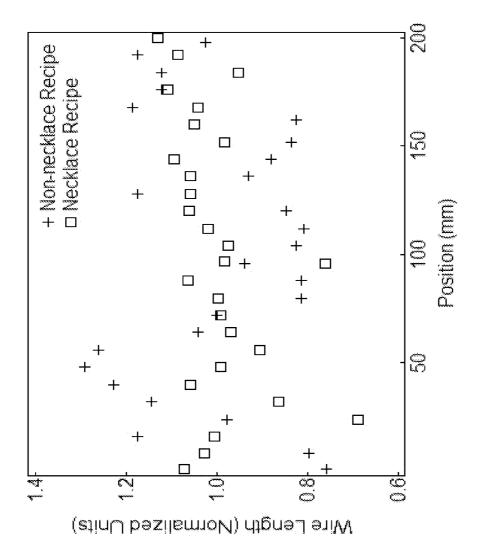

**[0015]** FIG. **8** depicts the distribution of nanowire lengths as a function of position for both a necklace-producing process and a similar non-necklace producing process.

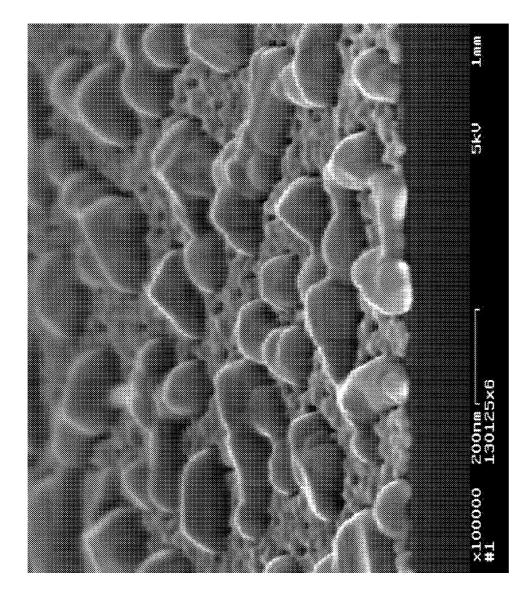

**[0016]** FIG. **9** is a tilted top view SEM image of a wafer after the second deposition step.

## DETAILED DESCRIPTION OF THE INVENTION

**[0017]** Before describing the present invention in detail, it is to be understood that this invention is not limited to specific solvents, materials, or device structures, as such may vary. It is also to be understood that the terminology used herein is for the purpose of describing particular embodiments only, and is not intended to be limiting.

**[0018]** Where a range of values is provided, it is intended that each intervening value between the upper and lower limit of that range and any other stated or intervening value in that stated range is encompassed within the disclosure. For example, if a range of 1  $\mu$ m to 8  $\mu$ m is stated, it is intended that 2  $\mu$ m, 3  $\mu$ m, 4  $\mu$ m, 5  $\mu$ m, 6  $\mu$ m, and 7  $\mu$ m are also disclosed, as well as the range of values greater than or equal to 1  $\mu$ m and the range of values less than or equal to 8  $\mu$ m.

**[0019]** In an embodiment of the disclosure, a structure is provided which comprises a silicon substrate and a plurality of necklaces of silicon nanowires which are in direct physical contact with a surface of the silicon substrate, wherein the necklaces cover an area of the silicon substrate.

**[0020]** The necklaces include sets of silicon nanowires which are arranged along a potentially curved line segment in the plane of the surface of the silicon substrate. Exemplary necklaces are depicted in FIGS. **4** and **5** in a top view and in FIG. **6** in a slanted view. The curved line segment along which the nanowires of a necklace are arranged may be visualized as the necklace's "footprint." The curved line segment may branch and may be or comprise a closed curve. The curved line segment along which the silicon nanowires are arranged may be circular in shape or it may be of more irregular shape, as may be seen in FIGS. **4** and **5**. The curved line segment may have limited curvature, such that its radius of curvature is at each point greater than a minimum. The minimum may be, for example, about 5 nm, about 10 nm, about 15 nm, about 20 nm, or about 25 nm.

**[0021]** The nanowires in a necklace may be joined to walls of silicon between them as shown in FIG. **9**. The walls may be lower than the nanowires. The nanowires may also be joined to each other. A necklace of joined nanowires may be a continuous wall with only small projections, or no projections, at the upper edge. FIG. **7** depicts necklaces of this type, which could also be described simply as walls of silicon. In the context of this application, the term height of a nanowire is used to denote the distance from tip to substrate along the nanowire's long axis rather than the height of the tip's projection above a wall of the type just discussed.

**[0022]** The nanowires, while very roughly round, may be thicker in the direction tangential to the curved line segment along which they are arranged. They may deviate from roundness in other ways. Such varying thickness may result, for example, in an average thickness in the direction perpendicular (normal) to the curved line segment along which they are arranged being no more than about 75%, no more than about 50%, or no more than about 35% of the average of the nanowires' diameters.

**[0023]** The nanowires may be tapered in the direction of their long axes. Desirable taper angles might be, for example, no more than about 0.5 degrees, about 1 degree, about 2 degrees, about 4 degrees, or about 10 degrees, or in a range between about 0.5 degrees and about 1 degree, about 2 degrees, about 4 degrees, or about 10 degrees.

**[0024]** The nanowires of the necklaces may be, for example, at least about 100 nm, 200 nm, 300 nm, 400 nm, 500 nm, 700 nm or 1  $\mu$ m tall. They may have thicknesses in the direction perpendicular to the curved line segment which are, for example, no more than about 5 nm, 10 nm, 15 nm, 25 nm, 50 nm, 75 nm, 100 nm, 200 nm, or 400 nm.

**[0025]** The curved line segments of the nanowire necklaces of the invention may be, for example, at least about 50 nm in length, at least about 100 nm in length, at least about 200 nm in length, at least about 400 nm in length, at least about 600 nm in length, at least about 1  $\mu$ m in length, at least about 2  $\mu$ m in length, or at least about 5  $\mu$ m in length.

**[0026]** The structure with necklaces of silicon nanowires may comprise a surface of black silicon comprising necklaces. The reflectivity of such a surface may be, for example, between about 1% and about 5%, or between about 3% and about 15%, prior to the application of an antireflection coating. In certain applications, as for example in photovoltaic applications, there may not be a need for an antireflection coating, with the nanostructuring being sufficient to achieve a desirably low reflectivity.

[0027] The structure with necklaces of silicon nanowires may, for example, exhibit a grading of the index of refraction. This may result, for example, from the fact that as one approaches the substrate, the percentage of silicon versus other material (e.g., air) in a plane parallel to the substrate increases. For example, when one is above the nanowires, the percentage of silicon in such a plane parallel to the substrate is zero. The percentage then rises above zero as one reaches the level of the nanowires. The percentage keeps increasing as one approaches the substrate. Then, when one reaches the substrate, the percentage of silicon jumps to its full bulk value (e.g., 100% for pure silicon). As a result of the increase of the percentage of silicon as one approaches the substrate in a direction perpendicular to the substrate, the index of refraction may also be expected to vary as one approaches the substrate in such a direction. The percentage of silicon just prior to the jump to full bulk value is a measure of the density of the nanowires. It may be, for example, less than about 5%, less than about 10%, less than about 25%, or less than about 60%; it may be, for example, greater than about 5%, greater than about 10%, greater than about 25%, or greater than about 60%. The percentage of silicon at the average nanowire height is an alternative measure of the nanowire density. It may be, for example, less than about 5%, less than about 10%, less than about 25%, or less than about 40%; it may be, for example, greater than about 5%, greater than about 10%, greater than about 25%, or greater than about 40%.

**[0028]** The structure with necklaces of silicon nanowires will generally be porous in the sense of having a relatively high ratio of surface area to volume in the portion lying above the bulk of the substrate.

**[0029]** The structure with necklaces of silicon nanowires may form part of a photovoltaic cell. As will be understood by those of skill in the art, a photovoltaic cell usually requires the formation of a p-n junction. Such a junction may be formed in the silicon nanowires or in the substrate below the silicon nanowires. The junction may be formed by a variety of doping technologies known to those of skill in the art. The photovoltaic application also requires contacts to be made to the front and back sides of the p-n junction. A variety of approaches may be taken to those contacts, as described for example in U.S. patent application Ser. No. 13/622,864 assigned to the present assignee.

**[0030]** The structure of the invention has other potential applications besides photovoltaics. It can in principle be employed wherever reasonably dense silicon nanowires are to be used, for example in the applications described in U.S. Published Patent Application No. 2009/256134.

**[0031]** In a further aspect of the present disclosure, a class of processes is provided. Nanoparticles comprising a first metal are deposited on the surface of a silicon-containing substrate. A layer of a second metal is deposited on top of the nanoparticles and silicon in such a way that the deposited metal is blocked from touching silicon or not present in an area near the nanoparticles which were deposited. The metallized substrate is contacted with an etchant aqueous solution comprising about 2 to about 49 weight percent HF and an oxidizing agent. The process causes etching to occur both in areas touched by the nanoparticles and in areas touched by the second metal.

**[0032]** The nanoparticles may be deposited preformed. Alternatively, they may be deposited by first putting down a layer of the first metal and then causing that layer to agglomerate. It is also possible in some cases to carry out a deposition process under conditions in which the first metal agglomerates as it is being deposited, for example using silver nitride solution. The first metal may, for example, form structures referred to as islands.

[0033] Where an agglomeration step is performed, it may be carried out by heating the substrate with the deposited first metal. An agglomeration step may also be referred to as annealing. The heating may take place in a chamber used for deposition, for example in the sputtering tool if the first metal was sputtered. The heating may alternatively take place in a separate chamber or oven. The heating may be carried out, for example, at a temperature of at least about  $200^{\circ}$  C., at least about  $250^{\circ}$  C., at least about  $300^{\circ}$  C., at least about  $350^{\circ}$  C., or at least about  $400^{\circ}$  C. The heating may be carried out, for example, for a time on the order of minutes, for example between about 1 and about 15 minutes, about 2 and 10 minutes, or about 3 and 7 minutes.

[0034] The second metal deposition may be carried out by suitable deposition techniques which may include physical and chemical forms of deposition. The second metal deposition forms a layer which lies above nanoparticles. FIG. 9 is a slanted view of the result of deposition above the nanoparticles. FIG. 2 is a schematic cross-section of what is believed to be present once the second layer is deposited. There is a substrate 100. Atop that substrate there are nanoparticles comprising the first metal, such as 110. Atop the nanoparticles there is a layer 120 of the second metal. There are areas like 130 in which the silicon appears to be exposed. Alternatively, even if the silicon is not entirely exposed in areas like 130, the covering of the second metal layer may be quite sparse, thin, and potentially non-continuous in such areas. The areas 130 are adjacent to areas like 140 in which the silicon is more fully covered by the second metal. It is believed that the formation of areas like 130 and 140 may result from Ostwald ripening which involves the deposited metal moving on the surface of the silicon shortly after or during deposition.

[0035] The deposition of nanoparticles patterns like those depicted in FIGS. 1, 2, 3 and 9 is helpful for the etching of nanowires. However, it may have other applications since it is a general technique suitable for producing a particular type of nanostructured metal deposition atop a surface. As may be seen in FIGS. 1, 3, and 9, the deposited nanostructures may be like a single ball or may have an appearance which may be reminiscent of a worm or of a rounded structure like a range of rounded hills or a set of balls of clay attached to each other. [0036] An appropriate etch is enhanced where a suitable (e.g., catalytic) metal such as silver touches the silicon, and is less in areas without such a metal. Generally speaking, such an etch leaves nanowires around the deposited, agglomerized metal particles in the areas where the second metal is thin or absent, etching away other areas. It is believed that the second metal may migrate further during the etch increasing the areas where it is thin or absent and where etch is consequently lessened or avoided. The thicknesses of material deposited in the first and second layers are commonly adjustable, e.g., manipulating deposition parameters. The thickness affects the size and spacing between the deposited nanostructures and the size and spacings of the resulting nanowires.

**[0037]** The metal-assisted etching step may be carried out in a variety of conditions and with the use of a range of oxidants, as described for example in U.S. Published Patent application No. 2009/256134 to the present assignee. Exemplary oxidants are  $H_2O_2$  and oxygen gas bubbled through the solution comprising HF. Milder or less mild oxidants may be desired according to the character of the etching which results. As described in U.S. Published Patent application No. 2009/256134, an additional etch may also be employed.

**[0038]** In the processes as described in this application, no use need be made of patterning by means of photolithography. While additional photolithographic steps are not excluded, it is believed that the process of agglomerization as described forms adequate nanosized patterns in many circumstances, which patterns are often suitable for metal-enhanced etching of useful nanostructures, providing adequate control for many applications without the need for the expense of photolithography.

[0039] In certain processes of the disclosure, an advantageous level of uniformity of the nanowires is achieved. The solar industry uses 156×156 mm<sup>2</sup> wafers, and thus uniformity across this area is desirable for solar cell manufacturing. Solution based processes and physical vapor deposition processes for the laying down of metal tend to encounter difficulty producing nanowires over this area. The solar industry uses 156×156 mm<sup>2</sup> wafers, and thus uniformity across this area is important for solar cell manufacturing. Unfortunately, neither the solution based processes nor the physical vapor deposition processes can uniformly produce nanowires over this area. Of these methods, sputtering gives the most uniform nanowire arrays, but manufacturing grade sputtering tools may vary by ±10% across a 6 inch area. Processes of the disclosure, with two metal deposition steps, are believed to be capable of compensating at least in part for this difficulty. FIG. 8 depicts the distribution of nanowire lengths as a function of position for both a necklace-producing process and a similar non-necklace producing process. The two processes are normalized to the same average nanowire length.

**[0040]** In what follows, exemplary processes of the disclosure are described. The following examples are put forth so as to provide those of ordinary skill in the art with a more complete disclosure and description of how to implement the invention, and are not intended to limit the scope of what the inventors regard as their invention. Efforts have been made to ensure accuracy with respect to numbers (e.g., amounts, temperature, etc.) but some errors and deviations should be accounted for.

#### **Exemplary Process 1**

**[0041]** Silicon material with a resistivity of 5 ohm-cm is selected having a surface with a (100) crystallographic orientation and p-type doping.

**[0042]** The first step is to do a saw damage removal process on the wafers. The saw damage removal comprises precleans and a KOH etch that removes the damage caused by forming the wafers. This is performed by first cleaning the wafers in a Piranha solution for 10 minutes. The Piranha step of this exemplary process employs 4 parts 96% sulfuric acid ( $H_2SO_4$ ) and 1 part 30% hydrogen peroxide ( $H_2O_2$ ) at elevated temperature. Prior to placing the wafer into the piranha solution, the latter is bubbled with  $N_2$  for 2 minutes. The bubbling is then continued and the wafer is submerged for 10 minutes. The solution is heated from the exothermic reaction. After the piranha etch, the wafer is cleaned 3 times with DI (deionized) water.

**[0043]** Next the wafers are dipped for 1 minute in 4 weight percent hydrofluoric acid (HF) solution to etch off the oxide formed during the Piranha clean. After the HF clean the wafers are removed and again rinsed three times and placed into a spin rinse dryer.

**[0044]** Next a polish etch is performed for 10 minutes in a solution of 1 part DI water, 1 part 30% potassium hydroxide (KOH) at about  $70^{\circ}$  C. The wafers are then rinsed three times in DI water. The wafers are then cleaned again with Piranha for 10 minutes and rinsed with water three times.

**[0045]** After the saw damage removal, the next step is to do a UV/Ozone clean in order to clean off any residue from the polish etch. The samples are pretreated with a 1 minute dip in an aqueous solution of about 4 weight percent HF. The HF dip removes the oxide formed during the Piranha etch. The wafers are rinsed three times and dried in a spin rinse dryer. The wafers are then placed in the UV/Ozone for 10 minutes at 400° C. with about 1 L/min of oxygen flowing through the chamber.

**[0046]** After the UV/Ozone clean, the sample is immediately placed into a sputtering chamber for the deposition of the first layer of silver. The sample is preferably placed in the sputtering chamber within 10 minutes of the UV/Ozone. The base pressure in the chamber is pumped down to  $7.0 \times 10^{-7}$  Torr and then 50 nm of silver (Ag) is sputter deposited on the front of the wafer at a rate of about 8 Å/s at a pressure of 5 mTorr. The samples are then removed from the chamber.

**[0047]** The next step is to heat the layer of metal so that it coalesces and agglomerates on the surface forming into balllike nanoparticle structures distributed more-or-less evenly on the surface of the wafer. The heating process can be done in situ in the sputtering tool or the sample can be removed from the sputtering tool and annealed in an oven or a furnace. For example, the samples may be removed from the sputtering tool and placed in a box furnace. The samples are then heated on a quartz plate at 300° C. for 5 minutes. FIG. **1** shows a picture of the silver on the silicon surface after this heating step.

**[0048]** When this heating step is performed outside of the sputtering tool, the wafers are then returned to the sputtering chamber. A second silver film is then sputtered onto the front

surface. 36 nm of silver are deposited at a rate of about 12 Å/s and a pressure of 5 mTorr. This deposition results in coating of both the silver particles and the bare silicon left after the silver has been agglomerated. A schematic of a cross section of the particles is shown in FIG. **2**. The silver is very thin in an area immediately surrounding the silver particles from the first deposition, leaving a ring of sparse or bare silicon around each of the silver particles shown, for example, in FIG. **1**.

**[0049]** The wafers are then removed from the sputtering chamber and etched to form nanowires. The nanowire formation occurs in an oxygen/HF bath. After the sample is removed from the sputtering chamber, it is placed in a dilute hydrofluoric acid (HF) bath. The bath contains 10 parts volume water to 1 part volume HF. The sample is etched in the HF bath for 10 minutes during which time oxygen is bubbled vigorously through the HF using a perforated teflon tube. After that, the sample is rinsed three times in DI.

**[0050]** The silver is then removed and the sample is cleaned in a series of wet baths. The first bath is a piranha clean which consists of 4 ml of sulfuric acid ( $H_2SO_4$ ) to 1 ml of 30 wt % hydrogen peroxide ( $H_2O_2$ ) at an elevated temperature around 70° C. Prior to placing the wafer into the piranha, the bath is bubbled for 2 minutes. The bubbling is then continued and the wafer is submerged for 2 minutes. After the piranha etch, the wafer is cleaned 3 times with DI water.

**[0051]** The sample is then placed in dilute HF for 30 seconds. This HF solution has a volume ratio of 24:1 of water to 49% HF and is at room temperature. The wafer is then rinsed three times with DI water and dried in the spin rinse dryer.

**[0052]** The following references may be relevant to this application: (1) Sami Franssila, *Introduction to Microfabrication* (2d ed. John Wiley & Sons 2010). (2) U.S. Published Patent Application No. 2009/256134. (3) U.S. patent application Ser. No. 13/622,864, published as 2013/99345. (4) H. Galinski et al., "Agglomeration of Pt thin films on dielectric substrates," *Phys. Rev. B*, 82, 235415 (2010). (5) Feng-Ming Liu & Mino Green, "Efficient SERS substrates made by electroless silver deposition into patterned silicon structures," *J. Mater. Chem.*, 14, 1526-1532 (2004). (6) D. W. Pashley et al., "The growth and structure of gold and silver deposits formed by evaporation inside an electron microscope," *Phil. Mag.*, 10:103, 127-158 (1964).

**[0053]** All patents, patent applications, and publications mentioned in this application are hereby incorporated by reference in their entireties. However, where a patent, patent application, or publication containing express definitions is incorporated by reference, those express definitions should be understood to apply to the incorporated patent, patent application, or publication in which they are found, and not to the remainder of the text of this application, in particular the claims of this application.

**1**. A structure comprising: a silicon substrate and a plurality of necklaces of silicon nanowires which are in direct physical contact with a surface of the silicon substrate, wherein the necklaces cover an area of the silicon substrate.

2. The structure of claim 1, wherein the necklaces of nanowires have an average height of at least about 350 nm.

**3**. The structure of claim **1**, wherein the silicon is monocrystalline.

**4**. The structure of claim **3**, wherein a surface with which the necklaces of nanowires are in direct physical contact has orientation (100).

5. The structure of claim 1, wherein the silicon is multic-rystalline.

6. The structure of claim 1, wherein the necklaces of nanowires comprise on average at least about 10 nanowires.

7. The structure of claim 1, wherein the necklaces of nanowires comprise on average no more than about 100 nanowires.

8. The structure of claim 1, further comprising a p-n junction in the silicon substrate, a conducting electrical contact to necklaces of nanowires, and a conducting electrical contract to a surface other than the surface with which necklaces of nanowires are in direct physical contact, such that the structure exhibits photovoltaic behavior when illuminated on a side with which circles of nanowires are in direct physical contact.

**9**. The structure of claim **1**, wherein the standard deviation of the heights of the nanowires in all necklaces collectively is no more than about 30%.

10. The structure of claim 1, wherein the necklaces of nanowires are approximately circular.

11. The structure of claim 1, wherein the necklaces of nanowires follow approximately the shape of a curved line segment having a radius of curvature no greater than a predetermined value at all of its points.

**12**. The structure of claim **11**, wherein the length of the curved line segment is no more than about **5** times the predetermined value.

**13**. The structure of claim **11**, wherein the average distance between two adjacent necklaces of nanowires is no more than about 5 times the predetermined value.

14. The structure of claim 1, further comprising silicon walls joining some or all pairs of adjacent nanowires which form part of at least one necklace.

**15**. The structure of claim **3**, wherein the silicon walls joining nanowires rise approximately to the height of the nanowires.

**16**. The structure of claim **1**, wherein the nanowires are of a density sufficient to result in black silicon.

17. The structure of claim 1, wherein the nanowires are tapered.

**18**. The structure of claim **1**, wherein as a result of the nanowires the index of refraction of the structure varies in a direction perpendicular to the nanowires.

**19**. The structure of claim **1**, wherein the nanowires are on average at an angle to a surface of the silicon substrate to which they are attached.

**20**. The structure of claim **19**, wherein the angle lies between about 10 degrees and about 30 degrees relative to a direction perpendicular to the surface.

**21**. A process for etching a silicon-containing substrate to form nanowires, comprising the steps of:

- (a) depositing nanoparticles comprising a first metal on the surface of a silicon-containing substrate,

- (b) depositing a layer of a second metal on top of the nanoparticles and silicon in such a way that areas of bare or sparsely covered silicon are produced in the vicinity of the nanoparticles, and

- (c) contacting the metallized substrate with an etchant aqueous solution comprising about 2 to about 49 weight percent HF and an oxidizing agent, wherein the process causes etching to occur in areas touched by the nanoparticles and in areas touched by the second metal.

22. The process of claim 21, wherein the first metal comprises silver.

23. The process of claim 21, wherein the second metal comprises silver.

**24**. The process of claim **21**, wherein the first and second metal are substantially identical.

**25**. The process of claim **21**, wherein step (a) of depositing nanoparticles comprises first depositing the first metal in an approximately uniform manner and then causing the metal so deposited to agglomerize.

**26**. The process of claim **25**, wherein agglomerizing is performed at least partly in a sputtering tool.

27. The process of claim 25, wherein agglomerizing results in balls comprising the first metal.

**28**. The process of claim **25**, wherein the step of agglomerizing comprises heating a layer of deposited first metal.

**29**. The process of claim **28**, wherein the heating of the first layer involves subjecting the substrate to temperatures in a range between about  $200^{\circ}$  C. and about  $400^{\circ}$  C.

**30**. The process of claim **29**, wherein the heating of the first layer involves subjecting the substrate to temperatures in the range for a time between about 2 and about 10 minutes.

**31**. The process of claim 25, wherein agglomerizing comprises placing the substrate with a deposited first layer of metal in a solution.

**32**. The process of claim **21**, wherein step (a) of depositing nanoparticles comprises sputtering.

**33**. The process of claim **21**, wherein prior to step (a) a UV-ozone clean process is performed.

**34.** The process of claim **30**, wherein step (a) is initiated no more than about 10 minutes after the UV-ozone clean process.

**35**. The process of claim **21**, wherein the oxidizing agent of step (c) comprises  $H_2O_2$  or oxygen bubbled through a perforated tube.

**36**. The process of claim **21**, wherein step (a) of depositing nanoparticles comprises a solution based process.

**37**. The process of claim **21**, wherein prior to step (a) a preclean of the surface is performed which alters the surface in such a way so the deposition of metal is altered.

**38**. A process for creating a nanosized pattern of a metal on a surface, comprising the steps of depositing the metal, annealing the deposited metal so as to produce a pattern comprising round deposits and elongated deposits with a worm-like shape covering the surface, and employing the nanosized pattern for the formation of other nanostructures by means of additional processing.

**39**. A structure comprising: a silicon substrate and a plurality of nanosized potentially curved silicon walls whose bottoms are in direct physical contact with a surface of the silicon substrate, wherein the walls cover an area of the silicon substrate.

**40**. The structure of claim **39**, wherein the walls have an average aspect ratio of at least about 10:1, at least about 20:1, or at least about 40:1.

**41**. The structure of claim **39**, wherein the silicon walls have silicon protrusions along their tops.

\* \* \* \* \*