(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5240749号

(P5240749)

(45) 発行日 平成25年7月17日(2013.7.17)

(24) 登録日 平成25年4月12日(2013.4.12)

(51) Int.Cl.

G02F 1/1335 (2006.01)

G02F 1/1368 (2006.01)

F 1

G02F 1/1335 520

G02F 1/1368

請求項の数 4 (全 16 頁)

(21) 出願番号 特願2007-103001 (P2007-103001)

(22) 出願日 平成19年4月10日 (2007.4.10)

(65) 公開番号 特開2008-122904 (P2008-122904A)

(43) 公開日 平成20年5月29日 (2008.5.29)

審査請求日 平成22年4月9日 (2010.4.9)

(31) 優先権主張番号 10-2006-0112859

(32) 優先日 平成18年11月15日 (2006.11.15)

(33) 優先権主張国 韓国 (KR)

(73) 特許権者 512187343

三星ディスプレイ株式会社

Samsung Display Co., Ltd.

大韓民国京畿道龍仁市器興区三星二路95

95, Samsung 2 Ro, Gih

eung-Gu, Yongin-City

, Gyeonggi-Do, Korea

(74) 代理人 110000671

八田国際特許業務法人

(72) 発明者 金 ▲てつ▼ 鑄

大韓民国京畿道龍仁市器興区農書洞 三星

電子株式会社器興プラント LCD ビジネス

MD プロセス開発チーム

最終頁に続く

(54) 【発明の名称】薄膜トランジスター基板、その製造方法及びこれを備える液晶表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

基板上を一方向に伸びて形成された複数のゲート線と、

前記ゲート線と交差して形成された複数のデータ線と、

前記データ線の間に位置する画素領域に形成された複数の画素電極と、を備え、

各画素領域は、

前記ゲート線を含む領域に形成された反射領域と、

前記反射領域を挟んで両側に形成された透過領域と、

前記基板上の任意の領域に形成された第1の電極パターンと、

前記第1の電極パターンと同一層で形成されて連なることで接続され、前記ゲート線の

下を通って前記データ線に接続された活性層と、を備え、

前記活性層は、

前記データ線に接続されたソース領域と、

前記画素電極に接続されたドレイン領域と、

前記ソース領域及びドレイン領域の間であって、上部に前記ゲート線を有するチャンネル領域と、

前記ゲート線と所定の間隔を隔てて形成された前記ストレジキャパシタの上部電極をなす第2の電極パターンと、を備え、

前記第2の電極パターンは、前記活性層と接続される部分を除き、前記第1の電極パターンと重なり合うように形成され、

10

20

前記画素電極は、それぞれ角部が丸く面取りされた矩形形状を有し、前記反射領域および前記透過領域にそれぞれ形成されるとともに、接合部により電気的に接続され、

前記ゲート線は前記反射領域と前記透過領域との境界のいずれか一方に沿って伸び、前記反射領域と重畳するように設けられていることを特徴とする薄膜トランジスター基板。

**【請求項 2】**

前記透過領域の前記画素電極には切欠部をさらに備えることを特徴とする請求項 1 に記載の薄膜トランジスター基板。

**【請求項 3】**

前記反射領域の前記画素電極の上部または下部に反射膜が形成されていることを特徴とする請求項 1 または 2 に記載の薄膜トランジスター基板。 10

**【請求項 4】**

基板上を一方向に伸びて形成された複数のゲート線と、

前記ゲート線と交差して形成された複数のデータ線と、

前記データ線の間に位置する画素領域に形成された複数の画素電極と、を備え、

各画素領域は、

前記ゲート線を含む領域に形成された反射領域と、

前記反射領域を挟んで両側に形成された透過領域と、

前記基板上の任意の領域に形成された第1の電極パターンと、

前記第1の電極パターンと同一層で形成されて連なることで接続され、前記ゲート線の下を通って前記データ線に接続された活性層と、を備え、 20

前記活性層は、

前記データ線に接続されたソース領域と、

前記画素電極に接続されたドレイン領域と、

前記ソース領域及びドレイン領域の間であって、上部に前記ゲート線を有するチャンネル領域と、

前記ゲート線と所定の間隔を隔てて形成された前記ストレジキャパシタの上部電極をなす第2の電極パターンと、を備え、

前記第2の電極パターンは、前記活性層と接続される部分を除き、前記第1の電極パターンと重なり合うように形成され、

前記画素電極は、それぞれ角部が丸く面取りされた矩形形状を有し、前記反射領域および前記透過領域にそれぞれ形成されるとともに、接合部により電気的に接続され、 30

前記ゲート線は前記反射領域と前記透過領域との境界のいずれか一方に沿って伸び、前記反射領域と重畳するように設けられている薄膜トランジスター基板と、

前記画素領域以外の領域に対応する第2の基板上の領域に形成されたブラックマトリックスと、前記画素領域に対応する前記第2の基板上の領域に形成されたカラーフィルターと、前記第2の基板上に形成された共通電極と、を備えるカラーフィルター基板と、

前記薄膜トランジスター基板と前記カラーフィルター基板との間に形成された液晶層と、

、

を備えることを特徴とする液晶表示装置。

**【発明の詳細な説明】**

40

**【技術分野】**

**【0001】**

本発明は液晶表示装置に係り、より詳しくは、画素領域の中央に反射領域を形成し、これを中心として対称をなすように透過領域を形成することにより透過領域の開口損失を低減することのできる半透過型の液晶表示装置に関する。

**【背景技術】**

**【0002】**

液晶表示装置 (Liquid Crystal Display; LCD) は、画素電極が形成された薄膜トランジスター基板と、共通電極が形成されたカラーフィルター基板と、これらの間に設けられた液晶層により構成され、画素電極及び共通電極に電圧を印加

50

して液晶層の液晶分子を再配列することで液晶層に透過する光の量を調節することにより画像を表示する。

#### 【0003】

この種の液晶表示装置は、自発光による画像の表示を行うことができず、外部から光が入射されて画像を形成するが、光源によって透過型の液晶表示装置、反射型の液晶表示装置及び半透過型の液晶表示装置に大別される。

#### 【0004】

透過型の液晶表示装置は、液晶パネルの背面に位置するバックライトを用いて画像を表示するのに対し、反射型の液晶表示装置は、外部光を用いて画像を表示する。また、半透過型の液晶表示装置は、透過型の液晶表示装置と反射型の液晶表示装置の構造を併せ持つものであり、屋内や外部光源が存在しない暗所においては表示素子自体のバックライトユニットを用いて画像を表示する透過モードにて作動し、屋外の外部光の照度が高い環境下においては、外部光を反射させて画像を表示する反射モードにて作動する。中型もしくは小型の液晶表示装置においては、透過型と反射型の長所を併せ持つ半透過型の液晶表示装置を採用しているが、半透過型の液晶表示装置は、画素領域の一部は透過領域をなすと共に、残りの領域は反射領域をなすものである。

10

#### 【0005】

一方、液晶表示装置のうち、電界が印加されていない状態で、液晶分子の長軸を薄膜トランジスター基板及びカラーフィルター基板に対して垂直に配列した垂直配向モードの液晶表示装置は、コントラスト比が大きくて広視野角の実現が容易であることから、注目を浴びている。垂直配向モードの液晶表示装置において広視野角を実現するための手段としては、電極に切欠パターンを形成する方法と、電極に突起を形成する方法などがある。これらのことにより広視野角を確保している。これらのうち、電極に切欠パターンを形成するパターンド垂直配向 (patterned vertical alignment: 以下、「PVA」と称する。) モードは、IPS (In Plane Switching) モードに代わりうる広視野角技術として認識されている。

20

#### 【0006】

上記の半透過型とPVAモードを組み合わせた半透過PVA液晶表示装置は、例えば、モバイルなどの中型小型製品に採用される場合、ゲート線とデータ線が交差する領域の画素領域の一部に透過領域が画定され、残りの画素領域に反射領域が画定されるが、透過領域には切欠パターンが形成される。このような中型小型表示装置に用いられる半透過PVA液晶表示装置は、薄膜トランジスターが形成されるゲート線に近い画素領域に反射領域が限定され、残りの画素領域が透過領域として画定される。ところが、透過領域が反射領域よりも大きく画定される場合、中小型の半透過PVA液晶表示装置の特性から、単一のドメインにより透過領域を限定することができず、透過領域を分離することになる。透過領域を分離してPVAモードにて動作させるためには、分離されたドメイン間を離隔する必要がある。このため、ドメイン間の離隔距離に見合う分だけ開口率が失われるという問題が発生する。また、互いに離隔されているドメインはブリッジにより接続させなければならないが、このようにしてブリッジされた領域の液晶はランダムに配列されるため、画像を表示することができなくなる。結果として、ドメインがブリッジされた領域に見合う分だけ開口率が失われるという問題が発生する。

30

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0007】

本発明の目的は、開口率を高めることのできる薄膜トランジスター基板、その製造方法及びこれを備える液晶表示装置を提供するところにある。

#### 【0008】

本発明の他の目的は、画素領域の中央部に反射領域を画定し、反射領域を中心として対称をなすように透過領域を画定することにより、透過領域間のブリッジを除去し、開口率

40

50

を高めることのできる薄膜トランジスター基板、その製造方法及びこれを備える液晶表示装置を提供するところにある。

【0009】

本発明のさらに他の目的は、画素領域の中央部に画定された反射領域にゲート線及びストレジキャパシタを配置することにより開口率を高めることのできる薄膜トランジスター基板、その製造方法及びこれを備える液晶表示装置を提供するところにある。

【課題を解決するための手段】

【0010】

本発明の一態様に係る薄膜トランジスター基板は、基板上を一方向に伸びて形成された複数のゲート線と、前記ゲート線と交差して形成された複数のデータ線と、前記データ線の間に位置する画素領域に形成された複数の画素電極と、を備え、各画素領域は、前記ゲート線を含む領域に形成された反射領域と、前記反射領域を挟んで両側に形成された透過領域と、を備える。10

【0011】

また、前記基板上の任意の領域に形成された第1の電極パターンと、前記第1の電極パターンに接続され、前記ゲート線の下を通って前記データ線に接続された活性層と、をさらに備え得る。

【0012】

前記活性層は、前記データ線に接続されたソース領域と、前記画素電極に接続されたドレイン領域と、前記ソース領域及びドレイン領域の間であって、上部に前記ゲート線を有するチャンネル領域と、を備え得る。20

【0013】

前記ゲート線と所定の間隔を隔てて形成された前記ストレジキャパシタの上部電極をなす第2の電極パターンをさらに備え得る。

【0014】

前記第2の電極パターンは、前記活性層と接続される部分を除き、前記第1の電極パターンと重なり合うように形成され得る。

【0015】

前記画素電極は、それぞれ角部が丸く面取りされた矩形形状を有し、前記反射領域および前記透過領域にそれぞれ形成されるとともに、接合部により電気的に接続され得る。30

【0016】

前記透過領域の前記画素電極には切欠部をさらに備え得る。

【0017】

前記反射領域の前記画素電極の上部または下部に反射膜が形成され得る。

【0018】

また、本発明の一態様に係る薄膜トランジスター基板の製造方法は、基板の上部に半導体層を形成した後、パターニングにより活性層および第1の電極パターンを形成する段階と、前記基板の上部全体にゲート絶縁膜及び第1の導電層を形成した後、前記第1の導電層をパターニングしてゲート線および第2の電極パターンを形成する段階と、前記基板の上部全体に第1の保護膜を形成した後、パターニングにより前記活性層の一部を露出させる第1のコンタクトホールを形成する段階と、前記基板の上部全体に第2の導電層を形成した後、パターニングにより、前記第1のコンタクトホールを通して前記活性層の一部に接続されるデータ線を形成する段階と、前記基板の上部全体に第2の保護膜を形成した後、パターニングにより前記活性層の一部を露出させる第2のコンタクトホールを形成する段階と、前記基板の上部全体に第3の導電層を形成した後、パターニングにより前記第2のコンタクトホールを介して前記活性層領域の他の一部に接続される画素電極を形成する段階と、前記画素電極の上部の所定の領域に反射膜を形成する段階と、を含む。40

【0019】

さらに、前記第2の保護膜を湾曲させる段階をさらに含み得る。

【0020】

10

20

30

40

50

そして、前記画素電極を形成する段階は、前記画素電極に切欠部を形成することを含み得る。

#### 【0021】

また、本発明の一態様に係る液晶表示装置は、第1の基板上の一方向に伸びて形成された複数のゲート線と、前記ゲート線と交差する方向に伸びて形成された複数のデータ線と、前記データ線の間に画定される画素領域に形成された画素電極と、を備え、前記画素領域は、前記ゲート線を含む領域に設けられた反射領域と、前記反射領域を挟み、前記反射領域を中心として対称となる位置に形成された透過領域と、を備える薄膜トランジスター基板と、前記画素領域の以外の領域に対応する第2の基板上の領域に形成されたブラックマトリックスと、前記画素領域に対応する前記第2の基板上の領域に形成されたカラーフィルターと、前記第2の基板上に形成された共通電極と、を備えるカラーフィルター基板と、前記薄膜トランジスター基板と前記カラーフィルター基板との間に形成された液晶層と、を備える。10

#### 【発明の効果】

#### 【0022】

本発明によれば、画素領域を1つの反射領域と反射領域により画定された2つの透過領域により構成し、反射領域をゲート線及びストレジキャパシタが設けられた領域に形成する。

#### 【0023】

これにより、2つの透過領域が隣接していた従来の薄膜トランジスター基板と比較すると、2つの透過領域が隣接していないため、2つの透過領域上に形成される画素電極を所定の間隔をもって離隔しなくてもよいので、離隔距離に相当する分だけ開口率を高めることができる。20

#### 【0024】

また、ゲート線及びストレジキャパシタが形成された領域に反射領域を限定することにより反射領域の面積を大きくすることができ、かつ、画素領域の面積を大きくすることができます。

#### 【発明を実施するための最良の形態】

#### 【0025】

以下、図面に基づき、本発明の好適な実施形態について詳細に説明する。しかし、本発明は以下述べる実施形態に限定されるものではなく、それと異なる形態においても実施可能であり、以下述べる実施形態は、単に本発明の開示を十分なものとし、かつ、この技術分野における通常の知識を有する者に発明の範囲を十分に知らせるために提供されるものである。30

#### 【0026】

図面中、種々の層及び各領域を明確に示すために膜厚を拡大して示した。また、図面中の同じ符号は同じ構成要素を示すものである。なお、層、膜、領域、板などの部分が他の部分の「上部に」または「その上」にあると表現される場合には、各部が他の部分の「直ぐ上部」または「真上」にある場合のみならず、各部と他の部分との間にさらに他の部分が介在される場合も含まれるものとする。40

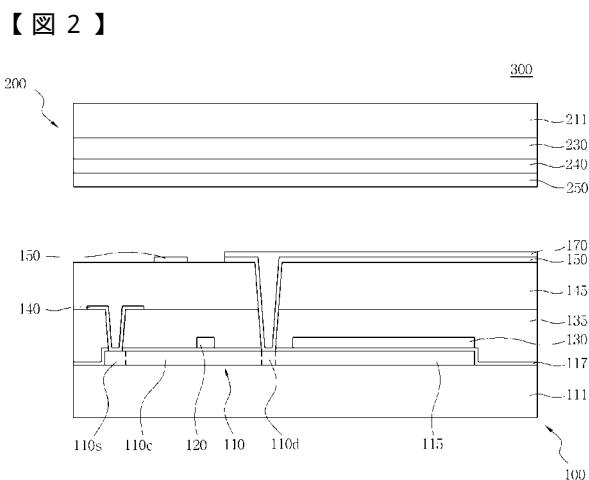

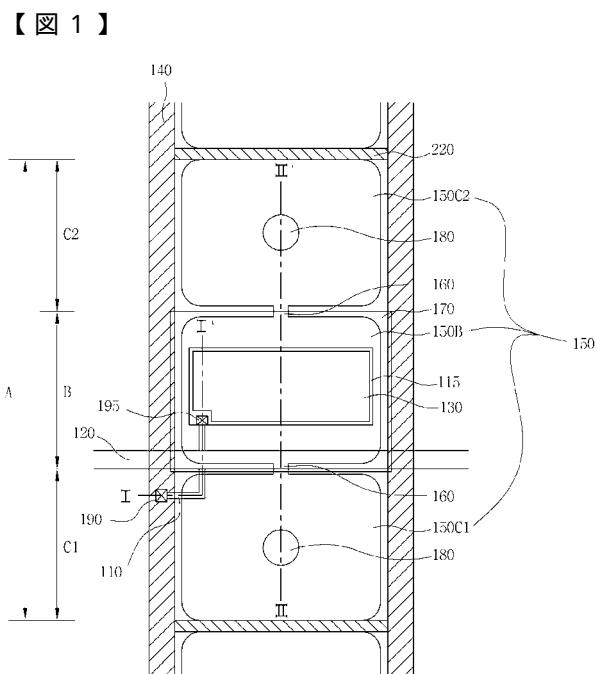

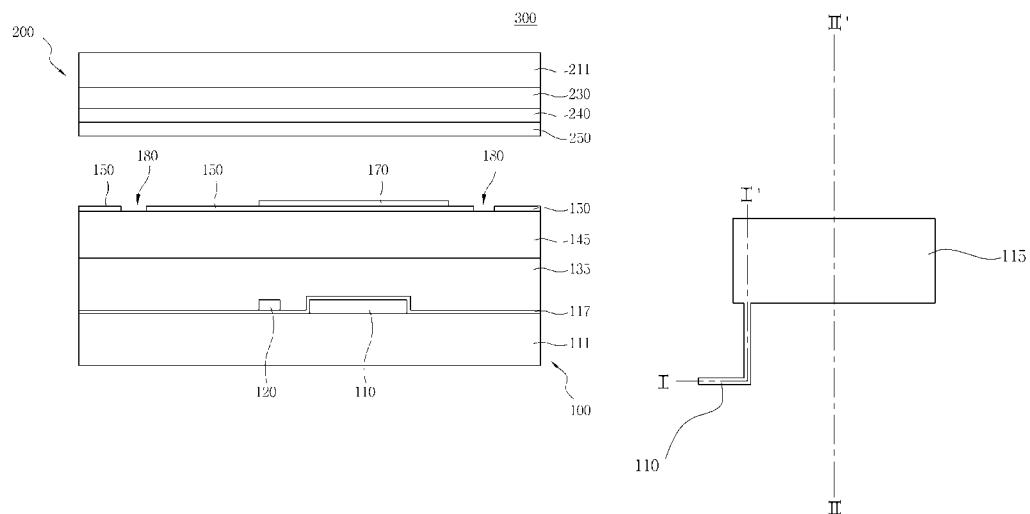

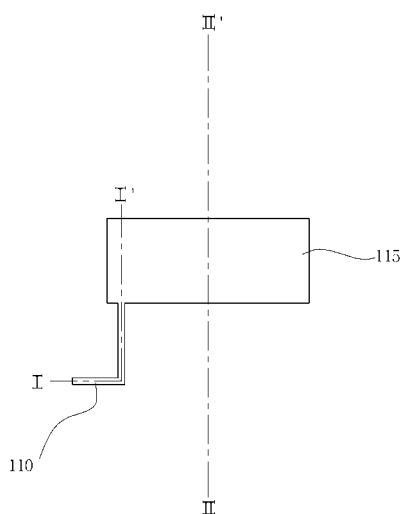

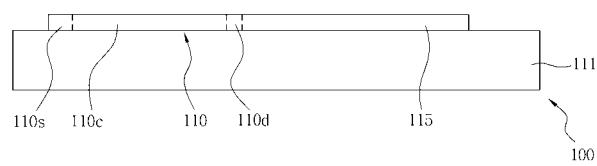

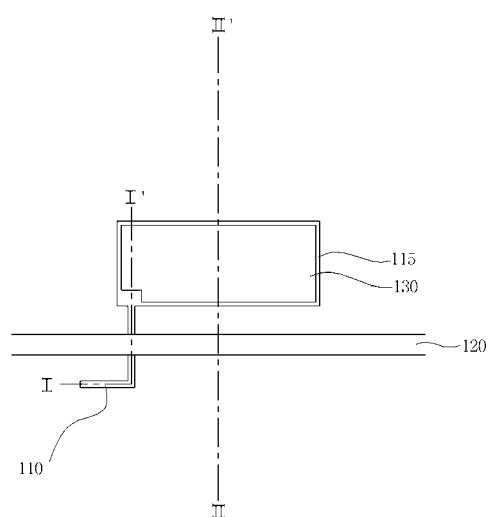

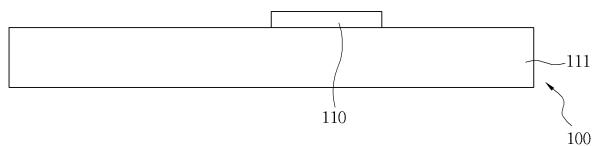

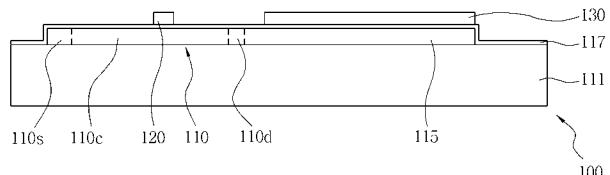

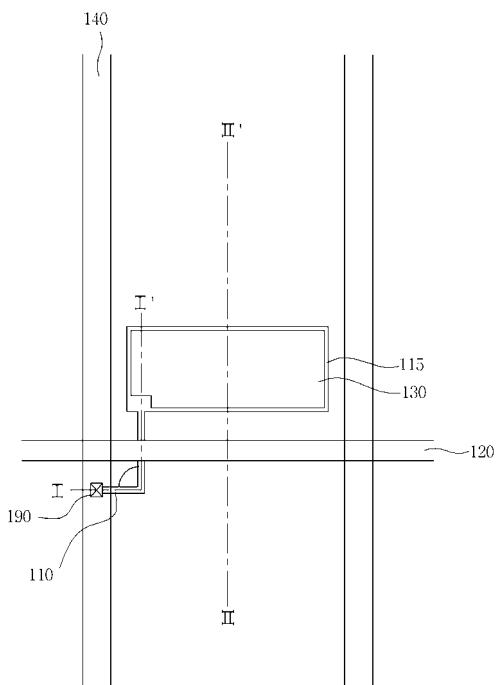

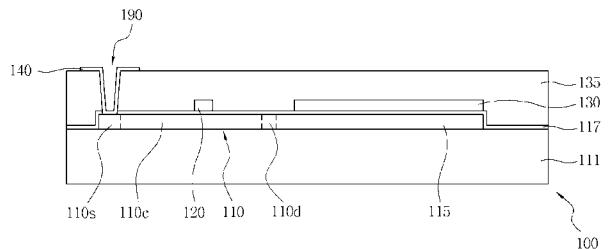

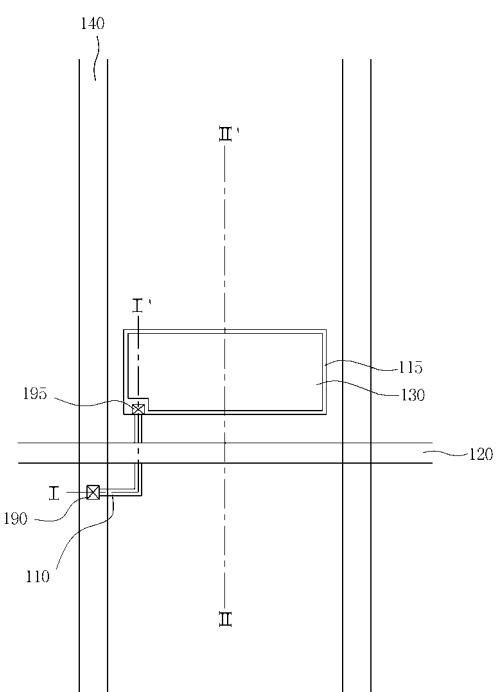

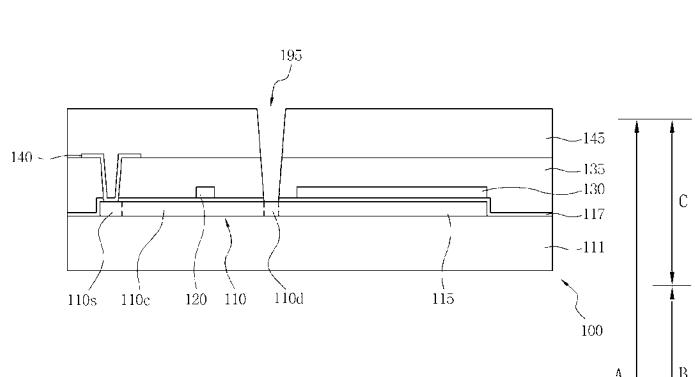

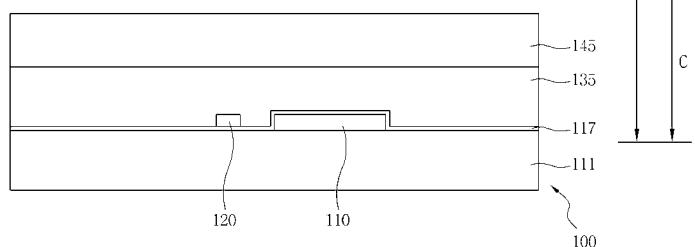

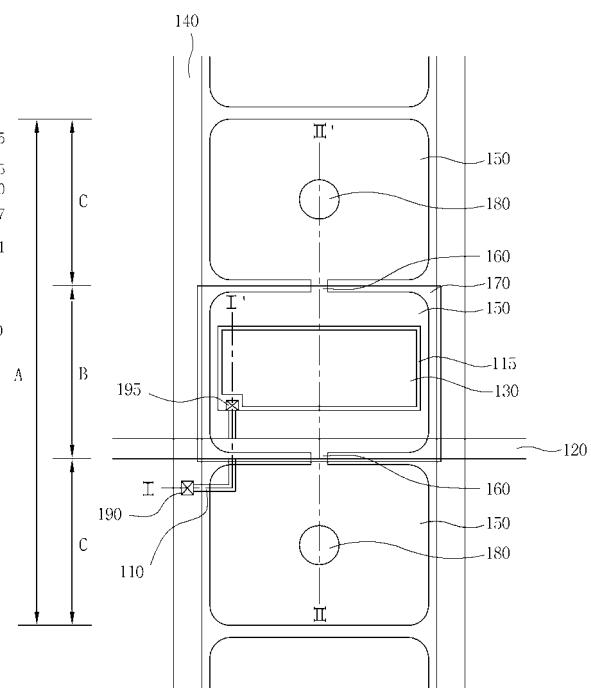

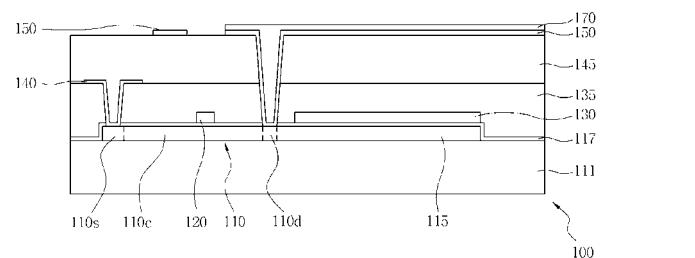

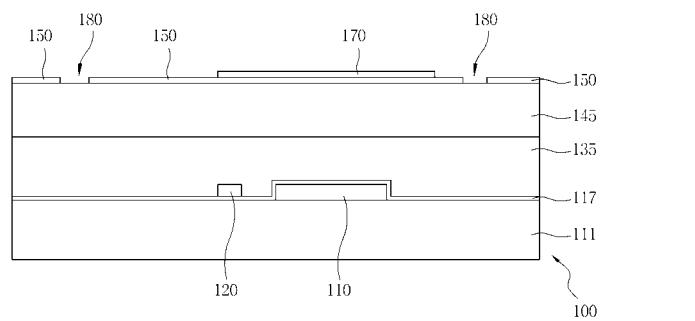

#### 【0027】

図1は、本発明による半透過PVAモードの液晶表示装置の一画素領域を示す平面図であり、図2は、図1のI-I'線における断面図であり、図3は、図1のII-II'線における断面図である。

#### 【0028】

液晶表示パネル300は、互いに対向する薄膜トランジスター基板100およびカラーフィルター基板200と、これらの間に位置する液晶層(図示せず)を備えてなる。

#### 【0029】

薄膜トランジスター基板100は、透過性絶縁基板である第1の絶縁基板111の上部に形成された活性層110と、活性層110の一部に連なって形成される第1の電極パタ

10

20

30

40

50

ーン 115 と、一方に向かって伸びる複数のゲート線 120 と、ゲート線 120 と平行して形成され、かつ、第 1 の電極パターン 115 と重なり合う第 2 の電極パターン 130 と、ゲート線 120 と直交する方向に伸びる複数のデータ線 140 と、データ線 140 の間に位置する画素領域 A に形成された画素電極 150 を備えてなる。ここで、画素領域 A は 3 領域、すなわち、画素領域 A の中央部の反射領域 B と、反射領域 B の両側の透過領域 C1、C2 により構成されている。すなわち、画素領域 A の中央部に、ゲート線 120 及び第 2 の電極パターン 130 が形成された反射領域 B が画定され、反射領域 B を除く残りの領域が画素領域 A として画定される。反射領域 B を中心として透過領域 C は対称をなしている。また、反射領域 B に形成された画素電極 150 の上部または下部には、好ましくは、画素電極 150 よりも大面積の反射膜 170 をさらに備え、透過領域 C の画素電極 150 の好ましくは中央部には、円形の切欠部 180 をさらに備える。ここで、反射領域 B に形成された反射膜 170 は湾曲して形成することにより反射面をより広げることが好ましい。反射領域 B 及び 2 つの透過領域 C1、C2 により構成された単位画素領域 A は、それぞれの画素電極 150 が所定の間隔をおいて形成されることにより画定される。

10

#### 【0030】

活性層 110 は、データ線 140 と一部が重なったデータ線 140 の下部の任意の領域から第 1 の電極パターン 115 の任意の領域まで拡がって形成される。活性層 110 はゲート線 120 の下部に位置する。また、活性層 110 はデータ線 140 と第 1 のコンタクトホール 190 を通して接続され、画素電極 150 と第 2 のコンタクトホール 195 を通して接続される。そして、活性層 110 は、低温ポリシリコン薄膜により形成され、データ線 140 と第 1 のコンタクトホール 190 を通して接続される領域がソース領域 110s となり、画素電極 150 と第 2 のコンタクトホール 195 を通して接続される領域がドレイン領域となり、ソース領域 110s およびドレイン領域 110d を除く残りの領域がチャンネル領域 110c となる。すなわち、低温ポリシリコン膜のソース領域 110s およびドレイン領域 110d となる領域には不純物によるイオン注入され、チャンネル領域 110c の上部を通るゲート線 120 がゲート電極として機能することにより薄膜トランジスターが構成される。

20

#### 【0031】

第 1 の電極パターン 115 は、ストレジキャパシタの下部電極として機能するものであり、反射領域 B に、例えば、矩形に形成され、活性層 110 と同時に低温ポリシリコン膜により形成される。さらに、第 1 の電極パターン 115 は、活性層 110 のドレイン領域 110d に連なって形成される。

30

#### 【0032】

ゲート線 120 は、所定の間隔をおいて複数横方向に伸びて形成される。また、ゲート線 120 は、ゲート絶縁膜 117 によって下部に形成された活性層 110 と絶縁される。

#### 【0033】

第 2 の電極パターン 130 は、ストレジキャパシタの上部電極として機能するものであり、ゲート線 120 と同時に形成される。このとき、第 2 の電極パターン 130 は、第 2 のコンタクトホール 195 が形成される領域を除いては、第 1 の電極パターン 115 と重なって形成することが好ましい。第 2 の電極パターン 130 は、ゲート絶縁膜 117 を挟んで第 1 の電極パターン 115 とストレジキャパシタをなす。

40

#### 【0034】

第 1 の保護膜 135 は、ゲート線 120 が形成された絶縁基板 111 上全体に形成される。ここで、第 1 の保護膜 135 は、窒化シリコンまたは酸化シリコンなどの無機物質から形成されてもよく、低誘電率の有機絶縁膜から形成されてもよい。もちろん、無機絶縁膜と有機絶縁膜との 2 重膜に形成されてもよい。

#### 【0035】

第 1 のコンタクトホール 190 は、活性層 110 のソース領域 110s を露出させるために、第 1 の保護膜 135 及びゲート絶縁膜 117 の一部分を除去することによって形成される。

50

## 【0036】

データ線 140 は、ゲート線 120 と直交するように一方に向いて伸びて形成され、その一部が第1のコンタクト 190 を通ってソース領域 110s に接続される。これにより、データ線 140 は、ソース電極としての機能も兼ねる。

## 【0037】

第2の保護膜 145 は、データ線 140 が形成された絶縁基板 111 上全体に形成される。ここでも、第2の保護膜 145 は、第1の保護膜 135 と同様に、窒化シリコンまたは酸化シリコンなどの無機物質から形成されてもよく、低誘電率の有機絶縁膜から形成されてもよい。もちろん、無機絶縁膜と有機絶縁膜との2重膜に形成されてもよい。また、第2の保護膜 145 は、反射領域 B において湾曲させて形成することが好ましく、透過領域 C1、C2 においても湾曲させて形成してもよい。10

## 【0038】

第2のコンタクトホール 195 は、活性層 110 のドレイン領域 110d を露出させるために、第2の保護膜 145、第1の保護膜 135 及びゲート絶縁膜 117 の一部を除去することによって形成される。

## 【0039】

画素電極 150 はデータ線 140 の間に位置する画素領域 A に形成される。具体的には、反射領域 B と透過領域 C1、C2 にそれぞれ矩形の角部が丸く面取りされた形状に形成される。また、画素電極 150 は、第2のコンタクトホール 195 を通してドレイン領域 110d に接続される。これにより、画素電極 150 は、ドレイン電極としての機能も兼ねる。なお、画素電極 150 は、インジウム錫酸化物 (ITO) またはインジウム亜鉛酸化物 (IZO) などの透明導電体から形成され、画素電極 150 と同時に形成された透明導電体製の接続部 160 により反射領域 B および透過領域 C1、C2 に形成された画素電極 150B、150C1、150C2 が互いに接続される。このように反射領域 B を挟んで透過領域 C1、C2 が画定され、各領域にそれぞれ画素電極 150B、150C1、150C2 が互いに隔離して形成されることとなる。よって、従来のように2つの透過領域が隣接していないため、2つの透過領域を隔離するために2つの透過領域間に一定の距離を別途設ける必要がなく、結果として、その離隔に必要であった距離に対応する分だけ開口率の損失を抑えることができる。20

## 【0040】

反射膜 170 は、反射領域 B における画素電極 150 の上部または下部に形成されるが、反射領域 B に形成された画素電極 150B よりも大きい面積にて形成されることが好ましい。また、反射膜 170 は、湾曲させて形成された第2の保護膜 145 に沿って湾曲させて形成されることが好ましい。

## 【0041】

また、透過領域 C1、C2 の画素電極 150C1、150C2 には、液晶の配列方向を整えるためのドメインコントロール手段として、切欠部 180 がそれぞれ形成される。切欠部 180 は、透過領域 C1、C2 の画素電極 150C1、150C2 の中央部に円形に形成されることが好ましい。これは、角部が丸く面取りされた矩形の画素電極 150C1、150C2 の液晶の配列方向を揃えるためである。さらに、画素電極 150C1、150C2 は、切欠部 180 の代わりに突起を備えてもよい。40

## 【0042】

一方、カラーフィルター基板 200 は、第2の絶縁基板 211 の上にブラックマトリックス 220 と、カラーフィルター 230 と、オーバーコート膜 240 と、共通電極 250 とを備える。

## 【0043】

ブラックマトリックス 220 は、薄膜トランジスター基板 100 の画素領域 A 以外の領域への光の漏れ、および隣り合う画素領域間の光干渉を防ぐために形成される。従って、ブラックマトリックス 220 は、薄膜トランジスター基板 100 の画素領域 A 以外の領域50

に対応する位置に形成される。すなわち、ブラックマトリックス 220 は、薄膜トランジスター基板 100 の画素領域 A を囲むように形成される。これにより、ブラックマトリックス 220 は、薄膜トランジスター基板 100 のデータ線 140 に対応する領域と、各画素電極 150 間の隙間に対応する領域に形成される。

#### 【0044】

カラーフィルター 230 には、ブラックマトリックス 220 を境界として赤色、緑色および青色フィルターが繰り返して形成される。カラーフィルター 230 は、液晶層（図示せず）を通過した光源からの光に色を付加する機能を有する。カラーフィルター 230 は、感光性の有機物質により形成される。

#### 【0045】

オーバーコート膜 240 は、カラーフィルター 230 とカラーフィルター 230 に覆われていないブラックマトリックス 220 の上部に形成される。オーバーコート膜 240 は、アクリル系のエポキシ材料により形成され、カラーフィルター 230 を平坦化させるとともに、カラーフィルター 230 を保護する。

#### 【0046】

オーバーコート膜 240 の上部には共通電極 250 が形成される。共通電極 250 は ITO またはIZO などの透明な導電物質により形成される。共通電極 250 には切欠パターン（図示せず）を形成してもよい。共通電極 250 の切欠パターン（図示せず）は、画素電極 150 の切欠部 180 とともに液晶層（図示せず）を多数の領域に分割する役割を果たす。

#### 【0047】

以下、図 4A から図 8C に基づき、本発明に係る液晶表示装置のうち薄膜トランジスター基板の製造方法を説明する。

#### 【0048】

図 4A、図 5A、図 6A、図 7A、図 8A は、本発明に係る薄膜トランジスター基板の製造工程を示す平面図であり、図 4B、図 5B、図 6B、図 7B、図 8B は、本発明に係る薄膜トランジスター基板の製造工程の I - I' 線における断面図であり、図 4C、図 5C、図 6C、図 7C、図 8C は、本発明による薄膜トランジスター基板の製造工程の II - II' 線における断面図である。

#### 【0049】

図 4A、図 4B および図 4C に示すように、まず、第 1 の絶縁基板 111 の上部に半導体層を形成する。半導体層は、低温ポリシリコン薄膜により形成するが、低温ポリシリコン薄膜は、非晶質シリコン薄膜を形成した後、低温下でポリシリコン薄膜に結晶化することによって得る。ここで、非晶質シリコン薄膜を低温ポリシリコン薄膜に結晶化するために汎用される方法としては、固相結晶化法（Solid Phase Crystallization；SPC）、エキシマレーザー結晶化法（Eximer Laser Crystallization；ELC）及び金属誘導結晶化法（Metal Induced Crystallization；MIC）などがある。次いで、第 1 のマスクを用いたフォト工程およびエッチング工程により半導体層をパターニングする。半導体層は所定の領域において矩形にパターニングされる。ここから所定の幅をもって伸長すなわち、半導体層は、矩形にパターニングされた領域から、後にデータ線 140 が形成される領域まで伸長され、このとき、後にゲート線 120 が形成される領域を通る。ここで、矩形にパターニングされた半導体層は第 1 の電極パターン 115 となり、ここから所定の幅をもって伸長された半導体層は薄膜トランジスターのソース領域、ドレイン領域及びチャンネル領域が形成される活性層 110 となる。そして、活性層 110 の所定の領域、すなわち、データ線 140 が形成される領域と重なる領域及び第 1 の電極パターン 115 と連なる領域に不純物によるイオン注入がなされる。不純物によるイオン注入がされた後、エキシマレーザーなどを用いてイオン注入された不純物を活性化させる。ここで、不純物がイオン注入された活性層 110 の領域はそれぞれソース領域 110s 及びドレイン領域 110d となり、それ以外の領域はチャンネル領域 110c となる。前記工程により薄

10

20

30

40

50

膜トランジスター 110 及び第 1 の電極パターン 115 が形成される。なお、第 1 の電極パターン 115 にも不純物によるイオン注入がされ得る。

#### 【0050】

図 5 A、図 5 B 及び図 5 C に示すように、ソース領域 110 s、ドレイン領域 110 d およびチャンネル領域 110 c が形成された活性層 110 および第 1 の電極パターン 115 が形成された第 1 の絶縁基板 111 の上部全体にゲート絶縁膜 117 を形成する。ゲート絶縁膜 117 は、例えば、酸化シリコンまたは窒化シリコンなどのシリコン系の絶縁体により形成する。次いで、第 1 の絶縁基板 111 の上部全体に第 1 の導電層を形成する。ここで、第 1 の導電層は、アルミニウム (Al)、ネオジム (Nd)、銀 (Ag)、クロム (Cr)、チタン (Ti)、タンタル (Ta) およびモリブデン (Mo) よりなる群から選ばれた少なくとも 1 種の金属またはこれらの合金により形成することが好ましい。また、第 1 の導電層は、単一層に形成されても、複数の金属層よりなる多重層に形成されてもよい。すなわち、物理的、化学的な特性に優れたクロム (Cr)、チタン (Ti)、タンタル (Ta)、モリブデン (Mo) などの金属層と、比抵抗の低いアルミニウム (Al) 系または銀 (Ag) 系の金属層とからなる 2 重層として形成することもできる。そして、第 2 のマスクを用いたフォト工程およびエッチング工程により第 1 の導電層をパターニングしてゲート線 120 および第 2 の電極パターン 130 を形成する。ここで、ゲート線 120 は、一方向に伸びて複数形成される。また、第 2 の電極パターン 130 は、ゲート線 120 と所定の間隔を隔てて、ドレイン領域 110 d を露出させるとともに、第 1 の電極パターン 115 と重なるように形成される。なお、第 2 の電極パターン 130 は、ゲート絶縁膜 117 を挟んで第 1 の電極パターン 115 とともにストレジキャパシタをなす。

10

#### 【0051】

図 6 A、図 6 B 及び図 6 C に示すように、ゲート線 120 及び第 2 の電極パターン 130 が形成された第 1 の絶縁基板 111 の上部全体に第 1 の保護膜 135 を形成する。ここで、第 1 の保護膜 135 は、窒化シリコンまたは酸化シリコンなどの無機物質から形成されてもよく、低誘電率の有機絶縁膜から形成されてもよく、さらには、無機絶縁膜と有機絶縁膜との 2 重膜から形成されてもよい。第 3 のマスクを用いたフォト工程およびエッチング工程により、第 1 の保護膜 135 およびその下部のゲート絶縁膜 117 をエッチングして、活性層 110 のソース領域 110 s を露出させることにより第 1 のコンタクトホール 190 を形成する。次に、第 1 の絶縁基板 111 の上部全体に第 2 の導電層を形成する。第 2 の導電層は、第 1 の導電層をなす物質と同じ物質により形成し得る。第 4 のマスクを用いたフォト工程およびエッチング工程により第 2 の導電層をパターニングして、データ線 140 を形成する。データ線 140 は、ゲート線 120 と垂直な方向に伸びて形成される。また、第 2 の導電層が第 1 のコンタクトホール 190 を通じてソース領域 110 s に接続される。これにより、データ線 140 は、ソース電極としての機能も兼ねる。

20

#### 【0052】

図 7 A、図 7 B および図 7 C に示すように、データ線 140 が形成された第 1 の絶縁基板 111 の上部全体に第 2 の保護膜 145 を形成する。第 2 の保護膜 145 は、第 1 の保護膜 135 と同様に、窒化シリコンまたは酸化シリコンなどの無機物質から形成されてもよく、低誘電率の有機絶縁膜から形成されてもよく、さらには、無機絶縁膜と有機絶縁膜との 2 重膜から形成されてもよい。また、反射領域 B の第 2 の保護膜 145 は湾曲して形成されることが好ましく、透過領域 C1、C2 の第 2 の保護膜 145 も湾曲して形成されることが好ましい。次いで、第 5 のマスクを用いたフォト工程およびエッチング工程により第 2 の保護膜 145、第 1 の保護膜 135 およびゲート絶縁膜 117 をエッチングして、活性層 110 のドレイン領域 110 d を露出させることにより第 2 のコンタクトホール 195 を形成する。

30

#### 【0053】

図 8 A、図 8 B 及び図 8 C に示すように、第 2 のコンタクトホール 195 が形成された第 1 の絶縁基板 111 の上部全体に第 3 の導電層を形成する。そして、第 6 のマスクを用いたフォト工程およびエッチング工程により第 3 の導電層をパターニングして画素電極 1

40

50を形成する。画素電極150は、データ線140の間に位置する画素領域Aに形成し、また、隣り合う画素電極とは所定の間隔離して形成する。画素領域Aは、ゲート線120および第2の電極パターン130が通る画素領域Aの中央部の反射領域Bと、反射領域Bの両側の透過領域C1、C2により構成される。また、反射領域Bと透過領域C1、C2に形成された画素電極150B、150C1、150C2はそれぞれ矩形の角部が丸く面取りされた形状に形成される。反射領域Bと透過領域C1、C2に形成された画素電極150は接続部160により電気的に接続されるが、接続部160は、第4の導電層をパターニングして画素電極150を形成するときに同時に形成される。また、画素電極150は、第2のコンタクトホール195を介してドレイン領域110dに接続される。これにより、画素電極150は、ドレイン電極としての機能も兼ねる。なお、画素電極150および接続部160を形成するための第4の導電層は、ITOまたはIZOなどの透明導電体により形成する。また、画素電極150をパターニングするとき、透過領域C1、C2における画素電極150C1150C2の中央部には円形の切欠部180を形成することが好ましい。次に、第1の絶縁基板111の上部全体に反射膜170を形成した後、第7のマスクを用いたフォト工程およびエッチング工程により反射領域Bにのみ反射膜170を残す。このとき、反射膜170は、反射領域Bに形成された画素電極150よりも大きな面積に形成することが好ましく、湾曲して形成された第2の保護膜145に沿って湾曲して形成されることが好ましい。ここで、反射膜170は、光反射率に優れた銀(Ag)、アルミニウム(Al)、金(Au)、ネオジム(Nd)及び銅(Cu)よりなる群から選ばれた少なくとも1種の金属からなる単一層または多重層を用いて形成することができる。10

#### 【0054】

上記のような薄膜トランジスター基板100の製造とは別に、カラーフィルター基板200を製造する。カラーフィルター基板200を製造するために、第2の絶縁基板211の所定の領域、すなわち、薄膜トランジスター基板100における画素電極150が形成されない領域に対応する領域にブラックマトリックス220を形成し、画素電極150が形成される領域に対応する領域にカラーフィルター230を形成する。そして、ブラックマトリックス220とカラーフィルター230との段差を無くすためにオーバーコート膜240を形成する。この後、カラーフィルター基板200の全面に共通電極250を形成する。20

#### 【0055】

このようにして製造された薄膜トランジスター基板100とカラーフィルター基板200を、それぞれの画素電極150と共に電極250を互いに對向するようにして封止する。このとき、2枚の基板の封止のために、所定のシール膜が塗布される。そして、2枚の基板間のセルギャップを維持するためにスペーサーが設けられることもできる。この後、組み合わせられた2枚の基板の間に液晶を封入して液晶表示パネル300を製作する。

#### 【0056】

このようにして製作された液晶表示パネルによれば、薄膜トランジスター基板100の薄膜トランジスター110を通して画素の形成に必要な電気的信号を画素電極150に印加し、カラーフィルター基板200の共通電極250に共通電圧を印加することにより、画素電極150と共に電極250との間に電界が形成される。このような電界により液晶層の配列が変わり、変わった配列により光透過度が変更されて目的とする画像を表示することが可能になる。40

#### 【産業上の利用可能性】

#### 【0057】

本発明は、主に薄型テレビジョンや、パーソナルコンピュータのディスプレイ、携帯電話などの製造分野に利用されるが、他の分野においても本発明の技術的思想の範囲において適用され得る。

#### 【図面の簡単な説明】

#### 【0058】

【図1】本発明による液晶表示装置の平面図、

【図2】図1のI-I'線における断面図、

【図3】図1のII-II'線における断面図、

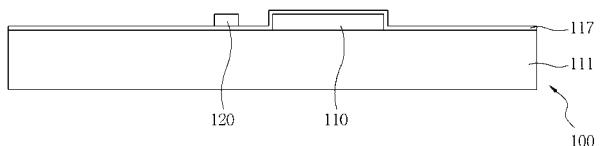

【図4A】本発明による薄膜トランジスター基板の製造方法を説明するための素子の工程手順別の断面図、

【図4B】図4AのI-I'線における断面図、

【図4C】図4A II-II'線における断面図、

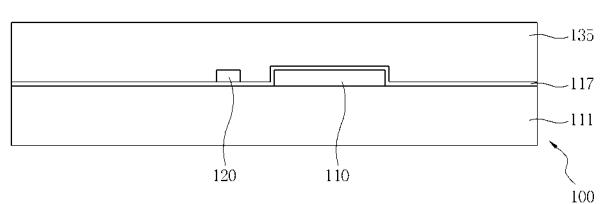

【図5A】本発明による薄膜トランジスター基板の製造方法を説明するための素子の工程手順別の断面図、

【図5B】図5AのI-I'線における断面図、

【図5C】図5AのII-II'線における断面図、

【図6A】本発明による薄膜トランジスター基板の製造方法を説明するための素子の工程手順別の断面図、

【図6B】図6AのI-I'線における断面図、

【図6C】図6AのII-II'線における断面図、

【図7A】本発明による薄膜トランジスター基板の製造方法を説明するための素子の工程手順別の断面図、

【図7B】図7AのI-I'線における断面図、

【図7C】図7AのII-II'線における断面図、

【図8A】本発明による薄膜トランジスター基板の製造方法を説明するための素子の工程手順別の断面図、

【図8B】図8AのI-I'線における断面図、

【図8C】図8AのII-II'線における断面図。

【符号の説明】

【0059】

A 画素領域、

B 反射領域、

C1、C2 透過領域、

100 薄膜トランジスター基板、

110 活性層、

110s ソース領域、

110c チャンネル、

110d ドレイン領域、

115 第1の電極パターン、

117 ゲート絶縁膜、

120 ゲート線、

130 第2の電極パターン、

135 第1の保護膜、

140 データ線、

145 第2の保護膜、

150 画素電極、

160 接続部、

170 反射膜、

180 切欠部、

200 カラーフィルター基板、

211 第2の絶縁基板、

220 ブラックマトリックス、

230 カラーフィルター、

240 オーバーコート膜、

250 共通電極、

10

20

30

40

50

## 300 液晶表示パネル。

【図3】

【図4A】

【図4B】

【図5A】

【図4C】

【図 5 B】

【図 5 C】

【図 6 A】

【図 6 B】

【図 6 C】

【図 7 A】

【図 7 B】

【図 7 C】

【図 8 A】

【図 8 B】

【図 8 C】

---

フロントページの続き

(72)発明者 文 國 哲

大韓民国京畿道龍仁市水枝区新鳳洞 現代アパート404棟301号

(72)発明者 金 宰 賢

大韓民国京畿道水原市靈通区靈通洞 ビョクジエゴルジュンアンアパート845棟501号

(72)発明者 孟 昊 せき

大韓民国ソウル特別市銅雀区上道5洞 三星レミアン2次アパート203棟203号

(72)発明者 李 相 勳

大韓民国ソウル特別市冠岳区奉天洞1654-9番地 ファインヒルオフィステル401号室

(72)発明者 金 京 勳

大韓民国京畿道儀旺市五全洞 デミヨングルムチェアパート203棟2106号

(72)発明者 朴 根 佑

大韓民国ソウル特別市江南区開浦4洞 シヨンアパート12棟507号

審査官 磯野 光司

(56)参考文献 特開2006-011398(JP,A)

特開2006-171455(JP,A)

特開2005-257809(JP,A)

特開2006-071866(JP,A)

特開2006-072087(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 02 F 1 / 1335

G 02 F 1 / 1343

G 02 F 1 / 1368