(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5097997号

(P5097997)

(45) 発行日 平成24年12月12日(2012.12.12)

(24) 登録日 平成24年10月5日(2012.10.5)

|                          |                |

|--------------------------|----------------|

| (51) Int.Cl.             | F 1            |

| HO 1 L 21/822 (2006.01)  | HO 1 L 27/04 C |

| HO 1 L 27/04 (2006.01)   | HO 1 L 27/04 D |

| HO 1 L 21/82 (2006.01)   | HO 1 L 21/82 L |

| HO 1 L 21/3205 (2006.01) | HO 1 L 21/88 Z |

| HO 1 L 21/768 (2006.01)  |                |

請求項の数 6 (全 19 頁) 最終頁に続く

(21) 出願番号 特願2009-240551 (P2009-240551)

(22) 出願日 平成21年10月19日 (2009.10.19)

(62) 分割の表示 特願2006-231229 (P2006-231229)

の分割

原出願日 平成14年2月22日 (2002.2.22)

(65) 公開番号 特開2010-21574 (P2010-21574A)

(43) 公開日 平成22年1月28日 (2010.1.28)

審査請求日 平成21年10月19日 (2009.10.19)

(73) 特許権者 302062931

ルネサスエレクトロニクス株式会社

神奈川県川崎市中原区下沼部 1753番地

(74) 代理人 100108855

弁理士 蔵田 昌俊

(74) 代理人 100091351

弁理士 河野 哲

(74) 代理人 100088683

弁理士 中村 誠

(74) 代理人 100109830

弁理士 福原 淑弘

(74) 代理人 100075672

弁理士 峰 隆司

(74) 代理人 100084618

弁理士 村松 貞男

最終頁に続く

(54) 【発明の名称】配線素子ブロックとそれを含む半導体チップ

## (57) 【特許請求の範囲】

## 【請求項 1】

同一方向にピッチ配列された複数の配線の、そのピッチ配列の方向が互いに交差するよう積層された複数の配線層と、

各配線層の、隣り合う配線におのおの異なる第1，第2の電位が供給されるように、前記複数の配線層の相互を接続する複数コンタクト部と

を具備し、

前記複数のコンタクト部は、ある配線層の最外側に位置する配線と他の配線層の配線との間にのみ設けられることを特徴とする配線素子ブロック。

## 【請求項 2】

同一方向にピッチ配列された複数の配線の、そのピッチ配列の方向が互いに交差するよう積層された複数の配線層と、

各配線層の、隣り合う配線におのおの異なる第1，第2の電位が供給されるように、前記複数の配線層の相互を接続する複数コンタクト部と

を具備し、

前記複数のコンタクト部は、ある配線層の最外側に位置する配線と他の配線層の配線との間に設けられ、

前記ある配線層の最外側以外に位置する、前記第1および前記第2の電位いずれか一方が供給される配線と、前記他の配線層の最外側以外に位置する、前記第1および前記第2の電位のいずれか一方が供給されるは配線との間には、前記コンタクト部を有しないこと

10

20

を特徴とする配線素子ブロック。

**【請求項 3】**

前記第1、第2の電位は、それぞれVDD、VSSであることを特徴とする請求項1又は2に記載の配線素子ブロック。

**【請求項 4】**

前記配線層の最外側に位置する配線は、VDD又はVSS電位供給源に接続されるVDD又はVSS配線であり、前記配線層の最外側以外に位置する配線の少なくとも1本は、信号配線であることを特徴とする請求項1又は2に記載の配線素子ブロック。

**【請求項 5】**

請求項1乃至請求項4に記載の配線素子ブロックを含む、半導体チップ。

10

**【請求項 6】**

電源グリッド配線を備え、前記配線素子ブロックは、前記電源グリッド配線と平面的に重なり合うように配置されていることを特徴とする請求項5に記載の半導体チップ。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

この発明は、多層配線装置に関するもので、特に、互いに直交する微細ピッチ多層配線構造を用いた並走配線間容量によるデカップリング容量に関する。

**【背景技術】**

**【0002】**

集積回路(LSI)において、電源電圧・電流の供給は、これまで安定したものであるとされてきた。しかし、回路数の増大によってチップ面積が大きくなり、さらに高速動作によって瞬間的に大きな電流が回路に流れると、電源配線抵抗やインダクタンスによる電源線(VDD, VSS)の電圧ドロップ(電源ノイズ)が発生し、回路が誤動作するなどの弊害がでてきた。

20

**【0003】**

従来、デカップリング容量を電源線間に挿入することにより、この弊害を軽減できることが知られている。すなわち、上記弊害を軽減するために、たとえば、パッケージのVDD, VSSピン間にセラミックコンデンサを挿入することが行われる。しかしながら、この方法の場合、半導体チップの入出力ドライバの電源ノイズを低減するのには有効であるが、LSI内部の高速で駆動される回路で生じる電源ノイズ(スパイク電流)に対しては効果がない。

30

**【0004】**

また、別の方法として、MOSFET(Metal Oxide Semiconductor Field Effect Transistor)のゲート酸化膜容量を使って、VDD, VSS間にデカップリング容量をつけることで、大きな電流により高速で駆動される回路のスパイク電流を吸収し、電源ノイズを低減する方法が知られている。この方法は有効ではあるものの、高周波、高速特性が悪いという欠点がある。また、大きなゲート面積の容量が必要であり、ゲート酸化膜の微小なピンホールによって、VDD, VSS間にリーキ電流が増大し、消費電力を大きくするという欠点があった。

40

**【0005】**

さらに、多層配線の並走配線間容量を複数の配線層にわたって構成し、VDD, VSS配線を交互に接続することによって大きなデカップリング容量をオンチップで作る提案もなされている(たとえば、非特許文献1参照)。この場合は、メタル配線間の容量であるため、上記したMOSFETのゲート酸化膜容量の場合と比べて、高周波、高速特性のよいデカップリング容量を提供できる利点がある。

**【0006】**

しかしながら、この方法の場合、高周波、高速特性には優れているものの、容量配線領域(エリア)にクロスさせて信号線を通すことができない。したがって、チップの周辺部にしか配置することができず、大きな電流により高速で駆動される回路のスパイク電流を

50

吸収しようとする場合にも、その回路の近傍に設けることができないという欠点があった。すなわち、半導体チップの内部には配置することができないという大きな問題があった。

**【先行技術文献】**

**【特許文献】**

**【0007】**

**【非特許文献1】** 2001 Symposium on VLSI Circuits Digest of Technical Paper, pp. 201 - 204

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0008】**

上記したように、従来においては、多層配線の並走配線間容量を複数の配線層にわたって構成し、VDD, VSS配線を交互に接続することによって、高周波、高速特性に優れた大きなデカップリング容量を形成できるものの、容量配線領域にクロスさせて信号線を通すことができないため、半導体チップの内部に配置できないという問題があった。

**【0009】**

そこで、この発明は、高周波、高速特性に優れた大きなデカップリング容量を形成できるとともに、容量配線領域にクロスさせて信号線を布設でき、半導体チップの内部に広く配置することが可能な配線素子ブロックとそれを含む半導体チップを提供することを目的としている。

**【課題を解決するための手段】**

**【0010】**

上記の目的を達成するために、この発明の配線素子ブロックにあっては、同一方向にピッチ配列された複数の配線の、そのピッチ配列の方向が互いに交差するように積層された複数の配線層と、各配線層の、隣り合う配線におのおの異なる第1, 第2の電位が供給されるように、前記複数の配線層の相互を接続する複数コンタクト部とを具備し、前記複数のコンタクト部は、ある配線層の最外側に位置する配線と他の配線層の配線との間にのみ設けられることを特徴とする。

**【0011】**

また、この発明の配線素子ブロックにあっては、同一方向にピッチ配列された複数の配線の、そのピッチ配列の方向が互いに交差するように積層された複数の配線層と、各配線層の、隣り合う配線におのおの異なる第1, 第2の電位が供給されるように、前記複数の配線層の相互を接続する複数コンタクト部とを具備し、前記複数のコンタクト部は、ある配線層の最外側に位置する配線と他の配線層の配線との間に設けられ、前記ある配線層の最外側以外に位置する、前記第1および前記第2の電位いずれか一方が供給される配線と、前記他の配線層の最外側以外に位置する、前記第1および前記第2の電位のいずれか一方が供給されるは配線との間には、前記コンタクト部を有しないことを特徴とする。

**【0012】**

さらに、この発明の配線素子ブロックにあって、第1、第2の電位は、それぞれVDD、VSSであることを特徴とし、配線層の最外側に位置する配線は、VDD又はVSS電位供給源に接続されるVDD又はVSS配線であり、前記配線層の最外側以外に位置する配線の少なくとも1本は、信号配線であることを特徴とする。

また、本発明の半導体チップにあっては、上記配線素子ブロックを含み、さらに、電源グリッド配線を備え、前記配線素子ブロックは、前記電源グリッド配線と平面的に重なり合うように配置されていることを特徴とする。

**【発明の効果】**

**【0013】**

この発明によれば、高周波、高速特性に優れた大きなデカップリング容量を形成できるとともに、容量配線領域にクロスさせて信号線を布設でき、半導体チップの内部に広く配置することが可能な配線素子ブロックとそれを含む半導体チップを提供できる。

10

20

30

40

50

**【0014】**

特に、各配線層の隣り合う配線に対する第1，第2の電位の供給を、スルーホールコンタクトを介して如何に供給するかを、効率的かつシステムティックに規定することが可能となる。

**【0015】**

しかも、スルーホールコンタクトの削除により、第1，第2の電位の供給をはずすことで、一部の配線を信号線としても使用することが可能である。これにより、容量配線領域にクロスさせて信号線を通すことが可能となる結果、高周波，高速特性に優れる大きなデカップリング容量を、大きな電流により高速で駆動される回路の近傍に設けることが可能となる。

10

**【0016】**

また、信号線の周囲にシールド配線を存在させることができるために、信号にノイズがのりにくくなり、ノイズによる誤動作が極めて少ない自動配線接続アルゴリズムを実現できる。

**【0017】**

また、配線素子ブロックをチップの全面に敷き詰めるようにした場合には、チップの表面での平坦性の確保が可能となり、メタル配線を形成する上で、チップ内での均一性や歩留まりの向上にとって好適となる。

**【0018】**

また、各配線層間をつなぐコンタクトの削除・追加のみにより、信号線の経路を任意に変更できるようになるため、ASICビジネスにおける設計期間短縮などの効果が期待できる。

20

**【0019】**

さらには、配線アーキテクチャとしての応用に関し、配線素子ブロック内の信号線の配線構造にともなう入出力信号伝播特性を、配線セルを中心としたライブラリとして管理することで、そのライブラリにもとづいたASIC，SoC（System on Chip）設計手法の展開が可能となる。

**【図面の簡単な説明】****【0020】**

**【図1】**本発明の第1の実施形態にかかる配線素子ブロックの配線構造を模式的に示す斜視図。

30

**【図2】**図1に示した配線素子ブロックの、各配線層間の接続の状態を分解して示す平面図。

**【図3】**図1に示した配線素子ブロックの、一部の配線を信号線として使用するようにした場合を例に示す分解斜視図。

**【図4】**本発明の第2の実施形態にかかり、図1に示した配線素子ブロックと同等の配線構造を、スルーホールコンタクトの数を減らして実現する場合の例を示す分解斜視図。

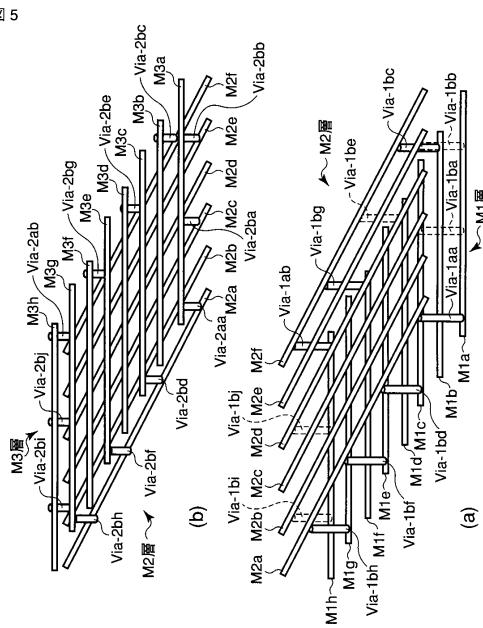

**【図5】**図4に示した配線素子ブロックの、一部の配線を信号線として使用するようにした場合を例に示す分解斜視図。

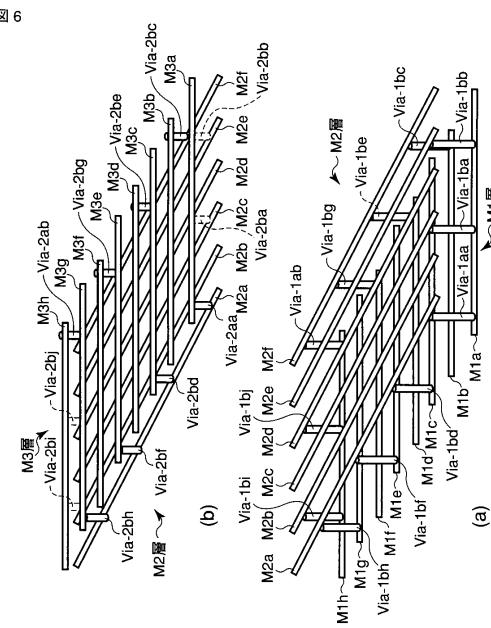

**【図6】**本発明の第3の実施形態にかかり、図1に示した配線素子ブロックと同等の配線構造を、スルーホールコンタクトの数を減らして実現する場合の他の例を示す分解斜視図。

40

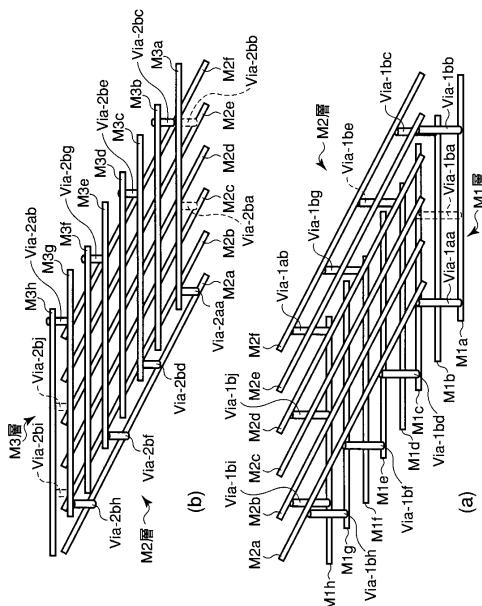

**【図7】**図6に示した配線素子ブロックの、一部の配線を信号線として使用するようにした場合を例に示す分解斜視図。

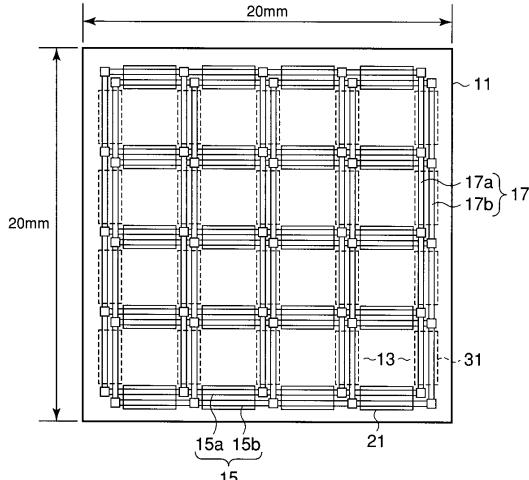

**【図8】**本発明の第4の実施形態にかかり、配線素子ブロックの配置の一例を示す平面図。

**【図9】**本発明の第5の実施形態にかかり、配線素子ブロックの配置の他の例を示す平面図。

**【図10】**本発明の第6の実施形態にかかり、配線方法について説明するために示す多層配線装置の平面図。

50

【図11】図10に示した多層配線装置に対する信号線の布設例を示す平面図。

【図12】本発明の第7の実施形態にかかり、多層配線装置の配線特性解析・予測方法について説明するために示す図。

**【発明を実施するための形態】**

**【0021】**

以下、この発明の実施の形態について図面を参照して説明する。

**【0022】**

(第1の実施形態)

図1, 図2は、本発明の第1の実施形態にかかる多層配線装置(多層配線構造の配線素子ブロック)の構成例を示すものである。なお、図1は、配線素子ブロックの配線構造を模式的に示す斜視図である。図2は、図1に示した配線素子ブロックの分解図であり、各配線層間の接続の状態を平面的に示したものである。また、ここでは、層数(m)を「5」とし、配線層の数(n)を「3」とした場合について説明する(ただし、m > n, n > 2)。この場合、配線層M1～M5(M1層～M5層)のうち、下層側のM1層～M3層が配線層として用いられ、図示していない上層側のM4層, M5層が電源グリッドとして用いられる。

**【0023】**

配線層M1～M3のうち、下段のM1層は、複数(p(i), i = 1～k)本の配線(ピッチ配線)M1a, M1b, …, M1hを有している。M1層の各配線M1a, M1b, …, M1hは、図面の上下方向に同一ピッチにより配列(ピッチ配列)されている。中段のM2層は、複数(p(i), i = 1～k)本の配線(ピッチ配線)M2a, M2b, …, M2fを有している。M2層の各配線M2a, M2b, …, M2fは、上記M1層と垂直に交わる方向、すなわち、図面の左右方向にピッチ配列されている。上段のM3層は、複数(p(i), i = 1～k)本の配線(ピッチ配線)M3a, M3b, …, M3hを有している。M3層の各配線M3a, M3b, …, M3hは、上記M2層と垂直に交わる方向、すなわち、上記M1層と同じ、図面の上下方向にピッチ配列されている。

**【0024】**

上記M1層および上記M2層は、図2(a)に示すように、第1のコンタクトであるスルーホールコンタクトVia-1aa, -1ab(図示印)と第2のコンタクトであるスルーホールコンタクトVia-1ba, -1bb, …, -1bj(図示印)とを介して、上記M2層および上記M3層は、図2(b)に示すように、第1のコンタクトであるスルーホールコンタクトVia-2aa, -2ab(図示印)と第2のコンタクトであるスルーホールコンタクトVia-2ba, -2bb, …, -2bj(図示印)とを介して、それぞれ電気的に接続されている。

**【0025】**

すなわち、スルーホールコンタクトVia-1aaは、上記M1層の配線M1aと上記M2層の配線M2aとの交点に、同じく、スルーホールコンタクトVia-1abは、上記M1層の配線M1hと上記M2層の配線M2fとの交点に、それぞれ設けられている。

**【0026】**

同様に、スルーホールコンタクトVia-1baは、上記M1層の配線M1aと上記M2層の配線M2cとの交点に設けられている。また、スルーホールコンタクトVia-1bbは、上記M1層の配線M1aと上記M2層の配線M2eとの交点に設けられている。また、スルーホールコンタクトVia-1bcは、上記M1層の配線M1bと上記M2層の配線M2fとの交点に設けられている。また、スルーホールコンタクトVia-1bdは、上記M1層の配線M1cと上記M2層の配線M2aとの交点に設けられている。また、スルーホールコンタクトVia-1beは、上記M1層の配線M1dと上記M2層の配線M2fとの交点に設けられている。

**【0027】**

また、スルーホールコンタクトVia-1bfは、上記M1層の配線M1eと上記M2層の配線M2aとの交点に設けられている。また、スルーホールコンタクトVia-1b

10

20

30

40

50

g は、上記 M 1 層の配線 M 1 f と上記 M 2 層の配線 M 2 f との交点に設けられている。また、スルーホールコンタクト V i a - 1 b h は、上記 M 1 層の配線 M 1 g と上記 M 2 層の配線 M 2 a との交点に設けられている。また、スルーホールコンタクト V i a - 1 b i は、上記 M 1 層の配線 M 1 h と上記 M 2 層の配線 M 2 b との交点に設けられている。また、スルーホールコンタクト V i a - 1 b j は、上記 M 1 層の配線 M 1 h と上記 M 2 層の配線 M 2 d との交点に設けられている。

#### 【 0 0 2 8 】

一方、スルーホールコンタクト V i a - 2 a a は、上記 M 2 層の配線 M 2 a と上記 M 3 層の配線 M 3 a との交点に、同じく、スルーホールコンタクト V i a - 2 a b は、上記 M 2 層の配線 M 2 f と上記 M 3 層の配線 M 3 h との交点に、それぞれ設けられている。

10

#### 【 0 0 2 9 】

同様に、スルーホールコンタクト V i a - 2 b a は、上記 M 2 層の配線 M 2 c と上記 M 3 層の配線 M 3 a との交点に設けられている。また、スルーホールコンタクト V i a - 2 b b は、上記 M 2 層の配線 M 2 e と上記 M 3 層の配線 M 3 a との交点に設けられている。また、スルーホールコンタクト V i a - 2 b c は、上記 M 2 層の配線 M 2 f と上記 M 3 層の配線 M 3 b との交点に設けられている。また、スルーホールコンタクト V i a - 2 b d は、上記 M 2 層の配線 M 2 a と上記 M 3 層の配線 M 3 c との交点に設けられている。また、スルーホールコンタクト V i a - 2 b e は、上記 M 2 層の配線 M 2 f と上記 M 3 層の配線 M 3 d との交点に設けられている。

#### 【 0 0 3 0 】

20

また、スルーホールコンタクト V i a - 2 b f は、上記 M 2 層の配線 M 2 a と上記 M 3 层の配線 M 3 e との交点に設けられている。また、スルーホールコンタクト V i a - 2 b g は、上記 M 2 層の配線 M 2 f と上記 M 3 層の配線 M 3 f との交点に設けられている。また、スルーホールコンタクト V i a - 2 b h は、上記 M 2 層の配線 M 2 a と上記 M 3 層の配線 M 3 g との交点に設けられている。また、スルーホールコンタクト V i a - 2 b i は、上記 M 2 層の配線 M 2 b と上記 M 3 層の配線 M 3 h との交点に設けられている。また、スルーホールコンタクト V i a - 2 b j は、上記 M 2 層の配線 M 2 d と上記 M 3 層の配線 M 3 h との交点に設けられている。

#### 【 0 0 3 1 】

30

ここで、各配線層 M 1 , M 2 , M 3 の平面サイズを、たとえば、 $20 \mu m$  角 ( $20 \mu m \times 20 \mu m$ ) の大きさとした場合、 $0.13 \mu m$  レベルの CMOS プロセスでは、各配線層 M 1 , M 2 , M 3 における配線のピッチは、おのおの、 $0.36 \mu m$  ,  $0.4 \mu m$  ,  $0.36 \mu m$  となる。したがって、上記サイズの配線層 M 1 , M 2 , M 3 に対して、それぞれ、55 本 , 50 本 , 55 本の配線を布設できる。

#### 【 0 0 3 2 】

30

各配線層 M 1 , M 2 , M 3 の最外側に配置された配線 M 1 a , M 1 h , M 2 a , M 2 f , M 3 a , M 3 h には、常に、VDD 電位供給源からの VDD 電位 (第 1 の電位) または VSS 電位供給源からの VSS 電位 (第 2 の電位) が供給されている。たとえば、配線 (VDD 配線) M 1 a , M 2 a , M 3 a には VDD 電位が、配線 (VSS 配線) M 1 h , M 2 f , M 3 h には VSS 電位が、それぞれ供給されている。これは、上記スルーホールコンタクト V i a - 1 a a , - 2 a a 、または、上記スルーホールコンタクト V i a - 1 a b , - 2 a b を介して、たとえば上記 M 3 層 , M 2 層 , M 1 層の順に、それぞれ、VDD 電位または VSS 電位が供給されることにより実現される。

40

#### 【 0 0 3 3 】

同様に、各配線層 M 1 , M 2 , M 3 の最外側以外の配線 (信号線としても利用することが可能な信号配線 (s(j) 本 (s(j) p(i) - 2 , j = 1 ~ k)) には、VDD 電位 , VSS 電位が隣り合うように供給される。たとえば、配線 (奇数番目の配線) M 1 c , M 1 e , M 1 g , M 2 c , M 2 e , M 3 c , M 3 e , M 3 g には VDD 電位が、配線 (偶数番目の配線) M 1 b , M 1 d , M 1 f , M 2 b , M 2 d , M 3 b , M 3 d , M 3 f には VSS 電位が、それぞれ供給されている。これは、上記スルーホールコンタクト V i

50

a - 1 b a , - 1 b b , - 1 b d , - 1 b f , - 1 b h , - 2 b a , - 2 b b , - 2 b d , - 2 b f , - 2 b h 、または、上記スルーホールコンタクト V i a - 1 b c , - 1 b e , - 1 b g , - 1 b i , - 1 b j , - 2 b c , - 2 b e , - 2 b g , - 2 b i , - 2 b j を介して、それぞれ、V D D 電位またはV S S 電位が供給されることにより実現される。

#### 【0034】

代表的な  $0.13\text{ }\mu\text{m}$  レベルの C M O S プロセスでの、各配線層 M 1 , M 2 , M 3 のピッチ配線隣接配線容量を  $0.26\text{ fF}/\mu\text{m}$  と仮定すると、 $20\text{ }\mu\text{m}$  角のエリア（容量配線領域）で、約  $0.2\text{ pF}$  の高速デカップリング容量を実現できる。

#### 【0035】

また、代表的な  $0.13\text{ }\mu\text{m}$  レベルの C M O S プロセスでの、各配線層 M 1 , M 2 , M 3 の配線シート抵抗値は  $0.07\text{ }\Omega/\text{角}$  であり、配線時定数は  $0.1\text{ ps}$  以下であり、十分、応答性に優れている。

#### 【0036】

このように、各配線層 M 1 , M 2 , M 3 における配線の隣接配線容量（微細ピッチ多層配線構造を用いた並走配線間容量）が V D D , V S S 間デカップリング容量として働くことにより、大きなデカップリング容量を形成することが可能である。

#### 【0037】

しかも、並走配線間容量を利用して大きなデカップリング容量を形成するものであるため、微細プロセス技術が進歩するのにともなって、その効果は増大される。

#### 【0038】

また、本実施形態にかかる多層配線装置の場合、各配線層 M 1 , M 2 , M 3 における一部の配線を信号線としても使用することが可能である。すなわち、各配線層 M 1 , M 2 , M 3 の最外側の配線以外、つまり、V D D 配線 M 1 a , M 2 a , M 3 a および V S S 配線 M 1 h , M 2 f , M 3 h を除く、全ての信号配線を信号線として使用することができる。

#### 【0039】

図 3 は、本実施形態にかかる多層配線装置において、一部の配線を信号線として使用するようにした場合を例に示すものである。なお、同図 (a) は、M 1 層と M 2 層との接続の状態を、同図 (b) は、M 2 層と M 3 層との接続の状態を、それぞれ示すものである。

#### 【0040】

たとえば、上記スルーホールコンタクト V i a - 1 b a , - 2 b a を削除し、配線 M 2 c に対する V D D 電位の供給をはずす（フローティング状態とする）ことによって、その配線 M 2 c を信号線として使うことができる。この場合、他の配線には、必ず、V D D 電位または V S S 電位のいずれかが供給されている。そのため、信号線として使用される配線 M 2 c は周囲が直流的な電極でシールドされる、つまり、配線 M 2 c は、これに隣接して V D D または V S S なる固定電位でシールドされた配線（シールド配線）が存在することになり、信号線ノイズ（クロストークノイズ）耐性に優れるという大きな利点もある。

#### 【0041】

このように、上記配線 M 2 c に限らず、V D D , V S S 配線を除く、所望の信号配線に対する V D D , V S S 電位の供給をはずすことによって、その信号配線を、容量配線領域にクロスする信号線として使用することが可能である。これにより、配線素子ブロックを半導体チップの内部に配置することが容易に可能となる。

#### 【0042】

上記したように、本実施形態においては、大きなデカップリング容量を持つとともに、従来の構造では不可能であった、信号線の通過を可能にする多層配線装置を実現できる。すなわち、従来の、多層配線の並走配線間容量を複数の配線層にわたって構成し、V D D , V S S 配線を交互に接続することにより、大きなデカップリング容量をオンチップで作る場合の大きな欠点であった、容量配線領域にクロスさせて信号線を通すことができなかつたという問題を解消し得、高速なデカップリング容量をチップ内部に広く配置することが可能となるものである。

#### 【0043】

10

20

30

40

50

特に、この構成の多層配線装置にあっては、たとえば高周波・高速C M O Sの分野において、最も利用される可能性が高い。また、チップ面積の大きいシステムL S Iにおける配線アーキテクチャとしても広く利用することが可能である。

#### 【0044】

なお、上記した第1の実施形態では、層数を「5」とし、そのうちのM 1層，M 2層，M 3層を配線層として用いた場合について説明したが、これに限らず、たとえばM 1層，M 2層，M 3層，M 4層を配線層として用いることも可能であり、また、層数も「5」に制限されるものではない。

#### 【0045】

##### (第2の実施形態)

10

図4(a), (b)は、本発明の第2の実施形態にかかる多層配線装置(多層配線構造の配線素子ブロック)の構成例を示すものである。ここでは、図1に示した構成の配線素子ブロックと同等の配線構造を、配線層M 1, M 2間のスルーホールコンタクトの数を減らして実現する場合の例について説明する。

#### 【0046】

同図(a)に示すように、スルーホールコンタクトV i a - 1 b a, - 1 b b, - 1 b i, - 1 b jを削除することによっても、図1に示した構成の配線素子ブロックと同等の配線構造を実現できる。

#### 【0047】

たとえば、スルーホールコンタクトV i a - 1 b aを削除した場合、配線M 2cへのV D D電位の供給は、スルーホールコンタクトV i a - 2 b aを介して、配線M 3aより行われる(同図(b)参照)。同様に、スルーホールコンタクトV i a - 1 b bを削除した場合、配線M 2eへのV D D電位の供給は、スルーホールコンタクトV i a - 2 b bを介して、配線M 3aより行われる(同図(b)参照)。同様に、スルーホールコンタクトV i a - 1 b iを削除した場合、配線M 2bへのV S S電位の供給は、スルーホールコンタクトV i a - 2 b iを介して、配線M 3hより行われる(同図(b)参照)。同様に、スルーホールコンタクトV i a - 1 b jを削除した場合、配線M 2dへのV S S電位の供給は、スルーホールコンタクトV i a - 2 b jを介して、配線M 3hより行われる(同図(b)参照)。

20

#### 【0048】

このように、図1に示した構成の配線素子ブロックにおいては、スルーホールコンタクトV i a - 1 b a, - 1 b b, - 1 b i, - 1 b jを削除することが可能であり、これにより、プロセスを簡素化できる。

30

#### 【0049】

また、図5(a), (b)に示すように、この第2の実施形態にかかる多層配線装置においても、上記した第1の実施形態の場合と同様に、一部の配線を信号線として使用することが可能である。

#### 【0050】

すなわち、スルーホールコンタクトV i a - 1 b a, - 1 b b, - 1 b i, - 1 b jを削除した構成において、たとえば同図(a)に示すように、上記スルーホールコンタクトV i a - 1 b eを削除し、配線M 1dに対するV S S電位の供給をはずすことによって、その配線M 1dを信号線として使うことができる。この場合も、他の配線には、必ず、V D D電位またはV S S電位のいずれかが供給されている。そのため、信号線として使用される配線M 1dは、信号線ノイズ耐性に優れたものとなる。

40

#### 【0051】

なお、上記配線M 1dに限らず、V D D, V S S配線を除く、所望の信号配線に対するV D D, V S S電位の供給をはずすことによって、その信号配線を、容量配線領域にクロスする信号線として使用することが可能なことは勿論である。

#### 【0052】

##### (第3の実施形態)

50

図6(a), (b)は、本発明の第3の実施形態にかかる多層配線装置(多層配線構造の配線素子ブロック)の構成例を示すものである。ここでは、図1に示した構成の配線素子ブロックと同等の配線構造を、配線層M2, M3間のスルーホールコンタクトの数を減らして実現する場合の例について説明する。

#### 【0053】

同図(b)に示すように、スルーホールコンタクトVia-2ba, -2bb, -2bi, -2bjを削除することによっても、図1に示した構成の配線素子ブロックと同等の配線構造を実現できる。

#### 【0054】

たとえば、スルーホールコンタクトVia-2baを削除した場合、配線M2cへのVDD電位の供給は、スルーホールコンタクトVia-1baを介して、配線M1aより行われる(同図(a)参照)。同様に、スルーホールコンタクトVia-2bbを削除した場合、配線M2eへのVDD電位の供給は、スルーホールコンタクトVia-1bbを介して、配線M1aより行われる(同図(a)参照)。同様に、スルーホールコンタクトVia-2biを削除した場合、配線M2bへのVSS電位の供給は、スルーホールコンタクトVia-1biを介して、配線M1hより行われる(同図(a)参照)。同様に、スルーホールコンタクトVia-2bjを削除した場合、配線M2dへのVSS電位の供給は、スルーホールコンタクトVia-1bjを介して、配線M1hより行われる(同図(a)参照)。

#### 【0055】

このように、図1に示した構成の配線素子ブロックにおいては、スルーホールコンタクトVia-2ba, -2bb, -2bi, -2bjを削除することが可能であり、これにより、プロセスを簡素化できる。

#### 【0056】

また、図7(a), (b)に示すように、この第3の実施形態にかかる多層配線装置においても、上記した第1の実施形態の場合と同様に、一部の配線を信号線として使用することが可能である。

#### 【0057】

すなわち、スルーホールコンタクトVia-2ba, -2bb, -2bi, -2bjを削除した構成において、たとえば同図(a)に示すように、上記スルーホールコンタクトVia-1baを削除し、配線M2cに対するVDD電位の供給をはずすことによって、その配線M2cを信号線として使うことができる。この場合も、他の配線には、必ず、VDD電位またはVSS電位のいずれかが供給されている。そのため、信号線として使用される配線M2cは、信号線ノイズ耐性に優れたものとなる。

#### 【0058】

なお、上記配線M2cに限らず、VDD, VSS配線を除く、所望の信号配線に対するVDD, VSS電位の供給をはずすことによって、その信号配線を、容量配線領域にクロスする信号線として使用することが可能なことは勿論である。

#### 【0059】

#### (第4の実施形態)

図8は、本発明の第4の実施形態にかかり、多層配線装置(多層配線構造の配線素子ブロック)の配置例を示すものである。ここでは、20\*20mm角のサイズを有する半導体チップ上に布設された100\*100μm角のパワーグリッド(以下、Pwグリッド)の下に、本発明の配線素子ブロックを埋め込んだ場合を例に説明する。

#### 【0060】

たとえば、20\*20mm角サイズの半導体チップ11において、上層側のM4層, M5層が電源グリッドとして用いられる場合、碁盤の目(マトリクス)状に16個の配線領域13が配置されている。各配線領域13の周辺部(この例では、100\*100μm角サイズのPwグリッドが布設されたグリッド辺)には、それぞれ、第1のVDD, VSSペア15および第2のVDD, VSSペア17が配設されている。

10

20

30

40

50

**【0061】**

第1のVDD, VSSペア15は、M4層に設けられたVDD電源線15aとVSS電源線15bとからなり、図面の左右方向にそれぞれ配設されている。第2のVDD, VSSペア17は、M5層に設けられたVDD電源線17aとVSS電源線17bとからなり、図面の上下方向にそれぞれ配設されている。

**【0062】**

上記第1, 第2のVDD, VSSペア15, 17のうち、図面の左右方向に配設された第1のVDD, VSSペア15の下には、たとえば図1に示した構成の配線素子ブロック21がそれぞれ埋め込まれている。つまり、M1層, M2層, M3層の3層を配線層として用いた配線素子ブロック21が、20個ずつ（全部で100個）埋め込まれている。

10

**【0063】**

一方、図面の上下方向に配設された第2のVDD, VSSペア17の下には、それぞれ、図示していないM1層, M2層, M3層, M4層の4層を配線層として用いた配線素子ブロック31が、20個ずつ（全部で100個）埋め込まれている。

**【0064】**

図面に示したように、 $100 * 100 \mu m$ 角サイズのPwグリッドを、 $20 * 20 mm$ 角サイズの半導体チップ11の全体に布設してなる場合、Pwグリッドの下に配線素子ブロック21, 31をそれぞれ埋め込むことにより、VDD, VSS電源線間にトータルで $200 nF$ のデカップリング容量を形成できる。この場合のデカップリング容量のCR時定数は $1 p s$ 以下であり、高速な電流ノイズ、容量結合ノイズを容易に吸収することが可能である。

20

**【0065】**

なお、本実施形態においては、第1のVDD, VSSペア15の形成にM5層を用い、第2のVDD, VSSペア17の形成にM4層を用いるようにすることにより、第1のVDD, VSSペア15の下に、配線素子ブロック31を埋め込むことも可能である。

**【0066】**

また、配線素子ブロック21, 31の平面サイズを $20 \mu m$ 角とした場合、そのCR時定数は $1 p s$ 以下であり、デカップリング容量として用いる場合を考えると十分すぎる応答速度である。しかしながら、このサイズに縛られるものではなく、たとえば、 $10 GHz$ のクロック応答に対応するには約 $100 GHz$ の応答特性が必要であり、そのためには $50 \mu m$ 角程度まで大きくしても問題はない。ただし、上記CR時定数は $0.13 \mu m$ レベルのCMOSプロセスを仮定して計算したものであり、技術レベルによって変化することは公知の事実である。

30

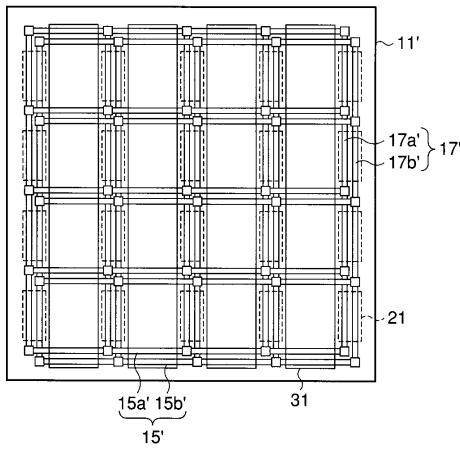

**【0067】****(第5の実施形態)**

図9は、本発明の第5の実施形態にかかり、多層配線装置（多層配線構造の配線素子ブロック）の配置例を示すものである。ここでは、 $20 * 20 mm$ 角のサイズを有する半導体チップの、その全面に、本発明の配線素子ブロックを埋め込んだ場合を例に説明する。

**【0068】**

たとえば、 $20 * 20 mm$ 角サイズの半導体チップ11'において、上層側のM4層, M5層が電源グリッドとして用いられる場合、 $100 * 100 \mu m$ 角サイズのPwグリッドが布設されたグリッド辺には、それぞれ、第1のVDD, VSSペア15'および第2のVDD, VSSペア17'が配設されている。

40

**【0069】**

第1のVDD, VSSペア15'は、M5層に設けられたVDD電源線15a'、とVSS電源線15b'、とからなり、図面の左右方向にそれぞれ配設されている。第2のVDD, VSSペア17'は、M4層に設けられたVDD電源線17a'、とVSS電源線17b'、とからなり、図面の上下方向にそれぞれ配設されている。

**【0070】**

上記第1, 第2のVDD, VSSペア15', 17'のうち、図面の上下方向に配設さ

50

れた第2のVDD, VSSペア17'の下には、それぞれ、たとえば図1に示した構成の配線素子ブロック21が、20個ずつ（全部で100個）埋め込まれている。

#### 【0071】

一方、図面の左右方向に配設された第1のVDD, VSSペア15'を含む、図面の上下方向に対応する、上記第2のVDD, VSSペア17'の相互間（図8の配線領域13に相当）の下には、それぞれ、図示していないM1層, M2層, M3層, M4層の4層を配線層として用いた配線素子ブロック31が、100個ずつ（全部で400個）埋め込まれている。

#### 【0072】

図面に示したように、 $100 * 100 \mu m$ 角サイズのPwグリッドを、 $20 * 20 mm$ 角サイズの半導体チップ11'の全体に布設してなる場合、つまり、半導体チップ11'の全面に配線素子ブロック21, 31をそれぞれ埋め込むことにより、上記した第4の実施形態に比べて、デカップリング容量を大幅に増大できる。よって、電源電圧の変動を抑え、LSI回路の動作を極めて安定なものとすることが可能となる。

10

#### 【0073】

また、半導体チップ11'の全面に配線素子ブロック21, 31をそれぞれ埋め込むようにした場合、CMP（Chemical Mechanical Polishing）技術において、配線層を形成する際に膜厚の均一性を保つために、微細な長方形形状の配線パターン（ダミーパターン）を配線の密度の少ない領域に敷き詰めるといった処理が必要になる。これにより、配線信号伝達性能の劣化や配線マスク設計の設定ミスなどの問題をも解消できる。また、プロセスの均一性の向上や静電破壊に対する耐性の向上などにとっても有効である。

20

#### 【0074】

なお、本実施形態においては、第1のVDD, VSSペア15'の形成にM4層を用い、第2のVDD, VSSペア17'の形成にM5層を用いるようにすることにより、図面の左右方向に、配線素子ブロック31を埋め込むことも可能であり、いずれの場合も、配線層の数が多い配線素子ブロック31をより多く配置した方が、デカップリング容量を増大させるのには都合（効率）がよい。

#### 【0075】

##### （第6の実施形態）

30

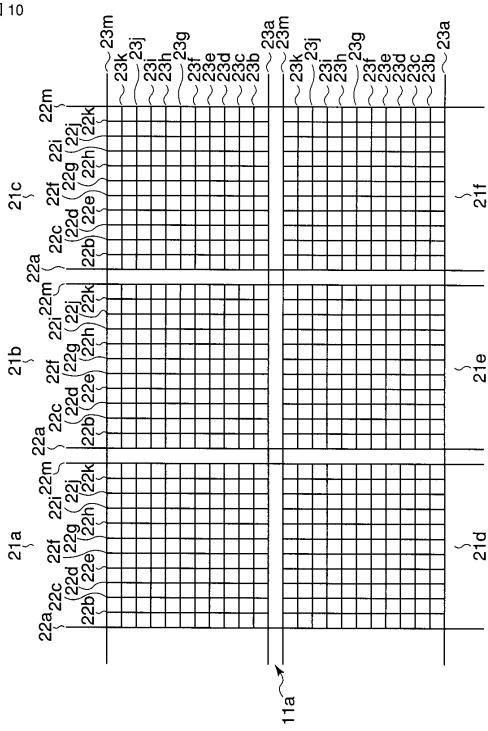

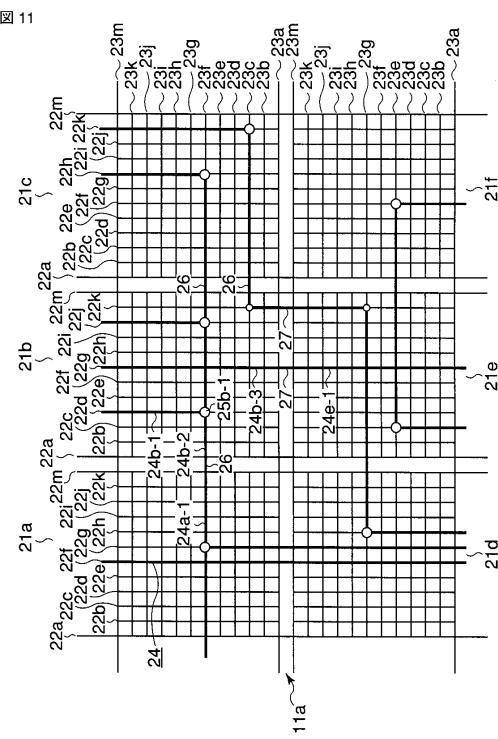

図10, 図11は、本発明の第6の実施形態にかかり、多層配線装置（多層配線構造の配線素子ブロック）の配線方法について示すものである。ここでは、6個の配線素子ブロックが、互いに重なり合わないようにして敷き詰められている場合を例に説明する。なお、図10はVDD, VSS電位の供給にかかる多層配線装置の基本構造を示すものであり、図11は図10に示した構成の多層配線装置に対する信号線の布設例を示すものである。

#### 【0076】

図10において、6個の配線素子ブロック21a, 21b, ..., 21fは、半導体チップ11a上の布設可能な領域（たとえば、電源配線領域、回路ブロック間信号配線領域）に、マトリクス（碁盤の目）状に配置されている。

40

#### 【0077】

各配線素子ブロック21a, 21b, ..., 21fは、図面の左右方向にそれぞれピッチ配列された、たとえばM3層（n層）からなる、12（p(i), i = 1 ~ k）本の配線22a, 22b, 22c, 22d, 22e, 22f, 22g, 22h, 22i, 22j, 22k, 22mを有するとともに、図面の上下方向にそれぞれピッチ配列された、たとえばM2層（n - 1層）からなる、12本の配線23a, 23b, 23c, 23d, 23e, 23f, 23g, 23h, 23i, 23j, 23k, 23mを有している。

#### 【0078】

各配線素子ブロック21a, 21b, ..., 21fは、各層の最外側の配線（第1, 第2の電位配線）が、共通のVSS配線（第2の電源線）22a, 23aまたは共通のVDD

50

配線（第1の電源線）22m, 23mに接続されている。この例の場合、VSS配線22aおよびVDD配線22mがM3層により、VSS配線23aおよびVDD配線23mがM2層により、それぞれ布設されている。

#### 【0079】

12本の配線22a, 22b, 22c, 22d, 22e, 22f, 22g, 22h, 22i, 22j, 22k, 22mのうち、上記VSS配線22aおよび上記VDD配線22mを除く、配線22b, 22c, 22d, 22e, 22f, 22g, 22h, 22i, 22j, 22kは、信号線としても利用できる信号配線(s(j)本(s(j)p(i)-2, j=1~k))として割り当てられている。信号配線22b, 22d, 22f, 22h, 22jはそれぞれVDD電位に設定され、信号配線22c, 22e, 22g, 22i, 22kはそれぞれVSS電位に設定されている。10

#### 【0080】

同様に、12本の配線23a, 23b, 23c, 23d, 23e, 23f, 23g, 23h, 23i, 23j, 23k, 23mのうち、上記VSS配線23aおよび上記VDD配線23mを除く、配線23b, 23c, 23d, 23e, 23f, 23g, 23h, 23i, 23j, 23kは、信号線としても利用できる信号配線(s(j)本(s(j)p(i)-2, j=1~k))として割り当てられている。信号配線23b, 23d, 23f, 23h, 23jはそれぞれVDD電位に設定され、信号配線23c, 23e, 23g, 23i, 23kはそれぞれVSS電位に設定されている。20

#### 【0081】

このように、各配線ブロック21a, 21b, ..., 21f内では、隣り合う配線にVDD, VSS電位が供給されて、並走配線間容量によるVDD, VSSデカップリング容量が形成されている。VDD, VSSデカップリング容量を大きくするには、各層の配線を最小ピッチで配列するのが望ましい。配線間容量が最も大きくなるからである。20

#### 【0082】

一方、図10に示した構成の多層配線装置において、信号線（図示太線）24を布設する場合、たとえば図11に示すように、同一ブロック内の配線の接続は、M2層, M3層間にブロック内接続Vi a（コントラクト配線）を設けることで実現する。たとえば、配線素子ブロック21b内の配線24b-1, 24b-2は、上下に位置するM2層, M3層間にブロック内接続Vi a（コントラクト配線）25b-1を設けることにより、相互に接続される。30

#### 【0083】

また、隣接ブロック（図面の左右方向に隣接するブロック）間での配線の接続は、両ブロック間にブロック間接続配線（M2層）26を設けることで実現する。たとえば、配線素子ブロック21bの配線24b-2と配線素子ブロック21aの配線24a-1とは、両ブロック21a, 21b間にブロック間接続配線26を設けることにより、相互が接続される。

#### 【0084】

同様に、隣接ブロック（図面の上下方向に隣接するブロック）間での配線の接続は、両ブロック間にブロック間接続配線（M3層）27を設けることで実現する。たとえば、配線素子ブロック21bの配線24b-3と配線素子ブロック21eの配線24e-1とは、両ブロック21b, 21e間にブロック間接続配線27を設けることにより、相互が接続される。40

#### 【0085】

なお、この場合、各配線素子ブロック21a, 21b, ..., 21fにおいて、信号線24として用いられる配線は、全て、VDDまたはVSS電位を供給するためのスルーホールコンタクトがあらかじめ削除されている（図3参照）。すなわち、先に述べたように、たとえば配線素子ブロック21bにおいては、信号線24b(24b-1, 24b-2, ...)として用いられる配線22d, 22g, 22j, 22k, 23c, 23fに対する、VDD, VSS電位の供給がはずされている。50

**【 0 0 8 6 】**

上記ブロック内接続 V i a 2 5 b -1および上記ブロック間接続配線 2 6 , 2 7 としては、低抵抗な導電材料が用いられる。または、高抵抗状態から低抵抗状態へとプログラム可能なヒューズ材料を用いることも可能である。

**【 0 0 8 7 】**

このような構成によれば、単に、大きなデカップリング容量を持つ多層配線装置を、半導体チップ 1 1 a 上の電源配線領域、回路ブロック間信号配線領域に配置できるだけでなく、任意の信号線 2 4 を高い自由度を持って引き回すことが容易に可能となる。

**【 0 0 8 8 】**

しかも、任意の信号線 2 4 の近傍には、V D D , V S S 電位が給電された配線を存在させることが容易に可能となる。すなわち、信号線 2 4 に近接させて、V D D , V S S 電位が給電された配線を配置するようとする。こうすることにより、V D D , V S S 電位が給電された配線を電磁界シールドとして働かせることができるとなる。このため、信号線 2 4 に対する電磁界ノイズの混入が少なくなり、シグナルインテグリティ（信号品質）を飛躍的に向上できるという大きな利点がある。したがって、ノイズによる誤動作が極めて少ない自動配線接続アルゴリズムの実現に好適である。10

**【 0 0 8 9 】**

また、コンタクトの位置を変えることによって、配線接続経路を任意に変更できるので、特に、A S I C ビジネスでの設計期間の短縮などに有効である。

**【 0 0 9 0 】**

本実施形態の場合、同一ブロック内において、信号線として割り当てられた配線は電気的につながっているので、基本的に一つの信号線路としてしか利用できない。この点、従来の配線方法と比べて配線密度が小さくなるという欠点がある。しかし、ブロック内の任意の場所で配線を切断する（電気的に絶縁する）手段を加えることによって、この欠点も容易に解決できる。20

**【 0 0 9 1 】**

また、M 2 層 , M 3 層を用いた場合を例に説明したが、これに限らず、たとえば 3 層以上の多層配線構造を有する多層配線装置の場合にも同様に実施することが可能である。

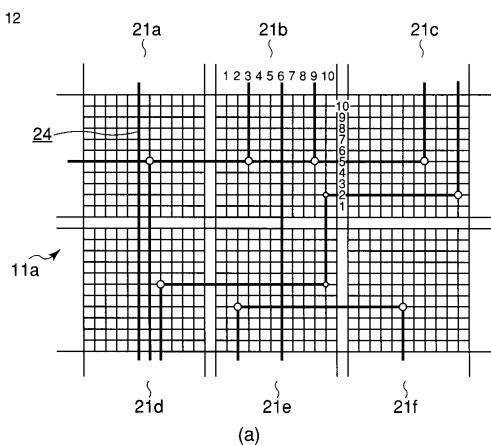

**【 0 0 9 2 】****( 第 7 の 実 施 形 態 )**

30

図 1 2 は、本発明の第 7 の実施形態にかかり、多層配線装置の配線特性解析・予測方法について示すものである。

**【 0 0 9 3 】**

同図 ( a ) は、図 1 1 に示した多層配線装置に対する信号線の布設例であり、たとえば配線素子ブロック 2 1 b は、図面の左右 ( X ) 方向にピッチ配列された、1 2 本の配線 2 2 a , 2 2 b , 2 2 c , 2 2 d , 2 2 e , 2 2 f , 2 2 g , 2 2 h , 2 2 i , 2 2 j , 2 2 k , 2 2 m と、図面の上下 ( Y ) 方向にピッチ配列された、1 2 本の配線 2 3 a , 2 3 b , 2 3 c , 2 3 d , 2 3 e , 2 3 f , 2 3 g , 2 3 h , 2 3 i , 2 3 j , 2 3 k , 2 3 m とを有している。したがって、たとえ全ての配線 ( V S S 配線 2 2 a , 2 3 a および V D D 配線 2 2 m , 2 3 m を除く ) が信号線として利用される場合でも、配線素子ブロック 2 1 b は 4 0 個の端子を持った基本ブロックとなる。40

**【 0 0 9 4 】**

同図 ( b ) は、同図 ( a ) より求められる、配線素子ブロック 2 1 b についての特性ライブラリの一例を示すものである。ここでは、X 方向の配線 2 2 b ~ 2 2 k および Y 方向の配線 2 3 b ~ 2 3 k を、それぞれ、X 値 1 ~ 1 0 , Y 値 1 ~ 1 0 に割り付けている。

**【 0 0 9 5 】**

また、信号伝達関数（入出力信号伝播特性）として、ここでは伝送特性（ディレイ値）をとっている。信号伝達関数としては、他に S パラメータなどを使うこともできる。

**【 0 0 9 6 】**

すなわち、4 0 個の端子間の信号伝達関数をあらゆる組み合わせについてあらかじめ計50

算し、その結果を、配線セルを中心としたライブラリとして管理する。これにより、任意のブロック間に布設した配線の特性は、このライブラリを参照しつつ、配線接続経路に応じた単純四則演算を行うことによって正確に予測することが可能となる。

#### 【 0 0 9 7 】

なお、特性ライブラリとしては、この形態に限らず、他の形態とすることも可能である。

#### 【 0 0 9 8 】

上述したように、いずれの実施形態においても、上下に位置する各配線層の配線方向は互いに直交する形で示されているが、平行でなければよく、必ずしも直交する方向に限定されるものではない。

10

#### 【 0 0 9 9 】

また、各配線層の最外側に V D D , V S S 配線を設置したが、これに限らず、たとえば上下に位置する全ての信号配線とクロスする配線を V D D , V S S 配線として設置することができる。

#### 【 0 1 0 0 】

また、この多層配線装置にあっては、たとえば、V D D , V S S 電源以外の信号線間に接続することによって、大きな容量値をもち、高周波特性に優れた容量素子としても使用できる。特に、アナログ回路における帰還容量として用いたり、スイッチトキャパシタ回路の容量素子として用いたりすることもできる。また、デジタル回路の電圧昇圧用容量などとして利用することも可能である。

20

#### 【 0 1 0 1 】

その他、本願発明は、上記（各）実施形態に限定されるものではなく、実施段階ではその要旨を逸脱しない範囲で種々に変形することが可能である。さらに、上記（各）実施形態には種々の段階の発明が含まれており、開示される複数の構成要件における適宜な組み合わせにより種々の発明が抽出され得る。たとえば、（各）実施形態に示される全構成要件からいくつかの構成要件が削除されても、発明が解決しようとする課題の欄で述べた課題（の少なくとも 1 つ）が解決でき、発明の効果の欄で述べられている効果（の少なくとも 1 つ）が得られる場合には、その構成要件が削除された構成が発明として抽出され得る。

30

#### 【 符号の説明 】

#### 【 0 1 0 2 】

M 1 ~ M 3 ... 配線層 (M 1 層, M 2 層, M 3 層)

M 1 a , M 1 b , ... , M 1 h ... 配線

M 2 a , M 2 b , ... , M 2 f ... 配線

M 3 a , M 3 b , ... , M 3 h ... 配線

V i a - 1 a a , - 1 a b ... スルーホールコンタクト

V i a - 1 b a , - 1 b b , ... , - 1 b j ... スルーホールコンタクト

V i a - 2 a a , - 2 a b ... スルーホールコンタクト

V i a - 2 b a , - 2 b b , ... , - 2 b j ... スルーホールコンタクト

1 1 , 1 1 ' , 1 1 a ... 半導体チップ

40

1 3 ... 配線領域

1 5 , 1 5 ' ... 第 1 の V D D , V S S ペア

1 5 a , 1 5 a ' ... V D D 電源線

1 5 b , 1 5 b ' ... V S S 電源線

1 7 , 1 7 ' ... 第 2 の V D D , V S S ペア

1 7 a , 1 7 a ' ... V D D 電源線

1 7 b , 1 7 b ' ... V S S 電源線

2 1 , 2 1 a , 2 1 b , ... , 2 1 f ... 配線素子ブロック

2 2 a ... V S S 配線

2 2 b , 2 2 c , 2 2 d , 2 2 e , 2 2 f , 2 2 g , 2 2 h , 2 2 i , 2 2 j , 2 2 k

50

...配線

2 2 m ... V D D 配線

2 3 a ... V S S 配線

2 3 b , 2 3 c , 2 3 d , 2 3 e , 2 3 f , 2 3 g , 2 3 h , 2 3 i , 2 3 j , 2 3 k

...配線

2 3 m ... V D D 配線

2 4 , 2 4 b ... 信号線

2 4 a -1 , 2 4 b -1 , 2 4 b -2 , 2 4 b -3 , 2 4 e -1 ... 配線

2 5 b -1 ... ブロック内接続 V i a

2 6 , 2 7 ... ブロック間接続配線

3 1 ... 配線素子ブロック

10

【図 1】

図 1

【図 2】

図 2

【 义 3 】

【 四 4 】

【図5】

【図6】

【図7】

図7

【図8】

図8

【図9】

図9

【図10】

図10

【図11】

【図12】

| X  | Y | X | Capacitor     | Resistor                       | 伝送特性( $\tau$ )                                 |

|----|---|---|---------------|--------------------------------|------------------------------------------------|

| 1  |   |   |               |                                |                                                |

| 2  |   |   |               |                                |                                                |

| 3  | 5 | 9 | $C3x=C5y=C9y$ | $R3x5y, R3x9x$<br>$R3y9x, R5y$ | $\tau 3x5y, \tau 3x9x$<br>$\tau 5y9x, \tau 5y$ |

| 4  |   |   |               |                                |                                                |

| 5  |   |   |               |                                |                                                |

| 6  | 6 |   | $C6x$         | $R6x$                          | $\tau 6x$                                      |

| 7  |   |   |               |                                |                                                |

| 8  |   |   |               |                                |                                                |

| 9  |   |   |               |                                |                                                |

| 10 | 2 |   | $C10x=C2y$    | $R10x2y$                       | $\tau 10x2y$                                   |

(b)

---

フロントページの続き

(51)Int.Cl. F I

H 01 L 23/522 (2006.01)

(72)発明者 増田 弘生

東京都あきる野市草花 2098-113

審査官 平野 崇

(56)参考文献 特開2001-250917 (JP, A)

特開平08-316323 (JP, A)

特開2000-252428 (JP, A)

特開2001-127162 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 21/822

H 01 L 21/3205

H 01 L 21/768

H 01 L 21/82

H 01 L 23/522

H 01 L 27/04

C i N i i

J S T P l u s ( J D r e a m I I )