(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4056500号

(P4056500)

(45) 発行日 平成20年3月5日(2008.3.5)

(24) 登録日 平成19年12月21日(2007.12.21)

(51) Int.Cl.

F 1

H01P 3/02 (2006.01)

H01P 3/02

H01L 23/12 (2006.01)

H01L 23/12

H01P 1/22 (2006.01)

H01P 1/22

3 O 1 Z

請求項の数 7 (全 16 頁)

(21) 出願番号

特願2004-190315 (P2004-190315)

(22) 出願日

平成16年6月28日 (2004.6.28)

(65) 公開番号

特開2006-14088 (P2006-14088A)

(43) 公開日

平成18年1月12日 (2006.1.12)

審査請求日

平成17年12月20日 (2005.12.20)

(73) 特許権者 000006013

三菱電機株式会社

東京都千代田区丸の内二丁目7番3号

(74) 代理人 100089118

弁理士 酒井 宏明

(72) 発明者 鈴木 拓也

東京都千代田区丸の内二丁目2番3号 三菱電機株式会社内

(72) 発明者 古屋 輝雄

東京都千代田区丸の内二丁目2番3号 三菱電機株式会社内

審査官 藤井 浩

最終頁に続く

(54) 【発明の名称】 伝送線路基板および半導体パッケージ

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体デバイスに入出力される駆動制御信号を伝送する伝送線路基板において、前記半導体デバイスに接続される信号線路を2つの等位相の信号線路に分配する分配器と、

前記分配された信号線路の一方につながり、マイクロ波帯及びミリ波帯の不要波の基板内実効波長の略1/2の長さを有する信号線路を有する遅延器と、

前記遅延器および前記分配された信号線路の他方につながり、不要波が互いに逆位相となる平行の2つの信号線路を有する平行2線路と、

前記平行2線路上に配置され、平行の2つの信号線路間を接続する抵抗体と、

前記平行2線路の2つの信号線路を合成する合成器と、

を有する不要波抑制回路を備えることを特徴とする伝送線路基板。

## 【請求項 2】

前記分配器、遅延器、平行2線路および合成器は、上下の接地導体層間に信号線路が形成されるトリプレート線路により構成されることを特徴とする請求項1に記載の伝送線路基板。

## 【請求項 3】

前記不要波抑制回路を複数個、縦続接続し、前記複数の不要波抑制回路の各遅延器の信号線路の長さを、異なる周波数を持つ複数の不要波の基板内実効波長の略1/2となるように、それぞれ異ならせたことを特徴とする請求項1または2に記載の伝送線路基板。

10

20

**【請求項 4】**

前記信号線路が不要波の基板内実効波長の $1/4$ 以下の間隔で配置される複数のグランドビアで囲まれていることを特徴とする請求項1～3のいずれか一つに記載の伝送線路基板。

**【請求項 5】**

1～複数の半導体デバイスを収容するために用いられ、請求項1～4のいずれか一つに記載の伝送線路基板を、前記半導体デバイスの駆動制御信号端子と外部端子との接続経路に設けたことを特徴とする半導体パッケージ。

**【請求項 6】**

1～複数の半導体デバイスと、 10

請求項1～4のいずれか一つに記載の伝送線路基板と、

を備え、該伝送線路基板を、前記半導体デバイスの駆動制御信号端子と外部端子との接続経路に設けたことを特徴とする半導体パッケージ。

**【請求項 7】**

半導体デバイスに入出力される駆動制御信号を伝送する伝送線路基板において、

前記半導体デバイスに接続される信号線路を2つの等位相の信号線路に分配する分配器と、

前記分配された信号線路の一方につながり、マイクロ波帯及びミリ波帯の不要波の基板内実効波長の略 $1/2$ の長さを有する信号線路を有する遅延器と、

前記遅延器および前記分配された信号線路の他方につながり、不要波が互いに逆位相となる平行の2つの信号線路を有する平行2線路と、 20

前記平行2線路上に配置され、平行の2つの信号線路間を接続する抵抗体と、

前記平行2線路の2つの信号線路を等位相で合成する合成器と、

を有する不要波抑制回路を備えることを特徴とする伝送線路基板。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、マイクロ波帯またはミリ波帯などの高周波帯で動作する半導体デバイスに対し入出力する信号を伝送する伝送線路基板および半導体パッケージに関し、さらに詳しくは半導体デバイスで発生される高周波信号のパッケージ外部への漏洩を効率よく抑止することが可能な伝送線路基板および半導体パッケージに関するものである。 30

**【背景技術】****【0002】**

マイクロ波帯またはミリ波帯などの高周波帯で動作する半導体デバイスが搭載される高周波パッケージにおいては、高周波パッケージに形成された外部端子と半導体デバイスの入出力端子との間を多層誘電体基板内に形成された表層信号線路や内層信号線路によって接続している。これらの線路によって、所望の高周波信号を入出力する他、半導体デバイスに対しDCバイアス電圧、制御信号などを入出力するようにしている。

**【0003】**

高周波パッケージ内において、高周波帯で動作する半導体デバイスは、その周りが、カバー、シーリング、接地導体面などにより遮蔽されているが、半導体デバイスの入出力端子から伝導的に漏洩する不要波としての高周波信号（不要信号）が、DCバイアス電圧や制御信号等の入出力用の信号線路を介して外部に放射されるという問題がある。このため、この種の高周波パッケージにおいては、各種の電波法のEMI規格を満足するのが非常に困難な状況下にある。 40

**【0004】**

このような高周波パッケージが含まれる機器モジュール全体を金属カバーで覆うことも考えられるが、この場合は、高価な筐体等が必要となるため、低コスト化のためにも、高周波パッケージ内で、上記のEMI規格を満足するような対策が望まれる。

**【0005】**

特許文献 1 では、誘電体基板の表面に、高周波部品搭載部と、高周波部品の高周波端子と接続される高周波用伝送回路と、高周波部品の電源端子と接続される電源回路とが形成された配線基板において、電源回路の中の電源線路やビアホール導体を、比透磁率が 80 以上、電気抵抗率が  $1.0 (\mu \text{m})$  以下、Fe、Co、Ni の少なくとも 1 種を含有する高透磁率低抵抗体で形成することによって、不要高周波信号を吸収するようにした従来技術が開示されている。

#### 【0006】

【特許文献 1】特開 2004 - 39739 号公報

#### 【発明の開示】

##### 【発明が解決しようとする課題】

10

#### 【0007】

上記従来技術の場合、内層信号線路に直列に抵抗体を接続していることと等価であり、内層信号線路を伝搬する不要波のみを減衰、吸収するという対処がなされていないので、内層信号線路を介して DC バイアスを通過させる場合、少なからず電圧降下が発生して、DC バイアスの伝送特性に悪影響を与えるという問題もある。

#### 【0008】

本発明は、上記に鑑みてなされたものであって、外部への不要波成分の漏洩を高周波パッケージ内で抑止することができるとともに、必要な DC バイアス電圧、制御信号あるいは中間周波数信号などの伝送特性に悪影響を与えることなく、不要波を効率よく電力減衰、吸収することが可能な伝送線路基板および半導体パッケージを得ることを目的とする。

20

#### 【課題を解決するための手段】

#### 【0009】

上述した課題を解決し、目的を達成するために、本発明は、半導体デバイスに入出力される信号を伝送する伝送線路基板において、前記半導体デバイスに接続される信号線路を 2 つの等位相の信号線路に分配する分配器と、前記分配された信号線路の一方につながり、不要波の基板内実効波長の略  $1/2$  の長さを有する信号線路を有する遅延器と、前記遅延器および前記分配された信号線路の他方につながり、不要波が互いに逆位相となる平行の 2 つの信号線路を有する平行 2 線路と、前記平行 2 線路上に配置され、平行の 2 つの信号線路間を接続する抵抗体と、前記平行 2 線路の 2 つの信号線路を合成する信号線路を有し、合成信号を外部に出力する合成器とを有する不要波抑制回路を備えることを特徴とする。

30

#### 【0010】

この発明では、遅延器によって平行 2 線路上を伝送する不要波を逆位相とすることにより、平行 2 線路間に電界を形成し、抵抗体を平行 2 線路上で前記電界方向に平行に設けている。

#### 【発明の効果】

#### 【0011】

この発明によれば、遅延器によって平行 2 線路上を伝送する不要波を逆位相とすることにより、平行 2 線路間に電界を形成し、抵抗体を平行 2 線路上で前記電界方向に平行に設けているので、DC バイアス電圧、制御信号あるいは中間周波数信号などの駆動制御信号の伝送特性に悪影響を与えることなく、不要波帯域のみに対して電圧降下を発生させ、不要波帯域のみを効率よく減衰、吸収させることが可能となる。

40

#### 【発明を実施するための最良の形態】

#### 【0012】

以下に、本発明にかかる伝送線路基板及び半導体パッケージの実施の形態を図面に基づいて詳細に説明する。なお、この実施の形態によりこの発明が限定されるものではない。

#### 【0013】

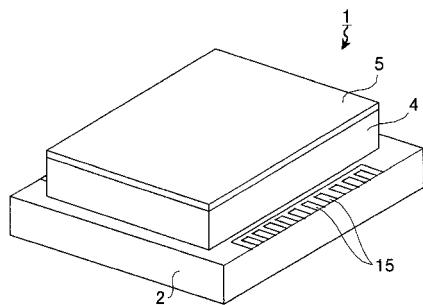

実施の形態 1.

図 1 ~ 図 3 はこの発明にかかる半導体パッケージ 1 を示すものである。この発明は、任意の周波数帯で動作する半導体デバイス(半導体 I C)が搭載された半導体パッケージに

50

適用可能であるが、ここではマイクロ波帯、ミリ波帯などの高周波帯で動作する複数の高周波半導体デバイス（M M I C、以下高周波デバイスと略す）が搭載される半導体パッケージ（以下、高周波パッケージという）1に本発明を適用した場合を示している。半導体パッケージ1は、例えば、F M - C W レーダに適用して好適である。

#### 【0014】

なお、F M - C W レーダは、周知のように、前方に向けて放射した電波が目標物（先行車両）にあたって反射してくる受信波と送信波との差からビート周波数を求め、そのビート周波数を使って目標までの距離および相対速度を算出するものである。

#### 【0015】

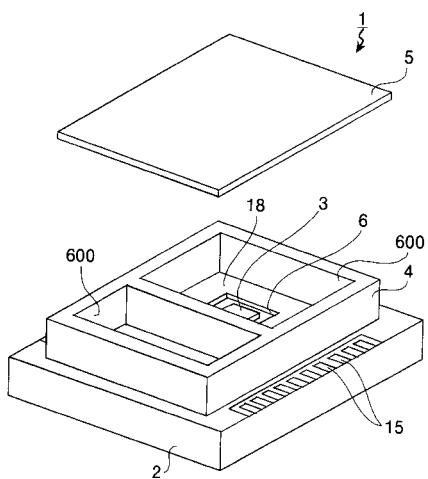

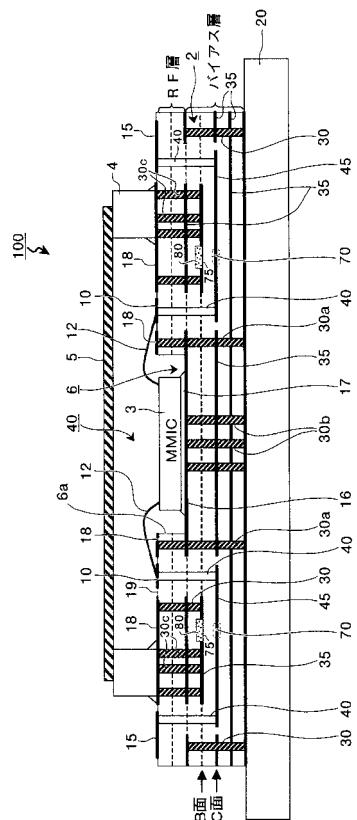

図1～図3に示す高周波パッケージ1では、接地されている金属製のキャリア20（図4参照）上に、多層誘電体基板2が搭載されている。多層誘電体基板2上には、金属製の枠形状のシールリング4が気密性を有してハンダや銀ろうなどのろう材で接合され、さらにシールリング4上には蓋体としてのカバー5が溶接接合されている。図1の例ではシールリング4として、2つの貫通穴（600）が設けられた日の字型の枠体を示している。

#### 【0016】

シールリング4およびカバー5の接合によって、多層誘電体基板2上に設けられた複数の高周波デバイス3は気密封止される。また、シールリング4およびカバー5は、多層誘電体基板2上に設けられた複数の高周波デバイス3から外部への不要放射をシールドする。すなわち、シールリング4およびカバー5によって、多層誘電体基板2の表層の一部および高周波デバイス3を覆う電磁シールド部材を構成している。なお、電磁シールドの構成は、この限りではなく、多層誘電体基板2の表面や内層に設けられた後述する接地導体や接地された複数のピア等の他、様々な構成要素が含まれる。

#### 【0017】

図2、図3に示すように、多層誘電体基板2上には、高周波デバイス3を搭載するための1～複数の凹部（以下、I C搭載凹部という）6が形成されている。I C搭載凹部は多層誘電体基板2の上位層にキャビティ（空洞）を形成し、キャビティはI C搭載凹部6の側壁6aによって囲まれる。I C搭載凹部の底面（キャビティ底面）には、その表面に接地導体16が形成されている。I C搭載凹部6上には、電圧制御発振器（VCO）、増幅器、電力分配器、遅倍器、ミクサなどの複数の高周波デバイス3が収容され、高周波デバイス3は接地導体16にハンダやろう材あるいは樹脂接着剤等の接合材17で接合されている。

#### 【0018】

また、図3に示すように、シールリング4の2つの貫通穴600の内側には、それぞれI C搭載凹部6が配置されている。各I C搭載凹部6には複数の高周波デバイス3が配置されている。シールリング4の2つの貫通穴600を画成するシールリング4'の下部には、フィードスルーブル7が設けられている。すなわち、上側のI C搭載凹部6に収容された高周波デバイス3と下側のI C搭載凹部6に収容された高周波デバイス3との間は、フィードスルーブル7およびマイクロストリップ線路8によって接続されている。フィードスルーブル7は、信号ピンあるいはマイクロストリップ線路を誘電体で覆うように構成され、これにより各I C搭載凹部6では気密状態を保持したまま、2つのI C搭載凹部6間で高周波信号が伝送される。マイクロストリップ線路8は多層誘電体基板2の表層に配置され、フィードスルーブル7に接続されている。高周波デバイス3に設けられた導体パッドとマイクロストリップ線路8とは、ワイヤ1200によって、ワイヤボンディング接続されている。

#### 【0019】

多層誘電体基板2の表層には、表層接地導体としての接地導体18が設けられグランド面で覆われている。接地導体18は、多層誘電体基板2におけるI C搭載凹部6の周囲に形成された複数のグランドピア（側壁グランドピアという）30aにより、半導体デバイス実装面の接地導体16と接続され、同電位となっている。これら側壁グランドピア30aの間隔は、不要波である高周波パッケージ1内にて使用する高周波信号の基板内実効波長gの1/2未満の値として設定しており、これによりI C搭載凹部6の側壁6aを介

10

20

30

40

50

した多層誘電体基板 2 内への不要波の進入を抑制し、上述したシールリング 4、カバー 5 とにより立体的に電磁シールドを形成している。

#### 【 0 0 2 0 】

シールリング 4 の内側の多層誘電体基板 2 の表層には、高周波デバイス 3 に DC バイアス電圧を供給したり、あるいは高周波デバイス 3 との間で制御信号（DC 領域に近い低周波信号）や高周波デバイス 3 から出力される IF 信号（中間周波数帯の信号）を入出力するための導体パッド（以下、内部導体パッドという）10 が設けられている。これら DC バイアス電圧、制御信号、IF 信号を総称して、高周波デバイス 3 の「駆動制御信号」ということにする。高周波デバイス 3 側にも、駆動制御信号入出力パッド 11（以下、導体パッド）が設けられている。内部導体パッド 10 と導体パッド 11 とは、金などで構成されるワイヤ 12 によってワイヤボンディング接続されている。なお、ワイヤ 12 による接続に代えて、金属バンプあるいはリボンによってこれらの接続をとるようにしてよい。10

#### 【 0 0 2 1 】

シールリング 4 の外側の多層誘電体基板 2 上には、外部端子としての複数の導体パッド（以下、外部導体パッドという）15 が設けられている。外部導体パッド 15 は、多層誘電体基板 2 内に形成された、後述する信号ビア（信号スルーホール）及び内層信号線路を介してシールリング 4 の内側の多層誘電体基板 2 上に設けられた内部導体パッド 10 と DC 的に接続されている。これらの外部導体パッド 15 は、ワイヤ等を介して、図示しない、電源回路基板、制御基板などに接続される。

#### 【 0 0 2 2 】

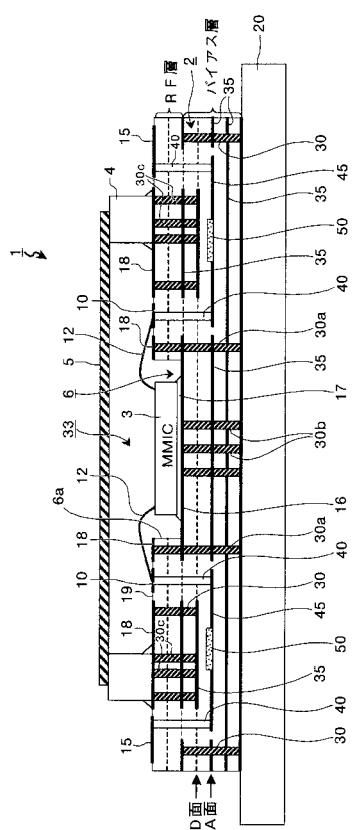

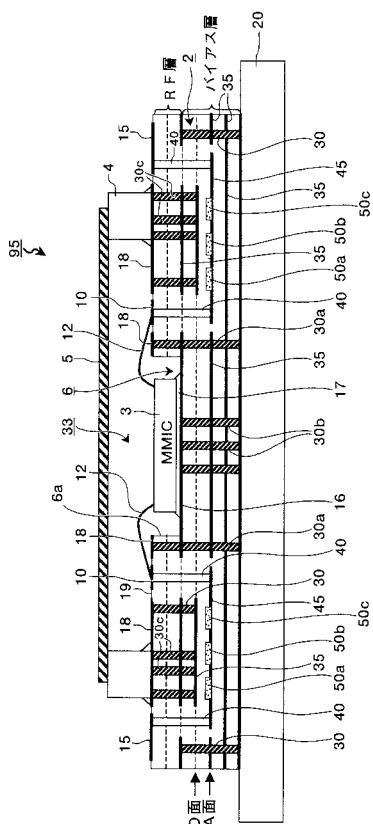

図 4 は、高周波パッケージ 1 の多層誘電体基板 2 内のビア構造（スルーホール構造）を示すものであり、多層誘電体基板 2 は、接地されている金属製のキャリア 20 に設けられている。図 4 においては、DC バイアス電圧、制御信号、IF 信号等の駆動制御信号が伝送される駆動制御信号用ビア（以下信号ビアという）40 は、白抜きで示し、グランドビア 30（30a, 30b, ...）はハッチング付きで示している。20

#### 【 0 0 2 3 】

この場合、多層誘電体基板 2 は第 1 層～第 6 層の 6 層構造を有しており、多層誘電体基板 2 の第 1 層および第 2 層の中央部が削除されることによって、前述の IC 搭載凹部 6 が形成されている。IC 搭載凹部 6 の底面、すなわち第 3 層の表面には、表層接地導体としてのグランド面 16 が形成されており、このグランド面 16 に半田 17（または導電性接着剤）を介して高周波デバイス 3 が搭載される。高周波デバイス 3 の下に配置されるグランド面 16 とキャリア 20 との間は、複数のグランドビア 30b で接続されており、これらのグランドビア 30b は放熱のためのサーマルビアの機能も有している。30

#### 【 0 0 2 4 】

IC 搭載凹部 6 の側壁（多層誘電体基板 2 の第 1 ～第 2 層の側壁面）6a は、この場合は、誘電体が露出された状態にある。しかし、前述したように、IC 搭載凹部 6 の周囲および内部導体パッド 10 には、複数の側壁グランドビア 30a が形成されており、これら側壁グランドビア 30a によって側壁 6a を介した多層誘電体基板 2 内への不要波の進入を抑制している。側壁グランドビア 30a は、多層誘電体基板 2 の第 1 層の表層に形成されたグランドパターン 18 とキャリア 20 とを接続している。多層誘電体基板 2 の第 1 層の表層には、複数の内部導体パッド 10 が設けられているが、これら内部導体パッド 10 の周囲の誘電体が露出された部分 19（図 3 参照）以外は、表層接地導体としてのグランドパターン 18 が形成されており、表層を介して多層誘電体基板 2 の内部に不要波が進入することを防止している。40

#### 【 0 0 2 5 】

前述したように、多層誘電体基板 2 上には、シールリング 4 が搭載され、さらにシールリング 4 上には蓋体としてのカバー 5 が設けられている。このように、多層誘電体基板 2 上における高周波デバイス 3 の実装エリアには、シールリング 4, カバー 5 などの電磁シールド部材によって気密のキャビティ 33 が形成されており、このキャビティ 33 は、シールリング 4, カバー 5 などの電磁シールド部材と、グランド面 16, グランドパターン

10

20

30

40

50

18などの表層接地導体と、複数の側壁グランドビア30aなどによって、電気的に外部と遮蔽されている。なお、複数の側壁グランドビア30aの代わりに、IC搭載凹部6の側壁6aをメタライズして側壁6aにグランド面を形成するようにしてもよい。

#### 【0026】

多層誘電体基板2のシールリング4の直下近傍には、高周波デバイス3から発生する不要波をシールドするための複数の（この場合3列）グランドビア（RFシールドビア）30cが設けられている。これらのグランドビア30, 30a, 30b, 30cは、表層接地導体、接地されたキャリア20、あるいは多層誘電体基板2の内層に形成される内層接地導体35に適宜接続されている。内層接地導体35は、基本的には、ベタグランド層として全ての層間に設けられている。

10

#### 【0027】

シールリング4の内側に配置される内部導体パッド10は、1～複数の信号ビア40および1～複数の内層信号線路45を介してシールリング4の外側に配置される外部導体パッド15と接続されている。図4では、明示されていないが、信号ビア40、内層信号線路45の周囲には、誘電体を挟んで複数のグランドビア30が配されており、これら複数のグランドビア30によるシールドによって、信号ビア40、内層信号線路45からの不要波の放射、周囲からの不要波の結合を抑制している。

#### 【0028】

しかし、導体パッド11は半導体デバイス3内のRF回路とDC的に接続されているため、半導体デバイス3内のRFチョーク回路（図示せず）で抑圧しきれない相当量の不要信号が漏洩する。この導体パッド11に対し、直接DC的に接続されるワイヤ12、内部導体パッド10、信号ビア40および内層信号線路45、外部導体パッド15を介して、高周波パッケージ1の外部にも不要信号が漏洩する。

20

#### 【0029】

また、露出された誘電体部分から多層誘電体基板内に進入して信号ビアや内層信号線路に結合する不要波も存在する。すなわち、上記のような誘電体基板内の不要波の放射・結合を抑圧するようなシールド構造においても、シールドされた空間内で半導体デバイス3から放射する不要波がひとたび内部導体パッドに結合してしまえば、DCバイアス線路は不要波の恰好のリーケ経路となってしまう。

#### 【0030】

30

そこで、実施の形態1においては、内層信号線路45の途中に、不要波抑制回路50を設けるようにしてあり、この不要波抑制回路50によって不要波を高効率で減衰、吸収させている。

#### 【0031】

この際、DCバイアスの伝送特性に悪影響を与えないように、内層信号線路45に直列に抵抗体を接続せずに、内層信号線路の上下層に接地導体層を形成し抵抗体を内層信号線路45に平行に接続する。具体的には、内層信号線路45の表面に抵抗体を塗布する。内層信号線路がトリプレート線路あるいはマイクロストリップ線路を構成する場合、通常は、接地導体層に向かう上下方向の電界が形成されることになる。この場合に、この上下方向に対して電界に垂直な面に抵抗体を形成すると、不要高周波信号の減衰、吸収効率が極めて悪くなる。このため、実施の形態1では、逆相信号の流れる平行2線路（結合差動線路）上に抵抗体を配置することによって、信号線路の電界方向に平行に抵抗体が配置されるようにしている。

40

#### 【0032】

なお、この図の例では、内層信号線路45は、誘電体を介して上下層の接地導体層35間に配されるように設けられており、これにより所謂トリプレート線路が構成されている。図4の場合は、第4層と第5層との間に内層信号線路45が設けられているので、内層信号線路45が形成されている位置に対応する第3層と第4層との間、第5層と第6層との間には、内層接地導体35が形成されている。

#### 【0033】

50

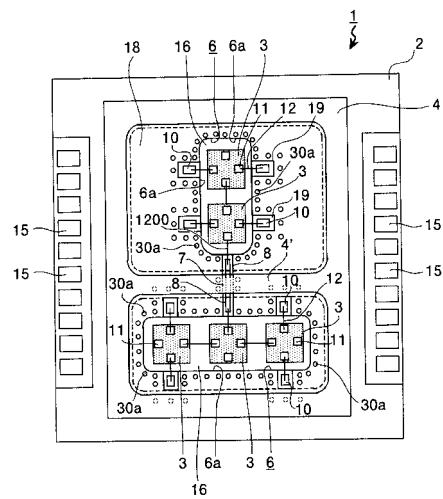

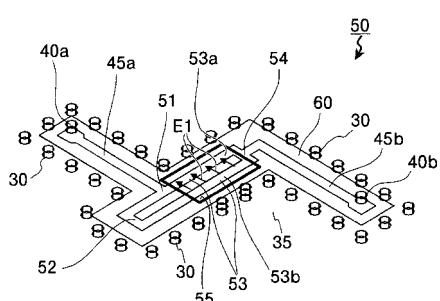

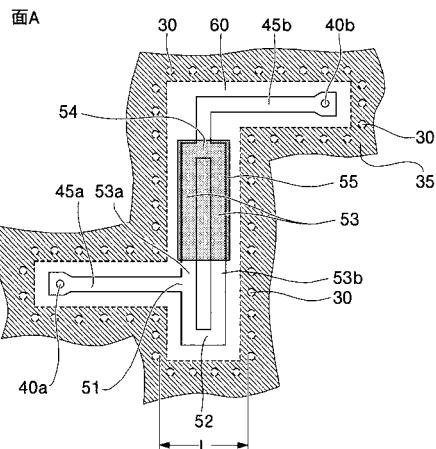

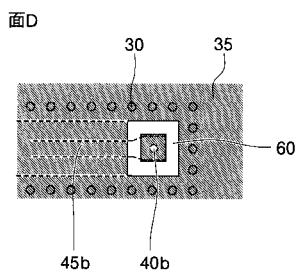

図5は不要波抑制回路50の構成例を示す斜視図である。図6-1は、図4に示す高周波パッケージ1において、多層誘電体基板2のA面（第4層と第5層との間）に配される不要波抑制回路50の構成を示す平面図であり、図6-2は多層誘電体基板2のD面（第3層と第4層との間）の状況を示すものである。

#### 【0034】

図5および図6-1において、一方の信号ビア40aが高周波デバイス3側の内部導体パッド10側に接続され、他方の信号ビア40bが外部導体パッド15側に接続されている。信号ビア40aに接続される内層信号線路45aと、信号ビア40bに接続される内層信号線路45bとの間に、不要波抑制回路50が形成されている。不要波抑制回路50は、分配器（T分岐）51と、遅延器52と、平行2線路53と、合成器54と、抵抗体（印刷抵抗）55とを備えている。信号ビア40a、40bの周囲には、誘電体60を挟んで複数のグランドビア30が配置されている。10

#### 【0035】

分配器（T分岐）51は、内層信号線路45aを2つの等位相の信号線路に分配する。遅延器は52は、分配器51で分配された信号線路の一方に形成され、不要波の基板内実効波長 $g$ の略 $1/2$ の長さを有する信号線路で構成される。平行2線路53は、2つの平行な信号線路53a, 53bから成り、一方の信号線路53aが分配器51で分配された線路につながり、他方の信号線路53bが遅延器52に接続されている。合成器54は、平行2線路53の2つの信号線路53a, 53bを合成する信号線路を有し、合成信号を外部導体パッド15側に出力する。抵抗体（印刷抵抗）55は、体積抵抗率が、0.0002~0.1(·m)の範囲の抵抗率を有し、平行2線路53上に配置され、2つの信号線路53a, 53b間を接続する。20

#### 【0036】

これら分配器51、遅延器52、平行2線路53および合成器54を構成する伝送線路は図の例では、トリプレート線路により構成されており、上下の内層接地導体35間に信号線路が形成されている。すなわち、図6-2に示すように、第3層と第4層との間（D面）と、第5層と第6層との間には、不要波抑制回路50を構成する内層信号線路に対応する箇所に、内層接地導体35が形成されている。また、分配器51、遅延器52、平行2線路53および合成器54を構成する伝送線路の周りには、誘電体60を挟んで複数のグランドビア30および内層接地導体35が配置されている。グランドビア30の隣接間隔は、不要波の基板内実効波長 $g$ の $1/4$ 以下に設定されており、また、対向するグランドビア30間の間隔 $L$ は、波長 $g$ の $1/2$ 以下に設定されている。30

#### 【0037】

遅延器52は、不要波の基板内実効波長 $g$ の略 $1/2$ の長さを有しているので、遅延器52において、不要波の位相は略 $g/2$ 遅延される。このため、不要波は、平行2線路53の2つの信号線路53a, 53bのうち、遅延器52を経由していない信号線路53aのほうが、遅延器52を経由している信号線路53bにくらべ、 $g/2$ だけ、位相が進むことになる。すなわち、平行2線路53において、不要波は逆相で結合されることになり、図5に示すように、信号線路53a, 53bは結合差動線路を構成して、信号線路53a, 53b間に電界E1が形成される。そして、この電界E1は、この逆相となる不要波の周波数帯（不要周波数帯）で、強度が最大となる。40

#### 【0038】

抵抗体55は平行2線路53上で2つの信号線路53a, 53b間を接続するように塗布されるので、抵抗体55は上記電界E1に平行に配置されることになる。このように、抵抗体55は、従来のように、電界に垂直に配置されるのではなく、平行2線路53間に故意に形成した電界E1に平行に配置されるとともに、平行2線路53間の電界E1を不要波の周波数で最大となるようにしたので、この不要周波数帯では、並行2線路間に生じた電位差に対し、直列に抵抗を入れた回路と等価となり、選択的に所望の不要周波数帯に対してのみ電圧降下を起こすことができる。すなわち、不要波の電力を抵抗体55で効率よく減衰、吸収させることが可能となる。50

## 【0039】

なお、前述したように、内層信号線路45は、トリプレート線路によって構成されているので、内層信号線路45から上下の内層接地導体35に対し上下方向の電界が形成されているが、不要波に関しては、位相制御により、平行2線路53間に形成される電界E1のほうが支配的であるので、不要波は抵抗体55で効率よく減衰、吸収されることとなる。また、遅延器の構成としては、上記の限りではなく、たとえば、多層基板の構造を生かした、信号ピアを含めて、不要波の基板内実効波長  $g$  の略  $1/2$  の長さを有する立体線路により構成しても良い。

## 【0040】

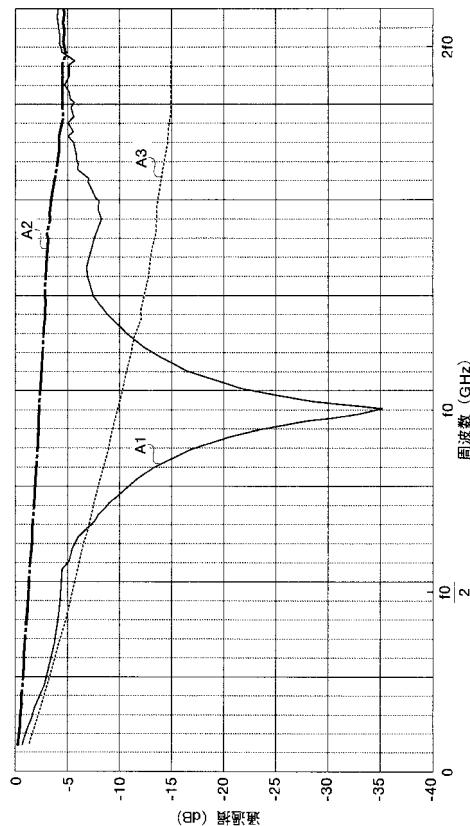

図7は、上記不要波抑制回路50の伝送特性を示すもので、実線(A1)が長さ(信号線伝送方向の長さ)1mmの抵抗体55を形成した場合の上記不要波抑制回路50の伝送特性を示し、一点鎖線(A2)が内層信号線路45に長さ3.5mmの抵抗体を単純に塗布した場合の伝送特性を示し、破線(A3)が内層信号線路45に長さ16.5mmの抵抗体を単純に塗布した場合の伝送特性を示している。この場合は、除去すべき不要波の周波数を  $f_0$  (GHz)としている。この図からも判るように、この不要波抑制回路50によれば、少ない抵抗体を用いて、不要波の周波数  $f_0$  の周辺帯域で、不要波を高効率で減衰、吸収することができる。

10

## 【0041】

このように実施の形態1によれば、遅延器52によって平行2線路53上を伝送する不要波を逆位相とすることにより、平行2線路間に電界を形成し、抵抗体を平行2線路上で前記電界方向に平行に設けているので、DCバイアス電圧、制御信号あるいはIF信号などの駆動制御信号の伝送特性に悪影響を与えることなく、小さな抵抗体を用いて不要波のみを効率よく減衰、吸収させることができとなり、これにより不要波が高周波パッケージ1の外部に放射されることを抑制することができ、高周波パッケージ単体で高周波信号(不要波)の放射を抑制することができる。

20

## 【0042】

なお、上述では、不要波抑制回路50をトリプレート線路に設けた例について説明したが、不要波抑制回路50をマイクロストリップ線路の途中に構成しても良い。このような場合であっても、マイクロストリップ線路から漏れ出る不要波信号を充分に抑圧する効果を得ることができる。

30

## 【0043】

## 実施の形態2.

図8は実施の形態2の高周波パッケージ95を示すものである。実施の形態2においては、図8に示すように、実施の形態1の不要波抑制回路50(50a～50c)を複数個、縦続接続するようにしてあり、これにより不要波の減衰率、吸収率を向上させるようしている。

## 【0044】

この場合、各不要波抑制回路における遅延器の信号線路の長さを同一にして、同一の周波数を持つ複数の不要波抑制回路50a～50cを、縦続接続すると良い。例えば、不要波抑制回路を2段接続するだけで、倍の減衰率を得ることができる。

40

## 【0045】

また、複数の不要波抑制回路50a～50cを縦続接続する場合、各不要波抑制回路50a～50cにおける遅延器52の信号線路の長さを異ならせることによって、複数の異なる不要波周波数を減衰、吸収させることもできる。例えば、不要波の基板内実効波長を  $g_1$  ,  $g_2$  ,  $g_3$  とした場合、不要波抑制回路50aの遅延器52の信号線路は  $g_1/2$  の長さに設定し、不要波抑制回路50bの遅延器52の信号線路は  $g_2/2$  の長さに設定し、不要波抑制回路50cの遅延器52の信号線路は  $g_3/2$  の長さに設定することで、複数の異なる不要波周波数を減衰、吸収させることができる。

## 【0046】

## 実施の形態3.

50

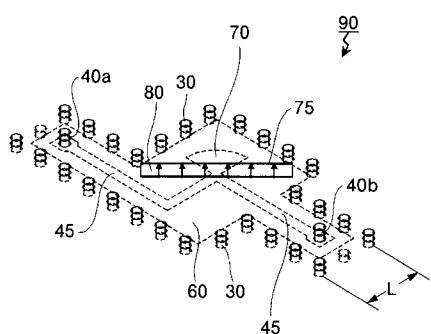

つぎに、図9～図12を用いてこの発明の実施の形態3について説明する。この実施の形態3の高周波パッケージ100においては、図9および図10に示すように、内層信号線路45には、不要波の基板内実効波長  $g$  の  $1/4$  の長さを有する先端開放スタブ70を設けるとともに、この先端開放スタブ70と内層信号線路45との接続位置の上層及び下層、あるいは上下層のいずれか一方の内層接地導体35に不要波の基板内実効波長  $g$  の  $1/2$  の長さを有する結合スロット（内層接地導体35の抜き部分）75を形成し、この結合スロット75上に抵抗体（印刷抵抗）80を形成するようにしている。図9の場合は、先端開放スタブ70が形成された内層信号線路45の上層にのみ結合スロット75を形成し、この結合スロット75に抵抗体80を塗布するようにしている。このように実施の形態3の不要波抑制回路90は、先端開放スタブ70、結合スロット75および抵抗体80によって構成されている。10

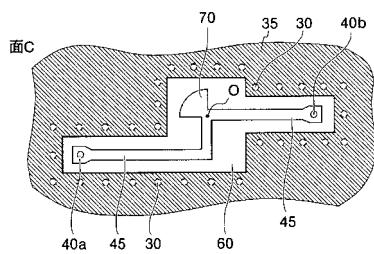

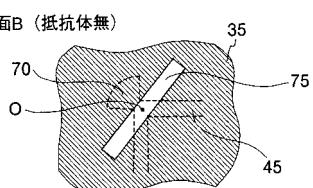

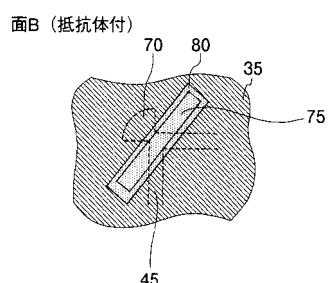

#### 【0047】

図11-1は、図9に示す高周波パッケージ100における多層誘電体基板2のC面（第4層と第5層との間）に配される先端開放スタブ70が形成された内層信号線路45を示す平面図であり、図11-2は多層誘電体基板2のB面（第3層と第4層との間）に配される結合スロット75を示す平面図であり（抵抗体80がない状態を示している）、図11-3は多層誘電体基板2のB面（第3層と第4層との間）に配される結合スロット75および抵抗体80を示す平面図である。

#### 【0048】

実施の形態3の場合においても、伝送線路はトリプレート線路により構成されており、20

上下の内層接地導体35間に内層信号線路45が形成されている。また、図10および図

11-1に示すように、内層信号線路45の周りには、誘電体60を挟んで複数のグラン

ドビア30および内層接地導体35が配置されている。グランドビア30の隣接間隔は、

不要波の基板内実効波長  $g$  の  $1/4$  以下に設定されており、また、対向するグランドビ

ア30間の間隔Lは、波長  $g$  の  $1/2$  以下に設定されている。

#### 【0049】

次に、実施の形態3の要部について説明する。まず、図10および図11-1に示すよ

うに、内層信号線路45には、不要波の基板内実効波長  $g$  の  $1/4$  の長さを有する先端

開放スタブ70を並列に接続している。この場合、先端開放スタブ70として、ラジアル

スタブを採用している。ラジアルスタブは、通常の矩形スタブに比べ、広帯域化が可能で

あるとともに、線路長が  $g/4$  より短くてよいので、小型化が可能である。なお、この

場合は、内層信号線路45における90度屈曲したクランクの角部に、先端開放スタブ7

0を配設しているが、直線状の内層信号線路45に対し90度の角度をもって先端開放ス

タブ70を接続するようにしてもよい。30

#### 【0050】

$g/4$  の長さを有する先端開放スタブ70においては、波長  $g$  の不要波に関しては

、先端部が開放点となり電界が最大レベルとなり、また先端開放スタブ70と内層信号線路45との接続位置Oが短絡点となり電界が最小レベルとなる。そして、図10および図

11-2に示すように、接続位置Oがその中心と一致するように結合スロット75を、先

端開放スタブ70が形成された層の上層及び下層、あるいは上下層のいずれか一方に形成

する。図9の高周波パッケージ1においては、上層側にのみ結合スロット75を形成して

いる。結合スロット75は、この場合、不要波の基板内実効波長  $g$  の  $1/2$  の長さを有し、かつ先端開放スタブ70に対し直角な方向に延在するように形成されている。結合スロット75は、内層接地導体35に抜きを形成することによって形成され、波長  $g$  の不

要波に関しては、その両端部は短絡点となって電界が最小レベルとなり、中心部は開放点とな

って電界が最大レベルとなる。このように、先端開放スタブ70の短絡点と結合スロ

ット75の開放点とを一致させることで、最も強い結合を得ることができ、内層信号線路

45を伝送する不要波を結合スロット75に効率よく結合させることができる。40

#### 【0051】

すなわち、結合スロット75は、先端開放スタブ70と内層信号線路45との接続位置50

の上下層、あるいは上下層のいずれか一方の接地導体に形成されて、この接続位置の周辺で定在波分布が開放となって、内層信号線路 4 5 と結合するように構成すればよい。

#### 【 0 0 5 2 】

結合スロット 7 5 上に結合した不要波は、結合スロット 7 5 に図示のように結合スロットの短手方向を向いた電界が形成され、これと平行に配置・塗布された抵抗体 8 0 により効率よく減衰、吸収されることとなる。

#### 【 0 0 5 3 】

このように実施の形態 3 では、 $g / 4$  の先端開放スタブ 7 0 の短絡点と上下層に設けた  $g / 2$  の結合スロット 7 5 の開放点が一致するように、先端開放スタブ 7 0 および結合スロット 7 5 を配置することにより、内層信号線路 4 5 を伝送する不要波を結合スロット 7 5 に効率よく結合させ、結合スロット 7 5 に結合された不要波を結合スロット 7 5 に形成された電界を用いてこの電界と平行に配置された抵抗体 8 0 で効率よく減衰、吸収させることができる。したがって、D C バイアス電圧、制御信号あるいは I F 信号などの駆動制御信号の伝送特性に悪影響を与えることなく、不要波のみを効率よく減衰、吸収させることができるとなり、これにより、実施の形態 1 と同様、不要波が高周波パッケージ 1 の外部に放射されることを抑制することができ、高周波パッケージ単体で高周波信号（不要波）の放射を抑制することができる。10

#### 【 0 0 5 4 】

なお、結合スロット 7 5 は、先端開放スタブ 7 0 またはラジアルスタブの中心軸に対し直交する方向に延在されている場合が、結合スロット 7 5 で最も強い結合を得ることができるが、結合スロット 7 5 を他の方向に延在するように形成するようにしてもよい。また、結合スロット 7 5 を、 $g / 2$  の整数倍の長さとしてもよい。また、上記接続位置 0 から一方の端部までの長さを  $g / 4$  の奇数倍の長さに設定し、接続位置 0 から他方の端部までの長さを  $g / 4$  の奇数倍の長さに設定した結合スロット 7 5 を採用するようにしてもよい。また、先端開放スタブ 7 0 は、 $g / 4$  の奇数倍の長さとしてもよい。さらに、抵抗体 8 0 を結合スロット 7 5 の全面ではなく、例えば、一方は不要波を結合するスロットとし、他方のスロット線路上に配設するようにしてもよい。20

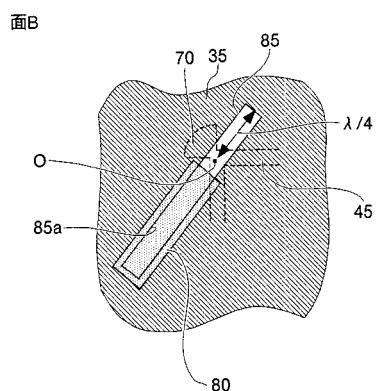

#### 【 0 0 5 5 】

図 1 2 は、実施の形態 3 の変形例を示すものである。この変形例の場合は、結合スロット 8 5 は、先端開放スタブ 7 0 と内層信号線路 4 5 との接続位置 0 から一方の端部までの長さを概ね  $g / 4$  としており、また接続位置 0 から他方の端部までの長さを任意の長さのスロット線路 8 5 a としている。そして、抵抗体 8 0 は、全面に塗布するのではなく、スロット線路 8 5 a 側にのみ塗布するようにしている。30

#### 【 0 0 5 6 】

この変形例においても、 $g / 4$  の長さを有する先端開放スタブ 7 0 においては、波長  $g$  の不要波に関しては、先端部が開放点となり電界が最大レベルとなり、また接続位置 0 が短絡点となり電界が最小レベルとなる。一方、結合スロット 8 5 は、波長  $g$  の不要波に関しては、その両端部は短絡点となって電界が最小レベルとなり、接続位置 0 に対応する点が開放点となって電界が最大レベルとなる。このように、図 1 2 に示す変形例においても、先端開放スタブ 7 0 の短絡点と結合スロット 8 5 の開放点とを一致させることで、最も強い結合を得るようにしている。40

#### 【 0 0 5 7 】

すなわち、この変形例の場合は、内層信号線路 4 5 を伝送する不要波を結合スロット 7 5 に効率よく結合させた後、不要波をスロット線路 8 5 a を伝搬させることで、不要波をスロット線路 8 5 a 上に配した抵抗体 8 0 で減衰、吸収せるようにしている。

#### 【 0 0 5 8 】

なお、不要波の吸収性のためには、スロット線路 8 5 a は、長い方が望ましい。また、接続位置 0 から一方の端部までの長さを概ね  $g / 4$  の奇数倍の長さとしてもよい。また、抵抗体 8 0 を、スロット線路 8 5 a 側にのみ塗布するのではなく、結合スロット 8 5 の全面に塗布するようにしてもよい。さらに、この場合も、先端開放スタブ 7 0 は、 $g /$ 50

4の奇数倍の長さとしてもよい。

**【0059】**

なお、上記実施の形態3の不要波抑制回路90を、複数個、縦続接続して、これにより不要波の減衰率、吸収率を向上させるようにしてもよい。この場合、各不要波抑制回路における結合スロットの長さを同一にして、同一の周波数を持つ複数の不要波抑制回路を、それぞれ縦続接続するとよい。例えば、不要波抑制回路を2段接続するだけで、倍の吸収率を得ることができる。あるいは、複数の不要波抑制回路を縦続接続し、各不要波抑制回路を構成する結合スロットの長さを、異なる周波数を持つ複数の不要波の基板実行波長の略1/2になるように、それぞれ異ならせてもよい。これによって、対応する複数の異なる波長について、それぞれ不要周波数を減衰、吸収させることができる。

10

**【0060】**

なお、上記実施の形態では、多層誘電体基板2内に形成したIC搭載凹部6内に高周波デバイス3を収容する構成の高周波パッケージ1に本発明を適用するようにしたが、本発明は、IC搭載凹部6を持たない平坦な多層誘電体基板2の表層に高周波デバイス3を搭載するような構成の高周波パッケージ1にも適用することができる。

**【産業上の利用可能性】**

**【0061】**

以上のように、本発明にかかる伝送線路基板および高周波パッケージは、高周波のEMI対策を講じる必要のあるFM-CWレーダなどの半導体電子機器に有用である。

20

**【図面の簡単な説明】**

**【0062】**

**【図1】**この発明にかかる半導体パッケージ（高周波パッケージ）の外観を示す斜視図である。

**【図2】**この発明にかかる半導体パッケージのカバーを外した外観を示す斜視図である。

**【図3】**この発明にかかる半導体パッケージの内部構成を示す平面図である。

**【図4】**実施の形態1の半導体パッケージの多層誘電体基板のビア構造を詳細に示す断面図である。

**【図5】**多層誘電体基板内に搭載される実施の形態1の不要波抑制回路の構成を示す斜視図である。

**【図6-1】**多層誘電体基板内に搭載される実施の形態1の不要波抑制回路の構成を示す平面図であり、図5の多層誘電体基板の面Aの状態を示す図である。

30

**【図6-2】**図7の多層誘電体基板の面Dの状態を示す図である。

**【図7】**実施の形態1の不要波抑制回路などの伝送特性を示すグラフである。

**【図8】**実施の形態2の半導体パッケージの多層誘電体基板のビア構造を詳細に示す断面図である。

**【図9】**実施の形態3の半導体パッケージの多層誘電体基板のビア構造を詳細に示す断面図である。

**【図10】**多層誘電体基板内に搭載される実施の形態3の不要波抑制回路の構成を示す斜視図である。

**【図11-1】**多層誘電体基板内に搭載される実施の形態3の不要波抑制回路の一部構成を示す平面図であり、図9の多層誘電体基板の面Cの状態を示す図である。

40

**【図11-2】**多層誘電体基板内に搭載される実施の形態3の不要波抑制回路の一部構成を示す平面図であり、図9の多層誘電体基板の面Bの状態（抵抗体省略）を示す図である。

**【図11-3】**多層誘電体基板内に搭載される実施の形態3の不要波抑制回路の一部構成を示す平面図であり、図9の多層誘電体基板の面Bの状態（抵抗体記載）を示す図である。

**【図12】**実施の形態3の変形例を示す平面図である。

**【符号の説明】**

**【0063】**

50

|                             |                           |    |

|-----------------------------|---------------------------|----|

| 1 , 9 5 , 1 0 0             | 高周波パッケージ(半導体パッケージ)        |    |

| 2                           | 多層誘電体基板                   |    |

| 3                           | 高周波デバイス(半導体デバイス、半導体 I C ) |    |

| 4                           | シールリング                    |    |

| 5                           | カバー                       |    |

| 6                           | I C 搭載凹部                  |    |

| 6 a                         | 側壁                        |    |

| 7                           | フィードスルー                   |    |

| 8                           | マイクロストリップ線路               |    |

| 1 0                         | 内部導体パッド                   | 10 |

| 1 1                         | 導体パッド                     |    |

| 1 2                         | ワイヤ                       |    |

| 1 5                         | 外部導体パッド                   |    |

| 1 6                         | グランド面                     |    |

| 1 7                         | 半田                        |    |

| 1 8                         | グランドパターン                  |    |

| 2 0                         | キャリア                      |    |

| 3 0 , 3 0 b , 3 0 c         | グランドビア                    |    |

| 3 0 a                       | 側壁グランドビア                  |    |

| 3 3                         | キャビティ                     | 20 |

| 3 5                         | 内層接地導体                    |    |

| 4 0 , 4 0 a , 4 0 b         | 信号ビア                      |    |

| 4 5 , 4 5 a , 4 5 b         | 内層信号線路                    |    |

| 5 0 , 5 0 a , 5 0 b , 5 0 c | 不要波抑制回路                   |    |

| 5 1                         | 分配器                       |    |

| 5 2                         | 遅延器                       |    |

| 5 3                         | 平行 2 線路                   |    |

| 5 4                         | 合成器                       |    |

| 5 5                         | 抵抗体                       |    |

| 6 0                         | 誘電体                       | 30 |

| 7 0                         | 先端開放スタブ                   |    |

| 7 5                         | 結合スロット                    |    |

| 8 0                         | 抵抗体                       |    |

| 8 5                         | 結合スロット                    |    |

| 8 5 a                       | スロット線路                    |    |

| 9 0                         | 不要波抑制回路                   |    |

【 図 1 】

【 図 2 】

【 四 4 】

【 义 3 】

【図5】

【図 6 - 1】

【図 6 - 2】

【 四 8 】

【 図 7 】

【図9】

【図10】

【図11-1】

【図11-2】

【図11-3】

【図12】

---

フロントページの続き

(56)参考文献 特開2004-056441(JP,A)

特開平05-110301(JP,A)

(58)調査した分野(Int.Cl., DB名)

H 01 P 1 / 22

H 01 P 3 / 02

H 01 P 5 / 08

H 01 L 23 / 12