등록특허 10-2728552

(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2024년11월12일

(11) 등록번호 10-2728552

(24) 등록일자 2024년11월06일

- (51) 국제특허분류(Int. Cl.)

*H01L 25/065* (2023.01) *G01R 31/28* (2006.01)

*G01R 31/3187* (2006.01) *G11C 29/12* (2015.01)

*H01L 21/66* (2006.01) *H01L 23/498* (2006.01)

- (52) CPC특허분류

*H01L 25/0657* (2023.08)

*G01R 31/2853* (2013.01)

- (21) 출원번호 10-2019-0173005

(22) 출원일자 2019년12월23일

심사청구일자 2022년11월01일

(65) 공개번호 10-2021-0080928

(43) 공개일자 2021년07월01일

- (56) 선행기술조사문헌

KR1020110039205 A\*

US20180247876 A1\*

KR1020150085643 A

KR1020110131976 A

- \*는 심사관에 의하여 인용된 문헌

(73) 특허권자

에스케이하이닉스 주식회사

경기도 이천시 부발읍 경충대로 2091

(72) 발명자

오상목

경기도 화성시 동탄순환대로22길 46, 1253동 130

1호(청계동, 청계숲 사랑으로 부영)

이강설

서울특별시 강동구 올림픽로89길 57, 105동 303

호(천호동, 강변그대家(가) River View(리버뷰))

(74) 대리인

신성특허법인(유한)

전체 청구항 수 : 총 20 항

심사관 : 김신

## (54) 발명의 명칭 적층형 반도체 장치 및 이의 테스트 방법

**(57) 요약**

본 발명은 적층형 반도체 장치에 관한 것으로, 베이스 다이; 및 상기 베이스 다이 상에 적층되어 다수의 관통 전극들 및 적어도 하나의 기준 관통 전극을 통해 연결된 다수 개의 코어 다이들을 포함하고, 상기 베이스 다이는, 테스트 동작 시 오실레이팅 신호를 상기 다수의 관통 전극들 중 적어도 하나의 타겟 관통 전극에 전달하고, 상기 오실레이팅 신호를 토대로 생성된 베이스 신호와 상기 기준 관통 전극을 통해 전달되는 코어 신호를 비교하여 테스트 출력 신호를 출력하는 제 1 테스트 회로를 포함하고, 상기 각 코어 다이는, 상기 테스트 동작 시 상기 타겟 관통 전극을 통해 전달되는 상기 오실레이팅 신호를 토대로 상기 코어 신호를 생성하고, 상기 코어 신호를 상기 기준 관통 전극으로 전달하는 제 2 테스트 회로를 포함할 수 있다.

**대 표 도**

(52) CPC특허분류

*G01R 31/3187* (2013.01)

*G11C 29/1201* (2013.01)

*H01L 22/14* (2013.01)

*H01L 23/49827* (2013.01)

*H01L 23/49838* (2013.01)

---

## 명세서

### 청구범위

#### 청구항 1

베이스 다이; 및

상기 베이스 다이 상에 적층되어 다수의 관통 전극들 및 기준 관통 전극을 통해 연결된 다수 개의 코어 다이들을 포함하고,

상기 베이스 다이는, 테스트 동작 시 오실레이팅 신호를 상기 다수의 관통 전극들 중 적어도 하나의 타겟 관통 전극에 전달하고, 상기 오실레이팅 신호를 토대로 생성된 베이스 신호와 상기 기준 관통 전극을 통해 전달되는 코어 신호를 비교하여 테스트 출력 신호를 출력하여 상기 기준 관통 전극을 통해서 상기 다수의 관통 전극들을 모니터링하는 제 1 테스트 회로를 포함하고,

상기 각 코어 다이는, 상기 테스트 동작 시 상기 타겟 관통 전극을 통해 전달되는 상기 오실레이팅 신호에 대응되는 상기 코어 신호를 생성하고, 상기 코어 신호를 상기 기준 관통 전극으로 전달하는 제 2 테스트 회로를 포함하는 적층형 반도체 장치.

#### 청구항 2

제 1 항에 있어서,

상기 베이스 다이는,

컨트롤러와 인터페이싱하는 제 1 영역, 상기 관통 전극들과 인터페이싱하는 제 2 영역 및 외부 테스트 장치와 직접 인터페이싱하는 제 3 영역을 포함하고,

상기 제 1 테스트 회로는 상기 제 2 영역에 배치되는 것을 특징으로 하는 적층형 반도체 장치.

#### 청구항 3

제 2 항에 있어서,

상기 제 1 테스트 회로는,

상기 테스트 출력 신호를 상기 제 3 영역에 배치된 테스트 출력 패드를 통해 출력하는

적층형 반도체 장치.

#### 청구항 4

제 2 항에 있어서,

상기 제 1 영역에는, 상기 컨트롤러로부터 전달되는 데이터를 입출력하는 제 1 입출력 버퍼 회로가 배치되고,

상기 제 2 영역에는, 상기 관통 전극들로부터 전달되는 데이터를 입출력하는 제 2 입출력 버퍼 회로

가 배치되는 적층형 반도체 장치.

#### 청구항 5

제 4 항에 있어서,

상기 제 1 테스트 회로는,

테스트 신호에 따라 상기 오실레이팅 신호를 생성하여 상기 제 2 입출력 버퍼 회로의 출력 버퍼에 제공하는 패턴 생성기;

상기 테스트 신호에 따라 상기 오실레이팅 신호를 카운팅하여 베이스 카운팅 신호를 생성하는 제 1 카운터;

상기 베이스 카운팅 신호를 직렬화하여 상기 베이스 신호를 출력하는 제 1 직렬화기; 및

상기 코어 신호와 베이스 신호를 비교하여 상기 테스트 출력 신호를 출력하는 비교기

를 포함하는 적층형 반도체 장치.

## 청구항 6

제 5 항에 있어서,

상기 테스트 신호는, 주파수 정보를 가지는 멀티 비트의 신호이며,

상기 패턴 생성기는 상기 테스트 신호의 상기 주파수 정보에 따라 소정 주기로 토클링하는 상기 오실레이팅 신호를 생성하는 적층형 반도체 장치.

## 청구항 7

제 5 항에 있어서,

상기 제 1 테스트 회로는,

상기 베이스 카운팅 신호를 저장하여 상기 제 1 직렬화기에 제공하는 제 1 레지스터

를 더 포함하는 적층형 반도체 장치.

## 청구항 8

제 4 항에 있어서,

상기 제 1 테스트 회로는,

테스트 신호에 따라 제 1 예비 오실레이팅 신호를 생성하는 패턴 생성기;

테스트 선택 신호에 따라 상기 제 1 예비 오실레이팅 신호 또는 테스트 입력 패드를 통해 입력되는 제 2 예비 오실레이팅 신호를 선택하여, 상기 제 1 입출력 버퍼 회로의 출력 버퍼에 상기 오실레이팅 신호로 제공하는 멱성 회로;

상기 테스트 신호에 따라 상기 제 1 예비 오실레이팅 신호 혹은 상기 제 2 예비 오실레이팅 신호를 카운팅하여 베이스 카운팅 신호를 생성하는 제 1 카운터;

상기 베이스 카운팅 신호를 직렬화하여 상기 베이스 신호를 출력하는 제 1 직렬화기; 및

상기 코어 신호와 베이스 신호를 비교하여 상기 테스트 출력 신호를 출력하는 비교기

를 포함하는 적층형 반도체 장치.

## 청구항 9

제 8 항에 있어서,

상기 제 1 테스트 회로는,

상기 베이스 카운팅 신호를 저장하여 상기 제 1 직렬화기에 제공하는 제 1 레지스터

를 더 포함하는 적층형 반도체 장치.

#### 청구항 10

제 1 항에 있어서,

상기 코어 다이는,

다수의 메모리 셀들이 배치되는 코어 영역; 및

상기 코어 영역을 제어하기 위한 주변 회로, 상기 관통 전극들과 인터페이싱하기 위한 회로 및 상기 관통 전극

들이 배치되는 주변 영역을 포함하며,

상기 제 2 테스트 회로는 상기 주변 영역에 배치되는 적층형 반도체 장치.

#### 청구항 11

제 10 항에 있어서,

상기 주변 영역에는,

상기 관통 전극들로부터 전달되는 데이터를 입출력하는 제 3 입출력 버퍼 회로

가 배치되는 적층형 반도체 장치.

#### 청구항 12

제 11 항에 있어서,

상기 제 2 테스트 회로는,

테스트 신호에 따라 활성화되며, 상기 제 3 입출력 버퍼 회로의 입력 버퍼를 통해 전달되는 상기 오실레이팅 신

호를 카운팅하여 코어 카운팅 신호를 생성하는 제 2 카운터; 및

상기 코어 카운팅 신호를 직렬화하여 상기 코어 신호를 출력하는 제 2 직렬화기

를 포함하는 적층형 반도체 장치.

#### 청구항 13

제 12 항에 있어서,

상기 제 2 테스트 회로는,

상기 코어 카운팅 신호를 저장하여 상기 제 2 직렬화기에 제공하는 제 2 레지스터

를 더 포함하는 적층형 반도체 장치.

#### 청구항 14

제 11 항에 있어서,

상기 코어 영역에는,

라이트 동작 시, 상기 제 3 입출력 버퍼 회로로부터 전달되는 데이터를 상기 메모리 셀들에 라이트하는 라이트

드라이버; 및

리드 동작 시, 상기 메모리 셀들로부터 출력되는 데이터를 제 3 입출력 버퍼 회로로 전달하는 입출력 센스 앤프가 더 배치되는 적층형 반도체 장치.

### 청구항 15

베이스 다이 및 상기 베이스 다이 상에 적층되어 다수의 관통 전극들 및 기준 관통 전극을 통해 연결된 다수 개의 코어 다이를 포함하는 적층형 반도체 장치에 있어서,

상기 베이스 다이에서, 오실레이팅 신호를 상기 다수의 관통 전극들 중 적어도 하나의 타겟 관통 전극에 전달하고, 상기 오실레이팅 신호를 토대로 베이스 신호를 생성하는 단계;

상기 코어 다이에서, 상기 타겟 관통 전극을 통해 전달되는 오실레이팅 신호를 토대로 코어 신호를 생성하는 단계; 및

상기 베이스 다이에서, 상기 기준 관통 전극을 통해 전달되는 코어 신호와 상기 베이스 신호를 비교하여 테스트 출력 신호를 출력하여 상기 기준 관통 전극을 통해서 상기 다수의 관통 전극들을 모니터링하는 단계

를 포함하는 적층형 반도체 장치의 테스트 방법.

### 청구항 16

제 15 항에 있어서,

상기 베이스 다이는,

컨트롤러와 인터페이싱하는 제 1 영역, 상기 관통 전극들과 인터페이싱하는 제 2 영역 및 외부 테스트 장치와 직접 인터페이싱하는 제 3 영역을 포함하고,

상기 베이스 다이에 의해, 상기 테스트 출력 신호를 상기 제 3 영역에 배치된 테스트 출력 패드를 통해 출력하는 단계

를 더 포함하는 적층형 반도체 장치의 테스트 방법.

### 청구항 17

제 16 항에 있어서,

상기 오실레이팅 신호는,

상기 제 3 영역에 배치된 테스트 입력 패드를 통해 외부로부터 입력되는 적층형 반도체 장치의 테스트 방법.

### 청구항 18

제 15 항에 있어서,

상기 오실레이팅 신호는,

주파수 정보를 가지는 멀티 비트의 테스트 신호에 따라 상기 베이스 다이 내부에서 생성되며, 상기 테스트 신호의 상기 주파수 정보에 따라 소정 주기로 토글링하는 적층형 반도체 장치의 테스트 방법.

### 청구항 19

제 15 항에 있어서,

상기 오실레이팅 신호를 토대로 베이스 신호를 생성하는 단계는,

테스트 신호에 따라 상기 오실레이팅 신호를 카운팅하여 베이스 카운팅 신호를 생성하는 단계;

상기 베이스 카운팅 신호를 저장하는 단계; 및

상기 저장된 베이스 카운팅 신호를 직렬화하여 상기 베이스 신호를 생성하는 단계

를 포함하는 적층형 반도체 장치의 테스트 방법.

## 청구항 20

제 15 항에 있어서,

상기 오실레이팅 신호를 토대로 코어 신호를 생성하는 단계는,

테스트 신호에 따라 상기 오실레이팅 신호를 카운팅하여 코어 카운팅 신호를 생성하는 단계;

상기 코어 카운팅 신호를 저장하는 단계; 및

상기 저장된 코어 카운팅 신호를 직렬화하여 상기 코어 신호를 생성하는 단계

를 포함하는 적층형 반도체 장치의 테스트 방법.

## 발명의 설명

### 기술 분야

[0001]

본 발명은 반도체 설계 기술에 관한 것으로, 특히, 적층형 반도체 장치의 테스트 방법에 관한 것이다.

### 배경 기술

[0003]

반도체 기술이 비약적으로 발전하면서 반도체 집적 장치에 대한 패키징 기술에 대해서도 점차 고집적화 및 고성능화가 요구되고 있다. 따라서, 집적 회로가 구현되는 반도체 칩들을 와이어나 범프를 이용해 인쇄회로기판(PCB)상에 평면적으로 배치시키는 2차원 구조에서 벗어나 다수개의 반도체 칩을 수직하게 적층시키는 3차원 구조에 관한 기술이 다양하게 발전하고 있다.

[0004]

이러한 3차원 구조는 다수개의 반도체 칩들을 수직으로 적층하는 적층형 반도체 장치를 통해 구현될 수 있다. 그리고, 이처럼 수직방향으로 탑재된 반도체 칩들은 관통 실리콘 비아(TSV, Through Silicon Via, 이하, '관통 전극'이라고 한다.)를 통해 서로 전기적으로 연결되면서 반도체 패키지용 기판에 탑재된다.

[0005]

한편, 관통 전극에는 다양한 불량이 발생할 수 있는데, 이러한 불량에는 관통 전극 내부에 전도 물질이 완전히 채워지지 못해 발생하는 보이드(void), 칩이 휘어지거나 범프(bump) 물질이 이동하여 발생하는 범프 컨택 페일(bump contact fail) 및 관통 전극 자체의 균열(crack) 등이 있을 수 있다. 관통 전극은 다수의 칩을 전기적으로 연결하는 기능을 수행하기 때문에 불량이 발생하여 관통 전극이 중간에 끊기는(open) 경우 관통 전극으로서 정상적인 기능을 발휘하지 못하게 된다. 따라서, 테스트를 통해 관통 전극의 불량 여부를 검출해야 한다.

## 발명의 내용

### 해결하려는 과제

[0007]

본 발명의 실시예들은 웨이퍼 레벨에서 관통 전극의 정상 동작 여부를 검증할 수 있는 적층형 반도체 장치를 제공하는 것이다.

[0008]

본 발명의 실시예들은 신호 전송율에 따른 관통 전극의 동작 특성을 테스트할 수 있는 적층형 반도체 장치를 제공하는 것이다.

[0009]

본 발명의 실시예들은 관통 전극 및 관통 전극용 인터페이스 회로만을 테스트할 수 있는 적층형 반도체 장치를 제공하는 것이다.

## 과제의 해결 수단

[0011]

본 발명의 일 실시예에 따른 적층형 반도체 장치는, 베이스 다이; 및 상기 베이스 다이 상에 적층되어 다수의 관통 전극들 및 적어도 하나의 기준 관통 전극을 통해 연결된 다수 개의 코어 다이들을 포함하고, 상기 베이스 다이는, 테스트 동작 시 오실레이팅 신호를 상기 다수의 관통 전극들 중 적어도 하나의 타겟 관통 전극에 전달하고, 상기 오실레이팅 신호를 토대로 생성된 베이스 신호와 상기 기준 관통 전극을 통해 전달되는 코어 신호를 비교하여 테스트 출력 신호를 출력하는 제 1 테스트 회로를 포함하고, 상기 각 코어 다이는, 상기 테스트 동작 시 상기 타겟 관통 전극을 통해 전달되는 상기 오실레이팅 신호를 토대로 상기 코어 신호를 생성하고, 상기 코어 신호를 상기 기준 관통 전극으로 전달하는 제 2 테스트 회로를 포함할 수 있다.

[0012]

본 발명의 일 실시예에 따른 적층형 반도체 장치의 테스트 방법은, 베이스 다이 및 상기 베이스 다이 상에 적층되어 다수의 관통 전극들 및 적어도 하나의 기준 관통 전극을 통해 연결된 다수 개의 코어 다이를 포함하는 적층형 반도체 장치에 있어서, 상기 베이스 다이에서, 오실레이팅 신호를 상기 다수의 관통 전극들 중 적어도 하나의 타겟 관통 전극에 전달하고, 상기 오실레이팅 신호를 토대로 베이스 신호를 생성하는 단계; 상기 코어 다이에서, 상기 타겟 관통 전극을 통해 전달되는 오실레이팅 신호를 토대로 코어 신호를 생성하는 단계; 및 상기 베이스 다이에서, 상기 기준 관통 전극을 통해 전달되는 코어 신호와 상기 베이스 신호를 비교하여 테스트 출력 신호를 출력하는 단계를 포함할 수 있다.

## 발명의 효과

[0014]

제안된 실시예에 따른 적층형 반도체 장치는, 관통 전극의 정상 동작 여부를 웨이퍼 레벨에서 검증함으로써 전체 칩 수율을 향상시킬 수 있다.

[0015]

제안된 실시예에 따른 적층형 반도체 장치는, 신호 전송율에 따른 관통 전극의 동작 특성을 파악함으로써 신호 전송의 정확성 및 효율을 증가시킬 수 있는 효과가 있다.

[0016]

제안된 실시예에 따른 적층형 반도체 장치는, 관통 전극 및 관통 전극용 인터페이스 회로만을 테스트함으로써 관통 전극의 신호 전송 상태를 정확하게 파악할 수 있는 효과가 있다.

## 도면의 간단한 설명

[0018]

도 1 은 본 발명의 실시예에 따른 반도체 메모리 시스템의 구성을 나타낸 도면이다.

도 2 는 도 1 의 적층형 메모리 장치를 설명하기 위한 사시도이다.

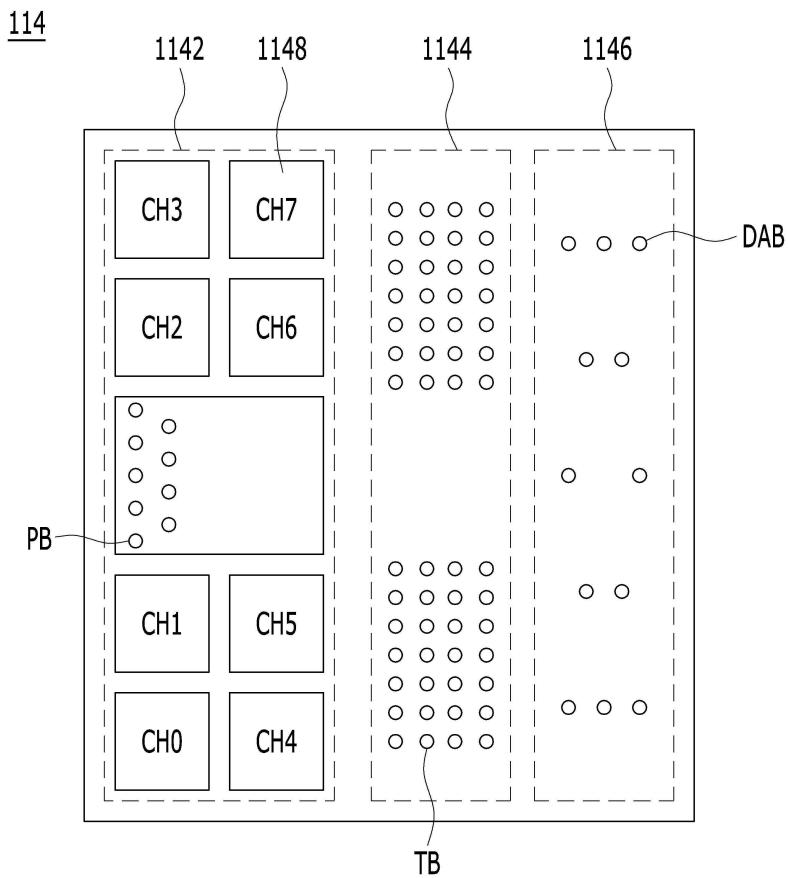

도 3 은 도 2 의 베이스 다이의 구성을 설명하기 위한 평면도이다.

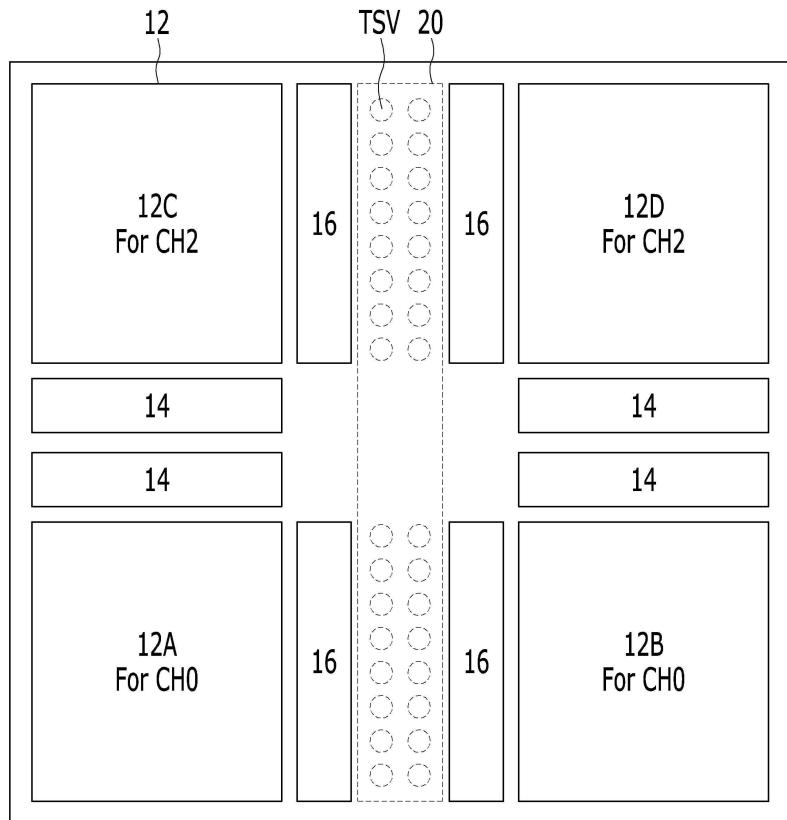

도 4 는 도 2 의 코어 다이의 구성을 설명하기 위한 평면도이다.

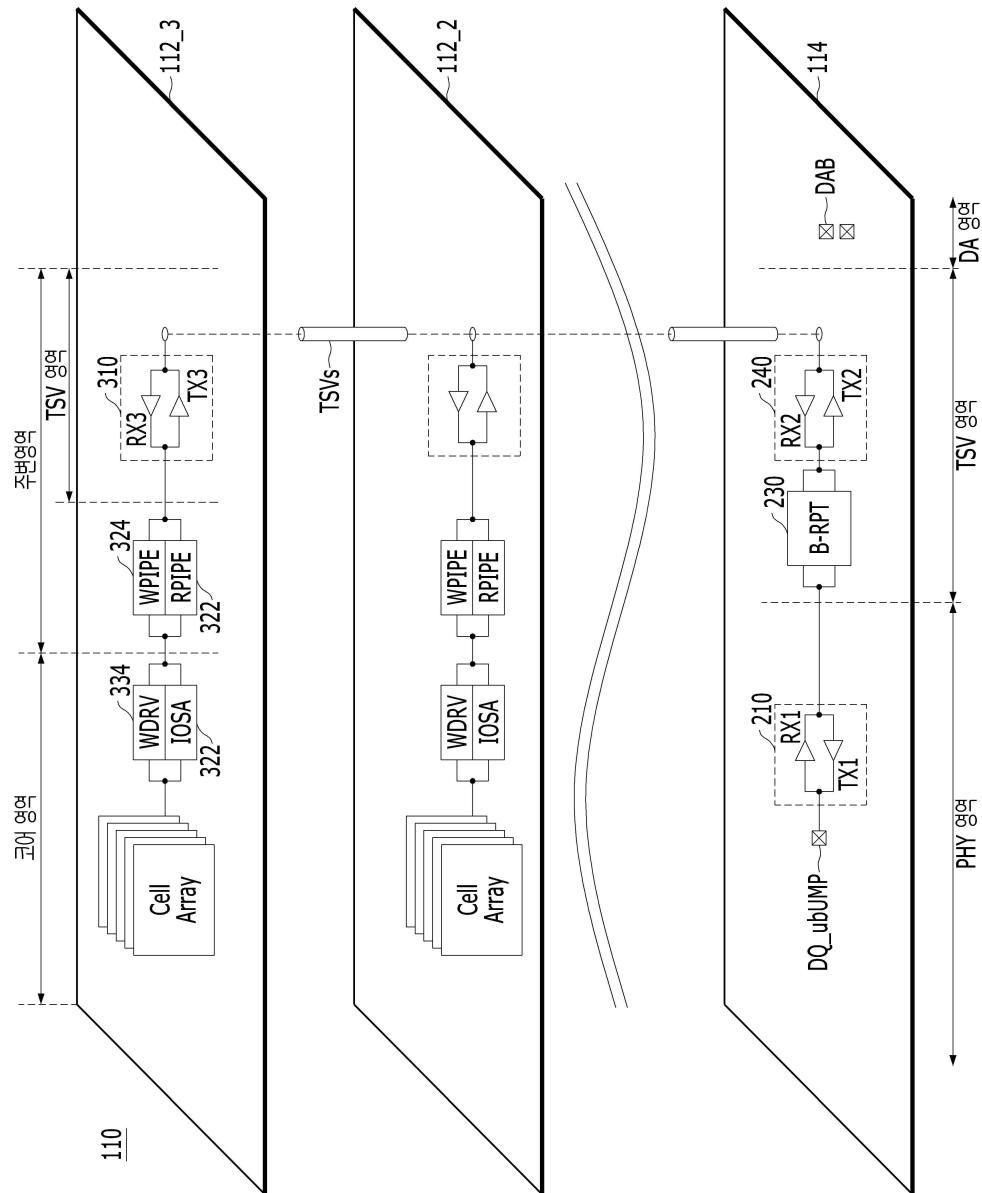

도 5 는 도 1 의 적층형 메모리 장치의 구성을 나타낸 도면이다.

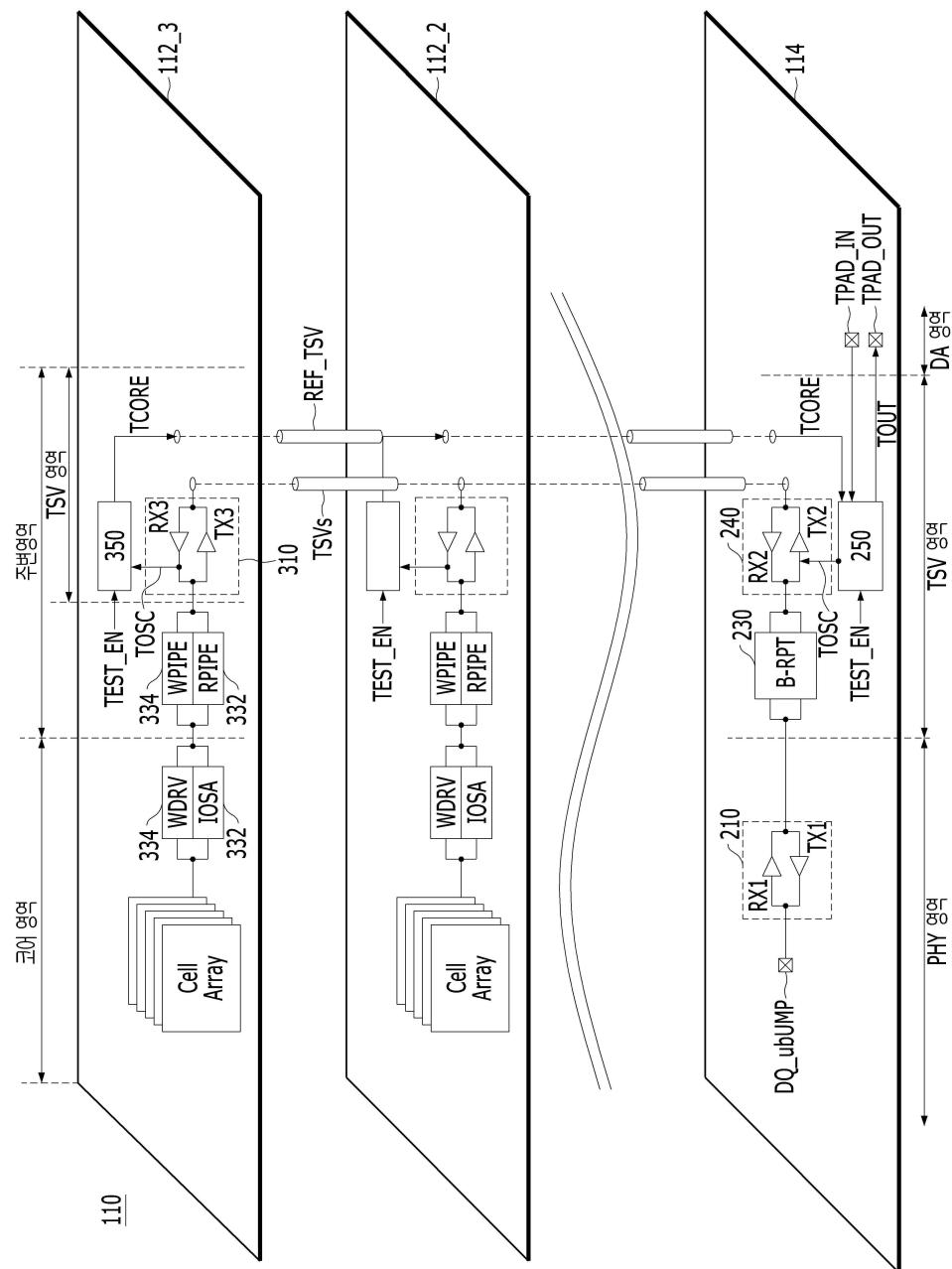

도 6 은 본 발명의 실시예에 따른 적층형 메모리 장치의 구성을 나타낸 도면이다.

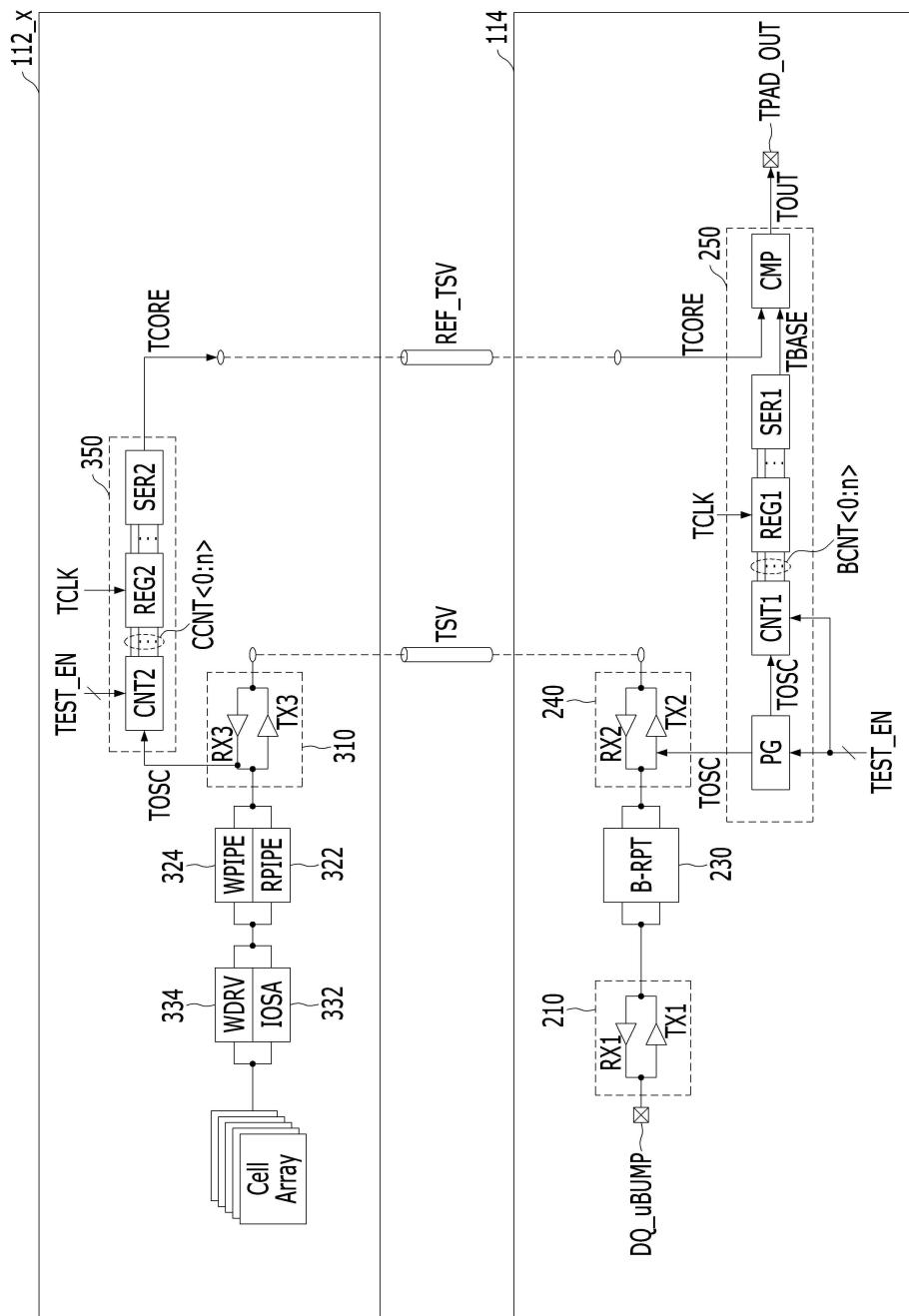

도 7 은 제 1 실시예에 따른 도 6 의 적층형 메모리 장치의 테스트 회로의 구성을 설명하기 위한 도면이다.

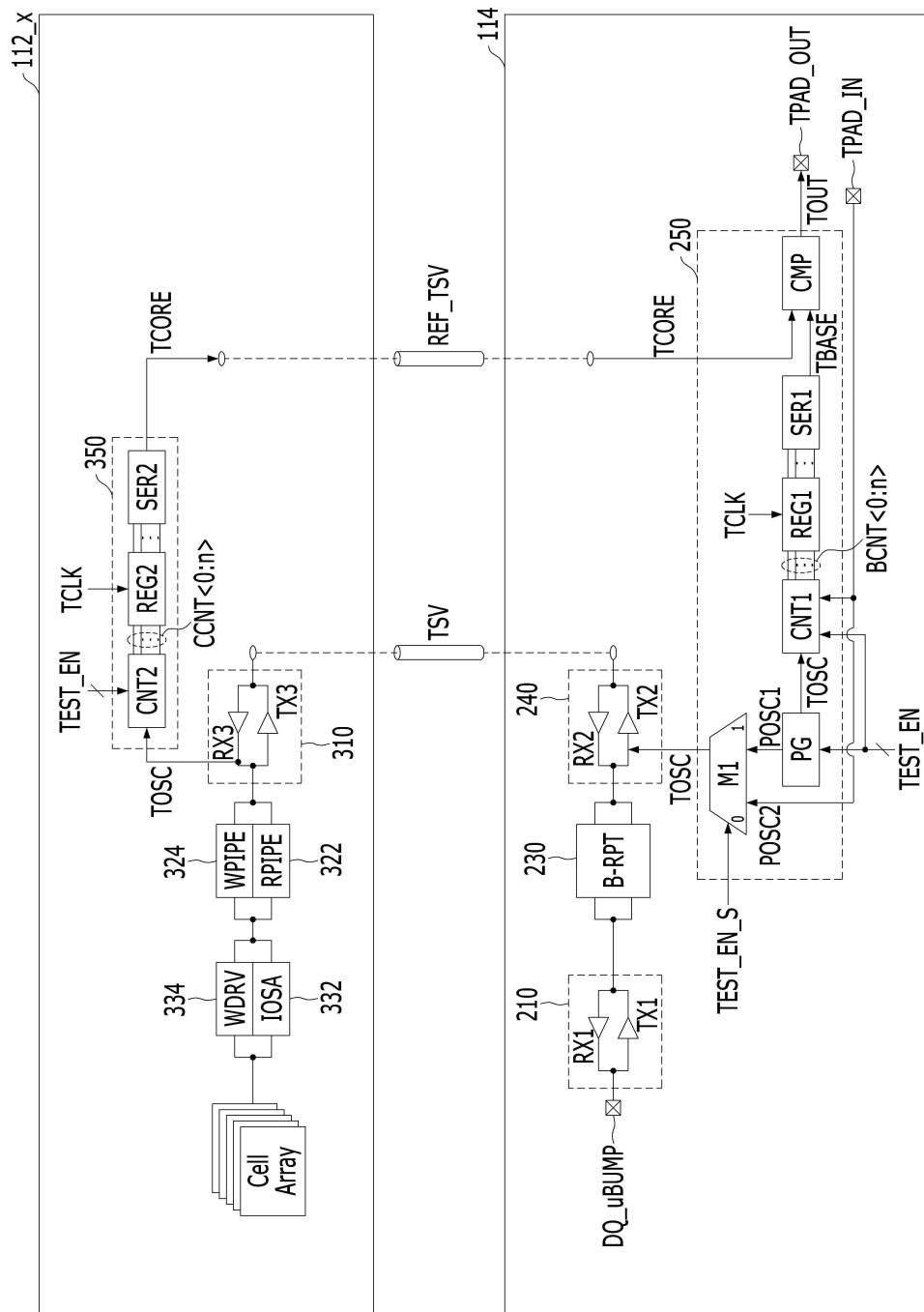

도 8 은 제 2 실시예에 따른 도 6 의 적층형 메모리 장치의 테스트 회로의 구성을 설명하기 위한 도면이다.

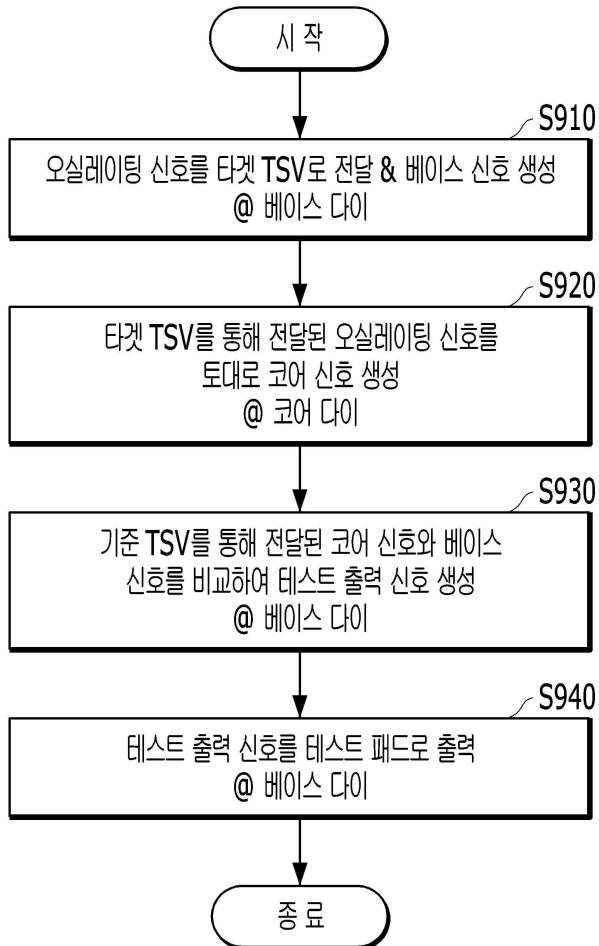

도 9 는 도 7 및 도 8 의 적층형 메모리 장치의 테스트 동작을 설명하기 위한 타이밍도이다.

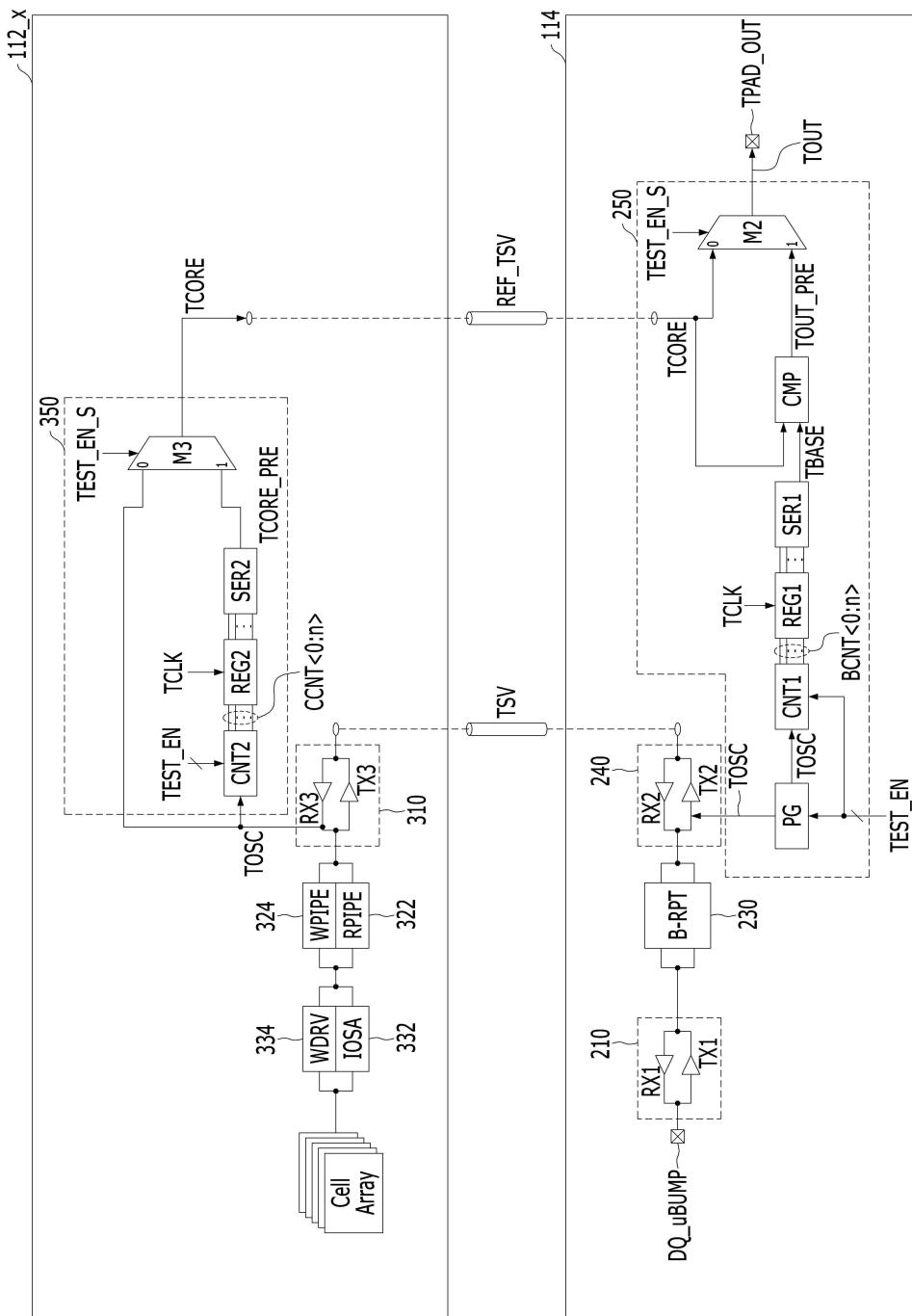

도 10 은 제 3 실시예에 따른 도 6 의 적층형 메모리 장치의 테스트 회로의 구성을 설명하기 위한 도면이다.

도 11 은 본 발명의 실시예에 따른 적층형 메모리 장치의 구성을 나타낸 도면이다.

## 발명을 실시하기 위한 구체적인 내용

[0019]

이하, 본 발명이 속하는 기술 분야에서 통상의 지식을 가진 자가 본 발명의 기술적 사상을 용이하게 실시할 수 있을 정도로 상세히 설명하기 위하여, 본 발명의 실시예를 첨부 도면을 참조하여 설명하기로 한다. 본 발명을 설명함에 있어서, 본 발명의 요지와 무관한 공지의 구성은 생략될 수 있다. 각 도면의 구성요소들에 참조 번호를 부가함에 있어서, 동일한 구성 요소들에 한해서는 비록 다른 도면상에 표시되더라도 가능한 한 동일한 번호를 가지도록 하고 있음에 유의하여야 한다.

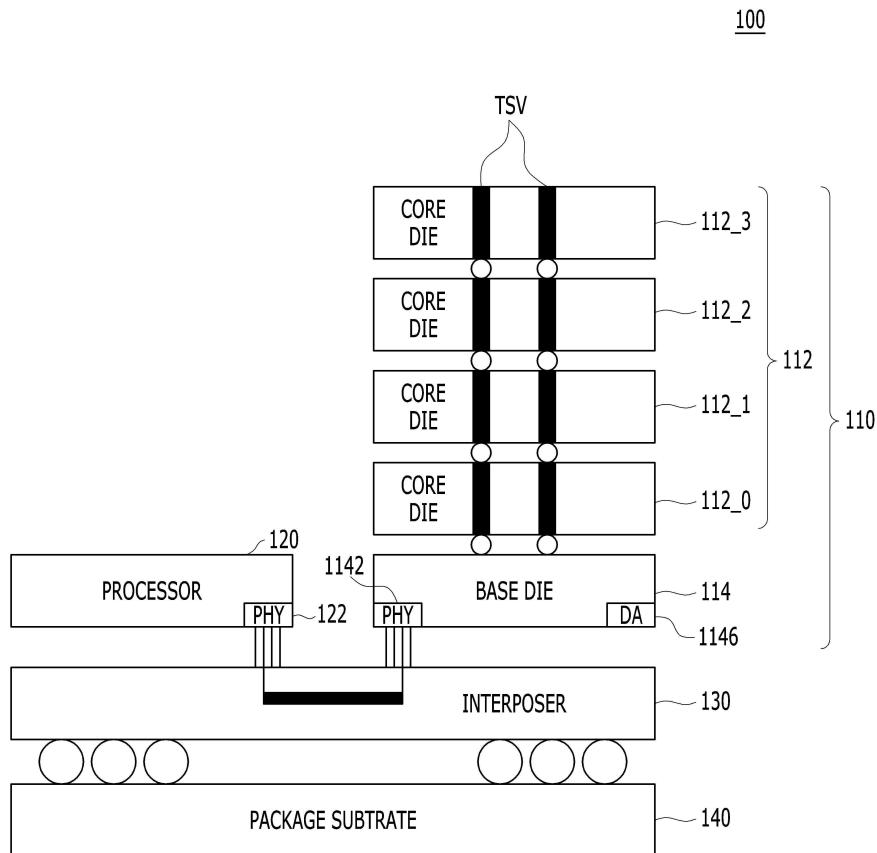

- [0021] 본 발명의 실시예에 따른 반도체 메모리 시스템은 시스템 인 패키지(System In Package), 멀티 칩 패키지(Multi-Chip Package), 시스템 온 칩(System On Chip)과 같은 형태로 구현될 수 있고, 다수의 패키지를 포함하는 패키지 온 패키지(Package On Package) 형태로도 구현될 수 있다. 이하에서는, 적층형 반도체 장치의 일례로 반도체 메모리 시스템을 설명하기로 한다.

- [0022] 도 1은 본 발명의 실시예에 따른 반도체 메모리 시스템(100)의 구성을 나타낸 도면이다.

- [0023] 도 1을 참조하면, 메모리 시스템(100)은 적층형 메모리 장치(110), 컨트롤러(120), 인터포저(Interposer, 130) 및 패키지 기판(Package Substrate, 140)을 포함할 수 있다.

- [0024] 패키지 기판(140) 상부에는 인터포저(130)가 형성될 수 있다.

- [0025] 인터포저(130) 상부에는 적층형 메모리 장치(110)와 컨트롤러(120)가 형성될 수 있다.

- [0026] 컨트롤러(120)는 CPU(Central Processing Unit), GPU(Graphic Processing Unit) 및 AP(Application Processor)와 같은 다양한 프로세서 내에 포함되는 것이 일반적이므로, 도 1에서는 컨트롤러(120)를 프로세서로 표기했다.

- [0027] 적층형 메모리 장치(110)의 물리 영역(PHY, 1142)은 인터포저(130)를 통해 컨트롤러(120)의 물리 영역(PHY, 122)과 연결될 수 있다. 각 물리 영역(1142, 122)에는 적층형 메모리 장치(110)와 컨트롤러(120) 간의 통신을 위한 인터페이스 회로가 배치될 수 있다.

- [0028] 적층형 메모리 장치(110)는 수직 방향으로 다수의 다이(Die)(즉, 반도체 칩)를 적층하고, 관통 전극(TSV)을 통해 전기적으로 연결시킴으로써 입/출력 유닛의 수를 늘려 대역폭(Bandwidth)을 증가시킨 HBM(High Bandwidth Memory) 형태로 구성될 수 있다.

- [0029] 다수의 다이는 베이스 다이(Base Die)(114) 및 다수의 코어 다이(Core Die)(112)를 포함할 수 있다. 코어 다이(112)는 베이스 다이(114) 상에 적층될 수 있으며, 관통 전극(TSV)을 통해 서로 연결될 수 있다. 도 1에는 4개의 코어 다이들(112), 즉, 제 1 내지 제 4 코어 다이(112\_0~112\_3)가 적층된 경우가 도시되어 있지만, 제안 발명은 이에 한정되지 않는다.

- [0030] 각 코어 다이(112)는 메모리 칩으로 구현될 수 있다. 각 코어 다이(112)에는 데이터를 저장하기 위한 다수의 메모리 셀들 및 메모리 셀의 코어 동작을 위한 회로들이 배치될 수 있다. 베이스 다이(114)에는 코어 다이(112)와 컨트롤러(120) 간의 인터페이스를 위한 회로가 설치될 수 있으며, 따라서, 반도체 메모리 시스템 내의 다양한 기능, 예를 들어, 메모리 셀들의 전력 관리 및 리프레쉬와 같은 메모리 관리 기능 혹은 상기 코어 다이(112)와 컨트롤러(120) 간의 타이밍 조절 기능들을 수행할 수 있다.

- [0031] 한편, 베이스 다이(114)에는, 컨트롤러(120) 간의 통신을 위한 인터페이스 회로가 배치되는 물리 영역(1142) 및 적층형 메모리 장치(110)를 테스트하기 위한 인터페이스 회로가 배치되는 직접 액세스(Direct Access, DA) 영역(1146)이 배치될 수 있다.

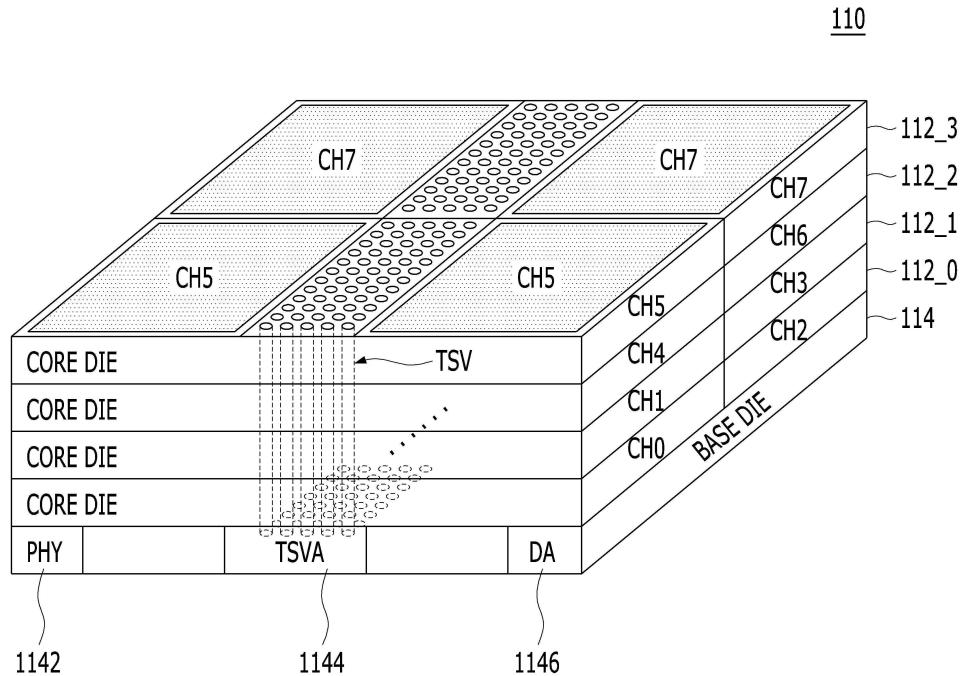

- [0032] 도 2는 도 1의 적층형 메모리 장치(110)를 설명하기 위한 사시도이다.

- [0033] 도 2를 참조하면, 제 1 내지 제 4 코어 다이(112\_0~112\_3) 각각은 하나 이상의 채널을 포함할 수 있다. 도 2에서는 하나의 코어 다이가 두 개의 채널을 포함하는 경우, 적층형 메모리 장치(110)가 제 1 내지 제 8 채널(CH0~CH7)을 갖는 예가 도시되었다. 예컨대, 제 1 코어 다이(112\_0)가 제 1 및 제 3 채널(CH0, CH2)에 대응되는 코어 영역을 포함하고, 제 2 코어 다이(112\_1)가 제 2 채널 및 제 4 채널(CH1, CH3)에 대응되는 코어 영역을 포함하며, 제 3 코어 다이(112\_2)가 제 5 채널 및 제 7 채널(CH4, CH6)에 대응되는 코어 영역을 포함하며, 제 4 코어 다이(112\_3)가 제 6 채널 및 제 8 채널(CH5, CH7)에 대응되는 코어 영역을 포함할 수 있다.

- [0034] 또한, 제 1 내지 제 4 코어 다이(112\_0~112\_3)를 관통하는 다수의 관통 전극들(TSV)은, 제 1 내지 제 8 채널(CH0~CH7)에 대응하여 배치될 수 있다. 각 채널이 128 비트의 대역폭(Bandwidth)을 갖는 경우, 관통 전극들(TSV)은 1024 비트의 데이터 입출력을 위한 구성을 포함할 수 있다.

- [0035] 베이스 다이(114)는 컨트롤러(도 1의 120)와 통신하고, 컨트롤러(120)로부터 커맨드, 어드레스 및 데이터를 수신할 수 있으며, 수신된 커맨드, 어드레스 및 데이터를 제 1 내지 제 4 코어 다이(112\_0~112\_3)로 제공할 수 있다.

- [0036] 베이스 다이(114)에는 물리 영역(PHY, 1142), TSV 영역(TSVA, 1144) 및 DA 영역(DA, 1146)이 배치될 수 있다.

- [0037] 베이스 다이(114)에는 물리 영역(PHY, 1142), TSV 영역(TSVA, 1144) 및 DA 영역(DA, 1146)이 배치될 수 있다.

- [0038] 물리 영역(1142)은 컨트롤러(120)와의 인터페이스를 위한 입/출력 관련 회로가 구성되는 영역으로, 컨트롤러(120)와 인접한 베이스 다이(114)의 제 1 엣지 영역에 배치될 수 있다. DA 영역(1146)은 외부 장치(예를 들어, 테스트 장치, 미도시)와 직접 인터페이스를 위한 입/출력 관련 회로가 구성되는 영역으로, 테스트 장치와 인접한 베이스 다이(114)의 제 2 엣지 영역에 배치될 수 있다. 제 2 엣지 영역은 제 1 엣지 영역과 반대되는 방향일 수 있다. TSV 영역(1144)은 제 1 내지 제 4 코어 다이(112\_0~112\_3)를 관통하는 관통 전극들(TSV)과 인터페이스를 위한 영역으로, 물리 영역(1142)과 DA 영역(1146) 사이의 영역, 즉, 베이스 다이(114)의 중심 영역일 수 있다.

- [0039] 컨트롤러(120)로부터 수신된 신호는 물리 영역(1142)으로부터 TSV 영역(1144)으로 전송될 수 있다. 테스트 장치로부터 수신된 테스트 신호는 DA 영역(1146)으로부터 TSV 영역(1144)으로 전송될 수 있다. 물리 영역(1142)로부터 수신된 신호 또는 DA 영역(1146)으로부터 수신된 테스트 신호는, TSV 영역(1144)에서 소정의 신호 처리 동작, 예를 들면 버퍼링 동작이 수행된 후에 관통 전극들(TSV)을 통해 제 1 내지 제 4 코어 다이(112\_0~112\_3)에 전송될 수 있다.

- [0041] 도 3 은 도 2 의 베이스 다이(114)의 구성을 설명하기 위한 평면도이다.

- [0042] 도 3 을 참조하면, 베이스 다이(114)는, 물리 영역(1142), TSV 영역(1144) 및 DA 영역(1146)으로 구분되며, 물리 영역(1142)에는, 제 1 내지 제 4 코어 다이(112\_0~112\_3)의 제 1 내지 제 8채널(CH0~CH7)과 인터페이스를 위한 채널 인터페이스 영역(IF\_CH0~IF\_CH7)이 배치될 수 있다.

- [0043] 물리 영역(1142)에는 컨트롤러(120)와 인터페이싱하는 PHY 범프들(PB)이 형성될 수 있으며, TSV 영역(1144)에는 관통 전극들(TSV)과 인터페이싱하는 TSV 범프들(TB)이 배치될 수 있다. DA 영역(1146)에는, 외부 테스트 장치가 인터포저(130)를 통하지 않고 적층형 메모리 장치(110)를 직접 억세스(예를 들어, Probing)하여 테스트하기 위한 다수의 DA 범프들(DAB)이 형성될 수 있다. PHY 범프들(PB), TSV 범프들(TB) 및 DA 범프들(DAB)은 마이크로 범프로 구성될 수 있다. 도면에 도시되지 않았지만, DA 영역(1146)에는, DA 범프들(DAB)과 연결되는 DA 패드들이 더 배치될 수 있다. DA 패드들은 PHY 범프들(PB) 보다 큰 면적을 가지도록 형성될 수 있다.

- [0044] 상기와 같이, PHY 범프들(PB)의 물리적인 크기가 매우 작고 개수가 1000개 이상으로 대단히 많기 때문에, PHY 범프들(PB)을 이용하여 적층형 메모리 장치(110)를 테스트하는 것은 현실적으로 어렵다. 또한, 적층형 메모리 장치(110)가 SIP(System In Package) 형태로 패키지 내부에서 컨트롤러(120)와 통신하므로, PHY 범프들(PB)을 이용해 적층형 메모리 장치(110)를 테스트하는 것은 더욱 어렵다. 이러한 이유로 PHY 범프들(PB) 보다 상대적으로 물리적인 사이즈가 크고 갯수가 적은 DA 범프들(DAB) 혹은 DA 패드들을 이용해 메모리 장치를 테스트할 수 있다.

- [0046] 도 4 는 도 2 의 제 1 코어 다이(112\_0)의 구성을 설명하기 위한 평면도이다. 제 2 내지 제 4 코어 다이(112\_1~112\_4)는 제 1 코어 다이(112\_0)와 실질적으로 동일한 구성을 가지므로 제 1 코어 다이(112\_0)를 예로 들어 설명하기로 한다.

- [0047] 도 4 를 참조하면, 제 1 코어 다이(112\_0)는, 코어 영역 및 주변 영역으로 구분될 수 있다.

- [0048] 코어 영역에는 다수의 셀 어레이 영역들(12)이 배치될 수 있다. 다수의 셀 어레이 영역들(12) 내에 메모리 셀들이 배치될 수 있다. 예를 들어, 도 2 에 도시된 바와 같이, 다수의 셀 어레이 영역들(12) 중 하부 셀 어레이 영역들(12A, 12B)은 제 1 채널(CH0)에 할당되고, 상부 셀 어레이 영역들(12C, 12D)은 제 3 채널(CH2)에 할당될 수 있다. 코어 영역에는 컬럼 디코더 영역들(14) 및 로우 디코더 영역들(16)이 추가로 배치될 수 있다. 컬럼 디코더 영역들(14)에는, 커맨드/어드레스 제어와 관련된 컬럼 디코더들(미도시)이 배치될 수 있다. 컬럼 디코더들은 어드레스를 입력 받아 이를 디코딩하여 코어 영역들의 컬럼 라인들(즉, 비트 라인들)을 선택할 수 있다. 컬럼 디코더 영역들(14)에는, 라이트 드라이버들(미도시) 및 입출력 센스 앰프들(미도시)이 추가로 배치될 수 있다. 로우 디코더 영역들(16)에는, 커맨드/어드레스 제어와 관련된 로우 디코더들(미도시)이 배치될 수 있다. 로우 디코더들은 어드레스를 입력 받아 이를 디코딩하여 코어 영역의 로우 라인들(즉, 워드 라인들)을 선택하기 위한 로우 어드레스를 출력할 수 있다. 코어 영역 주변에, 관통 전극들(TSV)을 포함하는 주변 영역이 배치될 수 있다.

- [0049] 주변 영역에는, 코어 영역을 제어하기 위한 주변 회로, 관통 전극들(TSV)과 인터페이싱하기 위한 회로 및 관통 전극들(TSV)이 배치될 수 있다. 특히, 주변 영역에서, 관통 전극들(TSV)과 인터페이싱하기 위한 회로 및 관통 전극들(TSV)이 배치되는 영역을 TSV 영역(20)으로 정의할 수 있다. 제 1 코어 다이(112\_0)는 관통 전극들(TSV)을 통하여 외부(예를 들어, 베이스 다이)로부터 신호를 수신하거나, 관통 전극들(TSV)을 통하여 외부로 신호를

전송할 수 있다. 실시예에 따라, TSV 영역(20)은 평면적 관점에서 제 1 코어 다이(112\_0)의 중앙부에 위치할 수 있다. 하지만, 본 발명이 이에 한정되는 것은 아니며, TSV 영역(20)의 평면적 배치는 다양하게 변경될 수 있다.

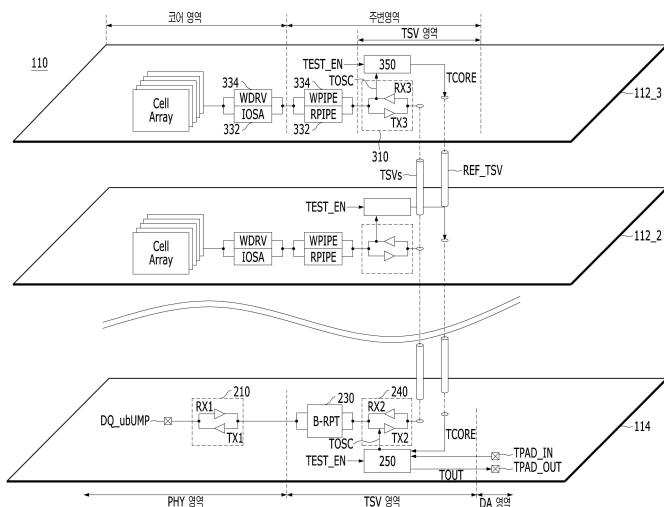

[0051] 도 5 는 도 1 의 적층형 메모리 장치(110)의 구성을 나타낸 도면이다. 설명의 편의를 위해 도 5 에는 각 다이마다 하나의 관통 전극이 도시되어 있지만, 실제로 다수의 관통 전극들(TSVs)이 배치될 수 있다. 참고로, 도 5 에는, 베이스 다이(114) 및 제 1 내지 제 4 코어 다이(114, 112\_0~112\_3)의 데이터 입출력 동작과 관련된 구성을 위주로 도시되어 있다.

[0052] 도 5 를 참조하면, 적층형 메모리 장치(110)는 베이스 다이(114) 및 제 1 내지 제 4 코어 다이(112\_0~112\_3)를 포함할 수 있다. 베이스 다이(114) 및 제 1 내지 제 4 코어 다이(114, 112\_0~112\_3)는 다수 개의 관통 전극들(TSVs)을 통해 기판에 수직 방향으로 연결되어 신호를 전달할 수 있다.

[0053] 베이스 다이(114)는, 물리 영역, TSV 영역 및 DA 영역으로 구분될 수 있다. 물리 영역에는, 데이터 패드(DQ\_uBUMP) 및 제 1 입출력 버퍼 회로(210)가 배치될 수 있다. TSV 영역에는, 양"님\* 리피터(B-RPT, 230), 제 2 입출력 버퍼 회로(240) 및 제 1 내지 제 4 코어 다이(112\_0~112\_3)를 관통하는 관통 전극들(TSVs)이 배치될 수 있다. DA 영역에는, 다수의 DA 범프들(DAB)이 형성될 수 있다. 한편, 도 5 에는 하나의 데이터 패드(DQ\_uBUMP)와 그에 대응되는 회로들이 도시되어 있지만 실제로 다수의 데이터 패드들과 그에 대응되는 회로들이 배치될 수 있다.

[0054] 데이터 패드(DQ\_uBUMP)는, 컨트롤러와 인터페이싱하는 마이크로 범프로 구성되며, 도 3 의 PHY 범프(PB)에 대응될 수 있다. 제 1 입출력 버퍼 회로(210)는, 데이터 패드(DQ\_uBUMP)를 통해 컨트롤러로부터 전달되는 데이터를 입출력할 수 있다. 제 1 입출력 버퍼 회로(210)는, 라이트 동작 시 컨트롤러로부터 데이터 패드(DQ\_uBUMP)를 통해 전달되는 라이트 데이터를 버퍼링하여 양"님\* 리피터(230)에 제공하는 입력 버퍼(RX1)와, 리드 동작 시 양"님\* 리피터(230)를 통해 전달되는 리드 데이터를 버퍼링하여 데이터 패드(DQ\_uBUMP)를 통해 컨트롤러로 제공하는 출력 버퍼(TX1)를 포함할 수 있다.

[0055] 양"님\* 리피터(230)는, 라이트 동작 시 입력 버퍼(RX1)로부터 전달되는 라이트 데이터를 재생/증폭하고, 리드 동작 시 제 2 입출력 버퍼 회로(240)로부터 전달되는 리드 데이터를 재생/증폭할 수 있다. 제 2 입출력 버퍼 회로(240)는, TSV 영역의 관통 전극(TSVs)으로부터 전달되는 데이터를 입출력할 수 있다. 제 2 입출력 버퍼 회로(240)는, 라이트 동작 시 양"님\* 리피터(230)로부터 전달되는 라이트 데이터를 버퍼링하여 관통 전극(TSV)으로 전달하는 입력 버퍼(RX2)와, 리드 동작 시 관통 전극(TSV)을 통해 전달되는 리드 데이터를 버퍼링하여 양"님\* 리피터(230)로 제공하는 출력 버퍼(TX2)를 포함할 수 있다. 제 2 입출력 버퍼 회로(240)는, 관통 전극용 인터페이스 회로로 정의할 수 있다.

[0056] 제 1 내지 제 4 코어 다이(114, 112\_0~112\_3)는 실질적으로 동일한 구성을 가지므로 제 4 코어 다이(112\_3)를 예로 들어 설명하기로 한다.

[0057] 제 4 코어 다이(112\_3)는, 코어 영역 및 주변 영역으로 구분될 수 있다. 코어 영역에는, 다수의 셀 어레이 영역들 중 어느 하나의 셀 어레이 영역이 배치될 수 있다. 코어 영역에는, 입출력 센스 앰프(332)/라이트 드라이버(334)가 추가로 배치될 수 있다. 주변 영역에는, 제 3 입출력 버퍼 회로(310), 리드 파이프 래치(322)/라이트 파이프 래치(324) 및 제 1 내지 제 4 코어 다이(112\_0~112\_3)를 관통하는 관통 전극들(TSVs)이 배치될 수 있다. 주변 영역에서, 관통 전극들(TSV) 및 관통 전극들(TSV)과 인터페이싱하기 위한 제 3 입출력 버퍼 회로(310)가 배치되는 영역을 TSV 영역으로 정의할 수 있다.

[0058] 제 3 입출력 버퍼 회로(310)는, TSV 영역의 관통 전극(TSVs)으로부터 전달되는 데이터를 입출력할 수 있다. 제 3 입출력 버퍼 회로(310)는, 라이트 동작 시 관통 전극(TSV)을 통해 전달되는 라이트 데이터를 버퍼링하여 라이트 파이프 래치(324)로 전달하는 입력 버퍼(RX3)와, 리드 동작 시 리드 파이프 래치(322)를 통해 전달되는 리드 데이터를 버퍼링하여 관통 전극(TSV)으로 제공하는 출력 버퍼(TX3)를 포함할 수 있다. 제 3 입출력 버퍼 회로(310)는, 관통 전극용 인터페이스 회로로 정의할 수 있다. 라이트 파이프 래치(324)는, 라이트 동작 시, 입력 버퍼(RX3)를 통해 전달되는 라이트 데이터를 정렬하여 라이트 드라이버(334)로 제공할 수 있다. 리드 파이프 래치(322)는, 증폭된 리드 데이터를 정렬하여 출력 버퍼(TX3)로 제공할 수 있다. 라이트 드라이버(334)는, 라이트 데이터를 셀 어레이 영역에 라이트할 수 있다. 입출력 센스 앰프(332)는, 리드 동작 시 셀 어레이 영역으로부터 출력되는 리드 데이터를 감지 증폭할 수 있다.

[0059] 한편, 제조 공정의 여러가지 요인으로 인하여 비정상적으로 형성된 관통 전극(TSV)은, 정상적으로 형성된 관통 전극(TSV) 보다 큰 저항값(resistance) 또는 커패시턴스값(Capacitance)를 가질 수 있다. 이 때, 비정상적으로

형성된 관통 전극(TSV)은 물리적인 연결 유무를 테스트하는 오픈/ショート(Open/Short) 테스트는 통과하더라도 신호 전송용으로는 사용되기 부적합할 수 있다. 기존에는, 관통 전극(TSV)의 신호 전송 상태를 테스트하기 위해서, 코어 영역의 셀 어레이 영역들에 데이터를 라이트하고 이를 다시 리드하여 정상적인 데이터인지를 확인하는 과정을 수행했다. 즉, 관통 전극(TSV)의 신호 전송 상태를 테스트하기 위해, 관통 전극(TSV)과 직접적인 관련이 없는 부가적인 회로들(예를 들어, 코어 영역의 셀 어레이 영역들, 주변 영역의 센스 앰프, 라이트 드라이버, 파이프 래치 등)의 동작이 이루어져야 하기 때문에 관통 전극(TSV)만의 특성 및 동작 전류 등을 확인하기에 어려움이 있었다.

- [0060] 이하, 제안 발명에서는, 코어 영역 및 주변 영역에 배치된 부가적인 회로를 배제하고, 관통 전극을 동작시키기 위한 최소한의 구성, 즉, 관통 전극 및 관통 전극용 인터페이스 회로만을 구동시켜 관통 전극(TSV)의 신호 전송 상태를 웨이퍼 레벨에서 테스트할 수 있는 방법에 대해 논의하고자 한다.

- [0062] 도 6 은 본 발명의 실시예에 따른 적층형 메모리 장치(110)의 구성을 나타낸 도면이다. 도 5 과 도 6 에서, 동일한 구성은 동일한 도면 부호를 부여하였으며, 관련된 상세 설명은 생략한다.

- [0063] 도 6 을 참조하면, 적층형 메모리 장치(110)는 베이스 다이(114) 및 제 1 내지 제 4 코어 다이(112\_0~112\_3)를 포함할 수 있다. 베이스 다이(114) 및 제 1 내지 제 4 코어 다이(114, 112\_0~112\_3)는 다수 개의 관통 전극(TSVs) 및 적어도 하나의 기준 관통 전극(REF\_TSV)을 통해 기판에 수직 방향으로 연결되어 신호를 전달할 수 있다.

- [0064] 베이스 다이(114)는 제 1 테스트 회로(250)를 포함할 수 있다. 제 1 테스트 회로(250)는, 테스트 동작 시 활성화되는 테스트 신호(TEST\_EN)에 따라 오실레이팅 신호(TOSC)를 다수의 관통 전극들(TSVs) 중 적어도 하나의 타겟 관통 전극에 전달할 수 있다. 타겟 관통 전극은, 기판에 수직 방향, 즉, 열(Column) 방향으로 연결된 관통 전극들(TSVs) 일 수 있다. 제 1 테스트 회로(250)는, 테스트 동작 시 오실레이팅 신호(TOSC)를 제 2 입출력 버퍼 회로(240)의 출력 버퍼(TX2)에 제공할 수 있다. 제 1 테스트 회로(250)는, 오실레이팅 신호(TOSC)를 토대로 생성된 베이스 신호(TBASE, 미도시)와 기준 관통 전극(REF\_TSV)을 통해 전달되는 코어 신호(TCORE)를 비교하여 테스트 출력 신호(TOUT)를 출력할 수 있다. 베이스 다이(114)는, 도 3 에서 설명된 물리 영역, TSV 영역 및 DA 영역을 포함할 수 있다. 바람직하게, 제 1 테스트 회로(250)는, 베이스 다이(114)의 TSV 영역에 배치될 수 있다. 베이스 다이(114)의 데이터 패드(DQ\_uBUMP), 제 1 입출력 버퍼 회로(210), 양"념\* 리피터(B-RPT, 230), 및 제 2 입출력 버퍼 회로(240)는 도 5 의 구성과 동일한 바 설명을 생략한다.

- [0065] 한편, 베이스 다이(114)에는, 테스트 출력 신호(TOUT)를 외부 장치(예를 들어, 테스트 장치)로 출력하기 위한 테스트 출력 패드(TPAD\_OUT)가 구비될 수 있다. 또한, 베이스 다이(114)에는, 오실레이팅 신호(TOSC)를 외부 장치로부터 입력받기 위한 테스트 입력 패드(TPAD\_IN)가 구비될 수 있다. 테스트 출력 패드(TPAD\_OUT) 및 테스트 입력 패드(TPAD\_IN)는, DA 범프들(DAB)로 구성되어 베이스 다이(114)의 DA 영역에 배치될 수 있다.

- [0066] 제 1 내지 제 4 코어 다이(114, 112\_0~112\_3)는 각각 제 2 테스트 회로(350)를 포함할 수 있다. 제 2 테스트 회로(350)는, 테스트 신호(TEST\_EN)에 따라 타겟 관통 전극(TSV)을 통해 전달되는 오실레이팅 신호(TOSC)에 대응되는 코어 신호(TCORE)를 생성하고, 코어 신호(TCORE)를 기준 관통 전극(REF\_TSV)으로 전달할 수 있다. 제 2 테스트 회로(350)는, 테스트 동작 시 제 3 입출력 버퍼 회로(310)의 입력 버퍼(RX3)를 통해 제공되는 오실레이팅 신호(TOSC)를 수신할 수 있다. 제 1 내지 제 4 코어 다이(114, 112\_0~112\_3)는 각각 도 4 에서 설명된 코어 영역 및 주변 영역을 포함할 수 있다. 바람직하게, 제 2 테스트 회로(350)는 주변 영역에 배치될 수 있다. 더 바람직하게, 제 2 테스트 회로(350)는, 주변 영역의 TSV 영역에 배치될 수 있다. 제 1 내지 제 4 코어 다이(114, 112\_0~112\_3)의 제 3 입출력 버퍼 회로(310), 리드 파이프 래치(322)/라이트 파이프 래치(324) 및 입출력 센스 앰프(332)/라이트 드라이버(334) 및 셀 어레이 영역은 도 5 의 구성과 동일한 바 설명을 생략한다.

- [0067] 한편, 부트업 동작이나 초기 동작 시, 칩 아이디 신호가 각 코어 다이 별로 할당될 수 있다. 예를 들어, 제 1 코어 다이(112\_0)에는 '00'의 칩 아이디 신호가 할당되고, 제 2 코어 다이(112\_1)에는 '01'의 칩 아이디 신호가 할당되고, 제 3 코어 다이(112\_2)에는 '10'의 칩 아이디 신호가 할당되고, 제 4 코어 다이(112\_3)에는 '11'의 칩 아이디 신호가 할당될 수 있다. 실시예에 따라, 이러한 칩 아이디 신호(즉, 적층 정보)를 이용하여 코어 다이 별 테스트 신호(TEST\_EN)가 활성화되어 해당하는 제 2 테스트 회로(250)가 동작할 수 있다.

- [0069] 이하, 도면을 참조하여 제 1 테스트 회로(250) 및 제 2 테스트 회로(350)의 구체적인 구성을 설명한다.

- [0070] 도 7 은 제 1 실시예에 따른 도 6 의 적층형 메모리 장치(110)의 제 1 테스트 회로(250) 및 제 2 테스트 회로(350)의 구성을 설명하기 위한 도면이다. 도 7 에서는, 제 1 내지 제 4 코어 다이(114, 112\_0~112\_3) 중 어느

하나의 코어 다이(112\_x)의 제 2 테스트 회로(350)가 활성화된 경우가 도시되어 있다.

[0071] 도 7 을 참조하면, 베이스 다이(114)의 물리 영역에는 제 1 입출력 버퍼 회로(210)가 배치되고, TSV 영역에는 타겟 관통 전극(TSV), 기준 관통 전극(REF\_TSV) 및 제 2 입출력 버퍼 회로(240)가 배치된다. 바람직하게, 제 1 테스트 회로(250)는, 베이스 다이(114)의 TSV 영역에 배치될 수 있다. 제 1 입출력 버퍼 회로(210) 및 제 2 입출력 버퍼 회로(240) 사이의 TSV 영역에는, 양"웜\* 리피터(B-RPT, 230)가 추가로 배치될 수 있다.

[0072] 제 1 테스트 회로(250)는, 패턴 생성기(PG), 제 1 카운터(CNT1), 제 1 직렬화기(SER1) 및 비교기(CMP)를 구비할 수 있다.

[0073] 패턴 생성기(PG)는, 테스트 신호(TEST\_EN)에 따라 오실레이팅 신호(TOSC)를 생성하여 제 2 입출력 버퍼 회로(240)의 출력 버퍼(TX2)에 제공할 수 있다. 출력 버퍼(TX2)는, 오실레이팅 신호(TOSC)를 타겟 관통 전극(TSV)을 통해 코어 다이(112\_x)로 전달할 수 있다. 테스트 신호(TEST\_EN)는 테스트 동작 시 활성화되는 신호이다. 바람직하게, 테스트 신호(TEST\_EN)는, 주파수 정보(FREQ\_INF)를 가지는 멀티 비트의 신호일 수 있다. 예를 들어, 테스트 신호(TEST\_EN)는 3비트의 신호(TEST\_EN<0:2>)로 구성될 수 있다. 테스트 신호(TEST\_EN)의 최하위 비트(TEST\_EN<0>)는 테스트 동작 시 로직 하이 레벨로 활성화되고, 나머지 두 비트(TEST\_EN<1:2>)는 주파수 정보(FREQ\_INF)에 따라 “00”, “01”, “10”, “11” 중 하나의 값을 가질 수 있다. 패턴 생성기(PG)는, 테스트 신호(TEST\_EN)의 주파수 정보(FREQ\_INF)에 따라 소정 주기로 토글링하는 오실레이팅 신호(TOSC)를 생성하여 제 2 입출력 버퍼 회로(240)의 출력 버퍼(TX2)에 제공할 수 있다. 예를 들어, 테스트 신호(TEST\_EN<0:2>)가 “101” 일 때는 제 1 주파수로 토글링하는 오실레이팅 신호(TOSC)를 생성하고, 테스트 신호(TEST\_EN<0:2>)가 “110” 일 때는 제 1 주파수 보다 높은 제 2 주파수로 토글링하는 오실레이팅 신호(TOSC)를 생성하고, 테스트 신호(TEST\_EN<0:2>)가 “111” 일 때는 제 2 주파수 보다 높은 제 3 주파수로 토글링하는 오실레이팅 신호(TOSC)를 생성할 수 있다. 실시예에 따라, 오실레이팅 신호(TOSC)는, 소정 주기로 토글링 할 수도 있고, 특정 패턴으로 토글링 할 수도 있다. 제 1 카운터(CNT1)는, 테스트 신호(TEST\_EN)에 따라 오실레이팅 신호(TOSC)를 카운팅하여 베이스 카운팅 신호(BCNT<0:n>)를 생성할 수 있다. 예를 들어, 제 1 카운터(CNT1)는, 테스트 신호(TEST\_EN)의 최하위 비트(TEST\_EN<0>)에 따라 활성화되어 오실레이팅 신호(TOSC)를 카운팅할 수 있다. 제 1 직렬화기(SER1)는, 베이스 카운팅 신호(BCNT<0:n>)를 직렬화하여 베이스 신호(TBASE)를 출력할 수 있다. 비교기(CMP)는, 코어 신호(TCORE)와 베이스 신호(TBASE)를 비교하여 테스트 출력 신호(TOUT)를 출력할 수 있다. 코어 신호(TCORE)는, 기준 관통 전극(REF\_TSV)을 통해 제공될 수 있다.

[0074] 또한, 제 1 테스트 회로(250)는 베이스 카운팅 신호(BCNT<0:n>)를 저장하여 제 1 직렬화기(SER1)에 제공하는 제 1 레지스터(REG1)를 더 구비할 수 있다. 바람직하게, 제 1 레지스터(REG1)는, 테스트 클럭 신호(TCLK)에 동기되어 베이스 카운팅 신호(BCNT<0:n>)를 저장할 수 있다.

[0075] 코어 다이(112\_x)의 코어 영역에는, 셀 어레이 영역 및 입출력 센스 앰프(332)/라이트 드라이버(334)가 배치되고, 주변 영역에는, 입출력 버퍼 회로(310), 리드 파이프 래치(322)/라이트 파이프 래치(324), 타겟 관통 전극(TSV), 기준 관통 전극(REF\_TSV)이 배치된다. 바람직하게, 제 2 테스트 회로(350)는, 코어 다이(112\_x)의 주변 영역의 TSV 영역에 배치될 수 있다.

[0076] 제 2 테스트 회로(350)는, 제 2 카운터(CNT2) 및 제 2 직렬화기(SER2)를 포함할 수 있다.

[0077] 제 2 카운터(CNT2)는, 테스트 신호(TEST\_EN)에 따라 활성화되며, 제 3 입출력 버퍼 회로(310)의 입력 버퍼(RX3)를 통해 전달되는 오실레이팅 신호(TOSC)를 카운팅하여 코어 카운팅 신호(CCNT<0:n>)를 생성할 수 있다. 예를 들어, 제 2 카운터(CNT2)는, 멀티 비트의 테스트 신호(TEST\_EN)의 최하위 비트(TEST\_EN<0>)에 따라 활성화될 수 있다. 제 2 직렬화기(SER2)는, 코어 카운팅 신호(CCNT<0:n>)를 직렬화하여 코어 신호(TCORE)를 기준 관통 전극(REF\_TSV)으로 제공할 수 있다.

[0078] 또한, 제 2 테스트 회로(350)는 코어 카운팅 신호(CCNT<0:n>)를 저장하여 제 2 직렬화기(SER2)에 제공하는 제 2 레지스터(REG2)를 더 구비할 수 있다. 바람직하게, 제 2 레지스터(REG2)는, 테스트 클럭 신호(TCLK)에 동기되어 코어 카운팅 신호(CCNT<0:n>)를 저장할 수 있다. 제안 발명의 실시예에서는, 제 1 레지스터(REG1) 및 제 2 레지스터(REG2)는, 동일한 테스트 클럭 신호(TCLK)에 따라 베이스 카운팅 신호(BCNT<0:n>) 및 코어 카운팅 신호(CCNT<0:n>)를 각각 저장한 후 저장된 카운팅 신호를 직렬화함으로써 코어 다이(112\_x)와 베이스 다이(114) 간의 신호 전송 시 발생하는 신호의 스큐를 최소화할 수 있다.

[0080] 한편, 제 1 실시예에서는, 베이스 다이(114)의 내부에서 오실레이팅 신호(TOSC)가 생성되는 경우를 예로 들어 설명하였다. 제 2 실시예에서는, 외부 테스트 장치로부터 오실레이팅 신호(TOSC)를 입력받거나 내부에서 오실레이팅 신호(TOSC)를 생성하는 경우를 예로 들어 설명하였다.

이팅 신호(TOSC)를 생성하는 경우를 모두 지원하는 예를 설명하기로 한다.

[0081] 도 8 은 제 2 실시예에 따른 도 6 의 적층형 메모리 장치(110)의 제 1 테스트 회로(250) 및 제 2 테스트 회로(350)의 구성을 설명하기 위한 도면이다. 도 7 및 도 8 에서 동일한 구성은 동일한 도면 부호를 부여하였다.

[0082] 도 8 을 참조하면, 제 1 테스트 회로(250)는, 패턴 생성기(PG), 멱성 회로(M1), 제 1 카운터(CNT1), 제 1 레지스터(REG1), 제 1 직렬화기(SER1) 및 비교기(CMP)를 구비할 수 있다.

[0083] 패턴 생성기(PG)는, 테스트 신호(TEST\_EN)에 따라 제 1 예비 오실레이팅 신호(POSC1)를 생성할 수 있다. 바람직하게, 테스트 신호(TEST\_EN)는, 주파수 정보(FREQ\_INF)를 가지는 멀티 비트의 신호일 수 있으며, 패턴 생성기(PG)는, 테스트 신호(TEST\_EN)의 주파수 정보(FREQ\_INF)에 따라 소정 주기로 토클링하는 제 1 예비 오실레이팅 신호(POSC1)를 생성할 수 있다.

[0084] 멱성 회로(M1)는, 테스트 선택 신호(TEST\_EN\_S)에 따라, 제 1 예비 오실레이팅 신호(POSC1) 또는 제 2 예비 오실레이팅 신호(POSC2)를 선택하여 제 2 입출력 버퍼 회로(240)의 출력 버퍼(TX2)에 오실레이팅 신호(TOSC)로 제공할 수 있다. 출력 버퍼(TX2)는, 오실레이팅 신호(TOSC)를 타겟 관통 전극(TSV)을 통해 코어 다이(112\_X)로 전달할 수 있다. 테스트 선택 신호(TEST\_EN\_S)는 외부 테스트 장치로부터 오실레이팅 신호(TOSC)를 입력받는 경우 제 1 로직 레벨(예를 들어, 로직 로우 레벨)을 가지고, 내부에서 오실레이팅 신호(TOSC)를 생성하는 경우 제 2 로직 레벨(예를 들어, 로직 하이 레벨)을 가지도록 설정될 수 있다. 제 2 예비 오실레이팅 신호(POSC2)는, 테스트 입력 패드(TPAD\_IN)를 통해 외부 테스트 장치로부터 입력되는 신호이다. 예를 들어, 멱성 회로(M1)는, 로직 하이 레벨의 테스트 선택 신호(TEST\_EN\_S)에 따라 제 1 예비 오실레이팅 신호(POSC1)를 선택하고, 로직 로우 레벨의 테스트 선택 신호(TEST\_EN\_S)에 따라 제 2 예비 오실레이팅 신호(POSC2)를 선택할 수 있다.

[0085] 제 1 카운터(CNT1)는, 테스트 신호(TEST\_EN)에 따라, 제 1 예비 오실레이팅 신호(POSC1) 혹은 제 2 예비 오실레이팅 신호(POSC2)를 카운팅하여 베이스 카운팅 신호(BCNT<0:n>)를 생성할 수 있다. 제 1 레지스터(REG1)는, 테스트 클럭 신호(TCLK)에 따라 베이스 카운팅 신호(BCNT<0:n>)를 저장할 수 있다. 제 1 직렬화기(SER1)는, 제 1 레지스터(REG1)에 저장된 베이스 카운팅 신호(BCNT<0:n>)를 직렬화하여 베이스 신호(TBASE)를 출력할 수 있다. 비교기(CMP)는, 코어 신호(TCORE)와 베이스 신호(TBASE)를 비교하여 테스트 출력 신호(TOUT)를 출력할 수 있다.

[0086] 도 8 의 제 2 테스트 회로(350)는 도 7 의 제 2 테스트 회로(350)와 실질적으로 동일한 구성을 가지므로 상세한 설명은 생략하기로 한다.

[0087] 도 9 는 도 7 및 도 8 의 적층형 메모리 장치의 테스트 동작을 설명하기 위한 타이밍도이다.

[0088] 도 9 를 참조하면, 다수 개의 관통 전극(TSVs) 및 적어도 하나의 기준 관통 전극(REF\_TSV)을 통해 기판에 수직 방향으로 연결되어 신호를 전달하는 베이스 다이(114) 및 제 1 내지 제 4 코어 다이(114, 112\_0~112\_3)를 포함하는 적층형 메모리 장치(110)의 테스트 방법이 설명되어 있다.

[0089] 베이스 다이(114)에서는, 오실레이팅 신호(TOSC)를 다수의 관통 전극들(TSVs) 중 적어도 하나의 타겟 관통 전극(TSV)에 전달하고, 오실레이팅 신호(TOSC)를 토대로 베이스 신호(TBASE)를 생성할 수 있다(S910). 보다 상세하게, 베이스 다이(114)의 제 1 테스트 회로(250)는, 주파수 정보(FREQ\_INF)를 가지는 멀티 비트의 테스트 신호(TEST\_EN)에 따라 소정 주기로 토클링하는 오실레이팅 신호(TOSC)를 생성할 수 있다. 또는, 제 1 테스트 회로(250)는, 테스트 입력 패드(TPAD\_IN)를 통해 외부 테스트 장치로부터 입력되는 오실레이팅 신호(TOSC)를 입력받아 타겟 관통 전극(TSV)에 전달할 수 있다. 제 1 테스트 회로(250)는, 오실레이팅 신호(TOSC)를 카운팅하여 베이스 카운팅 신호(BCNT<0:n>)를 생성하고, 테스트 클럭 신호(TCLK)에 따라 베이스 카운팅 신호(BCNT<0:n>)를 저장하고, 저장된 베이스 카운팅 신호(BCNT<0:n>)를 직렬화하여 베이스 신호(TBASE)를 생성할 수 있다. 참고로, 테스트 동작 시, 적층된 다이 및 그들의 관통 전극으로 인한 로딩 영향을 최소화하기 위해, 제 1 테스트 회로(250)는, 리드/라이트 동작 등의 노멀 동작 시 전달되는 노멀 신호의 전송 속도보다는 저속으로 동작하도록 오실레이팅 신호(TOSC)를 생성할 수 있다.

[0090] 코어 다이(112\_X)에서는, 타겟 관통 전극(TSV)을 통해 전달되는 오실레이팅 신호(TOSC)를 토대로 코어 신호(TCORE)를 생성할 수 있다(S920). 보다 상세하게, 코어 다이(112\_X)의 제 2 테스트 회로(350)는, 오실레이팅 신호(TOSC)를 카운팅하여 코어 카운팅 신호(CCNT<0:n>)를 생성하고, 테스트 클럭 신호(TCLK)에 따라 코어 카운팅 신호(CCNT<0:n>)를 저장하고, 저장된 코어 카운팅 신호(CCNT<0:n>)를 직렬화하여 코어 신호(TCORE)를 생성할 수 있다. 이 때, 베이스 다이(114) 및 코어 다이(112\_X)의 제 1 및 제 2 레지스터(REG1, REG2)는, 동일 테스트 클럭 신호(TCLK)에 따라 베이스 카운팅 신호(BCNT<0:n>) 및 코어 카운팅 신호(CCNT<0:n>)를 각각 저장하고, 제 1 및 제 2 직렬화부(SER1, SER2)가 저장된 카운팅 신호를 각각 직렬화함으로써 코어 다이(112\_X)와 베이스 다이

(114) 간의 신호 전송 시 발생하는 신호의 스케줄 최소화할 수 있다.

[0092] 이후, 베이스 다이(114)의 제 1 테스트 회로(250)는, 기준 관통 전극(REF\_TSV)을 통해 전달되는 코어 신호(TCORE)와 베이스 신호(TBASE)를 비교하여 테스트 출력 신호(TOUT)를 출력할 수 있다(S930). 베이스 다이(114)의 제 1 테스트 회로(250)는, 테스트 출력 신호(TOUT)를, DA 영역에 배치된 테스트 출력 패드(TPAD\_OUT)를 통해 출력할 수 있다(S940).

[0093] 한편, 외부 테스트 장치는 테스트 신호(TEST\_EN)의 주파수 정보(FREQ\_INF)를 변경할 수 있다. 예를 들어, 테스트 장치는, 3비트의 테스트 신호(TEST\_EN<0:2>)를 “100”, “101”, “110”, “111”의 순서로 순차적으로 변경하거나, 테스트 입력 패드(TPAD\_IN)를 통해 제 1 내지 제 4 주파수로 토클링하는 오실레이팅 신호(TOSC)를 순차적으로 제공할 수 있다. 베이스 다이(114)의 제 1 테스트 회로(250) 및 코어 다이(112\_x)의 제 2 테스트 회로(350)는, 제 1 내지 제 3 주파수로 토클링하는 오실레이팅 신호(TOSC)를 이용하여 상기 단계(S910~S930)을 반복 수행할 수 있다. 테스트 장치는, 각 주파수에 따른 테스트 출력 신호(TOUT)를 토대로 신호 전송율에 따른 타겟 관통 전극의 동작 특성을 파악할 수 있다.

[0094] 상기와 같이, 제안된 실시예에 따른 적층형 메모리 장치의 테스트 동작은, 적층형 메모리 장치가 컨트롤러와 패키징 되기 전의 웨이퍼 레벨에서 수행될 수 있다. 즉, 제안된 실시예에 따른 적층형 메모리 장치는, 관통 전극 용 인터페이스 회로만을 이용하여 관통 전극을 테스트함으로써 웨이퍼 레벨에서 관통 전극의 신호 전송 상태를 정확하게 파악할 수 있다. 또한, 본 발명의 실시예에 따른 적층형 메모리 장치는, 다양한 주기로 토클링하는 오실레이팅 신호(TOSC)를 생성하여 타겟 관통 전극으로 인가하여 테스트함으로써 신호 전송율에 따른 관통 전극의 동작 특성을 파악할 수 있다. 따라서, 신호 전송의 정확성 및 효율을 증가시킬 수 있다. 이로써, 관통 전극의 정상 동작 여부를 웨이퍼 레벨에서 검증함으로써 전체 칩 수율을 향상시킬 수 있다.

[0095] 이하, 제 3 실시예에서는, 카운팅 및 직렬화 동작 없이 관통 전극을 테스트하는 경우를 지원하는 예를 설명하기로 한다.

[0097] 도 10 은 제 3 실시예에 따른 적층형 메모리 장치(110)의 제 1 테스트 회로(250) 및 제 2 테스트 회로(350)의 구성을 설명하기 위한 도면이다. 도 7 및 도 10 에서, 동일한 구성은 동일한 도면 부호를 부여하였으며, 관련된 상세 설명은 생략한다.

[0098] 도 10 을 참조하면, 제 1 테스트 회로(250)는, 패턴 생성기(PG), 제 1 카운터(CNT1), 제 1 레지스터(REG1), 제 1 직렬화기(SER1), 비교기(CMP) 및 제 1 먹성 회로(M2)를 구비할 수 있다. 도 10 의 패턴 생성기(PG), 제 1 카운터(CNT1), 제 1 레지스터(REG1), 제 1 직렬화기(SER1) 및 비교기(CMP)는 도 7 의 구성들과 실질적으로 동일한 구성을 가지므로 상세한 설명은 생략하기로 한다. 제 1 먹성 회로(M2)는, 테스트 선택 신호(TEST\_EN\_S)에 따라, 비교기(CMP)로부터 출력되는 예비 테스트 출력 신호(TOUT\_PRE) 또는 기준 관통 전극(REF\_TSV)을 통해 제공되는 코어 신호(TCORE)를 선택하여 테스트 출력 신호(TOUT)를 출력할 수 있다. 예를 들어, 제 1 먹성 회로(M2)는, 테스트 선택 신호(TEST\_EN\_S)가 제 1 로직 레벨(예를 들어, 로직 로우 레벨)을 가지는 경우 코어 신호(TCORE)를 선택하고, 테스트 선택 신호(TEST\_EN\_S)가 제 2 로직 레벨(예를 들어, 로직 하이 레벨)을 가지는 경우 예비 테스트 출력 신호(TOUT\_PRE)를 선택할 수 있다.

[0099] 제 2 테스트 회로(350)는, 제 2 카운터(CNT2), 제 2 레지스터(REG2), 제 2 직렬화기(SER2) 및 제 2 먹성 회로(M3)를 구비할 수 있다. 도 10 의 제 2 카운터(CNT2), 제 2 레지스터(REG2) 및 제 2 직렬화기(SER2)는 도 7 의 구성들과 실질적으로 동일한 구성을 가지므로 상세한 설명은 생략하기로 한다. 제 2 먹성 회로(M3)는, 테스트 선택 신호(TEST\_EN\_S)에 따라, 제 2 직렬화기(SER2)로부터 제공되는 예비 코어 신호(TCORE\_PRE) 또는 제 3 입출력 버퍼 회로(310)의 입력 버퍼(RX3)를 통해 전달되는 오실레이팅 신호(TOSC)를 선택하여 기준 관통 전극(REF\_TSV)으로 제공할 수 있다. 예를 들어, 제 2 먹성 회로(M3)는, 테스트 선택 신호(TEST\_EN\_S)가 로직 로우 레벨일 때 오실레이팅 신호(TOSC)를 선택하고, 테스트 선택 신호(TEST\_EN\_S)가 로직 하이 레벨일 때 예비 코어 신호(TCORE\_PRE)를 선택할 수 있다.

[0100] 상기의 구성으로 적층형 메모리 장치의 테스트 동작을 설명하면 다음과 같다.

[0101] 테스트 선택 신호(TEST\_EN\_S)가 로직 하이 레벨로 설정된 경우, 적층형 반도체 장치의 테스트 동작은 도 9 에서 설명된 S910 내지 S940의 단계의 동작과 실질적으로 동일하다.

[0102] 테스트 선택 신호(TEST\_EN\_S)가 로직 로우 레벨로 설정된 경우, 제 1 테스트 회로(250)의 패턴 생성기(PG)는, 테스트 신호(TEST\_EN)에 따라 오실레이팅 신호(TOSC)를 생성하여 제 2 입출력 버퍼 회로(240)의 출력 버퍼(TX2)에 제공한다. 제 2 테스트 회로(350)의 제 2 먹성 회로(M3)는, 타겟 관통 전극(TSV)을 통해 전달되는 오실레이팅 신호(TOSC)를 선택하여 기준 관통 전극(REF\_TSV)으로 제공된다.

이팅 신호(TOSC)를 그대로 기준 관통 전극(REF\_TSV)으로 제공한다. 제 1 테스트 회로(250)의 제 1 멱성 회로(M2)는, 타겟 관통 전극(TSV)을 통해 제공되는 코어 신호(TCORE)를 선택하여 그대로 테스트 출력 신호(TOUT)로 출력할 수 있다. 테스트 출력 신호(TOUT)는, DA 영역에 배치된 테스트 출력 패드(TPAD\_OUT)를 통해 외부 테스트 장치로 출력될 수 있다.

[0104] 이하에서는, 하나의 기준 관통 전극(REF\_TSV)을 이용하여  $m$  개의 타겟 관통 전극들(TSVs)을 테스트하는 방법에 대해 설명하기로 한다.

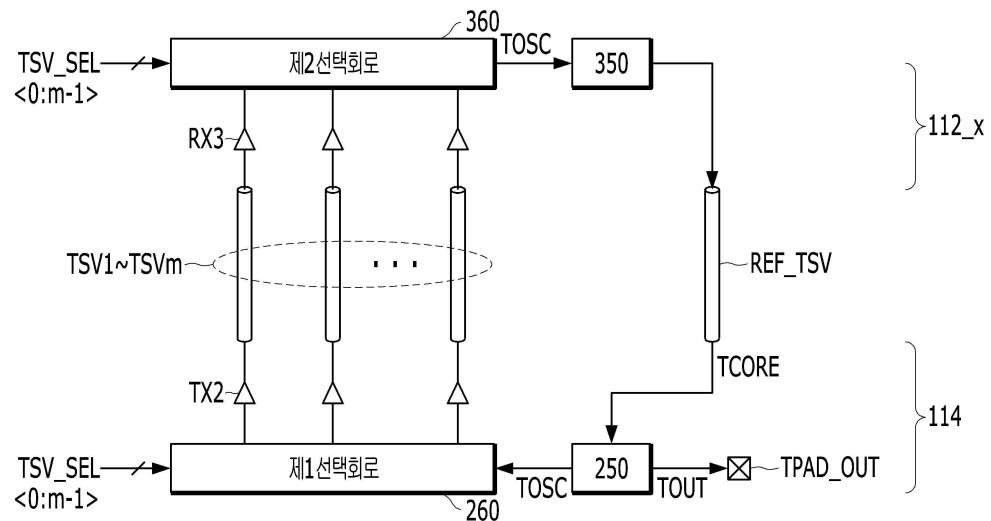

[0105] 도 11 은 본 발명의 다른 실시예에 따른 적층형 메모리 장치(110)의 구성을 개략적으로 나타낸 도면이다. 도 11 의 구성은 도 6 의 구성에서 테스트를 위해 필요한 구성만을 도시하였으며, 나머지 구성에 대한 설명은 생략한다.

[0106] 도 11 을 참조하면, 베이스 다이(114)는 제 1 테스트 회로(250) 및 제 1 선택 회로(260)를 포함하고, 코어 다이(112\_x)는 제 1 테스트 회로(350) 및 제 2 선택 회로(360)를 포함할 수 있다. 도 11 의 제 1 테스트 회로(250) 및 제 1 테스트 회로(350)는 도 7, 도 8 및 도 10 의 어느 하나의 구성과 실질적으로 동일할 수 있다.

[0107] 제 1 테스트 회로(250)는, 오실레이팅 신호(TOSC)를 제 1 선택 회로(260)로 제공한다. 제 1 선택 회로(260)는, 관통 전극 선택 신호(TSV\_SEL<0:m-1>)에 따라 제 1 내지 제  $m$  타겟 관통 전극(TSV1~TSVm) 중 하나를 선택하고, 제 1 테스트 회로(250)에서 제공되는 오실레이팅 신호(TOSC)를 선택된 타겟 관통 전극에 연결된 출력 버퍼(TX2)로 전달할 수 있다.

[0108] 제 2 선택 회로(360)는, 관통 전극 선택 신호(TSV\_SEL<0:m-1>)에 따라 제 1 내지 제  $m$  타겟 관통 전극(TSV1~TSVm) 중 하나를 선택하고, 선택된 타겟 관통 전극에 연결된 입력 버퍼(RX3)를 통해 전달되는 오실레이팅 신호(TOSC)를 제 1 테스트 회로(350)로 전달할 수 있다.

[0109] 상기의 구성으로 적층형 메모리 장치의 테스트 동작을 설명하면 다음과 같다.

[0110] 먼저, 관통 전극 선택 신호(TSV\_SEL<0:m-1>)의 제 1 비트(TSV\_SEL<0>)가 활성화됨에 따라 제 1 타겟 관통 전극들(TSV1)이 선택되고, 도 9 에서 설명된 S910 내지 S940의 단계가 수행될 수 있다. 이 때, 테스트 신호(TEST\_EN)의 주파수 정보(FREQ\_INF)가 변경됨에 따라 S910 내지 S940의 단계가 반복적으로 수행될 수 있다. 외부 테스트 장치는, 각 주파수에 따른 테스트 출력 신호(TOUT)를 토대로 신호 전송율에 따른 타겟 관통 전극의 동작 특성을 파악할 수 있다.

[0111] 이후, 관통 전극 선택 신호(TSV\_SEL<0:m-1>)의 각 비트가 순차적으로 활성화됨에 따라 제 2 내지 제  $m$  타겟 관통 전극((TSV2~TSVm))이 순차적으로 선택되고, 도 9 에서 설명된 S910 내지 S940의 단계가 수행될 수 있다. 마찬가지로, 테스트 신호(TEST\_EN)의 주파수 정보(FREQ\_INF)가 변경됨에 따라 S910 내지 S940의 단계가 반복적으로 수행되고, 외부 테스트 장치는, 각 주파수에 따른 테스트 출력 신호(TOUT)를 토대로 신호 전송율에 따른 타겟 관통 전극의 동작 특성을 파악할 수 있다.

[0112] 이 때, 다수의 관통 전극들의 특성을 하나의 기준 관통 전극을 통해서 모니터링할 수 있다. 즉, 통일된 기준으로 다수의 관통 전극들의 특성을 모니터링함으로써 신호 전송율에 따른 관통 전극의 동작 특성을 더 정확히 파악할 수 있다.

[0114] 본 발명의 기술 사상은 상기 바람직한 실시예에 따라 구체적으로 기록되었으나, 상기한 실시예는 그 설명을 위한 것이며 그 제한을 위한 것이 아님을 주의하여야 한다. 또한, 본 발명의 기술 분야의 통상의 전문가라면 본 발명의 기술 사상의 범위 내에서 다양한 실시예가 가능함을 이해할 수 있을 것이다.

[0115] 예컨대, 전술한 실시예에서 예시한 논리 게이트 및 트랜지스터는 입력되는 신호의 극성에 따라 그 위치 및 종류가 다르게 구현되어야 할 것이다.

## 도면

## 도면1

## 도면2

## 도면3

도면4

112\_0

도면5

도면6

도면7

## 도면8

## 도면9

도면 10

도면11