(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4128763号

(P4128763)

(45) 発行日 平成20年7月30日(2008.7.30)

(24) 登録日 平成20年5月23日(2008.5.23)

|               |               |

|---------------|---------------|

| (51) Int.Cl.  | F 1           |

| HO 1 L 21/822 | (2006.01)     |

| HO 1 L 27/04  | (2006.01)     |

| HO 3 K 17/693 | (2006.01)     |

|               | HO 1 L 27/04  |

|               | HO 1 L 27/04  |

|               | HO 3 K 17/693 |

|               | A             |

|               | B             |

|               | D             |

請求項の数 17 (全 17 頁)

|              |                               |           |                |

|--------------|-------------------------------|-----------|----------------|

| (21) 出願番号    | 特願2001-308693 (P2001-308693)  | (73) 特許権者 | 000003078      |

| (22) 出願日     | 平成13年10月4日 (2001.10.4)        |           | 株式会社東芝         |

| (65) 公開番号    | 特開2002-203910 (P2002-203910A) |           | 東京都港区芝浦一丁目1番1号 |

| (43) 公開日     | 平成14年7月19日 (2002.7.19)        | (74) 代理人  | 100058479      |

| 審査請求日        | 平成15年12月8日 (2003.12.8)        |           | 弁理士 鈴江 武彦      |

| (31) 優先権主張番号 | 特願2000-330973 (P2000-330973)  | (74) 代理人  | 100091351      |

| (32) 優先日     | 平成12年10月30日 (2000.10.30)      |           | 弁理士 河野 哲       |

| (33) 優先権主張国  | 日本国 (JP)                      | (74) 代理人  | 100088683      |

## 前置審査

|          |           |

|----------|-----------|

| (74) 代理人 | 弁理士 中村 誠  |

| (74) 代理人 | 100084618 |

|          | 弁理士 村松 貞男 |

| (74) 代理人 | 100092196 |

|          | 弁理士 橋本 良郎 |

| (74) 代理人 | 100070437 |

|          | 弁理士 河井 将次 |

最終頁に続く

(54) 【発明の名称】電圧切り替え回路

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の電圧を出力する能力を有する第1の回路と、

第2の電圧を出力する能力を有する第2の回路と、

前記第1の回路の出力ノードと前記第2の回路の出力ノードとの間に接続され、それぞれゲート絶縁膜を有する複数のトランジスタにより構成される第3の回路とを具備し、

前記複数のトランジスタは、しきい値電圧が互いに異なり、電流駆動能力が互いに異なる直列接続されたデプレッション型の第1、第2のトランジスタであることを特徴する電圧切り替え回路。

## 【請求項 2】

前記第1、第2のトランジスタは、異なるウエルに形成されていることを特徴とする請求項1記載の電圧切り替え回路。

## 【請求項 3】

前記第1、第2のトランジスタのうち一方は半導体基板上に形成され、他方は半導体基板と同極性のウエルに形成されることを特徴とする請求項1記載の電圧切り替え回路。

## 【請求項 4】

前記第1、第2のトランジスタは、同極性であることを特徴とする請求項1記載の電圧切り替え回路。

## 【請求項 5】

前記第2の電圧は、前記第1の電圧よりも高い電圧であり、かつ前記第2の電圧は、電

源電圧より高い電圧であることを特徴とする請求項 1 記載の電圧切り替え回路。

【請求項 6】

前記第 1 の電圧は、電源電圧以下の電圧であることを特徴とする請求項 5 記載の電圧切り替え回路。

【請求項 7】

前記第 1、第 2 のトランジスタは、チャネル部への不純物注入工程が互いに異なることを特徴とする請求項 1 乃至 6 のいずれか 1 項に記載の電圧切り替え回路。

【請求項 8】

前記第 1、第 2 のトランジスタは、チャネル部への不純物注入工程が同じであることを特徴とする請求項 1 乃至 6 のいずれか 1 項に記載の電圧切り替え回路。 10

【請求項 9】

前記第 1、第 2 のトランジスタは、ゲート絶縁膜厚が異なることを特徴とする請求項 1 乃至 8 のいずれか 1 項に記載の電圧切り替え回路。

【請求項 10】

前記第 2 の回路側に前記第 2 のトランジスタが接続され、前記第 2 のトランジスタのゲート絶縁膜厚は、前記第 1 のトランジスタのゲート絶縁膜厚よりも大きいことを特徴とする請求項 1 乃至 9 のいずれか 1 項に記載の電圧切り替え回路。

【請求項 11】

前記第 2 の回路側に前記第 2 のトランジスタが接続され、前記第 2 のトランジスタのしきい値電圧は、前記第 1 のトランジスタのしきい値電圧よりも低いことを特徴とする請求項 1 乃至 10 のいずれか 1 項に記載の電圧切り替え回路。 20

【請求項 12】

電圧出力ノードをさらに具備し、

前記第 2 の回路の出力ノードが前記電圧出力ノードに接続され、

前記第 3 の回路は前記第 1 の回路の出力ノードと前記電圧出力ノードとの間に接続されていることを特徴とする請求項 1 乃至 11 のいずれか 1 項に記載の電圧切り替え回路。

【請求項 13】

前記第 3 の回路は、制御信号に応じて前記第 1 の回路の出力ノードと前記第 2 の回路の出力ノードとの間を導通または遮断することを特徴とする請求項 1 乃至 12 のいずれか 1 項に記載の電圧切り替え回路。 30

【請求項 14】

前記第 3 の回路は、所定の期間に、前記第 1 の回路から出力される前記第 1 の電圧を前記電圧出力ノードに転送することを特徴とする請求項 12 記載の電圧切り替え回路。

【請求項 15】

前記第 1 の電圧は、前記所定の期間のうちの少なくとも一部の期間において、電源電圧の電圧レベルにあることを特徴とする請求項 14 記載の電圧切り替え回路。

【請求項 16】

前記第 1、第 2 のトランジスタのゲートには電源電圧以下の電圧レベルが印加されることを特徴とする請求項 1 乃至 15 のいずれか 1 項に記載の電圧切り替え回路。

【請求項 17】

前記第 1、第 2 のトランジスタのゲートの設定電圧は常に同じ電圧であることを特徴とする請求項 1 乃至 16 のいずれか 1 項に記載の電圧切り替え回路。 40

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は電圧切り替え回路に係り、特に N A N D セル、N O R セル、D I N O R セル、A N D セル等の電源電圧より高い電圧を使用する不揮発性半導体記憶装置の電圧切り替え回路に関するものである。

【0002】

【従来の技術】

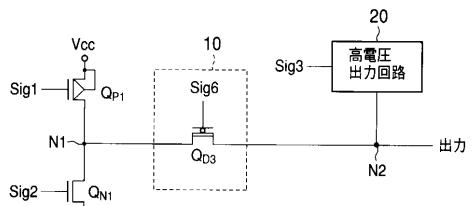

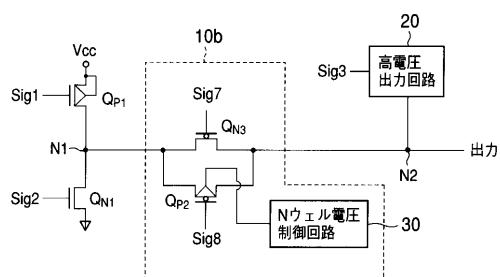

不揮発性半導体記憶装置に代表される電源電圧より高い昇圧電圧を使用するデバイスでは、1つの配線に対して0V、電源電圧V<sub>cc</sub>、高電圧（V<sub>cc</sub>より高い電圧）のように、高電圧及び電源電圧V<sub>cc</sub>以下の電圧を選択的に充電する回路が必要である。このような機能を有する従来の電圧切り替え回路の一例を図10に示す。

【0003】

図10に示す電圧切り替え回路は、ノードN1で互いに接続されたエンハンスマント型（以下E型と呼ぶ）のPチャネルトランジスタQ<sub>P1</sub>及びNチャネルトランジスタQ<sub>N1</sub>からなる第1の回路と、出力側のノードN2に接続された高電圧出力回路20からなる第2の回路と、ノードN1、N2の間に接続された厚いゲート絶縁膜を有するデプレッシャン型（以下D型と呼ぶ）NチャネルトランジスタQ<sub>D3</sub>からなる第3の回路により構成される。ここで、Q<sub>D3</sub>の厚いゲート絶縁膜は、高電圧出力回路20からドレイン側のノードN2に出力される高電圧に耐えるために用いられる。10

【0004】

第1の回路において、E型PチャネルトランジスタQ<sub>P1</sub>のドレインと基板との接続点に電源電圧V<sub>cc</sub>が付与され、ゲートに信号Sig1が入力され、ソースはノードN1に接続される。また、E型NチャネルトランジスタQ<sub>N1</sub>のソースは接地（0V）され、ゲートに信号Sig2が入力され、ドレインはノードN1に接続される。

【0005】

第2の回路において、高電圧出力回路20には信号Sig3が入力され、ノードN2に高電圧V<sub>pp</sub>が出力される。ここで高電圧V<sub>pp</sub>は例えば不揮発性半導体記憶装置のプログラム電圧として用いられる。20

【0006】

また、第3の回路において、D型NチャネルトランジスタQ<sub>D3</sub>のソースはノードN1に接続され、ゲートに信号Sig6が入力され、ドレインはノードN2に接続される。Q<sub>D3</sub>からなる第3の回路は、後に示すように本発明の電圧切り替え回路の主要部と密接に関連するため、特に破線の囲み10で示されている。

【0007】

次に、図10に示す電圧切り替え回路の動作について説明する。図10の電圧切り替え回路において、信号Sig1、Sig2、Sig3、及びSig6は、V<sub>cc</sub>を高レベル、0Vを低レベルとする信号である。またSig6は、0V以上の任意の電圧を高レベルとする場合がある。30

【0008】

第1の回路において、信号Sig1、Sig2を共に高レベルにすれば、Q<sub>P1</sub>オフ、Q<sub>N1</sub>オンとなるのでノードN1は0Vとなる。信号Sig1、Sig2を共に低レベルとすれば、Q<sub>P1</sub>オン、Q<sub>N1</sub>オフとなるのでノードN1はV<sub>cc</sub>となる。また、信号Sig1を高レベル、信号Sig2を低レベルとすれば、Q<sub>P1</sub>オフ、Q<sub>N1</sub>オフとなるのでノードN1はフローティング（高インピーダンス）状態となる。このように、信号Sig1、Sig2を用いてノードN1に0V、電源電圧V<sub>cc</sub>、及び高インピーダンス状態を出力することができる。

【0009】

第2の回路において、高電圧出力回路20に入力する信号Sig3を高レベルにすればノードN2に高電圧V<sub>pp</sub>が出力され、信号Sig3を低レベルにすればノードN2は高インピーダンス状態になる。

【0010】

また、第3の回路において信号Sig6を高レベルにすれば、Q<sub>D3</sub>はオン状態となりノードN1、N2の間は導通し、信号Sig6を低レベルにすればオフ状態となってノードN1、N2の間は遮断される。

【0011】

以上、第1、第2及び第3の回路について別個に説明した電圧切り替え回路の動作を取りまとめれば、信号Sig1、Sig2、Sig3及びSig6の高レベル、低レベルに対40

応して、従来の電圧切り替え回路の出力電圧を次のように表すことができる。

【0012】

[Sig1、Sig2、Sig3、Sig6]の各レベルに対応する電圧を順に記入して左側に示し、電圧切り替え回路の出力を右側に示せば、

(a) [Vcc、0V、0V、] 「出力電圧なし(高インピーダンス状態)」

(b) [Vcc、Vcc、0V、] 「出力電圧=0V」

(c) [0V、0V、0V、Vcc] 「出力電圧=Vcc」

(d) [0V、0V、Vcc、0V] 「出力電圧=Vpp」

ここで(a)、(b)の場合には、Sig6の信号レベルは0V以上であればよい。

【0013】

10

図10に示す電圧切り替え回路の特徴は、高電圧Vppが印加されるノードN2(出力ノード)と、Vcc以下の電圧しか印加されないノードN1との間に、D型トランジスタQD3が設けられていることである。このように、高電圧Vppが印加されるノードN2と高電圧が印加されないノードN1との間の遮断をトランジスタ1個で実現すれば、回路のパターン面積を小さくすることができる。

【0014】

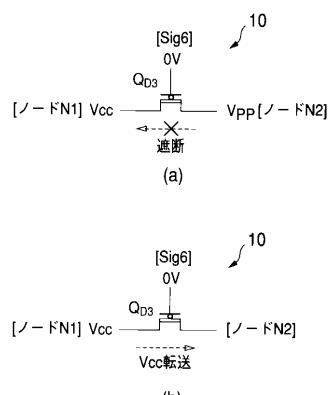

図11に第3の回路10の部分拡大図を示す。先に述べたように、電圧切り替え回路が所望の電圧を出力するためには、QD3は図11(a)、図11(b)に破線で矢示したような特性を満たさねばならない。

【0015】

20

すなわちQD3のゲート電圧をVg、ソース電圧をVs、ドレイン電圧をVdとすれば、VgはSig6の電圧、VsはノードN1の電圧、VdはノードN2の電圧にそれぞれ等しいので、図11(a)に示すように、QD3は[Vg、Vs、Vd]=[0V、Vcc、Vpp]の時に遮断状態になり、図11(b)に示すように[Vg、Vs]=[Vcc、Vcc]の時にソースの電源電圧Vccがドレインに転送されねばならない。

【0016】

図11(a)に示すQD3の特性が満たされない場合には、QD3を介して高電圧Vppのリーケ電流が流れるのでVppのレベル低下を生じる。また、図11(b)に示すQD3の特性が満たされない場合には、QD3の転送能力の低下により電圧切り替え回路の出力電圧Vccのレベル低下を生じる。

30

【0017】

一般に電源電圧Vccが高い場合には、図11(a)における(Vg-Vs)の値(= -Vcc)が小さくなるので図11(a)の遮断特性のマージンが大きくなり、D型トランジスタQD3のしきい値電圧(負の値)の絶対値を大きくすることができる。このため、十分なマージンをもって、図11(b)に示すVcc転送状態(オン状態)を実現することができる。しかし、電源電圧Vccが低くなるにつれて図11(a)の遮断状態を実現するためには、QD3のしきい値電圧の絶対値を小さくする必要があるので、Vcc転送状態に対して必要なQD3のしきい値電圧マージンが次第に小さくなる。

【0018】

すなわち、図11(a)において、電源電圧Vccが低くなるにつれてD型トランジスタQD3をオフするVg-Vsの値(0V - Vcc = -Vcc)が0Vに近づくので、第3の回路10を遮断状態にするためのQD3のしきい値電圧を0Vに近づけねばならず、従ってVcc転送状態に対するマージンが小さくなる。

40

【0019】

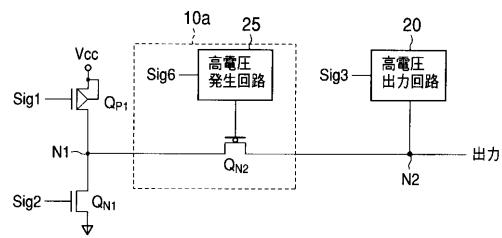

近年半導体集積回路の低消費電力化に伴い、電源電圧の低電圧化が進行し、図11(a)、図11(b)に示すD型NチャネルトランジスタQD3の特性を満たすことが困難になるという問題が生じていた。このため、図10に示す電圧切り替え回路の代わりに、図12、図13に示すように、D型トランジスタを用いない素子数の多い回路が使用されるようになった。

【0020】

50

図12に示す回路は、D型Nチャネルトランジスタ $Q_{D3}$ の代わりにE型Nチャネルトランジスタ $Q_{N2}$ 、及び信号 $Sig_6$ を受けて高電圧を $Q_{N2}$ のゲートに入力する高電圧発生回路25から構成される第3の回路10aを用いた電圧切り替え回路である。E型トランジスタを用いればしきい値電圧が正となり、電源電圧低下に伴うしきい値電圧マージン低下の問題を回避することができる。

【0021】

また、図13に示す回路は、D型Nチャネルトランジスタ $Q_{D3}$ の代わりに、ゲートに信号 $Sig_7$ を受けるE型Nチャネルトランジスタ $Q_{N3}$ と、ゲートに信号 $Sig_8$ を受け基板にNウエル電圧制御回路30の出力を受けるE型Pチャネルトランジスタ $Q_{P2}$ からなるトランジスタゲートを第3の回路10bとして用いた電圧切り替え回路である。図13に示す回路においても、E型トランジスタが用いられるのでしきい値電圧が正となり、電源電圧低下に伴うしきい値電圧マージン低下の問題を回避することができる。

10

【0022】

しかし、図12に示す電圧切り替え回路は高電圧発生回路25のパターン面積が大となり、また図13に示す電圧切り替え回路はNウエル電圧制御回路30のパターン面積が大となるため、いずれも図10に示す電圧切り替え回路に比べてパターン面積が大幅に増加するという欠点があった。

【0023】

【発明が解決しようとする課題】

上記したように、不揮発性半導体記憶装置等に用いる従来の電圧切り替え回路は、電源電圧が低くなればしきい値電圧マージンの低下により1個のD型トランジスタを用いた回路の使用が不可能になり、しきい値電圧マージンの低下を回避するためE型トランジスタを用いる回路を使用すればパターン面積が増加し、チップ面積が増加するという問題があった。

20

【0024】

本発明は上記の問題点を解決すべくなされたもので、チップ面積の増加を生じることなく動作マージンの大きい不揮発性半導体記憶装置等の電圧切り替え回路を提供することを目的とする。

【0025】

【課題を解決するための手段】

本発明の電圧切り替え回路は、従来1個のD型トランジスタで行われた高電圧の遮断と電源電圧の転送機能を、ゲート絶縁膜の膜厚又はしきい値電圧の異なる直列接続された2個のD型トランジスタで分担して行うことにより、しきい値電圧マージンの低下を回避しつつ最小のトランジスタ数で構成された電圧切り替え回路を提供することを主な特徴とする。

30

【0026】

具体的には、本発明の電圧切り替え回路は、第1の電圧を出力する能力を有する第1の回路と、第2の電圧を出力する能力を有する第2の回路と、第1の回路と第2の回路との間に接続され複数のトランジスタにより構成される第3の回路とを具備し、前記複数のトランジスタは直列接続され互いに電流駆動能力の異なる第1及び第2のトランジスタを有することを特徴とする。

40

【0027】

具体的には、本発明の電圧切り替え回路は、第1の電圧を出力する能力を有する第1の回路と、第2の電圧を出力する能力を有する第2の回路と、前記第1の回路の出力ノードと前記第2の回路の出力ノードとの間に接続され、それぞれゲート絶縁膜を有する複数のトランジスタにより構成される第3の回路とを具備し、前記複数のトランジスタは、しきい値電圧が互いに異なり、電流駆動能力が互いに異なる直列接続されたデプレッション型の第1、第2のトランジスタであることを特徴とする。

【0028】

<第1の実施形態>

50

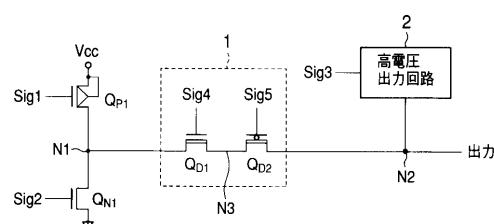

図1は、本発明の第1の実施形態に係る電圧切り替え回路の構成を示す図である。図1に示す電圧切り替え回路は、ノードN1で互いに接続されたE型PチャネルトランジスタQ<sub>P1</sub>及びE型NチャネルトランジスタQ<sub>N1</sub>からなる第1の回路と、信号Sig3を受けてノードN2に高電圧V<sub>PP</sub>を出力する高電圧出力回路2からなる第2の回路と、ゲートに信号Sig4が入力されソースがノードN1に接続されたD型NチャネルトランジスタQ<sub>D1</sub>及びゲートに信号Sig5が入力されソースがQ<sub>D1</sub>のドレインに接続されドレインがノードN2に接続されたD型NチャネルトランジスタQ<sub>D2</sub>からなる第3の回路1から構成される。

ここで、高電圧がゲート、ソース及びドレインに印加されてもゲート絶縁膜が破壊しないように、Q<sub>D2</sub>には厚いゲート絶縁膜が用いられる。

#### 【0029】

次に、本発明の電圧切り替え回路の動作を説明する。図1に示す第1及び第2の回路の動作は、先に図10を用いて説明した第1、第2の回路と同様であるから説明を省略する。図1における本発明の第3の回路1は、図10における第3の回路10と異なり、ゲートに信号Sig4を入力するD型トランジスタQ<sub>D1</sub>と、ゲートに信号Sig5を入力する厚いゲート絶縁膜を有するD型トランジスタQ<sub>D2</sub>との直列接続回路で構成される。

#### 【0030】

ここで、図1における信号Sig4、Sig5は、図10における信号Sig6と同様に電源電圧V<sub>CC</sub>を高レベル、0Vを低レベルとする信号である。また、Sig4、Sig5は0V以上の任意の電圧を高レベルとする場合がある。

#### 【0031】

第3の回路において、信号Sig4、Sig5を高レベルにすれば、D型NチャネルトランジスタQ<sub>D1</sub>、Q<sub>D2</sub>はオン状態となってノードN1、N2の間は導通し、信号Sig4、Sig5を低レベルにすればQ<sub>D1</sub>、Q<sub>D2</sub>はオフ状態となってノードN1、N2の間は遮断される。

#### 【0032】

本発明の電圧切り替え回路の動作を取りまとめて、信号Sig1乃至Sig5の高レベル、低レベルに対応する出力電圧を次のように表すことができる。

#### 【0033】

[Sig1、Sig2、Sig3、Sig4、Sig5]の各レベルに対応する電圧を順に記入して左側に示し、電圧切り替え回路の出力を右側に示せば、

- (a) [V<sub>CC</sub>、0V、0V、、] 「高インピーダンス状態」

- (b) [V<sub>CC</sub>、V<sub>CC</sub>、0V、、] 「出力電圧 = 0V」

- (c) [0V、0V、0V、V<sub>CC</sub>、V<sub>CC</sub>] 「出力電圧 = V<sub>CC</sub>」

- (d) [0V、0V、V<sub>CC</sub>、0V、0V] 「出力電圧 = V<sub>PP</sub>」

ここで、(a)、(b)の場合には、Sig4、Sig5の信号レベルは、0V以上であれば良い。

#### 【0034】

図1に示す電圧切り替え回路の特徴は、高電圧V<sub>PP</sub>が印加されるノードN2(出力ノード)と、V<sub>CC</sub>以下の電圧しか印加されないノードN1との間に、D型NチャネルトランジスタQ<sub>D1</sub>、Q<sub>D2</sub>が設けられていることである。Q<sub>D1</sub>、Q<sub>D2</sub>を用いることにより、高電圧出力時に高電圧V<sub>PP</sub>が印加されるノードN2と、高電圧が印加されないノードN1との間の電圧遮断をトランジスタ2個で容易に実現することができ、図12、図13に示す従来の電圧切り替え回路に比べてパターン面積を小さくすることができる。

#### 【0035】

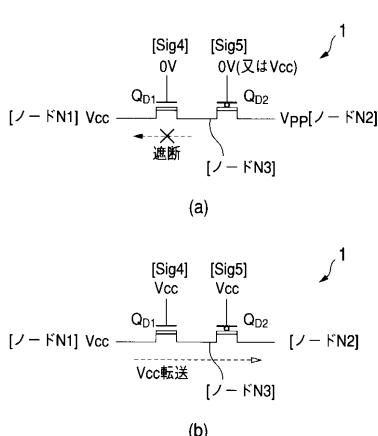

図2に第3の回路1の部分拡大図を示す。先に述べたように、電圧切り替え回路が所望の電圧を出力するためには、Q<sub>D1</sub>、Q<sub>D2</sub>は図2(a)、図2(b)に破線で矢示したような特性を満たさねばならない。

#### 【0036】

すなわち、[Sig4、Sig5、ノードN1、ノードN2] = [0V、0V、V<sub>CC</sub>、V<sub>PP</sub>]

10

20

30

40

50

$V_{PP}$ ] の時に  $Q_{D1}$ 、 $Q_{D2}$  のいずれかが遮断状態になり、[  $Sig\ 4$ 、 $Sig\ 5$ 、ノード  $N\ 1$  ] = [  $V_{CC}$ 、 $V_{CC}$ 、 $V_{CC}$  ] の時に、電源電圧  $V_{CC}$  が  $Q_{D1}$ 、 $Q_{D2}$  を介してノード  $N\ 2$  に転送されねばならない。

#### 【 0 0 3 7 】

なお、上記の例ではノード  $N\ 1$ 、 $N\ 2$  間を遮断状態にする  $Q_{D1}$ 、 $Q_{D2}$  のゲートバイアス条件は  $Sig\ 4$ 、 $Sig\ 5$  を  $0\ V$  とし、また、ノード  $N\ 1$ 、 $N\ 2$  間を  $V_{CC}$  転送状態にする  $Q_{D1}$ 、 $Q_{D2}$  のゲートバイアス条件は  $Sig\ 4$ 、 $Sig\ 5$  を  $V_{CC}$  としたが、必ずしもこれに限定されるものではない。

#### 【 0 0 3 8 】

例えば、 $Q_{D1}$  のしきい値電圧が  $Q_{D2}$  のしきい値電圧より低く（絶対値の大きい負の値）、ノード  $N\ 1$ 、 $N\ 2$  間の遮断条件と  $V_{CC}$  転送条件が  $Q_{D2}$  の動作で定まる場合には、 $Q_{D1}$  のゲートに入力する信号  $Sig\ 4$  を遮断条件と  $V_{CC}$  転送条件に対して共に  $0\ V$  又は  $V_{CC}$  とすることが可能であり、また、 $Q_{D2}$  のしきい値電圧が  $Q_{D1}$  のしきい値電圧より低く、ノード  $N\ 1$ 、 $N\ 2$  間の遮断条件と  $V_{CC}$  転送条件が  $Q_{D1}$  の動作で定まる場合には、 $Q_{D2}$  のゲートに入力する信号  $Sig\ 5$  を遮断条件と  $V_{CC}$  転送条件に対して共に  $0\ V$  又は  $V_{CC}$  とすることも可能である。

#### 【 0 0 3 9 】

図 2 ( a ) に示す  $Q_{D1}$ 、 $Q_{D2}$  の特性が満たされない場合には、 $Q_{D1}$ 、 $Q_{D2}$  を介して高電圧  $V_{PP}$  のリーク電流が流れるので、 $V_{PP}$  のレベル低下を生じる。また、図 2 ( b ) に示す  $Q_{D1}$ 、 $Q_{D2}$  の特性が満たされない場合には、 $Q_{D1}$ 、 $Q_{D2}$  の  $V_{CC}$  転送能力の低下により電圧切り替え回路の出力電圧  $V_{CC}$  のレベル低下を生じる。

#### 【 0 0 4 0 】

ここで、従来のように第 3 の回路 10 の部分に D 型ランジスタ  $Q_{D3}$  しか存在しない場合に比べて、本発明のように第 3 の回路 1 の部分に 2 個の D 型トランジスタ  $Q_{D1}$ 、 $Q_{D2}$  を設ければ、図 2 ( a )、図 2 ( b ) に示す遮断条件と転送条件を共に満たすことが容易になる理由について説明する。

#### 【 0 0 4 1 】

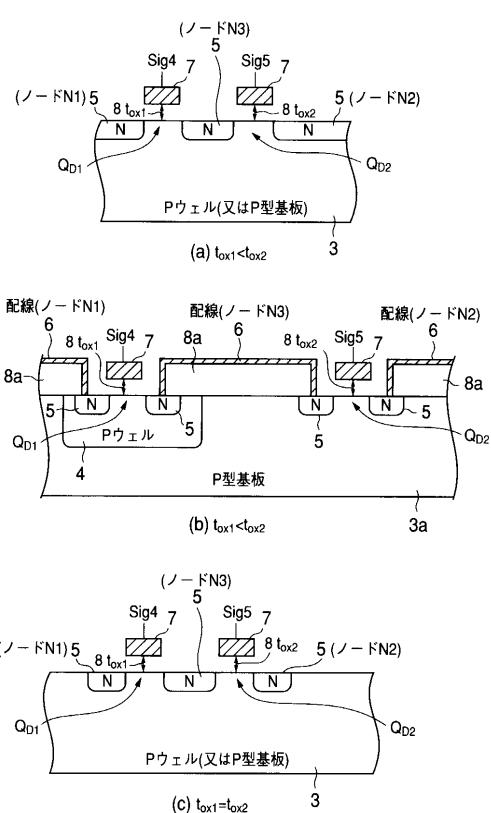

図 3 ( a ) は、半導体基板上に形成された D 型 N チャネルトランジスタ  $Q_{D1}$ 、 $Q_{D2}$  からなる第 3 の回路の断面構造を示す図である。図 3 ( a ) に示す断面構造は、P ウエル（又は P 型基板）3 と、N 型拡散層 5 と、ゲート電極 7 と、ゲート絶縁膜 8 ( $t_{ox1}$ 、 $t_{ox2}$  として厚さのみ表示) から構成され、 $Q_{D1}$  のソース拡散層 5 はノード  $N\ 1$  を成し、ドレイン拡散層 5 は  $Q_{D2}$  のソース拡散層と共にノード  $N\ 3$  を成し、 $Q_{D2}$  のドレイン拡散層 5 はノード  $N\ 2$  を成している。

#### 【 0 0 4 2 】

図 3 ( a ) に示す第 3 の回路では、 $Q_{D1}$ 、 $Q_{D2}$  のゲート絶縁膜の厚さ  $t_{ox1}$ 、 $t_{ox2}$  が互いに異なっている。 $Q_{D2}$  はドレイン拡散層 5 が高電圧  $V_{PP}$  が output するノード  $N\ 2$  に接続されるため厚いゲート絶縁膜が必要である。

#### 【 0 0 4 3 】

しかし、 $Q_{D1}$  はドレイン拡散層 5 がノード  $N\ 2$  に直接接続されておらず、また、ノード  $N\ 2$  に高電圧  $V_{PP}$  が印加される場合でも  $Q_{D2}$  のゲートは  $0\ V$  であって、 $Q_{D1}$  のドレイン拡散層 5 (ノード  $N\ 3$ ) には  $Q_{D2}$  のしきい値電圧の絶対値 ( $Q_{D2}$  のしきい値電圧が  $-V_{td2}$  であればノード  $N\ 3$  の電圧は  $V_{td2}$  ( $-V_{PP}$ ) ) 程度の電圧しか印加されないので、 $Q_{D1}$  のゲート絶縁膜の厚さは  $Q_{D2}$  のゲート絶縁膜の厚さよりも薄くすることができる ( $t_{ox1} < t_{ox2}$ )。

#### 【 0 0 4 4 】

一般に、ゲート絶縁膜が薄ければゲート電圧の変化に対するソース、ドレイン間電流の変化  $I_d / V_g$  が大きくなるため、図 2 ( a ) に示す遮断条件と図 2 ( b ) に示す  $V_{CC}$  転送条件とを両立させることができくなる。また図 3 ( a ) において遮断条件を  $Q_{D1}$  で満たすようにすれば、 $Q_{D2}$  は  $V_{CC}$  の転送条件のみ満たせばよいので、 $Q_{D2}$  のしきい値電圧を低くする（絶対値の大きい負の値にする）等の方法で  $V_{CC}$  の転送条件を容易に満たすことが

10

20

30

40

50

できる。

【0045】

従って、図3(a)に示す断面構造を備える2個のD型Nチャネルトランジスタ $Q_{D1}$ 、 $Q_{D2}$ からなる第3の回路1を用いれば、図10、図11に示す従来の1個のD型Nチャネルトランジスタ $Q_{D3}$ のみからなる第3の回路10を用いる場合に比べて、容易に遮断条件と $V_{cc}$ 転送条件を満たすことができる。

【0046】

このため、電源電圧 $V_{cc}$ が低い場合でも、図12、図13のようにパターン面積の大きな第3の回路10a、10bを用いることなく、動作マージンが大きく、かつ、チップ面積の小さい電圧切り替え回路を高い歩留まりで安価に提供することが可能になる。

10

【0047】

<第2の実施形態>

次に、図3(b)を用いて第2の実施形態に係る電圧切り替え回路について説明する。図3(b)は第2の実施形態における第3の回路の断面構造を示す図である。電圧切り替え回路を構成する第1、第2の回路については第1の実施形態と同様であるため説明を省略する。

【0048】

図3(b)に示す第3の回路は、P型基板3aと、P型基板上に形成されたPウエル4と、P型基板3a及びP型基板上のPウエル4に形成されたN型拡散層5を備えている。

20

【0049】

Pウエル4に形成されたD型Nチャネルトランジスタ $Q_{D1}$ のソース拡散層は、配線6を用いてノードN1に接続され、 $Q_{D1}$ のドレイン拡散層5は、ノードN3を成す配線6を用いてP型基板3aに形成されたD型Nチャネルトランジスタ

$Q_{D2}$ のソース拡散層に接続され、 $Q_{D2}$ のドレイン拡散層5は配線6を用いてノードN2に接続される。

【0050】

その他の部分の構成は、第1の実施形態と同様であるため説明を省略する。

【0051】

なお、図3(b)において、配線6と各拡散層5との接続部以外の半導体基板表面は絶縁膜8aで被覆されている。

30

【0052】

図3(b)に示すように、第3の回路を構成するD型トランジスタ $Q_{D1}$ 、 $Q_{D2}$ は、必ずしも同一のウエル又は同一基板上に形成する必要はなく、例えば $Q_{D1}$ はP型基板上のPウエルに形成し、 $Q_{D2}$ はP型基板上に形成する等、異なるウエルや基板上に形成することも可能であり、この場合にも $Q_{D1}$ 、 $Q_{D2}$ のゲート絶縁膜8の厚さを $t_{ox1} < t_{ox2}$ とすることでき、図3(a)と同様に遮断条件と $V_{cc}$ 転送条件とを容易に両立させることができる。

【0053】

<第3の実施形態>

次に、図3(c)を用いて第3の実施形態に係る電圧切り替え回路について説明する。図3(c)は、第3の実施形態における第3の回路の断面構造を示す図である。図3(c)に示す第3の回路の断面構造は、D型トランジスタ $Q_{D1}$ 、 $Q_{D2}$ のゲート絶縁膜8の厚さ $t_{ox1}$ 、 $t_{ox2}$ が互いに等しいこと以外は、図3(a)と同様であるから説明を省略する。

40

【0054】

図3(c)に示す第3の回路において、 $Q_{D1}$ 、 $Q_{D2}$ のゲート絶縁膜8の厚さ $t_{ox1}$ 、 $t_{ox2}$ は互いに等しいが、チャネルイオン注入の条件を変えることにより、 $Q_{D1}$ 、 $Q_{D2}$ のしきい値電圧の絶対値が互いに異なっている。このように $Q_{D1}$ 、 $Q_{D2}$ のしきい値電圧の設定に自由度を設ければ、ノードN3の電圧についても自由度が高くなるため、従来に比べて遮断条件と $V_{cc}$ 転送条件とを容易に両立させることができる。

【0055】

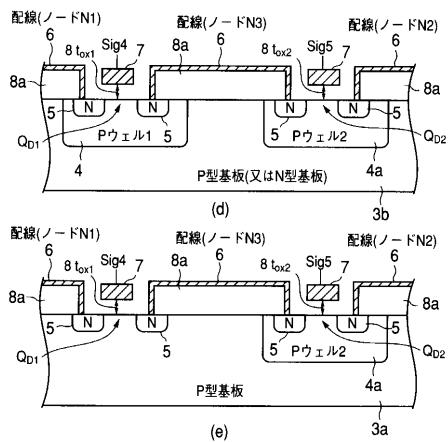

<第4の実施形態>

50

次に、図4(d)を用いて第4の実施形態に係る電圧切り替え回路について説明する。図4(d)は第4の実施形態における第3の回路の断面構造を示す図である。図4(d)に示す第3の回路の断面構造はD型トランジスタ $Q_{D1}$ 、 $Q_{D2}$ がP型基板(又はN型基板)3b上のPウエル1(4)、Pウエル2(4a)に形成されることが図3(b)と異なる。その他の構造は図3(b)と同様であるから説明を省略する。

#### 【0056】

一般にトランジスタが形成されるウエル又は基板の不純物濃度が低いほどゲート電圧の変化に対するソース、ドレイン間電流の変化 $Id/Vg$ が大きくなるため、遮断条件と $V_{cc}$ 転送条件とを両立させることができることになる。これをを利用して、 $Q_{D2}$ が形成されるPウエル2(4a)の不純物濃度を $Q_{D1}$ が形成されるPウエル1(4)の不純物濃度よりも低くしたり、あるいは高くしたりすることにより、トランジスタのしきい値電圧の組み合わせの自由度を高めることができ、遮断条件と $V_{cc}$ 転送条件とを容易に両立させることができることになる。

10

#### 【0057】

特に、不純物濃度がPウエル1 < Pウエル2の場合には、 $Q_{D1}$ の $Id/Vg$ をPウエル1 = Pウエル2の場合よりも大きくなり、従って、遮断条件と $V_{cc}$ 転送条件の両立が $Q_{D1}$ に対して容易となる。

#### 【0058】

##### <第5の実施形態>

次に、図4(e)を用いて第5の実施形態に係る電圧切り替え回路について説明する。図4(e)は第5の実施形態における第3の回路の断面構造を示す図である。図4(e)に示す第3の回路の断面構造は、D型トランジスタ $Q_{D1}$ がP型基板3a上に形成され、D型トランジスタ $Q_{D2}$ がP型基板3a上のPウエル2(4a)に形成されることが図3(b)と異なる。その他の構造は図3(b)と同様であるから説明を省略する。

20

#### 【0059】

図4(e)に示すように、 $Q_{D1}$ のみをP型基板上に形成し $Q_{D2}$ をPウエル上に形成する場合でも、通常P型基板の不純物濃度はPウエルの不純物濃度に比べて低いので、図4(d)の場合と同様に $Q_{D1}$ が遮断条件と $V_{cc}$ 転送条件を満たすことが容易になる。なお、第4、第5の実施形態において、ゲート絶縁膜の厚さを $t_{ox1} = t_{ox2}$ としても図10に示す従来の回路に比べて大幅な改善が可能であるが、さらに $t_{ox1} < t_{ox2}$ とすれば、不純物濃度とゲート絶縁膜の厚さとの相乗効果により、さらに大きい改善が得られる。

30

#### 【0060】

以上図1乃至図4を用いて説明した第1乃至第5の実施形態では、基本的に第1のD型トランジスタ $Q_{D1}$ はノードN1、N2間の遮断条件と $V_{cc}$ 転送条件とを両立させる役割を果たし、第2のD型トランジスタ $Q_{D2}$ は、ノードN3に転送される電圧レベルの最大値を $V_{PP}$ よりも低下させるという役割を含めてノードN1、N2間の $V_{cc}$ 転送条件のみを達成するという役割分担がなされている。

#### 【0061】

##### <第6の実施形態>

次に、第6の実施形態としてD型トランジスタ $Q_{D1}$ 、 $Q_{D2}$ の製造方法について説明する。通常トランジスタを製造する際、しきい値電圧を目標値に合わせるためにトランジスタのチャネル部に不純物をイオン注入する(以下チャネル注入と呼ぶ)。チャネル注入は、しきい値電圧 $V_t$ の異なるトランジスタに対しては別個に行われる場合が多いため、トランジスタの種類と同数のチャネル注入工程用マスクが必要となるが、このマスク数が少ないとチップの製造コストを削減することができる。

40

#### 【0062】

先に述べたように、本発明における第1のD型トランジスタ $Q_{D1}$ はノードN1、N2間の遮断条件と $V_{cc}$ 転送条件とを両立させ、第2のD型トランジスタ $Q_{D2}$ はノードN1、N2間の $V_{cc}$ 転送条件のみを達成するという方針なので、 $Q_{D2}$ のしきい値電圧は、比較的低い(特に $Q_{D1}$ のしきい値電圧より低い、つまり $V_t(Q_{D1}) > V_t(Q_{D2})$ )ことが望ましい

50

。

## 【0063】

図3(a)に示すように、ゲート絶縁膜の厚さの間に  $t_{ox1} < t_{ox2}$  の関係があり、かつ  $Q_{D1}$ 、 $Q_{D2}$  が同一のウエル(又は同一基板)上に形成される場合、 $Q_{D1}$ 、 $Q_{D2}$  に対して同一のチャネル注入を行えば、通常、 $Q_{D1}$  のしきい値電圧の絶対値( $V_{td1}$ )は $Q_{D2}$ のしきい値電圧の絶対値( $V_{td2}$ )より小さくなる( $V_{td1} < V_{td2}$ )ため、 $V_t(Q_{D1}) = -V_{td1} > V_t(Q_{D2}) = -V_{td2}$ となる。従って、 $Q_{D1}$ 、 $Q_{D2}$ に対してチャネル注入を共通にすることが可能になる。

## 【0064】

このように、ゲート絶縁膜の厚さの間に  $t_{ox1} < t_{ox2}$  の関係がある場合に  $Q_{D1}$ 、 $Q_{D2}$  に対してチャネル注入工程を共通化(同一化)することにより、マスク数と工程数の削減が可能となりチップ製造コストの低減を達成することができる。チャネル注入工程の同一化については、図3(a)以外にも、図3(b)、図3(d)、図3(e)場合にも適用可能であり、同様の効果を達成することができる。

10

## 【0065】

<第7の実施形態>

次に、図5を用いて第7の実施形態に係る電圧切り替え回路について説明する。第7の実施形態では、第1の実施形態の電圧切り替え回路の変形例について説明する。

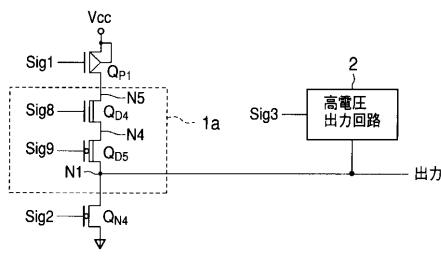

## 【0066】

図5に示す第7の実施形態の電圧切り替え回路は、図1に示す第1の実施形態における第1の回路のノードN1とE型Pチャネルトランジスタ $Q_{P1}$ との間に、D型Nチャネルトランジスタ $Q_{D4}$ 、 $Q_{D5}$ からなる第3の回路1aを接続することにより構成される。

20

## 【0067】

ノードN1には直接第1の実施形態における第2の高電圧出力回路の $V_{PP}$ が出力され、ノードN5には高々電源電圧 $V_{CC}$ ( $V_{PP}$ )が出力されるに過ぎないので、ノードN5に接続される $Q_{D4}$ のゲート絶縁膜はノードN1に接続される $Q_{D5}$ のゲート絶縁膜に比べて薄くされている。

## 【0068】

$Q_{D4}$ 、 $Q_{D5}$ のゲートに入力する信号をそれぞれSig8、Sig9とし、第1の実施形態の議論を適用すれば、各入力信号の高レベル、低レベルに対応する出力電圧は次のように表される。

30

## 【0069】

[Sig1、Sig2、Sig3、Sig8、Sig9]の各レベルに対応する電圧を順に記入して左側に示し、電圧切り替え回路の出力を右側に示せば、

(a) [V<sub>CC</sub>、0V、0V、] 「高インピーダンス状態」

(b) [V<sub>CC</sub>、V<sub>CC</sub>、0V、] 「出力電圧 = 0V」

(c) [0V、0V、0V、V<sub>CC</sub>、V<sub>CC</sub>] 「出力電圧 = V<sub>CC</sub>」

(d) [0V、0V、V<sub>CC</sub>、0V、0V] 「出力電圧 = V<sub>PP</sub>」

上記(a)乃至(d)の出力は第1の実施形態と同様である。

## 【0070】

40

従って、第7の実施形態の電圧切り替え回路は、第1の実施形態の電圧切り替え回路と同様の機能を具備している。しかし、ノードN1に高電圧 $V_{PP}$ が出力されるため、E型Nチャネルトランジスタ $Q_{N4}$ のゲート絶縁膜も $Q_{D5}$ と同程度にする必要がある。

## 【0071】

<第8の実施形態>

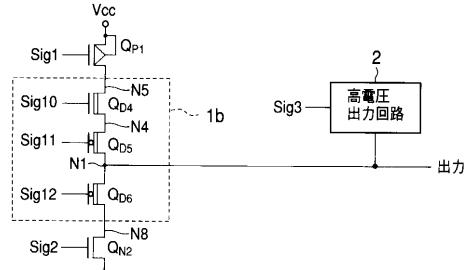

次に、図6を用いて第8の実施形態に係る電圧切り替え回路について説明する。第8の実施形態では、第7の実施形態の電圧切り替え回路の変形例について説明する。

## 【0072】

図6に示す第8の実施形態の電圧切り替え回路は、図5に示す第7の実施形態におけるノードN1とE型Nチャネルトランジスタ $Q_{N4}$ との間に、D型Nチャネルトランジスタ $Q_{D6}$

50

が接続された構成に相当している。図5のトランジスタ回路1aに対応する部分が図6のトランジスタ回路1bとして示されている。

【0073】

図6のトランジスタ回路1bは、ノードN1とノードN5との間に $V_{PP}$ 遮断条件と $V_{CC}$ 転送条件とを改善する2個のD型Nチャネルトランジスタ $Q_{D4}$ 、 $Q_{D5}$ を備えるばかりでなく、ノードN1とノードN8との間にも $V_{PP}$ 遮断条件を改善する1個のD型Nチャネルトランジスタ $Q_{D6}$ を備えている。

【0074】

ノードN1には直接第1の実施形態における第2の高電圧出力回路の $V_{PP}$ が出力され、ノードN5には高々電源電圧 $V_{CC}$ ( $V_{PP}$ )が出力されるに過ぎないので、ノードN5に接続される $Q_{D4}$ のゲート絶縁膜は、ノードN1に接続される $Q_{D5}$ 、 $Q_{D6}$ のゲート絶縁膜に比べて薄くされている。

10

【0075】

$Q_{D4}$ 、 $Q_{D5}$ のゲートに入力する信号をそれぞれ $Sig10$ 、 $Sig11$ とし、 $Q_{D6}$ のゲートに入力する信号を $Sig12$ とすれば、各入力信号の高レベル、低レベルに対応する出力電圧は次のように表される。

【0076】

[ $Sig1$ 、 $Sig2$ 、 $Sig3$ 、 $Sig10$ 、 $Sig11$ 、 $Sig12$ ]の各レベルに対応する電圧を順に記入して左側に示し、電圧切り替え回路の出力を右側に示せば、

(a) [ $V_{CC}$ 、 $0V$ 、 $0V$ 、 $\cdot$ 、 $\cdot$ ] 「高インピーダンス状態」

20

(b) [ $V_{CC}$ 、 $V_{CC}$ 、 $0V$ 、 $\cdot$ 、 $\cdot$ ] 「出力電圧 =  $0V$ 」

(c) [ $0V$ 、 $0V$ 、 $0V$ 、 $V_{CC}$ 、 $V_{CC}$ ] 「出力電圧 =  $V_{CC}$ 」

(d) [ $0V$ 、 $0V$ 、 $V_{CC}$ 、 $0V$ 、 $0V$ 、 $0V$ ] 「出力電圧 =  $V_{PP}$ 」

上記(a)乃至(d)の出力は第7の実施形態と同様である。

【0077】

従って、第8の実施形態の電圧切り替え回路は、第7の実施形態の電圧切り替え回路と同様の機能を具備している。しかし、ノードN1に高電圧 $V_{PP}$ が出力されるため、D型Nチャネルトランジスタ $Q_{D6}$ のゲート絶縁膜を $Q_{D5}$ と同程度にする必要があり、その代わりに $Sig2$ 入力のトランジスタ $Q_{N2}$ のゲート絶縁膜を図1の $Q_{N1}$ と同程度にできる。

【0078】

30

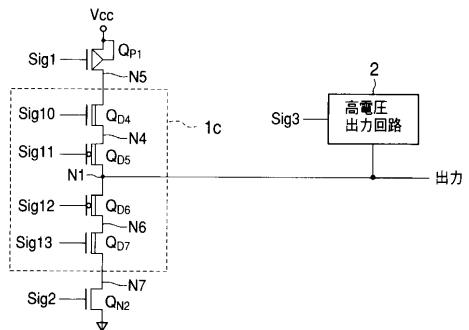

<第9の実施形態>

次に、図7を用いて第9の実施形態に係る電圧切り替え回路について説明する。第9の実施形態では、第8の実施形態の電圧切り替え回路の変形例について説明する。

【0079】

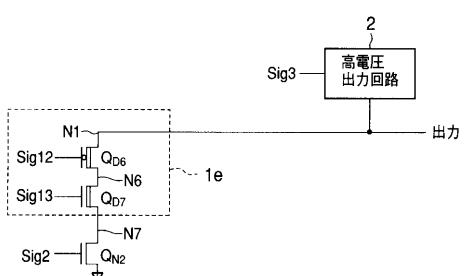

図7に示す第9の実施形態の電圧切り替え回路は、図6に示す第8の実施形態におけるD型Nチャネルトランジスタ $Q_{D6}$ のソースとE型Nチャネルトランジスタ $Q_{N2}$ との間に、D型Nチャネルトランジスタ $Q_{D7}$ を接続することにより構成される。図6のトランジスタ回路1bに対応する部分が図7のトランジスタ回路1cとして示されている。

【0080】

図7のトランジスタ回路1cは、ノードN1とノードN5との間に $V_{PP}$ 遮断条件と $V_{CC}$ 転送条件とを改善する2個のD型Nチャネルトランジスタ $Q_{D4}$ 、 $Q_{D5}$ を備え、かつノードN1とノードN7との間にも $V_{PP}$ 遮断条件と $V_{CC}$ 転送条件とを改善する2個のD型Nチャネルトランジスタ $Q_{D6}$ 、 $Q_{D7}$ を備えている。

40

【0081】

ノードN1には直接第1の実施形態における第2の高電圧出力回路の $V_{PP}$ が出力され、ノードN5には高々電源電圧 $V_{CC}$ ( $V_{PP}$ )が出力されるに過ぎないので、ノードN5に接続される $Q_{D4}$ のゲート絶縁膜は、ノードN1に接続される $Q_{D5}$ 、 $Q_{D6}$ のゲート絶縁膜より薄くされている。同様にノードN7に接続される $Q_{D7}$ のゲート絶縁膜は $Q_{D5}$ 、 $Q_{D6}$ のゲート絶縁膜より薄くされている。

【0082】

50

$Q_{D4}$ 、 $Q_{D5}$ のゲートに入力する信号をそれぞれ  $Sig10$ 、 $Sig11$  とし、 $Q_{D6}$ 、 $Q_{D7}$  のゲートに入力する信号を  $Sig12$ 、 $Sig13$  とすれば、各入力信号の高レベル、低レベルに対応する出力電圧は次のように表される。

【0083】

[ $Sig1$ 、 $Sig2$ 、 $Sig3$ 、 $Sig10$ 、 $Sig11$ 、 $Sig12$ 、 $Sig13$ ] の各レベルに対応する電圧を順に記入して左側に示し、電圧切り替え回路の出力を右側に示せば、

- (a) [  $V_{cc}$ 、 $0V$ 、 $0V$ 、 $\cdot$ 、 $\cdot$ 、 $\cdot$  ] 「高インピーダンス状態」

- (b) [  $V_{cc}$ 、 $V_{cc}$ 、 $0V$ 、 $\cdot$ 、 $\cdot$ 、 $\cdot$  ] 「出力電圧 =  $0V$ 」

- (c) [  $0V$ 、 $0V$ 、 $0V$ 、 $V_{cc}$ 、 $V_{cc}$ 、 $\cdot$  ] 「出力電圧 =  $V_{cc}$ 」

- (d) [  $0V$ 、 $0V$ 、 $V_{cc}$ 、 $0V$ 、 $0V$ 、 $0V$  ] 「出力電圧 =  $V_{pp}$ 」

上記 (a) 乃至 (d) の出力は第 8 の実施形態と同様である。

【0084】

従って、第 9 の実施形態の電圧切り替え回路は、第 8 の実施形態の電圧切り替え回路と同様の機能を具備している。また、第 8 の実施形態と同様、ノード N 1 に高電圧  $V_{pp}$  が出力されるため、D 型 N チャネルトランジスタ  $Q_{D6}$  のゲート絶縁膜を  $Q_{D5}$  と同程度にしている。

【0085】

なお、第 9 の実施形態では、第 7、第 8 の実施形態の電圧切り替え回路に比べてトランジスタ数は増加しているが、第 9 の実施形態では、 $V_{cc}$  側のノード N 1、N 5 間ばかりでなく、接地側のノード N 1、N 7 間も 2 個の D 型トランジスタ  $Q_{D6}$ 、 $Q_{D7}$  を用いて  $V_{pp}$  の遮断条件と  $0V$  の転送条件とを最適化することができるので、低い電源電圧  $V_{cc}$  で安定に動作する電圧切り替え回路を提供することができる。

【0086】

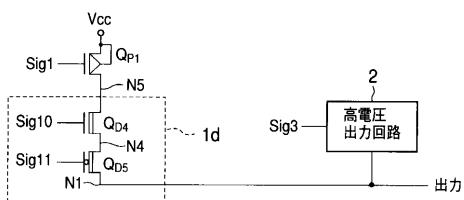

<第 10 の実施形態>

次に、図 8、図 9 を用いて第 10 の実施形態に係る電圧切り替え回路について説明する。図 8 に示す電圧切り替え回路は、図 7 に示すトランジスタ回路のノード N 1 と  $V_{cc}$  間のみが図 8 のノード N 1 に接続されることにより構成され、図 9 に示す電圧切り替え回路は、図 7 に示すトランジスタ回路のノード N 1 と接地間のみが図 8 のノード N 1 に接続されることにより構成される。

【0087】

図 8 に示す電圧切り替え回路の出力は電源電圧  $V_{cc}$  と高電圧  $V_{pp}$  と高インピーダンス状態であり、図 9 に示す電圧切り替え回路の出力は  $0V$  と高電圧  $V_{pp}$  と高インピーダンス状態であることは、図 7 の説明から明らかである。本発明の適用対象となる半導体装置の回路構成によっては、電圧レベルとして  $V_{cc}$  や  $0V$  を要しない場合もあるので、このとき、第 10 の実施形態の電圧切り替え回路が有効となる。

【0088】

なお本発明は上記の実施形態に限定されることはない。例えば以上の各実施形態において、電圧切り替え回路を構成する第 3 の回路の一方のノードに高電圧  $V_{pp}$  が印加され、他方のノードに電源電圧  $V_{cc}$  以下の電圧が印加される場合について説明したが、必ずしもこれに限定されるものではない。一方のノードに高電圧  $V_{pp}$  が印加され、他方のノードに中間電圧  $V_m$  ( $V_{cc} < V_m < V_{pp}$ ) が印加される場合にも本発明は有効である。

【0089】

また、第 1 乃至第 4 の実施形態において、ゲート絶縁膜の厚さが異なる D 型トランジスタを直列接続した構成、及び複数の D 型トランジスタでチャネル注入条件を同一化すること、及び D 型トランジスタを互いに異なるウエル上に、又はウエル上と基板上とにそれぞれ別個に形成すること等について説明したが、これらの製造工程は、必ずしも D 型トランジスタに限定されるものではない。E 型トランジスタに対しても同様にこれらの製造工程を適用することができる。

【0090】

10

20

30

40

50

以上説明した回路において、各回路を構成する構成要素の導電型（極性）を反転しても同様の回路機能を実現することができる。また、以上の実施形態において、主として2個のD型トランジスタを直列に接続したことを基本とする第3の回路の機能を説明したが、直列接続された3個以上のD型トランジスタを用いても同様な機能が実現されることはいうまでもない。その他本発明の要旨を逸脱しない範囲で種々変形して実施することができる。

【0091】

【発明の効果】

上述したように本発明の電圧切り替え回路によれば、電源電圧が低い場合においても、チップ面積の増加を生じることなく、動作マージンの大きい不揮発性半導体記憶装置等の電圧切り替え回路を提供することが可能になる。

10

【図面の簡単な説明】

【図1】第1の実施形態に係る電圧切り替え回路の構成を示す図。

【図2】第3の回路の動作を説明する図であって、

(a)は遮断条件を示す図。

(b)はVcc転送条件を示す図。

【図3】第3の回路の断面構造を示す図であって、

(a)は第1の実施形態における第3の回路の構造を示す断面図。

(b)は第2の実施形態における第3の回路の構造を示す断面図。

(c)は第3の実施形態における第3の回路の構造を示す断面図。

20

【図4】第3の回路の断面構造を示す図であって、

(d)は第4の実施形態における第3の回路の構造を示す断面図。

(e)は第5の実施形態における第3の回路の構造を示す断面図。

【図5】第7の実施形態に係る電圧切り替え回路の構成を示す図。

【図6】第8の実施形態に係る電圧切り替え回路の構成を示す図。

【図7】第9の実施形態に係る電圧切り替え回路の構成を示す図。

【図8】第10の実施形態に係る電圧切り替え回路の構成を示す図。

【図9】第10の実施形態に係る他の電圧切り替え回路の構成を示す図。

【図10】従来の電圧切り替え回路の構成を示す図。

【図11】従来の第3の回路の動作を説明する図であって、

30

(a)は遮断条件を示す図。

(b)はVcc転送条件を示す図。

【図12】従来のE型トランジスタを用いた第3の回路の構成を示す図。

【図13】従来のE型トランジスタを用いた第3の回路の他の構成を示す図。

【符号の説明】

1、1a、1b、1c、1d、1e…第3の回路

2…高電圧出力回路

3…Pウエル（又はP型基板）

3a…P型基板

3b…P型基板（又はN型基板）

40

4…Pウエル、Pウエル1

4a…Pウエル2

5…N型拡散層

6…配線

7…ゲート電極

8…ゲート絶縁膜

8a…絶縁膜

10、10a、10b…第3の回路

20…高電圧回路

25…高電圧発生回路

50

## 3 0 ... N ウエル電圧制御回路

【図 1】

【図 2】

【図 3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図10】

【図9】

【図11】

### 【図12】

### 【図13】

---

フロントページの続き

(72)発明者 中村 寛

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝マイクロエレクトロニクスセンター内

審査官 大嶋 洋一

(56)参考文献 特開平09-270196 (JP, A)

特開平05-335917 (JP, A)

特開平05-259473 (JP, A)

特開平05-090515 (JP, A)

特開平02-187997 (JP, A)

特開平02-186666 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/822

H01L 27/04

H03K 17/693