(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2020-4859

(P2020-4859A)

(43) 公開日 令和2年1月9日(2020.1.9)

| (51) Int.Cl.                 | F 1        | テーマコード (参考) |       |  |

|------------------------------|------------|-------------|-------|--|

| <b>H01L 21/336 (2006.01)</b> | HO1L 29/78 | 618Z        | 2H192 |  |

| <b>H01L 29/786 (2006.01)</b> | HO1L 29/78 | 619A        | 5C094 |  |

| <b>H01L 21/20 (2006.01)</b>  | HO1L 29/78 | 616U        | 5F110 |  |

| <b>G09F 9/30 (2006.01)</b>   | HO1L 29/78 | 616V        | 5F152 |  |

| <b>G02F 1/1368 (2006.01)</b> | HO1L 29/78 | 627G        |       |  |

審査請求 未請求 請求項の数 11 O.L. (全 21 頁) 最終頁に続く

|           |                              |          |                                               |

|-----------|------------------------------|----------|-----------------------------------------------|

| (21) 出願番号 | 特願2018-123444 (P2018-123444) | (71) 出願人 | 512225287<br>堺ディスプレイプロダクト株式会社<br>大阪府堺市堺区匠町1番地 |

| (22) 出願日  | 平成30年6月28日 (2018.6.28)       | (74) 代理人 | 100114557<br>弁理士 河野 英仁                        |

|           |                              | (74) 代理人 | 100078868<br>弁理士 河野 登夫                        |

|           |                              | (72) 発明者 | 菅原 祐太<br>大阪府堺市堺区匠町1番地 堀ディスプレイプロダクト株式会社内       |

|           |                              | (72) 発明者 | 田中 優數<br>大阪府堺市堺区匠町1番地 堀ディスプレイプロダクト株式会社内       |

最終頁に続く

(54) 【発明の名称】薄膜トランジスタ、表示装置及び薄膜トランジスタの製造方法

## (57) 【要約】

【課題】移動度の低下を抑えつつ、オフ電流を低減することの可能な薄膜トランジスタが提供される。

【解決手段】薄膜トランジスタは、基板1に支持されたゲート電極2と、ゲート電極2を覆うゲート絶縁層3と、ゲート絶縁層3上に設けられた、結晶質シリコン領域Rcを有するシリコン半導体層4であって、結晶質シリコン領域Rcは、第1領域4sと、第2領域4dと、第1領域4sおよび第2領域4dの間に位置するチャネル領域4cとを含み、チャネル領域4c、第1領域4sおよび第2領域4dは、ゲート絶縁層3を介してゲート電極2と重なっている、シリコン半導体層4と、シリコン半導体層4上に、チャネル領域4cを覆い、かつ、第1領域4sおよび第2領域4dを露出するように配置された保護絶縁層5と、第1領域4sと電気的に接続されたソース電極6Aと、第2領域4dと電気的に接続されたドレイン電極6Bとを備え、チャネル領域4cの結晶性は、第1領域4sおよび第2領域4dの結晶性よりも低い。

【選択図】図16

## 【特許請求の範囲】

## 【請求項 1】

基板と、

前記基板に支持されたゲート電極と、

前記ゲート電極を覆うゲート絶縁層と、

前記ゲート絶縁層上に設けられた、結晶質シリコン領域を有するシリコン半導体層であって、前記結晶質シリコン領域は、第1領域と、第2領域と、前記第1領域および前記第2領域の間に位置するチャネル領域とを含み、前記チャネル領域、前記第1領域および前記第2領域は、前記ゲート絶縁層を介して前記ゲート電極と重なっている、シリコン半導体層と、

10

前記シリコン半導体層上に、前記チャネル領域を覆い、かつ、前記第1領域および前記第2領域を露出するように配置された保護絶縁層と、

前記第1領域と電気的に接続されたソース電極と、

前記第2領域と電気的に接続されたドレイン電極と

を備え、

前記チャネル領域の結晶性は、前記第1領域および前記第2領域の結晶性よりも低い、薄膜トランジスタ。

## 【請求項 2】

前記チャネル領域の平均結晶粒径は、前記第1領域および前記第2領域の平均結晶粒径よりも小さい、請求項1に記載の薄膜トランジスタ。

20

## 【請求項 3】

前記チャネル領域は、微結晶シリコンを含み、

前記第1領域および前記第2領域は、多結晶シリコンを含む、請求項1または2に記載の薄膜トランジスタ。

## 【請求項 4】

前記シリコン半導体層は、非晶質シリコン領域をさらに含む、請求項1から3のいずれかに記載の薄膜トランジスタ。

## 【請求項 5】

前記保護絶縁層の一部は、前記シリコン半導体層と前記ソース電極との間に位置し、前記保護絶縁層の他の一部は、前記シリコン半導体層と前記ドレイン電極との間に位置している、請求項1から4のいずれかに記載の薄膜トランジスタ。

30

## 【請求項 6】

前記保護絶縁層の側面の傾斜角は60°以上である、請求項1から5のいずれかに記載の薄膜トランジスタ。

## 【請求項 7】

前記第1領域と前記ソース電極との間に配置され、前記ソース電極と前記第1領域とを接続する第1コンタクト層と、

前記第2領域と前記ドレイン電極との間に配置され、前記ドレイン電極と前記第2領域とを接続する第2コンタクト層と

をさらに備え、

前記第1コンタクト層および前記第2コンタクト層は、それぞれ、n型不純物を含むn<sup>+</sup>型シリコン層を含む、請求項1から6のいずれかに記載の薄膜トランジスタ。

40

## 【請求項 8】

請求項1から7のいずれかに記載の薄膜トランジスタと、

複数の画素を有する表示領域とを有し、

前記薄膜トランジスタは、前記複数の画素のそれぞれに配置されている、表示装置。

## 【請求項 9】

ゲート電極と、前記ゲート電極を覆うゲート絶縁層とが表面に形成された基板を用意する工程(A)と、

前記ゲート絶縁層上に、アモルファスシリコンからなる半導体膜を形成する工程(B)

50

と、

前記半導体膜上に絶縁膜を形成し、前記絶縁膜のパターニングを行うことにより、前記半導体膜のうちチャネル領域となる部分を覆う保護絶縁層を形成する工程（C）と、

前記保護絶縁層の上方から前記半導体膜にレーザ光を照射することによって、前記基板の法線方向から見たときに前記ゲート電極と重なる領域において、前記半導体膜のうち前記保護絶縁層で覆われた部分の結晶性が前記保護絶縁層で覆われていない部分の結晶性よりも低くなるように、結晶化させる工程（D）と、

前記半導体膜のうち前記保護絶縁層で覆われていない前記部分の一部に電気的に接続するソース電極と、前記保護絶縁層で覆われていない前記部分の他の一部に電気的に接続するドレイン電極とを形成する工程（E）と

を包含する、薄膜トランジスタの製造方法。

#### 【請求項 10】

前記レーザ光の波長は、約351nmであり、前記保護絶縁層は酸化珪素層である、請求項9に記載の製造方法。

#### 【請求項 11】

前記工程（D）では、前記半導体膜の一部のみに前記レーザ光を照射して結晶化させ、前記半導体膜のうち前記レーザ光が照射されなかった部分を非晶質のまま残す、請求項9または10に記載の製造方法。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、薄膜トランジスタ、表示装置及び薄膜トランジスタの製造方法に関する。

##### 【背景技術】

##### 【0002】

薄膜トランジスタ（TFT：Thin Film Transistor）は、例えば、液晶ディスプレイや有機EL（Electro-Luminescence）ディスプレイ等の表示装置において、各画素のスイッチング素子として広く用いられている。

##### 【0003】

薄膜トランジスタは、ゲート電極、絶縁層、半導体層（チャネル層）、ソース電極及びドレイン電極を基板上に形成した構成を備える。このうち、ボトムゲート型の薄膜トランジスタは、ゲート電極がチャネル層よりも基板側に形成されていることを特徴としている。

##### 【0004】

ボトムゲート型の薄膜トランジスタの一例として、例えば特許文献1には、ソース電極とドレイン電極との間のチャネル部におけるアモルファスシリコン層をレーザアニール技術により多結晶化した構造が開示されている。

##### 【0005】

また、ボトムゲート型の薄膜トランジスタの他の例として、例えば特許文献2には、部分的にレーザアニールを施し、チャネル部の一部にアモルファスシリコン層を残した構造が開示されている。

##### 【先行技術文献】

##### 【特許文献】

##### 【0006】

【特許文献1】特開2012-114131号公報

【特許文献2】国際公開第2016/072024号

##### 【発明の概要】

##### 【発明が解決しようとする課題】

##### 【0007】

ところで、特許文献1のように、ソース電極とドレイン電極との間のチャネル部を多結晶シリコン層で接続した構成では、移動度が高くなるという利点を有するが、オフ電流も

10

20

30

40

50

高くなるという問題点を有している。

【0008】

一方、特許文献2のように、チャネル部の一部にアモルファスシリコン層を残す構造では、チャネル部の抵抗上昇により、オフ電流は低くなるが、同時に移動度も低くなるという問題点を有している。

【0009】

本発明は、斯かる事情に鑑みてなされたものであり、ソース電極とドレイン電極との間のチャネル部における移動度の低下を抑えつつ、オフ電流を低下させることができる薄膜トランジスタ、薄膜トランジスタを用いた表示装置、薄膜トランジスタの製造方法を提供することを目的とする。

10

【課題を解決するための手段】

【0010】

本発明による一実施形態の薄膜トランジスタは、基板と、前記基板に支持されたゲート電極と、前記ゲート電極を覆うゲート絶縁層と、前記ゲート絶縁層上に設けられた、結晶質シリコン領域を有するシリコン半導体層であって、前記結晶質シリコン領域は、第1領域と、第2領域と、前記第1領域および前記第2領域の間に位置するチャネル領域とを含み、前記チャネル領域、前記第1領域および前記第2領域は、前記ゲート絶縁層を介して前記ゲート電極と重なっている、シリコン半導体層と、前記シリコン半導体層上に、前記チャネル領域を覆い、かつ、前記第1領域および前記第2領域を露出するように配置された保護絶縁層と、前記第1領域と電気的に接続されたソース電極と、前記第2領域と電気的に接続されたドレイン電極とを備え、前記チャネル領域の結晶性は、前記第1領域および前記第2領域の結晶性よりも低い。

20

【0011】

ある実施形態において、前記チャネル領域の平均結晶粒径は、前記第1領域および前記第2領域の平均結晶粒径よりも小さい。

【0012】

ある実施形態において、前記チャネル領域は、微結晶シリコンを含み、前記第1領域および前記第2領域は、多結晶シリコンを含む。

30

【0013】

ある実施形態において、前記シリコン半導体層は、非晶質シリコン領域をさらに含む。

【0014】

ある実施形態において、前記保護絶縁層の一部は、前記シリコン半導体層と前記ソース電極との間に位置し、前記保護絶縁層の他の一部は、前記シリコン半導体層と前記ドレイン電極との間に位置している。

40

【0015】

ある実施形態において、前記保護絶縁層の側面の傾斜角は60°以上である。

【0016】

ある実施形態において、上記薄膜トランジスタは、前記第1領域と前記ソース電極との間に配置され、前記ソース電極と前記第1領域とを接続する第1コンタクト層と、前記第2領域と前記ドレイン電極との間に配置され、前記ドレイン電極と前記第2領域とを接続する第2コンタクト層とをさらに備え、前記第1コンタクト層および前記第2コンタクト層は、それぞれ、n型不純物を含むn<sup>+</sup>型シリコン層を含む。

【0017】

本発明の一実施形態の表示装置は、上記のいずれかに記載の薄膜トランジスタと、複数の画素を有する表示領域とを有し、前記薄膜トランジスタは、前記複数の画素のそれぞれに配置されている。

【0018】

本発明の一実施形態の、薄膜トランジスタの製造方法は、ゲート電極と、前記ゲート電極を覆うゲート絶縁層とが表面に形成された基板を用意する工程(A)と、前記ゲート絶縁層上に、アモルファスシリコンからなる半導体膜を形成する工程(B)と、前記半導体

50

膜上に絶縁膜を形成し、前記絶縁膜のパターニングを行うことにより、前記半導体膜のうちチャネル領域となる部分を覆う保護絶縁層を形成する工程（C）と、前記保護絶縁層の上方から前記半導体膜にレーザ光を照射することによって、前記基板の法線方向から見たときに前記ゲート電極と重なる領域において、前記半導体膜のうち前記保護絶縁層で覆われた部分の結晶性が前記保護絶縁層で覆われていない部分の結晶性よりも低くなるように、結晶化させる工程（D）と、前記半導体膜のうち前記保護絶縁層で覆われていない前記部分の一部に電気的に接続するソース電極と、前記保護絶縁層で覆われていない前記部分の他の一部に電気的に接続するドレイン電極とを形成する工程（E）とを包含する。

#### 【0019】

ある実施形態において、前記レーザ光の波長は、約351nmであり、前記保護絶縁層は酸化珪素層である。

#### 【0020】

ある実施形態において、前記工程（D）では、前記半導体膜の一部のみに前記レーザ光を照射して結晶化させ、前記半導体膜のうち前記レーザ光が照射されなかつた部分を非晶質のまま残す。

#### 【発明の効果】

#### 【0021】

本願によれば、ソース電極とドレイン電極との間のチャネル部における移動度の低下を抑えつつ、オフ電流を低下させることができる。

#### 【図面の簡単な説明】

#### 【0022】

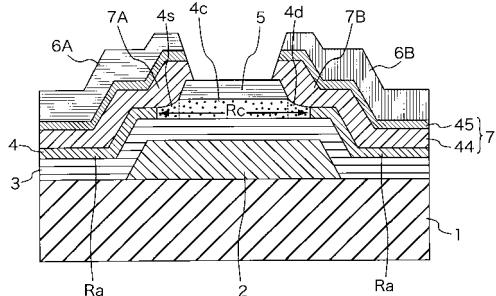

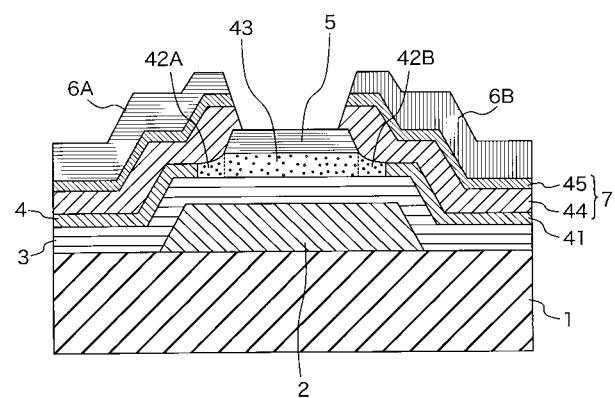

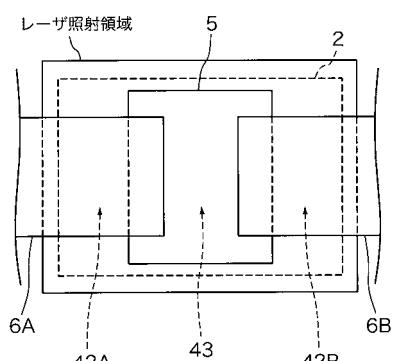

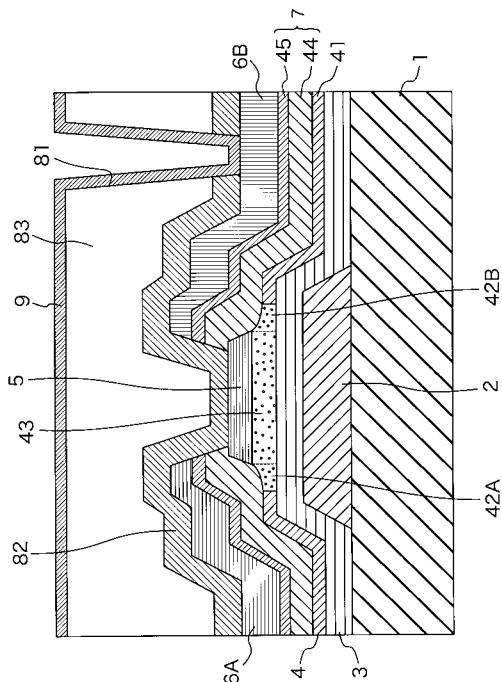

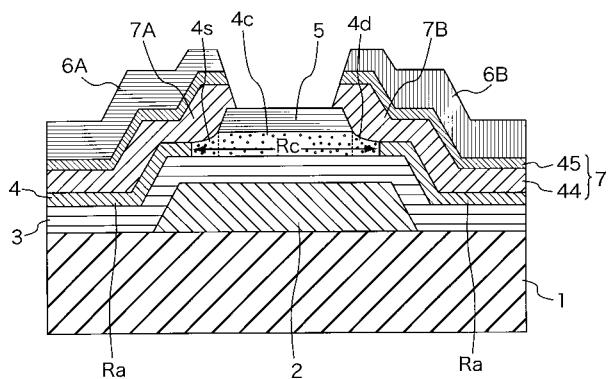

【図1】実施の形態1に係る薄膜トランジスタの構成を説明する模式的断面図である。

【図2】実施の形態1に係る薄膜トランジスタの構成を説明する模式的平面図である。

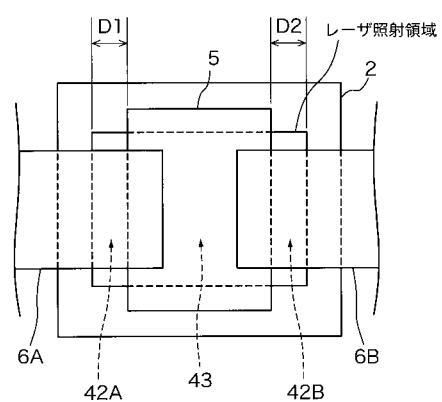

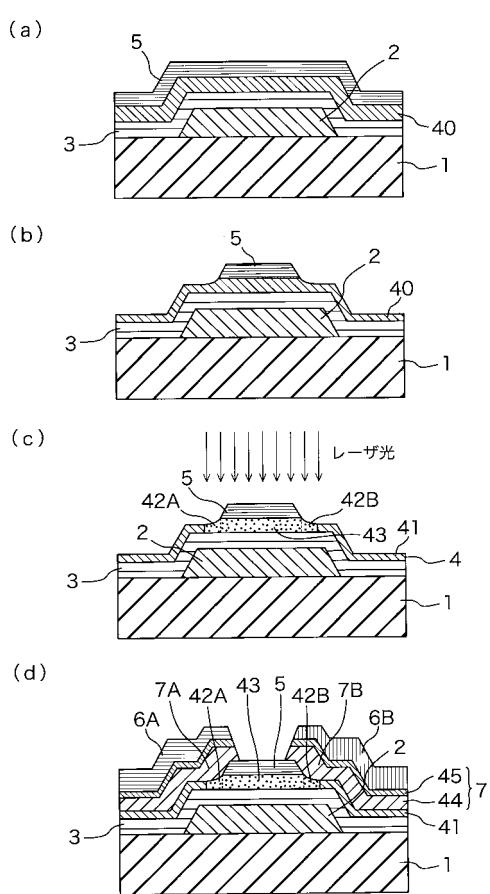

【図3】実施の形態1に係る薄膜トランジスタの製造方法を説明する模式的断面図である。

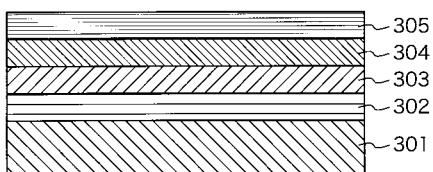

【図4】レーザ光吸収率を計算する際に用いた膜構造モデルを示す模式的断面図である。

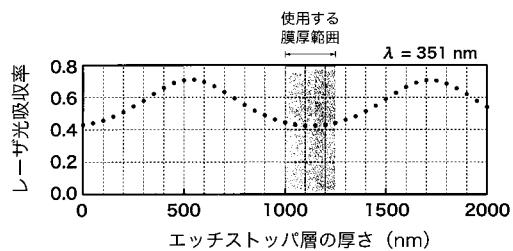

【図5】レーザ光吸収率の計算結果を示すグラフである。

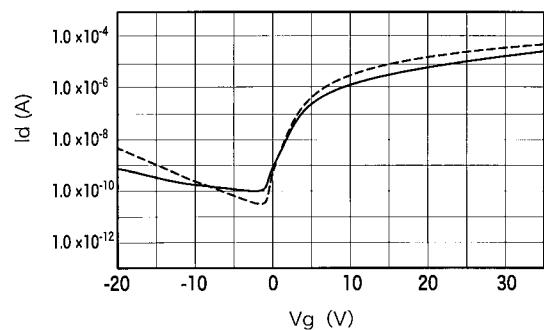

【図6】本実施の形態に係る薄膜トランジスタのVg - Id特性を示すグラフである。

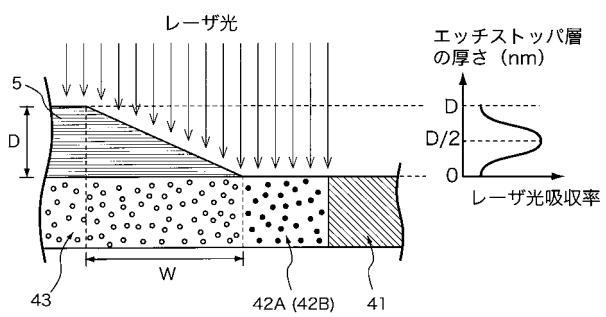

【図7】エッチストップ膜のエッジにおける傾斜角と結晶性との関係を説明する説明図である。

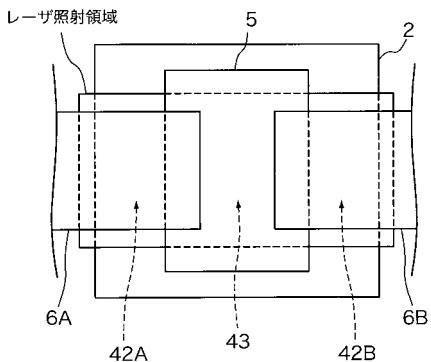

【図8】変形例1における薄膜トランジスタの模式的平面図である。

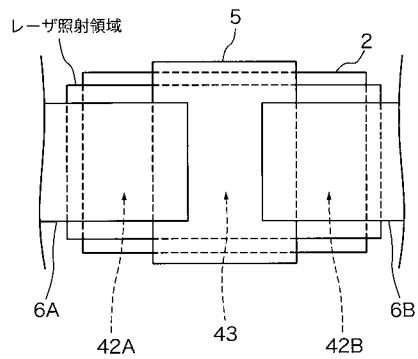

【図9】変形例2における薄膜トランジスタの模式的平面図である。

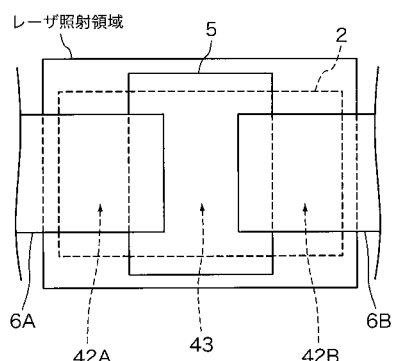

【図10】変形例3における薄膜トランジスタの模式的平面図である。

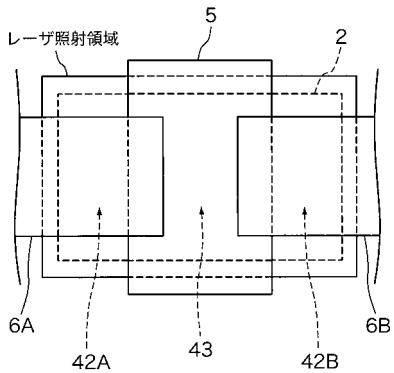

【図11】変形例4における薄膜トランジスタの模式的平面図である。

【図12】変形例5における薄膜トランジスタの模式的平面図である。

【図13】実施の形態2に係る薄膜トランジスタの構成を説明する模式的断面図である。

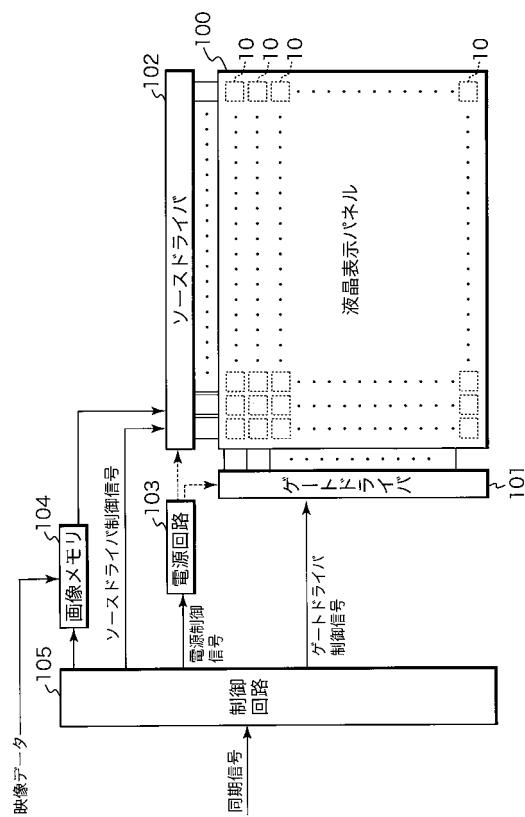

【図14】実施の形態2に係る表示装置の構成を説明するブロック図である。

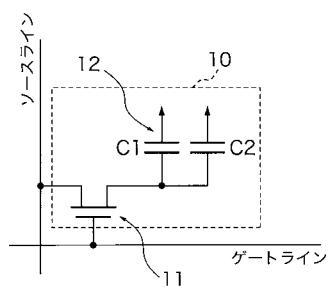

【図15】各画素の構成例を説明する回路図である。

【図16】実施の形態の薄膜トランジスタの断面図である。

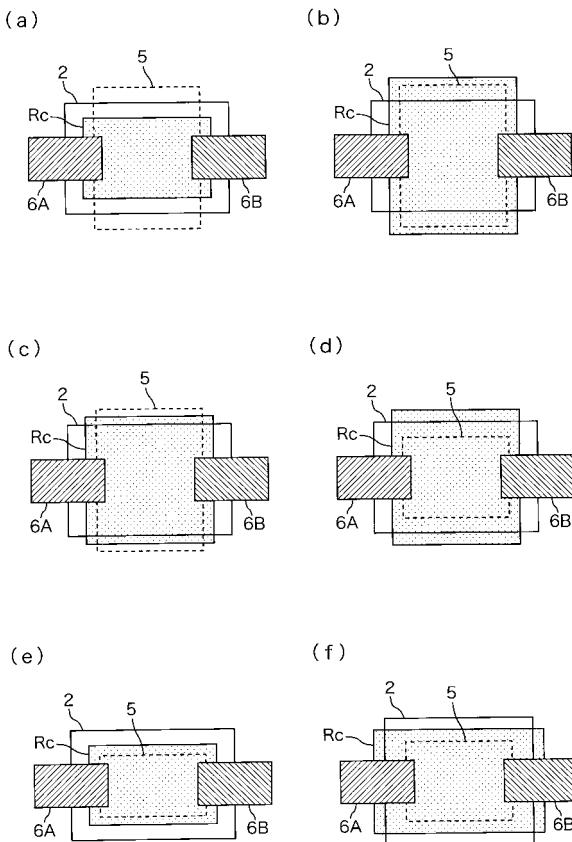

【図17】薄膜トランジスタのさらに他の例を示す平面図である。

#### 【発明を実施するための形態】

#### 【0023】

本発明の実施の形態を図面に基づいて具体的に説明する。

（実施の形態1）

図1は実施の形態1に係る薄膜トランジスタの構成を説明する模式的断面図であり、図2はその模式的平面図である。実施の形態1に係る薄膜トランジスタは、例えば、ゲート電極2、ゲート絶縁層3、半導体層4、コンタクト層7、エッチストップ膜（保護絶縁層）5、ソース電極6A及びドレイン電極6Bを備える。なお、図2の平面図では、簡略化のために、ゲート電極2と、半導体層4を構成する多結晶シリコン領域42A、42B及び微結晶シリコン領域43と、エッチストップ膜5との位置関係のみを示しており、薄膜

10

20

30

40

50

トランジスタのその他の構成については省略して示している。

【0024】

ゲート電極2は、基板1の表面にパターン形成された電極であり、例えばAl、Mg、Mo、Cr、Ta、Cu、Ti、Ni、W、Mn等の金属、これらの金属を主成分とする合金、又は金属酸化物等の材料を用いて形成することができる。ここで、基板1としては、例えばガラス基板などの絶縁性を有する基板が用いられる。

【0025】

ゲート絶縁層3は、基板1上でゲート電極2を覆うように形成されている。ゲート絶縁層3は、有機物質の絶縁膜であってもよく、無機物質の絶縁膜であってもよい。有機物質の絶縁膜では、例えばTEOS (Tetraethyl orthosilicate, オルトケイ酸テトラエチル)を用いることができる。また、無機物質の絶縁膜では、SiO<sub>2</sub>、SiO<sub>2</sub>/SiN、SiN、SiON、Al<sub>2</sub>O<sub>3</sub>、HfO<sub>2</sub>などを用いることができる。

【0026】

半導体層4は、第1アモルファスシリコン領域41、多結晶シリコン領域42A、42Bおよび微結晶シリコン領域43を含む。コンタクト層7は、第2アモルファスシリコン層44、及びn<sup>+</sup>シリコン層45を含む。第1アモルファスシリコン領域41は、ゲート絶縁層3の上側(基板と反対側)に形成されており、例えば25nm以上の厚さを有する。また、多結晶シリコン領域42A、42B及び微結晶シリコン領域43は、第1アモルファスシリコン領域41と同様にゲート絶縁層3の上側に形成されており、第1アモルファスシリコン領域41と同一レイヤ内に存在する。

【0027】

本実施の形態では、平面視においてゲート電極2の外縁により画定される領域(図2に示す例では矩形状の領域であり、以下「ゲート領域」という)の内側に多結晶シリコン領域42A、42B、及び微結晶シリコン領域43が形成されている。また、本実施の形態では、半導体層4のうちエッチストップ膜5に覆われた領域が微結晶シリコン領域43であり、微結晶シリコン領域43を挟んで両側に位置する領域が、それぞれ、多結晶シリコン領域42A、42Bである。すなわち、本実施の形態では、半導体層4のうちエッチストップ膜5で覆われた領域の結晶性が、その外側の2つの領域の結晶性より低い。ここで、微結晶シリコン領域43を挟んで両側に位置し、エッチストップ膜5により覆われていない領域42A、42Bの幅D1、D2は、それぞれ、3μm以上であることが好ましい。

【0028】

なお、半導体層4の結晶性は、例えば透過型電子顕微鏡(TEM)を用いた断面形状の観察などにより判別することができる。例えば、透過型電子顕微鏡による回折像において、リング状の回折パターンがなく、ぼんやりとしたハローパターンのみを有しているもの、若しくはハローパターンの中にリング状の回折パターンを1つだけ有しているものを、非晶質(アモルファス)として判別することができる。また、透過型電子顕微鏡による回折像において、リング状の回折パターン(デバイシェラーリング)が2つ以上観測される場合であって、観測されるデバイシェラーリングの数が多いものを多結晶と判別し、少ないものを微結晶と判別することができる。

【0029】

また、電子顕微鏡写真を用いた結晶粒の形状測定によっても、半導体層4の結晶性を判別することができる。例えば、微結晶の結晶系は、立方晶系又は六方晶系の何れか一方であってもよく、両方の結晶系が混合された状態であってもよい。また、微結晶における結晶粒の大きさは1nm以上15nm以下、好ましくは5nm以上15nm以下、より好ましくは10nm以上15nm以下である。一方、多結晶は、複数の面方位を含む結晶の集まりであってもよく、ある面方位が主となって成長した微結晶の集まりであってもよい。多結晶における結晶粒の大きさは、好ましくは15nm以上10μm以下である。

【0030】

更に、ラマン分光法を用いて結晶化率を測定してもよい。例えば、結晶化率Xcは、X

10

20

30

40

50

$c = (P_c + P_m) / (P_c + P_m + P_a)$  により算出される。ここで、 $P_c$  はラマン分光スペクトルの  $520\text{ cm}^{-1}$  付近のピークのピーク面積、(シリコン結晶のピーク面積)を表し、 $P_m$  はラマン分光スペクトルの  $509\text{ cm}^{-1}$  付近のピークのピーク面積(シリコン微結晶のピーク面積)を表し、 $P_a$  は  $480\text{ cm}^{-1}$  付近のピークのピーク面積(アモルファスシリコンのピーク面積)を表す。測定した結晶化率  $X_c$  が 90% 以上のものを多結晶、90%未満 50% 以上のものを微結晶、50%未満のものを非晶質として判別することができる。

#### 【0031】

以上のような第 1 アモルファスシリコン領域 41 及び多結晶シリコン領域 42A, 42B の上側には、コンタクト層 7 が形成されている。コンタクト層 7 は、例えば、厚さが 50 ~ 90 nm 程度の第 2 アモルファスシリコン層 44 と、第 2 アモルファスシリコン層 44 の上に配置された、厚さが 10 ~ 50 nm 程度の  $n^+$  シリコン層 45 を含む。 $n^+$  シリコン層 45 は、リンやヒ素などの不純物を高濃度で含むシリコン層である。

10

#### 【0032】

また、微結晶シリコン領域 43 の上側には島状のエッチストップ膜 5 が形成されている。エッチストップ膜 5 は、例えば  $\text{SiO}_2$  などの材料を用いて形成することができる。本実施の形態では、ゲート電極 2 の上方に位置し、ゲート領域の内側において半導体層 4 の一部の領域(微結晶シリコン領域 43 が形成される領域)を覆うようにエッチストップ膜 5 が形成されている。

20

#### 【0033】

コンタクト層 7 ( $n^+$  シリコン層 45) の上には、所要のパターンを有するソース電極 6A 及びドレイン電極 6B が互いに離隔して形成されている。ソース電極 6A 及びドレイン電極 6B は、例えば Al、Mg、Mo、Cr、Ta、Cu、Ti、Ni、W、Mn 等の金属、これらの金属を主成分とする合金、又は金属酸化物等の材料を用いて形成することができる。本実施の形態では、エッチストップ膜 5 により覆われていない一方の多結晶シリコン領域 42A の上方にソース電極 6A が形成され、エッチストップ膜 5 により覆われていない他方の多結晶シリコン領域 42B の上方にドレイン電極 6B が形成されている。

20

#### 【0034】

図 3 は実施の形態 1 に係る薄膜トランジスタの製造方法を説明する模式的断面図である。まず、ガラス基板等の絶縁性を有する基板 1 の表面に、スパッタリング法により、例えば Al、Mg、Mo、Cr、Ta、Cu、Ti、Ni、W、Mn 等の金属、これらの金属を主成分とする合金、又は金属酸化物等の材料による金属膜を成膜し、フォトマスクを用いたフォトリソグラフィ、金属膜のドライエッティング、レジストの剥離、及び洗浄を行うことにより、ゲート電極 2 をパターン形成する。

30

#### 【0035】

次いで、CVD (Chemical Vapor Deposition) 法により、例えば  $\text{SiO}_2$ 、 $\text{SiN}$  等の材料を用いて成膜することにより、基板 1 上でゲート電極 2 を覆うようにゲート絶縁層 3 を形成する。ゲート絶縁層 3 は、例えば  $\text{SiO}_2$ 、 $\text{SiN}$  等の材料の積層膜でも良い。

#### 【0036】

次いで、CVD 法を用いて、30 ~ 100 nm 程度の厚さを有するアモルファスシリコン膜 40 を形成する。また、CVD 法を用いて、100 ~ 125 nm 程度の厚さを有する  $\text{SiO}_2$  膜を成膜することにより、アモルファスシリコン膜 40 の上にエッチストップ膜 5 を形成する。図 3 (a) は、基板 1 の表面に、ゲート電極 2、ゲート絶縁層 3、アモルファスシリコン膜 40、及びエッチストップ膜 5 を形成した状態を示している。

40

#### 【0037】

次に、アモルファスシリコン膜 40 における水素濃度が 2 at% 以下となるように脱水素化を行うと共に、フォトマスクを用いたフォトリソグラフィ、エッチストップ膜 5 のドライエッティング、レジストの剥離、及び洗浄を行うことにより、エッチストップ膜 5 を島状に形成する。この時点で、アモルファスシリコン膜 40 は、エッチストップ膜 5 により覆われた領域と、エッチストップ膜 5 により覆われていない領域とを有する。エッチスト

50

ツバ膜 5 で覆われた領域の厚さは、エッチストップ膜 5 で覆われていない領域の厚さよりも大きく、例えば 250 以上であってもよい。図 3 (b) は、アモルファスシリコン膜 40 の上に島状のエッチストップ膜 5 を形成した状態を示している。

#### 【0038】

次に、エッチストップ膜 5 の上側から、平面視でゲート領域の内側であって、エッチストップ膜 5 の外縁により画定される領域よりも大きな領域にレーザ光（エネルギービーム）を照射して、アモルファスシリコン膜 40 のアニール処理を行う。アニール処理に用いるレーザ光としては、200 ~ 400 nm の波長を有する XeF、KrF、XeCl などの混合ガスを用いたエキシマレーザ、若しくは YAG (Yttrium Aluminum Garnet)、3 倍波などの固体レーザを使用することができる。アモルファスシリコン膜 40 におけるレーザ光吸收率は、エッチストップ膜 5 の厚さによって変化する。本実施の形態では、以下の観点から、エッチストップ膜 5 の厚さが設定される。

#### 【0039】

図 4 はレーザ光吸收率を計算する際に用いた膜構造モデルを示す模式的断面図であり、図 5 はレーザ光吸收率の計算結果を示すグラフである。本実施の形態では、ゲート電極 301、ゲート絶縁層 302、303、アモルファスシリコン層 304、及びエッチストップ層 305 の 5 つの層からなる多層膜構造の膜構造モデルを採用し、各膜の境界面において振幅反射率及び振幅透過率を考慮することにより、アモルファスシリコン層におけるレーザ光吸收率を計算した。

#### 【0040】

なお、計算に使用したレーザ光の波長を 351 nm とした。また、ゲート電極 301 は、上記レーザ光に対する屈折率が 3.06、消衰係数が 3.22 の Mo 膜（厚さ：未設定）とした。ゲート絶縁層 302 は、上記レーザ光に対する屈折率が 2.1、消衰係数が 0 の SiN 膜（厚さ：固定）とし、ゲート絶縁層 303 は、屈折率が 1.48、消衰係数が 0 の SiO<sub>2</sub> 膜（厚さ：固定）とした。アモルファスシリコン層 304 は、屈折率が 4.5、消衰係数が 3.42 のアモルファスシリコン膜（厚さ：固定）とした。エッチストップ層 305 は、屈折率 1.48、消衰係数 0 の酸化珪素 (SiO<sub>2</sub>) 膜（厚さ：可変）とした。

#### 【0041】

上記膜構造モデルの表面と垂直な方向から波長 351 nm のレーザ光を入射したときの多重干渉を考慮し、エッチストップ層 305 の厚さを変化させながら、アモルファスシリコン層 304 におけるレーザ光の吸収率を計算した。

#### 【0042】

図 5 に示すグラフは、エッチストップ層 305 の厚さを変化させたときのアモルファスシリコン層 304 におけるレーザ光吸収率の計算結果を示している。グラフの横軸はエッチストップ層 305 の厚さ (nm) を表し、縦軸はアモルファスシリコン層 304 におけるレーザ光吸収率を表している。図 5 に示す計算結果から、アモルファスシリコン層 304 (アモルファスシリコン膜 40 に対応) におけるレーザ光吸収率は、エッチストップ層 305 (エッチストップ膜 5 に対応) の厚さに対して、およそ 0.4 (極小値) から 0.7 (極大値) の範囲で周期的に変化することが分かる。

#### 【0043】

本実施の形態では、図 5 の計算結果を参照して、エッチストップ膜 5 の厚さを設定する。具体的には、アモルファスシリコン膜 40 におけるレーザ光吸収率が、極小値又は極小値近傍の値（極小値を含む所定範囲内の値）となるような厚さを設定する。

#### 【0044】

例えば、本実施の形態では、アモルファスシリコン膜 40 におけるレーザ光吸収率が極小値を含む所定範囲内の値となるように、エッチストップ膜 5 の厚さを 100 ~ 125 nm の範囲で設定し、設定した厚さとなるようにエッチストップ膜 5 を成膜する。その後、ドライエッ칭、レジストの剥離、及び洗浄によりエッチストップ膜 5 を島状に形成し、更に上記波長を有するレーザ光（エキシマレーザ又は固体レーザ）を照射して、アモル

10

20

30

40

50

ファスシリコン膜40にアニール処理を施し、結晶化させる。

【0045】

エッチストップ膜5の厚さが100～125nmの範囲においてアモルファスシリコン膜40のレーザ光吸収率は極小値又は極小値近傍の値となり、エッチストップ膜5が存在しない場合(厚さが0の場合)とレーザ光吸収率が略同等となる。すなわち、アモルファスシリコン膜40のうちエッチストップ膜5で覆われた領域のレーザ光吸収率と、エッチストップ膜5で覆われていない領域のレーザ光吸収率とは略同じであるため、両者におけるレーザ光吸収による熱エネルギーの発生は本来的に略同等である。

【0046】

しかしながら、エッチストップ膜5で覆われている領域では、エッチストップ膜5により熱が吸収され、アモルファスシリコンが結晶化するための熱エネルギーが減少するので、エッチストップ膜5で覆われている領域の結晶性は、エッチストップ膜5で覆われていない領域の結晶性よりも低くなる。この結果、例えば、アモルファスシリコン膜40のうちエッチストップ膜5で覆われている領域では、アモルファスシリコンの一部が微結晶シリコンに変化し、エッチストップ膜5で覆われていない領域では、アモルファスシリコンの一部が多結晶シリコンに変化する。

【0047】

なお、アニール処理に用いるレーザ光のエネルギーを増加させた場合、形成された多結晶シリコンの凝集が発生し、層内にシリコンが存在しない領域(ボイド)が形成される可能性がある。このようなボイドが存在する場合、個々の薄膜トランジスタの特性にばらつきが生じ、表示パネルのスイッチング素子として用いたときのムラの要因となり得る。本実施の形態では、エッチストップ膜5により覆われた領域と、エッチストップ膜5により覆われていない領域とにおいて、アモルファスシリコン膜40におけるレーザ光吸収率が同程度であり、しかもエッチストップ膜5により覆われている領域での発熱は、エッチストップ膜5による熱の吸収があるため、エッチストップ膜5により覆われていない領域と比較して小さくなる。よって、本実施の形態では、エッチストップ膜5で覆われていない領域において結晶性が高くなりすぎる条件(大粒径化)でアニール処理をしない限り、エッチストップ膜5で覆われた領域にてボイドの発生は起こりにくい。

【0048】

上述したレーザ光を用いてエッチストップ膜5の上方からアモルファスシリコン膜40にアニール処理を施すことにより、アモルファスシリコン膜40のうちエッチストップ膜5で覆われた領域に微結晶シリコン領域43が形成され、微結晶シリコン領域43の両側に位置し、エッチストップ膜5で覆われていない領域に多結晶シリコン領域42A、42Bが形成される。アモルファスシリコン膜40のうちレーザ光が照射されなかった領域は、非晶質のまま残る(第1アモルファスシリコン領域41)。図3(c)はレーザ光によるアニール処理により、第1アモルファスシリコン領域41、多結晶シリコン領域42A、42B、及び微結晶シリコン領域43を含む半導体層4を形成した状態を示している。

【0049】

次に、CVD法を用いて、30～100nm程度の厚さを有するアモルファスシリコンの膜を成膜し、第2アモルファスシリコン層44を形成する。また、CVD法を用いて、リンやヒ素などの不純物濃度が高いアモルファスシリコンの膜を成膜し、第2アモルファスシリコン層44の上に、10～50nm程度の厚さを有するn<sup>+</sup>シリコン層45を形成する。

【0050】

次いで、スパッタリング法により、例えばAl、Mg、Mo、Cr、Ta、Cu、Ti、Ni、W、Mn等の金属、これらの金属を主成分とする合金、又は金属酸化物等の材料による金属膜を成膜し、フォトマスクを用いたフォトリソグラフィ、金属膜のドライエッティング、レジストの剥離、及び洗浄を行うことにより、コンタクト層7の上にソース電極6A及びドレイン電極6Bをパターン形成する。このとき、エッチストップ膜5の上でソース電極6A及びドレイン電極6Bは互いに離隔し、かつ、多結晶シリコン領域42Aの

10

20

30

40

50

上方にソース電極 6 A の一部、多結晶シリコン領域 4 2 B の上方にドレイン電極 6 B の一部が位置するように、フォトマスクを用いたフォトリソグラフィ、及び金属膜のドライエッティングを行う。コンタクト層 7 も、同様に、ソース電極 6 A 側とドレイン電極 6 B 側とに分離してもよい。コンタクト層 7 のうちソース電極 6 A と多結晶シリコン領域 4 2 A とを接続する部分 7 A を第 1 コンタクト層、ドレイン電極 6 B と多結晶シリコン領域 4 2 B とを接続する部分 7 B を第 2 コンタクト層と呼ぶ。図 3 ( d ) はソース電極 6 A 及びドレイン電極 6 B を形成した状態を示している。

#### 【 0 0 5 1 】

次に、本実施の形態に係る薄膜トランジスタの電気的特性について説明する。

図 6 は本実施の形態に係る薄膜トランジスタの  $V_g$  -  $I_d$  特性を示すグラフである。グラフの横軸はゲート電圧  $V_g$  ( V )、縦軸はドレイン電流  $I_d$  ( A ) を表している。なお、ドレイン電圧  $V_d$  の値を 10 V とした。図 6 において、実線のグラフは本実施の形態に係る薄膜トランジスタの  $V_g$  -  $I_d$  特性を表し、破線のグラフはチャネル部が多結晶シリコン領域のみにより形成された比較例の薄膜トランジスタにおける  $V_g$  -  $I_d$  特性を表している。

#### 【 0 0 5 2 】

図 6 に示すグラフから以下の電気的特性が得られた。

( 1 ) 移動度は、比較例では  $6.05 \text{ cm}^2 / \text{V s}$  であったのに対し、本実施の形態に係る薄膜トランジスタでは  $3.73 \text{ cm}^2 / \text{V s}$  となった。

( 2 ) サブスレッショルド係数は、比較例では  $4.2 \text{ V / dec}$  であったのに対し、本実施の形態に係る薄膜トランジスタでは  $8.22 \text{ V / dec}$  となった。

( 3 ) 閾値電圧は、比較例では  $0.89 \text{ V}$  であったのに対し、本実施の形態に係る薄膜トランジスタでは  $1.28 \text{ V}$  となった。

( 4 ) オフ電流は、ゲート電圧が  $-15 \text{ V}$  のとき、比較例では  $1.03 \times 10^{-9} \text{ A}$  であったのに対し、本実施の形態に係る薄膜トランジスタでは  $3.56 \times 10^{-10} \text{ A}$  となった。

#### 【 0 0 5 3 】

上記の結果から、移動度については比較例と較べて低下するものの、液晶ディスプレイパネルなどの周辺駆動回路を形成するのに十分な値を確保できることが分かった。また、オフ電流については、比較例と較べて 1 衍近く下げることが可能となることが分かった。

#### 【 0 0 5 4 】

以上のように、本実施の形態では、ソース電極 6 A とドレイン電極 6 B との間のチャネル部を結晶性の高い多結晶シリコン領域 4 2 A、4 2 B を介して、結晶性の低い微結晶シリコン領域 4 3 で接続することにより、チャネル部における抵抗を増加させることができ、ソース電極 6 A とドレイン電極 6 B との間のチャネル部における移動度の低下を抑えつつ、オフ電流を下げることが可能となった。

#### 【 0 0 5 5 】

なお、本実施の形態では、エッチストップ膜 5 のエッジは急峻な傾斜角（例えば 60 度以上）を有することが好ましい。

#### 【 0 0 5 6 】

図 7 はエッチストップ膜 5 のエッジ（側面）における傾斜角と結晶性との関係を説明する説明図である。図 7 に示されているように、エッチストップ膜 5 のエッジが傾斜している場合、エッジにおけるエッチストップ膜 5 の厚さは 0 から D ( D は設定された厚さ ) まで変化する。また、厚さが変化する領域 W は、エッジの傾斜角が小さくなる程、広くなる。本実施の形態では、レーザ光によるアーナール処理をアモルファスシリコン膜 4 0 に施すことにより、微結晶シリコン領域 4 3 及び多結晶シリコン領域 4 2 A、4 2 B を形成している。上述したように、微結晶シリコン領域 4 3 における結晶性は、エッチストップ膜 5 の厚さによって変化するので、厚さが変化する領域 W が広い場合、この領域 W 内でレーザ光の吸収率が高い領域（厚さが D / 2 付近の領域）が発生し、アブレーションが発生する可能性がある。以上のことから、本実施の形態では、エッチストップ膜 5 のエッジは急峻な傾斜角（例えば 60 度以上）を有することが好ましい。傾斜角は約 90 度以下であって

10

20

30

40

50

もよい。なお、エッチストッパ膜 5 の傾斜角は、ドライエッチング時のガス圧やレジスト形状を適宜調整することにより制御することが可能である。

【0057】

次に、ゲート電極 2、結晶質シリコン領域（すなわちレーザ照射領域）、及びエッチストッパ膜 5 の配置関係が実施の形態 1 とは異なる変形例について説明する。

【0058】

（変形例 1）

図 8 は変形例 1 における薄膜トランジスタの模式的平面図である。変形例 1 では、結晶質シリコン領域（すなわちレーザ照射領域）がゲート領域からはみ出している。このような構成は、アモルファスシリコン膜 40 のアニール処理において、レーザ光の照射領域をゲート領域の外側まで拡大することにより形成される。

10

【0059】

（変形例 2）

図 9 は変形例 2 における薄膜トランジスタの模式的平面図である。変形例 2 では、結晶質シリコン領域（すなわちレーザ照射領域）がゲート領域からはみ出して形成され、かつ、エッチストッパ膜 5 がゲート領域からはみ出した部分を有する。このような構成は、エッチストッパ膜 5 のエッチングを行う際に、フォトマスクの範囲をゲート領域の外側まで拡大し、ゲート領域の外側部分を残すことによって形成される。また、アモルファスシリコン膜 40 のアニール処理において、レーザ光の照射領域をゲート領域の外側まで拡大することにより形成される。

20

【0060】

（変形例 3）

図 10 は変形例 3 における薄膜トランジスタの模式的平面図である。変形例 3 では、エッチストッパ膜 5 がゲート領域からはみ出した部分を有し、結晶質シリコン領域（すなわちレーザ照射領域）がゲート領域及びエッチストッパ膜 5 の外縁により画定される領域からはみ出している。このような構成は、エッチストッパ膜 5 のエッチングの際に、フォトマスクの範囲をゲート領域の外側まで拡大し、ゲート領域の外側部分を残すことによって形成される。また、アモルファスシリコン膜 40 のアニール処理において、レーザ光の照射領域をゲート領域及びエッチストッパ膜 5 の外縁により画定される領域の外側まで拡大することにより形成される。

30

【0061】

（変形例 4）

図 11 は変形例 4 における薄膜トランジスタの模式的平面図である。変形例 4 では、結晶質シリコン領域（すなわちレーザ照射領域）がゲート領域からはみ出して形成され、エッチストッパ膜 5 がゲート領域及び結晶質シリコン領域（すなわちレーザ照射領域）からはみ出した部分を有する。このような構成は、エッチストッパ膜 5 のエッチングの際に、フォトマスクの範囲をゲート領域及び結晶質シリコン領域（すなわちレーザ照射領域）の外側まで拡大し、ゲート領域及び結晶質シリコン領域（すなわちレーザ照射領域）の外側部分を残すことによって形成される。また、アモルファスシリコン膜 40 のアニール処理において、レーザ光の照射領域をゲート領域の外側まで拡大することにより形成される。

40

【0062】

（変形例 5）

図 12 は変形例 5 における薄膜トランジスタの模式的平面図である。変形例 5 では、アモルファスシリコン膜 40 のアニール処理において、結晶質シリコン領域（すなわちレーザ照射領域）がゲート領域からはみ出して形成され、エッチストッパ膜 5 がゲート領域の内側の領域に形成されていることを特徴とする。このよう構成は、エッチストッパ膜 5 のエッチングの際に、フォトマスクの範囲をゲート領域の内側に制限することによって形成される。また、アモルファスシリコン膜 40 のアニール処理において、レーザ光の照射領域をゲート領域の外側まで拡大することにより形成される。

50

【0063】

## (実施の形態 2 )

実施の形態 2 では、本実施の形態に係る薄膜トランジスタを用いた表示装置の構成について説明する。

## 【0064】

実施の形態 1 に係る薄膜トランジスタを液晶表示装置におけるスイッチング素子として用いる場合、ソース電極 6 A 及びドレイン電極 6 B の上層には、パッシベーション膜 8 2 、有機膜 8 3 及び画素電極 9 が順次形成される（図 13 を参照）。

## 【0065】

図 13 は実施の形態 2 に係る薄膜トランジスタの構成を説明する模式的断面図である。実施の形態 2 に係る薄膜トランジスタは、例えば、ゲート電極 2 、ゲート絶縁層 3 、半導体層 4 、エッチストップ膜 5 、コンタクト層 7 、ソース電極 6 A 及びドレイン電極 6 B 、並びにパッシベーション膜 8 2 、有機膜 8 3 及び画素電極 9 を備える。なお、ゲート電極 2 、ゲート絶縁層 3 、半導体層 4 、エッチストップ膜 5 、コンタクト層 7 、ソース電極 6 A 及びドレイン電極 6 B の構成は実施の形態 1 と同様である。

10

## 【0066】

パッシベーション膜 8 2 は、例えば SiN 等を用いた CVD 法により、ソース電極 6 A 及びドレイン電極 6 B の上層に形成される。また、パッシベーション膜 8 2 の上層には、アクリル系の樹脂からなる SOG (Spin-on Glass) 等の有機膜 8 3 が形成される。その後、フォトリソグラフィ、ドライエッティング、レジストの剥離、及び洗浄によりパターニングされてドレイン電極 6 B に対するコンタクトホール 8 1 が設けられる。また、有機膜 8 3 の上層には、スパッタリング法により ITO (Indium Tin Oxide) 膜が形成され、パターニングすることにより画素電極 9 が形成される。

20

## 【0067】

図 14 は実施の形態 2 に係る表示装置の構成を説明するブロック図である。図 14 に示す表示装置は、液晶表示装置の一例を示したものであり、例えば、液晶表示パネル 100 、ゲートドライバ 101 、ソースドライバ 102 、電源回路 103 、画像メモリ 104 、及び制御回路 105 を備える。

## 【0068】

制御回路 105 は、外部から入力される同期信号に同期して、ゲートドライバ 101 、ソースドライバ 102 、電源回路 103 、及び画像メモリ 104 をそれぞれ制御するための制御信号を出力する。

30

## 【0069】

画像メモリ 104 は、表示対象の映像データを一時的に記憶し、制御回路 105 から入力されるメモリ制御信号に従い、映像データをソースドライバ 102 へ出力する。なお、画像メモリ 104 は、制御回路 105 に内蔵され、制御回路 105 の内部処理を経てソースドライバ 102 へ映像データを出力する構成であってもよい。

## 【0070】

電源回路 103 は、制御回路 105 から入力される電源制御信号に基づき、ゲートドライバ 101 用の駆動電圧、及びソースドライバ 102 用の駆動電圧等を生成し、それぞれゲートドライバ 101 及びソースドライバ 102 へ供給する。

40

## 【0071】

ゲートドライバ 101 は、制御回路 105 から入力されるゲートドライバ制御信号に基づき、液晶表示パネル 100 にマトリクス状に配置されている各画素 10 が備えるスイッチング素子 11 (図 15 を参照) をオン / オフするための走査信号を生成し、生成した走査信号をゲートドライバに接続された各ゲートラインへ順次印加する。

## 【0072】

ソースドライバ 102 は、制御回路 105 から入力されるソースドライバ制御信号に基づき、画像メモリ 104 から入力される映像データに応じたデータ信号を生成し、生成したデータ信号をソースドライバ 102 のそれぞれに接続された各ソースラインへ順次印加する。ソースドライバ 102 よりソースラインを通じて供給されるデータ信号は、対応す

50

るスイッチング素子 11 がオンである場合に、各画素 10 に書き込まれる。

【0073】

なお、本実施の形態では、ゲートドライバ 101 及びソースドライバ 102 を液晶表示パネル 100 の外部に設けた構成について説明したが、液晶表示パネル 100 の周縁にゲートドライバ 101 及びソースドライバ 102 を実装する構成としてもよい。

【0074】

図 15 は各画素 10 の構成例を説明する回路図である。各画素 10 は、スイッチング素子 11 と、表示素子 12 とを備える。スイッチング素子 11 は、例えば実施の形態 1 に示す薄膜トランジスタであり、そのソース電極 6A はソースラインに接続され、ドレイン電極 6B は画素電極 9 に接続されている。また、スイッチング素子 11 のゲート電極 2 はゲートラインに接続されている。スイッチング素子 11 は、ゲートラインに供給される走査信号に応じてオン / オフの状態が切り替わり、画素電極 9 をソースラインから電気的に切り離したり、画素電極 9 をソースラインに電気的に接続したりすることが可能である。

10

【0075】

液晶表示パネル 100 は、画素電極 9 に対向した対向電極を備える。画素電極 9 と対向電極との間には液晶物質が封入され、これにより液晶容量 C1 が形成されている。対向電極は、図に示していない共通電圧発生回路に接続されており、この共通電圧発生回路によって共通電圧 Vcom が印加されることにより、例えば固定電位に維持される。

20

【0076】

各画素 10 は、液晶容量 C1 に対して並列に接続された保持容量 C2 を備え、画素電極 9 に電圧が印加される際に、この保持容量 C2 に対しても電荷がチャージされるように構成されている。このため、ソースラインを通じてデータ電圧が印加されていない期間であっても、保持容量 C2 が保持している電位によって画素 10 の電圧値を保持することができる。

20

【0077】

液晶表示装置の制御回路 105 は、ゲートドライバ 101 及びソースドライバ 102 等を通じて、画素電極 9 と対向電極との間に印加される電圧の大きさを制御して、各画素 10 における液晶物質の透過率を制御することにより、液晶物質を透過する光の光量を調整して映像表示を行う。

30

【0078】

各画素 10 が備えるスイッチング素子 11 として、実施の形態 1 に示す薄膜トランジスタを採用することにより、低消費電力を実現することができる。実施の形態 1 に示す薄膜トランジスタを採用することにより、薄膜トランジスタ間の特性のばらつきを抑えることができるので、液晶表示パネル 100 における表示品質を良好に保つことができる。

【0079】

なお、実施の形態 2 では、表示装置の一例として液晶表示装置を示したが、有機 EL 表示装置に用いられる画素選択用のスイッチング素子、又は画素駆動用のスイッチング素子として実施の形態 1 に示す薄膜トランジスタを採用した構成としてもよい。

30

【0080】

今回開示された実施の形態は、全ての点で例示であって、制限的なものではないと考えられるべきである。本発明の範囲は、上述した意味ではなく、請求の範囲によって示され、請求の範囲と均等の意味及び範囲内での全ての変更が含まれることが意図される。

40

【0081】

以上の実施の形態に関し、更に以下の付記を開示する。

【0082】

本発明の一態様に係る薄膜トランジスタは、基板上に形成されたゲート電極と、該ゲート電極を覆うように形成されたゲート絶縁層と、該ゲート絶縁層上に形成された半導体層と、前記ゲート電極の上方に位置し、前記半導体層の一部の領域を覆うエッチストップ膜とを備え、前記半導体層は結晶性を有するシリコン層を含み、前記エッチストップ層により覆われた前記一部の領域における前記シリコン層は、前記一部の領域を挟んで両側に位

50

置する 2 つの領域における前記シリコン層よりも結晶性が低く、前記半導体層上で離隔して設けられ、少なくとも一部が前記 2 つの領域の一方の上方に位置するソース電極と、少なくとも一部が前記 2 つの領域の他方の上方に位置するドレイン電極とを備える。

【 0 0 8 3 】

本発明の一態様に係る薄膜トランジスタは、前記一部の領域における前記シリコン層は微結晶シリコン層であり、前記 2 つの領域における前記シリコン層は多結晶シリコン層である。

【 0 0 8 4 】

本発明の一態様に係る薄膜トランジスタは、前記微結晶シリコン層及び前記多結晶シリコン層と同一の層内にアモルファスシリコン層を備える。

10

【 0 0 8 5 】

本発明の一態様に係る薄膜トランジスタは、前記エッチストッパ膜のエッジの傾斜角を 60 度以上としてある。

【 0 0 8 6 】

本発明の一態様に係る表示装置は、複数の表示素子と、表示すべき表示素子を選択又は駆動する前記薄膜トランジスタとを備える。

【 0 0 8 7 】

本発明の一態様に係る薄膜トランジスタの製造方法は、基板上にゲート電極を形成し、該ゲート電極を覆うようにゲート絶縁層を形成し、該ゲート絶縁層上にアモルファスシリコン層を含む半導体層を形成し、照射すべきエネルギービームに対する前記アモルファスシリコン層の吸収率が極小値を含む所定範囲内の値となるように設定された厚さを有するエッチストッパ層を前記半導体層上に形成し、前記アモルファスシリコン層が前記エッチストッパ膜により覆われていない 2 つの領域を有するように、前記エッチストッパ膜の一部を除去し、前記エッチストッパ膜の上方から前記エネルギービームを照射して、前記エッチストッパ膜により覆われた領域におけるアモルファスシリコン層の結晶性が、前記エッチストッパ膜により覆われていない前記 2 つの領域におけるアモルファスシリコン層の結晶性よりも低くなるように、前記半導体層が備えるアモルファスシリコン層の結晶性を変化させ、少なくとも一部が前記 2 つの領域の一方の上方に位置するソース電極と、少なくとも一部が前記 2 つの領域の他方の上方に位置するドレイン電極とを前記半導体層上に離隔して形成する。

20

【 0 0 8 8 】

図 16 を参照して、本発明の一態様の薄膜トランジスタの構成をさらに説明する。

薄膜トランジスタは、基板 1 と、基板 1 に支持されたゲート電極 2 と、ゲート電極を覆うゲート絶縁層 3 と、ゲート絶縁層 3 上に設けられた、結晶質シリコン領域 R c を有する半導体層(シリコン半導体層) 4 と、半導体層 4 の一部上に配置された保護絶縁層(エッチストッパ層ともいう) 5 と、ソース電極 6 A およびドレイン電極 6 B とを備える。

30

【 0 0 8 9 】

なお、本明細書では、「結晶質シリコン領域 R c 」は、結晶質シリコン(多結晶シリコン、微結晶シリコン、単結晶シリコンを含む)を主として含む領域である。

40

【 0 0 9 0 】

結晶質シリコン領域 R c は、第 1 領域 4 s と、第 2 領域 4 d と、第 1 領域 4 s および第 2 領域 4 d の間に位置するチャネル領域 4 c とを含む。第 1 領域 4 s は、ソース電極 6 A と電気的に接続される領域(ソースコンタクト領域)である。第 2 領域 4 d は、ドレイン電極 6 B と電気的に接続される領域(ドレインコンタクト領域)である。本実施形態では、チャネル領域 4 c 、第 1 領域 4 s および第 2 領域 4 d は、ゲート絶縁層 3 を介してゲート電極 2 と重なっている。

【 0 0 9 1 】

保護絶縁層 5 は、半導体層 4 上に、チャネル領域 4 c を覆い、かつ、第 1 領域 4 s および第 2 領域 4 d を露出するように配置されている。保護絶縁層 5 は、チャネル領域 4 c の上面と接していてもよい。図示する例では、保護絶縁層 5 は島状である。なお、保護絶縁

50

層5は、半導体層4全体を覆うように形成され、かつ、半導体層4の第1領域4sを露出する開口部と、第2領域4dを露出する開口部とを有していてもよい。

【0092】

保護絶縁層5は、導電膜をパターニングしてソース電極6Aとドレイン電極6Bとを形成する工程(ソース・ドレイン分離工程)において、チャネル領域4cを保護するエッチストップ層として機能する。すなわち、保護絶縁層5は、上記導電膜よりも下層に(つまり、半導体層4を形成した後、ソースおよびドレイン電極用の導電膜を形成する前に)形成されている。このため、保護絶縁層5の一部は、半導体層4とソース電極6Aとの間(この例では、半導体層4と第1コンタクト層7Aとの間)に位置し、保護絶縁層5の他の一部は、半導体層4とドレイン電極6Bとの間(この例では、半導体層4と第2コンタクト層7Bとの間)に位置している。

10

【0093】

本実施形態では、結晶質シリコン領域Rcにおけるチャネル領域4cの結晶性は、第1領域4sおよび第2領域4dの結晶性よりも低い。このような結晶構造は、前述したように、アモルファスシリコン膜の一部上に保護絶縁層5を形成した後、保護絶縁層5の上方からレーザ光を照射する結晶化工程を行い、半導体膜のうち保護絶縁層5で覆われた部分によるレーザ光の吸収率(すなわち、保護絶縁層5を有する積層構造によるレーザ光の反射率)を制御することによって製造され得る。

【0094】

一例として、チャネル領域4cの平均結晶粒径は、第1領域4sおよび第2領域4dの平均結晶粒径よりも小さくてもよい。あるいは、ラマン分光法を用いて測定したチャネル領域4cの結晶化率が、第1領域4sおよび第2領域4dの結晶化率よりも小さくてもよい。つまり、チャネル領域4cに含まれるアモルファス層の体積率は、第1領域4sおよび第2領域4dに含まれるアモルファス層の体積率よりも大きくてもよい。

20

【0095】

チャネル領域4c、第1領域4sおよび第2領域4dは、いずれも、多結晶シリコンを含んでもよい。あるいは、これらの領域は、いずれも、微結晶シリコンを含んでもよい。または、チャネル領域4cは微結晶シリコンを含み、第1領域4sおよび第2領域4dは多結晶シリコンを含んでもよい。

30

【0096】

半導体層4は、結晶質シリコン領域Rcに加えて、非晶質シリコン領域Raをさらに含んでもよい。例えば、アモルファスシリコン膜の一部のみにレーザ光を照射して結晶化させると、レーザ光で照射された領域が結晶質シリコン領域Rcとなり、レーザ光で照射されなかつた領域が非晶質シリコン領域Raとして残る。このような結晶化方法について、例えば、国際公開第2011/055618号、国際公開第2011/132559号、国際公開第2016/157351号、国際公開第2016/170571号の開示内容の全てを本願明細書に援用する。

【0097】

薄膜トランジスタは、第1領域4sとソース電極6Aとの間に配置され、ソース電極6Aと第1領域4sとを接続する第1コンタクト層7Aと、第2領域4dとドレイン電極6Bとの間に配置され、ドレイン電極6Bと第2領域4dとを接続する第2コンタクト層7Bとをさらに備えてよい。第1コンタクト層7Aおよび第2コンタクト層7B(以下、「コンタクト層7」と総称する)は、それぞれ、n型不純物を含む。n型不純物を含むn<sup>+</sup>型シリコン層45はアモルファスシリコン層でもよいし、結晶質シリコン層でもよい。n<sup>+</sup>型シリコン層45の上面は、ソース電極6Aまたはドレイン電極6Bと直接接してもよい。第1コンタクト層7Aおよび第2コンタクト層7Bにおけるn<sup>+</sup>型シリコン層45は、離間して配置される。

40

【0098】

コンタクト層7は、n<sup>+</sup>型シリコン層45と、n<sup>+</sup>型シリコン層45の基板1側に配置された第2アモルファスシリコン層44とを含む積層構造を有してもよい。第2アモルフ

50

アスシリコン層44は真性（実質的に不純物を含まない）でもよいし、 $n^+$ 型シリコン層45よりも低い濃度で不純物を含んでもよい。第2アモルファスシリコン層44の下面是、第1領域4sまたは第2領域4dと直接接していてもよい。なお、第1コンタクト層7Aおよび第2コンタクト層7Bにおける $n^+$ 型シリコン層45は、互いに分離して配置されるが、第1コンタクト層7Aおよび第2コンタクト層7Bにおける第2アモルファスシリコン層44は、分離していなくてもよい（保護絶縁層5上で繋がっていてもよい）。

## 【0099】

コンタクト層7は、 $n^+$ 型シリコン層45の単層であってもよい。この場合、 $n^+$ 型シリコン層45の下面是、第1領域4sまたは第2領域4dと直接接していてもよい。

## 【0100】

上述したように、保護絶縁層5の側面の傾斜角（保護絶縁層5の下面と側面との間の角度）は、例えば、60°以上であってもよい。また、傾斜角は90°以下であってもよい。保護絶縁層5が島状ではなく、半導体層4全体を覆うように形成され、かつ、半導体層4の第1領域4sおよび第2領域4dをそれぞれ露出する開口部を有する場合には、保護絶縁層5の側面の傾斜角は、保護絶縁層5の下面と、開口部の内壁面との間の角度をいう。

## 【0101】

また、本実施形態の薄膜トランジスタは、例えば以下のようにして製造され得る。

まず、基板1上に、ゲート電極2と、ゲート電極2を覆うゲート絶縁層3とを形成する。次いで、ゲート絶縁層3上に、アモルファスシリコンからなる半導体膜40（アモルファスシリコン膜40）を形成する。続いて、半導体膜40上に、保護絶縁膜となる絶縁膜を形成し、絶縁膜のパターニングを行うことにより、半導体膜40のうちチャネル領域となる部分を覆う保護絶縁層5を得る（図3（b）参照）。

## 【0102】

この後、保護絶縁層5の上方から半導体膜40にレーザ光を照射することによって、基板1の法線方向から見たときにゲート電極2と重なる領域において、半導体膜40のうち保護絶縁層5で覆われた部分の結晶性が保護絶縁層5で覆われていない部分の結晶性よりも低くなるように、結晶化させる。これにより、レーザで照射された領域が結晶化され、結晶質シリコン領域Rcを有する半導体層4が得られる。

## 【0103】

続いて、結晶質シリコン領域Rcのうち保護絶縁層5で覆われていない部分の一部（ここでは第1領域4s）に電気的に接続するソース電極6Aと、結晶質シリコン領域Rcのうち保護絶縁層5で覆われていない部分の他の一部（ここでは第2領域4d）に電気的に接続するドレイン電極6Bとを形成する。このようにして、薄膜トランジスタが製造される。

## 【0104】

本実施形態によると、薄膜トランジスタの半導体層（活性層）4のうちソース電極6Aとドレイン電極6Bとの間を流れる電流の経路となる部分（第1領域4s、第2領域4dおよびチャネル領域4c）が結晶質シリコンで構成されるので、薄膜トランジスタの移動度の低下を抑制できる。また、上記電流の経路となる部分の結晶性を部分的に低く（ここではチャネル領域4cの結晶性を低く）することで、オフ電流を低減できる。従って、所望のオン特性を確保しつつ、オフ特性を高めることができる。

## 【0105】

また、上述した方法で薄膜トランジスタを製造すると、保護絶縁膜をパターニングして保護絶縁層5を形成した後で、パターニングされた保護絶縁層5の上方から半導体膜40にレーザ光を照射し、レーザアニールを行う。このため、半導体膜40のうち保護絶縁層5で覆われている部分と覆われていない部分とで、結晶性を異ならせることが可能である。つまり、保護絶縁層5を利用することで、照射条件の異なる複数回のレーザアニールを行わなくても、結晶性の異なる領域を作り分けることができる。

## 【0106】

10

20

30

40

50

基板 1 の法線方向から見たときの、ゲート電極 2、保護絶縁層 5 および結晶質シリコン領域 R c (レーザ光で照射された領域)の配置関係は、図 1、図 8 ~ 図 12 に示す例に限定されない。図 17 は薄膜トランジスタのさらに他の例を示す平面図である。例えば、図 17 (a) ~ 図 17 (f) に例示するような配置も可能である。いずれの配置例でも、保護絶縁層 5 は、ゲート電極 2 の一部のみと重なるように配置される。また、結晶質シリコン領域 R c は、ゲート電極 2 と少なくとも部分的に重なるように配置される。結晶質シリコン領域 R c は、ゲート電極 2 および保護絶縁層 5 の両方と重なる部分と、ゲート電極 2 と重なり、保護絶縁層 5 と重ならない部分とを含む。

## 【0107】

例えば、保護絶縁層 5 は、基板 1 の法線方向から見たとき、薄膜トランジスタのチャネル幅方向に結晶質シリコン領域 R c を横切って延びていてもよい。あるいは、保護絶縁層 5 は島状であり、基板 1 の法線方向から見たとき、結晶質シリコン領域 R c の内部に位置していてもよい。結晶質シリコン領域 R c は、基板 1 の法線方向から見たとき、ゲート電極 2 の内部に位置してもよい。あるいは、結晶質シリコン領域 R c の一部はゲート電極 2 と重なっていなくてもよい。例えば、アモルファスシリコンからなる半導体膜全面に亘って走査するレーザアニール方法により、半導体膜全体を結晶化させてもよい。

10

## 【符号の説明】

## 【0108】

- |              |                      |    |

|--------------|----------------------|----|

| 1            | 基板                   |    |

| 2            | ゲート電極                | 20 |

| 3            | ゲート絶縁層               |    |

| 4            | 半導体層                 |    |

| 4 c          | チャネル領域               |    |

| 4 s          | 第 1 領域               |    |

| 4 d          | 第 2 領域               |    |

| 7            | コンタクト層               |    |

| 4 0          | アモルファスシリコン膜          |    |

| 4 1          | 第 1 アモルファスシリコン領域     |    |

| 4 2 A, 4 2 B | 多結晶シリコン領域            |    |

| 4 3          | 微結晶シリコン領域            | 30 |

| 4 4          | 第 2 アモルファスシリコン層      |    |

| 4 5          | n <sup>+</sup> シリコン層 |    |

| 5            | エッチストップ膜             |    |

| 6 A          | ソース電極                |    |

| 6 B          | ドレイン電極               |    |

| 8 2          | パッシベーション膜            |    |

| 8 3          | 有機膜                  |    |

| 8 1          | コンタクトホール             |    |

| 9            | 画素電極                 |    |

| 1 0          | 画素                   | 40 |

| 1 1          | スイッチング素子             |    |

| 1 2          | 表示素子                 |    |

| 1 0 0        | 液晶表示パネル              |    |

| 1 0 1        | ゲートドライバ              |    |

| 1 0 2        | ソースドライバ              |    |

| 1 0 3        | 電源回路                 |    |

| 1 0 4        | 画像メモリ                |    |

| 1 0 5        | 制御回路                 |    |

| C 1          | 液晶容量                 |    |

| C 2          | 保持容量                 | 50 |

R c 結晶質シリコン領域

R a 非晶質シリコン領域

【図 1】

【図 2】

【図 3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【 図 1 3 】

【 図 1 4 】

【 図 1 5 】

【 図 1 6 】

【 図 17 】

## フロントページの続き

(51) Int.Cl.

F I

テーマコード(参考)

H 0 1 L 21/20

G 0 9 F 9/30 3 3 8

G 0 2 F 1/1368

(72) 発明者 野寺 伸武

大阪府堺市堺区匠町1番地 堀ディスプレイプロダクト株式会社内

(72) 発明者 松本 隆夫

大阪府堺市堺区匠町1番地 堀ディスプレイプロダクト株式会社内

F ターム(参考) 2H192 AA24 BC31 CB05 CB34 CB35 CB42 CB44 CB52 CB71 CC72

EA74 HA82

5C094 AA25 AA53 BA03 BA43 DA13 FB14 GB10 JA09 JA11

5F110 AA01 AA06 BB01 CC07 DD02 EE02 EE03 EE04 EE06 EE44

FF01 FF02 FF03 FF04 FF09 FF29 GG02 GG06 GG12 GG13

GG14 GG16 GG22 GG25 GG44 GG58 HK02 HK03 HK04 HK06

HK09 HK16 HK22 HK25 HK33 HK34 HL07 HL23 HM07 NN03

NN14 NN16 NN23 NN24 NN27 NN35 PP03 PP04 PP15 PP35

5F152 AA06 AA10 BB03 CC02 CD13 CD14 CD15 CD16 CD17 CD24

CE05 CE12 CE24 CE43 CE45 CF02 CF13 CF24 FF03 FF06

FF43 FF47 FH08