## (12)发明专利

(10)授权公告号 CN 105474178 B

(45)授权公告日 2019.11.26

(21)申请号 201480046839.7

(72)发明人 安舒尔·高霍尔

(22)申请日 2014.09.26

拉加万德拉·桑塔纳戈帕尔

普拉德普·库马尔·巴博

(65)同一申请的已公布的文献号

申请公布号 CN 105474178 A

(74)专利代理机构 北京律盟知识产权代理有限公司 11287

(43)申请公布日 2016.04.06

代理人 林斯凯

(30)优先权数据

14/038,743 2013.09.26 US

(51)Int.Cl.

G06F 11/263(2006.01)

(85)PCT国际申请进入国家阶段日

2016.02.24

(56)对比文件

US 2004/0267480 A1, 2004.12.30, 说明书

第[0009]段-第[0047]段、附图1-4.

(86)PCT国际申请的申请数据

PCT/US2014/057579 2014.09.26

US 5475624 A, 1995.12.12, 全文.

(87)PCT国际申请的公布数据

W02015/048366 EN 2015.04.02

US 7188063 B1, 2007.03.06, 全文.

(73)专利权人 德州仪器公司

审查员 周丹

地址 美国德克萨斯州

权利要求书2页 说明书8页 附图4页

(54)发明名称

基于可编程接口的验证和调试

(57)摘要

在所描述的实例中，测试连接器经布置以将受测试设计(460)通信地耦合到测试夹具。可编程逻辑接口(450)通信地耦合到所述测试连接器且经布置以接纳可下载测试台(454)。所述可下载测试台(454)经布置以将来自第一组测试向量(444)的测试向量应用到第一测试控制总线(458)。多路复用器(462)经布置以将所述第一测试控制总线(458)和第二测试控制总线(464)中的一者选择性地耦合到共享测试总线(466)，所述共享测试总线(466)耦合到所述测试连接器。所述第二测试控制总线(464)经布置以应用来自第二组测试向量的测试向量。

1. 一种测试夹具,其包括:

测试连接器,其经布置以将受测试设计通信地耦合到所述测试夹具;以及

可编程逻辑接口,其通信地耦合到所述测试连接器且经布置以接纳可下载测试台,其中所述可下载测试台经布置以将来自第一组测试向量的测试向量应用到第一测试控制总线;

多路复用器,其经布置以将所述第一测试控制总线和第二测试控制总线中的一者选择性地耦合到共享测试总线,所述共享测试总线耦合到所述受测试设计的第一组所选择引脚,其中所述第二测试控制总线经布置以应用来自第二组测试向量的测试向量。

2. 根据权利要求1所述的测试夹具,其中通过调试器供应所述第二组测试向量,所述调试器可由人操作以控制所述第一组测试向量的执行。

3. 根据权利要求2所述的测试夹具,其包括仲裁器,所述仲裁器经布置以在所述调试器与可下载测试台之间转移对所述共享测试总线的主控身份。

4. 根据权利要求2所述的测试夹具,其中所述第一组测试向量经布置以验证耦合到所述测试连接器的所述受测试设计的性能。

5. 根据权利要求1所述的测试夹具,其包括其中存储所述第一组测试向量的可寻址存储器。

6. 根据权利要求5所述的测试夹具,其中所述可编程逻辑接口包含现场可编程门阵列FPGA,其经编程以包含程序计数器,所述程序计数器经布置以产生通过其从所述可寻址存储器检索来自所述第一组测试向量的测试向量的地址。

7. 根据权利要求6所述的测试夹具,其中响应于来自所述第一组测试向量的所检索到的测试向量的值而改变所述程序计数器的值。

8. 根据权利要求7所述的测试夹具,其中将来自所述第一组测试向量的第一组所检索到的测试向量的第一部分应用到所述测试连接器的第一组所选择引脚,且其中将所述第一组测试向量的所述第一组所检索到的测试向量的第二部分应用到耦合到所述测试连接器的第二组所选择引脚的第三测试总线,其中所述测试连接器的所述第二组所选择引脚包含的所选择引脚不同于所述第一组所选择引脚中的所选择引脚。

9. 一种用于验证和调试受测试设计的方法,其包括以下步骤:

经由测试连接器将所述受测试设计与测试夹具进行通信;

从第一测试控制总线接收可下载测试台的第一组测试向量;

从第二测试控制总线接收第二组测试向量;以及

将所述第一测试控制总线和所述第二测试控制总线中的一者选择性地耦合到共享测试总线,所述共享测试总线耦合到所述受测试设计的第一组所选择引脚。

10. 根据权利要求9所述的方法,其中:

从可由人类操作的调试器供应所述第二组测试向量以控制所述第一组测试向量的执行。

11. 根据权利要求10所述的方法,其进一步包括以下步骤:

在所述调试器与所述可下载测试台之间转移对所述共享测试总线的主控身份。

12. 根据权利要求10所述的方法,其进一步包括以下步骤:

经由所述第一组测试向量验证耦合到所述测试连接器的所述受测试设计的性能。

13. 根据权利要求9所述的方法,其进一步包括以下步骤:

将所述第一组测试向量存储在可寻址存储器中。

14. 根据权利要求13所述的方法,其进一步包括以下步骤:

经由程序计数器产生通过其从所述可寻址存储器检索来自所述第一组测试向量的测试向量的地址。

15. 根据权利要求14所述的方法,其进一步包括以下步骤:

响应于来自所述第一组测试向量的所检索到的测试向量的值而改变所述程序计数器的值。

16. 根据权利要求15所述的方法,其进一步包括以下步骤:

检索所述第一组测试向量的第一组所检索到的测试向量的第一部分;

应用所述测试连接器的第一组所选择引脚;

检索所述第一组测试向量的所述第一组所检索到的测试向量的第二部分;

将所述第一组所检索到的测试向量的所述第二部分应用到耦合到所述测试连接器的第二组所选择引脚的第三测试总线,其中所述测试连接器的所述第二组所选择引脚包含的所选择引脚不同于所述第一组所选择引脚中的所选择引脚。

## 基于可编程接口的验证和调试

### 技术领域

[0001] 本发明大体上涉及自动测试设备,且特定来说,涉及基于可编程接口的验证和调试。

### 背景技术

[0002] 自动测试设备(ATE)可用于许多电子设计(且尤其是使用集成电路实施的电子设计)的验证和调试。因为集成电路的相对复杂性,调试和装置验证通常是耗时的且涉及使用ATE的测试向量的许多迭代。因为ATE的复杂性,将ATE用于调试受测试设计的成本是相当昂贵的。调试的难度因用于执行受测试设计的接口的输入/输出限制而进一步加大。

### 发明内容

[0003] 在所描述的实例中,测试连接器经布置以将受测试设计通信地耦合到测试夹具。可编程逻辑接口通信地耦合到测试连接器且经布置以接纳可下载测试台。可下载测试台经布置以将来自第一组测试向量的测试向量应用到第一测试控制总线。多路复用器经布置以将第一测试控制总线和第二测试控制总线中的一者选择性地耦合到共享测试总线,所述共享测试总线耦合到测试连接器。第二测试控制总线经布置以应用来自第二组测试向量的测试向量。

### 附图说明

[0004] 图1展示根据本发明的实例实施例的说明性电子装置。

[0005] 图2为根据本发明的实例实施例的用于使用验证设计和调试板执行调试的测试流程的流程图。

[0006] 图3为根据本发明的实例实施例的验证设计和调试板的组件的框图。

[0007] 图4为根据本发明的实例实施例的验证设计和调试板系统的组件的架构图。

[0008] 图5为根据本发明的实例实施例的用于受测试设计的验证设计和调试板总线接口的架构图。

### 具体实施方式

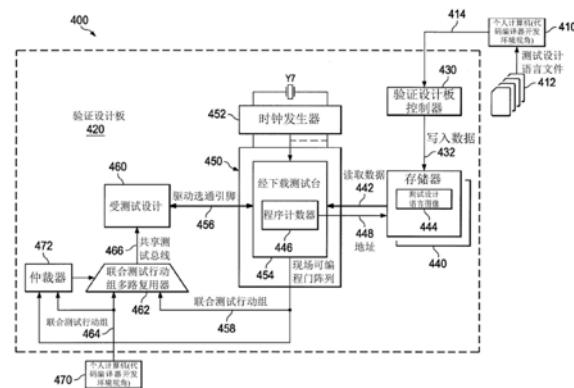

[0009] 图1展示根据本发明的优选实施例的说明性计算装置100。例如,计算装置100为或并入电子系统129,例如,膝上型计算机、移动装置、个人数字助理、个人计算机、电子控制“箱”或显示器、电子测试台或任何其它类型的电子系统。计算装置100可由线路电流、太阳能电池和/或蓄电池(或电容性)储能供电。在一个实例中,计算装置100包含基于可编程接口的验证和调试系统,其提供用于增强特别网络通信的具有成本效益的解决方案。

[0010] 在一些实施例中,计算装置100包含兆单元或芯片上系统(SoC),其包含控制逻辑(例如,CPU 112)(中央处理单元)、存储装置114(例如,随机存取存储器(RAM))和VDB调试器110(例如,至少部分以硬件体现的可执行软件)程序(其经布置以存取VDB(验证设计和调试

板) 131)。CPU 112可为(例如)CISC型(复杂指令集计算机)CPU、RISC型CPU(精简指令集计算机)、MCU型(微控制器单元)或数字信号处理器(DSP)。存储装置114(其可为例如处理器上高速缓冲存储器、处理器外高速缓冲存储器、RAM、快闪存储器或磁盘存储装置等等的存储器)存储一或多个软件应用程序130(例如,嵌入式应用程序),所述软件应用程序在由CPU 112执行时执行与计算装置100相关联的任何合适功能。

[0011] CPU 112包含存储器和逻辑,其存储从由存储装置114提供的存储器频繁存取的信息。计算装置100通常由用户使用UI(用户接口)116控制,UI 116在软件应用程序130的执行期间将输出提供到用户及从用户接收输入。使用显示器118、指示灯、扬声器、振动和其它方式提供输出。使用音频和/或视频输入(例如,使用语音或图像辨识)和机械装置(例如,键盘、开关和远程检测器)接收输入。CPU 112和VDB调试器110耦合到I/O(输入/输出)端口128,端口128提供接口,例如,JTAG(联合测试行动组)接口,其经配置以从VDB 131接收输入(和/或将输出提供到VDB 131)。I/O端口128可为例如USB(通用串行总线)、RS-232(电子工业联盟的无线电部门)和I2C(集成电路间)等等的总线。计算装置100还可耦合到外围设备和/或计算装置,包含有形、非暂时性媒体(例如,快闪存储器)和/或有线或无线媒体。这些和其它输入和/输出装置使用无线或有线连接通过外部装置选择性地耦合到计算装置100。存储装置114可(例如)由外部装置经由I/O端口128存取。

[0012] VDB调试器110为监视和控制系统,且包含支持对受测试设计(DUT)的监视、控制、测试和调试的逻辑和功能性(至少部分以硬件体现且至少部分由软件应用程序130控制,软件应用程序130至少部分存储在存储装置114中)。例如,VDB调试器110可用于下载和/或控制可编程逻辑(至少部分以硬件体现)接口,例如VDB FPGA(现场可编程门阵列)142,其包含在例如验证设计和调试版VDB 131等的测试夹具中。因此,在一个实例中,调试器110为不同于测试夹具(例如,VDB 131)的独立成套计算机系统(例如,膝上型个人计算机)。

[0013] VDB调试器110和VDB FPGA 142的组件允许经由连接器J1验证实体DUT和/或DUT的仿真器。例如,通过将仿真器的插座插入到连接器J1中,仿真器可在各种条件下(例如,DUT的组件将如何与软件应用程序130交互)在所期望的最终实施例(例如,封装的集成电路)中复制DUT的操作性能。以此方式,可在类似于前生产操作或后生产操作的单个环境中调试DUT。

[0014] 常规测试设备通常提供以相对固定方式与受测试设计交互的主要面向硬件的环境。例如,将测试向量(例如,用于设置或验证测试引脚的设置的信息,即使当测试引脚出现在单行代码中时)加载到DUT存储器中。在一个实例中,在通过测试向量将程序代码加载到装置存储器中之后,不对测试向量的执行施加任何外部控制。在测试向量的执行之后,测试结果通常限于用以提供测试是通过还是失败的指示的标记。

[0015] 相比之下,VDB调试器110提供对DUT内部电路的控制和对DUT内部电路的可见性。例如,VDB调试器110包含调试器软件,例如,代码编译器开发环境(CCS)111,其用于(例如)调试集成在DUT内的处理器(例如,微处理器、DSP和微控制器)。CCS 111提供调试命令。在一个实例中,调试命令为高级命令,其被转换成用于调试DUT的JTAG命令。当用作测试主控装置(如下文进一步论述)时,CCS 111提供(例如,DUT内部寄存器和存储器的状态的)可见性和调试功能性(例如,步长、运行、中止和断点),其优于(例如)使用JTAG(联合测试行动组)接口断言的验证低级命令。因此,DUT中的处理器可被中止且单步调试(single stepped

through) 代码,同时检查内部寄存器的状态,作为对确定在使用验证低级命令时发生的失败的原因和位置的辅助。

[0016] 因此,VDB 131可用于初始装置测试、用于装置置信度建立(例如,通过在设计被还原到硅之后执行设计验证和应用程序测试来建立)、用作客户演示板、用于现场故障测试以及用作其它类似用途。此外,VDB FPGA 142可经重新编程以适应(和/或提供)经改进或新的受测试设计的新接口要求,这促进了测试设备和夹具的可重用性并缩短了测试设备和夹具的设计时间。

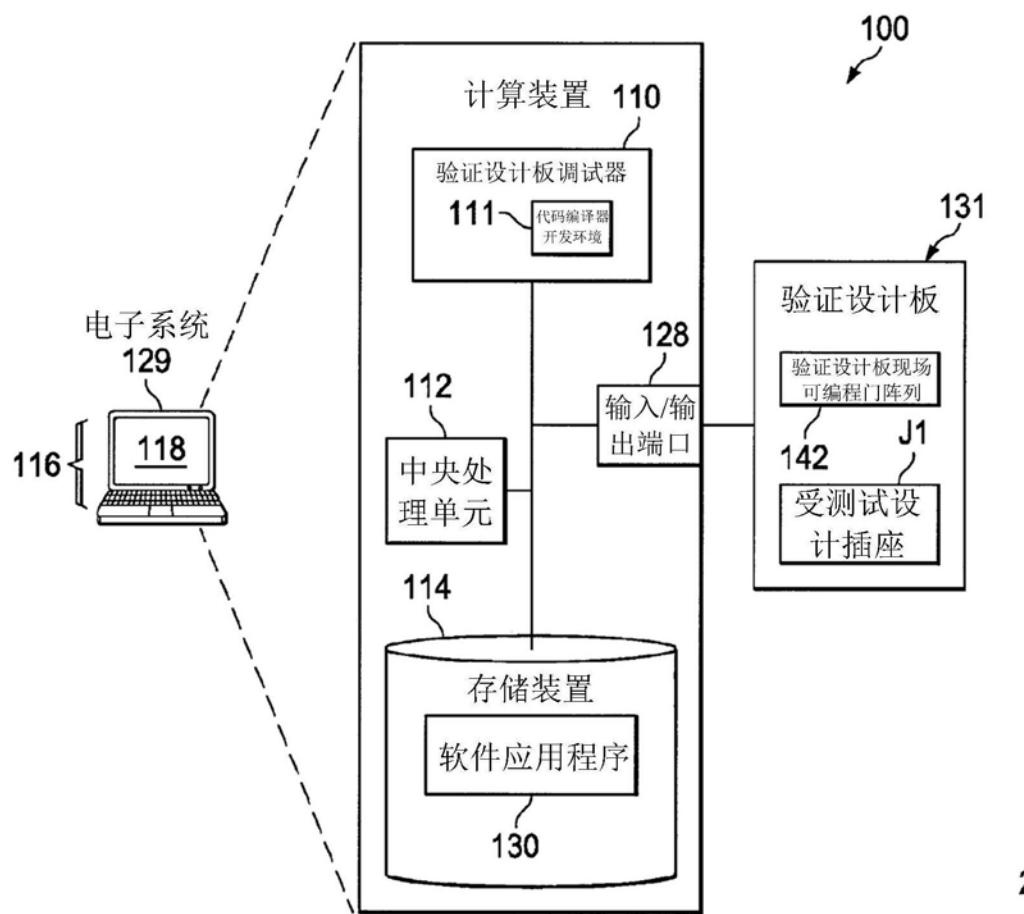

[0017] 图2为根据本发明的实例实施例的用于使用验证设计和调试板执行调试的测试流程的流程图。在大体上描述的情况下,测试流程200包含用于经由可编程接口(例如,VDB FPGA 142)将测试向量加载到受测试设计上的实例过程。虽然测试流程描述为与以硅(“还原到硅”)体现为单片集成电路的DUT相关,但本发明可适用于可耦合到VDB FPGA142(例如,经由连接器J1)的DUT的仿真器。

[0018] 更具体地,测试流程在节点202处开始且继续进行到操作210,在操作210处,初始化验证设计和调试板131以用于测试。例如,通过使用网络列表对VDB FPGA 142进行编程以将测试向量(例如,从VDB调试器110接收的测试向量)耦合到DUT的特定输入来初始化验证设计和调试板。根据封装中的引脚(例如,集成电路的封装中的引脚)和/或连接器(例如,连接器J1)将特定输入指派给特定引脚(例如,有序“引脚输出”。

[0019] 在对VDB FPGA 142进行编程之后,将VDB 131上的信号置于正确操作状态中。例如,可取消断言复位信号,可将所选择的操作频率的时钟耦合到DUT的相应输入,且可探知DUT中的电子引信(electronic fuse)的状态。在初始化之后,测试流程在操作220中继续。

[0020] 在操作220中,起始可测性设计(DFT)模式。与常规技术(其中,例如,起始基于JTAG的测试且暂停对过程的控制和监督直到测试完成为止)相比,验证设计和调试板经布置以进入DFT模式,同时允许监督过程(例如,由CCS 111控制和观察的监督过程)监视并改变个别寄存器的值和DUT的存储器位置,运行特定范围的测试向量(例如,测试向量的单步执行和/或所选择块)以及中止测试执行(例如,在预定位置处)。在进入可测性设计模式之后,测试流程200在操作230中继续。

[0021] 在操作230中,将用于测试DUT的程序代码加载到验证设计和调试板131中。更具体地,加载用于测试DUT的特定部分的特定程序代码,且可在加载特定于待测试的DUT的任何所选择部分的不同程序代码时测试DUT的各个部分。因此,例如,可将用于配置DUT的测试场景的程序代码(以及其他此类程序代码)加载到验证设计和测试板131上,使得程序代码部分驻留在验证设计和调试板131上。可将程序代码加载到如以下关于图3和下文描述的存储器中的一者中。

[0022] 可通过测试流程200中的监督过程中断测试流程200中的操作中的每一者,使得可中断不同操作(例如,操作230或操作240)且可通过监督过程检查各个组件的状态。因此,例如,可在中止或以其它方式终止正执行的测试之前检查正执行的测试的结果。测试流程200在操作240中继续。

[0023] 在操作240中,执行程序代码。例如,从监督器过程(例如,CCS 111)接收命令(例如,调试命令),其引导验证设计和调试板131(响应于所接收到的命令)将所选择的测试向量应用到DUT的相应引脚。在测试向量是基于TDL(测试设计语言)的实例中,将授予监督器

过程对共享的JTAG总线的主控，并根据所接收到的命令将来自监督器过程的测试序列应用到DUT的JTAG特定的引脚。

[0024] 例如，可以TDL书写测试，其中测试可表示为具有行和列的矩阵。TDL的每一行与特定时段(例如，时间片或测试时钟)相关联，且其中在特定测试时间处将对每一行的刺激按顺序应用到DUT的设计引脚(并从所述设计引脚测量响应)。在一个实例中，每一列与设计引脚相关联，且TDL的每一行具有作为刺激和/或值(其与在设计引脚上接收的响应进行比较)应用的值。因此，可在与TDL的特定行相关联的测试流程中的某一点处应用和/或测量值。

[0025] 在各个实施例中，测试流程200的操作不一定按顺序执行。例如，DUT的第一部分可通过执行用于测试所述第一部分的代码来进行测试，而DUT的第二部分可通过执行用于测试所述第二部分的代码来进行测试，其中在与执行用于测试第二部分的代码的第二时段至少部分重叠的第一时段期间执行用于测试第一部分的代码。因此，可通过改变起始用于测试第一和第二部分的代码的相对时间(例如，响应于从CCS 111接收的单独命令)来测试对异步事件的响应。

[0026] 在操作250中，存取或(“转储(dump)”)测试结果以供分析。可通过监视I/O迹线、比较测试标记、读取DUT上的JTAG寄存器、读取存储器和/或寄存器内容、读取存储器中存储的内建测试(BIT)装置的结果以及通过其它类似操作来存取测试结果。

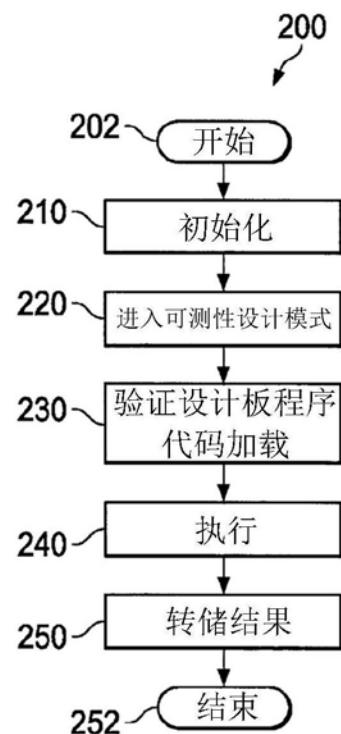

[0027] 图3为根据本发明的实例实施例的验证设计和调试板的组件的框图。验证设计和调试板300为包含用于与VDB控制器(例如，VDB调试器110)通信的一或多个接口的验证设计和调试板，例如VDB 131。例如，VDB调试器110经布置以经由专用接口(I/F)(例如，VDB I/F 302)或经由基于标准的接口(例如，JTAG接口304)与VDB 300通信。

[0028] 验证设计和调试板300包含用于给VDB 300和经由连接器J1耦合到VDB 300的DUT供电的一或多个电力供应器。例如，VDB 300包含电力供应器310，例如，可编程电力供应器PPS1到PPS10312和固定电力供应器FPS1到FPS7314。可编程电力供应器PPS1到PPS10可通过VDB调试器110编程以提供用于对VDB FPGA 336进行编程并给DUT的所选择部分供电的电压。固定电力供应器FPS1到FPS7经布置以分别提供适合于半导体设计的电压，例如0.9V、1V、1.2V、1.8V、2.5V、3.3V和5V。可使用测量单元316测量电力供应器输出(以及来自DUT的模拟信号输出)。测量单元316包含电子开关矩阵S1，其经布置以(例如，响应于来自VDB调试器111的命令)将来自(固定或可编程)电力供应器或DUT引脚(例如，经由连接器J1)的信号选择性地耦合到模/数转换器(ADC1)的输入。

[0029] 验证设计和调试板300还包含用于给VDB 300和经由连接器J1耦合到VDB 300的DUT供电的一或多个时钟发生器320。例如，VDB 300包含时钟发生器320，例如，可编程时钟发生器CLK1到CLK15322和固定时钟发生器Y1到Y7324。可编程时钟发生器CLK1到CLK15可通过VDB调试器110编程以提供用于为DUT的所选择部分计时的所选择频率(和/或相位)。

[0030] 验证设计和调试板300还包含一或多个子卡(DC)，例如，DUT DC 330、存储器(MEM)DC 346、外围(PERIPH)DC 360和追溯DC 370。VDB 300经布置以使用连接器接纳子卡，所述连接器中的每一者经布置以将电力和信号提供到子卡且从子卡接收信号。每一子卡的功能性可直接在VDB 300上部分地实施或完全实施。然而，子卡的使用促进了VDB300能力的升级，这是因为，例如，由于用于被替换的子卡的新一代组件(例如，存储器)变得可用，因此可替换整个子卡。

[0031] 受测试设计子卡(DUT DC)330包含用于托管DUT(和/或托管DUT的仿真器插座)的功能性。例如,DUT DC 330包含DUT连接器J1,其经布置以接纳含有DUT或仿真插座(和/或插头)的集成电路。连接器J1还经布置以将来自DUT的信号耦合(例如,电耦合)到DUT DC 330的电路。因此,VDB调试器110经布置以经由VDB 131和DUT DC 330与DUT通信。DUT DC 330还包含直接通信接口,例如JTAG接口334、USB版本2.0接口338和以太网(物理层)接口340。直接通信接口允许与各种外部外围装置的直接通信以用于测试和评估DUT。

[0032] DUT DC还包含VDB FPGA 336。VDB调试器110经布置以执行合成的“硬件测试台”,所述硬件测试台经布置以将所选择的测试向量应用于测试DUT。合成的硬件测试台程序端口连接到VDB FPGA 336(例如,用于对VDB FPGA 336进行编程)。根据DUT的“引脚输出”(包含输入/输出信号的功能性和排序)对VDB FPGA 336进行编程。因此,VDB FPGA336经布置以在测试DUT(例如,制成的单片半导体、仿真设计的仿真装置和具有适合于耦合到连接器J1的接口的电子系统)时将所选择的测试向量(例如,按顺序)应用到DUT的对应引脚(“设计引脚”)上。

[0033] 一旦经由VDB FPGA 336将所选择的测试向量加载到DUT存储器(例如,使用驱动/选通引脚总线456和/或JTAG总线458),就将执行所选择测试向量的控制引导到监督过程(例如,耦合到VDB 300的VDB调试器110)。举例来说,VDB调试器110具有受测试装置中的各种寄存器或存储器内容的完整处理器视角。VDB调试器110能够中止执行、单步调试程序代码和添加断点,这有助于缩短和加快调试循环。因此,将可合成硬件测试台下载到VDB FPGA336相对于常规ATE解决方案扩展了可见性和可控性。

[0034] 验证设计和调试板300提供由DUT DC 330的组件用于测试DUT的存储器。例如,DUT DC 330包含存储器332,存储器332紧密耦合到DUT连接器J1且可相对于从DUT读取或写入到DUT快速存取。辅助存储器(例如,32位宽静态RAM(SRAM 342)和双倍数据速率RAM版本2(DDR2)344)提供使用宽数据总线选择性地耦合到DUT的大存储器库。辅助存储器可用于存储、供应和捕获测试刺激和/或测试结果,例如,视频流或音频流。提供一或多个时钟发生器Y7用于产生时钟信号以控制DUT DC 330的组件的操作,例如提供用于测试DUT的所选择部分的所选择频率(和/或相位)。

[0035] 验证设计和调试板300还包含用于将额外存储器提供和/或耦合到VDB 300的一或多个扩展存储器卡(MEM DC)360。例如,VDB 300包含异步存储器348和同步存储器352。异步存储器包含异步存储器组件350,其可包含例如快闪存储器和/或静态RAM(SRAM)的存储器。同步存储器包含同步存储器组件352,其可包含例如SRAM 354、DDR356和移动DDR(MDDR)358的存储器。双列直插封装(DIP)插座J2可用于扩展或替换现有存储器组件,例如异步存储器组件350和同步存储器组件352。

[0036] 验证设计和调试板300还包含用于将额外功能性提供和/或耦合到VDB 300的一或多个外围子卡(PERIPH DC)360。例如,VDB 300包含测试接口(例如,JTAG接口(JTAG)362),其提供用于耦合来自具有外部JTAG能力的装置的测试向量的JTAG接口。下载到VDB FPGA 336中的硬件测试台可经布置以在由具有外部JTAG能力的装置起始的测试流程中执行JTAG相关编程。VDB调试器110(例如,在PC 410上托管的VDB调试器110)经布置以控制由具有外部JTAG能力的装置起始的测试流程编程。外围子卡(PERIPH DC)360使用例如J3到J9的连接器提供用于内部电路仿真外部外围设备(例如,Quickturn和Palladium测试设备)的其它测

试接口。I2C(集成电路间)接口366可用于将集成电路耦合(例如,表面安装)到VDB FPGA 336、连接器J1、VDB调试器110和其它测试器。

[0037] 验证设计和调试板300还包含用于追溯功能性和/或接口连接到VDB 300的一或多个追溯子卡(追溯DC)370。例如,追溯DC 370包含追溯存储器372,其经布置以捕获用于记录在触发器和/或捕获事件发生之前存在的环境的信息。追溯存储器可布置为循环队列且连续记录相对大量的信息,其中覆写较旧信息使得循环队列的大小确定捕获多少追溯信息。当事件发生时(例如,响应于JTAG控制器(例如,VDB调试器110)接收命令),停止数据的记录(除事件后记录的所选择部分之外)使得围绕事件的数据不被覆写。围绕事件的所捕获数据可用于调试围绕事件的环境(例如,装置状态)。

[0038] FPGA 384可经编程以实施对追溯功能性的控制。在一个实例中,振荡器Y7经布置以提供用于驱动追溯控制电路的时钟,且提供用于写入到追溯存储器372和从追溯存储器372读取的信号。到DUT的接口(到DUT的IF)370经布置以响应于FPGA 384操作,且(例如)将来自DUT的信息耦合到追溯存储器372。

[0039] 追溯DC 370包含用于提供追溯功能性的各种接口。DUT DC 370包含通信接口(例如,串行通信接口),例如JTAG接口374、USB版本2.0接口382和以太网(物理层)接口380。DUT DC 370包含通信接口(例如,串行和/或并行通信接口),例如惠普(Hewlett-Packard)接口(HPI)、个人计算机接口(PCI)和VLYNQ(Texas Instruments®专用接口)接口378。直接通信接口将内部总线扩展到(例如)用于测试和评估DUT的外部外围装置的总线。视频接口386和“其它”接口388可用于接收刺激和/测试结果,例如视频或音频流。

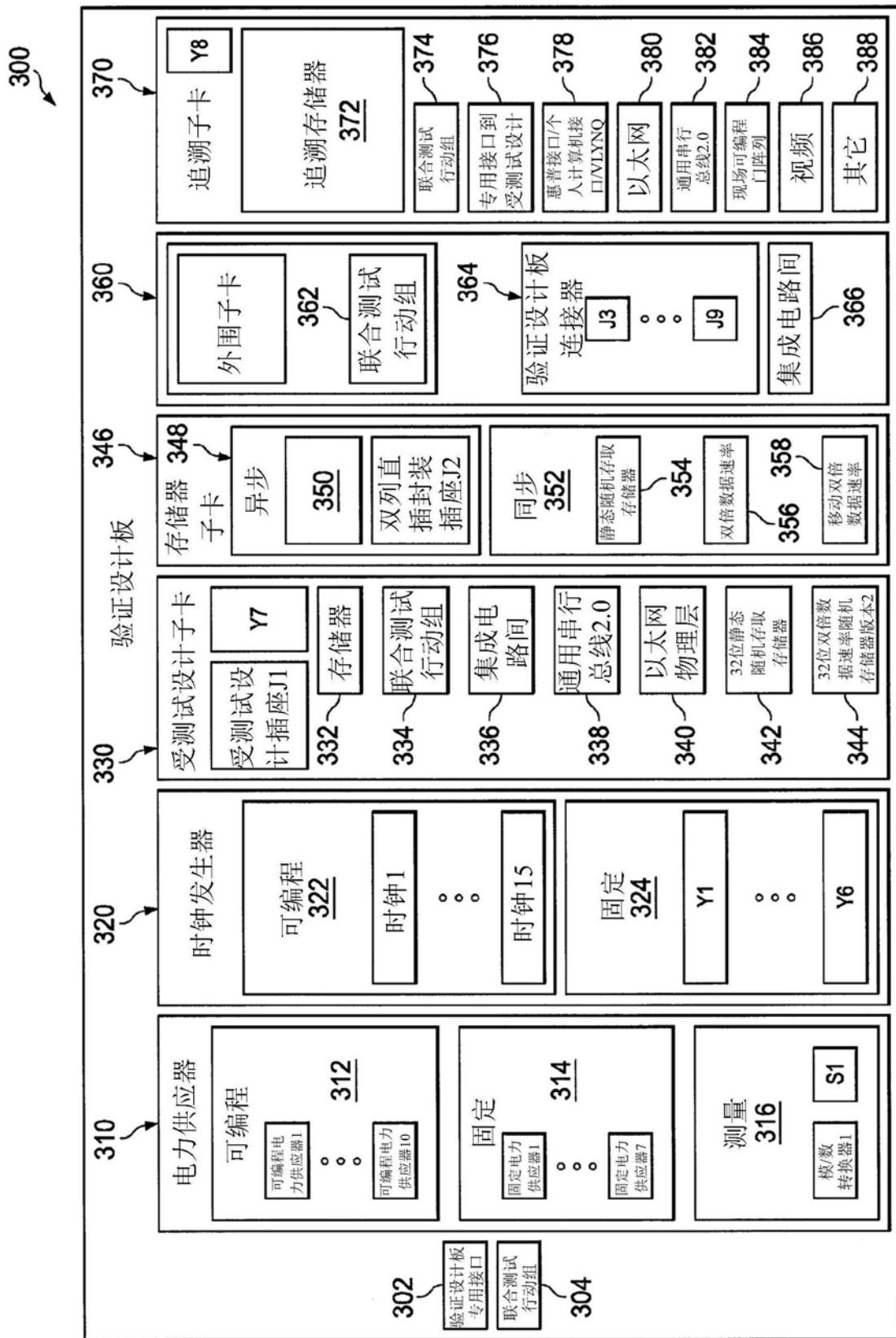

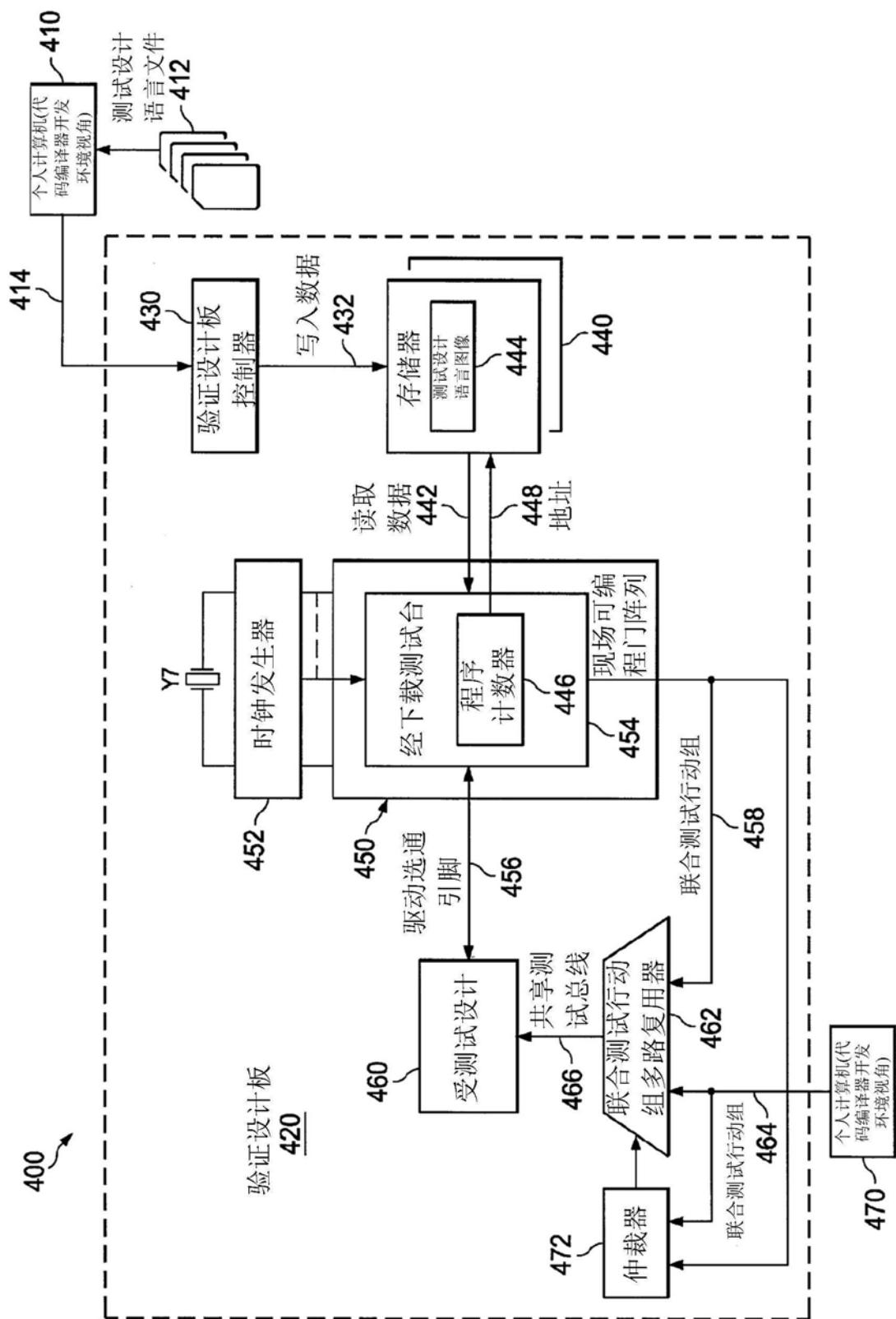

[0040] 图4为根据本发明的实例实施例的验证设计和调试板系统的组件的架构图。验证设计和调试板系统400包含经布置以用于测试DUT 460的个人计算机(PC)410和TDL文件412。PC 410为计算装置(例如,个人计算装置),例如,经布置以创建用于将TDL文件412的所选择内容应用到DUT 460的设计引脚的可下载测试台的计算装置100。PC 410经布置以使用接口(例如,JTAG总线414)将测试台和相关联测试向量应用到验证设计和调试板420(其为例如VDB 300的验证设计和调试板)。

[0041] VDB控制器430经布置以(经由JTAG总线414)接收可下载测试台的图像和相关联测试向量。所接收到的可下载测试台的图像和存储在所选择的TDL文件中的相关联测试向量(经由写入总线432)存储为存储器440的内容(例如,TDL图像444)。存储器440的内容经布置以由FPGA 450经由读取总线442读取。FPGA 450(例如,在VDB控制器430的控制下)经布置以读取所接收到的可下载测试台的图像并将所述图像例示为经下载测试台454。当可下载测试台经例示(例如,经编程)为经下载测试台454时,振荡器Y7和时钟发生器452经布置以提供用于驱动经下载测试台454并为其计时的一或多个时钟。

[0042] 在FPGA 450中例示的经下载测试台454经布置以经由驱动/选通引脚总线456和JTAG总线458与受测试设计(DUT)460通信。在一个实例中,驱动/选通引脚总线456不与另一总线主控装置共享。JTAG总线458耦合到JTAG多路复用器(MUX)462的第一输入。当经下载测试台454处在测试主控模式(例如,相对于DUT 460)中时,JTAG多路复用器462经布置以经由共享测试总线466将JTAG总线458耦合到DUT 460的JTAG总线设计引脚。共享测试总线466为测试控制器总线(与驱动/选通引脚总线456相比)且可用于(例如)从DUT上的JTAG扫描链起始测试或读取。在一个实例中,共享测试总线所耦合到的DUT的一组引脚不同于驱动/选通

引脚总线456所耦合到的DUT的一组引脚。

[0043] 经下载测试台454经布置以从TDL图像444存取测试向量,且(例如)在进入可测性设计模式之后在测试期间按顺序将TDL图像的时间片应用到设计引脚。例如,测试向量的每一片(例如,每一“行”或“排”)可由递增程序计数器446根据从时钟发生器452接收到的时钟按顺序读取。程序计数器446的值可用于形成在地址总线448上断言以用于寻址TDL图像444的存储器内容的目的地址。

[0044] PC 470经布置以经由JTAG总线464与受测试设计(DUT) 460通信。JTAG总线458耦合到JTAG多路复用器(MUX) 462的第二输入。当PC 470处在测试主控模式(例如,相对于DUT 460)中时,JTAG多路复用器462经布置以经由共享测试总线466将JTAG总线464耦合到DUT 460的JTAG总线设计引脚。例如,在PC 470上执行的CCS 111对DUT 460(和共享测试总线466)的“主控身份”允许CCS 111观察和控制经布置以执行来自TDL图像444的TDL的测试流程。

[0045] 与常规解决方案相比,例如在以交替方式使用两个测试主控装置的情况下允许对TDL图像444的代码的执行流程的完全控制。在各种实施例中,测试主控装置可为相同或不同装置(或源于相同或不同装置),使得例如PC 410和PC 470可为相同或不同物理(或虚拟)装置。在实例实施例中,通过建立PC 470的CCS 111与VDB上的设计的连接性来实现对TDL图像444的代码的执行流程的控制,从而用于提供对加载到存储器440中的TDL图像444的执行流程的控制。

[0046] 可通过将测试主控控制从经下载测试台454转移到PC 470的CCS 111来实现对TDL图像444的代码的执行流程的完全控制。例如,经下载测试台454经布置以充当对于在DUT 460中加载并执行TDL图像444的代码的测试主控装置(例如,通过经由共享测试总线466控制DUT 460的JTAG引脚)。在执行已到达TDL图像444中的某个点(例如,由PC 410的CCS 111预先设置的预定断点)之后,经下载测试台454经布置以将对测试的控制转移到PC 470的CCS 111,使得PC 470的CCS 111变成新的测试主控装置。仲裁器(例如,体现为硅衬底中的逻辑门的机构)470经实施以促进对测试总线的主控身份在经下载测试台454与PC 470的CCS 111之间的转移。当CCS 111不再需要对测试总线的主控身份时,经下载测试台可通过充当测试总线的当前主控装置来恢复测试(包含重启或执行新下载的测试序列)。

[0047] 仲裁器472可选择经下载测试台454和PC 470的CCS 111中的哪一个将为共享总线466的主控装置。仲裁器472可响应于复位状态、从控制器(例如,VDB控制器430或VDB调试器110)接收的命令或评估JTAG总线464的内容、DUT双态输出和/或JTAG总线458的内容来选择哪一个将为共享总线466的主控装置。

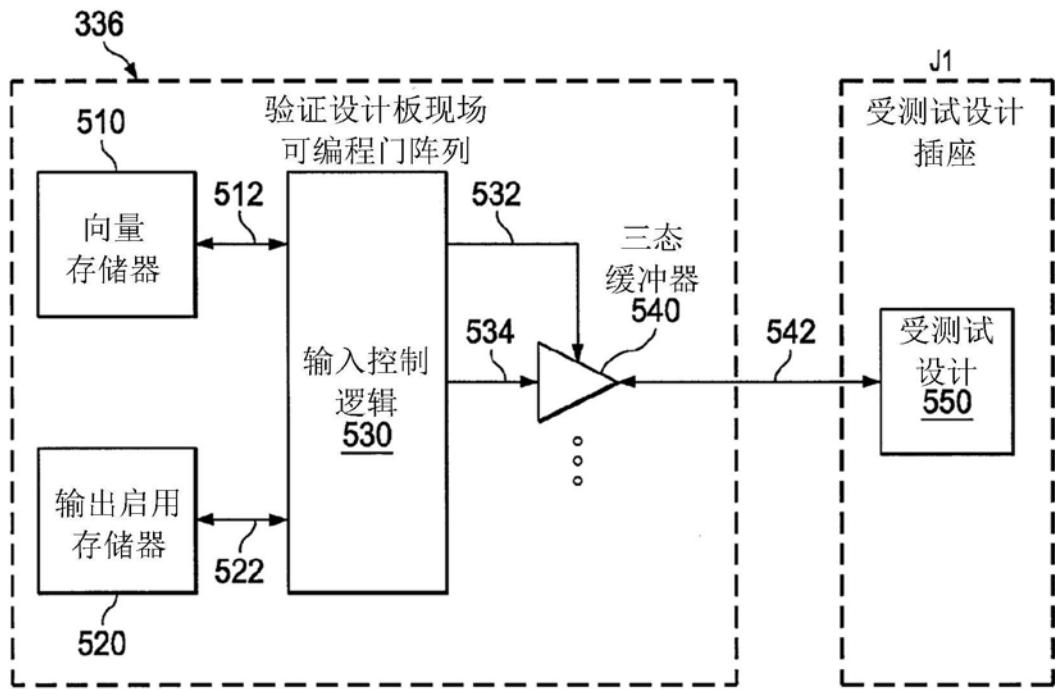

[0048] 图5为根据本发明的实例实施例的用于受测试设计的验证设计和调试板总线接口的架构图。验证设计和调试板FPGA 336(和/或FPGA 450)包含向量存储器510和输出启用存储器520,其分别用于经由总线512和522驱动输入控制逻辑(例如,至少部分以硬件体现)530。虽然向量存储器510和OEN存储器520展示为驻留在VDB FPGA 336上,但向量存储器510和OEN存储器520的所有或一些部分可驻留在VDB FPGA 336之外(例如,同时仍驻留在VDB 300上)。

[0049] 向量存储器510经布置以存储将被驱动到DUT 550设计引脚中的每一者上的值中的每一者。向量存储器510还经布置以存储用于控制各种TDL构造(例如,SETR(例如,以期望

速率设置引脚值)、RUNP(例如,通过重复先前设置的值运行“封装”)和END(例如,中止执行))的执行的信息。如上文提及,程序计数器446可用于产生用于存取测试向量的地址。在实施例中,程序计数器包含状态机,其经布置以从相关联存储器取出并压缩测试向量,并且以期望速率将测试向量应用到设计引脚上(例如,SETR构造)。当状态机遭遇RUNP时,将先前压缩的值驱动到设计引脚上直到RUNP数截止为止。当遭遇END构造时,驱动先前压缩的值,直到(例如)在FPGA 336或450外部发生复位(或改变)状态机的事件为止。

[0050] OEN存储器520经布置以针对测试向量(或测试向量组)存储DUT设计引脚(或引脚组)的状态的方向信息(例如,输出和/或输入)。举例来说,可通过针对每一向量使用一个字(例如,32位)的方向信息来关联方向信息或通过针对基于TDL的测试向量的每一排(例如,每一行)使用一个字来优化存储器存储。

[0051] 在操作中,经下载测试台454经布置以(例如)响应于TDL图像444产生方向信息。当执行向量存储器510中的测试向量时,还将用于选择TDL的特定排的地址用于检索TDL的所选择排的相关联方向信息。将所检索到的TDL的所选择排的相关联方向信息用于控制一或多个三态缓冲器540(出于清楚起见未展示所有缓冲器)的状态。例如,经由总线532应用方向信息,所述方向信息确定总线534的所选择内容(例如,位或字)是否由所选择的经启用三态缓冲器540输出到总线542(其经由连接器J1耦合到DUT 550)上。

[0052] 修改在所描述的实施例中是可行的,并且其它实施例在权利要求书的范围内是可行的。

图 1

图 2

图3

图4

图5