## (12)发明专利申请

(10)申请公布号 CN 110616416 A

(43)申请公布日 2019.12.27

(21)申请号 201910525969.3

(22)申请日 2019.06.18

(30)优先权数据

16/010,800 2018.06.18 US

(71)申请人 东京毅力科创株式会社

地址 日本东京

(72)发明人 田端雅弘

(74)专利代理机构 北京品源专利代理有限公司

11332

代理人 吕琳 朴秀玉

(51)Int.Cl.

C23C 16/455(2006.01)

C23C 16/513(2006.01)

权利要求书2页 说明书9页 附图5页

(54)发明名称

基板处理方法及基板处理装置

(57)摘要

本发明涉及基板处理方法及基板处理装置，能够精密控制半导体基板的图案。本发明的基板处理装置包括：处理装置，其具有腔室；以及控制器，其具有存储器、以及与该存储器连接的处理器。其中，存储器存储用于对处理器进行控制而对处理装置的处理进行控制的、可通过计算机执行的命令。处理装置的处理包括第1处理，通过化学气相沉积(CVD)，在腔室内的基板的第1区域内形成第1膜。此外，处理装置的处理包括第2处理，通过原子层沉积(ALD)，在腔室内的基板的第2区域内形成第2膜。此外，处理装置不将基板从腔室移动至其外而实施第1处理及第2处理。

1. 一种基板处理装置,包括:

处理装置,其具有腔室;以及

控制器,其具有存储器、以及与该存储器连接的处理器,

其特征在于:

所述存储器存储用于对所述处理器进行控制而对基于所述处理装置实施的处理进行控制的、可通过计算机执行的命令,该处理包括:

第1处理,通过化学气相沉积,在所述腔室内的基板的第1区域内形成第1膜;以及

第2处理,通过原子层沉积,在所述腔室内的所述基板的第2区域内形成第2膜,

所述基板处理装置不将所述基板从所述腔室移动至其外部而实施所述第1处理及所述第2处理。

2. 根据权利要求1所述的基板处理装置,其特征在于,还包括:

天线,其由所述控制器控制;以及

下部电极,其与所述天线相对配置,构成为将所述基板保持于其上,该下部电极由所述控制器控制,

所述处理还包括:

在所述化学气相沉积中,向所述下部电极施加电压;以及

在所述原子层沉积的改性步骤中,向所述天线施加电压。

3. 根据权利要求1所述的基板处理装置,其特征在于,还包括:

天线,其配置于所述腔室之上,由所述控制器控制;以及

下部电极,其与所述天线相对配置,构成为将所述基板保持于其上,该下部电极由所述控制器控制,

所述处理还包括:

在所述化学气相沉积中,不向所述天线施加电压,向所述下部电极施加电压;以及

在所述原子层沉积的改性步骤中,不向所述下部电极施加电压,向所述天线施加电压。

4. 根据权利要求1~3中的任一项所述的基板处理装置,其特征在于:

所述第1处理中,在所述基板的亲水性表面的第1区域上形成所述第1膜作为疏水性表面;

所述第2处理中,在所述基板的所述亲水性表面的所述第2区域上,通过吸附与羟基发生反应的前驱体来形成所述第2膜。

5. 根据权利要求1~4中的任一项所述的基板处理装置,其特征在于:

所述第2处理中,从所述基板去除所述第1膜中的至少一部分。

6. 根据权利要求1~5中的任一项所述的基板处理装置,其特征在于:

所述第1处理中,通过氟碳等离子体沉积所述第1膜。

7. 根据权利要求2所述的基板处理装置,其特征在于:

所述第1处理中,通过对向所述下部电极施加的电压进行控制,来实施各向异性化学气相沉积及各向同性化学气相沉积中的任一种。

8. 根据权利要求1~7中的任一项所述的基板处理装置,其特征在于:

所述第1处理中,在所述基板的凹凸的顶部及底部形成所述第1膜;所述第2处理中,在所述基板的凹凸的侧壁形成所述第2膜。

9. 根据权利要求1~8中的任一项所述的基板处理装置,其特征在于:

所述基板含有SiO<sub>2</sub>、SiN、Si及Ge中的至少一种,

所述第2处理中,形成含硅的膜作为所述第2膜。

10. 根据权利要求1~9中的任一项所述的基板处理装置,其特征在于:

按照所述第1处理及所述第2处理的顺序来重复实施。

11. 根据权利要求1~10中的任一项所述的基板处理装置,其特征在于:

使用电感耦合等离子体或者电容耦合等离子体来实施所述第1处理及所述第2处理。

12. 一种基板处理装置,包括:

处理装置,其具有腔室;以及

控制器,其具有存储器、以及与该存储器连接的处理器,

其特征在于:

所述存储器存储用于对所述处理器进行控制而对处理进行控制的、可通过计算机执行的命令,该处理包括:

第1处理,通过化学气相沉积,在所述腔室内的基板的第1区域内形成第1膜;

第2处理,通过原子层沉积,在所述腔室内的所述基板的第2区域内形成第2膜;以及

第3处理,对所述基板进行蚀刻,

所述基板处理装置不将所述基板移动至所述腔室的外部而实施所述第1处理、所述第2处理及所述第3处理。

13. 根据权利要求12所述的基板处理装置,其特征在于:

所述第3处理包括原子层蚀刻,

所述第3处理还包括:

通过N等离子体及H等离子体中的一种对所述基板的表面进行改性;

对所述腔室进行吹扫;以及

通过卤素气体将被所述N等离子体及H等离子体中的一种改性后的所述表面去除。

14. 一种基板处理方法,其特征在于,包括:

第1处理,通过化学气相沉积,在处理装置的腔室内的基板的第1区域内形成第1膜;以及

第2处理,通过原子层沉积,在所述腔室内的所述基板的第2区域内形成第2膜,其中,

不将所述基板移动至所述腔室的外部而实施所述第1处理及所述第2处理。

15. 根据权利要求14所述的基板处理方法,其特征在于,还包括:

第3处理,对所述基板进行蚀刻,其中,

不将所述基板移动至所述腔室的外部而实施所述第1处理、所述第2处理及所述第3处理。

16. 根据权利要求15所述的基板处理方法,其特征在于:

所述第3处理包括原子层蚀刻,

所述第3处理还包括:

通过N等离子体及H等离子体中的一种对所述基板的表面进行改性;

对所述腔室进行吹扫;以及

通过卤素气体将被所述N等离子体及H等离子体中的一种改性后的所述表面去除。

## 基板处理方法及基板处理装置

### 技术领域

[0001] 本发明涉及基板处理方法及基板处理装置。

### 背景技术

[0002] 目前已知有各种成膜方法。例如，化学气相沉积 (CVD, chemical vapor deposition) 是利用气体成分的反应或分解来在基板表面形成固体膜。此外，原子层沉积 (ALD, Atomic layer deposition) 可以说是CVD的一种，但其本质上具有形成共形 (Conformal) 膜的特征。

[0003] 为了提高半导体装置的集成度、对其进行微型化，目前已开发出多种方法，但随着对进一步的高集成度及微型化的要求，需要更加精密地对图案进行控制。

[0004] 专利文献1：美国专利第9716005号说明书

[0005] 专利文献2：美国专利申请公开第2017/117134号说明书

### 发明内容

[0006] 本发明的目的在于，提供一种能够精密控制半导体基板的图案的技术。

[0007] 基于本发明的一种实施方式的基板处理装置包括处理装置及控制器。处理装置具有腔室。控制器具有存储器、以及与该存储器连接的处理器。存储器存储用于对处理器进行控制而对基于处理装置的处理进行控制的、可通过计算机执行的命令。基于处理装置进行的处理包括第1处理，通过化学气相沉积 (CVD) , 在上述腔室内的基板的第1区域内形成第1膜。此外，基于处理装置进行的处理包括第2处理，通过原子层沉积 (ALD) , 在腔室内的基板的第2区域内形成第2膜。此外，处理装置不将基板从腔室移动至其外部而实施第1处理及第2处理。

[0008] 根据本发明，能够精密控制半导体基板的图案。

### 附图说明

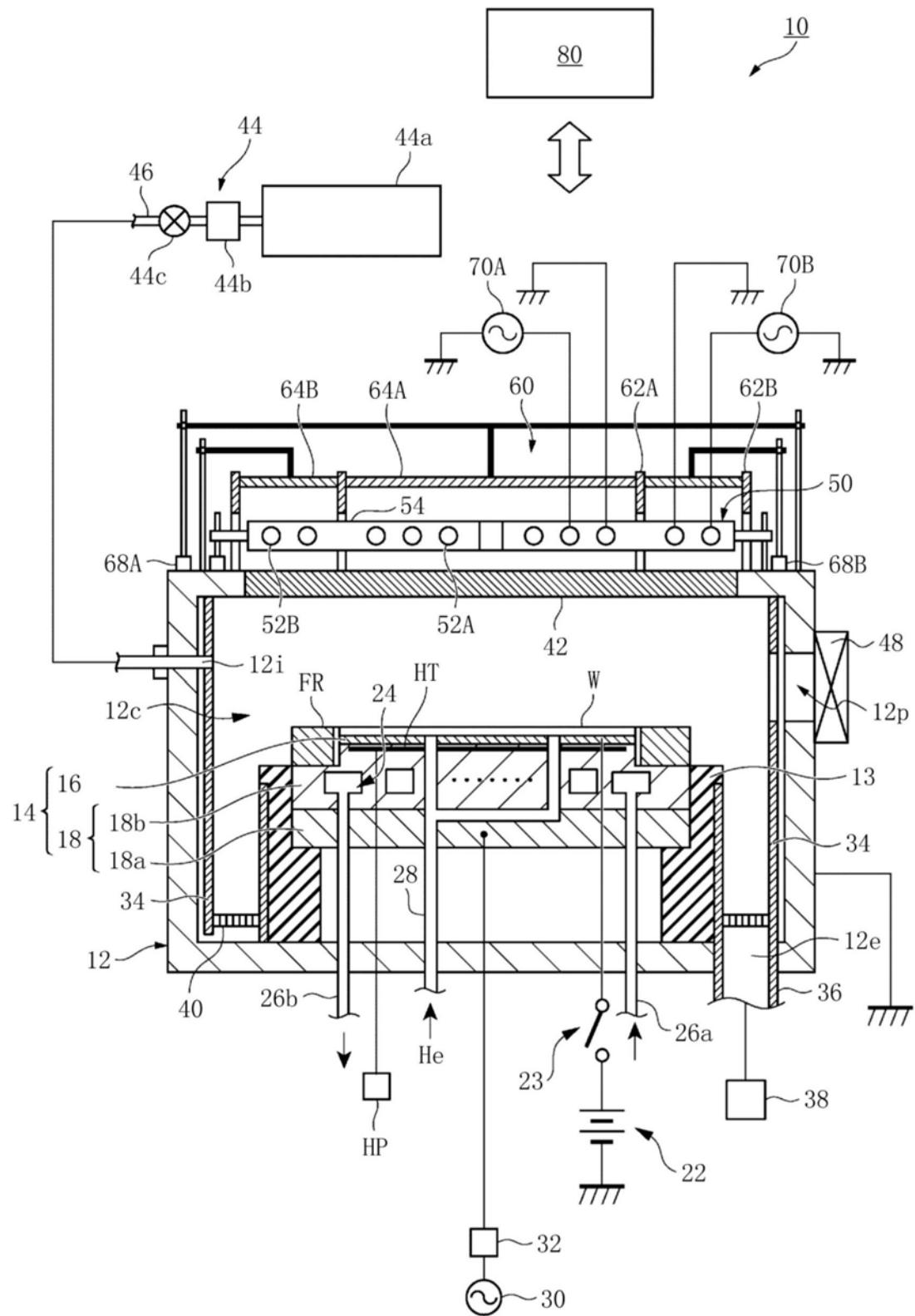

[0009] 图1为本发明的一个实施方式涉及的处理装置的概略截面图。

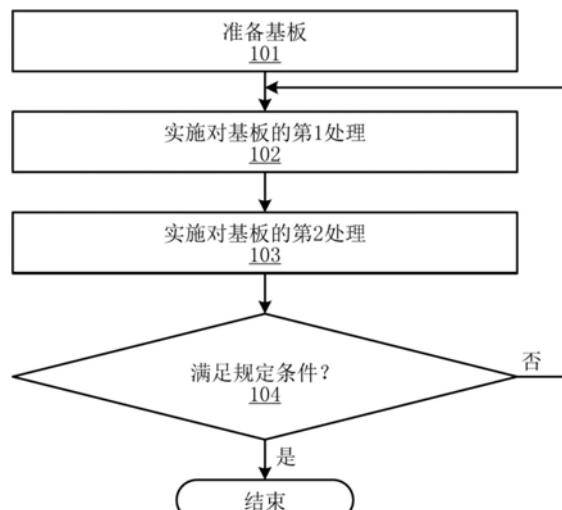

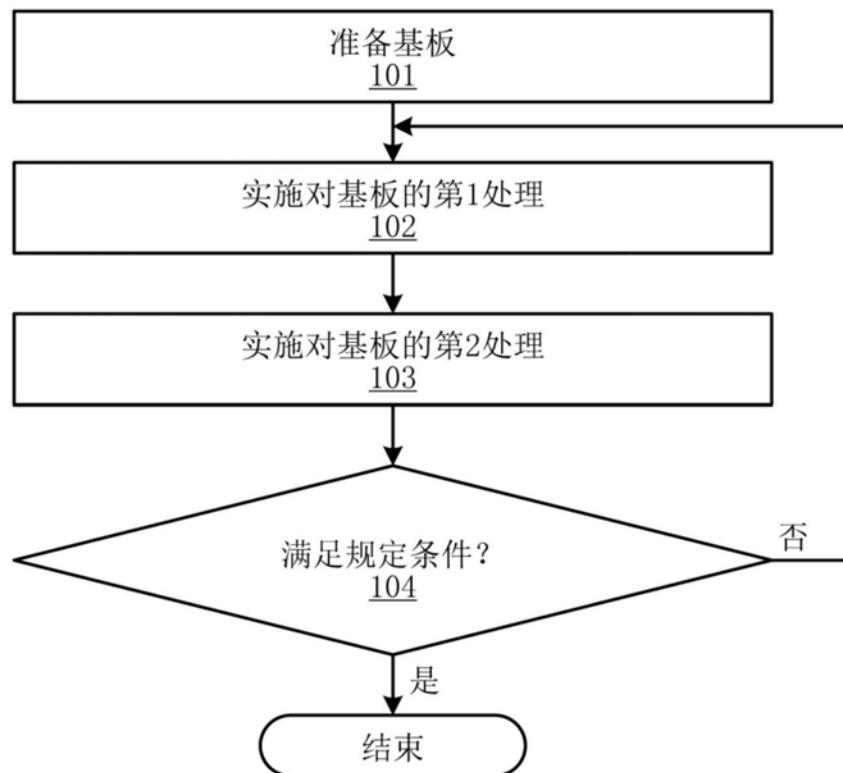

[0010] 图2为表示本发明的一个实施方式涉及的处理方法的一个示例的流程图。

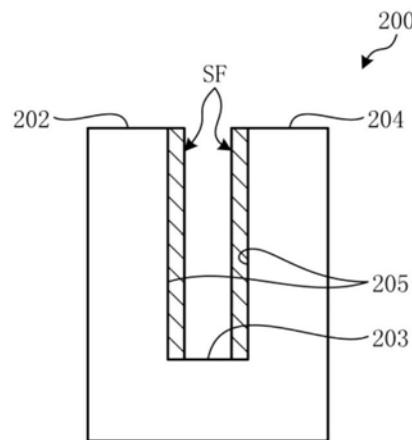

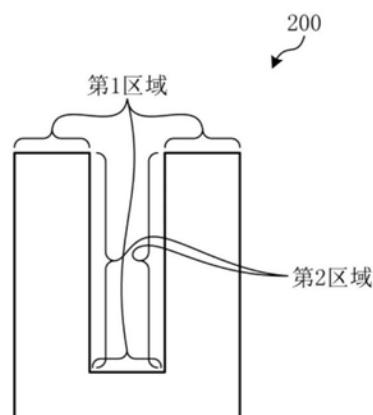

[0011] 图3A为表示本发明的一个实施方式中被处理的基板的一个示例的图。

[0012] 图3B为表示本发明的一个实施方式中被处理的基板的一个示例的图。

[0013] 图3C为表示本发明的一个实施方式中被处理的基板的一个示例的图。

[0014] 图4A为表示本发明的一个实施方式中被处理的基板的另一个示例的图。

[0015] 图4B为表示本发明的一个实施方式中被处理的基板的另一个示例的图。

[0016] 图4C为表示本发明的一个实施方式中被处理的基板的另一个示例的图。

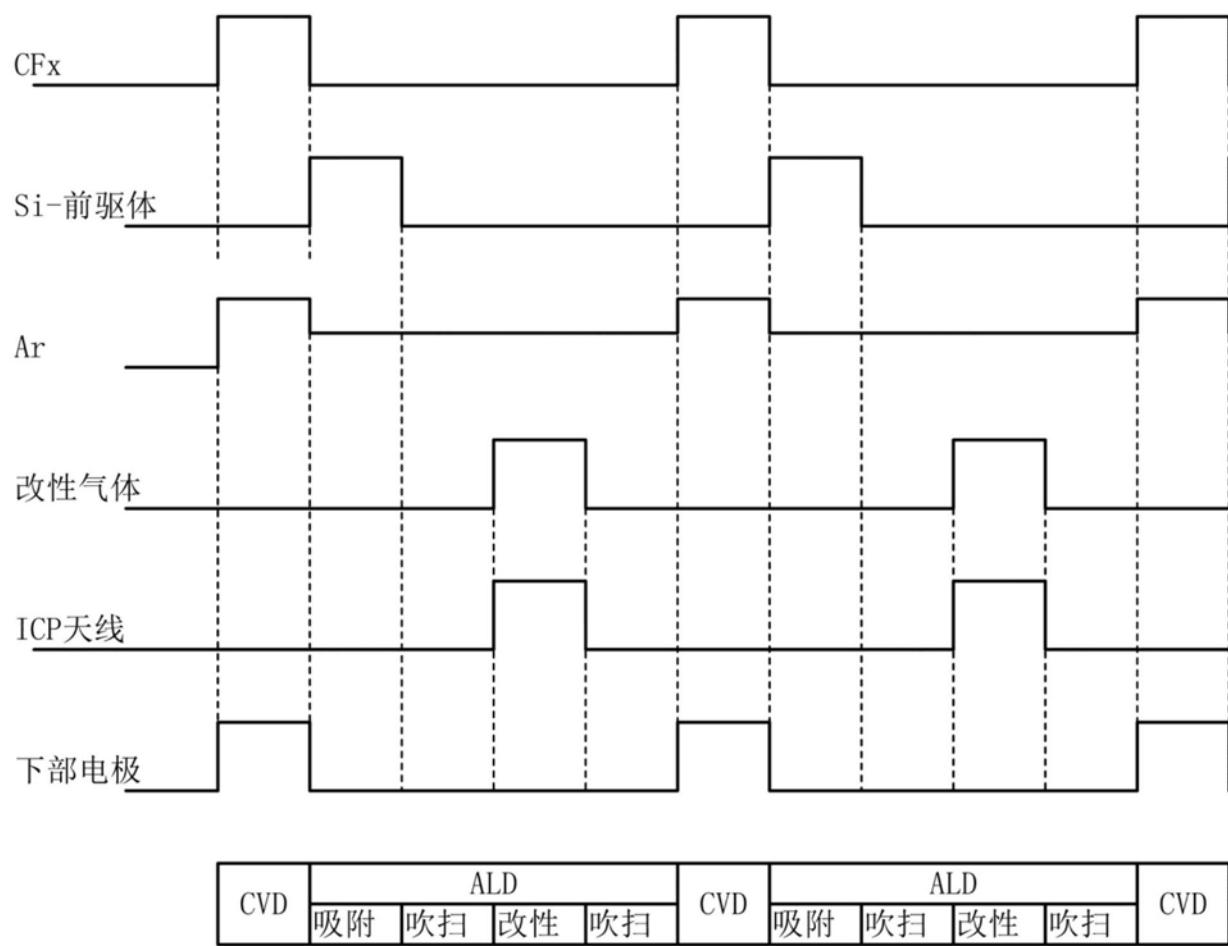

[0017] 图5为表示本发明的一个实施方式涉及的处理的流程的时序图。

[0018] 符号说明

[0019] 10 处理装置

- [0020] 12 腔室

- [0021] 12c 空间

- [0022] 12e 排气口

- [0023] 12i 进气口

- [0024] 12p 开口

- [0025] 13 支承机构

- [0026] 14 平台

- [0027] 16 静电卡盘

- [0028] 18 下部电极

- [0029] 18a 第1板

- [0030] 18b 第2板

- [0031] 22 直流电源

- [0032] 23 开关

- [0033] 24 流路

- [0034] 26a,26b 管道

- [0035] 28 气体供给管线

- [0036] 30 RF电源

- [0037] 32 整合器

- [0038] 34 屏蔽体

- [0039] 36 管道

- [0040] 38 排气装置

- [0041] 40 遮护板

- [0042] 42 窗

- [0043] 44 气体供给部

- [0044] 44a 气体源

- [0045] 44b 流量控制器

- [0046] 44c 阀

- [0047] 46 管道

- [0048] 48 闸阀

- [0049] 50 天线

- [0050] 52A 内侧天线元件

- [0051] 52B 外侧天线元件

- [0052] 54 夹具

- [0053] 60 屏蔽体

- [0054] 62A 内侧屏蔽体壁

- [0055] 62B 外侧屏蔽体壁

- [0056] 64A 内侧屏蔽板

- [0057] 64B 外侧屏蔽板

- [0058] 68A、68B 致动器

- [0059] 70A、70B RF电源

- [0060] 80 控制器

- [0061] FR 聚焦环 (focus ring)

- [0062] HT 加热器

- [0063] HP 加热器电源

- [0064] W 工件。

## 具体实施方式

[0065] 以下结合附图,对本发明的基板处理方法及基板处理装置的一个实施方式进行详细的说明。另外,以下公开的作为示例的实施方式在任何方面均不构成对本发明的限定。

### [0066] 基板处理装置的一个示例

[0067] 图1为表示本发明的一个实施方式涉及的处理装置10的概略结构的图。处理装置10为本发明的一个实施方式涉及的基板处理装置的一个示例。图1所示的处理装置10能够用于实现本发明的一个实施方式涉及的方法。图1所示的处理装置10为所谓的电感耦合等离子体(Inductively-coupled plasma: ICP)装置,具有用于生成电感耦合等离子体的等离子体源。不过,本发明的一个实施方式涉及的基板处理装置也可以利用通过其他方法生成的等离子体。例如,本发明的一个实施方式涉及的基板处理装置可以是利用:电容耦合等离子体(capacitively coupled plasma: CCP)、ECR等离子体(electron-cyclotron-resonance plasma)、螺旋波激发等离子体(helicon wave excited plasma:HWP)、或者表面波等离子体(surface wave plasma: SWP)等的装置。

[0068] 处理装置10具有腔室12。腔室12由铝等金属形成。腔室12例如大致为圆筒形状。在腔室12内设有用于实施处理的空间12c。

[0069] 在空间12c的下方配置有平台14。平台14构成为保持载置于其上的工件W。工件W例如是通过本发明的一个实施方式的方法进行处理的基板。

[0070] 平台14可以由支承机构13支承。支承机构13在空间12c内从腔室12的底部向上方延伸。支承机构13可以呈大致圆筒形。支承机构13可以由石英等绝缘材料构成。

[0071] 平台14包括静电卡盘16及下部电极18。下部电极18包括第1板18a及第2板18b。第1板18a及第2板18b由铝等金属构成。第1板18a及第2板18b例如呈大致圆筒形。第2板18b配置于第1板18a之上。第2板18b与第1板18a电连接。

[0072] 静电卡盘16配置在第2板18b之上。静电卡盘16包括绝缘层及配置于该绝缘层内的薄膜电极。直流电源22通过开关23与静电卡盘16的薄膜电极电连接。静电卡盘16基于直流电源22的直流电压生成静电力。静电卡盘16通过生成的静电力吸附并保持工件W。

[0073] 处理装置10动作时,聚焦环FR以包围工件W及静电卡盘16的外周的方式,配置于第2板18b之上且在第2板18b的周围。聚焦环FR具有提高处理的均一性的作用。聚焦环FR例如由石英形成。

[0074] 在第2板18b内形成有流路24。从配置于腔室12外部的温度调节部(例如冷却单元(chiller unit))向流路24供给用于温度控制的制冷剂等热交换介质。温度调节部调节热交换介质的温度。热交换介质从温度调节部通过管道26a供给至流路24。然后,从温度调节部通过管道26a被供给至流路24的热交换介质,通过管道26b被送回温度调节部。热交换介

质在由温度调节部进行温度调节之后,返回平台14内的流路24。如此,能够调节平台14的温度即工件W的温度。

[0075] 处理装置10还具有从平台14中穿过而延伸至静电卡盘16的上表面的气体供给管线28。从热交换气体供给机构,通过气体供给管线28,氦气(He)等热交换气体被供给至静电卡盘16的上表面与工件W的下表面之间的空间中。如此,可促进平台14与工件W之间的热交换。

[0076] 此外,加热器HT也可以配置于平台14内。加热器HT为加热装置。加热器HT例如嵌入第2板18b或静电卡盘16内。加热器HT与加热器电源HP连接。加热器电源HP向加热器HT供给电力,由此调整平台14的温度乃至工件W的温度。

[0077] 平台14的下部电极18通过整合器32与高频(RF)电源30连接。从RF电源30能够向下部电极18供给RF电流。RF电源30生成RF电力,向载置于平台14上的工件W引入离子。即,RF电源30生成形成偏置电压的RF电流。RF电源30生成的RF电流的频率例如在400千赫至40.68兆赫的范围内。在一个示例中,RF电流的频率为13.56兆赫。

[0078] 整合器32包含进行来自RF电源30的输出阻抗与负载侧即下部电极18侧的阻抗之间的匹配的电路。处理装置10能够不使用用于生成等离子体生成用的RF电流的附加的等离子体源,而通过向下部电极18供给RF电压来生成等离子体。

[0079] 处理装置10还具有可拆卸地安装于腔室12的内壁的屏蔽体34。并且,屏蔽体34配置成包围支承机构13的外周。屏蔽体34用于防止由处理生成的副产物附着于腔室12。屏蔽体34可以是由Y<sub>2</sub>O<sub>3</sub>等陶瓷涂布的铝部件。

[0080] 在平台14与腔室12的侧壁之间形成有排气通路。排气通路与形成于腔室12底部的排气口12e连接。排气口12e通过管道36与排气装置38连接。排气装置38包括压力调整部、以及涡轮分子泵(TMP)等真空泵。遮护板40配置于排气通路内即平台14与腔室12的侧壁之间。遮护板40具有在厚度方向上贯穿遮护板40的多个贯穿孔。遮护板40可以是由Y<sub>2</sub>O<sub>3</sub>等陶瓷涂布表面的铝部件。

[0081] 在腔室12的上侧形成有开口。开口由窗42封闭。窗42由石英等电介质形成。窗42例如是平板。

[0082] 在腔室12的侧壁形成有进气口12i。进气口12i通过管道46与气体供给部44连接。气体供给部44将在处理中使用的各种气体供给至空间12c。气体供给部44包括:多个气体源44a、多个流量控制器44b及多个阀44c。图1中未明示,也可以按照供给的气体设有不同的多个进气口,以使气体不混合。

[0083] 多个气体源44a包括后述的各种气体的气体源。1个气体源也可以供给1种以上的气体。多个流量控制器44b可以是质量流量控制器(MFC),流量控制器44b通过压力控制实现流量控制。多个气体源44a中包含的各气体源通过多个流量控制器44b中对应的一个流量控制器及多个阀44c中对应的一个阀与进气口12i连接。对进气口12i的位置不做特别的限定。例如,进气口12i可以不形成于腔室12的侧壁而形成于窗42内。

[0084] 在腔室12的侧壁内形成有开口12p。开口12p作为从外部将工件W搬入腔室12的空间12c、以及从空间12c内将工件W向腔室12的外部搬出的、工件W的搬入搬出路径。在腔室12的侧壁上设有闸阀48,能够使开口12p打开或封闭。

[0085] 在腔室12及窗42之上,配置有天线50及屏蔽体60。天线50及屏蔽体60配置于腔室

12的外侧。在本发明的一个实施方式中，天线50包括内侧天线元件52A及外侧天线元件52B。内侧天线元件52A为配置于窗42中央的螺旋线圈。外侧天线元件52B为配置于窗42之上且在内侧天线元件52A外周侧的螺旋线圈。内侧天线元件52A及外侧天线元件52B分别由铜、铝、不锈钢等导电性材料构成。

[0086] 内侧天线元件52A及外侧天线元件52B由多个夹具54夹持而被整体保持。多个夹具54分别呈棒状。多个夹具54从内侧天线元件52A的大致中央向外侧天线元件52B的外周侧沿径向延伸。

[0087] 天线50由屏蔽体60覆盖。屏蔽体60具有内侧屏蔽体壁62A及外侧屏蔽体壁62B。内侧屏蔽体壁62A为圆筒形状。内侧屏蔽体壁62A配置于内侧天线元件52A与外侧天线元件52B之间，并包围内侧天线元件52A。外侧屏蔽体壁62B为圆筒形状。外侧屏蔽体壁62B配置于外侧天线元件52B的外侧，并包围外侧天线元件52B。

[0088] 在内侧天线元件52A之上配置有圆盘状的内侧屏蔽板64A，覆盖内侧屏蔽体壁62A的开口。在外侧天线元件52B之上配置有平板环形的外侧屏蔽板64B，覆盖内侧屏蔽体壁62A与外侧屏蔽体壁62B之间的开口。

[0089] 屏蔽体60中包括的屏蔽体壁及屏蔽板的形状并不受以上的记载所限定。例如，屏蔽体60的屏蔽体壁也可以是截面为4边形的棱柱状。

[0090] 内侧天线元件52A及外侧天线元件52B与RF电源70A及RF电源70B分别连接。内侧天线元件52A及外侧天线元件52B分别从RF电源70A及RF电源70B接收相同或不同频率的电力供给。RF电力从RF电源70A被供给至内侧天线元件52A时，在空间12c内会产生感应磁场，激发空间12c内的气体而使得在工件W的中心上方产生等离子体。另一方面，RF电力从RF电源70B被供给至外侧天线元件52B时，在空间12c内会产生感应磁场，激发空间12c内的气体而使得在工件W的外周部上方产生环状的等离子体。

[0091] 根据从RF电源70A及RF电源70B输出的频率，对内侧天线元件52A及外侧天线元件52B各自的电长度进行调整。由此，内侧屏蔽板64A及外侧屏蔽板64B的z轴方向的位置各自独立地由致动器68A及68B调整。

[0092] 处理装置10还具有控制器80。控制器80可以是包括处理器、存储器等存储部、输入部、显示器等的计算装置。控制器80基于存储于存储部的控制程序或配方数据(recipe data)而动作，来控制处理装置10的各部分。例如，控制器80控制多个流量控制器44b、多个阀44c、排气装置38、RF电源70A、70B、RF电源30、整合器32、加热器电源HP等。控制器80在实现本发明的一个实施方式涉及的方法时，可以根据上述控制程序或配方数据来控制处理装置10的各部分。

[0093] 本发明的一个实施方式涉及的处理的流程的一个示例

[0094] 图2为表示本发明的一个实施方式涉及的处理方法的一个示例的流程图。本发明的一个实施方式涉及的处理装置10对半导体基板等的工件W进行处理。

[0095] 在步骤101中，首先准备用于本发明的一个实施方式涉及的处理的基板。在本发明的一个实施方式中，基板被搬入腔室12内，可以载置并保持于静电卡盘16上。并且，可以对基板实施预处理。例如，在基板表面的特性不均一时，可以实施用于均一化的处理。处理对象基板可以由二氧化硅(SiO<sub>2</sub>)、氮化硅(SiN)或者锗(Ge)等形成。不过，只要基板的表面为亲水性，或者基板具有实施了亲水化处理的表面即可，基板也可以含有其他的材料。基板可

以具有通孔、沟槽、接触孔等凹凸。基板的凹凸也可以是通过蚀刻而形成的。基板可以是硅基板。在蚀刻中,可以使用HBr等卤素气体。蚀刻可以在与实施蚀刻后的处理例如后述的第1处理及第2处理的腔室相同的腔室内实施。不过,也可以在与实施第1处理及第2处理的腔室不同的腔室内实施蚀刻。

[0096] 在步骤102中控制器80控制处理装置10来实施第1处理。第1处理中,在基板上的第1区域形成第1膜。在本发明的一个实施方式中,第1处理为化学气相沉积(CVD)处理。第1处理可以是等离子体CVD。不过,第1处理也可以不使用等离子体来实施。

[0097] 在第1处理中,通过气体供给部44向腔室12导入第1气体。控制器80控制RF电源30来将RF电力供给至下部电极18。由此,第1气体被等离子体化,在基板表面上形成第1膜。

[0098] 第1气体可以为含碳气体。第1气体例如可以是:氟碳气体、氢氟碳气体、碳氢气体。例如可以使用CF<sub>4</sub>、C<sub>4</sub>F<sub>6</sub>、C<sub>4</sub>F<sub>8</sub>、CH<sub>2</sub>F<sub>2</sub>、CHF<sub>3</sub>、CH<sub>4</sub>等气体。例如,PPFC(Plasma Polymerized Fluorocarbon,等离子聚合氟碳化合物)膜为疏水性,适于本发明的一个实施方式的第1膜。不过,只要能够在基板的亲水性表面上形成疏水性的膜,作为第1气体可以利用任何气体。并且,由第1气体形成的疏水膜优选在后述第2处理中被去除。在第1处理中,第1气体可以包含氮气(N<sub>2</sub>)、氩气(Ar)等不活泼气体作为承载气体。

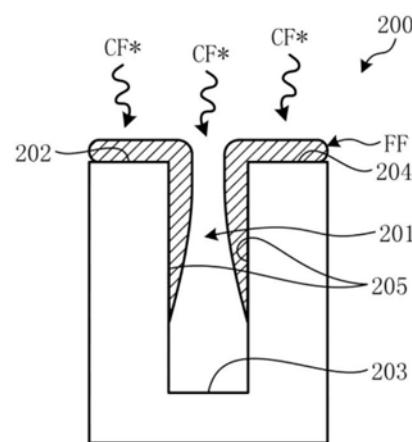

[0099] 第1膜可以形成于基板的第1区域内。第1区域的位置可以根据基板上的凹凸来决定。此外,第1区域的位置也可以根据第1处理的种类来决定。例如,可以根据第1处理为各向异性CVD还是各向同性CVD来决定第1区域的位置。图3A为作为本发明的一个实施方式涉及的处理的对象的基板的概略图。图3A中,基板200具有沟槽201。沟槽201的开口的顶部与底部具有大致相同的大小。在对该基板200实施各向异性CVD时,如图3A所示,使CF<sub>x</sub>等第1膜FF在区域202、203、204沉积。例如,图3A中的第1膜FF形成于顶部202、204及底部203,但不形成在侧壁205上。各向异性CVD的情况下,成膜材料主要在一个方向上沉积。在图3A的示例中,CF<sub>x</sub>在垂直方向上沉积,而在水平方向上不沉积。另外,垂直方向是指与基板200的表面正交的方向,水平方向是指与基板200的表面平行的方向。由此,第1膜FF不形成于侧壁205上。然而,第1膜FF也可以相比于在顶部202、204及底部203上少量地,在侧壁205上沉积。此外,第1膜FF也可以在底部203上的膜厚比在顶部202、204上薄。

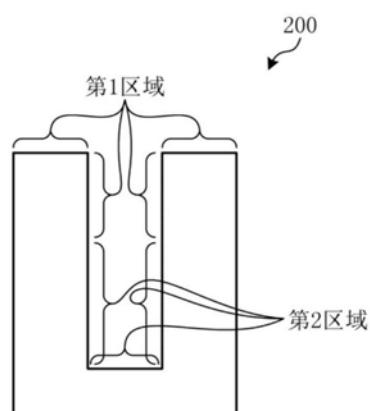

[0100] 另一方面,在各向同性CVD的情况下,可以如图4A所示地形成第1膜FF。在图4A中,第1膜FF形成于顶部202、204及侧壁205的上部,但不形成于底部203及侧壁205的下部。第1膜FF的膜厚并非大致均一,而是以在沟槽201的上端隆起的方式沉积。这样,第1区域的位置可以根据基板的凹凸而变化。

[0101] 在步骤103中,控制器80控制处理装置10来实施第2处理。第2处理在基板上的第2区域形成第2膜。在本发明的一个实施方式中,第2处理可以为原子层沉积(ALD)处理。在步骤103中,可以重复实施1次以上的ALD处理,直到第2膜SF的膜厚达到规定值。另外,这里设通过1次ALD处理形成1原子层。优选地,每实施1次第1处理,就在第2处理中实施1次以上的ALD处理。在第2处理的期间中第1膜FF被完全或部分去除后,可以再次实施第1处理即步骤102。优选地,在第1膜FF被完全去除前,重复实施第1处理。

[0102] ALD处理包括吸附步骤及活性化步骤即改性步骤。在吸附步骤中,吸附于基板200的物质的前驱体被导入腔室12内。接着在活性化步骤中,在腔室12内生成改性气体的等离子体,对基板表面上的吸附层进行改性,由吸附于表面的前驱体形成第2膜。

[0103] 在本发明的一个实施方式中,前驱体从可以吸附于羟基的材料中选出。例如可以是:前驱体为含硅的前驱体,改性气体为O<sub>2</sub>、CO、CO<sub>2</sub>、NO、NO<sub>2</sub>等含有氧元素的气体。

[0104] 在第1处理中,第1膜在基板的第1区域上沉积。由于第1膜具有疏水性表面,在第2处理中被导入的前驱体不会吸附于第1区域。并且,前驱体会吸附于基板200上的第1区域以外的区域。在接下来的改性步骤中,吸附的前驱体被改性而在第1区域以外的区域形成第2膜。第1区域以外的区域也称为第2区域。

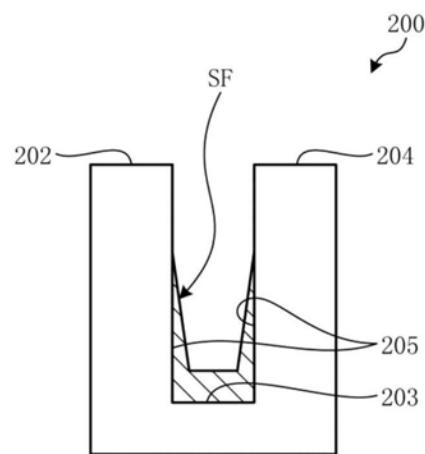

[0105] 如图3B的示例所示,对图3A的基板200实施第2处理,则图3B及图4B所示的第2膜SF会在侧壁205上形成。同时,顶部202、204及底部203上的第1膜FF在第2处理中会受等离子体的影响而被去除。由此,第2膜SF仅在基板200的侧壁205上形成。第1膜FF在第2处理后仍残存于顶部202、204及底部203的情况下,还可以实施用于去除第1膜FF的其他处理。例如,在第2处理后,可以将基板200暴露于氩气或氧气的等离子体中。

[0106] 如图4A所示地对基板200进行第2处理,则如图4B所示,第2膜SF形成于底部203及侧壁205的下部。由此,根据基板的凹凸及第1处理的种类(即,是各向异性CVD还是各向同性CVD),作为处理的结果得到的第2膜SF的形状及位置会变化。如图3C所示,在第1处理中实施各向异性CVD的情况下,第1区域为顶部202、204及底部203,第2区域为侧壁205。即,在第1处理为各向异性CVD的情况下,第1区域为水平区域,第2区域为垂直区域。此外,在第1处理为各向异性CVD的情况下,第1区域为在第1方向上延伸的表面,第2区域为在与第1方向不同的第2方向上延伸的表面。第1方向与第2方向所呈的角度可以为约90度。此外,也可以是:第1方向为与膜的沉积方向正交的方向,第2方向为与沉积方向平行的方向。另一方面,如图4C所示,在第1处理为各向同性CVD的情况下,第1区域为顶部202、204及侧壁205的上部,第2区域为底部203及侧壁205的下部。例如,在第1处理为各向同性CVD的情况下,第1区域为比第2区域靠近顶部的区域,第2区域为比第1区域靠近底部的区域。第1区域为由第1处理形成膜的区域,第2区域为由第2处理形成膜的区域。第1区域及第2区域可以有部分重合。

[0107] 如图2所示,步骤102及103后,在步骤104中对是否满足规定的条件进行判定。规定的条件是指:对同一基板已实施的第1处理及第2处理的次数、或者在基板上沉积的第2膜SF的膜厚。此外,规定的条件也可以是在基板200的表面上残存的第1膜FF的膜厚。

[0108] 例如,可以预先设定在第2处理中实施的ALD处理的次数,在存储部内将其存储为控制程序。例如,可以计算出由1次第2处理形成的第2膜的膜厚,而设定为了使第2膜的膜厚达到期望值所需要的ALD处理的次数。并且,在步骤104中,可以判定对同一基板是否已实施规定次数的第2处理。

[0109] 作为上述处理的代替,或者除上述处理之外,在步骤104中,可以对残存于基板上的第1膜的膜厚是否达到了规定值例如“0”进行判定。在第2膜的膜厚尚未达到规定值而第1膜已从基板上被完全去除的情况下,再次实施步骤102及103。此外,也可以在步骤102之后实施其他的对规定的条件是否达成进行判定的追加步骤,来判定第1膜的膜厚是否达到了规定值。

[0110] 步骤104中,控制器80可以基于存储于存储部的控制程序来进行实施。在步骤104中判定为满足了规定的条件的情况下(步骤104,是),处理结束。另一方面,在步骤104中判定为尚未满足规定的条件的情况下(步骤104,否),处理返回步骤102。例如,控制器80重复实施步骤102及103,直到满足规定的条件。控制程序也可以设定为:在步骤104中判定为尚

未满足规定的条件的情况下,仅实施步骤102与步骤103中的任何一方。

[0111] 在原位 (In Situ) 的动作

[0112] 不将基板从腔室12取出而实施步骤102及步骤103。即,第1处理及第2处理不会破坏腔室12内的真空状态而在原位 (in situ) 实施。本发明的一个实施方式涉及的装置例如处理装置10具有气体供给部44,气体供给部44能够向腔室12内供给各种气体。此外,本发明的一个实施方式涉及的装置能够不破坏腔室12内的真空状态地实施第1处理及第2处理。此外,本发明的一个实施方式涉及的装置具有排气通路、排气口12e、排气装置3等排气机构,能够使不同种类的气体不在腔室12内混合地实施吹扫处理。因此,本发明的一个实施方式的装置能够在原位 (in situ)、或者不破坏真空状态地,实施步骤102及步骤103。

[0113] 第1处理及第2处理中的电力控制

[0114] 此外,本发明的一个实施方式涉及的装置可以根据处理过程改变等离子体生成的状态。例如,控制器80可以控制天线50及下部电极18,在第1处理期间中仅对下部电极18施加电压,在第2处理期间中仅对天线50施加电压。

[0115] 控制器80在第1处理中使天线50及下部电极18双方动作的情况下,第1气体可能会过度解离。这种情况下,由第1气体生成的自由基有可能会对基板造成损伤。因此在第1处理中,控制器80可以控制处理装置10,对下部电极18供给电力而不对天线50供给电力。此外,在第1处理中,控制器80也可以控制处理装置10,对下部电极18及天线50双方供给电力。这种情况下,控制器80将供给至天线50的电力控制在不会对基板造成损伤的程度。另一方面,在第2处理中,理想的是形成高质量的第2膜。因此,在第2处理中,优选生成高电子密度且是低电离能的等离子体。因此,在第2处理中,控制器80可以控制处理装置10,对天线50供给电力而不对下部电极18供给电力。此外,在第2处理中,控制器80也可以控制处理装置10,对下部电极18及天线50双方供给电力。这种情况下,控制器80将供给至下部电极18的电力控制在可生成低电离能的等离子体的较低水平。

[0116] 例如,控制器80可以基于如图5所示的时序,对处理装置10的各部分进行控制。如图5所示,第1处理 (CVD处理) 中,控制器80可以控制气体供给部44,将第1气体例如CF<sub>x</sub>气体及氩气供给至腔室12。同时,控制器80可以控制RF电源30,向下部电极18供给电力。第1处理中,控制器80不使(图5中表示为“ICP天线”的) 天线50动作。

[0117] 进而,在第1处理后,开始第2处理的吸附步骤。控制器80控制气体供给部44将含硅的前驱体(图5中表示为“Si-前驱体”) 等前驱体供给至腔室12内。在此期间中,控制器80也可以将氩气等承载气体供给至腔室12内。控制器80可以控制气体供给部44,在基板处理期间中恒定地将规定流量的承载气体供给至腔室12内。在此期间中,天线50及下部电极18不进行动作。含硅的前驱体被导入并吸附于基板后,控制器80对腔室12进行吹扫,将不需要的气体成分从腔室12排出。

[0118] 接下来,控制器80开始活性化步骤即改性步骤,对吸附的前驱体进行改性。在活性化步骤中,控制器80控制气体供给部44,将氧气等改性气体供给至腔室12内。同时,控制器80控制RF电源70A及70B,向天线50供给电力。在此期间中,控制器80不使下部电极18动作。然后,控制器80再次实施吹扫处理。吸附步骤及活性化步骤后的吹扫处理可以省略。并且,控制器80根据是否满足规定的条件,重复第1处理及第2处理。进而,控制器80也可以对第1处理及第2处理中的任何一方单独地重复实施。

[0119] 蚀刻处理

[0120] 在本发明的一个实施方式涉及的装置中,除了第1处理及第2处理,还可以在原位(*in situ*)实施其他的处理作为第3处理。例如,本发明的一个实施方式涉及的装置还可以实施蚀刻处理,由此能够进一步提高生产率。蚀刻处理可以是原子层蚀刻(ALE,atomic layer etching)处理。

[0121] 另外,ALE处理可以包含形成反应层的改性步骤、以及将改性后的反应层去除的去除步骤。ALE处理还可以包含分别设置于改性步骤及去除步骤之后的吹扫步骤。改性步骤可以使用N(氮)等离子体或者H(氢)等离子体来实施。去除步骤可以使用F(氟)等卤素等离子体(成分)来实施。

[0122] 在本发明的一个实施方式中,可以按照第1处理、第2处理及第3处理的顺序对其重复实施。各处理的重复次数也可以彼此不同。例如,可以在实施1次第1处理后实施10次第2处理。此外,第1处理、第2处理、第3处理的实施顺序也可以改变。

[0123] 以上为了完整并且明确地公开,对具体实施方式进行了说明。但是,本发明权利要求书中所记载的权利要求,不应根据上述公开对其进行限定性解释,应理解为本领域技术人员所能想到的、并且属于在本说明书中示出的基本的教导的范围内的、所有的变形例及替代性的构成例均包含于其中。

图1

图2

图3A

图3B

图3C

图4A

图4B

图4C

图5