[56]

| [54] | AUTOMATIC GRADER FOR SORTING OBJECTS ACCORDING TO BRIGHTNESS |                                             |  |  |  |

|------|--------------------------------------------------------------|---------------------------------------------|--|--|--|

|      | AND COLOR TONES                                              |                                             |  |  |  |

| [75] | Inventor:                                                    | Joseph R. Perkins, III, Burke, Va.          |  |  |  |

| [73] | Assignee:                                                    | <b>AMF Incorporated,</b> White Plains, N.Y. |  |  |  |

| [22] | Filed:                                                       | May 15, 1973                                |  |  |  |

| [21] | Appl. No.                                                    | : 360,570                                   |  |  |  |

| [52] | U.S. Cl                                                      |                                             |  |  |  |

| [51] | Int. Cl                                                      | B07c 5/342                                  |  |  |  |

| [58] | Field of Search 356/51, 221, 222, 229,                       |                                             |  |  |  |

|      |                                                              | 6/176, 177, 178, 179, 191, 186, 195;        |  |  |  |

|      | 209/                                                         | 111.6, 111.7, 111.5; 250/223 R, 226         |  |  |  |

|           | UNITED  | STATES PATENTS |           |

|-----------|---------|----------------|-----------|

| 3,066,797 | 12/1962 | Fraenkel       | 209/111.6 |

| 3,373,870 | 3/1968  | Black et al    |           |

| 3,737,239 | 6/1973  | Adams et al    |           |

| 3,744,919 | 7/1973  | Babb           |           |

| 3,750,883 | 8/1973  | Irving et al   |           |

References Cited

Primary Examiner—Allen N. Knowles

Attorney, Agent, or Firm—George W. Price; Charles J.

Worth

## [57] ABSTRACT

A system and apparatus for grading and sorting tobacco leaves and other objects according to brightness and two color tones are provided. The tobacco leaves or objects are caused to traverse a background plate of known color and both are impinged by polychromatic light. The light reflected therefrom in three distinct spectral bands is detected and analyzed according to a predetermined mathematical relationship to compare the brightness and two color tones of the said leaves or objects to standards which are selectively dialed in to the apparatus. Logic circuitry is provided to constrain acceptance or rejection of the leaves or objects by the system in response to a determination that at least one of the characteristics of brightness and two color tones exceeds a predetermined deviation from the preset standards. One of the spectral bands is chosen to provide uniform reflectivity from the series of leaves or objects being sorted to normalize the size of the various objects to that of the background sur-

## . 82 Claims, 46 Drawing Figures

SHEET OIL OF 40

SHEET 02 OF 40

SHEET 03 OF 40

SHEET 05 OF 40 Y2A Y2B FIG 5 **Y3A** R23 R24 **3**8 R22 <u>Y3</u> Y2 9 (5) 6 (2)  $\oplus$ 4 3 ZL LOAD CIO 10 FIG. 5B CII3 R21 ZLID ZLI: (SAI) (SA2) (SA3) (SDI) (SCI) 6 (SC2) -(SC3): (SC4) **ම** (3)  $\mathbb{Q}$ 2 8 9 <u>(8)</u> 6 Y33 Y34 RN-I GN-I T0 4 7 7 4 FIG 5C ZDR ZDG SMP-586

FIG. 5A

SHEET 09 OF 40

SHEET 11 OF 40

SHEET 12 OF 40

SHEET 14 OF 40

SHEET 19 OF 40

SHEET 27 OF 40

SHEET 31 OF 40

SHEET 32 OF 40 AC2 BLOW-OFF ALARM ACI ACI Y300 Y288 Y30I RI02 R95 **RI03** (TIME CLOCK) (2) Y287A (BLOW-0FF) Y287 (a) (b) (b) 9 ⊜1 AC2 ACI AC2/ R94-≽ RIOO 🛠 è B 0 @ **@** 6 ACL Y286 MCT2D LEDY @ R93 \$R99 Ø\$ <u>∞</u> TO FIG.

SHEET 33 OF 40

SHEET 34 OF 40

× ...

SHEET 35 OF 40 (FROM ST3#I) RL-TO FIG. 19A ST3E 40A 40B ST3#2 40 UL CHANNEL # 2 ST3D (FROM ST3#2) RL ST3E FL 40A 40B 40 ST3#3 CHANNEL #3 ST3D (FROM ST3#3) RL-ST3E STI-ST2  $I_{L}$ 40A 40B 40 ST3#4 UL CHANNEL # 4 RL ST3D FIG. 19B TO FIG. 19C 🕹 🖠

SHEET 36 OF 40

FIG. 21

SHEET 38 OF 40

SHEET 40 OF 40

FIG. 23

# AUTOMATIC GRADER FOR SORTING OBJECTS ACCORDING TO BRIGHTNESS AND COLOR TONES

This invention relates to automatic graders and more 5 particularly to systems and apparatus for automatically grading tobacco leaves and the like according to color.

In the past and at the present time, it is a normal practice to grade tobacco by manual methods, i.e., by 10 ing logic of the present invention; visual inspection of each leaf to determine given grades of tobacco leaves.

Furthermore, should a leaf be too green for present processing, such as a green sucker, manual inspection is also presently used to remove these leaves from fur- 15 ther processing as undesirable grades.

As a result, accurate duplication of tobacco grades is very difficult to achieve at the present time. This is due to the difference of opinion which exists among manual sorters who must use their own judgment in determin- 20 ing the grade of a given tobacco leaf. The eye of the observer is the standard rather than an actual grade reference.

It is, therefore, an object of the present invention to provide a new and novel automatic grader which can 25 readily duplicate grades of tobacco leaves and the like according to color regardless of the size or condition of the leaves.

It is another object of the present invention to provide a means of rapidly grading tobacco leaves and the 30 gram clock logic of the present invention; like without the need for manual inspection of each leaf.

It is another object of the present invention to provide a new and novel automatic grading system and apparatus which operates to grade tobacco leaves and the 35 the present invention; like by comparing the color of a given leaf with a background color standard over which the given leaf must pass during the sorting and grading process to which it is being subjected.

Still another object of the present invention is to provide a new and novel automatic grader utilizing a color comparison system which may be embodied in a transducer arrangement for adapting existing manual sorting equipment to fully automatic sorting and grading equipment.

Still another object of the present invention is to provide a new and novel automatic grader system and apparatus utilizing an unique combination of three color detection and resulting detected color signal strength to provide selective grading of tobacco leaves and the like for both brightness of color and redness and greenness of leaf.

Yet another object of the invention is to provide a new and novel automatic tobacco sorting and grading system and apparatus which may be operated as a series of machines or devices performing a like series of sorting and selecting functions such that all of the leaves in a given batch of tobacco being graded will be separated into desired categories.

These and other objects of the present invention will become more fully apparent with reference to the following specification and drawings which relate to a preferred embodiment of the invention.

In the drawings:

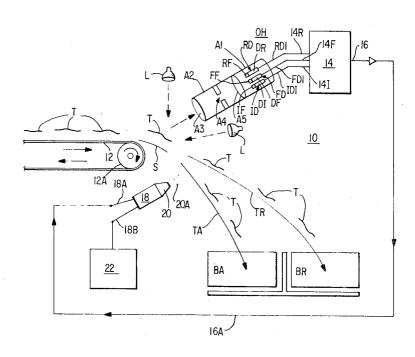

FIG. 1 is a general schematic of the present invention including the basic physical details of a preferred optical system for same;

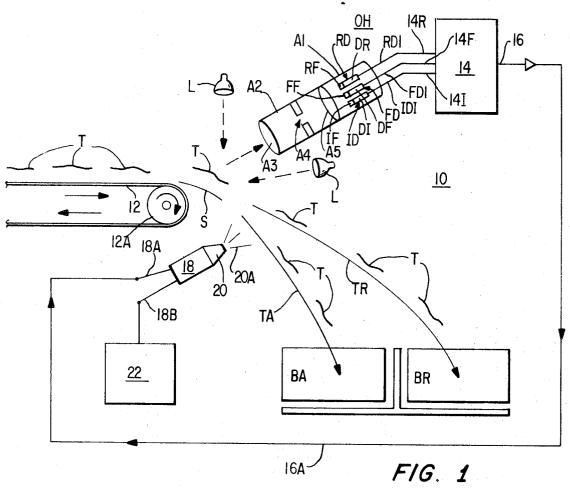

- FIG. 2 is a schematic of the front control panel of the present invention;

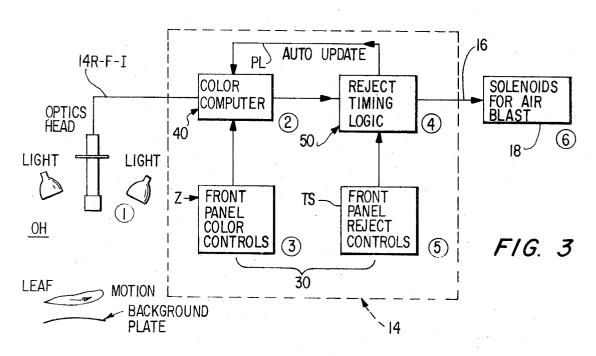

- FIG. 3 is a general block diagram of the control circuit of the present invention;

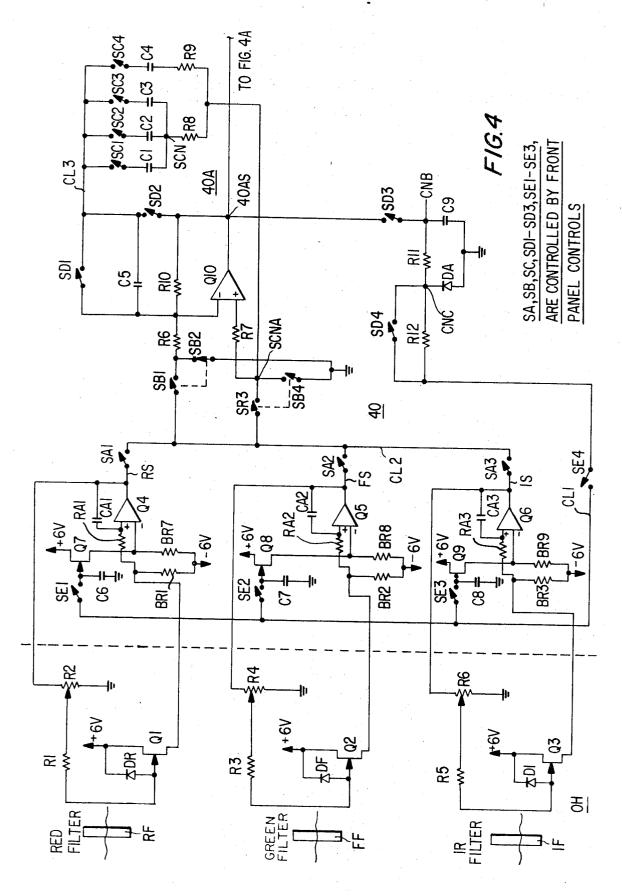

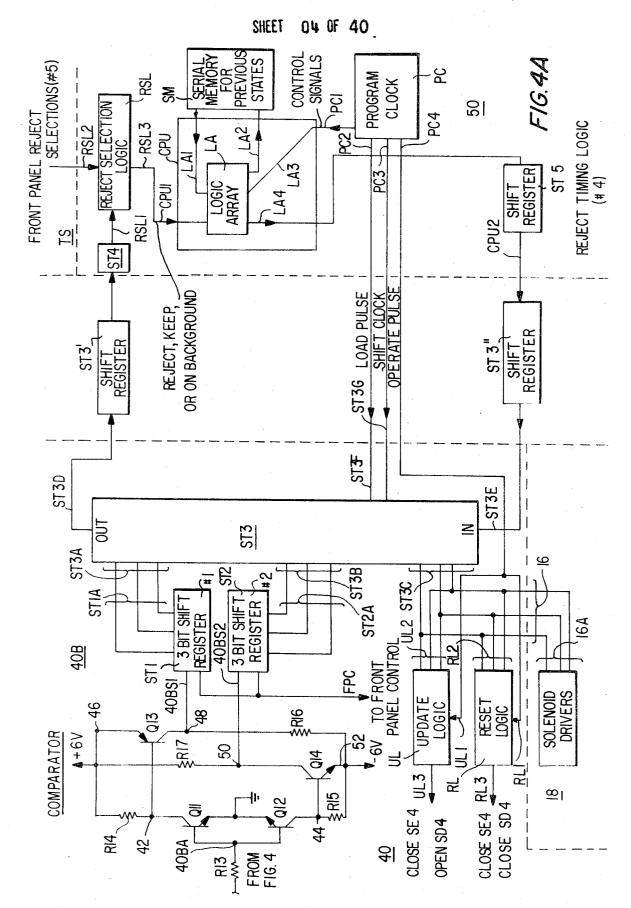

- FIGS. 4 and 4A together comprise a more detailed block diagram and schematic of the control circuit of the present invention;

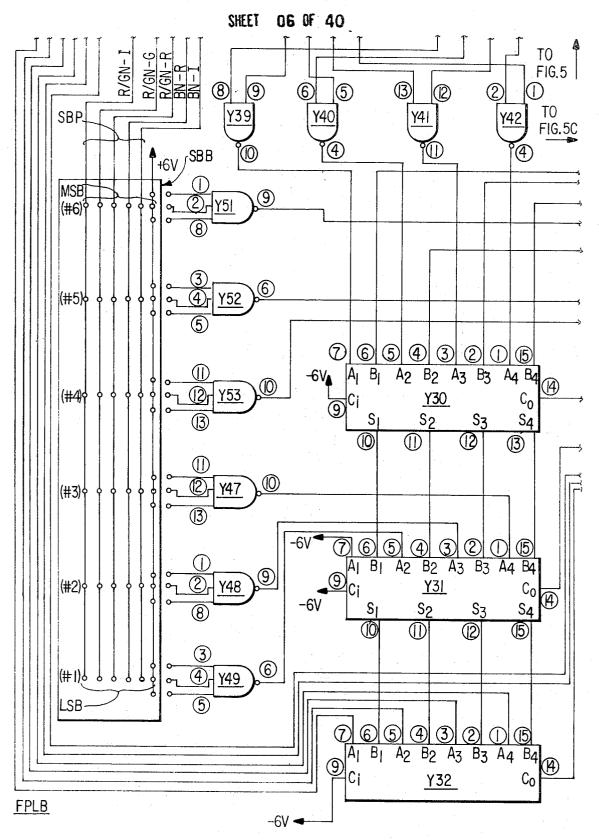

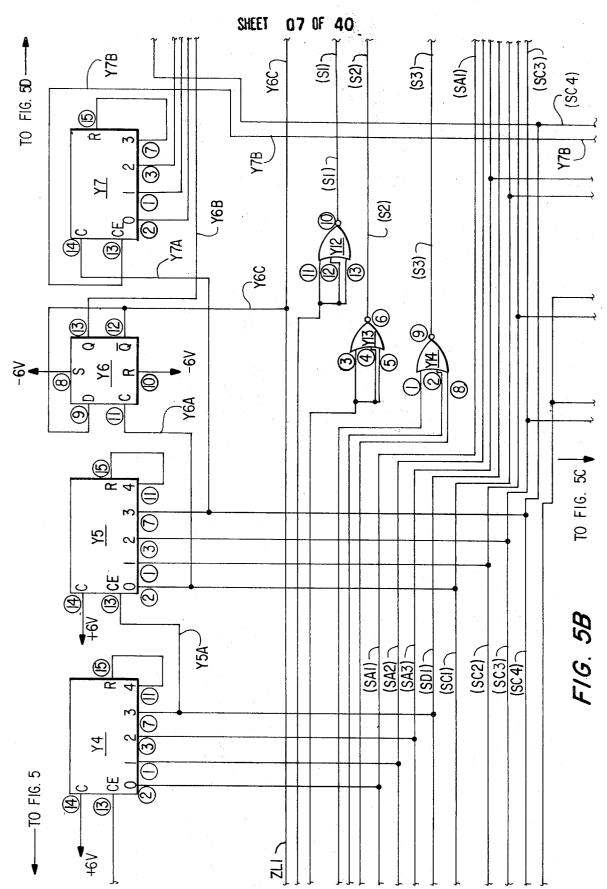

- FIGS. 5, 5A, 5B, 5C, 5D and 5E together comprise a detailed schematic of the front panel switch and cod-

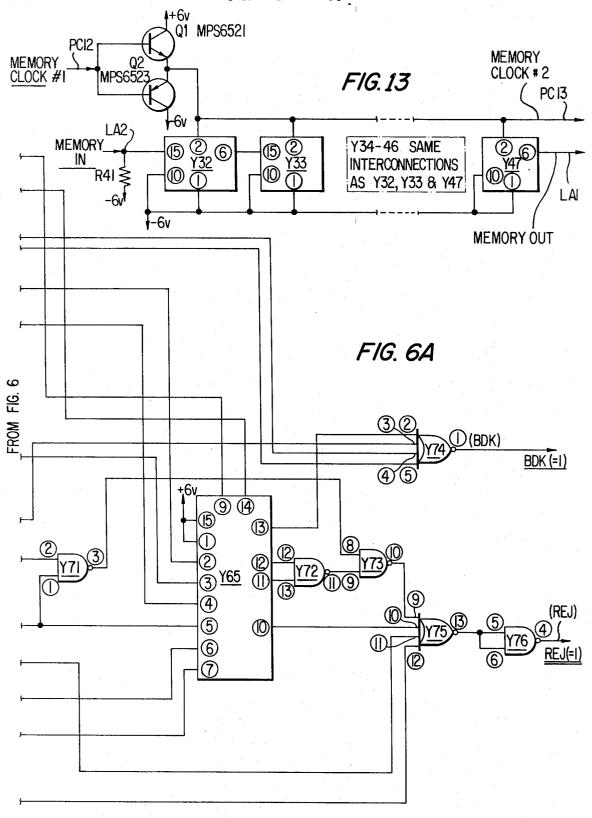

- FIGS. 6 and 6A together comprise a detailed schematic of the reject selection logic of the present inven-

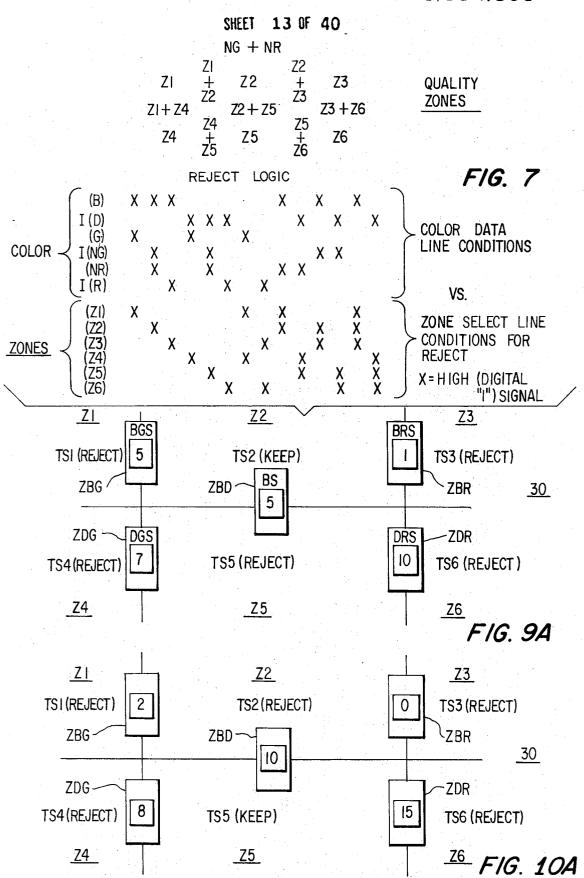

- FIG. 7 is a combind schematic of the possible color zones and combinations derived from the front control panel and an associated reject logic table illustrating color data line conditions vs. zone select line conditions for selective reject of various leaf colors;

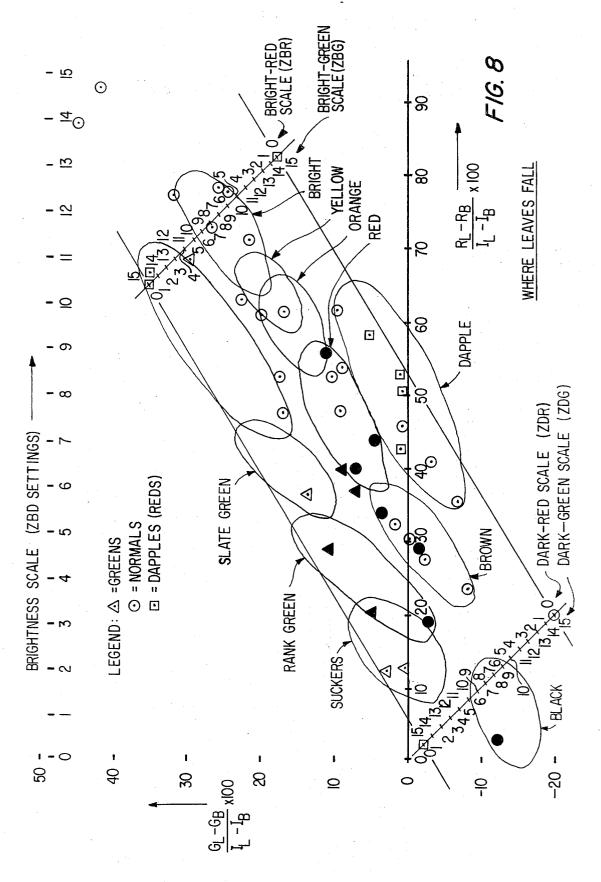

- FIG. 8 is a graphic portrayal of colors of tobacco leaves relative to the ordinates of red and green reflectivity in the present invention;

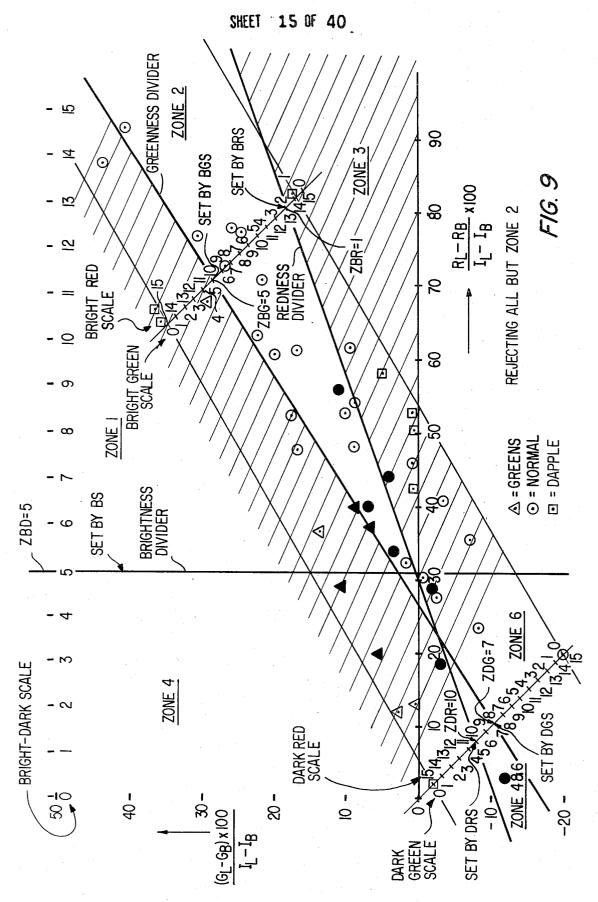

- FIGS. 9 and 9A illustrate one example of color zones selected for reject and the corresponding front panel switch settings, respectively;

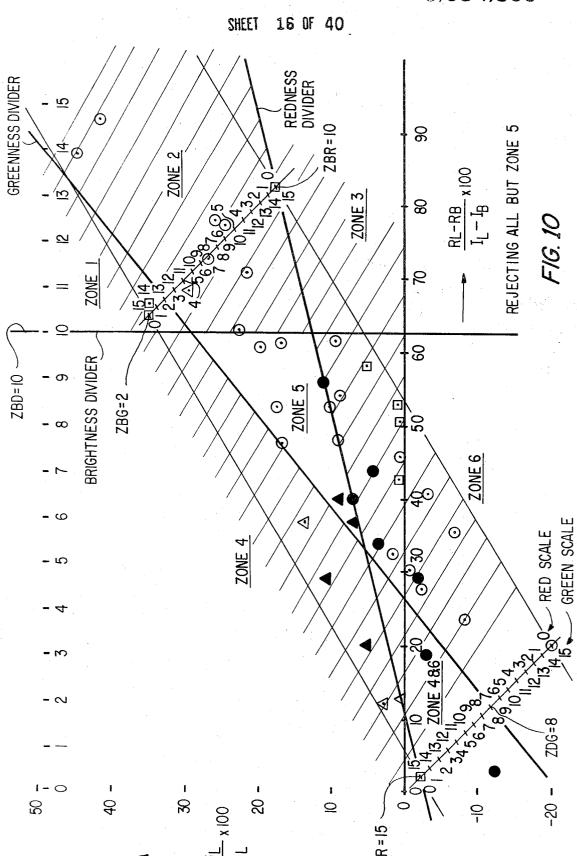

- FIGS. 10 and 10A illustrate another example of color zones selected for reject and the corresponding front panel switch settings, respectively;

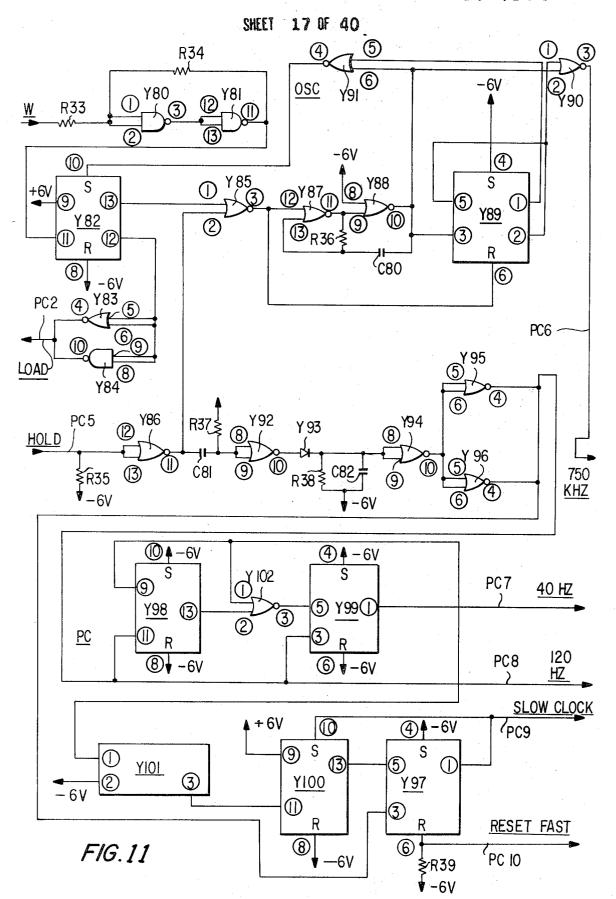

- FIG. 11 is a block diagram of a portion of the pro-

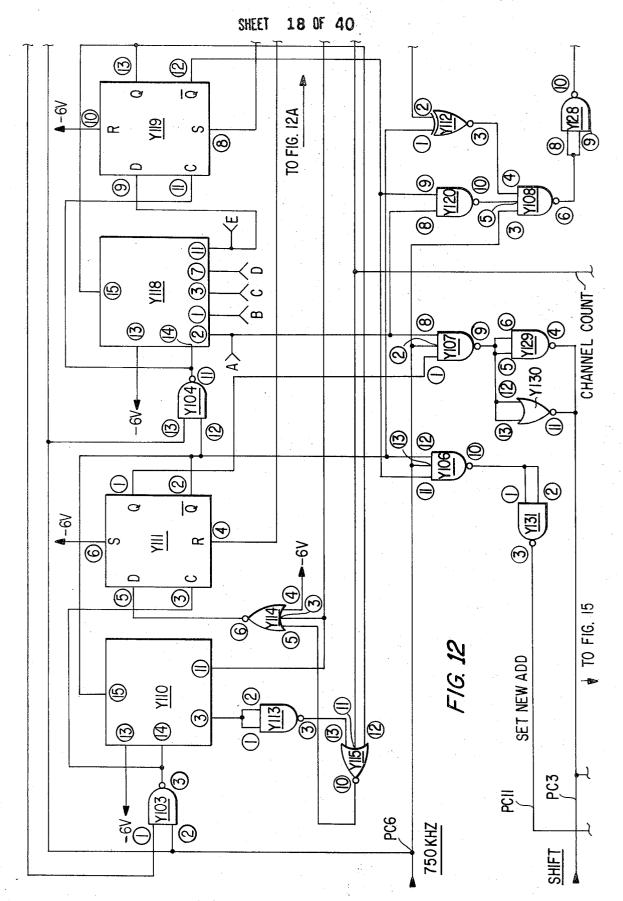

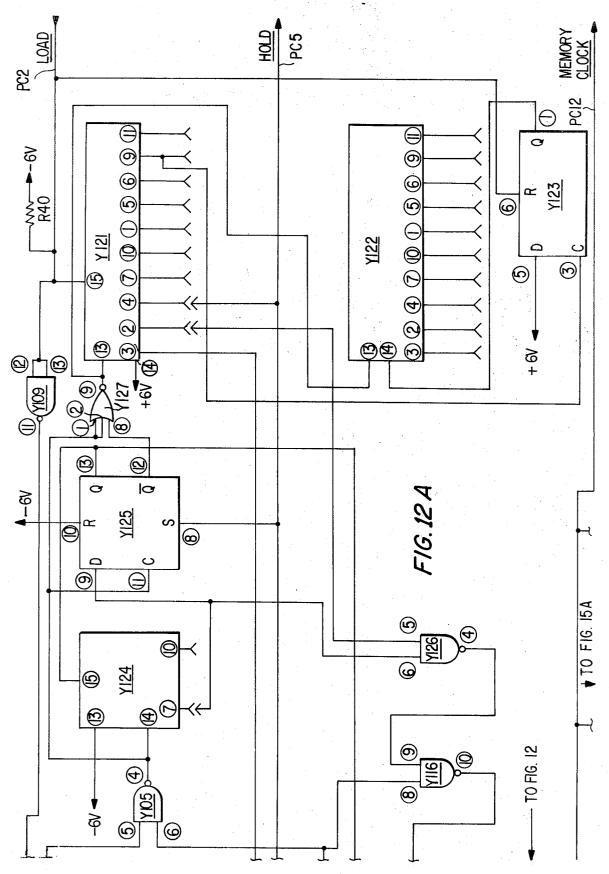

- FIGS. 12 and 12A together comprise a block diagram of another portion of the program clock logic of the present invention;

- FIG. 13 is a block diagram of the serial memory of

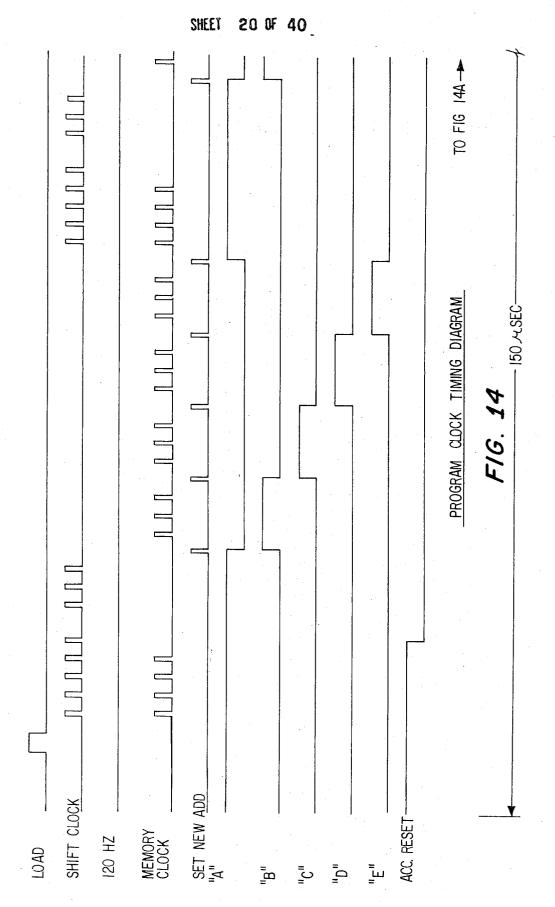

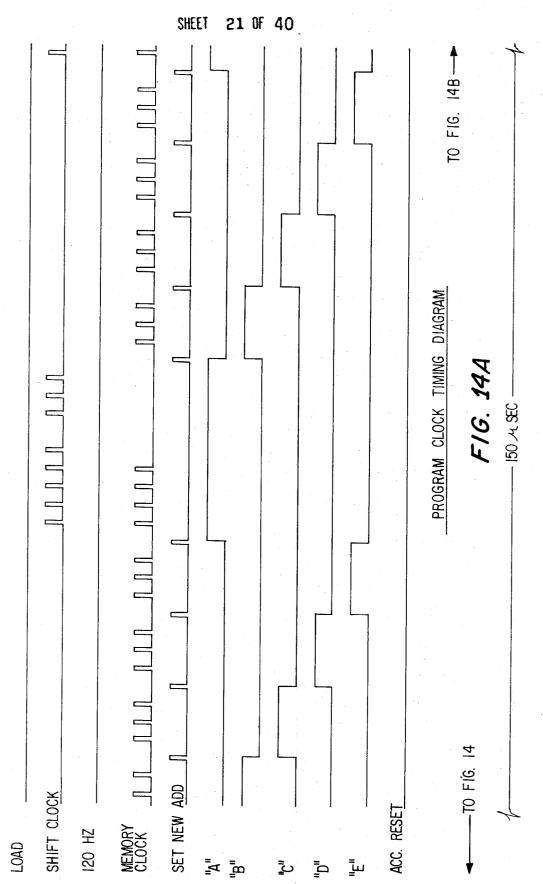

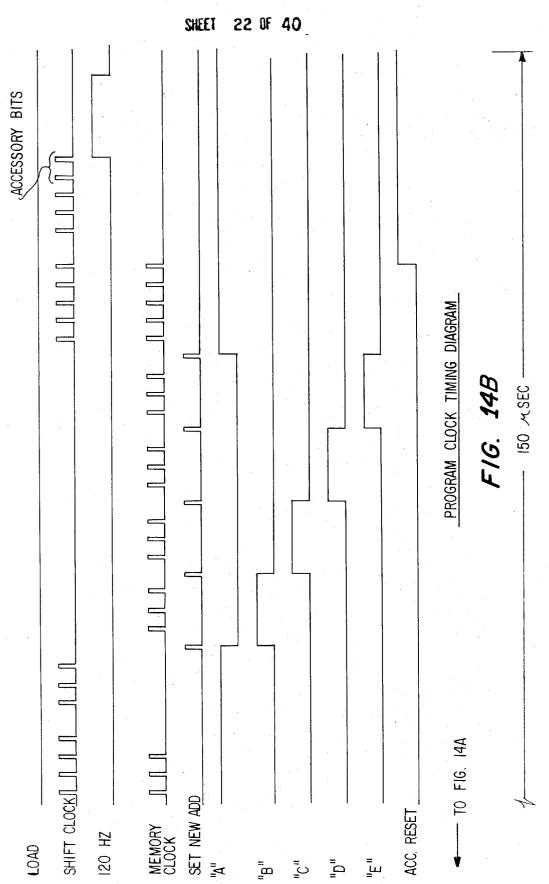

- FIGS. 14, 14A and 14B together comprise a timing diagram of the program clock signals of the present in-

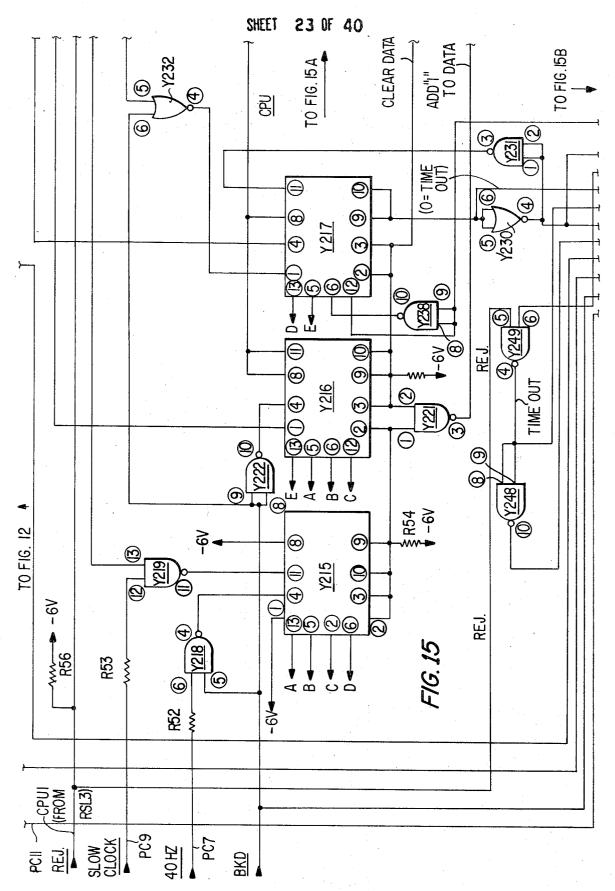

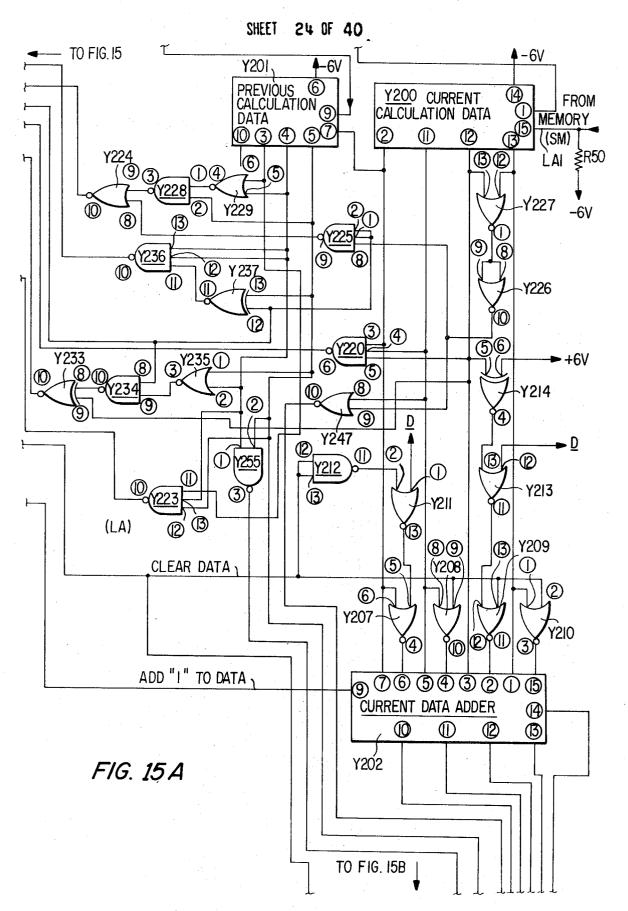

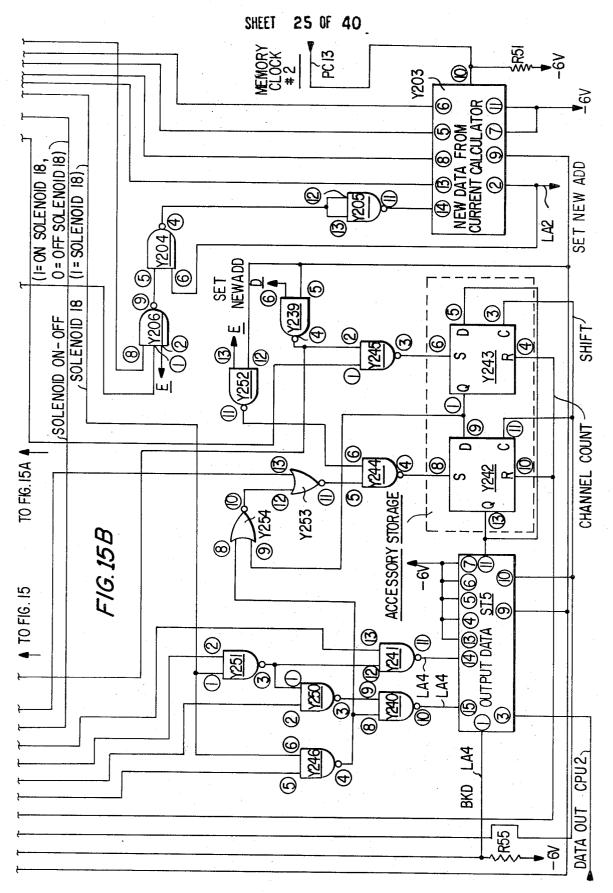

- FIGS. 15, 15A and 15B together comprise a sche-40 matic of the central process unit logic of the present invention:

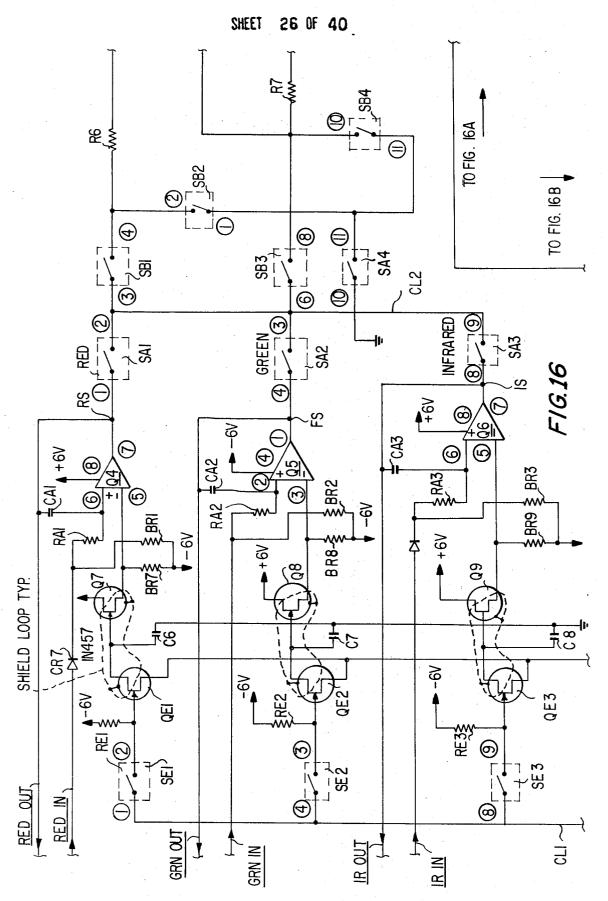

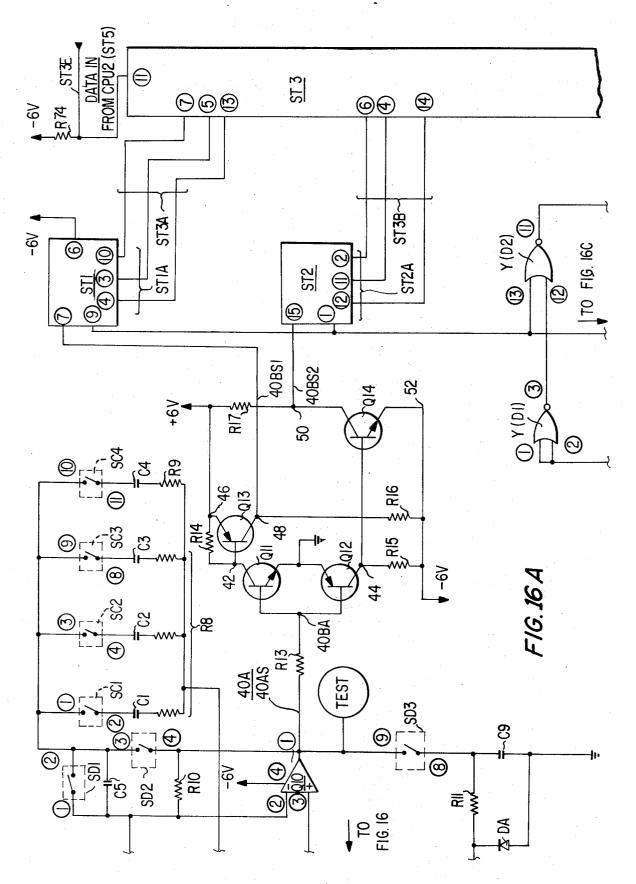

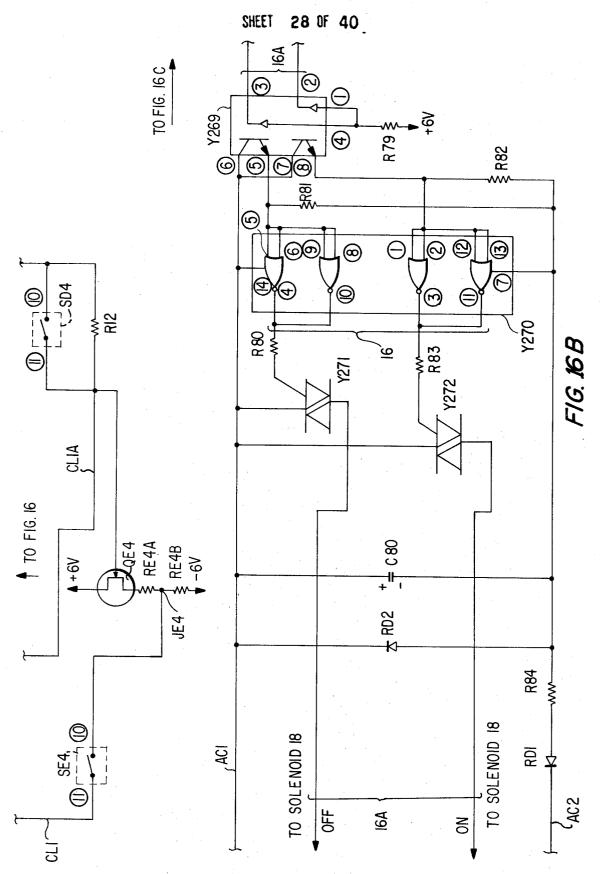

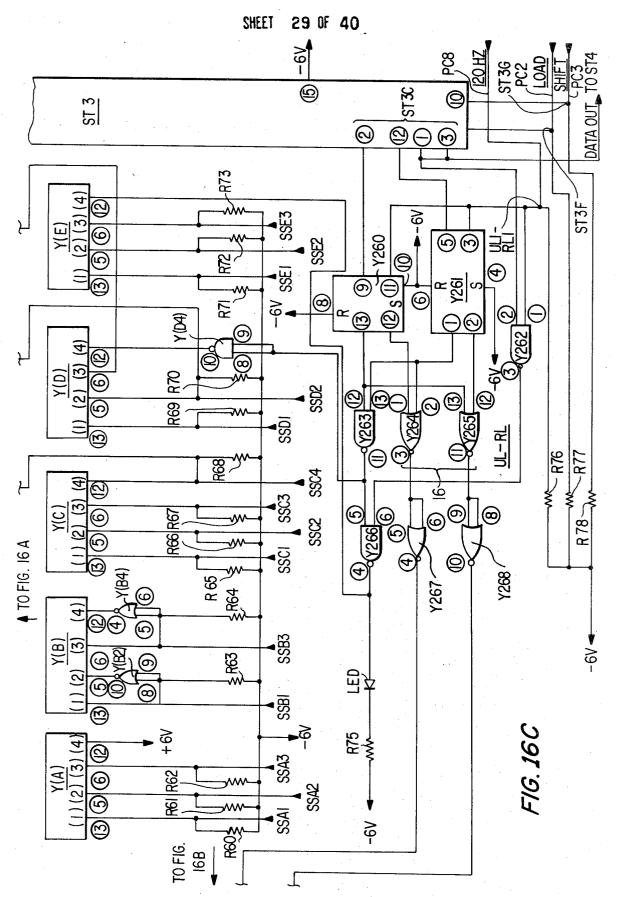

- FIGS. 16, 16A, 16B and 16C together comprise a more detailed schematic of the color computer color input logic and circuitry of the present invention, more generally shown in FIGS. 4 and 4A;

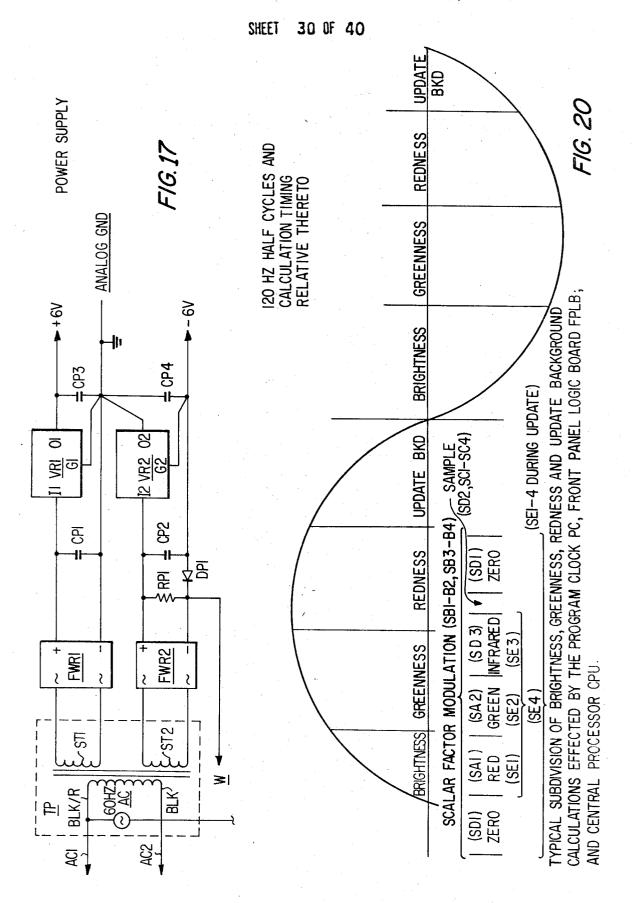

- FIG. 17 is a diagram of a power supply for the present invention;

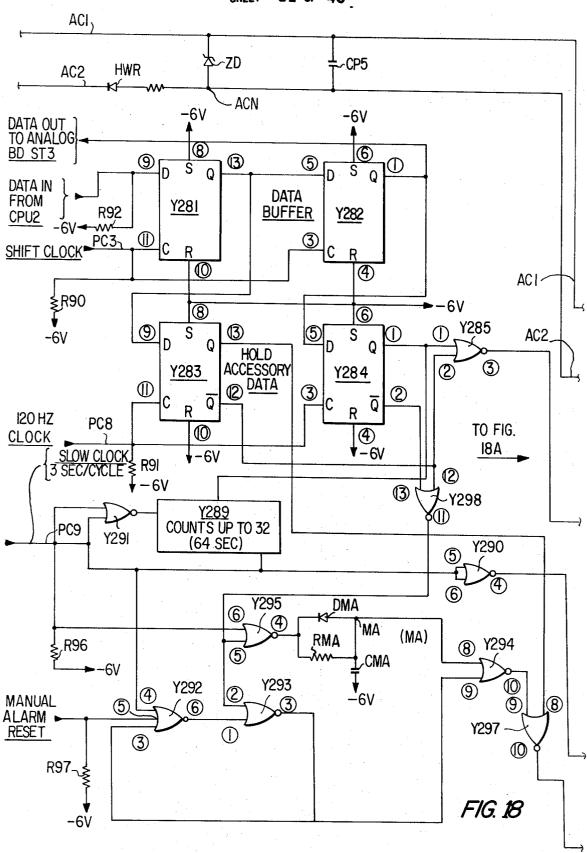

- FIGS. 18 and 18A together comprise a schematic of data buffer and accessory control logic of the present

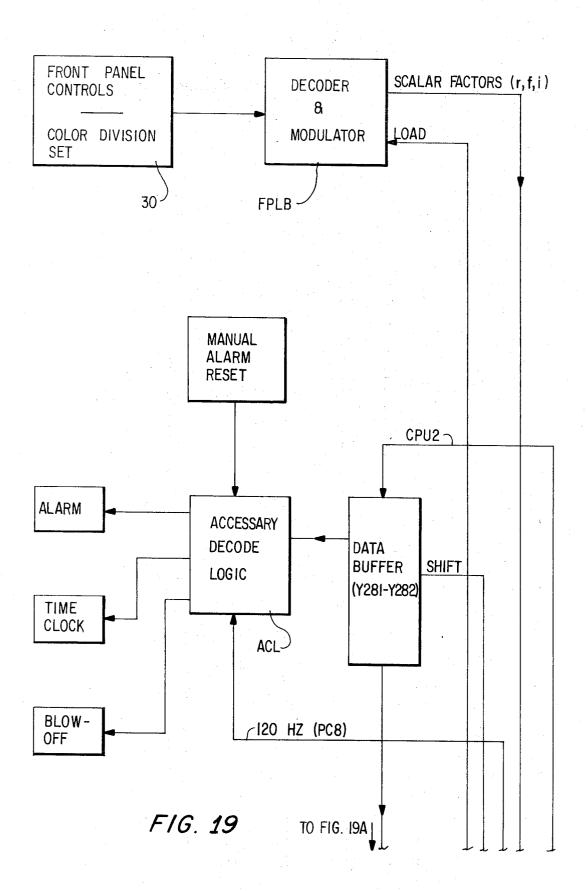

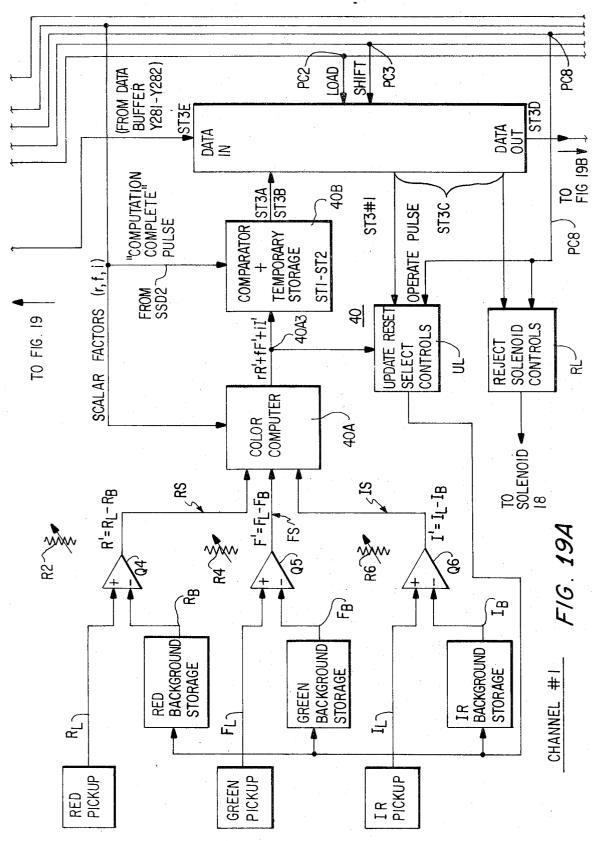

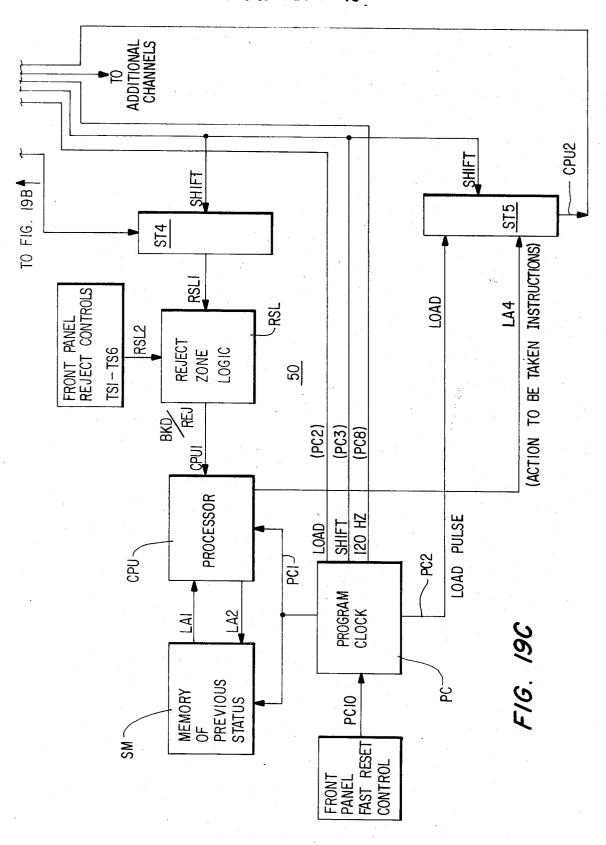

- FIGS. 19, 19A, 19B and 19C together comprise a block diagram of a four-channel embodiment of the present invention;

- FIG. 20 is a diagram illustrating the color calculation timing of the present invention;

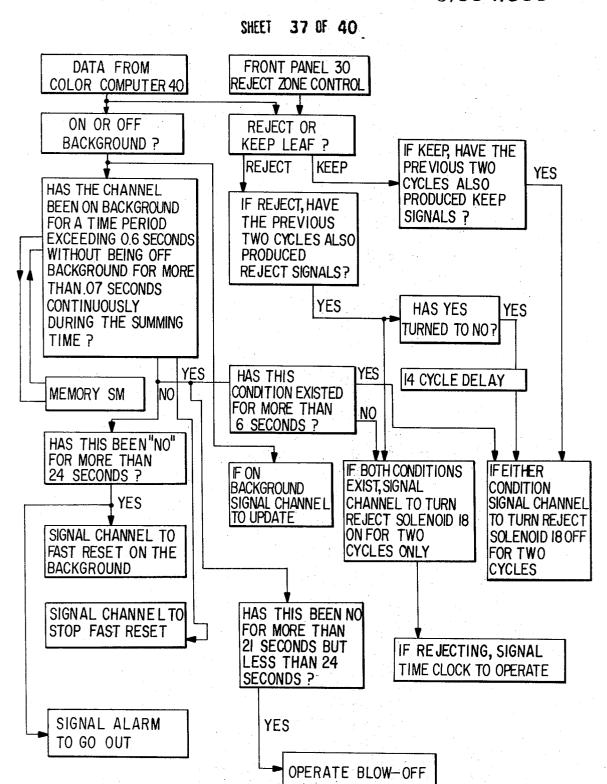

- FIG. 21 is a flow diagram of the operating program of the present invention;

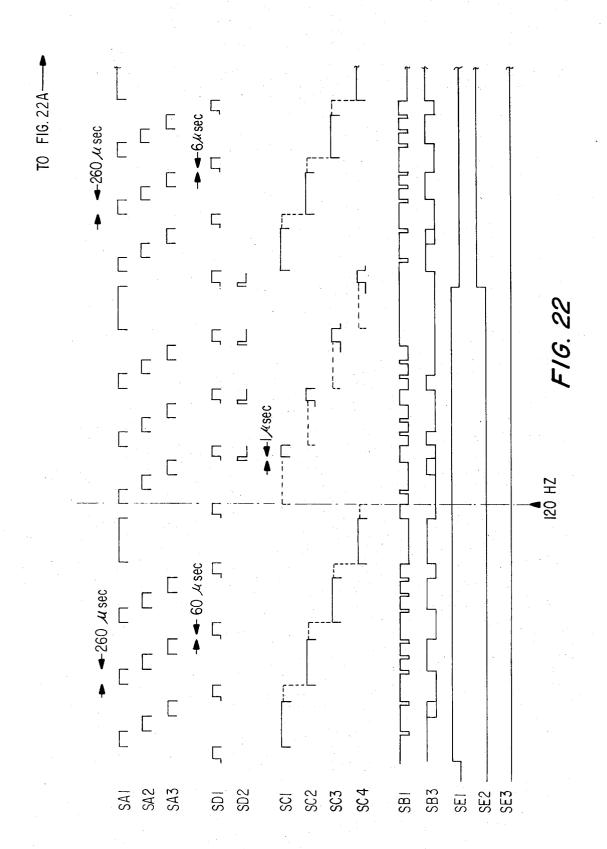

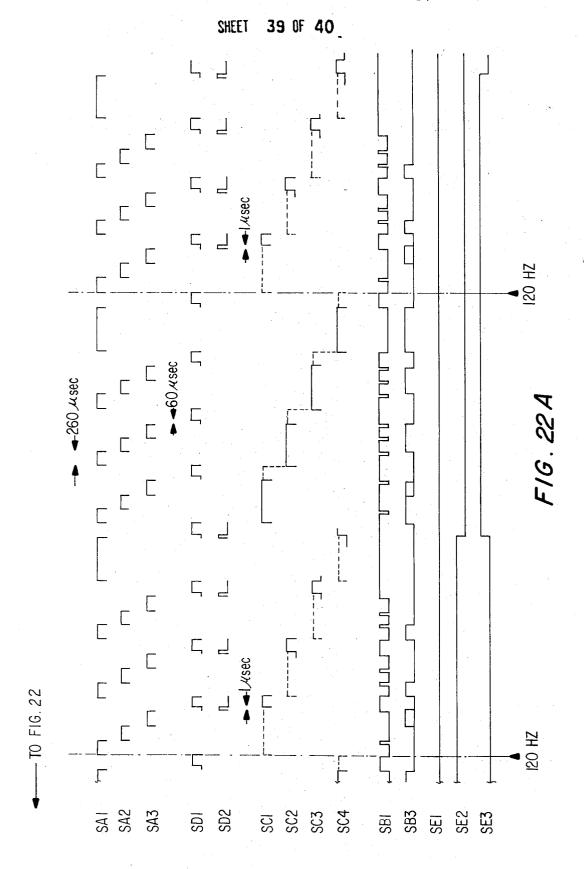

- FIGS. 22 and 22A taken together comprise a timing diagram of the color input, color computing, scalar value and update control means of the present invention:

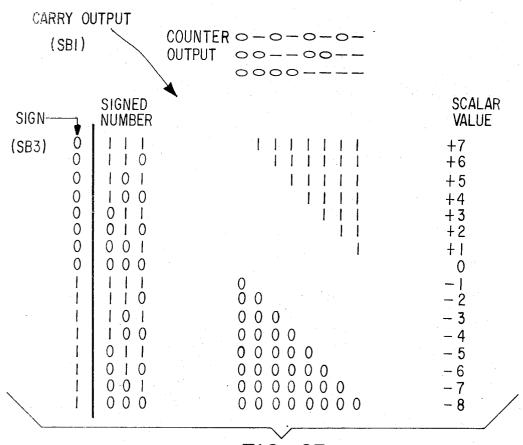

- FIG. 23 is a tabular illustraton of the logical generation of positive and negative scalar values of the present invention; and

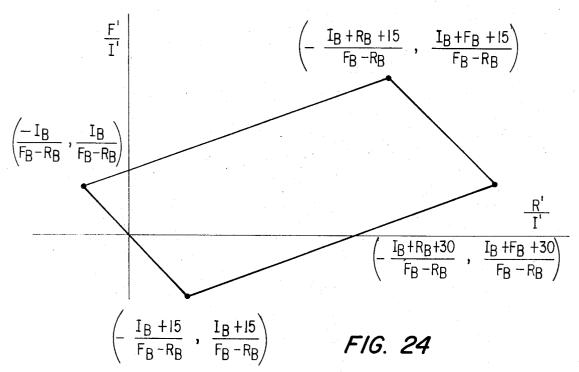

- FIG. 24 is a graphic illustration of the analysis and related parameters for same performed by the present invention.

# REFLECTIVITY OF TOBACCO LEAVES AND BACKGROUND STANDARDS

It has been ascertained that for properly cured tobacco leaves, there is a predictable difference between 5 the reflectivity of green light and red light, the red reflectivity being on the order of 20 percent greater than the green, depending upon the type of tobacco and its curing process.

This predictable difference will be varied by the 10 greenness of the leaf being monitored, thereby providing parameters that are determinative of the acceptability of a tobacco leaf according to its degree of greenness or redness, regardless of its acceptance in a given color grade based on its relative brightness.

Either the red reflectivity or the green reflectivity (or a combination thereof) of a given leaf can be utilized to effect automatic grading on the basis of relative brighness of the leaf to a background color standard.

The purpose of a standard color background is two- 20 and optical field of view into account, are as follows: fold. First, the optical means used to detect the reflectivity of the various colors is calibrated against this background; and second, in the event that a tobacco leaf passing over the standard background does not completely fill the field of view of the optics, the visible 25 portion of the background will present a known factor which can be compensated for in a computational means associated with the optical means.

Calibration is required since such components as photodetectors, light sources, and related components 30 follows: are subject to drift in their various response characteristics and require periodic recalibration to prevent er-

In regard to the size of the leaves relative to the field of view of the optical means, to bacco leaves are not al-  $^{35}$ ways large enough to fill the field of view of a given optical means and the resulting color reflection sensed by that optical means is a combination of the reflectivities of the leaf and the standrd background. However, if the color of the background is a known standard or reference, that portion of the response attributed to the plate can be compensated for to reveal the true color of the leaf being analyzed, provided that a measure of the relative contribution, to the response, of the leaf and the background can be determined.

It is a known factor of tobacco leaves that they consistently absorb the shorter wavelengths and reflect the longer wavelengths (about 80 percent reflection at 1000nM) regardless of the visual color differences of individual leaves.

Hence, it is possible to generate signals via the chosen optical means that are a measure of the size of the tobacco leaves by using a color filter to detect either the infrared or the ultraviolet light reflected from the leaf and use this as a calibration signal for the visual color measurements provided that the color of the background plate is sufficiently different from that of the leaves in one of the regions of the spectrum.

There are two parameters which are sufficient to define the visual color differences of tobacco leaves, namely, brightness-darkness (or gray scale) and greenness-redness. In practice, it has been established that a deep red filter centered at 670 nM to 700 nM in combination with an orange, yellow or green filter is sufficient to make such measurements of visual color difference. The sum of the outputs of two filterphotodetector combinations determines the brightness of the leaf and the difference of these two outputs determines the greenness-redness thereof.

It has also been established that it is advantageous to have the color of the background reference close enough in the visual region to that of the leaves being sorted such that the contribution of the background reference to the total generated signal is minimized. For example, using the colors red and green for detection and infrared for calibration is compatible with blue, green, brown, red or purple background references or a gray background reference having a reflectivity in the range of 20 to 30 percent for wavelengths from 600 nM to 1000 nM, the unit "nM" conventionally designating nanometers.

## THEORY

The mathematical relationships of the several color reflectivities from the background reference and tobacco leaves taking the proportionate size of the leaf

**Definitions**

a = proportion of field of view covered by tobacco leaf;

R = red reflectivity signal in percent;

F = green reflectivity signal in percent;

I = near infrared relfectivity signal in percent; and L and B are subscripts which denote leaf and background, respectively.

The foregoing quantities are basically interrelated as

$$R = aR_L + (1 - a) R_B$$

$$F = aF_L + (1 - a) F_B$$

$$I = aI_L + (1 - a) I_B$$

In the system of the present invention the three known reflectivity signals from the background reference  $(R_B, F_B \text{ and } I_B)$  are stored in order that these can be subtracted from the resultant reflectivities R, F and I, as follows:

$$(R - R_B) = a(R_L - R_B)$$

$(F - F_B) = a(F_L - F_B)$

$(I - I_B) = a(I_L - I_B)$

Accordingly when a = 0 (i.e., no leaf is present in the optical field of view of the present invention), all of these quantities are equal to zero. Also, as a result, any linear combination of these signals will be zero when a = 0.

To remove the effect of a, the size of the leaf relative to the field of view on the background reference, the relatively constant infrared signal component  $(I_L - I_B)$ is used as a standard, by using the well known ratio tecnhique.

Two ratios may be computed from this standard as follows:

$$a(\mathbf{R}_L - \mathbf{R}_B)/a(\mathbf{I}_L - \mathbf{I}_B) = \mathbf{R}_L - \mathbf{R}_B/\mathbf{I}_L - \mathbf{I}_B$$

and

$$a(\mathbf{F}_L - \mathbf{F}_B)/a(\mathbf{I}_L - \mathbf{I}_B) = \mathbf{F}_L - \mathbf{F}_B/\mathbf{I}_L - \mathbf{I}_B$$

To compute the color of a leaf, the following function is calculated in which the quantity m is a scalar factor either positive or negative:

$$Color = R_L - R_B/I_L - I_B + m(F_L - F_B/I_L - I_B)$$

25

By manipulation, the foregoing relationship can be expressed as:

$$color = R_L + mF_L/I_L - I_B - R_B + mF_B/I_L - I_B$$

Now, since  $(I_L - I_B)$  and  $R_B + mF_B$ ) are known constants, all of there components being known, these quantities can be removed by multiplication and subtraction leaving the quantity  $R_L + mF_L$  as the unknown to be determined as a measure of leaf color.

If this general unknown is compared to a predetermined quantity C to determine its relative magnitude, then the dividing line between acceptable or unacceptable tobacco leaves in the grading process and system of the present invention can be expressed as the equation:

$$R_L + mF_L + C = 0$$

In the present invention this dividing line is also expressed as:

$$R_L + mF_L/I_L + I_B - R_B + mF_B/I_L - I_B + b = 0$$

By manipulation, the following expression is derived:

$$R_L + mF_L - [R_B + mF_B + b(I_L - I_B)] = 0$$

where b is a scalar factor chosen such that

$$C = -[R_B + mF_B + b (I_L - I_B)]$$

Multiplying last-derived dividing line equation by the  $^{30}$  leaf size factor a, results in:

$$a (R_L + mF_L) - a [R_B + mF_B + b (I_L - I_B)] = 0$$

which, when expanded and rewritten, is as follows:

$$a (R_L - R_B) - m [a (F_L - F_B)] - b [a(I_L - I_B)] = 0$$

Therefore any appropriate acceptability dividing lines for the leaves under test can be established and the relative color of the leaves to these established dividing lines determined from a linear combination of the available optically generated signals  $(R_L - R_B)$ ,  $(F_L - F_B)$  and  $I_L - I_B)$ , the resultant signals of the combined reflectivities from the background reference and leaves for each of the chosen colors.

In the actual practice of the invention the above equation is not made equal to zero, but to a small quantity  $\pm d$ . Thus a determination is made to see if the weighted sum of the colors is greater than +d or less than -d. Exactly how small "d" is determines the gain of the system.

The equation  $r(R_L - R_B) + f(F_L - F_B) + i (I_L - I_B) = \pm d$  can be described as two parallel planes in  $(R_L - R_B)$ ,  $(F_L - F_B)$ , and  $(I_L - I_B)$  space, that are displaced from the origin by  $\pm d$ , a small quantity. Hence it can be seen that in the general case where  $R_L$ ,  $F_L$  and  $I_L$  are all variables, the three color system can accomplish separation of different colored objects by using planes at various angles and tilts. However in the case of tobacco leaves where  $I_L$  is relatively constant, it is more convenient to think in terms of two dimensions, with  $I_L$  a calibrating signal.

# BACKGROUND OF THE INVENTION

By utilizing two color response, sorting of leaves for relative brightness, greenness and/or redness can be achieved. However, in such a two color process the dappled (red) and green leaves cannot be sorted at the same time since the color of the background reference is the determining point of division for acceptable and unacceptable leaves.

Accordingly, the need for a "neutral" background reference and a means whereby the red and green divisions of acceptability could be achieved to permit automatic separation of leaves on both sides of a desired range of normality or acceptability is clearly present.

If such a capability were available in color sorting equipment, then the need for a wide range of background references and the maintenance and storage thereof would be obviated.

### SUMMARY OF THE INVENTION

By using three colors for generating response signals in the color sorting equipment of the present invention, one of these colors can be utilized to measure the size of the leaf or other object being graded in the field of view of the optical means utilized to detect the several color reflections from the background reference and a leaf or object being tested when it is positioned over that reference in the field of view of the said optical means.

A bias signal can then be developed from the third color response signal that can be used to electronically alter the appearance of the background relative to the leaf, thereby permitting the use of a neutral (single) selected background reference and electronic controls such as dials or the like for establishing desired bright/dark and green/red divisions of acceptability for the objects under test.

Basically, a light is provided which impinges upon a background reference plate over which tobacco leaves are projected by a conveyor in a ballistic path which carries the leaves through the field of view of an optics head having red, green and infrared sensing means thereon to generate signals representative of the reflected light in these selected spectral regions or wavelengths.

A control panel and associated logic module are provided to permit the latitude of acceptable and unacceptable colors of the leaves (or other objects being graded by color) to be selectively adjusted as desired, and provide commensurate control signals to the color computer to constrain it to either accept or reject the leaves being analyzed according to the control panel settings.

The color computer solves the equations discussed under Theory in the general discussion of Reflectivity Of Tobacco Leaves And Background Standards herein so that the divisions between acceptable and unacceptable leaves are determined and then compared to the colors of individual leaves to either constrain an accept or reject condition on each leaf.

The computer also stores the color of the background reference upon command from a reject timing logic means that determines when and if a leaf should be rejected in response to computer output signals indicating the results of comparison of actual leaf colors with the desired accept — reject settings of the control panel. This reject timing logic means also determines when the background reference is in view of the optics head so that this reference color can be stored in the computer and that storage can be updated for current calculations.

2,02.,200

Subject to the results determined by the color computer and associated logic, a solenoid actuated air jet is provided adjacent the ballistic path of the leaves to cause unacceptable leaves to change their ballistic paths and arrive at a reject bin or other predetermined 5 destination apart from the acceptable leaves.

Three accessary functions are also provided by the associated logic. The first is a clock that is controlled to determine how long the color grader has been grading. The second is a side blower for the background 10 plate to clean it of obstructions and dust; and the third is an alarm light to indicate when the background is properly stored in memory when it has been necessary to recalibrate while in operation.

### THE BASIC SYSTEM AND APPARATUS

With the foregoing consideration of reflectivity established, the basic system and apparatus of the present invention can best be described by reference to FIG. 1, where the grading means 10 of the present invention is 20 schematically illustrated.

Tobacco leaves T are fed sequentially over a background color standard (platen) S by means of an endless belt conveyor 12 driven by a pulley drive 12A (or by other suitable conveyor means).

Mounted above the color standard S is a light source comprising a plurality of lamps L, three detector means, namely, a red light detector RD and a green light detector FD and an infrared or near infrared detector ID, which, in a preferred embodiment comprise photodiodes DR, DF and DI with red, green and infrared filters RF, FF and IF optically coupling them, respectively, with the light from the lends A5. These filters may have suitable light gathering optics associated therewith if desired.

The optical system OH comprises a housing A1 with an enlarged telescope tube A2 extending therefrom. An objective lens A3 is mounted in the front of the telescope tube A2 facing the obverse surface of the background reference S and focuses reflected light. from the latter through an apertured plate A4, defining the field of view of the optical system OH.

A field lens A5 is positioned in the telescope tube A2, and directs the green, red and infrared light into the housing A1.

The detector means RD, FD and ID are connected via signal leads RD1, FD1 and ID1, respectively, to signal inputs 14R, 14F, and 14I of a control circuit 14, the latter generating a control signal at a control output 16, which signal is conveyed through output lead 16A to the control terminal 18A of a pneumatic reject mechanism 18

The pneumatic reject mechanism 18 includes a solenoid controlled air jet 20 which directs stream of air 20A against the underside of selected ones of the tobacco leaves T, namely, undesired or rejected ones of the leaves T to contstrain upon the latter a trajectory TR which, when leaving the background standard S, is predictably different from the trajectory TA taken by acceptable ones of the leaves T which are of the grade desired.

The trajectories TA and TR carry the leaves T into a pair of receiving bins BA and BR, or conveyor belts, respectively for acceptable and rejected ones of the leaves T.

As further shown in FIG. 1, the pneumatic reject mechanism has a pressure input 18B which is con-

8

nected to a pneumatic source 22 to provide the pressurized air for the jet 20.

The light source L is positioned to illuminate the background reference S and any leaf T thereon and cause reflection of that light back to the optical system OH.

In basic operation, which will be hereinafter more fully described, those leaves T which are within the color limit set within to control circuit 14 are permitted to fall from the background reference S and assume the acceptable trajectory TA into the acceptable grade bin RA

When a leaf T is of a color external of the preset limit, this difference is detected by the detectors RD, 15 FD and ID and a resulting control signal is generated in the control circuit 14, and thence transmitted through the control output 16, control lead 16A and input terminal 18A to energize the pneumatic reject mechanism 18 before that particular leaf T leaves the 20 platen shaped background reference S.

Accordingly, an upwardly directed stream of air 20A is emitted from the jet 20 and lifts the rejected (undesirable) leaf T to constrain it into the reject trajectory TR and into the reject bin BR, effecting a selective grading of the tobacco leaves T.

As will be hereinafter more fully described, the duration of the airstream 20A is timed such that it will not interfere with the trajectory of the next successive leaf T unless the latter is not within the preset color limits for acceptable leaves.

The color filters RF, FF and IF are centered, respectively, at 540nM(green), 670nM(red) and 900nM (infrared) in a preferred embodiment of the invention.

# THE CONTROL PANEL

Referring now to FIG. 2, a control panel 30 for selecting the division between acceptable and unacceptable leaves is shown as divided into six quality zones by a BRIGHT-DARK divider line with a transverse GREEN line and a transverse RED line thereacross.

These quality zones are labelled as follows:

|    | BRIGHT (Not Red — Not Green) | Z2         |

|----|------------------------------|------------|

| .5 | DARK (Not Red — Not Green)   | Z5         |

|    | BRIGHT-RED                   | Z3         |

|    | DARK-RED                     | <b>Z</b> 6 |

|    | BRIGHT-GREEN                 | Zi         |

|    | DARK-GREEN                   | 7.4        |

In each zone is a toggle switch TS which has a RE-JECT position and a KEEP position. As will be more fully described hereinafter, the KEEP position constrains the color sorter 10 to accept leaves qualifying for a correlated quality zone and the reject position constrains a rejection of leaves qualifying for that zone.

From the previous discussion of the theory of threecolor sorting it can be readily seen that the color function to be calculated by the control circuit 14 (FIG. 1) is of the form rR + fF + iI, where R, F and I are the red, green and infrared color signals and r, f and i are scalar factors which are to be established depending upon the desired division between quality zones, such that the toggle switches TS can be thrown to constrain predetermined acceptance and rejection of leaves by the sorter 10.

When the color function is zero, then the only thing in the field of view of the optics OH is the background reference S. If this color function is positive or negative then there is an object (leaf) in the field of view that is below or above the preset color, i.e., in the various BRIGHT or DARK quality zones, respectively, with these zones being defined by predetermined selection of the scalar factors r, f and i.

Thus, the BRIGHT-DARK, GREEN and RED lines on the control panel 30 simulate a graph of relative color qualities which graph will be more fully defined hereinafter with reference to FIGS. 8, 9 and 10. When 10 dividing lines between the various color zones are established, the control panel 30 via the toggle switches TS, determines which quality zones (ranges) of colors in a given leaf will be accepted or rejected by the sorter 10.

The quality zones Z1–Z6 are established prior to sorting by means of five (5) scalar factor thumbwheel switches ZBD, ZBG, ZDG, ZBR and ZDR which select the division lines between the various color zones.

The scalar factor switch ZBD sets the division be- 20 tween the BRIGHT and DARK zones; the scalar factor switches ZBG and ZDG in the BRIGHT-GREEN and DARK-GREEN zones set the accept-reject tolerance to light and dark green leaves, i.e., tilt the BRIGHT-DARK and GREEN division lines relative to one an- 25 other, mathematically, to enlarge or reduce the range of greens in a given one of the "green" zones as well as setting the degree of greenness accepted; and the scalar factor switches ZBR and ZDR in the BRIGHT-RED and DARK-RED zones set the accept-reject tolerance 30 to light and dark red leaves, i.e., tilt the BRIGHT-DARK and RED division lines relative to one another, mathematically, to enlarge or reduce the range of reds in a given one of the "red" zones as well as determine the degree of redness acceptable.

Each of the scalar factor switches comprise, for example, sixteen-position thumbwheel switches which impose input constraints on compatible logic circuitry, the latter controlling the relative durations of the red, green and infrared signals R, F and I in a given sensing cycle such that when these signals are integrated, the resulting magnitudes will be proportionately modified or modulated by the desired scalar factors to provide color parameters for comparison with the preset quality zone divisions by a color computer 40, see FIG. 3.

The accept-reject function of the sorter 10 is controlled by the correlation between the comparison of a leaf color parameter as being above or below the desired division line in magnitude (i.e. a positive or negative comparison) and the positions of the toggle switches TS, which, referring to FIG. 3, are shown as controlling an accept-reject logic module 50, the latter serving to update the quality division line data in the color computer module 40 through a programming lead PL.

Referring to FIG. 4A, the optics head OH is shown as including the red, green and infrared filters RF, FF and IF with the photodiodes or phototransistors DR, DF and DI respectively associated therewith, together with field effect transistors Q1, Q2 and Q3 connected, respectively, with their control terminals connected at the respective anodes of the said diodes and with another electrode in common connection with a positive bias, for example +6V, and the cathode of the said diodes. The other electrodes of the said transistors Q1, Q2 and Q3 are connected, respectively, to the positive

inputs of operational amplifiers Q4, Q5, and Q6 in the color computer 40 via coupling resistors RA1, RA2 and RA3, respectively, as well as through biasing resistors BR1, BR2 and BR3 to a source of negative bias, shown for example, as -6V.

The anodes of the photodiodes DR, DF and DI are respectively connected through load resistors R1, R3 and R5 to the variable taps of trimming resistors R2, R4 and R6 which serve to adjust the response characteristics of the said photodiodes to the incident filtered light impinging thereon through the respective filters RF, FF and IF.

The trimming resistors R2, R4 and R6 have one end thereof connected to ground and their opposite ends connected, respectively, to the outputs RS, FS and IS of the operational amplifiers Q4, Q5 and Q6. The designations RS, FS and IS indicate that the red signal (R), green signal (F) and infrared signal (I) of the function to be solved by the color computer 40 appear at these respective outputs of the operational amplifiers Q4, Q5 and Q6.

The trimming resistors R2, R4 and R6 thus provide a means for adjusting the amplitudes of the color signal outputs RS, FS and IS of the operational amplifiers Q4, Q5 and Q6. In practice R2, R4, and R6 are adjusted so that a voltage swing of six volts will result when the reflectance signal is made to change from 100% to 0%. This calibrates each color detector and insures uniform grading from one head to another.

The positive inputs of the operational amplifiers Q4, Q5, and Q6 are respectively connected to the junction of CA1 and RA1, CA2 and RA2, and CA3 and RA3. These resistor-capacitor combinations limit the bandwidth of the photo detectors to that required to track the leaves as they pass under the heads; this extra feedback also maintains the output impedance of Q4, Q5, and Q6 at a low value.

RA1, RA2, and RA3 are respectively connected to the negative bias source (-6V) through bias resistors BR1, BR2 and BR3 and are further respectively connected to one of the electrodes of field effect transistors Q7, Q8 and Q9. The other of the electrodes of these transistors Q7, Q8 and Q9 are connected to the source of positive bias (+6V) which in the preferred embodiment of the invention is symmetrical with the negative bias (-6V).

The control electrodes of the transistors Q7, Q8 and Q9 are respectively connected to ground through reference capacitors C6, C7 and C8 and selectively, through switch means SE1, SE2 and SE3, respectively, to a common circuit lead CL1 on the opposite sides of the said switch means.

This interconnection of the operational amplifiers Q4, Q5 and Q6 with the photodiodes DR, DF and DI results in the maintenance of a constant voltage at the junctions between the anodes of the said photodiodes and their respectively associated load resistors R1, R3 and R5, whereby the voltages at the outputs RS, FS and IS correspond to the respective amounts of filtered light impinging upon the said diodes.

Further, the power dissipated in the field effect transistors Q1, Q2 and Q3 is maintained constant, thereby keeping the voltage constant across the respectively associated photodiodes DR, DF and DI, whereby linearity is maintained over a wide range of magnitudes of light incident upon the said photodiodes and "thermal memory" effects are avoided.

The red, green and infrared signal outputs RS, FS and IS are connected, respectively, through selectively actuated switch means SA1, SA2 and SA3 to a second common circuit lead CL2 which serves as a common input to an integrator circuit 40A including an operational amplifier Q10 having input resistors R6 and R7 connected at one end, respectively, with the negative and positive inputs of the said amplifier Q10.

The other end of the negative terminal load resistor R6 is selectively connected to the second common lead 10 the input 40BA of a comparator circuit 40B. CL2 or to the ground by means of a ganged pair of switch means SB1 and SB2, respectively, operating to assume opposite open and closed states one from the other.

The other end of the positive terminal load resistor 15 R7 is selectively connected to the second common lead CL2 or to the ground by means of a ganged pair of switch means SB3 and SB4, respectively, operating to assume opposite open and closed states one from the

The negative input terminal of the integrator amplifier Q10 is directly connected through a feedback resistor R10 to the amplifier output 40AS, that feedback resistor R10 being selectively by-passed through the integration capacitor C5 via a selectively actuated switch 25 means SD2 in series between amplifier output 40AS and one side of the said capacitor C5, that side of the capacitor C5 being directly connected to a third common circuit lead CL3.

The other side of the said capacitor C5 is connected 30 to the negative input terminal of the integrator amplifier Q10 and a selectively activated switch means SD1 is connected across the said capacitor C5 to connect the said negative input terminal either directly to the third common circuit lead CL3 or through the said capacitor C5 to the said third common circuit lead CL3.

The selective switch means SD2 serves to directly connect the amplifier output 40AS to the said third common circuit lead CL3 in its closed state.

First, second and third storage capacitors C1, C2, and C3 are connected on one side to a common node SCN and on the other sides thereof, respectively, through selectively activated storage control switch means SC1, SC2 and SC3 to the third common circuit lead CL3. The common node SCN is connected through a reference resistor R8 to the common connection SCNA between the positive terminal input resistor R7 and the ganged switch pair SB3, SB4 which serve, respectively, to selectively connect one side of the said reference resistor R8 to either the second common circuit lead CL2 or to ground.

A fourth storage capacitor C4 is selectively connected to the third circuit lead CL3 through a fourth storage control switch means SC4 on one side thereof and on the other side thereof through a reference resistance R9 and the common connection SCNA to either the second common circuit lead CL2 or ground via the said ganged switch pair SB3, SB4.

The integrator amplifier ouput 40AS is further connected through a selectively activated switch means SD3 to a circuit node CNB, the latter being connected to ground through a capacitor C9 to form a sample and hold circuit and to another circuit node CNC through a resistor R11, the latter circuit node being connected to ground through the reverse direction of a clamping diode DA.

The node CNC is connected to the first common circuit lead CL1 either directly through a selectively activated switch means SD4 or through a reference resistor R12, the latter being selectively shunted by the said switch means SD4 to implement the FAST RESET function of the color grader as will be more fully described hereinafter.

A final connection of the output 40AS of the integrator amplifier Q10 is through a coupling resistor R13 to

The comparator circuit 40B comprises an input stage having two NPN transistors Q11 and Q12 with their bases commonly connected to the comparator input 40BA; their emitters commonly connected to ground; and their collectors 42 and 44 connected, respectively, directly to the bases of output transistors Q13 and Q14.

The first output transistor Q13 is of the PNP type while the second output transistor Q14 is of the NPN 20 type.

The collector 42 of the first input transistor Q11 and the base of the first output transistor Q13 are connected through a coupling resistor R14 to the emitter 46 of the first output transistor Q13 and the source of positive bias (+6V).

The collector 44 of the second input transistor Q12 and the base of the second output transistor Q14 are connected through resistor R15 to the source of negative bias (-6V) and the collector 48 of the first output transistor Q13 is connected through a resistor R16 to the source of negative bias (-6V), with the said collector 48 comprising a positive comparison output 40BS1 of the comparator 40B.

The collector 50 of the second output transistor Q14 comprises a negative comparison output 40BS2 of the comparator 40B and is connected through a biasing resistor R17 to a positive bias source which for example, is shown as +6V. The emitter 52 of the second output transistor Q14 is directly connected to a source of negative bias, symmetrical with the positive bias, which is shown, therefore as -6V.

The comparator outputs 40BS1 and 40BS2 comprise the data inputs of first and second 3-bit shift registers ST1 and ST2 which store, respectively, the positive and negative signals on the comparator outputs 40BS1 and 40BS2. Each of these shift registers has a central clock to be hereinafter more fully described.

The 3-bit outputs ST1A and ST2A of the first and second shift registers ST1 and ST2 drive 3-bit data inputs ST3A and ST3B, respectively, of an 8-bit shift register ST3, the latter having a 3-bit control output ST3C. a serial data output ST3D, a serial data input ST3E, a load pulse input ST3F and a shift clock input ST3G.

The serial data output terminal ST3D is connected through a data transfer register ST4 to the first data input RSL1 of a reject selection logic module RSL, the latter having a second data input RSL2 from the six toggle switches TS on the front control panel 30 and an output terminal RSL3 which drives the main data input CPU1 of a central processing input CPU.

The central processing unit or computer CPU includes a logic array LA into which the main data input CPU1 feeds. The logic array LA also includes in and out terminals LA1 and LA2, respectively, which effect recirculation of data into and out of a serial memory SM which stores the state of the logic array LA subsequent to the receipt of data from the reject selection logic module RSL. A clock input LA3 is provided the logic array LA from the output PC1 of a program clock PC. The data output terminal LA4 of the logic array LA comprises the output CPU2 of the computer CPU and is connected through an output data transfer register ST5 to the serial data input ST3E of the 8-bit shift register ST3.

The program clock PC has a load pulse output PC2 directly connected to the load pulse control input ST3F of the 8-bit shift register ST3; a shift clock output PC3 10 directly connected to the shift clock control input ST3G of the 8-bit shift register ST3; and an operate pulse output PC4 directly connected to the control inputs UL1 and RL1 of an update logic module UL and a reject logic module RL, respectively.

The update logic module UL and the reject logic module RL have 3-bit data input terminals UL2 and RL2, respectively, connected to the 3-bit control output ST3C of the 8-bit shift register ST3 and further include respective control outputs UL3 and RL3.

The 3-bit control outputs \$T3C of the 8-bit shift register \$T3 comprise the general control output 16 of the general control circuit 14 and are connected directly to the input leads 16A of the solenoid driver circuit 18.

# FRONT PANEL LOGIC BOARD FOR CODING THUMBWHEEL SWITCHES ZBG, ZDG, ZBD, ZBR AND ZDR

Referring to FIG. 5, a preferred embodiment of logic board FPLB for encoding the quality zone setting thumbwheel switches ZBG, ZDG, ZBD, ZBR and ZDR on the front control panel 30 and generating the resulting sequencing signals for the control switches SA1—SA3, SC1—SC4, SD1, SD2, SB3 (SB4), SB1 (SB2), 35 and SE1—SE4 will now be described.

In all of the following descriptions all modular components are commercially available types and are listed in Appendix I. Further, all commercially available modules are presented in the drawings with conventional terminal pin numbers such that when interconnected as shown and described will result in the performance of the functions to be defined hereinafter.

The load pulse from the output PC2 of the program clock PC (see FIG. 4B), is applied to the clock input 45 terminal ZL of the control panel board FPLB and thence into the No. 5 terminal of a sample and hold type phase comparator Y1 (CD4016AE module of RCA), the latter having its No. 3 terminal connected with the No. 3 terminal of a voltage controlled oscillator Y2 (CD4007AE of RCA) as well as through a coupling capacitor C10 to the source of negative bias (-6V), and its No. 4 terminal connected to a circuit lead ZL1 through a resistor R20 and the negative bias source (-6V) through a coupling capacitor C11. The load pulse input ZL is connected to the negative bias source (-6V) through a resistor R21.

The No. 4, No. 6 and No. 12 terminals of the oscillator Y2 are connected through a resistor R22 to a node Y2A, the latter being connected to the No. 10 and No. 5 terminals of the oscillator Y2 through resistors R23 and R24, respectively. The node Y2A is connected through a coupling capacitor C12 to the oscillator output Y2B, the latter being directly connected to the No. 8 and No. 13 terminals of the oscillator Y2 and to the No. 1 terminal comprising an input Y3A of a seven-bit counter circuit Y3 (CD4024AE module of RCA).

The No. 2 terminal of the seven-bit counter Y3 is connected to the source of negative bias (-6V). The No. 12, No. 11, No. 9, No. 6, No. 5, No. 4 and No. 3 terminals of the counter Y3 correspond to the 1st through seventh bits, in that order, counted by Y3, with the carry signal from the counter Y3 exiting at its No. 3 terminal, the latter being connected to the No. 13 terminal of a five-bit counter Y4 (CD4022AE module of RCA), the No. 14 terminal of the counter Y4 being connected to the source of positive bias (+6V).

The 7-bit counter Y3 subdivides each of the color computation periods by controlling the sequencing of the various switches in the input circuit A and color computer 40 as will be hereinafter more fully described.

The count of 4 counter Y4 has its No. 2, No. 1, No. 3, No. 7 and No. 11 terminals corresponding to the first through fifth counts (0, 1, 2, 3, 4) in that order, with the No. 11 terminal connected to the No. 15 terminal to reset the counter Y4 and the No. 7 terminal of the latter is connected to the input Y5A (No. 13 terminal) of a second count of four counter Y5 (CD4022AE module of RCA), the latter having its No. 14 terminal 25 pin connected to the source of positive bias (+6V).

The first count of 4 counter Y4 serves to sequence the selector switch means SA1, SA2 and SA3 and SD1 in the color computer 40 while the second count of 4 counter serves to sequence the storage selector or sampling switch means SC1, SC2, SC3 and SC4 in the color computer 40.

As in the first count of 4 counter Y4, the No. 2, No. 1, No. 3, No. 7 and No. 11 terminals of the second counter Y5 correspond to the first through fifth counts (0, 1, 2, 3, 4), in that order, with the No. 11 terminal connected to the No. 15 terminal to reset the said counter Y5.

The No. 2 terminal of the second count of 4 counter Y5 is connected to the input Y6A (No. 11 terminal) of phase counting flip-flop Y6 (CD4013AE module of RCA) and, the No. 7 terminal of the second 5-bit counter Y5 is connected to the input Y7A (No, 14 terminal) of a count of 3 update switch selection counter Y7 (CD4022AE module of RCA).

The phase counting flip-flop Y6 has its No. 8 and No. 10 terminals connected to the source of negative bias (-6V), its No. 13 terminal providing a first half cycle signal output Y6B and its No. 9 and No. 12 terminals providing a second half cycle signal output Y6C. These two outputs Y6B and Y6C serve as control inputs for sequencing the storage sampling switches SC1, SC2, SC3, SC4, the zero switch SD1, the main sampling switch SD2 and the selector switches SB3 (SB4) and SB1 (SB2) which control the scalar factor values in the color computations as will be more fully described hereinafter.

The count of 3 counter Y7, designated also as the update selection counter, ultimately controls the sequencing of the update selector switches SE1, SE2 and SE3 to thereby control the application of updated background reference voltages to the reference capacitors C1, C2 and C3 in the optics input circuitry A previously described in FIG. 4. This sequencing is correlated with the sequencing of the color selector switches SA1, SA2 and SA3 and the sample switch SD2 as will become more readily apparent hereinafter.

The No. 13 terminal of the counter Y7 is connected to the control output SSD2 of the sample switch SD2 by a lead Y7B.

15

The No. 2, No. 1, No. 3 and No. 7 terminals of the (update selection) counter Y7 correspond to the first 5 through fourth counts (0, 1, 2, 3) in that order, of the said counter Y7, with the No. 7 terminal connected to the No. 15 terminal to reset the said counter.

The No. 2 terminal of the update selection counter Y7 comprises the control output SSE3 for the update switch SE3; the No. 1 terminal comprises the control output SSE1 for the update switch SE1; and the No. 3 terminal comprises the control output SSE2 for the update switch SE2. (SC3), (SC4), Y6C and Y6B are provided by either direct or combined connections of the outputs counters Y3, Y4, Y5 and Y6 as follows:

1. The control line (S1) commences at the output (No. 10 terminal) of a NOR gate Y12 (CD4025 AE module of RCA) connected as an inverter by

The No. 2, No. 1 and No. 3 terminals of the update 15 selection counter Y7 are connected, respectively, to the No. 3, No. 5 and No. 7 terminals of a color switch selector Y9 (CD4019AE logic module of RCA) to serve as part of the sequencing data for the color switches SA1, SA2 and SA3 as correlated with the up-20 date switches SE1 — SE3.

The No. 2, No. 4 and No. 6 terminal pins of the color switch selector Y9 are directly connected with the No. 2, No. 1 and No. 3 terminals, respectively, of the first counter Y4 to provide the primary sequencing information for the color switches SA1, SA2 and SA3 through the leads containing the switch designations in parantheses, (SA1), (SA2), etc. The No. 7 terminal of the said counter Y4 is connected through the lead (SD1) to the No. 13 terminal of a NOR gate Y10 (CD4001AE module of RCA) the output thereof comprising a No. 11 terminal which drives the No. 2 terminal of a like NOR gate Y11 as well as the No. 9 terminal of the color switch selector Y9.

The No. 12 terminal comprising the other input of <sup>35</sup> the NOR gate Y10 is driven through the lead (SC4) from the No. 7 terminal of the second counter Y5.

The No. 1 terminal comprising the other input of the NOR gate Y11 is driven through the lead (SD1) from the No. 3 terminal of the first counter Y4 and the output (No. 3 terminal) of the NOR gate Y11 drives the No. 14 terminal of the color switch selector Y9.

Thus, the switches in the SA, SC, SD and SE series are seen to be interrelated in their respective sequences.

The control terminals, SSA1—SSA3, SSC1—SSC4, SSD1, SSD2, SSB3 and SSB1 for the various sequenced switches are selectively gated ON or OFF by flip-flops (CD4013AE modules of RCA) as follows:

- 1. SSA1 is the NO. 1 terminal of a flip-flop FFA1;

- 2. SSA2 is the No. 13 terminal of a flip-flop FFA2;

- 3. 1 SSA3 is the No. 1 terminal of a flip-flop FFA3;

- 4. SSC1 is the No. 12 terminal of a flip-flop FFC1;

- 5. SSC2 is the No. 2 terminal of a flip-flop FFC2;

- 6. SSC3 is the No. 12 terminal of a flip-flop FFC3;

- 7. SSC4 is the No. 2 terminal of a flip-flop FFC4;

- 8. SSD1 is the No. 12 terminal of a flip-flop FFD1; 60

- 6. GODT is the 140. 12 terminal of a impriop 11 D1,

- 9. SSD2 is the No. 1 terminal of a flip-flop FFD2;10. SSB3 (B4) is the No. 1 terminal of a flip-flop FFB3; and

- 11. SSB1 (B2) is the No. 12 terminal of a flip-flop 65 FFB1.

The counters Y3, Y4, Y5, Y6 and Y7 comprise a sequence control clock for the selector switches SA1 —

SA3, SC1 — SC4, SD2, SB1 (B2), SB3 (B4) and SE1 — SE3.

In order to complete the controlling input connections to the control terminals (like designations with the prefix S) of these switches, with the exception of the terminals SSE3 — SSE4 driven directly from the update selection counter Y7, signal lines (S1), (S2), (S3), (SA1), (SA2), (SA3), (SD1), (SC1), (SC2), (SC3), (SC4), Y6C and Y6B are provided by either direct or combined connections of the outputs of the counters Y3, Y4, Y5 and Y6 as follows:

- 1. The control line (S1) commences at the output (No. 10 terminal) of a NOR gate Y12 (CD4025 AE module of RCA) connected as an inverter by a common connection of its No. 11, No. 12 and No. 13 terminals to the No. 12 terminal (No. 1 bit) of the 7-bit counter Y3;

- 2. The control line (S2) commences at the output (No. 6 terminal) of a NOR gate Y13 (CD4025AE module of RCA) connected as an inverter by a common connection of its No. 3, No. 4 and No. 5 terminals to the No. 11 terminal (No. 2 bit) of the 7-bit counter Y3;

- 3. The control line (S3) commences at the output (No. 9 terminal) of a NOR gate Y14 (CD4025AE module of RCA) having its No. 1, No. 2 and No. 8 input terminals connected, respectively, to the No. 5 (No. 5 bit), No. 4 (No. 6 bit) and No. 3 (No. 7 bit) terminals, respectively, of the 7-bit counter Y3:

- 4. The control lines (SA1) (SA3) have previously been defined as extending from the No. 2, No. 1, No. 3 terminals (No. 0, No. 1 and No. 2 counts) of the first counter Y4 to the No. 2, No. 4 and No. 6 terminals, respectively of the color selector module Y9:

- 5. The control line (SD1) commences at the No. 7 terminal (No. 3 count) of the first counter Y4 and extends to the No. 13 terminal of the NOR gate Y10 and ultimately drives the No. 9 terminal of the color selector Y9; and

- 6. The control lines (SC1), (SC2), (SC3), (SC4) originate at the No. 2, No. 1, No. 3 and No. 7 terminals (No. 0, No. 1, No. 2 and No. 3 counts) of the second counter Y5, which sequences the calculations being performed in the color computer 40, and extend to various inputs and gates associated with the sequenced switch controlling flip-flops FFA1-A3, FFC1-C4 FFD1-D2, FFB1 and FFB 3 as will now be described.

The control line (SD1) is connected to the No. 1 terminal of the NOR gate Y11; the No. 9 terminal of an EXCLUSIVE OR gate Y15 (CD4030 AE module of RCA); the No. 1 terminal of a NAND gate Y16 (CD4011 AE module of RCA); the No. 13 terminal of a like NAND gate Y17; and the No. 1 terminal of a NOR GATE Y18 (CD4001 AE module of RCA). Thus, the control line (SD1) carries sequencing signals for all of the switch control flip-flops FFA1 – A3, FFC1 – C4, FFD1 – D2, FFB1 and FFB3 as will become more fully apparent hereinafter.

As previously disclosed, the calculations are performed once in each half cycle in the color computer 40 to compensate for ripple and for offset in the integrator amplifier Q10 (FIG. 4). Accordingly, part of the required sequencing signals involve the generation of a 1st half cycle and second half cycle pulse from the

16

40

phase counter Y6 on the control lines Y6B and Y6C, respectively.

The other input to the EXCLUSIVE OR gate Y15 is the control line Y6B connected to the No. 8 terminal of the said gate Y15, the output (No. 10 terminal) 5 (SD1) inf thereof being commonly connected to the No. 2, No. 5, No. 12 and No. 9 terminals (inputs) of NAND gates Y19, Y20, Y21 and Y22, respectively. The control lines (SC1), (SC2), (SC3) and (SC4), respectively, drive the remaining inputs (No. 1, No. 6, No. 13 and No. 8 terminals) respectively, of the said NAND gates Y19, Y20, Y21, and Y22 (all of which are CD4011 AE modules of RCA).

The outputs (No. 3, No. 4, No. 11 and No. 10 terminals) of the respective NAND gates Y19 – Y22 drive, 15 respectively, the input terminals No. 9, No. 5, No. 9 and No. 5 of the switch controlling flip-flops FFC1, FFC2, FFC3 and FFC4.

The control line S2 is commonly connected to the other input terminals No. 11, No. 3, No. 11 and No. 3 20 of the said flip-flops FFC1, FFC2, FFC3 and FFC4, respectively, as well as to the input terminals No. 11 and No. 3 of the control flip-flops FFD1 and FFD2, respectively.

The remaining control flip-flops FFA1, FFA2, FFA3, 25 FFB3 and FFB1 have terminals No. 3, No. 11, No. 3, No. 3 and No. 11, respectively, connected in common to the control line (S1).

The control line (S3) is connected to the No. 8 and No. 9 terminals of a NOR gate Y23 (CD4001 AE module of RCA) which is thus wired as an inverter with its No. 10 terminal (output) constituting a control line  $(\overline{S3})$ .

The control flip-flop FFD1 (for the zero switch SD1) has the control line (S2) driving one input (No. 11 terminal) and the output (No. 3 terminal) of the NAND gate Y16 driving another imput (No. 9 terminal). The No. 1 and No. 2 terminals (inputs) of the NAND gate Y16 are driven by the control lines (SD1) and  $(\overline{S3})$ , respectively.

The control flip-flop FFD2 (for the sample switch SD2) has the control line (S2) driving one input (No. 3 terminal) and the output (No. 11 terminal) of the NAND gate Y17 driving another input (No. 5 terminal)

The NAND gate Y17 is driven at one input (No. 13 terminal) by the control line (SD1) and at its other input (No. 12 terminal) by the output (No. 4 terminal) of a NOR gate Y24 (CD4001 AE module of RCA), the latter being driven at one input (No. 5 terminal) by the first half cycle control line Y6B and at the other input (No. 6 terminal) by the control line (S3). The input Y7B (No. 13 terminal) of the update selection counter Y7 is connected to the sample switch control output SSD2 (No. 1 terminal) of the control flip-flop FFD2 to correlate the updating function with the sampling function in the color computer 40.

Additional control lines (SB1) 8nd (SB3) for the ganged control switches SB1 – SB2 and SB3 – SB4, respectively, originate from the carry-out (No. 14 terminals) terminals of 4-bit adders Y25 and Y26, respectively (CD4008 AE modules of RCA).

The control flip-flop FFB2 has one input (No. 3 terminal) driven by the control line (S1) and another input (No. 5 terminal) driven by the output (No. 11 terminal) of an EXCLUSIVE OR gate Y27 (CD4030 AE module of RCA), the latter having two inputs (No.

12 and No. 13 terminals) driven, respectively, by the output (No. 11 terminal) of a NOR gate Y28 (CD4001 AE module of RCA) and the output (No. 3 terminal) of the NOR gate Y18. Thus, the control lines Y6C and (SD1) influence the flip-flop FFB3 via the NOR gate Y18 and the control lines (SC4) and (SB3) influence the flip-flop FFB3 via the NOR gate Y28 since these latter control lines are connected, respectively, to the inputs (No. 12 and No. 13 terminals) of the said NOR gate Y28.

The control flip-flop FFB2 has one input (No. 11 terminal) driven by the control line (S1) and another input (No. 9 terminal) driven by the output (No. 3 terminal) of an EXCLUSIVE OR gate Y29 (CD4030 AE module of RCA), the latter having two inputs (No. 1 and No. 2 terminals) driven, respectively, by the output (No. 3 terminal) of the NOR gate Y18 and the control line (SB1). Thus, the control flip-flop FFB1 is influenced by the control lines (SD1) and Y6C via the NOR gate Y18 and EXCLUSIVE OR gate Y29, as well as by the control line (SB1) via the EXCLUSIVE OR gate Y29 and the control line (S1) by direct connection at the No. 11 terminal of the control flip-flop FFB1.

In the sequencing operation, the EXCLUSIVE OR gates Y27 and Y29 serve to reverse the logic between the first and second half cycles to permit the dual calculation in the color computer 40 to be more fully described in reference to the operation of FIG. 4.

To complete the logic interconnection of the several control flip-flops, all of the set and reset terminals thereof are connected to a common lead FFV which is connected to the source of negative bias (-6V).

The set and reset and output terminal Nos. of each of the said flip-flops are as follows:

Output Designation

| 0 | Control<br>Flip-Flop | <b>Curpu</b>       |   | Reset<br>Terminal<br>No. |

|---|----------------------|--------------------|---|--------------------------|

| _ | FFA1                 | SSA1 (No. 1)       | 6 | 4                        |

|   | FFA2                 | SSA2 (No. 13)      | 8 | 10                       |

|   | FFA3                 | SSA3 (No. 1)       | 6 | 4                        |

|   | FFC1                 | SSC1 (No. 12)      | 8 | 10                       |

|   | FFC2                 | SSC2 (No. 2)       | 6 | 4                        |

| 5 | FFC3                 | SSC3 (No. 12)      | 8 | 10                       |

|   | FFC4                 | SSC4 (No. 2)       | 6 | 4                        |

|   | FFD1                 | SSD1 (No. 12)      | 8 | 10                       |

|   | FFD2                 | SSD2 (No. 1)       | 6 | 4                        |

|   | FFB3                 | SSB3 (B4) (No. 1)  | 6 | 4                        |

|   | FFB1                 | SSB1 (B2) (No. 12) | 8 | 10                       |

The front panel quality zone selector switches ZDR, ZDG, ZBR, ZBG and ZBD (Interswitch BB239/s Hexadecimal Switches with two commons) are all driven through suitable logic circuitry from the control lines (SA1-A3), (SD1), (SC1-C4) and in turn, drive the group of adders including the adders Y25 and Y26 to determine the sign and magnitude of the various scalar multipliers previously set forth in the Theory discussion.

There are five adders, manely Y25, Y26, Y30, Y31 and Y32 (all comprising CD4008AE modules of RCA) which are additionally driven by the outputs of the 7-bit counter Y3 such that the periods of closure of the color switch means SB1, SB2, SB3 and SB4 will be as required for the three scalar factors involved in each color calculation.

The quality zone switch inputs are as follows:

The dark-red zone switch ZDR has its No. 7 terminal connected in common with the No. 4 terminal of the bright-red zone switch ZBR, the No. 7 terminal of the latter being connected in common with the source of positive bias (+6V) together with the No. 4 terminal of 5 the bright-green zone switch ZBG and the No. 7 terminal of the bright-dark zone switch ZBD.

The No. 4 terminal of the dark-green zone switch ZDG is connected in common with the No. 7 terminal of the bright-green zone switch ZBG.

The No. 4 terminal of the dark-red switch ZDR is driven from the output (No. 10 terminal) of a NAND gate Y33 (CD4011AE module of RCA), the latter having its inputs (No. 8 and No. 9 terminals) driven by the control lines (SA3) and (SC3), respectively.

The dark-green zone switch ZDG has its No. 7 terminal driven by the output (No. 4 terminal) of the like NAND gate Y34, the latter having its inputs (No. 5 and No. 6 terminals) driven by the control lines (SA3) and (SC2), respectively.

The bright-red zone switch ZBR has its No. 4 terminal (as well as the No. 7 terminal of ZDR) driven by the output (No. 3 terminal) of a NAND gate Y35 (CD4011 AE module of RCA), the latter having its inputs (No. 1 and No. 2 terminals) driven by the control line (SC3) 25 and the output (No. 3 terminal) of a NOR gate Y36 (CD4001 AE module of RCA), respectively, the latter having its inputs (No. 5 and No. 6 terminals) driven, respectively, by the control lines (SD1) and (SA3).

The bright-green zone switch ZBG has its No. 7 ter- 30 minal (as well as the No. 4 terminal of the zone switch ZDG) driven by the otput (No. 11 terminal) of a NAND gate Y37 (CD4011 AE module of RCA), the latter having its inputs (No. 12 and No. 13 terminals) driven by the output (No. 4 terminal) of the NOR gate Y36 and the control line (SC2), respectively. Thus, the zone switch ZBG is driven by the control lines (SA3) or (SD1) via the NOR gate Y36 and the control line (SD2), all routed through the said NAND gate Y37.

The bright-dark zone switch ZBD is driven at its No. <sup>40</sup> 4 terminal by the output (No. 4 terminal) of a NAND gate Y38 having its inputs (No. 5 and No. 6 terminals) driven, respectively, by control lines (SA3) and (SC1), respectively.

All of the zone switches ZDR, ZDG, ZBR, ZBG and <sup>45</sup> ZBD drive inputs of the adder Y30 as follows:

The No. 5 terminal of zone switch ZDR and the No. 5 terminal of zone switch ZDG drive the No. 9 and No. 8 terminals (inputs), respectively, of a NAND gate Y39 (CD4011 AE module of RCA), having its output (No. 10 terminal) connected to the No. 7 terminal of the adder Y30.

The No. 8 terminals of the zone switches ZDR and ZDG drive, respectively, the No. 5 and No. 6 terminals (inputs) of a like NAND gate Y40, having its output (No. 4 terminal) connected to the No. 5 terminal of the adder Y30.

The No. 6 terminals of the zone switches ZDR and ZDG drive, respectively, the No. 13 and No. 12 terminals (inputs) of a like NAND gate Y41 having its output (No. 11 terminal) connected to the No. 3 terminal of the adder Y30.

The No. 9 terminals of the zone switches ZDR and ZDG drive, respectively, the No. 1 and No. 2 terminals of a like NAND gate Y42, having its output (No. 4 terminal) connected to the No. 1 terminal of the adder Y30.

The zone switches ZBR, ZBG and ZBD have their No. 5 terminals driving, respectively, the No. 13, No. 11 and No. 12 terminals (inputs) of a NAND gate Y43 (CD4023 AE module of RCA), having its output (No. 10 terminal) connected to the No. 6 terminal of the adder Y30.

The No. 8 terminals of the zone switches ZBR, ZBG and ZBD drive, respectively, the No. 3, No. 4 and No. 8 terminals of a like NAND gate Y44, having its output (No. 9 terminal) connected to the No. 4 terminal of the adder Y30.

The No. 6 terminals of the zone switches ZBR, ZBG and ZBD drive, respectively, the No. 3, No. 4 and No. 5 terminals (inputs) of a like NAND gate Y45, having its output (No. 6 terminal) connected with the No. 2 terminal of the adder Y30.

The No. 9 terminals of the zone switches ZBR, ZBG and ZBD drive, respectively, the No. 1, No. 2 and No. 8 terminals (inputs) of a like NAND gate Y46, having 20 its output (No. 9 terminal) connected to the No. 15 terminal of the adder Y30.

Since each of the zone switches ZDR, ZDG, ZBR, ZBG and ZBD are sixteen position thumbwheel switches with the positions designated by the numbers zero to fifteen, the four outputs (No. 5, No. 8 No. 6 and No. 9 terminals) from each of said switches carries a binary code designating switch position. Therefore, the combination of these position codes via the NAND logic gates Y39–Y46, drives the adder Y30 to provide the parameters indicating the three divisions between the six quality zones Z1–Z6 as set by the said zone switches. In conjunction with other parameters to be defined, the adder Y30 drives certain inputs on two additional 4-bit adders Y31 and Y26 interconnected to provide a 6-bit scalar multiplier output and the sequencing of the control line (SB3).

This scalar multiplier output of the adders Y31 and Y26, together with other parameters to be defined, drives certain inputs on two additional 4-bit adders Y32 and Y25 to effect the proper sequencing of the control line (SB1).

The No. 9 terminal of the adder Y30 is connected to the source of negative bias (-6V).

The remaining terminals (No. 10, No. 11, No. 12, No. 13 and No. 14) of the adder Y30 comprise the first through fourth and carry-out bits, respectively, of the coded sum output of the adder Y30 and are connected, respectively, with the No. 6, No. 4, No. 2 and No. 15 terminals of the adder Y31 and the No. 6 terminal of the adder Y26.

The coded sum output of the adder Y31 comprises its No. 10, No. 11, No. 12 and No. 13 terminals representing the first through fourth bits, respectively, of the scalar multiplier number for a given red, green or infrared parameter in the color calculations and are respectively connected to the No. 6, No. 4, No. 2 and No. 15 terminals of the adder Y32.

The fifth and sixth bits of the scalar multiplier number appear at the coded outputs comprising the No. 10 and No. 11 terminals, respectively, of the adder Y26 which terminals are respectively connected to the No. 6 and No. 4 terminals of the adder Y25. As previously disclosed the carry-out bit (No. 14 terminal) of the adder Y26 determines the algebraic sign of the scalar multiplier and sequences the control line (SB3); and the carry-out bit (No. 14 terminal) of the adder Y25 sequences the control line (SB1).

The remaining inputs to the adders Y31 and Y26 are as follows:

The carry-out bit (No. 14 terminal) of the adder Y31 drives the No. 9 terminal of the adder Y26.

The No. 1, No. 3 and No. 5 terminals of the adder 5 Y31 are driven by the respective outputs (No. 10, No. 9 and No. 6 terminals) of NAND gates Y47, Y48 and Y49 (CD4023 AE modules of RCA).

The No. 3 terminal of the adder Y26 is driven by the output (No. 10 terminal) of a NAND gate Y50 (CD4023 AE module of RCA) having its No. 11, No. 12 and No. 13 terminals (inputs) connected in common to the output (No. 9 terminal) of a like NAND gate Y51. The No. 5 and No. 7 terminals of the adder 15 Y26 are driven by the respective outputs (No. 6 and No. 10 terminals) of like NAND gates Y52 and Y53.

The No. 7 and No. 9 terminals of the adder Y31 and the No. 4 terminal of the adder Y26 are connected to the source of negative bias (-6V); and the No. 1 and No. 2 terminals of the adder Y26 are connected to the source of positive bias (+6V).

and Y25 are as follows:

The carry-out bit (No. 14 terminal) of the adder Y32 drives the No. 9 terminal of the adder Y25.

The No. 9 terminal of the adder Y32 is connected to No. 2 terminals of the adder Y25 are connected to the source of positive bias (+6V).

The second through seventh bits of the calculation period subdivision counter Y3 (No. 11, No. 9, No. 6, No. 5, No. 4 and No. 3 terminals, respectively) are connected, respectively, to the No. 7 No. 5, No. 3, No. 1 terminals of the adder Y25.

Scalar bias parameters SBP for determining the range and starting points of the control switches ZDR 40 through ZBD thereof for driving the adders Y31 and Y26 are as follows:

- 1. R/GN-I: redness or greenness, infrared mode.

- 2. R/GN-G: redness or greenness, green mode.

- 3. R/GN-R: redness or greenness, red mode.

- 4. BN-R: brightness, red mode.

- 5. BN-I: brightness, infrared mode.

When the values for the bias parameters SBP have been determined as will be described hereinafter, the values are hard-wired into scalar bias circuit board SBB which serves as an interface between certain control line logic and the inputs of the NAND gates Y47-Y49 and Y51-Y53 driving the adders Y31 and Y26.

The scaler multiplier board has five inputs designated 55 as the scalar bias parameters SBP, the said inputs corresponding to R/GN-I, R/GN-G, R/GN-R, BN-R and BN-I, respectively, with a sixth input connected to the source of positive bias (-6V) as shown.

The number of hard-wired terminals are for 6-bit pa- 60 rameters SBP with the most significant bit MSB determining the algebraic sign of the particular wired parameter SBP. The position of the least significant bits LSB is also indicated on the scalar bias board SBB.

The input terminal numbers for the NAND gates Y4- 65 7-Y49 and Y51-Y53 for connection with the scalar bias board SBB are as follows:

| NAND Gate | Input Terminal Nos.    |

|-----------|------------------------|

| Y47       | No. 11, No. 12, No. 13 |

| Y48       | No. 1, No. 2, No. 8    |

| Y49       | No. 3, No. 4, No. 5    |

| Y51       | No. 1, No. 2, No. 8    |

| Y52       | No. 3, No. 4, No. 5    |

| Y53       | No. 11, No. 12, No. 13 |

From the foregoing table and from the drawing it can be seen that several of the foregoing gates can be provided in a single CD4023 AE module (IC chip) with the designated terminals connected to provide multiple NAND gate functions therethrough. This is also the case for like designated NAND, NOR and other gates of like commercial designation in the description of FIG. 5 and other Figures. The gates are individually shown and described to better show the interplay of the logic in controlling the various sequencing or clocking functions involved.

The scalar bias parameters SBP are generated as follows:

- 1. R/GN-I: the control lines (SC1) and (SC4) drive The remaining connections of the 4-bit adders Y32 25 the inputs (No. 8 and No. 9 terminals, respectively) of a NOR gate Y54 (CD4001 AE module of RCA), the output (No. 10 terminal) of the latter driving one input (No. 9 terminal) of a NAND gate Y55 (CD4011 AE module of RCA). The other input (No. 8 terminal) of the source of negative bias (-6V); and the No. 1 and 30 the NAND gate Y55 is driven by the control line (SA3) and the output (No. 10 terminal) of the NAND gate Y55 controls the parameter R/GN-I.

- 2. R/GN-G: the control line (SA2) drives one input (No. 13 terminal) of a like NAND gate Y56 having its other input (No. 12 terminal) connected to the output (No. 10 terminal) of the NOR gate Y54. Thus the output (No. 11 terminal) of the NAND gate Y56 controls the parameter R/GN-G.

- 3. R/GN-R: the control line (SA1) drives one input (No. 1 terminal) of a like NAND gate Y57 having its other input (No. 2 terminal) driven by the output (No. 10 terminal) of the NOR gate Y54. Thus, the output (No. 3 terminal) of the NAND gate Y57 controls the parameter R/GN-R.

- 4. BN-R: the control line (SA1) drives one input (No. 5 terminal) and the control line (SC1) drives the other input (No. 6 terminal) of a like NAND gate Y58, the output (No. 4 terminal) thereof controls the parameter BN-R.

- 5. BN-I: this parameter is signaled by the output (No. 4 terminal) of a like NAND gate Y38, previously described, and control is derived from the control lines (SA3) and (SC1) previously defined as the inputs to the NAND gate Y38.

Thus, because of the parenthetical designations of the control lines (SA1), (SA2), (SA3), (SC1) and (SC4) corresponding to the control switch means bearing like primary designations, the scalar bias parameters SBP are clearly controlled by the color selection means SA1, SA2, SA3 (red, green, infrared, respectively) and the first and last of the storage control means SC1 and SC4, respectively, which also control the switches in the color computer 40 (see FIGS. 4A and 4B).

All of the thumbwheel switches ZDR, ZDG, ZBR, ZBG and ZBD are of the hexadecimal 1248 code and compliment type with two (2) commons and wheel positions 0 - 15 such as the BB239/S modules of Inter Switch.

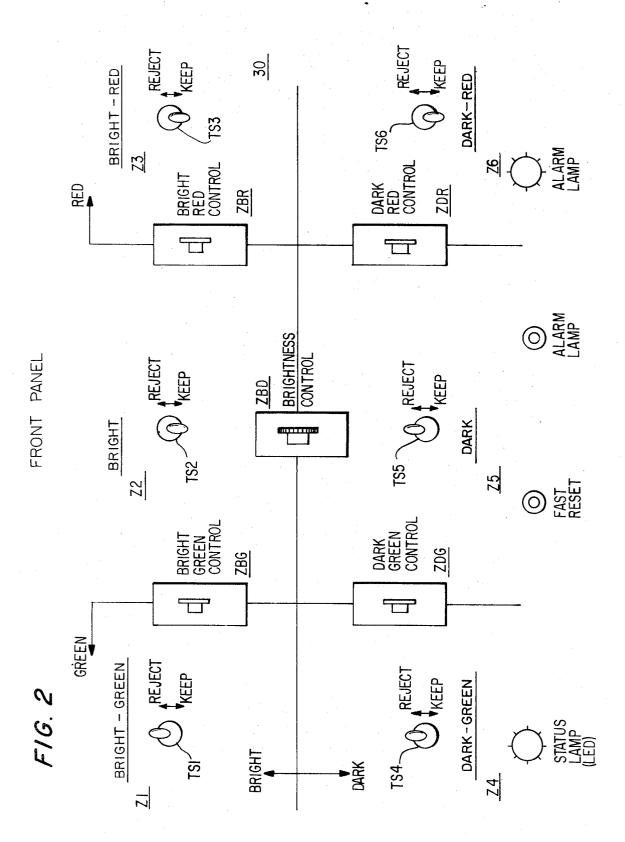

#### THE REJECT SELECTION LOGIC RSL

Referring now to FIG. 6, the shift register ST4 providing the data input between the register ST3 and the reject selection logic RSL is shown as having a SHIFT CLOCK input driving the No. 9 terminal of a first 8-bit shift register ST4A and the No. 1 terminal of a second 8-bit shift register ST4B (both comprising a CD4015 10 AE module of RCA) and a DATA IN terminal (RSL1) receiving the data from the output ST3D of the shift register ST3, as generally described previously in reference to FIGS. 4A and 4B, driving the No. 7 terminal of the first register ST4A.

The No. 7 and No. 9 terminals of the first register ST4A are connected to the source of negative bias (-6V) through resistors R25 and R26, respectively, while the No. 6 terminal of the first register ST4A and the No. 14 terminal of the second register ST4B are directly connected to the said source of negative bias (-6V).

The No. 10 terminal of the first register ST4A drives the No. 15 terminal of the second register ST4B and the resulting interaction of the two said registers results 25 in six (6) bits of information which relate to the color of the objects detected by the comparator 40B of the color computer 40 in the following manner:

$B \equiv Bright$

D = Dark

G = Green

$NG \equiv Not Green$

NR = Not Red

$R \equiv Red$

The foregoing symbols in parentheses designate corresponding data lines on which representative data bits appear to indicate the presence or absence of that given color characteristic of the objects (leaves) detected.

The BRIGHT data line (B) originates at the No. 5 <sup>40</sup> source of negative bias (-6V); terminal of the first register ST4A. The No. 11 terminal is connected to the state of the

The DARK data line (D) originates at the output (No. 4 terminal) of a NOR gate Y60 (CD4001 AE module of RCA) connected as an inverter by connecting both its inputs (No. 5 and No. 6 terminals) to the No. 4 terminal of the first register ST4A.

The GREEN data line (G) originates at the No. 3 terminal of the first register ST4A.

The NOT GREEN data line (NG) originates at the output (No. 11 terminal) of a NOR gate Y51 (CD4001 AE module of RCA) connected as an inverter by having both its inputs (No. 12 and No. 13 terminals) connected with the No. 10 terminal of the first register ST4A.

The NOT RED data line (NR) originates at the No. 13 terminal of the second register ST4B.

The RED data line (R) originates at the output (No. 10 terminal) of a NOR gate Y62 (CD4001 AE module of RCA) connected as an inverter by having both its inputs (No. 8 and No. 9 terminals) connected with the No. 12 terminal of the second register ST4B.

If all of the said color data lines are driven low, this indicates that the comparator has detected only the background reference with no leaves present over its 65

All other combinations of signals on the said color data lines indicate the relative brightness, greenness

and/or redness of a leaf to the quality zone dividing lines set on the front control panel FPC.

Thus, the color data lines (B), (D), (G), (NG), (NR) and (R) comprise the first input RSL1 of the reject selection logic circuit RSL.

The selected quality zone data from the toggle switches TS in each of the quality zones Z1–Z6 (on the front control panel FPC) is received on the second data input RSL2, the latter comprising six corresponding zone select lines (Z1), (Z2), (Z3), (Z4), (Z5) and (Z6) which drive the reject selection logic circuit RSL through in-line protection resistors R27, R28, R29, R30, R31 and R32, respectively.

The color data lines and the zone select lines selectively drive three interconnected AND/OR SELECT modules Y63, Y64 and Y65 (CD4019 AE modules of RCA) as follows:

| 20 | Color Data Line  | AND/OR SELECT<br>MODULE | TERMINAL<br>NUMBER |