(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2019년04월17일

(11) 등록번호 10-1943235

(24) 등록일자 2019년01월22일

- (51) 국제특허분류(Int. Cl.)

*G09G 3/36* (2006.01) *H01L 27/12* (2006.01)

*H01L 29/786* (2006.01)

(52) CPC특허분류

*G09G 3/3677* (2013.01)

*H01L 27/1225* (2013.01)

(21) 출원번호 10-2017-7007045

(22) 출원일자(국제) 2015년02월06일

심사청구일자 2017년03월14일

(85) 번역문제출일자 2017년03월14일

(65) 공개번호 10-2017-0042352

(43) 공개일자 2017년04월18일

(86) 국제출원번호 PCT/CN2015/072360

(87) 국제공개번호 WO 2016/070515

국제공개일자 2016년05월12일

(30) 우선권주장 201410626091.X 2014년11월07일 중국(CN)

(73) 특허권자

센젠 차이나 스타 옵토일렉트로닉스 테크놀로지

컴퍼니 리미티드

중국 광동 프로빈스, 센젠 시티, 광밍 뉴 디스트

릭트, 탕밍 로드, 넘버 9-2

(72) 발명자

다이, 췔오

중국, 광동 518132, 선전 광밍 디스트릭트, 탕밍

로드, 넘버 9-2

(74) 대리인

특허법의 티애아이

## (56) 선행기술조사문현

CN103021360 A

CN103680386 B

CN103928009 A

CN103400601 A

심사관 : 윤난영

(54) 발명의 명칭 산화물 반도체 박막 트랜지스터용 스캔 구동회로

(57) 요약

본 발명은 산화물 반도체 박막 트랜지스터용 스캔 구동회로를 제공하며, 상기 산화물 반도체 박막 트랜지스터용 스캔 구동회로의 풀다운 유지회로부(600)는 주 인버터와 보조 인버터를 구비하고, 정전압 저전위(DCL)를 도입하여, 정전압 저전위(DCL)<제2 부전위(VSS2)<제1 부전위(VSS1)로 설정함으로써, 산화물 반도체 박막 트랜지스터의 전기적 특성이 스캔 구동회로에 미치는 영향, 특히 누전 문제가 가져오는 기능적인 불량을 방지할 수 있어, 풀다운 유지회로부(600)가 작용 기간에는 정상적으로 풀다운되고, 비작용 기간에는 비교적 높은 전위에 처하여, 제1 노드(Q(N))와 출력단(G(N))이 효과적으로 저전위를 유지할 수 있다.

## 대표도 - 도7

(52) CPC특허분류

**H01L 29/7869** (2013.01)

G09G 2300/0408 (2013.01)

G09G 2320/0214 (2013.01)

G09G 2320/045 (2013.01)

---

## 명세서

### 청구범위

#### 청구항 1

캐스케이드 연결된 복수의 GOA 유닛을 포함하고, N은 양의 정수로서, 제N 단계 GOA 유닛은 풀업제어부, 풀업부, 전송부, 제1 풀다운부, 부트스트랩 커패시터부 및 풀다운 유지회로부를 포함하는 산화물 반도체 박막 트랜지스터의 스캔 구동회로에 있어서,

상기 풀업제어부는 게이트가 상기 제N 단계 GOA 유닛의 두 단계 이전 GOA 유닛인 제N-2 단계 GOA 유닛의 구동 출력단에 전기적으로 연결되고, 드레인은 상기 제N 단계 GOA 유닛의 두 단계 이전 GOA 유닛인 제N-2 단계 GOA 유닛의 출력단에 전기적으로 연결되며, 소스는 제1 노드에 전기적으로 연결되는 제11 트랜지스터를 포함하고;

상기 제1 풀다운부는 게이트가 상기 제N 단계 GOA 유닛의 두 단계 다음 GOA 유닛인 제N+2 단계 GOA 유닛의 출력 단에 전기적으로 연결되고, 드레인은 제1 노드에 전기적으로 연결되며, 소스는 제2 부전위 또는 출력단에 전기적으로 연결되는 제41 트랜지스터를 포함하며;

상기 풀다운 유지회로부는 게이트와 드레인이 모두 정전압 고전위에 전기적으로 연결되고, 소스는 제4 노드에 전기적으로 연결되는 제51 트랜지스터; 게이트는 제1 노드에 전기적으로 연결되고, 드레인은 제4 노드에 전기적으로 연결되며, 소스는 제1 부전위에 전기적으로 연결되는 제52 트랜지스터; 게이트는 제4 노드에 전기적으로 연결되고, 드레인은 정전압 고전위에 전기적으로 연결되며, 소스는 제2 노드에 전기적으로 연결되는 제53 트랜지스터; 게이트는 제1 노드에 전기적으로 연결되고, 드레인은 제2 노드에 전기적으로 연결되며, 소스는 제3 노드에 전기적으로 연결되는 제54 트랜지스터; 게이트는 제4 노드에 전기적으로 연결되고, 드레인은 정전압 고전위에 전기적으로 연결되며, 소스는 제3 노드에 전기적으로 연결되는 제73 트랜지스터; 게이트는 제1 노드에 전기적으로 연결되고, 드레인은 제3 노드에 전기적으로 연결되며, 소스는 정전압 저전위에 전기적으로 연결되는 제74 트랜지스터; 게이트는 제2 노드에 전기적으로 연결되고, 드레인은 제1 노드에 전기적으로 연결되며, 소스는 제2 부전위에 전기적으로 연결되는 제42 트랜지스터; 게이트는 제2 노드에 전기적으로 연결되고, 드레인은 정전압 고전위에 전기적으로 연결되며, 소스는 제1 부전위에 전기적으로 연결되는 제32 트랜지스터를 포함하고;

상기 제51 트랜지스터, 제52 트랜지스터, 제53 트랜지스터, 제54 트랜지스터는 주 인버터를 구성하여, 상기 주 인버터로 제32 트랜지스터와 제42 트랜지스터를 제어하고; 상기 제73 트랜지스터, 제74 트랜지스터는 보조 인버터를 구성하여, 상기 보조 인버터는 작용 기간에 주 인버터로 저전위를 공급하고, 비작용 기간에 주 인버터로 고전위를 제공하며;

상기 제1 부전위, 제2 부전위와 정전압 저전위의 관계는 정전압 저전위<제2 부전위<제1 부전위이되,

상기 풀업부는 게이트는 제1 노드에 전기적으로 연결되고, 드레인은 클럭 신호에 전기적으로 연결되며, 소스는 출력단에 전기적으로 연결되는 제21 트랜지스터를 포함하고;

상기 전송부는 게이트는 제1 노드에 전기적으로 연결되고, 드레인은 클럭 신호에 전기적으로 연결되며, 소스는 구동 출력단에 전기적으로 연결되는 제22 트랜지스터를 포함하며;

상기 부트스트랩 커패시터부는 일단이 제1 노드에 전기적으로 연결되고, 타단은 출력단에 전기적으로 연결되는 커패시터를 포함하는 산화물 반도체 박막 트랜지스터용 스캔 구동회로.

#### 청구항 2

제1항에 있어서,

상기 보조 인버터는 게이트와 드레인이 모두 정전압 고전위에 전기적으로 연결되고, 소스는 제73 트랜지스터의 게이트에 전기적으로 연결되는 제71 트랜지스터; 게이트는 제1 노드에 전기적으로 연결되고, 드레인은 제73 트랜지스터의 게이트에 전기적으로 연결되며, 소스는 정전압 저전위에 전기적으로 연결되는 제72 트랜지스터를 더 포함하며; 상기 제73 트랜지스터의 게이트는 제4 노드와 차단되는 산화물 반도체 박막 트랜지스터용 스캔 구동회로.

**청구항 3**

제1항에 있어서,

채택된 단계 전송 방식은 제N-2단계에서 제N단계로 전송하는 방식인 산화물 반도체 박막 트랜지스터용 스캔 구동회로.

**청구항 4**

제1항에 있어서,

상기 스캔 구동회로의 제1단계 연결관계에서, 제11 트랜지스터의 게이트는 회로의 시동 신호단에 전기적으로 연결되고, 드레인은 회로의 시동 신호단에 전기적으로 연결되며;

상기 스캔 구동회로의 제2단계 연결관계에서, 제11 트랜지스터의 게이트와 드레인은 모두 회로의 시동 신호단에 전기적으로 연결되는 산화물 반도체 박막 트랜지스터용 스캔 구동회로.

**청구항 5**

제1항에 있어서,

상기 스캔 구동회로의 마지막 단계의 연결관계에서, 제41 트랜지스터의 게이트는 회로의 시동 신호단에 전기적으로 연결되고;

상기 스캔 구동회로의 끝에서 두 번째 단계의 연결관계에서, 제41 트랜지스터의 게이트는 회로의 시동 신호단에 전기적으로 연결되는 산화물 반도체 박막 트랜지스터용 스캔 구동회로.

**청구항 6**

제1항에 있어서,

상기 클럭신호의 평형 드uty비는 50/50 미만인 산화물 반도체 박막 트랜지스터용 스캔 구동회로.

**청구항 7**

제6항에 있어서,

상기 클럭신호의 평형 드uty비는 40/60인 산화물 반도체 박막 트랜지스터용 스캔 구동회로.

**청구항 8**

제1항에 있어서,

상기 제1 노드의 신호 출력 평형은 "凸"자형인 산화물 반도체 박막 트랜지스터용 스캔 구동회로.

**청구항 9**

제1항에 있어서,

상기 클럭신호는 4세트의 클럭신호인 제1 클럭신호, 제2 클럭신호, 제3 클럭신호, 제4 클럭신호를 포함하는 산화물 반도체 박막 트랜지스터용 스캔 구동회로.

**청구항 10**

캐스케이드 연결된 복수의 GOA 유닛을 포함하고, N은 양의 정수로서, 제N 단계 GOA 유닛은 풀업제어부, 풀업부, 전송부, 제1 풀다운부, 부트스트랩 커패시터부 및 풀다운 유지회로부를 포함하는 산화물 반도체 박막 트랜지스터의 스캔 구동회로에 있어서,

상기 풀업제어부는 게이트가 상기 제N 단계 GOA 유닛의 두 단계 이전 GOA 유닛인 제N-2 단계 GOA 유닛의 구동 출력단에 전기적으로 연결되고, 드레인은 상기 제N 단계 GOA 유닛의 두 단계 이전 GOA 유닛인 제N-2 단계 GOA 유닛의 출력단에 전기적으로 연결되며, 소스는 제1 노드에 전기적으로 연결되는 제11 트랜지스터를 포함하고;

상기 제1 풀다운부는 게이트가 상기 제N 단계 GOA 유닛의 두 단계 다음 GOA 유닛인 제N+2 단계 GOA 유닛의 출력

단에 전기적으로 연결되고, 드레인은 제1 노드에 전기적으로 연결되며, 소스는 제2 부전위 또는 출력단에 전기적으로 연결되는 제41 트랜지스터를 포함하며;

상기 풀다운 유지회로부는 게이트와 드레인 모두 정전압 고전위에 전기적으로 연결되고, 소스는 제4 노드에 전기적으로 연결되는 제51 트랜지스터; 게이트는 제1 노드에 전기적으로 연결되고, 드레인은 제4 노드에 전기적으로 연결되며, 소스는 제1 부전위에 전기적으로 연결되는 제52 트랜지스터; 게이트는 제4 노드에 전기적으로 연결되고, 드레인은 정전압 고전위에 전기적으로 연결되며, 소스는 제2 노드에 전기적으로 연결되는 제53 트랜지스터; 게이트는 제1 노드에 전기적으로 연결되고, 드레인은 제2 노드에 전기적으로 연결되며, 소스는 제3 노드에 전기적으로 연결되는 제54 트랜지스터; 게이트는 제4 노드에 전기적으로 연결되고, 드레인은 정전압 고전위에 전기적으로 연결되며, 소스는 제3 노드에 전기적으로 연결되는 제73 트랜지스터; 게이트는 제1 노드에 전기적으로 연결되고, 드레인은 제3 노드에 전기적으로 연결되며, 소스는 정전압 저전위에 전기적으로 연결되는 제74 트랜지스터; 게이트는 제2 노드에 전기적으로 연결되고, 드레인은 제1 노드에 전기적으로 연결되며, 소스는 제2 부전위에 전기적으로 연결되는 제42 트랜지스터; 게이트는 제2 노드에 전기적으로 연결되고, 드레인은 출력단에 전기적으로 연결되며, 소스는 제1 부전위에 전기적으로 연결되는 제32 트랜지스터를 포함하고;

상기 제51 트랜지스터, 제52 트랜지스터, 제53 트랜지스터, 제54 트랜지스터는 주 인버터를 구성하여, 상기 주 인버터로 제32 트랜지스터와 제42 트랜지스터를 제어하고; 상기 제73 트랜지스터, 제74 트랜지스터는 보조 인버터를 구성하여, 상기 보조 인버터는 작용 기간에 주 인버터로 저전위를 공급하고, 비작용 기간에 주 인버터로 고전위를 제공하며;

상기 제1 부전위, 제2 부전위와 정전압 저전위의 관계는 정전압 저전위<제2 부전위<제1 부전위이고;

상기 풀업부는 게이트는 제1 노드에 전기적으로 연결되고, 드레인은 클럭신호에 전기적으로 연결되며, 소스는 출력단에 전기적으로 연결되는 제21 트랜지스터를 포함하며;

상기 전송부는 게이트는 제1 노드에 전기적으로 연결되고, 드레인은 클럭신호에 전기적으로 연결되며, 소스는 구동 출력단에 전기적으로 연결되는 제22 트랜지스터를 포함하고;

상기 부트스트랩 커패시터부는 일단이 제1 노드에 전기적으로 연결되고, 타단은 출력단에 전기적으로 연결되는 커패시터를 포함하며;

상기 클럭신호의 파형 둑티비는 50/50 미만이고;

상기 클럭신호의 파형 둑티비는 40/60이며;

상기 제1 노드의 신호 출력 파형은 "凸"자형인 산화물 반도체 박막 트랜지스터용 스캔 구동회로.

## 청구항 11

삭제

## 청구항 12

제10항에 있어서,

채택된 단계 전송 방식은 제N-2단계에서 제N단계로 전송하는 방식인 산화물 반도체 박막 트랜지스터용 스캔 구동회로.

## 청구항 13

제10항에 있어서,

상기 스캔 구동회로의 제1단계 연결관계에서, 제11 트랜지스터의 게이트는 회로의 시동 신호단에 전기적으로 연결되고, 드레인은 회로의 시동 신호단에 전기적으로 연결되며;

상기 스캔 구동회로의 제2단계 연결관계에서, 제11 트랜지스터의 게이트와 드레인은 모두 회로의 시동 신호단에 전기적으로 연결되는 산화물 반도체 박막 트랜지스터용 스캔 구동회로.

## 청구항 14

제10항에 있어서,

상기 스캔 구동회로의 마지막 단계의 연결관계에서, 제41 트랜지스터의 게이트는 회로의 시동 신호단에 전기적으로 연결되고;

상기 스캔 구동회로의 끝에서 두 번째 단계의 연결관계에서, 제41 트랜지스터의 게이트는 회로의 시동 신호단에 전기적으로 연결되는 산화물 반도체 박막 트랜지스터용 스캔 구동회로.

### 청구항 15

제10항에 있어서,

상기 클럭신호는 4세트의 클럭신호인 제1 클럭신호, 제2 클럭신호, 제3 클럭신호, 제4 클럭신호를 포함하는 산화물 반도체 박막 트랜지스터용 스캔 구동회로.

## 발명의 설명

### 기술 분야

[0001] 본 발명은 액정 디스플레이 분야에 관한 것으로서, 특히 산화물 반도체 박막 트랜지스터용 스캔 구동회로에 관한 것이다.

### 배경 기술

[0002] GOA(Gate Drive On Array)는 박막 트랜지스터(thin film transistor, TFT) 액정 디스플레이 어레이(Array) 제조공정을 이용하여 게이트 드라이버를 박막 트랜지스터 어레이 기판에 제작함으로써 순차주사를 구현하는 구동 방식이다.

[0003] 통상적으로, GOA 회로는 주로 풀업부(Pull-up part), 풀업제어부(Pull-up control part), 전송부(Transfer part), 풀다운부(Pull-down part), 풀다운 유지회로부(Pull-down Holding part), 및 전위를 상승시키는 부스트부(Boost part)로 구성되며, 부스트부는 일반적으로 부트스트랩 커판시터로 구성된다.

[0004] 풀업부는 주로 입력된 클럭신호(Clock)를 박막 트랜지스터의 게이트로 출력하는 일을 담당하며, 액정 디스플레이의 구동신호 역할을 한다. 풀업제어부는 주로 풀업부의 개방을 제어하는 일을 담당하며, 일반적으로 이전 단계의 GOA 회로로부터 전달되는 신호에 의해 작용한다. 풀다운부는 주로 스캔신호를 출력 후, 신속히 스캔신호(즉 박막 트랜지스터의 게이트의 전위)를 로우레벨로 낮추는 일을 담당한다. 풀다운 유지회로부는 즉 주로 스캔신호와 풀업부의 신호를 차단 상태(즉 설정된 부전위)로 유지하는 일을 담당한다. 부스트부는 즉 주로 풀업부의 전위에 대해 2차 상승을 수행하여 풀업부의 정상적인 출력을 보장하는 일을 담당한다.

[0005] 산화물 반도체 박막 트랜지스터가 발전함에 따라, 산화물 반도체에 상응하는 패널 주변의 집적회로 역시 관심의 초점이 되었다. 산화물 반도체 트랜지스터의 캐리어 이동도는 비정질 실리콘 박막 트랜지스터의 20~30배로서, TFT의 화소전극에 대한 충방전 속도를 대폭 향상시킬 수 있어 화소의 응답 속도가 향상되고, 보다 빠른 리프레시 속도를 구현함과 동시에, 더욱 빠른 응답은 화소의 라인 스캔 속도 또한 크게 향상시킬 수 있어, TFT-LCD에서 초고해상도가 가능해진다. 따라서, 산화물 반도체 박막 트랜지스터의 GOA 회로는 향후 비정질 실리콘의 GOA 회로를 대체할 가능성이 있다. 종래 기술 중, 산화물 반도체 박막 트랜지스터의 GOA 회로의 개발이 비교적 드물고, 특히 산화물 박막 트랜지스터의 전기적 특성 자체가 가져오는 여러 문제들을 극복할 필요가 있다. 예를 들어, 종래의 비정질 실리콘 박막 트랜지스터의 전기적 특성 중 임계전압은 일반적으로 0V 이상이고, 또한 서브임계 영역의 전압은 전류에 비해 요동폭이 비교적 크다. 그렇기 때문에, 회로 설계에 있어, 설사 모종의 트랜지스터가 작동 시 트랜지스터의 게이트와 소스 간의 전압( $V_{GS}$ )이 거의 0V와 같더라도, 발생되는 누설전류가 비교적 작다. 그러나 산화물 반도체 박막 트랜지스터는 그 재료 자체의 특성이 비정질 실리콘과 뚜렷한 차이가 있어, 그 임계전압은 0V 정도이고, 또한 서브임계 영역의 요동폭이 비교적 작다. 그런데 GOA 회로는 off 상태일 때 대부분의 소자가  $V_{GS}=0V$ 에서 작동하기 때문에, 산화물 반도체 박막 트랜지스터 GOA 회로 설계의 난도가 증가할 수 있으며, 비정질 실리콘 반도체에 적용되는 약간의 스캔 구동 회로를 산화물 반도체에 응용할 경우 약간의 기능적인 문제가 존재할 수 있다. 이밖에, 모종의 외재적인 요소의 유도 및 응력 작용에 의해, 산화물 반도체 박막 트랜지스터는 임계전압이 음의 값을 향해 감소하는 추세가 발생하기도 하는데, 이렇게 되면 산화물 반도체 박막 트랜지스터 GOA 회로가 작동할 수 없는 상황을 직접적으로 초래할 수 있다. 따라서 회로 설계 시 이러한 소자 특성이 GOA 회로에 미치는 영향을 반드시 고려해야 한다.

## 발명의 내용

### 해결하려는 과제

[0006] 본 발명의 목적은 산화물 박막 트랜지스터의 전기성이 GOA 구동 회로에 미치는 영향, 특히 누설 전류 문제가 가져오는 기능적인 불량을 해결하고, 현재의 산화물 박막 트랜지스터 스캔 구동회로 중 풀다운 유지회로부가 비작용 기간에 비교적 높은 전위에 놓이지 못하는 문제를 해결하기 위한 산화물 반도체 박막 트랜지스터용 스캔 구동회로를 제공하고자 하는데 있다.

### 과제의 해결 수단

[0007] 상기 목적에 대하여, 본 발명은 산화물 반도체 박막 트랜지스터의 스캔 구동회로를 제공하며, 이는 캐스케이드 연결된 복수의 GOA 유닛을 포함하고, N은 양의 정수로서, 제N 단계 GOA 유닛은 풀업제어부, 풀업부, 전송부, 제1 풀다운부, 부트스트랩 커패시터부 및 풀다운 유지회로부를 포함하며;

[0008] 상기 풀업제어부는 게이트가 상기 제N 단계 GOA 유닛의 두 단계 이전 GOA 유닛인 제N-2 단계 GOA 유닛의 구동 출력단에 전기적으로 연결되고, 드레인은 상기 제N 단계 GOA 유닛의 두 단계 이전 GOA 유닛인 제N-2 단계 GOA 유닛의 출력단에 전기적으로 연결되며, 소스는 제1 노드에 전기적으로 연결되는 제11 트랜지스터를 포함하고;

[0009] 상기 제1 풀다운부는 게이트가 상기 제N 단계 GOA 유닛의 두 단계 다음 GOA 유닛인 제N+2 단계 GOA 유닛의 출력 단에 전기적으로 연결되고, 드레인은 제1 노드에 전기적으로 연결되며, 소스는 제2 부전위 또는 출력단에 전기적으로 연결되는 제41 트랜지스터를 포함하며;

[0010] 상기 풀다운 유지부는 게이트와 드레인이 모두 정전압 고전위에 전기적으로 연결되고, 소스는 제4 노드에 전기적으로 연결되는 제51 트랜지스터; 게이트는 제1 노드에 전기적으로 연결되고, 드레인은 제4 노드에 전기적으로 연결되며, 소스는 제1 부전위에 전기적으로 연결되는 제52 트랜지스터; 게이트는 제4 노드에 전기적으로 연결되고, 드레인은 정전압 고전위에 전기적으로 연결되며, 소스는 제2 노드에 전기적으로 연결되는 제53 트랜지스터; 게이트는 제1 노드에 전기적으로 연결되고, 드레인은 제2 노드에 전기적으로 연결되며, 소스는 제3 노드에 전기적으로 연결되는 제54 트랜지스터; 게이트는 제4 노드에 전기적으로 연결되고, 드레인은 정전압 고전위에 전기적으로 연결되며, 소스는 제3 노드에 전기적으로 연결되는 제73 트랜지스터; 게이트는 제1 노드에 전기적으로 연결되고, 드레인은 제3 노드에 전기적으로 연결되며, 소스는 정전압 저전위에 전기적으로 연결되는 제74 트랜지스터; 게이트는 제2 노드에 전기적으로 연결되고, 드레인은 제1 노드에 전기적으로 연결되며, 소스는 제2 부전위에 전기적으로 연결되는 제42 트랜지스터; 게이트는 제2 노드에 전기적으로 연결되고, 드레인은 출력단에 전기적으로 연결되며, 소스는 제1 부전위에 전기적으로 연결되는 제32 트랜지스터를 포함하고;

[0011] 상기 제51 트랜지스터, 제52 트랜지스터, 제53 트랜지스터, 제54 트랜지스터는 주 인버터를 구성하여, 상기 주 인버터로 제32 트랜지스터와 제42 트랜지스터를 제어하고; 상기 제73 트랜지스터, 제74 트랜지스터는 보조 인버터를 구성하여, 상기 보조 인버터는 작용 기간에 주 인버터로 저전위를 공급하고, 비작용 기간에 주 인버터로 고전위를 제공하며;

[0012] 상기 제1 부전위, 제2 부전위와 정전압 저전위의 관계는 정전압 저전위<제2 부전위<제1 부전위이다.

[0013] 상기 보조 인버터는 게이트와 드레인이 모두 정전압 고전위에 전기적으로 연결되고, 소스는 제73 트랜지스터의 게이트에 전기적으로 연결되는 제71 트랜지스터; 게이트는 제1 노드에 전기적으로 연결되고, 드레인은 제73 트랜지스터의 게이트에 전기적으로 연결되며, 소스는 정전압 저전위에 전기적으로 연결되는 제72 트랜지스터를 더 포함하며; 상기 제73 트랜지스터의 게이트는 제4 노드와 차단된다.

[0014] 상기 스캔 구동회로에 채택된 단계 전송 방식은 제N-2단계에서 제N단계로 전송하는 방식이다.

[0015] 상기 풀업부는 게이트는 제1 노드에 전기적으로 연결되고, 드레인은 클럭 신호에 전기적으로 연결되며, 소스는 출력단에 전기적으로 연결되는 제21 트랜지스터를 포함하고;

[0016] 상기 전송부는 게이트는 제1 노드에 전기적으로 연결되고, 드레인은 클럭 신호에 전기적으로 연결되며, 소스는 구동 출력단에 전기적으로 연결되는 제22 트랜지스터를 포함하며;

[0017] 상기 부트스트랩 커패시터부는 일단이 제1 노드에 전기적으로 연결되고, 타단은 출력단에 전기적으로 연결되는 커패시터를 포함한다.

- [0018] 상기 스캔 구동회로의 제1단계 연결관계에서, 제11 트랜지스터의 게이트는 회로의 시동 신호단에 전기적으로 연결되고, 드레인은 회로의 시동 신호단에 전기적으로 연결되며;

- [0019] 상기 스캔 구동회로의 제2단계 연결관계에서, 제11 트랜지스터의 게이트와 드레인은 모두 회로의 시동 신호단에 전기적으로 연결된다.

- [0020] 상기 스캔 구동회로의 마지막 단계의 연결관계에서, 제41 트랜지스터의 게이트는 회로의 시동 신호단에 전기적으로 연결되고;

- [0021] 상기 스캔 구동회로의 끝에서 두 번째 단계의 연결관계에서, 제41 트랜지스터의 게이트는 회로의 시동 신호단에 전기적으로 연결된다.

- [0022] 상기 클럭신호의 파형 뉴티비는 50/50 미만이다.

- [0023] 상기 클럭신호의 파형 뉴티비는 40/60이다.

- [0024] 상기 제1 노드의 신호 출력 파형은 "凸"자형이다.

- [0025] 상기 클럭신호는 4세트의 클럭신호인 제1 클럭신호, 제2 클럭신호, 제3 클럭신호, 제4 클럭신호를 포함한다.

### 발명의 효과

- [0026] 본 발명의 유익한 효과는 다음과 같다. 본 발명은 산화물 반도체 박막 트랜지스터용 스캔 구동회로를 제공하며, 상기 산화물 반도체 박막 트랜지스터용 스캔 구동회로의 풀다운 유지회로부는 주 인버터와 보조 인버터를 구비하고, 정전압 저전위를 도입하여, 정전압 저전위<제2 부전위<제1 부전위로 설정함으로써, 산화물 반도체 박막 트랜지스터의 전기적 특성이 스캔 구동회로에 미치는 영향, 특히 누설전류 문제가 가져오는 기능적인 불량을 방지할 수 있어, 풀다운 유지회로부가 작용 기간에는 정상적으로 풀다운되고, 비작용 기간에는 비교적 높은 전위에 처하여, 제1 노드와 출력단이 효과적으로 저전위를 유지할 수 있다.

### 도면의 간단한 설명

- [0027] 본 발명의 특징 및 기술 내용을 좀 더 구체적으로 이해할 수 있도록, 이하 본 발명에 관한 상세한 설명과 첨부 도면을 참조하기 바라며, 단 첨부도면은 단지 참고 및 설명용으로 제공되는 것일 뿐, 결코 본 발명을 제한하기 위한 것이 아니다.

도면 중,

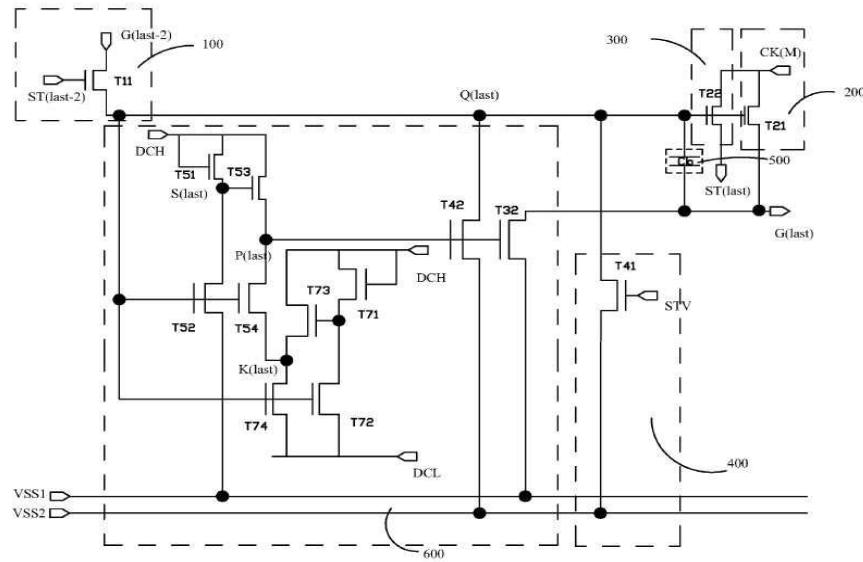

도 1은 본 발명의 산화물 반도체 박막 트랜지스터용 스캔 구동회로의 제1 실시예의 회로도이다.

도 2는 도 1에 도시된 제1 실시예의 제1 단계 GOA 유닛의 회로도이다.

도 3은 도 1에 도시된 제1 실시예의 제2 단계 GOA 유닛의 회로도이다.

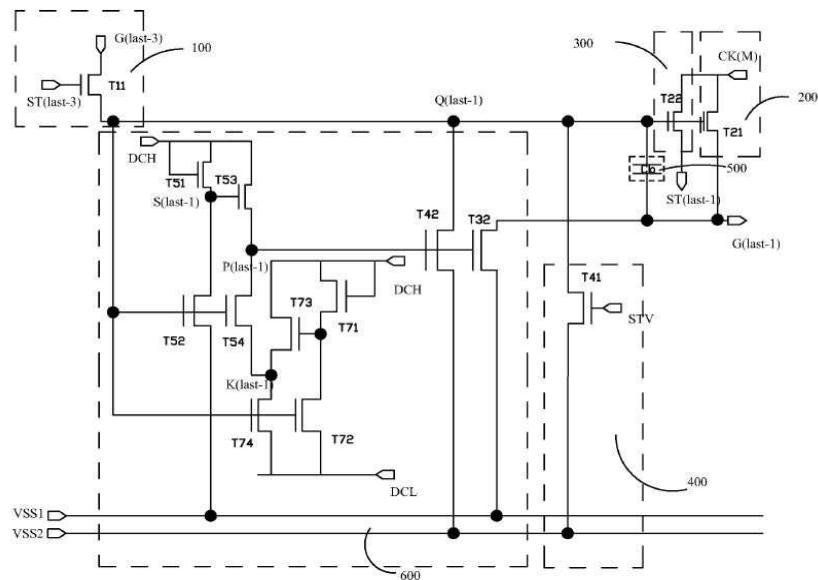

도 4는 도 1에 도시된 제1 실시예의 끝에서 두 번째 단계의 GOA 유닛의 회로도이다.

도 5는 도 1에 도시된 제1 실시예의 마지막 단계 즉 끝에서 첫 번째 단계의 GOA 유닛의 회로도이다.

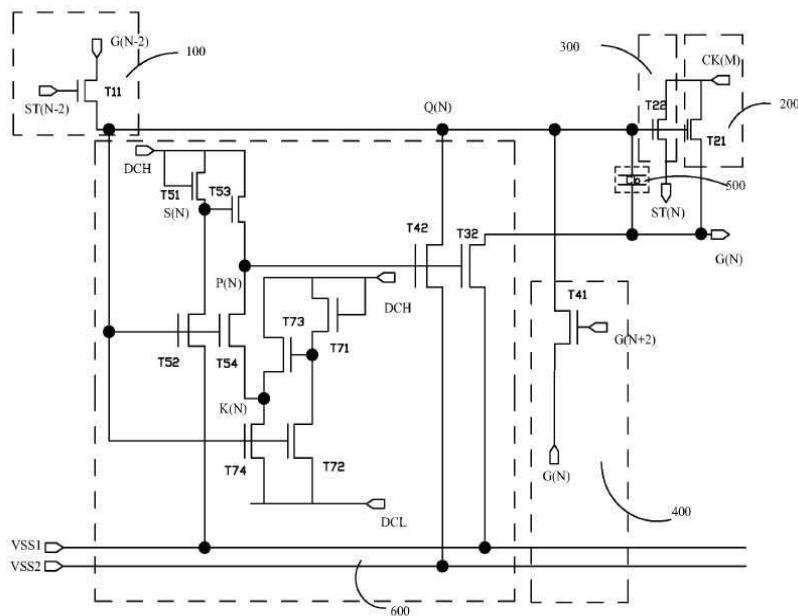

도 6은 본 발명의 산화물 반도체 박막 트랜지스터용 스캔 구동회로의 제2 실시예의 회로도이다.

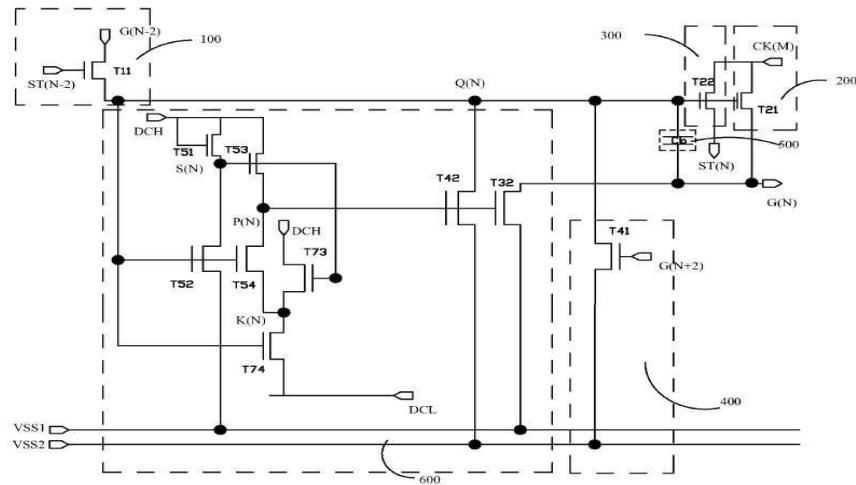

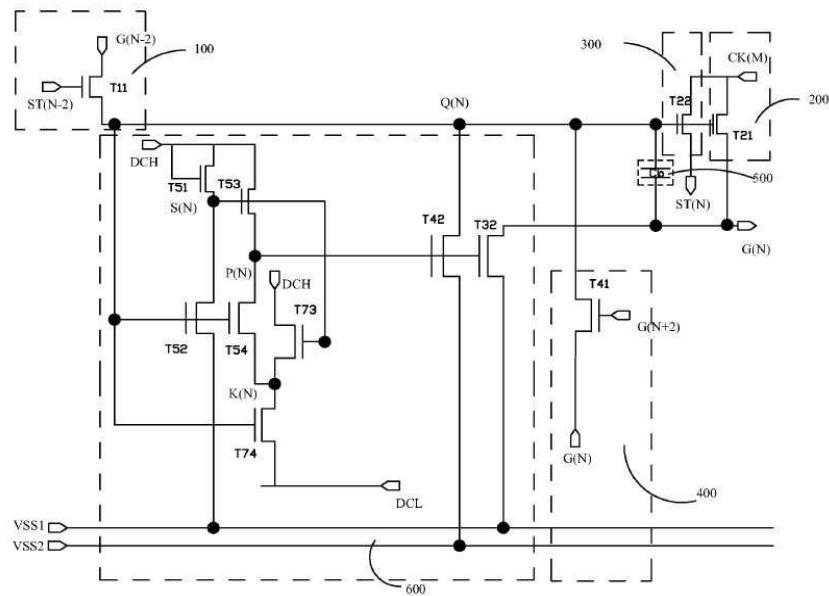

도 7은 본 발명의 산화물 반도체 박막 트랜지스터용 스캔 구동회로의 제3 실시예의 회로도이다.

도 8은 본 발명의 산화물 반도체 박막 트랜지스터용 스캔 구동회로의 제4 실시예의 회로도이다.

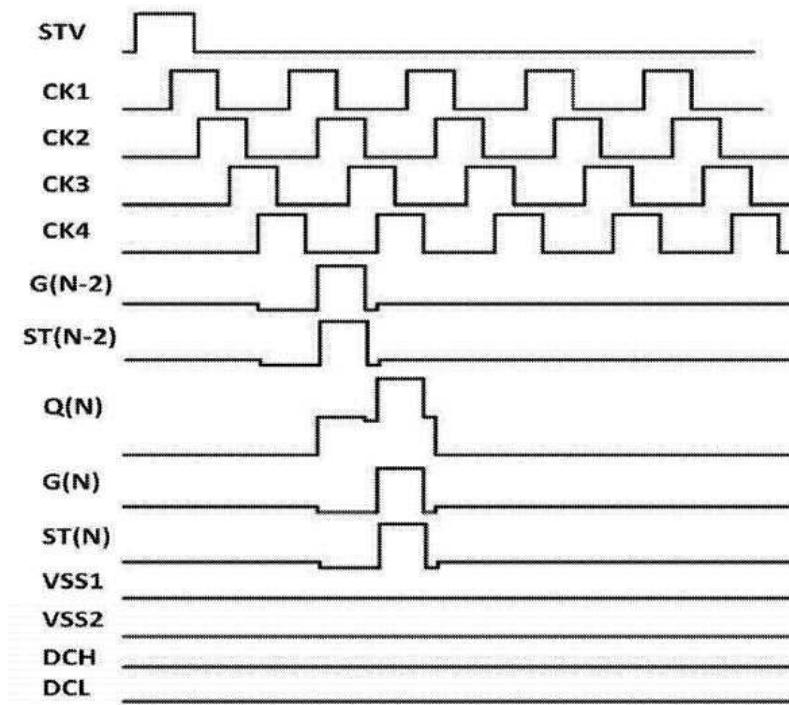

도 9는 본 발명의 산화물 반도체 박막 트랜지스터용 스캔 구동회로의 파형 설정과 키 노드의 출력파형도이다.

### 발명을 실시하기 위한 구체적인 내용

- [0028] 본 발명이 채택한 기술 수단 및 그 효과를 좀 더 구체적으로 설명하기 위하여, 이하 본 발명의 바람직한 실시예 및 그 첨부도면을 결합하여 상세히 설명한다.

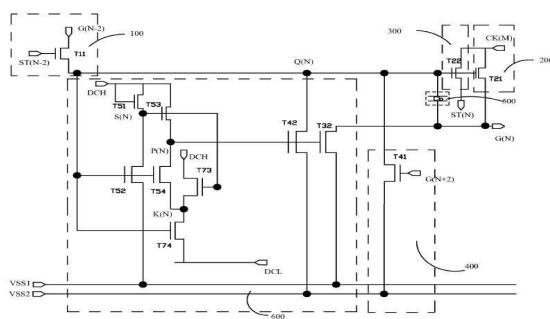

- [0029] 도 1-5를 참조하면, 본 발명의 산화물 반도체 박막 트랜지스터용 스캔 구동회로의 제1 일시예이다. 도 1에 도시된 바와 같이, 상기 산화물 반도체 박막 트랜지스터용 스캔 구동회로는 인듐갈륨아연 산화물(Indium Gallium Zinc Oxide, IGZO) 박막 트랜지스터의 스캔 구동회로이며, 캐스케이드 연결된 복수의 GOA 유닛을 포함하며, N은

양의 정수로서, 제N 단계 GOA 유닛은 풀업 제어부(100), 풀업부(200), 전송부(300), 제1 풀다운부(400), 부트스 트랩 커패시터(500)부 및 풀다운 유지회로부(600)를 포함한다.

[0030] 상기 각 부분의 구성 및 구체적인 연결방식은 다음과 같다.

[0031] 상기 풀업 제어부(100)는 제11 트랜지스터(T11)를 포함하며, 상기 제11 트랜지스터(T11)의 게이트는 상기 제N 단계 GOA 유닛의 두 단계 이전 GOA 유닛인 제N-2 단계 GOA 유닛의 구동 출력단(ST(N-2))에 전기적으로 연결되고, 드레인은 상기 제N 단계 GOA 유닛의 두 단계 이전 GOA 유닛인 제N-2 단계 GOA 유닛의 출력단(G(N-2))에 전기적으로 연결되며, 소스는 제1 노드(Q(N))에 전기적으로 연결되고;

[0032] 상기 풀업부(200)는 제21 트랜지스터(T21)를 포함하며, 상기 제21 트랜지스터(T21)의 게이트는 제1 노드(Q(N))에 전기적으로 연결되고, 드레인은 클럭신호(CK(M))에 전기적으로 연결되며, 소스는 출력단(G(N))에 전기적으로 연결되고;

[0033] 상기 전송부(300)는 제22 트랜지스터(T22)를 포함하며, 상기 제22 트랜지스터(T22)의 게이트는 제1 노드(Q(N))에 전기적으로 연결되고, 드레인은 클럭신호(CK(M))에 전기적으로 연결되며, 소스는 구동 출력단(ST(N))에 전기적으로 연결되고;

[0034] 상기 제1 풀다운부(400)는 제41 트랜지스터(T41)를 포함하며, 상기 제41 트랜지스터(T41)의 게이트는 상기 제N 단계 GOA 유닛의 두 단계 다음 GOA 유닛인 제N+2 단계 GOA 유닛의 출력단(G(N+2))에 전기적으로 연결되고, 드레인은 제1 노드(Q(N))에 전기적으로 연결되며, 소스는 제2 부전위(VSS2)에 전기적으로 연결되고;

[0035] 상기 부트스트랩 커패시터부(500)는 커패시터(Cb)를 포함하며, 상기 커패시터(Cb)의 일단은 제1 노드(Q(N))에 전기적으로 연결되고, 타단은 출력단(G(N))에 전기적으로 연결되며;

[0036] 상기 풀다운 유지부(600)는 게이트와 드레인이 모두 정전압 고전위(DCH)에 전기적으로 연결되고, 소스는 제4 노드(S(N))에 전기적으로 연결되는 제51 트랜지스터(T51);

[0037] 게이트는 제1 노드(Q(N))에 전기적으로 연결되고, 드레인은 제4 노드(S(N))에 전기적으로 연결되며, 소스는 제1 부전위(VSS1)에 전기적으로 연결되는 제52 트랜지스터(T52);

[0038] 게이트는 제4 노드(S(N))에 전기적으로 연결되고, 드레인은 정전압 고전위(DCH)에 전기적으로 연결되며, 소스는 제2 노드(P(N))에 전기적으로 연결되는 제53 트랜지스터(T53);

[0039] 게이트는 제1 노드(Q(N))에 전기적으로 연결되고, 드레인은 제2 노드(P(N))에 전기적으로 연결되며, 소스는 제3 노드(K(N))에 전기적으로 연결되는 제54 트랜지스터(T54);

[0040] 게이트와 드레인은 모두 정전압 고전위(DCH)에 전기적으로 연결되고, 소스는 제73 트랜지스터(T73)의 게이트에 연결되는 제71 트랜지스터(T71);

[0041] 게이트는 제1 노드(Q(N))에 전기적으로 연결되고, 드레인은 제73 트랜지스터(T73)의 게이트에 전기적으로 연결되며, 소스는 정전압 저전위(DCL)에 전기적으로 연결되는 제72 트랜지스터(T72);

[0042] 게이트는 제71 트랜지스터(T71)의 소스에 전기적으로 연결되고, 드레인은 정전압 고전위(DCH)에 전기적으로 연결되며, 소스는 제3 노드(K(N))에 전기적으로 연결되는 제73 트랜지스터;

[0043] 게이트는 제1 노드(Q(N))에 전기적으로 연결되고, 드레인은 제3 노드(K(N))에 전기적으로 연결되며, 소스는 정전압 저전위(DCL)에 전기적으로 연결되는 제74 트랜지스터(T74);

[0044] 게이트는 제2 노드(P(N))에 전기적으로 연결되고, 드레인은 제1 노드(Q(N))에 전기적으로 연결되며, 소스는 제2 부전위(VSS2)에 전기적으로 연결되는 제42 트랜지스터(T42);

[0045] 게이트는 제2 노드(P(N))에 전기적으로 연결되고, 드레인은 출력단(G(N))에 전기적으로 연결되며, 소스는 제1 부전위(VSS1)에 전기적으로 연결되는 제32 트랜지스터(T32)를 포함한다.

[0046] 특별히 설명해 두어야 할 점으로, 먼저, 상기 제1 부전위(VSS1), 제2 부전위(VSS2)와 정전압 전위(DCL)의 관계는 정전압 저전위(DCL)<제2 부전위(VSS2)<제1 부전위(VSS1)이다.

[0047] 그 다음, 상기 스캔 구동회로에 채택된 단계 전송 방식은 제N-2단계가 제N단계로 전송해주는 방식이며, 도 2에 도시된 바와 같이, 상기 스캔 구동회로의 제1단계 연결관계에서, 제11 트랜지스터(T11)의 게이트와 드레인은 회로의 시동 신호단(STV)에 전기적으로 연결된다.

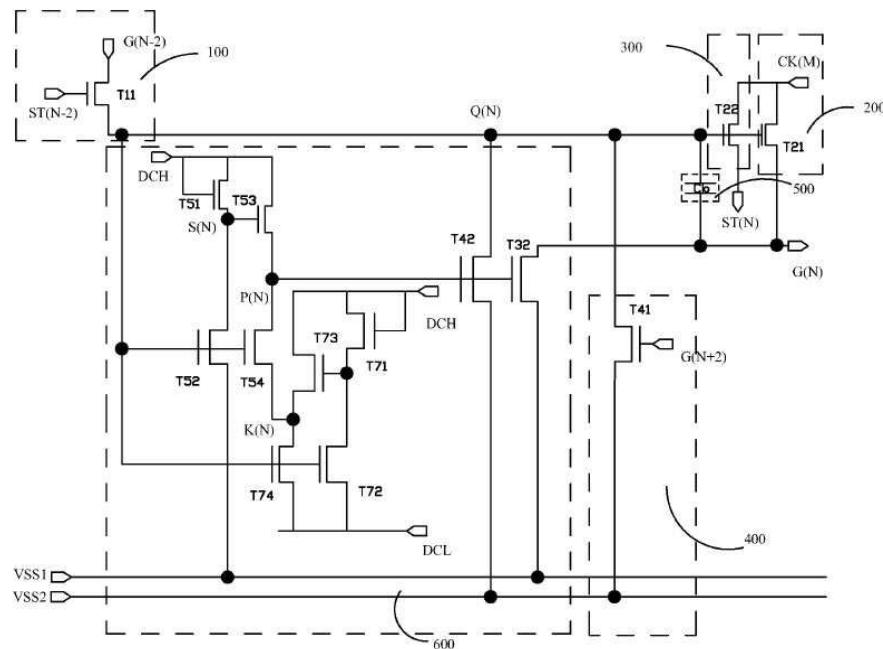

- [0048] 도 3에 도시된 바와 같이, 상기 스캔 구동회로의 제2단계 연결관계에서, 제11 트랜지스터(T11)의 게이트와 드레인은 모두 회로의 시동 신호단(STV)에 전기적으로 연결된다.

- [0049] 도 4에 도시된 바와 같이, 상기 스캔 구동회로의 끝에서 두 번째 단계의 연결관계에서, 제41 트랜지스터(T41)의 게이트는 회로의 시동 신호단(STV)에 전기적으로 연결된다.

- [0050] 도 5에 도시된 바와 같이, 상기 스캔 구동회로의 마지막 단계인 끝에서 첫 번째 단계의 연결관계에서, 제41 트랜지스터(T41)의 게이트는 회로의 시동 신호단(STV)에 전기적으로 연결된다.

- [0051] 또한, 제1 풀다운부(400)는 제41 트랜지스터(T41)만 제1 노드(Q(N))의 풀다운을 담당하고, 제41 트랜지스터(T41)의 게이트는 제N+2 단계 GOA 유닛의 출력단(G(N+2))에 전기적으로 연결되며, T41의 소스는 제2 부전위(VSS2)에 전기적으로 연결된다. 상기 클럭신호(CK(M))는 4세트의 클럭신호인 제1 클럭신호(CK(1)), 제2 클럭신호(CK(2)), 제3 클럭신호(CK(3)), 제4 클럭신호(CK(4))를 포함하며, 또한 클럭신호(CK(M))의 뉴티비는 제1 노드(Q(N))가 "凸"자형을 나타내도록 50/50 미만으로 설정하여야 하고, 상기 클럭신호(CK(M))의 파형 뉴티비는 40/60인 것이 바람직하다.

- [0052] 가장 중요한 것은, 상기 풀다운 유지회로부(600)는 특수한 이중 인버터 설계를 채택하였다는 점이다. 그 중 제51 트랜지스터(T51), 제52 트랜지스터(T52), 제53 트랜지스터(T53), 제54 트랜지스터(T54) 4개의 트랜지스터로 주 인버터를 구성하고, 제71 트랜지스터(T71), 제72 트랜지스터(T72), 제73 트랜지스터(T73), 제74 트랜지스터(T74) 4개의 트랜지스터로 보조 인버터를 구성한다. 상기 주 인버터의 작용은 제32 트랜지스터(T32)와 제42 트랜지스터(T42) 2개의 트랜지스터를 제어하는 것이고, 상기 보조 인버터의 작용은 작용 기간에 주 인버터로 저전위를 제공하고, 비작용 기간에 주 인버터에 적당한 고전위를 제공하여 제54 트랜지스터(T54)의 누전을 감소시킴으로써, 주 인버터가 비작용 기간에 비교적 높은 전위를 발생시킬 수 있도록 하는 것이다.

- [0053] 작용 기간에, 보조 인버터가 정전압 고전위(DCH)와 정전압 저전위(DCL)의 고/저 전압을 통해 구동된 후, 제52 트랜지스터(T52)는 제1 부전위(VSS1)로 풀다운되고, 제74 트랜지스터(T74), 제72 트랜지스터(T72)는 제1 노드(Q(N))가 고전위일 때 개방되어 정전압 고전위(DCH)를 풀다운시킴으로써, 제3 노드(K(N))를 더욱 낮은 전위에 이르게 하며, 제2 노드(P(N)) 역시 더욱 낮은 전위로 풀다운된다. 즉 보조 인버터가 작용 기간에 주 인버터로 저전위를 제공하기 때문에, 제32 트랜지스터(T32), 제42 트랜지스터(T42)에 임계전압이 비교적 낮거나 또는 0V에 가까워지는 물리적인 특성으로 유발되는 누전의 발생을 철저히 방지함으로써, 상기 풀다운 유지회로부(600)가 작용 기간에 정상적으로 풀다운될 수 있도록 보장한다.

- [0054] 비작용 기간에, 제52 트랜지스터(T52), 제54 트랜지스터(T54), 제72 트랜지스터(T72), 제74 트랜지스터(T74)는 모두 컷오프된다. 제54 트랜지스터(T54)의 게이트가 제1 노드(Q(N))에 전기적으로 연결되고, 소스는 제3 노드(K(N))에 전기적으로 연결되며, 상기 제54 트랜지스터(T54)의 게이트는 부전위이고, 소스는 정전위이기 때문에, Vgs는 상대적으로 상당히 음의 값인 전위로서, 제54 트랜지스터(T54)를 매우 잘 차단시켜 누전을 감소시킬 수 있으며, 즉 보조 인버터가 비작용 기간에 주 인버터로 하나의 적당한 고전위를 제공함으로써 제54 트랜지스터(T54)의 누전을 감소시키고, 상기 풀다운 유지회로부(600)가 비작용 기간에 비교적 높은 전위에 놓이도록 보장하며, 제1 노드(Q(N))와 출력단(G(N))은 저전위를 효과적으로 유지할 수 있다. 또한, 제3 노드(K(N))가 고전위일 경우, 저항 분압 기능을 더 구비하여, 제2 노드(P(N))의 전위가 더욱 높아지도록 할 수 있기 때문에, 제2 노드(P(N))의 전위를 안정화시킬 수 있다.

- [0055] 도 6을 참조하면, 본 발명의 산화물 반도체 박막 트랜지스터용 스캔 구동회로의 제2 실시예이다. 상기 제2 실시예와 제1 실시예의 차이점은, 상기 제41 트랜지스터(T41)의 소스가 출력단(G(N))에 전기적으로 연결된다는데 있으며, 제41 트랜지스터(T41)의 소스를 출력단(G(N))에 전기적으로 연결하면, 작용 기간에 상기 제41 트랜지스터(T41)를 통한 제1 노드(Q(N))의 누전을 감소시킬 수 있다. 이 부분을 제외하고, 도 6과 도 1 중 동일한 부호를 갖는 부분의 구성, 연결관계, 기능과 조작 원리가 같으므로, 여기서는 중복 설명을 생략한다.

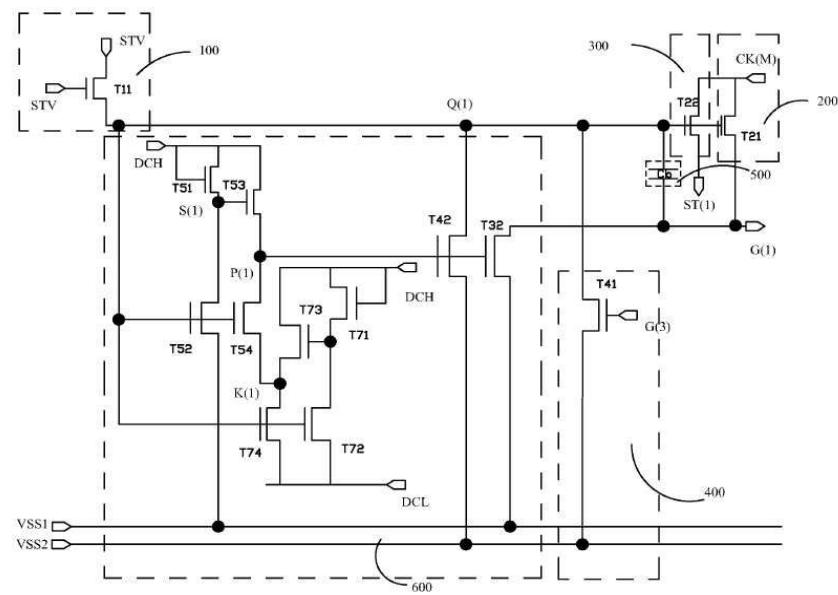

- [0056] 도 7을 참조하면, 본 발명의 산화물 반도체 박막 트랜지스터용 스캔 구동회로의 제3 실시예이다. 상기 제3 실시예와 제1 실시예의 차이점은, 상기 보조 인버터부에서 제71 트랜지스터(T71)와 제72 트랜지스터(T72)를 삭제하고, 상기 제73 트랜지스터(T73)의 게이트를 제4 노드(S(N))에 전기적으로 연결하여, 제73 트랜지스터(T73)와 제74 트랜지스터(T74)만으로 보조 인버터를 구성하였는데 있으며, 상기 보조 인버터는 주 인버터 중의 제4 노드(S(N))를 인용하여 제73 트랜지스터(T73)를 제어함으로써, 보조 인버터의 부품 수량을 감소시킬 수 있고, 별도의 부품으로 S(N) 노드와 유사한 파형을 발생시켜 제73 트랜지스터(T73)를 제어할 필요가 없다.

- [0057] 작용 기간에, 보조 인버터가 제4 노드(S(N))와 정전압 저전위(DCL)의 고/저 전압을 통해 구동된 후, 제52 트랜지

스터(T52)는 제1 부전위(VSS1)로 풀다운되고, 제74 트랜지스터(T74), 제1 노드(Q(N))가 고전위일 때 개방되어 정전압 고전위(DCH)를 풀다운시킴으로써, 제3 노드(K(N))를 더욱 낮은 전위에 이르게 하며, 제2 노드(P(N)) 역시 더욱 낮은 전위로 풀다운된다. 즉 보조 인버터가 작용 기간에 주 인버터로 저전위를 제공하기 때문에, 제32 트랜지스터(T32), 제2 트랜지스터(T42)에 임계전압이 비교적 낮거나 또는 0V에 가까워지는 물리적인 특성으로 유발되는 누전의 발생을 철저히 방지함으로써, 상기 풀다운 유지회로부(600)가 작용 기간에 정상적으로 풀다운될 수 있도록 보장한다.

[0058] 비작용 기간에, 제52 트랜지스터(T52), 제54 트랜지스터(T54), 제74 트랜지스터(T74)는 모두 컷오프된다. 제54 트랜지스터(T54)의 게이트가 제1 노드(Q(N))에 전기적으로 연결되고, 소스는 제3 노드(K(N))에 전기적으로 연결되며, 상기 제54 트랜지스터(T54)의 게이트는 부전위이고, 소스는 정전위이기 때문에,  $V_{GS}$ 는 상대적으로 상당히 음의 값인 전위로서, 제54 트랜지스터(T54)를 매우 잘 차단시켜 누전을 감소시킬 수 있으며, 즉 보조 인버터가 비작용 기간에 주 인버터로 하나의 적당한 고전위를 제공함으로써 제54 트랜지스터(T54)의 누전을 감소시키고, 상기 풀다운 유지회로부(600)가 비작용 기간에 비교적 높은 전위에 놓이도록 보장하며, 제1 노드(Q(N))와 출력단(G(N))은 저전위를 효과적으로 유지할 수 있다. 이밖에, 제3 노드(K(N))가 고전위일 경우, 저항 분압 기능을 더 구비하여, 제2 노드(P(N))의 전위가 더욱 높아지도록 할 수 있기 때문에, 제2 노드(P(N))의 전위를 안정화시킬 수 있다. 이 부분을 제외하고, 도 7과 도 1 중 동일한 부호를 갖는 부분의 구성, 연결관계, 기능과 조작 원리는 동일하므로, 여기서는 중복 설명을 생략한다.

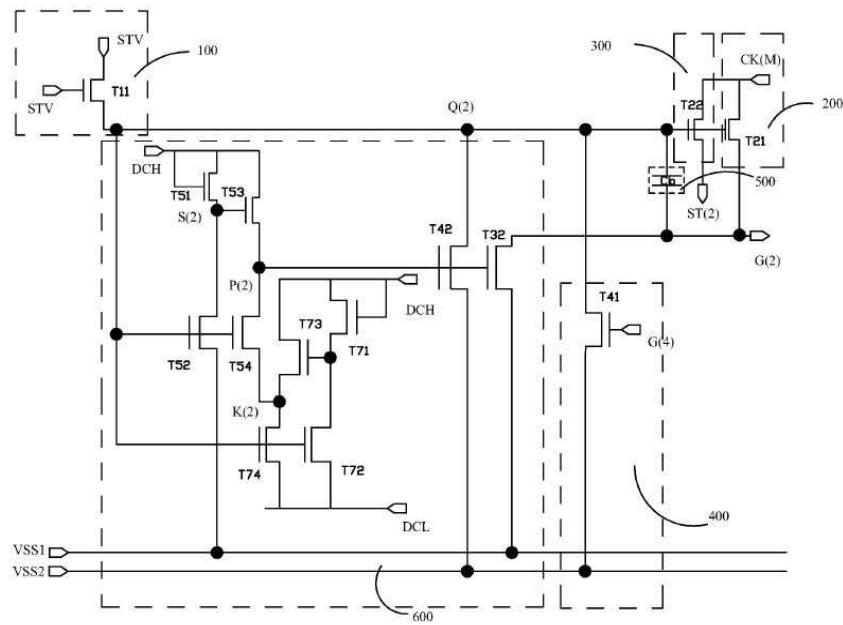

[0059] 도 8을 참조하면, 본 발명의 산화물 반도체 박막 트랜지스터의 스캔 구동회로의 제4 실시예이다. 상기 제4 실시예와 제3 실시예의 차이점은, 상기 제41 트랜지스터(T41)의 소스가 출력단(G(N))에 전기적으로 연결된다는 데 있으며, 제41 트랜지스터(T41)의 소스를 출력단(G(N))에 전기적으로 연결하면, 작용 기간에 상기 제41 트랜지스터(T41)를 통한 제1 노드(Q(N))의 누전을 감소시킬 수 있다. 이 부분을 제외하고, 도 8과 도 7 중 동일한 부호를 갖는 부분의 구성, 연결관계, 기능과 조작 원리가 같으므로, 여기서는 중복 설명을 생략한다.

[0060] 도 9를 참조하면, 본 발명의 산화물 반도체 박막 트랜지스터용 스캔 구동회로의 과형 설정과 키 노드의 출력 과형도이다. 그 중 STV는 회로의 시동 신호이고; CK(1)-CK(4)는 회로의 클럭신호이며, 여기에 도시된 클럭신호의 과형 뉴티비는 40/60으로서, 제1 노드의 Q(N)의 신호 출력 과형이 "凸"자형을 나타내도록 보장할 수 있다. VSS1, VSS2, DCH, DCL은 입력된 정전압 제어신호이고, DCH는 고전위이며, VSS1, VSS2, DCL은 모두 정전압 저전위이고, 또한 DCL<VSS2<VSS1이다. 나머지는 회로의 키 노드가 발생시키는 출력신호 과형이다. 도면을 통해 알 수 있듯이, 제1 노드(Q(N))의 신호 출력과형은 "凸"자형을 나타내고, 출력단(G(N))은 정상적으로 출력되며; 비작용 기간에, 제1 노드(Q(N))와 출력단(G(N))은 저전위에 처한다.

[0061] 결론적으로, 본 발명의 산화물 반도체 박막 트랜지스터용 스캔 구동회로의 풀다운 유지회로부는 주 인버터와 보조 인버터를 구비하고, 정전압 전위를 도입하여, 정전압 저전위<제2 부전위<제1 부전위로 설정함으로써, 산화물 반도체 박막 트랜지스터의 전기적 특성이 스캔 구동회로에 미치는 영향, 특히 누설전류 문제가 가져오는 기능성 불량을 방지할 수 있어, 풀다운 유지회로부가 작용 기간에는 정상적으로 풀다운되고, 비작용 기간에는 비교적 높은 전위에 처하여, 제1 노드와 출력단이 효과적으로 저전위를 유지할 수 있다.

[0062] 비록 본 발명은 바람직한 실시예를 상기와 같이 공개하였으나, 상기 바람직한 실시예는 결코 본 발명을 제한하기 위한 것이 아니며, 상기 분야의 보통 기술자라면 본 발명의 정신과 범위를 벗어나지 않고 각종 변경과 수식을 실시할 수 있으며, 따라서 본 발명의 보호범위는 청구항으로 한정된 범위를 기준으로 한다.

## 도면

## 도면1

## 도면2

## 도면3

## 도면4

## 도면5

## 도면6

## 도면7

## 도면8

## 도면9

## 【심사관 직권보정사항】

## 【직권보정 1】

【보정항목】 청구범위

【보정세부항목】 청구항 12

## 【변경전】

제11항에 있어서,

## 【변경후】

제10항에 있어서,

## 【직권보정 2】

【보정항목】 청구범위

【보정세부항목】 청구항 15

## 【변경전】

제11항에 있어서,

## 【변경후】

제10항에 있어서,

## 【직권보정 3】

【보정항목】 청구범위

【보정세부항목】 청구항 14

## 【변경전】

제11항에 있어서,

## 【변경후】

제10항에 있어서,

## 【직권보정 4】

【보정항목】 청구범위

【보정세부항목】 청구항 13

【변경전】

제11항에 있어서,

【변경후】

제10항에 있어서,