(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3964608号

(P3964608)

(45) 発行日 平成19年8月22日(2007.8.22)

(24) 登録日 平成19年6月1日(2007.6.1)

(51) Int.C1.

F 1

|              |           |            |      |

|--------------|-----------|------------|------|

| HO1L 21/027  | (2006.01) | HO1L 21/30 | 516A |

| GO3F 1/08    | (2006.01) | HO1L 21/30 | 502P |

| GO3F 7/20    | (2006.01) | GO3F 1/08  | A    |

| HO1L 21/82   | (2006.01) | GO3F 7/20  | 521  |

| HO1L 21/3205 | (2006.01) | HO1L 21/82 | W    |

請求項の数 4 (全 25 頁) 最終頁に続く

(21) 出願番号

特願2000-247702 (P2000-247702)

(22) 出願日

平成12年8月17日 (2000.8.17)

(65) 公開番号

特開2002-64043 (P2002-64043A)

(43) 公開日

平成14年2月28日 (2002.2.28)

審査請求日

平成16年12月3日 (2004.12.3)

(73) 特許権者 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(74) 代理人 100058479

弁理士 鈴江 武彦

(74) 代理人 100084618

弁理士 村松 貞男

(74) 代理人 100092196

弁理士 橋本 良郎

(74) 代理人 100091351

弁理士 河野 哲

(74) 代理人 100088683

弁理士 中村 誠

(74) 代理人 100070437

弁理士 河井 将次

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体基板と、

前記半導体基板上の第1の領域で、それぞれライン幅Lを有する導電体からなる第1、第2、第3、第4のラインパターンがそれぞれライン間スペースSを介して順に並ぶよう形成された第1のライン&スペースパターンと、

前記半導体基板上の第2の領域で、それぞれライン幅L以上を有する導電体からなる第5、第6のラインパターンがライン間スペースS以上を介して順に並ぶよう形成された第2のライン&スペースパターンと、

前記半導体基板上の前記第1の領域と第2の領域との間に存在する第3の領域で、前記第1のラインパターンと前記第5のラインパターンに連なる導電体からなる第7のラインパターンおよび前記第3のラインパターンと前記第6のラインパターンに連なる導電体からなる第8のラインパターンが形成された第3のライン&スペースパターンとを具備し、

前記第2のラインパターンは前記第1の領域と第3の領域との境界位置で終端されており、前記第4のラインパターンは前記第3の領域と第2の領域との境界位置で終端されており、

前記第7のラインパターンは、前記第3の領域内の長さ方向の途中でライン幅が変化し、前記第1のラインパターン側よりも前記第5のラインパターン側の方がライン幅が太くなるように形成されており、

前記第8のラインパターンは、前記第3の領域内の長さ方向の途中でライン幅が変化し

10

20

、前記第3のラインパターン側よりも前記第6のラインパターン側の方がライン幅が太くなるように形成されていることを特徴とする半導体装置。

【請求項2】

前記第7のラインパターンおよび第8のラインパターンのライン幅が変化する位置は、前記第3の領域と第1の領域との境界位置から長さ方向に前記S以上、かつ、前記第3の領域と第2の領域との境界位置から長さ方向に前記L以上の位置であることを特徴とする請求項1記載の半導体装置。

【請求項3】

前記第8のラインパターンと第4のラインパターンのスペースが、前記第3の領域において前記Sであることを特徴とする請求項1記載の半導体装置。 10

【請求項4】

前記第1の領域はメモリセルアレイが形成されている領域であり、前記第2の領域はメモリセル周辺回路が形成されている領域であることを特徴とする請求項1記載の半導体装置。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は、半導体装置とその製造方法および半導体装置パターン露光用マスクに係り、特にピッチの異なる配線を接続する領域における配線パターンおよびその形成方法ならびにそれに使用される半導体装置パターン露光用マスクに関するもので、例えばNAND型フラッシュメモリのメモリセルアレイ領域とメモリセル周辺回路領域との境界領域に適用されるものである。 20

【0002】

【従来の技術】

半導体メモリやマイクロプロセッサなどの半導体装置の製造には、光リソグラフィが用いられるのが一般的である。光リソグラフィとは、パターンを形成したパターン露光用マスクに光線を照射し、光学系を介して半導体基板上のフォトレジストに光線を投影し、フォトレジストを露光してマスクのパターンを半導体基板上へ転写する技術である。

【0003】

半導体装置は、高集積化、低コスト化などを目的として微細化が進められているが、そのためには光リソグラフィにより形成されるパターンの微細化を実現することがまず必要である。 30

【0004】

一般に、光リソグラフィにおける解像度Rと焦点深度DOFは、以下のレイリーの式で表される。

【0005】

$$R = k_1 (\quad / N_A)$$

$$DOF = k_2 (\quad / N_A^2)$$

ここで、 $\lambda$ ：光源の波長、NA：開口率、 $k_1$ 、 $k_2$ ：プロセス等による定数である。

【0006】

上式より分かるように、微細なパターンを転写するには光源の波長を短くすることが有効である。露光装置の光源として、従来は波長365 nmの*i*線が一般に用いられてきたが、さらに微細なパターンを形成するために、現在では波長248 nmのKrFエキシマレーザが一般に使用される。 40

【0007】

より微細化を進めるためには、より短波長の光源を用いること、 $k_1$ 、 $k_2$ を小さくすること、開口率NAを増加させること（高NA化）が必要となる。ここで、短波長の光源としては波長193 nmのArFエキシマレーザが有望とされているものの、ArFエキシマレーザ用の光学系やフォトレジスト等を含めた開発が困難であり、未だ実用化には至っていない。また、 $k_1$ 、 $k_2$ はレジストやプロセスの改良により小さくできるものの、一般 50

には0.4～0.5程度が限界となっている。また、高NA化に関しては、大面積を露光できる高NAレンズの加工が困難であることから実用的ではない。しかも、実際の露光では焦点深度をある程度以上確保する必要があるが、前記レイリーの式より明らかのように、高NA化を進めると焦点深度が低下してしまうため、この点からも高NA化は困難である。

#### 【0008】

上述したように、波長、開口率、プロセスの改善だけでは解像度の向上に限界がある。そこで、解像度をさらに高める技術として、ハーフトーン位相シフトマスクを使用する方法や、マスクパターンの露光に際して変形照明を使用する方法など、いわゆる超解像技術が用いられるようになってきている。ここで、超解像技術について簡単に説明する。

#### 【0009】

ハーフトーン位相シフトマスクでは、ラインパターン部でも完全に光を遮断せずに、クロムなどの代わりに一般に透過係数3～10%の半透明な膜を形成して光を透過させ、しかも、透過光の位相を180度ずらすようにする。この時、ラインパターン部を透過する光とスペースパターン部を透過する光との間に生じる干渉により、ラインパターンとスペースパターンの境界における光強度分布が急峻になるようにして解像度を向上させるものである。これに対して、通常のマスクでは、ラインパターン部は、通常はフォトレジストが露光されないようにクロムなどで光を遮断するようになっている。

#### 【0010】

また、変形照明法では、光源の中心付近を遮光するアパーチャを設置することによって、斜め方向に入射する光のみをマスクに照射する。このような変形照明法を使用した場合、回折光の内の±1次光のどちらかは投影されず、残った一方の回折光が投影される。このような0次光と±1次光のいずれかの2つの光束を用いて結像させる方法により解像度を向上させることができる。これに対して、通常の照明方法では、光源よりマスクに照射された光は、0次光と回折により生じた±1次光の3つの光束が投影されることによって半導体基板上に光学像が結像される。

#### 【0011】

しかし、上述したような超解像技術は、周期的に配置された密なパターンに対しては非常に有効であるが、密なパターンと同時に疎なパターンを形成することが困難である。これに関して、例えば以下のようないわゆる問題がある。

#### 【0012】

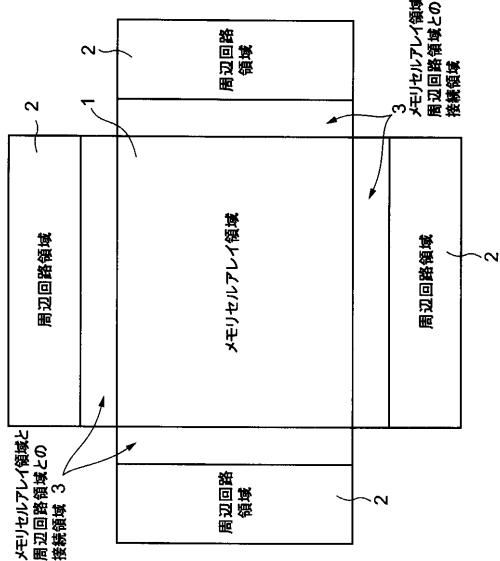

図19は、半導体メモリの一般的なパターン配置を示している。

#### 【0013】

メモリセルアレイ領域1を囲むように、メモリセルアレイを駆動する周辺回路領域2が配置される。メモリセルアレイ領域1のゲート線や金属配線などは、一般に単純なライン・アンド・スペース(ライン&スペース)のような周期的に配置された密なパターンにより形成されるが、周辺回路領域2のゲート線や金属配線は、メモリセルアレイ領域1よりも疎なパターンにより形成されている。また、周辺回路領域2におけるゲート線や金属配線は、ある程度の周期性はもつが、メモリセルアレイ領域1よりも複雑なパターンになっている。そして、メモリセルアレイ領域1のゲート線や金属配線は、そのままメモリセルアレイ領域1の外に延び、接続領域3を経て周辺回路領域2のゲート線や金属配線に接続される。

#### 【0014】

しかし、このようなメモリセルアレイ領域1と周辺回路領域2との間の接続領域3では、メモリセルアレイ領域1内の微細なライン・アンド・スペースのパターンがそのまま延びてきている上にパターンの周期性が崩れているので、この接続領域3における解像度や焦点深度が悪化しやすい。その結果、所望通りのパターンが形成されず、配線の断線やショートの原因になる。

#### 【0015】

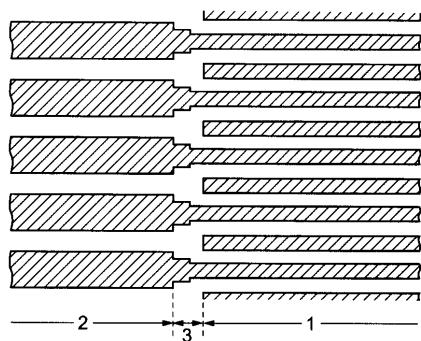

図20は、図19中のメモリセルアレイ領域1と周辺回路領域2とを接続する配線パターンが形成されたパターン露光用マスクを示す。

10

20

30

40

50

## 【0016】

図中、メモリセルアレイ領域1には、ライン幅L、ライン間スペースS、ピッチ( $L + S$ )の配線パターンが形成されており、周辺回路領域2には、ピッチが $2 \times (L + S)$ の配線パターンが形成されており、接続領域3にはメモリセルアレイ領域1の例えは奇数番の配線パターンを周辺回路領域2の配線パターンに接続するための配線パターンが形成されている。この場合、メモリセルアレイ領域1の残り(偶数番)の各配線パターンは、一端が接続領域3との境界線上で終端されている。また、接続領域3の各配線パターンは、ライン幅が二段階に変化しており、それぞれの変化位置は同一線上に揃っている。

## 【0017】

図21は、図20に示したパターン露光用マスクを用いて半導体基板上のレジストに露光した時に得られるレジストパターンをシミュレーションにより求めた結果を示す。ここで、レジストパターンは、光強度分布を求め、等強度の分布を示したものであり、レジストパターン中の3本の線は、配線寸法が狙い通りにできる光強度と、それより+/-10%の光強度のそれぞれにおけるレジストのパターンを示す。

10

## 【0018】

上記シミュレーションの計算の条件として、半導体基板上の配線のライン幅、ライン間スペースは共に半導体基板上で $0.15 \mu m$ であり、光源は波長 =  $248 nm$ のKrFエキシマレーザ、開口率NA = 0.6、コヒーレント係数 = 0.75としており、光源の中央部分を覆う(面積比率で光源全体の3分の2を覆う)輪帯を使用した。また、パターン露光用マスクとして、透過率6%、位相を180度回転させるハーフトーン型位相シフトマスクを使用した。また、焦点深度が確保できているかどうか調べるために、最適フォーカスから $0.4 \mu m$ ずらした条件で露光されていると仮定した。

20

## 【0019】

しかし、図21に示した3本のシミュレーション結果のうち、最もライン幅が細いもの、即ち、露光量が最適値より10%増加した場合に配線の断線が生じていることが分かる。即ち、実際の露光では露光量のばらつきやレジスト感度などに起因して配線の断線が発生する可能性があり、誤動作の原因となる。このように配線の周期性が途切れた部分で所望のパターンが形成されないのは、配線の終端部あるいは配線のライン幅が変化する部分で生じた回折光が隣接パターンに影響を及ぼしているからである。

## 【0020】

30

上述したように超解像技術を用いることによってメモリセルアレイ領域における微細化が可能であっても、前述のようなメモリセルアレイ領域と周辺回路領域との間の配線の接続領域3において所望通りのパターンを形成することが困難であり、場合によっては、この接続領域3のパターン部分によりメモリセルアレイのピッチが制限され、半導体メモリのチップサイズの増大につながるという問題があった。

## 【0021】

## 【発明が解決しようとする課題】

上記したように従来の半導体メモリは、露光装置の光源の波長以下のようないくつかの微細なピッチでライン & スペースの配線パターンが形成されているメモリセルアレイ領域と、それよりは大きいピッチで配線パターンが形成されている周辺回路領域との境界領域において、光リソグラフィを用いた配線パターン形成時の光の干渉などにより解像度や焦点深度が悪化し易く、所望通りのパターンが形成されず、配線の断線やショートが発生し易いという問題があった。

40

## 【0022】

本発明は上記の問題点を解決するためになされたもので、露光装置の光源の波長以下のようないくつかの微細なピッチPでライン & スペースの配線パターンが形成されている第1領域と、それよりは大きいピッチで配線パターンが形成されている第2領域との境界領域における光リソグラフィを用いた配線パターン形成時の解像度や焦点深度の悪化を抑制し、ピッチの異なる配線を接続する領域における配線パターンの断線やショートを防止でき、高集積化が可能となる半導体装置を提供することを目的とする。

50

## 【0023】

## 【課題を解決するための手段】

本発明の半導体装置は、半導体基板と、前記半導体基板上の第1の領域で、それぞれライン幅Lを有する導電体からなる第1、第2、第3、第4のラインパターンがそれぞれライン間スペースSを介して順に並ぶように形成された第1のライン&スペースパターンと、前記半導体基板上の第2の領域で、それぞれライン幅L以上を有する導電体からなる第5、第6のラインパターンがライン間スペースS以上を介して順に並ぶように形成された第2のライン&スペースパターンと、前記半導体基板上の前記第1の領域と第2の領域との間に存在する第3の領域で、前記第1のラインパターンと前記第5のラインパターンに連なる導電体からなる第7のラインパターンおよび前記第3のラインパターンと前記第6のラインパターンに連なる導電体からなる第8のラインパターンが形成された第3のライン&スペースパターンとを具備し、前記第2のラインパターンは前記第1の領域と第3の領域との境界位置で終端されており、前記第4のラインパターンは前記第3の領域と第2の領域との境界位置で終端されており、前記第7のラインパターンは、前記第3の領域内の長さ方向の途中でライン幅が変化し、前記第1のラインパターン側よりも前記第5のラインパターン側の方がライン幅が太くなるように形成されており、前記第8のラインパターンは、前記第3の領域内の長さ方向の途中でライン幅が変化し、前記第3のラインパターン側よりも前記第6のラインパターン側の方がライン幅が太くなるように形成されていることを特徴とする。

## 【0024】

本発明の第2の半導体装置は、半導体基板と、前記半導体基板上の第1の領域で、それ

ぞれ導電体からなる複数(n)本のラインパターンが第1のライン間スペースを介してピッ

チP1で順に並ぶように形成された第1、第2、第3、第4のライン&スペースパターンと、前記半導体基板上の第2の領域で、それぞれ導電体からなるn本のラインパターンが第2のライン間スペースを介してP1より大きなピッチP2で繰り返すように形成された第5、第6のライン&スペースパターンと、前記半導体基板上の前記第1の領域と第2の領域との間に存在する第3の領域で、前記第2のライン&スペースパターンのn本の導電体からなるラインパターンと前記第5のライン&スペースパターンのn本の導電体からなるラインパターンに連なるn本の導電体からなるラインパターンおよびライン間スペースが繰り返すように形成された第7のライン&スペースパターン、ならびに、前記第3のライン&スペースパターンのn本の導電体からなるラインパターンと前記第6のライン&スペースパターンのn本の導電体からなるラインパターンに連なるn本の導電体からなるラインパターンおよびライン間スペースが繰り返すように形成された第8のライン&スペースパターンとを具備し、前記第1のライン&スペースパターンおよび第4のライン&スペースパターンの各ラインパターンは前記第1の領域と第3の領域との境界位置および第3の領域内で終端されており、前記第7のライン&スペースパターンおよび第8のライン&スペースパターンの各ラインパターンの各一部は、前記第1の領域のパターンの長さ方向に対して斜めに配置されており、かつ、斜めに配置された部分のピッチP3は、P1 < P3 < P2であることを特徴とする。

## 【0025】

本発明の第3の半導体装置は、半導体基板と、前記半導体基板上の第1の領域で、導電体からなる複数(n)本のラインパターンがそれぞれライン間スペースSを介して順に並ぶように形成された第1のライン&スペースパターンと、前記半導体基板上の第2の領域で、導電体からなるn/2本のラインパターンがライン間スペースを介して繰り返すように形成された第2のライン&スペースパターンと、前記半導体基板上の前記第1の領域と第2の領域との間に存在する第3の領域で、前記第1のライン&スペースパターンのうちの1つ置きのn/2本のラインパターンと前記第2のライン&スペースパターンの前記n/2本のラインパターンに連なるn/2本の導電体からなるラインパターンが形成された第3のライン&スペースパターンとを具備し、前記第1のライン&スペースパターンのうちで前記第2のライン&スペースパターンに連ならないn/2本の各ラインパターンは、

10

20

30

40

50

前記第1の領域と第3の領域との境界位置、前記第3の領域と第2の領域との境界位置、第3の領域内のいずれかの位置で終端されていることを特徴とする。

【0035】

【発明の実施の形態】

以下、図面を参照して本発明の実施の形態を詳細に説明する。

【0036】

<第1の実施の形態に係る半導体装置パターン露光用マスク>

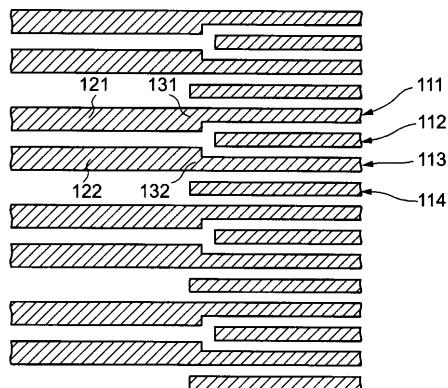

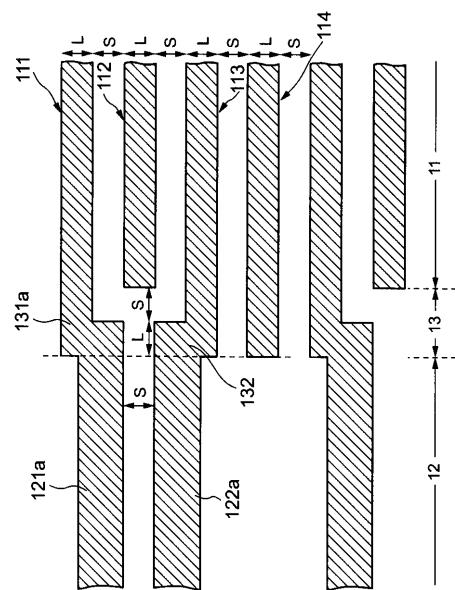

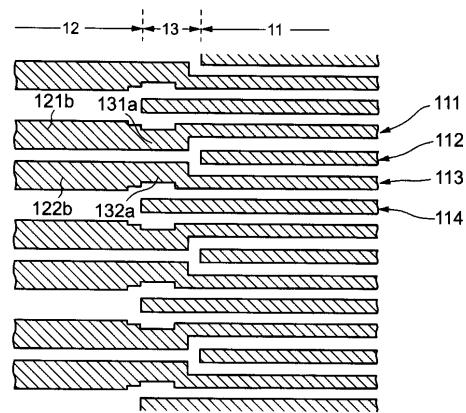

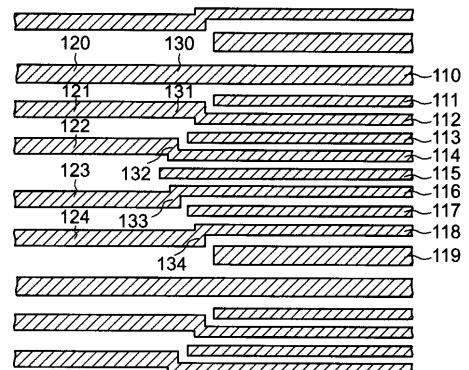

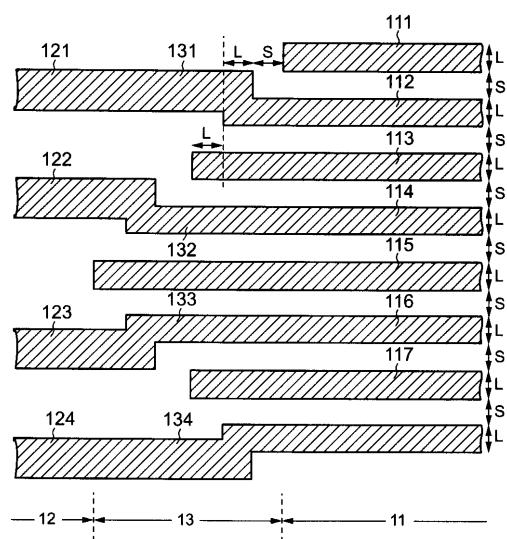

図1は、本発明の第1の実施の形態に係る半導体装置パターン露光用マスクに形成されているマスクパターンの一部を示す平面図である。図2は、図1のマスクパターンの一部を取り出して拡大して示している。

10

【0037】

図1および図2に示すマスクパターンは、半導体メモリのパターン露光用マスクであり、11はメモリセルアレイ領域に対応する第1のマスク領域、12は周辺回路領域に対応する第2のマスク領域、13はメモリセルアレイ領域と周辺回路領域との境界領域（接続領域）に対応する第3のマスク領域を示している。そして、斜線部は遮光部（遮光体パターン）、白地部は透光部を示しており、それぞれ対応して半導体基板上にラインパターン、スペースパターンを転写するためのものである。

【0038】

第1のマスク領域11には、第1のラインパターン111、第2のラインパターン112、第3のラインパターン113および第4のラインパターン114がそれぞれライン幅Lを有し、それぞれライン間スペースSを介して順に並び（配線ピッチはL+Sである）、かつ、これらのラインパターン111～114が少なくとも2組以上周期的に繰り返すように配置された第1のライン&スペースパターンが形成されている。

20

【0039】

第2のマスク領域12には、それぞれライン幅L以上を有する第5のラインパターン121および第6のラインパターン122がライン間スペースS以上を介して並び（配線ピッチは、 $2 \times (L + S)$ である）、かつ、これらのラインパターン121、122が少なくとも2組以上周期的に繰り返すように配置された第2のライン&スペースパターンが形成されている。

【0040】

30

前記第1のマスク領域11におけるラインパターン111～114のうちの第1のラインパターン111および第3のラインパターン113の各一端側は、延長され、第3のマスク領域13における第7のラインパターン131および第8のラインパターン132を経て第2のマスク領域12における第5のラインパターン121および第6のラインパターン122に接続されている。

【0041】

これに対して、前記第1のマスク領域11におけるラインパターン111～114のうちの第2のラインパターン112および第4のラインパターン114の各一端側は、第3のマスク領域12において終端されている。この場合、第2のラインパターン112は、第1のマスク領域11と第3のマスク領域13との境界位置で終端されており、第4のラインパターン114は第3のマスク領域13と第2のマスク領域12との境界位置まで延長されて終端されている。

40

【0042】

即ち、第3のマスク領域13には、第1のラインパターン111と第5のラインパターン121に連なる第7のラインパターン131および第3のラインパターン113と第6のラインパターン122に連なる第8のラインパターン132が並び、かつ、上記第5、第6のラインパターンが少なくとも2組以上周期的に繰り返すように配置された第3のライン&スペースパターンが形成されている。

【0043】

なお、第1のマスク領域11の他端側にも、図1中に示した第3のマスク領域13および第2のマスク領域12と対称的に、図示しない第3のマスク領域および第2のマスク領域が存在

50

している。そして、第1のマスク領域11における第1のラインパターン111 および第3のラインパターン113 の各他端側は、図示しない第3のマスク領域において終端されている。また、第1のマスク領域11における第2のラインパターン112 および第4のラインパターン114 の各他端側は、延長され、図示しない第3のマスク領域内を経て図示しない第2のマスク領域のラインパターンに接続されている。こうして、第1のマスク領域11の全てのラインパターン111 ~ 114 が第2のマスク領域へ接続されるようにしている。

【0044】

さらに、第3のマスク領域13内において、第7のラインパターン131 は、長さ方向の途中でライン幅が段状に変化し、第1のラインパターン111 側よりも第5のラインパターン121 側の方がライン幅が段状に太くなるように形成されている。同様に、第8のラインパターン132 は、第3のマスク領域13内の長さ方向の途中でライン幅が段状に変化し、第3のラインパターン113 側よりも第6のラインパターン122 側の方がライン幅が段状に太くなるように形成されている。10

【0045】

第7のラインパターン131 および第8のラインパターン132 のライン幅が段状に変化する位置は、第3のマスク領域13と第1のマスク領域11との境界位置から長さ方向にS以上、かつ、第3のマスク領域13と第2のマスク領域12との境界位置から長さ方向にL以上の位置である。

【0046】

本例では、第7のラインパターン131 の一部として、第1のラインパターン111 がそのライン幅のままで第3のマスク領域13内へパターン長さ方向へ距離Sの部分まで延びており、この距離Sの部分で第7のラインパターン131 のライン幅が広くなっている。同様に、第8のラインパターン132 の一部として、第3のラインパターン113 がそのライン幅のままで第3のマスク領域13内へパターン長さ方向へ距離Sの部分まで延びており、この距離Sの部分で第8のラインパターン132 のライン幅が広くなっている。20

【0047】

また、第7のラインパターン131 および第8のラインパターン132 と平行に、第1のマスク領域11における第4のラインパターン114 がそのライン幅Lのまま延びている。

【0048】

ここで、上記した第1の実施の形態に係る半導体装置パターン露光用マスクの特徴を要約すると、(a) ラインパターンが遮光部により形成され、スペースパターンが透光部により形成されるマスク基板と、(b) 前記マスク基板上の第1の領域で、それぞれライン幅Lを有する第1、第2、第3、第4のラインパターンがそれぞれライン間スペースSを介して順に並ぶように形成された第1のライン&スペースパターンと、(c) 前記マスク基板上の第2の領域で、それぞれライン幅L以上を有する第5、第6のラインパターンがライン間スペースS以上を介して順に並ぶように形成された第2のライン&スペースパターンと、(d) 前記マスク基板上の前記第1の領域と第2の領域との間に存在する第3の領域で、前記第1のラインパターンと前記第5のラインパターンに連なる遮光体からなる第7のラインパターンおよび前記第3のラインパターンと前記第6のラインパターンに連なる遮光体からなる第8のラインパターンが形成された第3のライン&スペースパターンとを具備している。そして、(e) 前記第2のラインパターンは前記第1の領域と第3の領域との境界位置で終端されており、前記第4のラインパターンは前記第3の領域と第2の領域との境界位置まで延長されて終端されており、(f) 前記第7のラインパターンは、第3の領域内の長さ方向の途中でライン幅が変化し、前記第1のラインパターン側よりも前記第5のラインパターン側の方がライン幅が太くなるように形成されており、(g) 前記第8のラインパターンは、第3の領域内の長さ方向の途中でライン幅が変化し、前記第3のラインパターン側よりも前記第6のラインパターン側の方がライン幅が太くなるように形成されており、(h) 前記各ライン&スペースパターンはそれぞれ対応する領域で少なくとも2組以上周期的に繰り返すように配置されている。3040

【0049】

なお、第7のラインパターン131 および第8のラインパターン132 のライン幅が段状に変化する位置は、第3のマスク領域13と第1のマスク領域11との境界位置からSより大きくても構わないが、余り大きくすると、パターンの占有面積が大きくなってしまい、製作しようとする半導体装置のコスト増加を招き、望ましくない。そこで、この部分の距離はSとすることが適当である。

【0050】

上述したマスクパターンにおいて、マスク上の最小スペースはSであり、このマスク上の最小スペースSは、ライン&スペースパターンの最小スペースSと合わせることが望ましい。その理由を以下に説明する。

【0051】

マスクの製造工程において、ダストなどに起因してマスクのパターンが所望のものとは異なるってしまう可能性がある。そこで、マスク上にパターンを形成した後、欠陥の有無を検査する必要がある。欠陥の検査は、レーザー顕微鏡など、光を用いた検査装置で行われるので、検査可能なパターンの大きさは、検査装置の光源の波長により制限される。欠陥検査を完全に行うためには、パターンの寸法をある程度大きい値にしておく必要がある。

【0052】

メモリセルアレイ領域と周辺回路領域を同時に形成するためのマスクでは、一般に、あるマスク内に存在する最も寸法の小さいパターンは、メモリセルアレイ領域内のパターンに対応する。したがって、マスク内のあらゆるパターンの配線ライン幅および配線間スペースを、メモリセルアレイ領域の配線のライン幅と配線間スペースにそれぞれ合わせておけば、マスク内の欠陥の検査を完全に行うことができるようになる。

【0053】

また、半導体メモリのゲート線や配線を形成した後に、前記マスクのライン間スペースに対応するパターン部分は後で層間絶縁膜で埋め込まれるが、この時、ゲート線間や配線間のスペースが小さ過ぎると、この部分に層間絶縁膜を埋め込むことができないおそれがある。すると、この部分に異物が残り、メモリの誤動作の原因となるおそれがある。このように層間絶縁膜の埋め込みを完全に行うためにも、ゲート線や配線のスペースはメモリセルアレイ領域の最小スペースに合わせておくことが望ましい。

【0054】

なお、光リソグラフィでは、一般に縮小投影露光が用いられるので、マスクパターンの寸法は半導体基板上に形成されるレジストパターンの寸法の4倍あるいは5倍などの値となる。即ち、例えば $0.15\text{ }\mu\text{m}$ のレジストパターンを形成するためのマスクの寸法は $0.6\text{ }\mu\text{m}$ や $0.75\text{ }\mu\text{m}$ などになる。以下、説明の簡単化のため、マスクパターンの寸法をレジストパターンと同じとして説明している。

【0055】

<第1の実施形態に係る半導体装置>

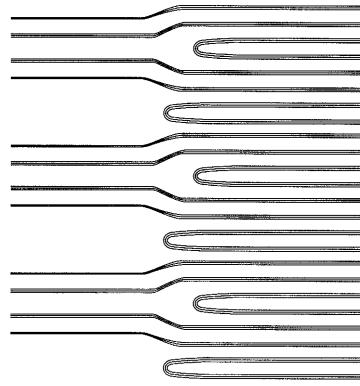

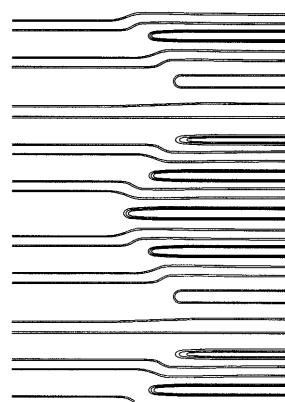

図3は、図1のマスクパターンを使用して半導体装置上のフォトレジストに露光することにより得られるレジストパターンを光学シミュレーションにより求めた結果を示している。

【0056】

ここで、前記マスクのラインパターンに対応するラインパターンのライン幅、ライン間スペースが共に半導体基板上で $0.15\text{ }\mu\text{m}$ であり、光源の波長 =  $248\text{ nm}$ のKrFエキシマレーザ、開口率NA = 0.6、コヒーレント係数 = 0.75とし、光源の中央部分を光源全体の面積に対して3分の2程度覆う輪帯を適用し、遮光部には透過率6%、位相を180度回転させるハーフトーン型位相シフトマスクを使用した場合について計算したものである。

【0057】

また、実際の露光に際しては、露光装置のステージ高さのずれや、半導体基板の反りなどに起因する段差、基板上の段差などによるフォーカスのずれを考慮する必要があり、フォーカスのずれを $0.4\text{ }\mu\text{m}$ として計算している。

【0058】

10

20

30

40

50

以上の条件下で光学シミュレーションにより半導体基板上の光強度分布を求め、等強度の分布を図3に示したものであり、図中の3本の線は、配線寸法が狙い通りの0.15μmになる光強度と、それより+/-10%の光強度のそれぞれにおけるレジストのパターンを示す。

#### 【0059】

図3に示したレジストパターンは、図1のマスクパターンに対応して形成されており、配線の断線、ショートなどが見られず、また、ライン幅が極端に細い部分やスペースが極端に狭い部分も見られない。図21に示した従来のレジストパターンと比較すると、配線の終端部や配線のライン幅が変化する部分同士の距離が適度に離れて配置されるので、そのような部分で生じる回折光の影響によって隣接する配線パターンに不具合が生じ難くなっていることが分かる。したがって、図1のマスクパターンを用いて実際に半導体基板上にパターン露光を行った場合にも、十分なプロセスマージンを確保でき、良好な配線パターンが得られるものと予想される。

#### 【0060】

ここで、図1のマスクパターンを用いて形成された第1の実施の形態に係る半導体装置のパターンの特徴を要約すると、(a)半導体基板上の第1の領域で、それぞれライン幅Lを有する導電体からなる第1、第2、第3、第4のラインパターンがそれぞれライン間スペースSを介して順に並ぶように形成された第1のライン&スペースパターンと、(b)半導体基板上の第2の領域で、それぞれライン幅L以上を有する導電体からなる第5、第6のラインパターンがそれぞれライン間スペースS以上を介して順に並ぶように形成された第2のライン&スペースパターンと、(c)半導体基板上の前記第1の領域と第2の領域との間に存在する第3の領域で、前記第1のラインパターンと前記第5のラインパターンに連なる導電体からなる第7のラインパターンおよび前記第3のラインパターンと前記第6のラインパターンに連なる導電体からなる第8のラインパターンが形成された第3のライン&スペースパターンとを具備している。そして、(d)前記第2のラインパターンは前記第1の領域と第3の領域との境界位置で終端されており、前記第4のラインパターンは前記第3の領域と第2の領域との境界位置まで延長されて終端されており、(e)前記第7のラインパターンは、第3の領域内の長さ方向の途中でライン幅が段状に変化し、前記第1のラインパターン側よりも前記第5のラインパターン側の方がライン幅が段状に太くなるように形成されており、(f)前記第8のラインパターンは、第3の領域内の長さ方向の途中でライン幅が段状に変化し、前記第3のラインパターン側よりも前記第6のラインパターン側の方がライン幅が段状に太くなるように形成されており、(g)前記各ライン&スペースパターンはそれぞれ対応する領域で少なくとも2組以上周期的に繰り返すように配置されている。

#### 【0061】

<第1の実施形態に係る半導体装置の製造方法>

次に、図1のマスクを使用して半導体基板上のフォトレジストにパターンを転写し、配線パターンを形成する方法について簡単に説明する。

#### 【0062】

まず、半導体基板上に堆積された導電体膜(金属膜あるいは半導体膜)上にフォトレジストを塗布し、このフォトレジストに対して図1のマスクを用いて光リソグラフィによりパターン露光を行う。次に、露光後のフォトレジストの一部を剥離し、導電体膜の露出部をエッチング除去してパテーニングを行う。この際、露光工程は、通常照明法を用いてもよいが、変形照明法を用いることも可能である。また、図1のマスクの各遮光部を位相を変化させる半透明な材料に変えたハーフトーン位相シフトマスクを使用することも可能である。

#### 【0063】

<第1の実施形態に係るマスク、半導体装置およびその製造方法の変形例>

第1の実施形態に係るマスクの変形例として、第1の実施形態に係るマスクにおけるライン&スペースパターンにおける遮光部と透光部を逆にした反転マスクを構成してもよい。

#### 【0064】

10

20

30

40

50

次に、この反転マスクを使用して半導体基板上のフォトレジストにパターンを転写し、配線パターンを形成する方法について簡単に説明する。

#### 【0065】

まず、半導体基板上の絶縁膜上にフォトレジストを塗布し、このフォトレジストに対して前記反転マスクを用いて光リソグラフィによりパターン露光を行う。次に、前記露光後のフォトレジストの一部を剥離し、絶縁膜の露出部をエッチング除去して配線形成用の溝を形成する。この後、配線形成用の溝の内部に導電体を埋め込み形成する。この際、露光工程は、通常照明法を用いてもよいが、変形照明法を用いることも可能である。また、反転マスクの各遮光部を位相を変化させる半透明な材料に変えたハーフトーン位相シフトマスクを使用することも可能である。

10

#### 【0066】

〈第2の実施の形態に係るマスク〉

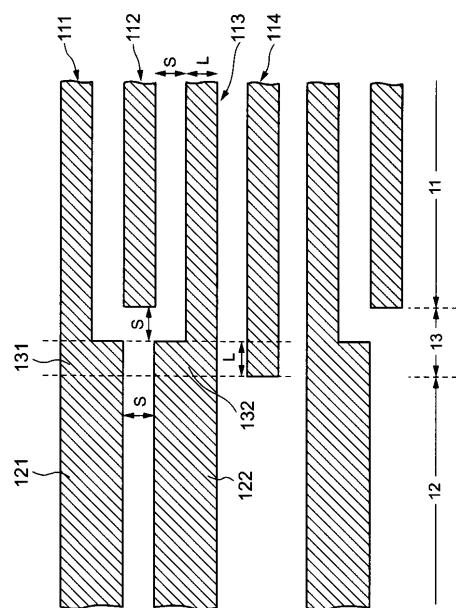

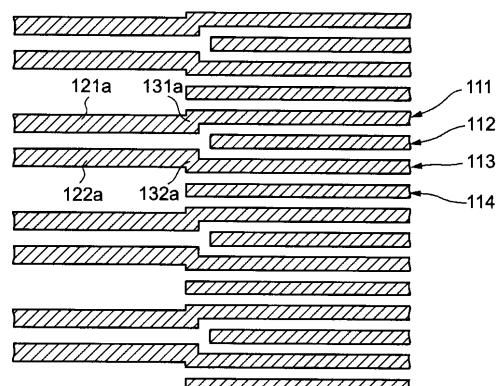

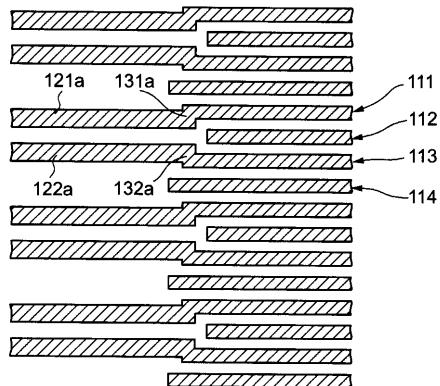

図4は、本発明の第2の実施の形態に係る半導体装置パターン露光用マスクに形成されているマスクパターンの一部を示す平面図である。図5は、図4のマスクパターンの一部を取り出して拡大して示している。

#### 【0067】

図4および図5に示すマスクパターンは、図1および図2を参照して前述した第1の実施の形態に係るマスクパターンと比べて、(1)第2のマスク領域12内において、第5のラインパターン121の位置が図面の下方向へ少しシフトしており、結果として、第3のマスク領域13内において、第7のラインパターン131aが段状に屈曲している点、(2)第2のマスク領域12内において、第6のラインパターン122の位置が図面の上方向(第5のラインパターン121のシフト方向とは逆方向)へ少しシフトしており(第5のラインパターン121との間隔はS以上)、結果として、第3のマスク領域13内において、第8のラインパターン132aが段状に屈曲している点が異なり、その他は同じであるので図1および図2中と同一符号を付している。

20

#### 【0068】

即ち、第3のマスク領域13において、第7のラインパターン131aは、長さ方向の途中でライン幅が段状に変化し、第1のラインパターン111側よりも第5のラインパターン121a側の方がライン幅が段状に太くなるように形成されている。同様に、第8のラインパターン132aは、第3のマスク領域13内の長さ方向の途中でライン幅が段状に変化し、第3のラインパターン113側よりも第6のラインパターン122a側の方がライン幅が段状に太くなるように形成されている。

30

#### 【0069】

上記第7のラインパターン131aおよび第8のラインパターン132aが屈曲する向きは、それぞれが互いに接近する方向になっている。また、屈曲している部分の配線のライン幅はLである。この部分のライン幅はLよりも大きくてかまわないが、占有面積の増大につながるため望ましくなく、Lとすることが適当である。

#### 【0070】

また、上記第7のラインパターン131aおよび第8のラインパターン132aと平行に、第1のマスク領域11における第4のラインパターン114がそのライン幅Lのまま延びている。上記第7のラインパターン131a、第8のラインパターン132aおよび第4のラインパターン114のピッチは $2 \times (L + S)$ となっており、ライン間スペースはSとなっているが、Sよりも大きくて構わない。

40

#### 【0071】

前記第7のラインパターン131aおよび第8のラインパターン132aのライン幅が段状に屈曲する位置は、第3のマスク領域13と第1のマスク領域11との境界位置から長さ方向に前記S以上、かつ、第3のマスク領域13と第2のマスク領域12との境界位置から長さ方向に前記L以上(本例ではL)の位置である。

#### 【0072】

本例では、第7のラインパターン131aおよび第8のラインパターン132aは、前記第1のラ

50

インパターン111 および第3のラインパターン113 がそのライン幅のままで第3のマスク領域13内へパターン長さ方向へ距離Sの部分まで延び、この部分でライン幅が広くなっている。

【0073】

なお、上記第7のラインパターン131aおよび第8のラインパターン132aのライン幅が段状に屈曲する位置は、第3のマスク領域13と第1のマスク領域11との境界位置からSより大きくても構わないが、余り大きくすると、パターンの占有面積が大きくなってしまい、製作しようとする半導体装置のコスト増加を招き、望ましくない。そこで、この部分の距離はSとすることが適当である。

【0074】

上述したマスクパターンにおいて、マスク上の最小スペースはSであり、このマスク上の最小スペースSは、ライン&スペースパターンの最小スペースSと合わせることが望ましい。その理由は第1の実施の形態で前述した通りである。

【0075】

<第2の実施形態に係る半導体装置>

図6は、図4のマスクパターンを使用して半導体装置上のフォトレジストに露光することにより得られるレジストパターンを光学シミュレーションにより求めた結果を示している。このシミュレーションに際して、光源の条件などは第1の実施の形態と同様である。

【0076】

図6に示すレジストパターンは、図4のマスクパターンに対応して形成されており、配線の断線、ショートなどが見られず、また、ライン幅が極端に細い部分やスペースが極端に狭い部分も見られない。したがって、実際に半導体基板上にパターン露光を行った場合にも、十分なプロセスマージンを確保でき、良好な配線パターンが得られるものと予想される。

【0077】

なお、第2の実施形態に係る半導体装置の製法は、前述した第1の実施形態に準じて実施すればよく、また、図4のマスクパターンの反転マスクを使用して製造することも可能である。

【0078】

<第3の実施の形態に係るマスク>

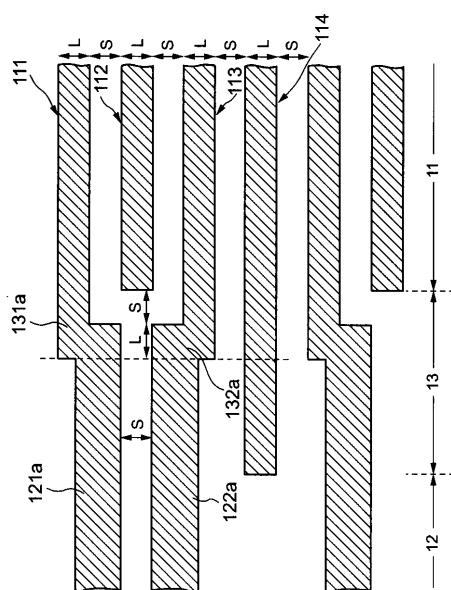

図7は、本発明の第3の実施の形態に係る半導体装置パターン露光用マスクに形成されているマスクパターンの一部を示す平面図である。図8は、図7のマスクパターンの一部を取り出して拡大して示している。

【0079】

図7および図8に示すマスクパターンは、図4および図5を参照して前述した第2の実施の形態に係るマスクパターンと比べて、第4のラインパターン114の終端位置が第7のラインパターン131aあるいは第8のラインパターン132aの屈曲部分よりもさらに第2の領域12に近づいている点が異なり、その他は同じであるので図1および図2中と同一符号を付している。

【0080】

換言すれば、第4のラインパターン114の終端位置は、第3の領域13と第2の領域12との境界位置であり、この境界位置から長さ方向にL以上の位置で第7のラインパターン131aおよび第8のラインパターン132aのライン幅方向の一端側が段状に屈曲しており、この屈曲位置からさらに長さ方向にLの位置で第7のラインパターン131aおよび第8のラインパターン132aのライン幅方向の他端側が段状に屈曲している。

【0081】

<第3の実施形態に係る半導体装置>

図9は、図7のマスクパターンを使用して半導体装置上のフォトレジストに露光することにより得られるレジストパターンを光学シミュレーションにより求めた結果を示している。このシミュレーションに際して、光源の条件などは第1の実施の形態と同様である。

10

20

30

40

50

**【 0 0 8 2 】**

図9に示すレジストパターンは、図7のマスクパターンに対応して形成されており、配線の断線、ショートなどが見られず、また、ライン幅が極端に細い部分やスペースが極端に狭い部分も見られない。したがって、実際に半導体基板上にパターン露光を行った場合にも、十分なプロセスマージンを確保でき、良好な配線パターンが得られるものと予想される。

**【 0 0 8 3 】**

しかも、図7のマスクを使用した場合には、第2の実施形態に係る図4のマスクを使用した場合と比べて、第4のラインパターン113の終端部付近で生じた回折光と、マスクの第7のラインパターン131aの屈曲部付近および第8のラインパターン132aの屈曲部付近で生じた回折光との干渉を小さくすることができ、配線の断線やショートを防止する効果をさらに高めることができる。

10

**【 0 0 8 4 】**

なお、第3の実施形態に係る半導体装置の製法は、前述した第1の実施形態に準じて実施すればよく、また、図7のマスクパターンの反転マスクを使用して製造することも可能である。

**【 0 0 8 5 】**

<第4の実施の形態に係るマスク>

図10は、本発明の第4の実施の形態に係る半導体装置パターン露光用マスクに形成されているマスクパターンの一部を示す平面図である。

20

**【 0 0 8 6 】**

図10に示すマスクパターンは、図7および図8を参照して前述した第3の実施の形態に係るマスクパターンと比べて、第2の領域12における第5ラインパターン121bおよび第6のラインパターン122bのライン幅が第3の領域13と第2の領域12との境界位置およびその近傍で段状に変化し、第5ラインパターン121bおよび第6のラインパターン122bが互いに接近する方向に段状に太くなっている点が異なり、その他は同じであるので図1および図2中と同一符号を付している。

**【 0 0 8 7 】**

換言すれば、配線ピッチが $2 \times (L + S)$ のように大きい第5ラインパターン121bおよび第6のラインパターン122bのライン幅方向の一端側に補助パターンが付加されている。

30

**【 0 0 8 8 】**

<第4の実施形態に係る半導体装置>

図11は、図10のマスクパターンを使用して半導体装置上のフォトレジストに露光することにより得られるレジストパターンを光学シミュレーションにより求めた結果を示している。このシミュレーションに際して、光源の条件などは第1の実施の形態と同様である。

**【 0 0 8 9 】**

図11に示すレジストパターンは、図10のマスクパターンに対応して形成されており、配線の断線、ショートなどが見られず、また、ライン幅が極端に細い部分やスペースが極端に狭い部分も見られない。したがって、実際に半導体基板上にパターン露光を行った場合にも、十分なプロセスマージンを確保でき、良好な配線パターンが得られるものと予想される。

40

**【 0 0 9 0 】**

しかも、図10のマスクを使用した場合には、第3の実施形態に係る図7のマスクを使用した場合と比べて、第2の領域12における第5ラインパターン121bおよび第6のラインパターン122bのライン幅が第3の領域13と第2の領域12との境界位置およびその近傍で段状に広くなっている、この近傍で生じた回折光と第4のラインパターン114の終端部付近で生じた回折光の干渉を小さくすることができ、配線の断線やショートを防止する効果をさらに高めることができる。

**【 0 0 9 1 】**

50

なお、第4の実施形態に係る半導体装置の製法は、前述した第1の実施形態に準じて実施すればよく、また、図10のマスクパターンの反転マスクを使用して製造することも可能である。

【0092】

第1～第4の実施の形態においては、マスクの第1の領域11における第1のライン＆スペースパターンは、ライン幅L以上を有するラインパターンがそれぞれライン間スペースSを介して順に並ぶように形成され、第2の領域12における第2のライン＆スペースパターンは、ライン幅L以上を有するラインパターンがそれぞれライン間スペースS以上を介して順に並ぶように形成されている場合を示した。

【0093】

この第1～第4の実施の形態の変形例として、第1のライン＆スペースパターンは、ラインパターンがピッチPで順に並ぶように形成され、第2のライン＆スペースパターンは、ラインパターンがピッチ $2 \times P$ 以上で順に並ぶように形成された場合でも、第1～第4の実施の形態とほぼ同様の効果が得られる。

【0094】

また、この変形例に係るマスクパターンの反転マスクを使用して製造することも可能である。

【0095】

<第5の実施の形態に係るマスク>

第5の実施の形態に係るマスクは、EEPROMの一種であるNAND型フラッシュメモリのパターン露光用マスクである。

【0096】

ここで、NAND型フラッシュメモリについて簡単に説明する。不揮発性半導体記憶装置の一種であるEEPROMは、通常は、浮遊ゲートと制御ゲートが積層されたMOS構造のメモリセル(EEPROMセル)を用いており、電気的に書き換え可能である。NAND型フラッシュメモリは、上記EEPROMセルを複数個直列接続したNANDセルのアレイを有するものであり、高集積化に向いている。

【0097】

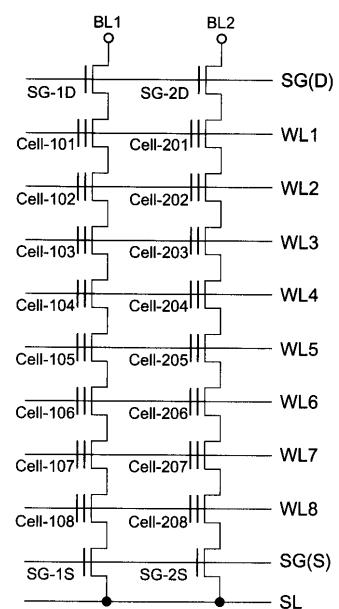

図12は、NAND型フラッシュメモリのメモリセルアレイにおけるワード線方向に配列された2ブロック分を取り出して等価回路を示している。

【0098】

8個のEEPROMセル101～108、201～208が直列に接続されてそれぞれNANDセルを構成しており、これらのNANDセルのドレイン側は、ドレイン側選択トランジスタ1D、2Dを介してビット線BL1、BL2に接続され、ソース側は、ソース側選択トランジスタ1S、2Sを介してソース線SLに接続されている。

【0099】

上記ドレイン側選択トランジスタ1個、NANDセル1個、ソース側選択トランジスタ1個を組み合わせたものを1ブロックとする複数個のブロックによってメモリセルアレイが構成されている。なお、NANDセルを構成するEEPROMセルの個数は8個に限らず、4個、16個、32個などいくつでも構わない。

【0100】

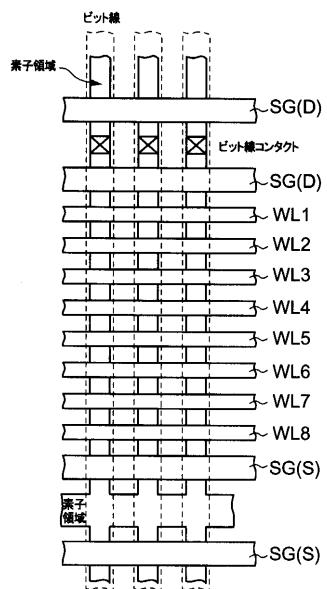

図13は、NAND型フラッシュメモリのメモリセルアレイにおけるワード線方向に配列された3ブロック分を取り出して平面パターンを示している。

【0101】

NANDセルの制御ゲート電極はワード線WL1～WL8に接続されており、このワード線WL1～WL8は隣接するNANDセルの制御ゲート電極に共通に接続されている。また、隣接するドレイン側選択トランジスタ1D、2Dのゲート電極は共通にドレイン側選択ゲート線SG(D)に接続され、隣接するソース側選択トランジスタ1S、2Sのゲート電極は共通にソース側選択ゲート線SG(S)に接続されている。

【0102】

10

20

30

40

50

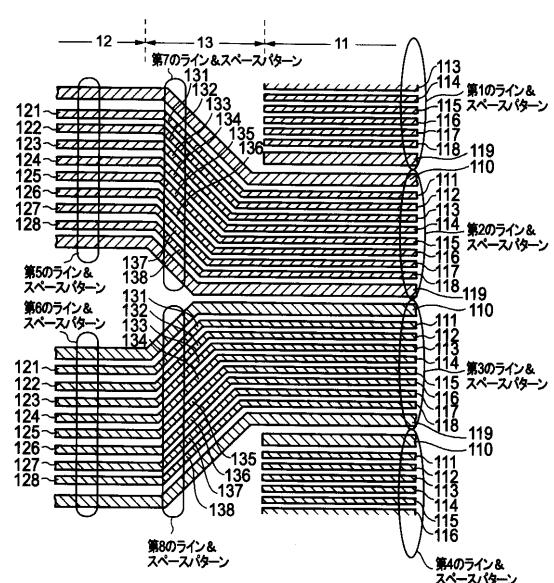

図14は、本発明の第5の実施の形態に係る半導体装置パターン露光用マスクに形成されているマスクパターンの一部を示す平面図である。図15は、図14のマスクパターンの一部を取り出して拡大して示している。

#### 【0103】

図14および図15に示すマスクパターンにおいて、11はNAND型フラッシュメモリのメモリセルアレイ領域に対応する第1のマスク領域、12は周辺回路領域に対応する第2のマスク領域、13はメモリセルアレイ領域と周辺回路領域との境界領域(接続領域)に対応する第3のマスク領域を示している。そして、斜線部は遮光部(遮光体パターン)、白地部は透光部を示しており、それぞれ対応して半導体基板上にラインパターン、スペースパターンを転写するためのものである。

10

#### 【0104】

第1のマスク領域11には、それぞれライン幅Lを有する第1のラインパターン111～第8のラインパターン118がそれぞれライン間スペースSを介して順に並び(配線ピッチはL+Sである)、かつ、上記ラインパターン111～118が少なくとも2組以上周期的に繰り返すように配置された第1のライン&スペースパターンが形成されている。この場合、上記ラインパターン111～118は、NANDセルの8本のワード線WL1～WL8に対応するものであり、このラインパターン111～118の各組の相互間に前記NANDセルのドレイン側選択ゲート線SG(D)およびソース側選択ゲート線SG(S)に対応するラインパターン110および119が配置されて形成されている。上記ドレイン側選択ゲート線に対応するラインパターン110の一端側は、そのライン幅のまま延長され、第3のマスク領域13内を経て第2のマスク領域12におけるラインパターン120に接続されている。

20

#### 【0105】

第2のマスク領域12には、それぞれライン幅L以上を有する第9のラインパターン121～第12のラインパターン124がそれぞれライン間スペースS以上を介して並び(配線ピッチは、2×(L+S)である)、かつ、上記ラインパターン121～124が少なくとも2組以上周期的に繰り返すように配置された第2のライン&スペースパターンが形成されている。この場合、上記ラインパターン121～124の各組の相互間に前記ドレイン側選択ゲート線に対応するラインパターン120が配置されている。

#### 【0106】

そして、第1のマスク領域11におけるラインパターン111～118のうちの例えば偶数番目の第2、第4、第6、第8のラインパターン112、114、116、118の各一端側は、延長され、第3のマスク領域13内を経て第2のマスク領域12におけるラインパターン121～124に接続されている。

30

#### 【0107】

これに対して、第1のマスク領域11におけるラインパターン111～118のうちの残りの奇数番目の第1、第3、第5、第7のラインパターン111、113、115、117の各一端側は、第3のマスク領域13において終端されている。この場合、第1のラインパターン111は、第1のマスク領域11と第3のマスク領域13との境界位置で終端されており、第3のラインパターン113および第7のラインパターン117はそのライン幅のまま延長され、第3のマスク領域13の中間位置で終端されており、第5のラインパターン115は第3のマスク領域13と第2のマスク領域12との境界位置までそのライン幅のまま延長されて終端されている。

40

#### 【0108】

換言すれば、第1のライン&スペースパターンのうちで第2のライン&スペースパターンに連ならない4本の各ラインパターン(第1、第3、第5、第7のラインパターン111、113、115、117)は、第1の領域11と第3の領域13との境界位置、第3の領域13と第2の領域12との境界位置、第3の領域13内のいずれかの位置で終端され、かつ、第1のライン&スペースパターンの配列の中央部に位置するほど終端位置が第2の領域12に近づいている。

#### 【0109】

50

即ち、第3のマスク領域13には、第2のラインパターン112と第9のラインパターン121に連なる第13のラインパターン131、第4のラインパターン114と第10のラインパターン122に連なる第14のラインパターン132、第6のラインパターン116と第11のラインパターン123に連なる第15のラインパターン133および第8のラインパターン118と第12のラインパターン124に連なる第16のラインパターン134が並び、かつ、上記ラインパターン131～134が少なくとも2組以上周期的に繰り返すように配置された第3のライン&スペースパターンが形成されている。この場合、第1のマスク領域11における第3、第5、第7のラインパターン111、113、115、117は第3のマスク領域13内に延長されており、第3のマスク領域13内のラインパターンの配列順は、131、113、132、115、133、117、134である。さらに、上記ラインパターン131～134の各組の相互間に前記ドレイン側選択ゲート線に対応するラインパターン130が配置されている。10

#### 【0110】

そして、上記ラインパターン131～134は、第3の領域13内の長さ方向の途中でライン幅が段状に変化するとともに段状に屈曲し、第1のライン&スペースパターン側よりも第2のライン&スペースパターン側の方がライン幅が段状に太くなるように形成されており、かつ、ライン幅が段状に変化する位置は第3のライン&スペースパターンの配列の中央部に位置するほど第2の領域12に近づいている。

#### 【0111】

この場合、第13のラインパターン131が屈曲する向きは、第1のラインパターン111に近付く方向になっており、屈曲部分の長さはL以上（パターンの占有面積を抑制する点からLとすることが適当である）であり、そのライン幅方向の一端が段状に変化する位置は、第1のラインパターン111の終端位置から長さ方向にS以上（パターンの占有面積を抑制する点からSとすることが適当である）の位置である。20

#### 【0112】

また、第3のラインパターン113の終端位置は、第13のラインパターン131のライン幅方向の他端が段状に変化する位置から長さ方向にS以上（パターンの占有面積を抑制する点からSとすることが適当である）の位置である。

#### 【0113】

また、第14のラインパターン132が屈曲する向きは、第3のラインパターン113に近付く方向になっており、屈曲部分の長さはL以上（パターンの占有面積を抑制する点からLとすることが適当である）であり、そのライン幅方向の一端が段状に変化する位置は、第3のラインパターン113の終端位置から長さ方向にS以上（パターンの占有面積を抑制する点からSとすることが適当である）の位置である。30

#### 【0114】

また、第5のラインパターン115の終端位置は、第14のラインパターン132のライン幅方向の他端が段状に変化する位置から長さ方向にL以上（パターンの占有面積を抑制する点からLとすることが適当である）の位置である。

#### 【0115】

また、第15のラインパターン133が屈曲する向きは、第7のラインパターン117に近付く方向になっており、屈曲部分の長さはL以上（パターンの占有面積を抑制する点からLとすることが適当である）であり、そのライン幅方向の一端が段状に変化する位置は、第3のラインパターン113の終端位置から長さ方向にS以上（パターンの占有面積を抑制する点からSとすることが適当である）の位置である。つまり、第15のラインパターン133が屈曲する位置は第14のラインパターン132が屈曲する位置と同一線上である。40

#### 【0116】

また、第7のラインパターン117の終端位置は、第13のラインパターン131のライン幅方向の他端が段状に変化する位置から長さ方向にS以上（パターンの占有面積を抑制する点からSとすることが適当である）の位置である。つまり、第7のラインパターン117の終端位置は第3のラインパターン113の終端位置と同一線上である。

#### 【0117】

10

20

30

40

50

また、第16のラインパターン134が屈曲する向きは、第7のラインパターン117から遠去かる方向になっており、そのライン幅方向の一端が段状に変化する位置は、第1のラインパターン111の終端位置から長さ方向にS以上(パターンの占有面積を抑制する点からSとすることが適当である)の位置であり、屈曲部分の長さはL以上(パターンの占有面積を抑制する点からLとすることが適当である)である。つまり、第16のラインパターン134が屈曲する位置は第13のラインパターン131が屈曲する位置と同一線上である。

【0118】

上述したマスクパターンにおいて、マスク上の最小スペースはSであり、このマスク上の最小スペースSは、ライン&スペースパターンの最小スペースSと合わせることが望ましい。その理由は第1の実施の形態で前述した通りである。

10

【0119】

なお、第1のマスク領域11の他端側にも、図1中に示した第3のマスク領域13および第2のマスク領域12と対称的に、図示しない第3のマスク領域および第2のマスク領域が存在している。そして、第1のマスク領域11における第2、第4、第6、第8のラインパターン112、114、116、118の各他端側は、図示しない第3のマスク領域13において終端されている。

【0120】

また、第1のマスク領域11における第1、第3、第5、第7のラインパターン111、113、115、117の各他端側は、延長され、図示しない第3のマスク領域13内を経て図示しない第2のマスク領域12のラインパターンに接続されている。こうして、第1のマスク領域11の全てのラインパターンが第2のマスク領域へ接続される。

20

【0121】

<第5の実施形態に係る半導体装置>

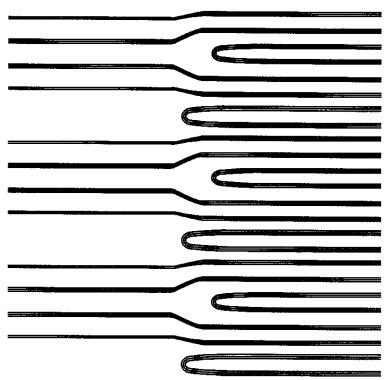

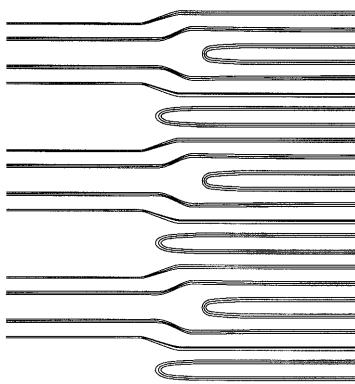

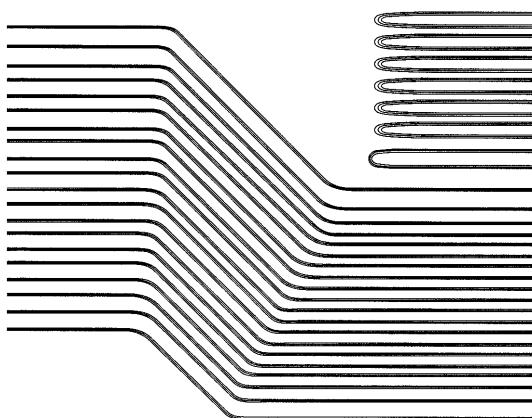

図16は、図14のマスクパターンを使用してNAND型フラッシュメモリ上のフォトレジストに露光することにより得られるレジストパターンを光学シミュレーションにより求めた結果を示している。このシミュレーションに際して、光源の条件などは第1の実施の形態と同様である。

30

【0122】

図16に示すレジストパターンは、図14のマスクパターンに対応して形成されており、配線の断線、ショートなどが見られず、また、ライン幅が極端に細い部分やスペースが極端に狭い部分も見られない。したがって、実際に半導体基板上にパターン露光を行った場合にも、十分なプロセスマージンを確保でき、良好な配線パターンが得られるものと予想される。

【0123】

なお、第5の実施形態に係る半導体装置の製法は、前述した第1の実施形態に準じて実施すればよく、また、図14のマスクパターンの反転マスクを使用して製造することも可能である。

【0124】

<第6の実施の形態に係るマスク>

図17は、本発明の第6の実施の形態に係る半導体装置パターン露光用マスクに形成されているマスクパターンの一部を示す平面図である。

40

【0125】

図17に示すマスクパターンは、NAND型フラッシュメモリのパターン露光用マスクであり、11はNAND型フラッシュメモリのメモリセルアレイにおける第1のマスク領域、12は周辺回路領域に対応する第2のマスク領域、13はメモリセルアレイ領域と周辺回路領域との境界領域(接続領域)に対応する第3のマスク領域を示している。

【0126】

NAND型フラッシュメモリのメモリセルアレイにおいては、図12に示した等価回路を参照して前述したように、例えばドレイン側選択トランジスタ1D、8個のEEPROMセル101～108が直列接続されてなるNANDセル、ソース側選択トランジスタ1Sを組み合わせたものを1

50

ブロックとする複数個のブロックによってメモリセルアレイが構成されている。ここでは、ビット線方向に配列された4ブロック分に対応する領域を示している。

【0127】

第1のマスク領域11には、メモリセルアレイ領域の第1のブロック、第2のブロック、第3のブロック、第4のブロックの各NANDセルのワード線WL1～WL8を形成するためのそれぞれ遮光体からなる8本のラインパターン111～118がライン間スペースSを介してピッチP1で順に並ぶように形成された少なくとも4個(第1、第2、第3、第4)のライン&スペースパターンが配置されている。

【0128】

第2のマスク領域12には、それぞれ遮光体からなる8本のラインパターン121～128がライン間スペースを介して $2 \times P1$ 以上のピッチで繰り返すように形成された第5、第6のライン&スペースパターンが配置されている。

10

【0129】

第3のマスク領域13には、第7のライン&スペースパターンと第8のライン&スペースパターンが繰り返すように配置されている。上記第7のライン&スペースパターンは、第1のマスク領域11における第2のライン&スペースパターンの8本のラインパターン111～118と第2のマスク領域12における第5のライン&スペースパターンの8本のラインパターン121～128に連なるそれぞれ遮光体からなる8本のラインパターン131～138およびライン間スペースパターンが繰り返すように形成されている。前記第8のライン&スペースパターンは、第3のライン&スペースパターンの8本のラインパターン111～118と第6のライン&スペースパターンの8本のラインパターン121～128に連なるそれぞれ遮光体からなる8本のラインパターン131～138およびライン間スペースパターンが繰り返すように形成されている。

20

【0130】

第1のマスク領域11における第1のライン&スペースパターンおよび第4のライン&スペースパターンの各ラインパターン111～118は、第1の領域11と第3の領域13との境界位置で終端されている。

【0131】

第3のマスク領域13における第7のライン&スペースパターンおよび第8のライン&スペースパターンの各ラインパターン131～138の各一部は、第1のマスク領域11のパターンの長さ方向に対して斜めに配置されており、かつ、斜めに配置された部分のピッチP2は、第1のマスク領域11におけるラインパターン111～118のピッチP1よりも大きく、第2のマスク領域12におけるラインパターン121～128のピッチ $2 \times P1$ よりも小さくなっている。即ち、 $P1 < P2 < 2 \times P1$ である。

30

【0132】

そして、第1、第2、第3、第4のライン&スペースパターンは、第1のマスク領域11で少なくとも2組以上周期的に繰り返すように配置され、第5、第6のライン&スペースパターンは第2のマスク領域12で少なくとも2組以上周期的に繰り返すように配置され、第7、第8のライン&スペースパターンは第3のマスク領域13で少なくとも2組以上周期的に繰り返すように配置されている。

40

【0133】

なお、第1のマスク領域11の他端側にも、図17中に示した第3のマスク領域13および第2のマスク領域12と対称的に、図示しない第3のマスク領域および第2のマスク領域が存在している。そして、第1のマスク領域における第2、第3のライン&スペース中のラインパターン111～118(第2、第3のブロック内の各メモリセルのゲート線)の各他端側は、図示しない第3のマスク領域において終端されている。また、第1のマスク領域における第1、第4のライン&スペース中のラインパターン111～118(第1、第4のブロック内の各メモリセルのゲート線)の各他端側は、延長され、図示しない第3のマスク領域内を経て図示しない第2のマスク領域のラインパターンに接続されている。こうして、第1のマスク領域11の全てのラインパターン111～118が第2のマスク領域へ接続されるよ

50

うにしている。

【0134】

なお、図17中、110はNANDセルブロックのドレイン側選択ゲート線SG(D)に対応するラインパターンであり、119はソース側選択ゲート線SG(S)に対応するラインパターンである。

【0135】

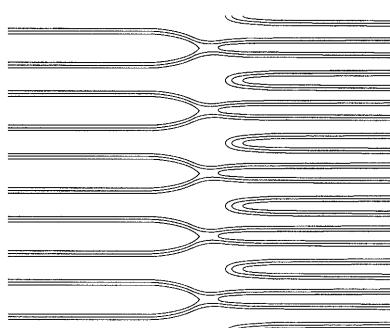

<第6の実施形態に係る半導体装置>

図18は、図17のマスクパターンを使用してNAND型フラッシュメモリ上のフォトトレジストに露光することにより得られるレジストパターンを光学シミュレーションにより求めた結果を示している。このシミュレーションに際して、光源の条件などは第1の実施の形態と同様である。

10

【0136】

図18に示すレジストパターンは、図17のマスクパターンに対応して形成されており、配線の断線、ショートなどが見られず、また、ライン幅が極端に細い部分やスペースが極端に狭い部分も見られない。したがって、実際に半導体基板上にパターン露光を行った場合にも、十分なプロセスマージンを確保でき、良好な配線パターンが得られるものと予想される。

【0137】

なお、第6の実施形態に係る半導体装置の製法は、前述した第1の実施形態に準じて実施すればよく、また、図17のマスクパターンの反転マスクを使用して製造することも可能である。

20

【0138】

【発明の効果】

上述したように本発明によれば、配線ピッチが異なる領域間の接続領域における光リソグラフィを用いた微細な配線パターンを形成する時の解像度や焦点深度の悪化を抑制し、配線パターンの断線やショートが発生する可能性を低減し、高集積化が可能となる半導体装置を提供することができる。

【図面の簡単な説明】

【図1】本発明の第1の実施の形態に係る半導体装置パターン露光用マスクに形成されているマスクパターンの一部を示す平面図。

30

【図2】図1のマスクパターンの一部を取り出して拡大して示す平面図。

【図3】図1のマスクパターンを使用して半導体装置上のフォトトレジストに露光することにより得られるレジストパターンを光学シミュレーションにより求めた結果を示す図。

【図4】本発明の第2の実施の形態に係る半導体装置パターン露光用マスクに形成されているマスクパターンの一部を示す平面図。

【図5】図4のマスクパターンの一部を取り出して拡大して示す平面図。

【図6】図4のマスクパターンを使用して半導体装置上のフォトトレジストに露光することにより得られるレジストパターンを光学シミュレーションにより求めた結果を示す図。

【図7】本発明の第3の実施の形態に係る半導体装置パターン露光用マスクに形成されているマスクパターンの一部を示す平面図。

40

【図8】図7のマスクパターンの一部を取り出して拡大して示す平面図。

【図9】図7のマスクパターンを使用して半導体装置上のフォトトレジストに露光することにより得られるレジストパターンを光学シミュレーションにより求めた結果を示す図。

【図10】本発明の第4の実施の形態に係る半導体装置パターン露光用マスクに形成されているマスクパターンの一部を示す平面図。

【図11】図10のマスクパターンを使用して半導体装置上のフォトトレジストに露光することにより得られるレジストパターンを光学シミュレーションにより求めた結果を示す図。

【図12】本発明の第5の実施の形態を説明するためにNAND型フラッシュメモリのメモリセルアレイにおけるワード線方向に配列された2ブロック分を取り出して等価回路を示す

50

図。

【図13】図12のNAND型フラッシュメモリのメモリセルアレイにおけるワード線方向に配列された3ブロック分を取り出して平面パターンを示す図。

【図14】本発明の第5の実施の形態に係る半導体装置パターン露光用マスクに形成されているマスクパターンの一部を示す平面図。

【図15】図14のマスクパターンの一部を取り出して拡大して示す平面図。

【図16】図14のマスクパターンを使用してNAND型フラッシュメモリ上のフォトレジストに露光することにより得られるレジストパターンを光学シミュレーションにより求めた結果を示す図。

【図17】本発明の第6の実施の形態に係る半導体装置パターン露光用マスクに形成されているマスクパターンの一部を示す平面図。 10

【図18】図17のマスクパターンを使用してNAND型フラッシュメモリ上のフォトレジストに露光することにより得られるレジストパターンを光学シミュレーションにより求めた結果を示す図。

【図19】半導体メモリの一般的なパターン配置を示す図。

【図20】図19中のメモリセルアレイ領域と周辺回路領域とを接続する配線パターンが形成されたパターン露光用マスクを示す図。

【図21】図20に示した配線パターンが形成されたパターン露光用マスクを用いて半導体基板上のレジストに露光した時に得られるレジストパターンをシミュレーションにより求めた結果を示す図。 20

【符号の説明】

11... 第1のマスク領域、

12... 第2のマスク領域、

13... 第3のマスク領域、

111 ~ 114 ... 第1 ~ 第4のラインパターン、

121 ... 第5のラインパターン、

122 ... 第6のラインパターン、

131 ... 第7のラインパターン、

132 ... 第8のラインパターン、

L ... ライン幅、 30

S ... ライン間スペース。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【 図 1 3 】

【 図 1 4 】

〔 図 15 〕

〔 図 16 〕

【図17】

【図18】

【図19】

【図20】

【図21】

---

フロントページの続き

| (51)Int.Cl.                     | F I                |

|---------------------------------|--------------------|

| <b>H 01 L 21/8247 (2006.01)</b> | H 01 L 21/88 B     |

| <b>H 01 L 27/115 (2006.01)</b>  | H 01 L 27/10 4 3 4 |

| <b>H 01 L 29/792 (2006.01)</b>  | H 01 L 29/78 3 7 1 |

| <b>H 01 L 29/788 (2006.01)</b>  | H 01 L 27/10 4 7 1 |

| <b>H 01 L 27/10 (2006.01)</b>   |                    |

(72)発明者 竹内 祐司

神奈川県横浜市磯子区新杉田町8番地 株式会社東芝横浜事業所内

(72)発明者 荒井 史隆

神奈川県横浜市磯子区新杉田町8番地 株式会社東芝横浜事業所内

審査官 南 宏輔

(56)参考文献 特開2000-019709(JP,A)

特開平09-162305(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/027

H01L 21/82

H01L 27/10

H01L 29/788

H01L 29/792

G03F 1/00-16

G03F 7/20-24